# Trends and patterns in ASIC and FPGA use in space missions and impact in technology roadmaps of the European Space Agency

# **Master Thesis**

Roger Boada Gardenyes

15<sup>th</sup> August 2012

#### **ABSTRACT**

ASIC (Application-Specific Integrated Circuit) and FPGA (Field-Programmable Gate Array) are the two most complex and versatile integrated circuit technologies used nowadays in space missions. They are key technologies and perform the core of the avionics control and data processing of every satellite and spacecraft. Quantities used of ASIC and FPGA in space missions have been increasing significantly in the last years. Some of the fundamental differences between ASIC and FPGA are the development costs and the reprogrammability features, while in both cases there is a lengthy and costly customer design process behind. This research attempts to quantify the use of ASIC and FPGA technologies in space missions in the last years, to show the patterns and trends of use and to assess how these conclusions match the priorities established in the present technology roadmaps of the European Space Agency. The results of this study will be used as valuable inputs for future strategic and investment decisions of the European Space Agency and the European space community actors.

Keywords: ASIC, FPGA, European Space Agency, space missions, technology roadmaps.

# **AKNOWLEDGEMENTS**

In these last lines of my thesis I would like to thank all the people that have made possible this Master Thesis and with who I have shared one of the most valuable experiences of my life.

First of all, my biggest gratitude to Agustin Fernandez-Leon, head of the Microelectronics section in ESA, to give me the great opportunity to undertake an internship in the European Space Agency. It has been an amazing and exciting work and life experience that I am sure it will be a very important milestone in my life. I really appreciate all the effort and time he has spent with me during this last months teaching, helping and supporting me in all the aspects of this research. I think I could not have a better mentor than him.

In addition, all my thanks to my supervisors from the Technical University from Delft, Scott Cunningham, Petra Heijnen and Wil Thissen, to accept the challenge to supervise my Master Thesis without knowing me before and facing the difficulties of being an exchange student and doing the research in an external company. I think it has been a very good experience from both sides and it has been very interesting to meet both the visions from the university and the industry in this project.

I would like also to give thanks to my colleagues in ESA which accompanied me during my stay and make it an unforgettable experience. Specially, to Gabriele Tiotto and Javier Eroles, my officemates, for their help and support in the last steps of my research and for the all the great times and fun we had together in the work. And, of course, my crazy friend Johan and the rest of stagiaires and YGTs to share this experience with them and for all the activities and parties we have done together during our stay in ESA. Also, many thanks to my Dutch housemates to be my family in Leiden and introduce me to the real Dutch life style.

I want also to give thanks to all ESA managers and engineers that participate and collaborate in this research because without their contribution and work this research will have not been possible. Specially, the people from the Microelectronics section for their warm welcome in ESA and all their support during this months.

Finally, my warmest regards to my parents Pere and Josepa, and my brother Guillem, that even though the distance of being studying abroad, they have lived all this experience very close to me, being my best support not only in the good moments but also in the most difficult ones. I am very happy to dedicate this thesis to them.

# **ACRONYMS**

AFMS ASIC, FPGA, Microprocessor and Standard ASIC

ARTES Advanced Research in Telecommunication Systems

ASIC Application Specific Integrated Circuit

CMOS Complementary Metal Oxide Semiconductor

CNES Centre National d'Études Spatiales

DCL Declared Component List

DMS Data Management System

ECI European Component Initiative

ESCC Electronic, Electrical and Electromechanical ESCC European Space Components Coordination

ESA European Space Agency

FPGA Field Programmable Gate Array

GEO Geostationary Earth Orbit

GSTP General Support Technology Programme

IC Integrated Circuit

IPC Industrial Policy Committee

ITAR International Traffic in Arms Regulation

ITRS International Technology Roadmap for Semiconductors

LEO Low Earth Orbit

MEO Medium Earth Orbit

MTR Microelectronics Technology Roadmaps

NASA National Aerospace and Space Administration

NRE Non-Recurring Engineering

PA Product Assurance

PF Platform

PL Payload

THAG Technology Harmonisation Advisory Group

TDM Technical Dossier of Microelectronics

TRP Technology Research Programme

# **TABLE OF CONTENTS**

| TAB | LE OF FIG                                             | GURES                                                    | V   |

|-----|-------------------------------------------------------|----------------------------------------------------------|-----|

| TAB | LE OF TA                                              | BLES                                                     | VII |

| 1   | INTROD                                                | UCTION                                                   | 1   |

| 1.1 | Motiv                                                 | vation of research                                       | 1   |

| 1.2 | Resea                                                 | arch objectives                                          | 4   |

| 1.3 | Antic                                                 | ipated issues                                            | 7   |

| 2   | BACKGR                                                | ROUND INFORMATION                                        | 8   |

| 2.1 | ASIC,                                                 | FPGA, Microprocessor and Standard ASIC technology        | 8   |

| 2.2 | European Space Agency (ESA)                           |                                                          | 14  |

|     | 2.2.1                                                 | ESA Facts                                                | 14  |

|     | 2.2.2                                                 | ESA space missions                                       | 14  |

|     | 2.2.3                                                 | ESA Technology Programmes                                | 16  |

|     | 2.2.4                                                 | ESA Organization                                         | 18  |

|     | 2.2.5                                                 | European Space Technology Harmonisation                  | 19  |

| 2.3 | Techr                                                 | nology Roadmaps                                          | 24  |

| 3   | METHODOLOGY                                           |                                                          | 28  |

| 3.1 | Integ                                                 | rated circuit technologies and space missions studied    | 28  |

|     | 3.1.1                                                 | Integrated circuit technologies subject of this research | 28  |

|     | 3.1.2                                                 | IC Technical parameters                                  | 29  |

|     | 3.1.3                                                 | Space Missions                                           | 30  |

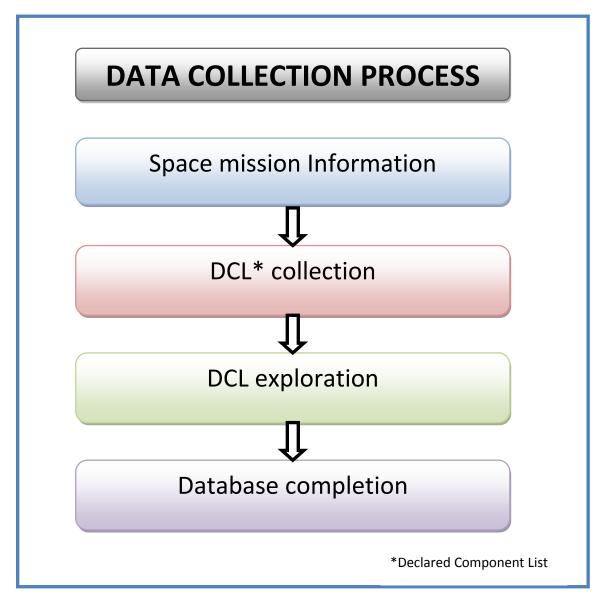

| 3.2 | Data                                                  | collection                                               | 34  |

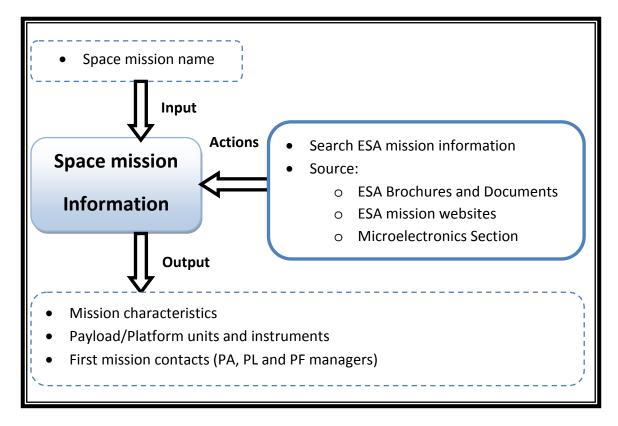

|     | 3.2.1                                                 | Space mission information                                | 39  |

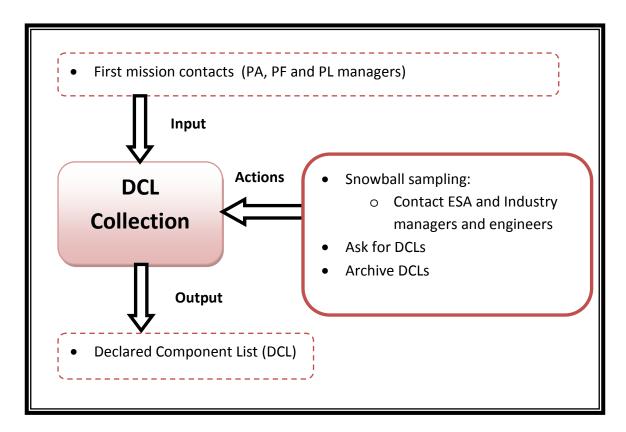

|     | 3.2.2                                                 | DCL collection                                           | 40  |

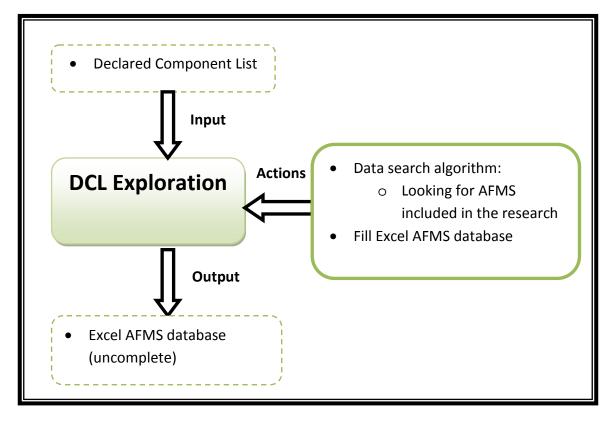

|     | 3.2.3                                                 | DCL exploration                                          | 42  |

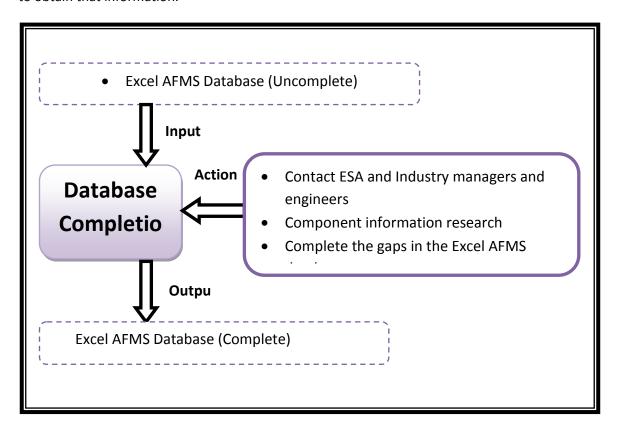

|     | 3.2.4                                                 | Database completion                                      | 45  |

| 3.3 | Data Exploration                                      |                                                          | 48  |

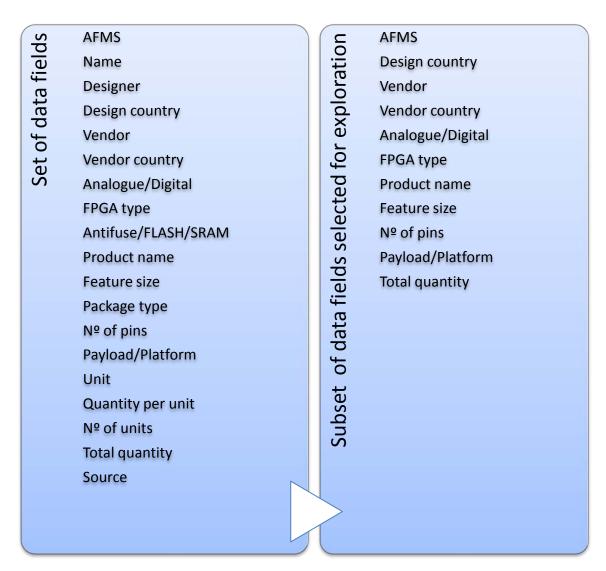

|     | 3.3.1                                                 | Subset of IC parameters explored                         | 48  |

|     | 3.3.2                                                 | Types of tables and graphs used for the data exploration | 56  |

| 3.4 | ESA N                                                 | Aicroelectronics roadmap exploration                     | 60  |

| 4   | RESULTS                                               | S                                                        | 62  |

| 4.1 | Quantities and types of AFMS used in space missions63 |                                                          |     |

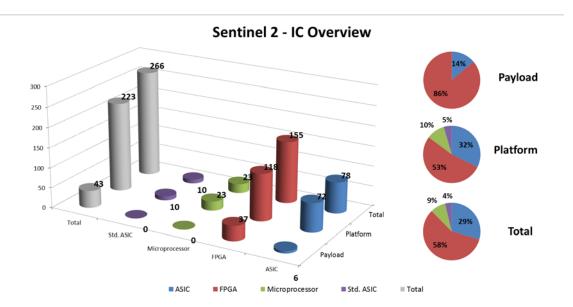

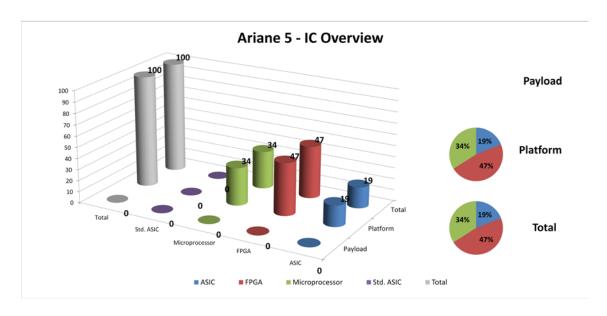

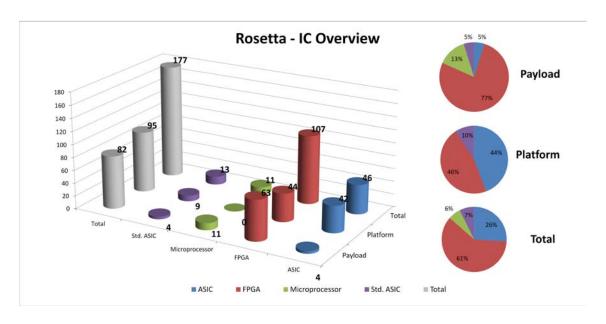

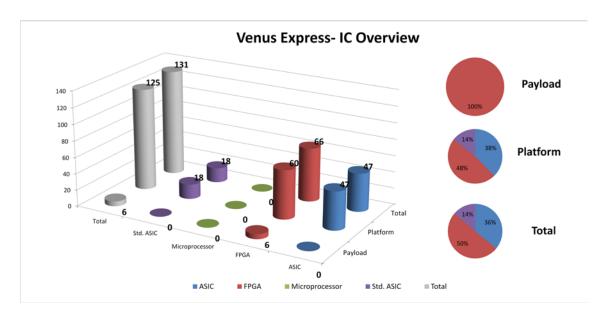

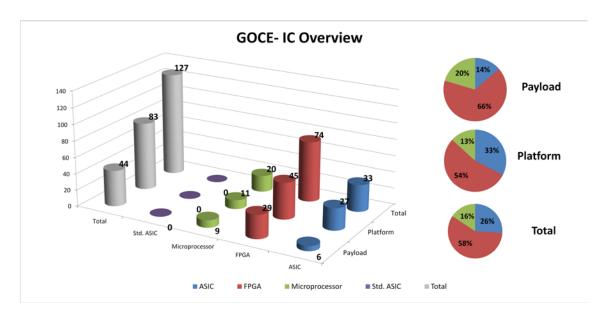

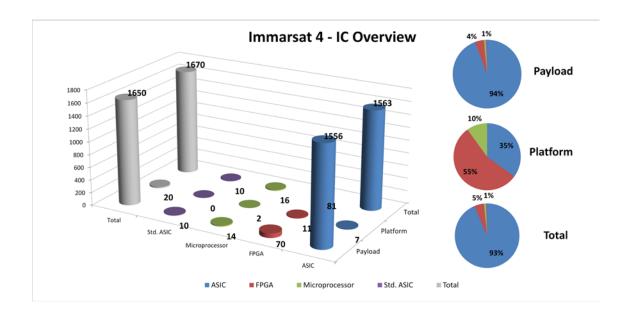

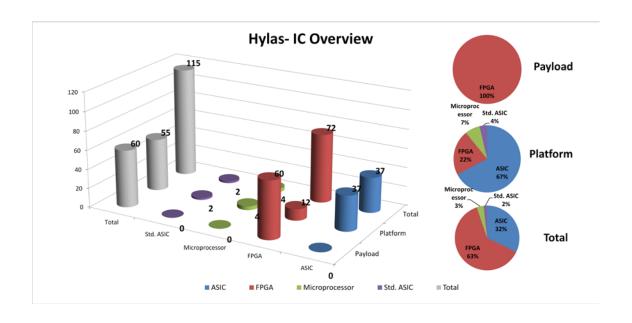

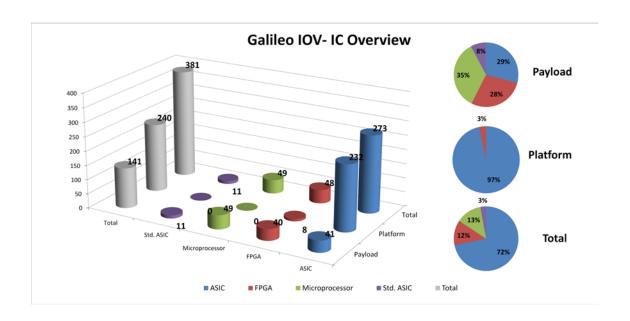

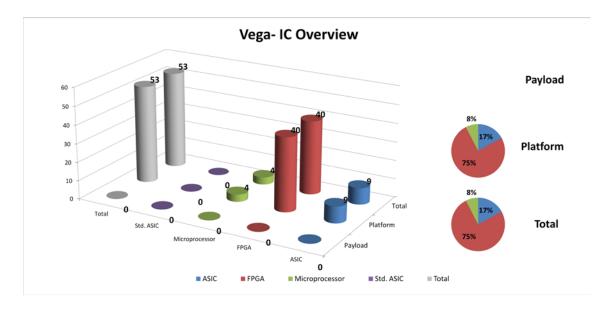

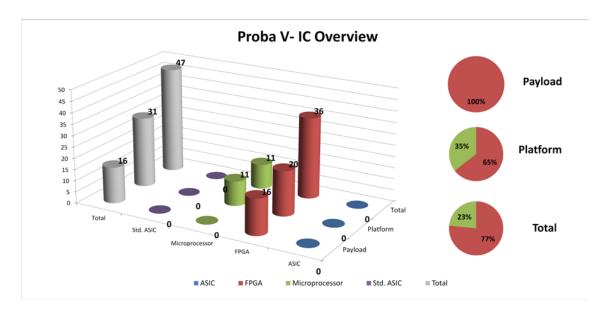

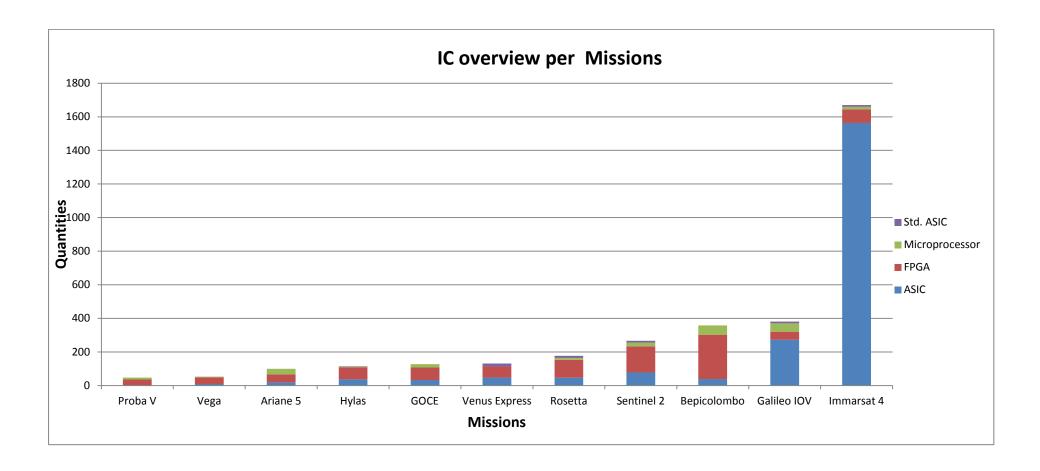

|     | 4.1.1                                                                                | IC Overview                                                                      | 64  |

|-----|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|

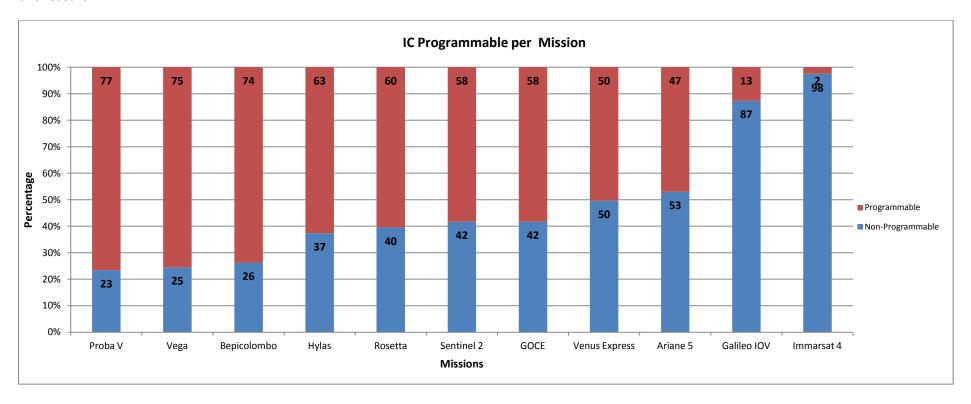

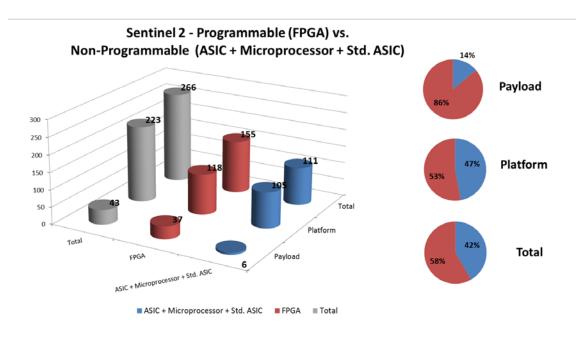

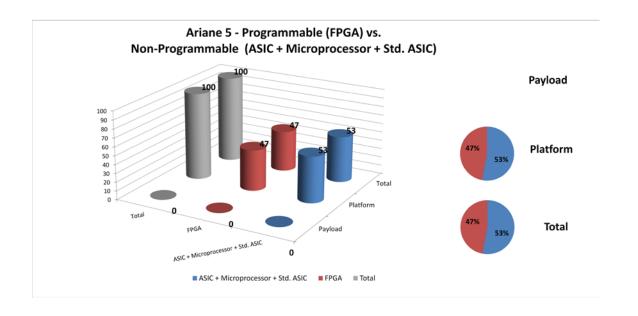

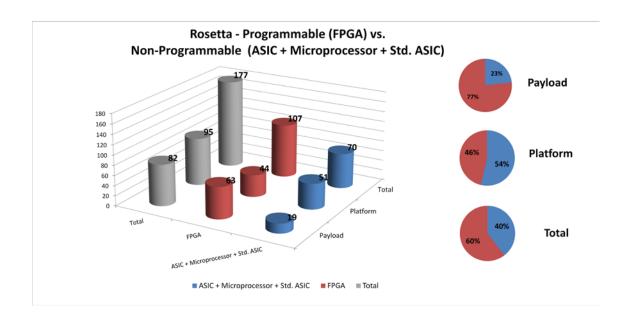

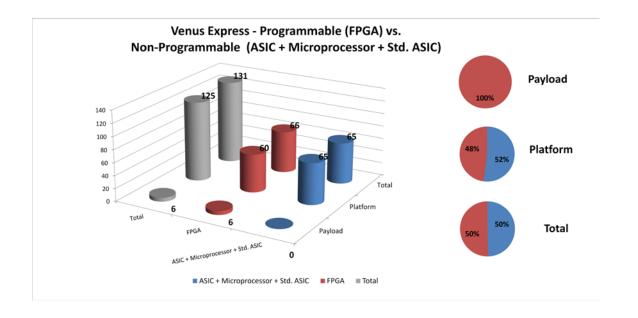

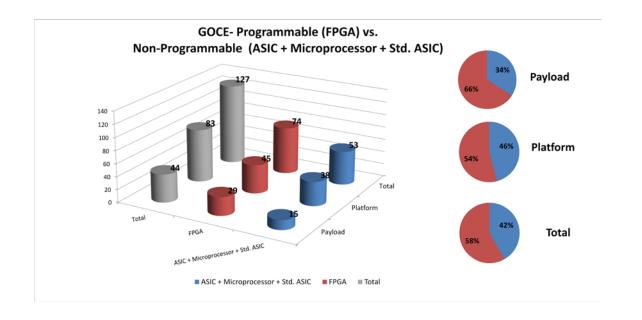

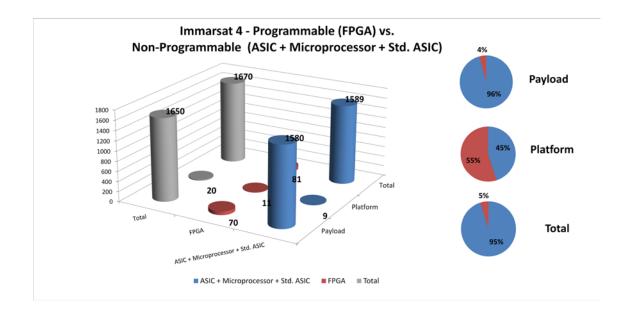

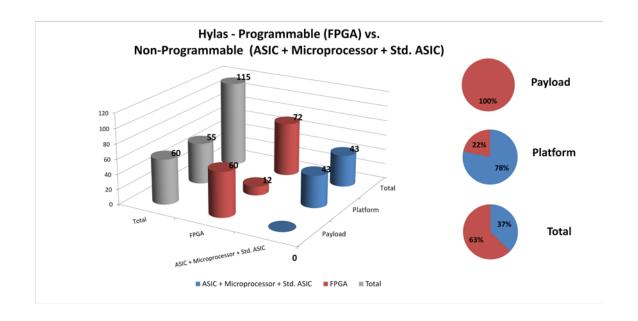

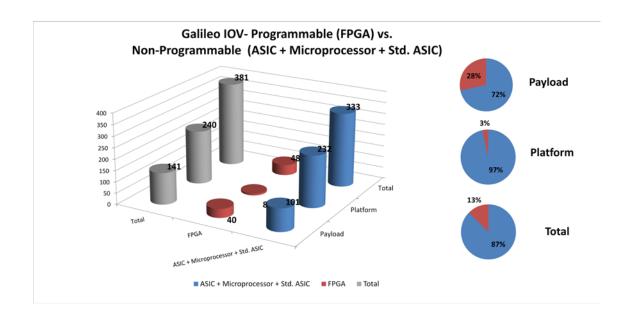

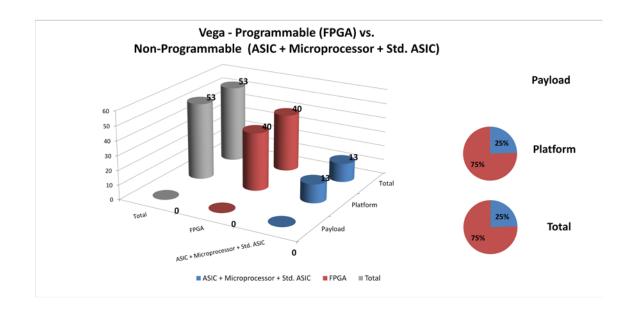

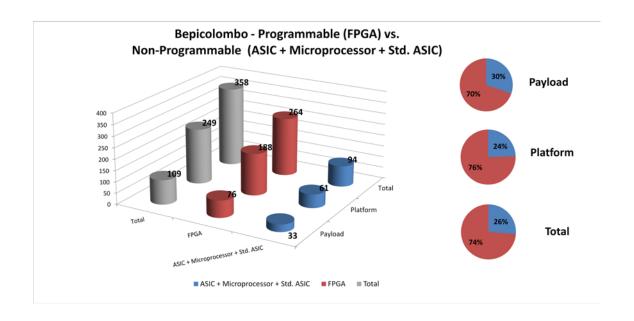

|     | 4.1.2<br>ASIC)                                                                       | Programmable (FPGA) vs. Non-programmable (ASIC + Microprocessor + Std. 67        |     |

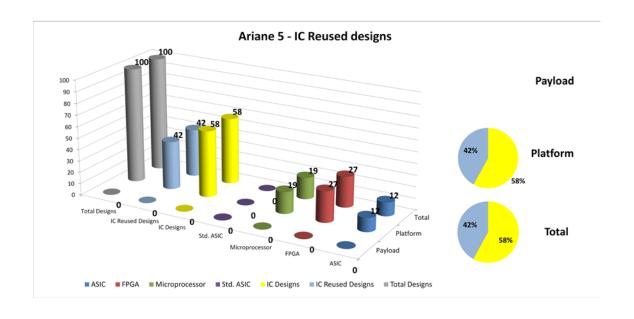

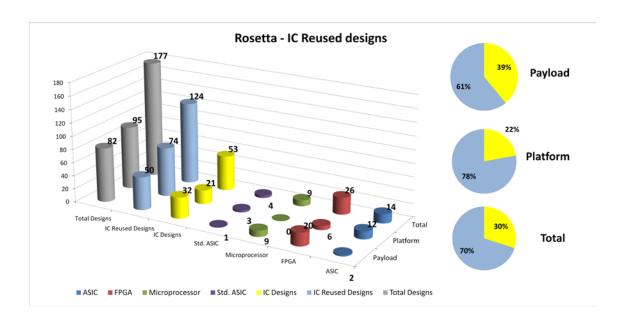

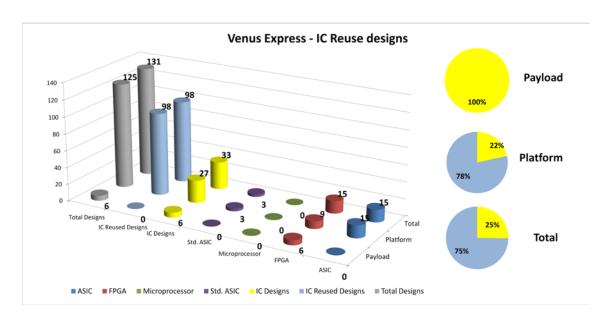

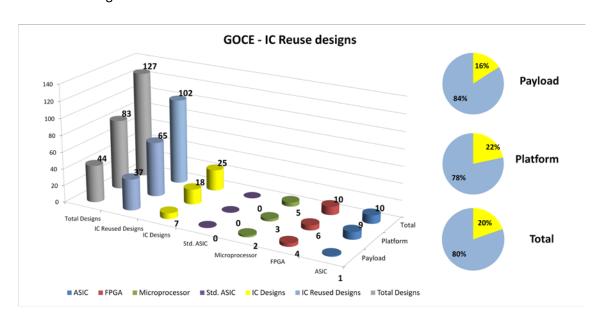

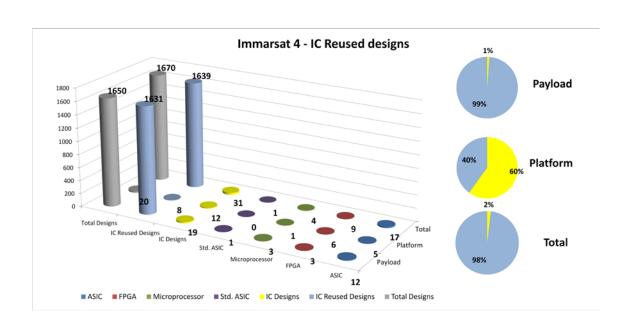

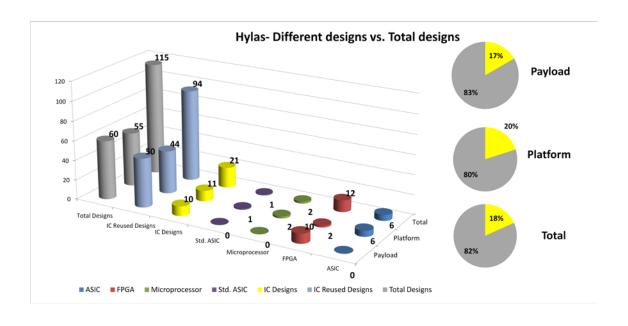

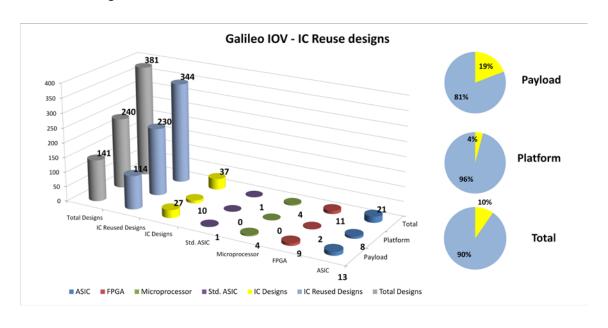

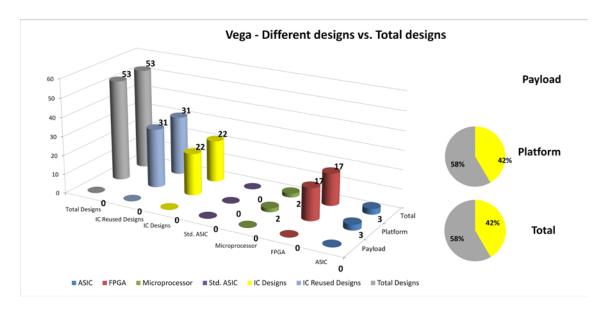

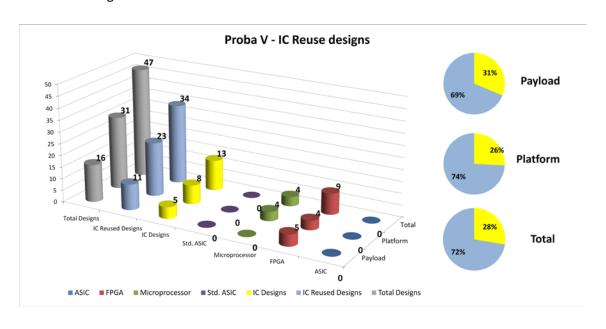

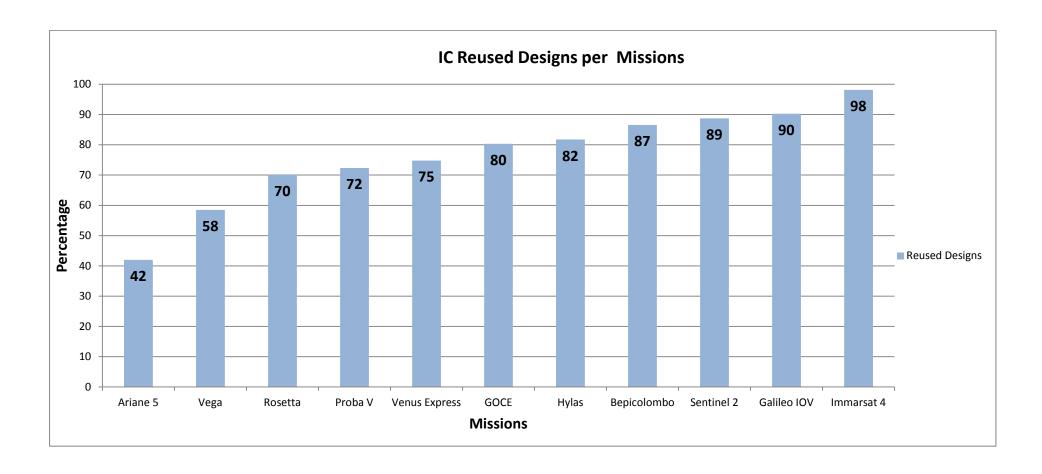

|     | 4.1.3                                                                                | Reused IC designs                                                                | 69  |

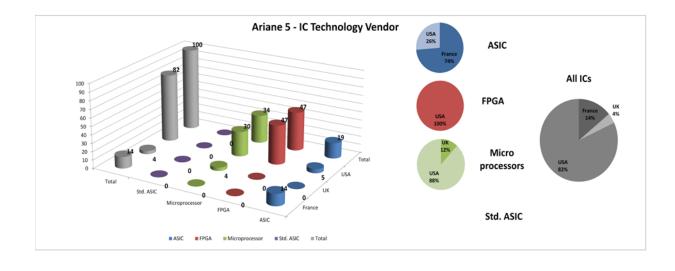

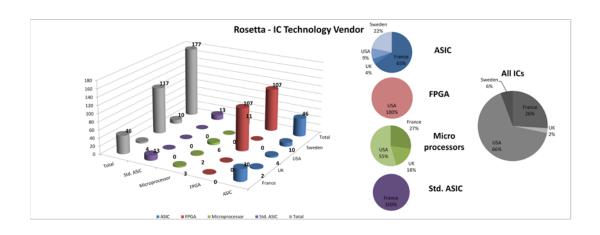

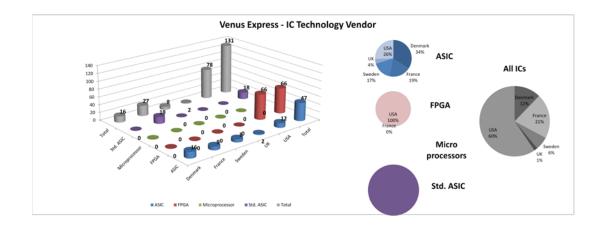

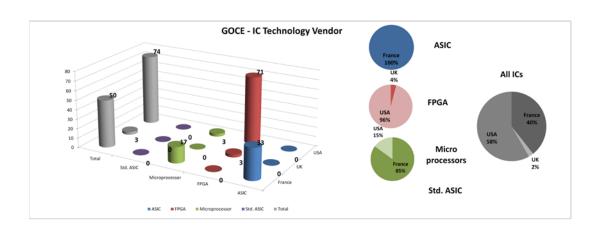

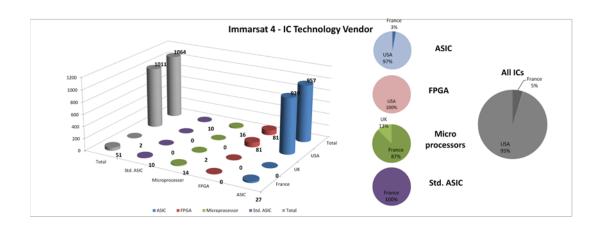

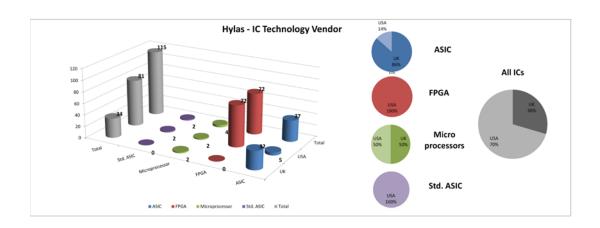

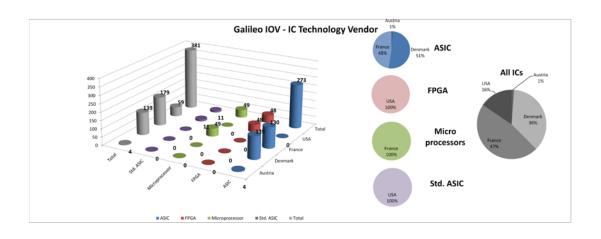

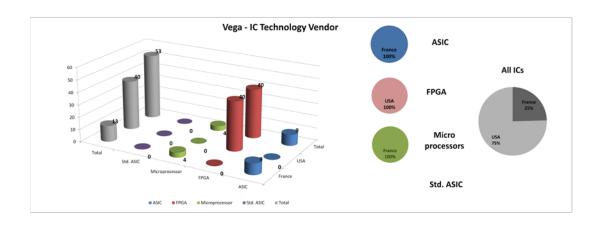

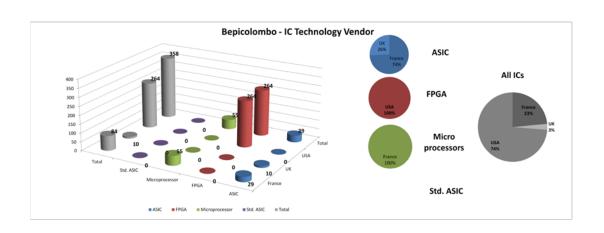

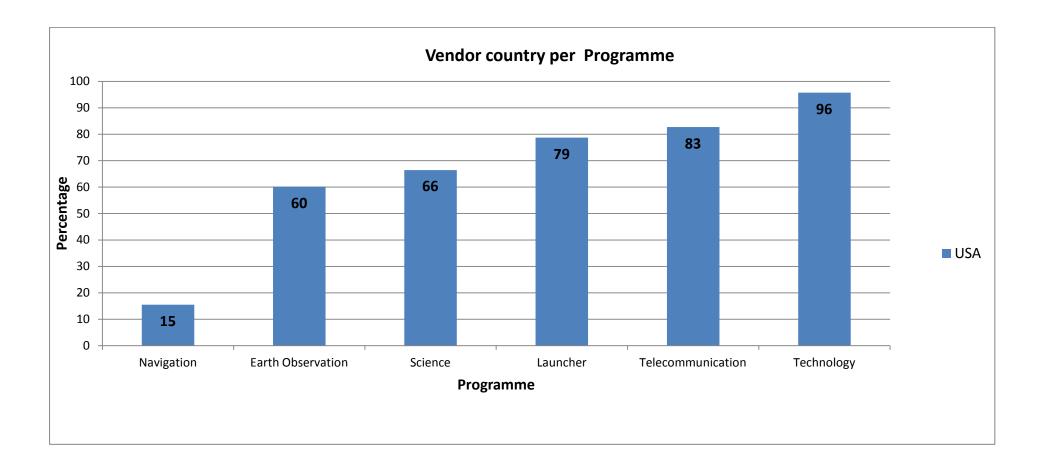

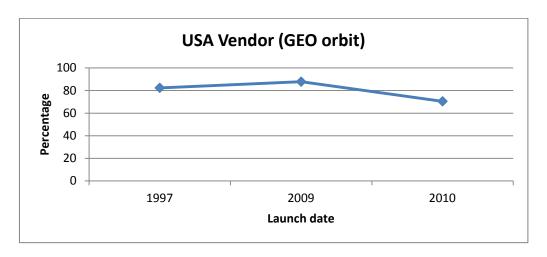

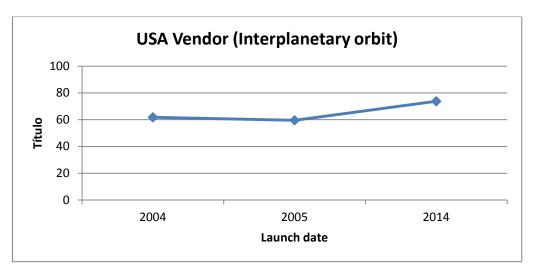

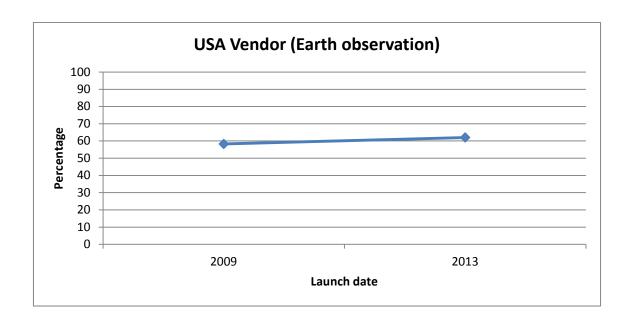

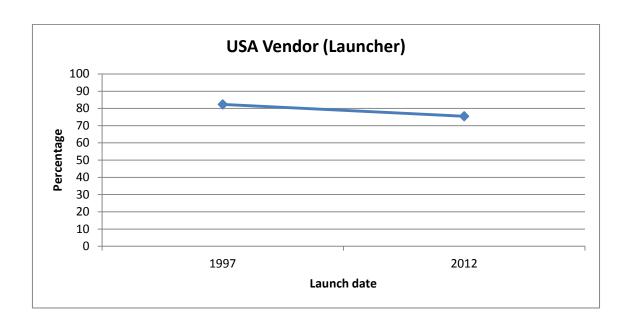

|     | 4.1.4                                                                                | IC Technology vendor country                                                     | 71  |

| 4.2 | Trends                                                                               | and patterns of use of AFMS in space missions                                    | 74  |

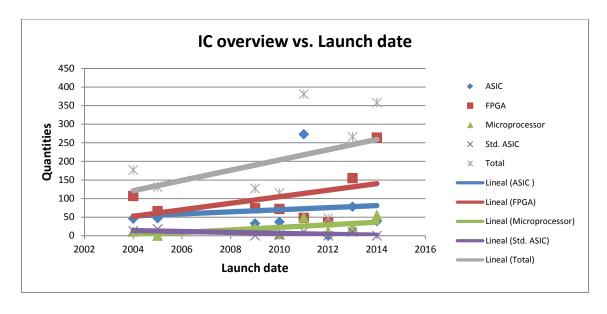

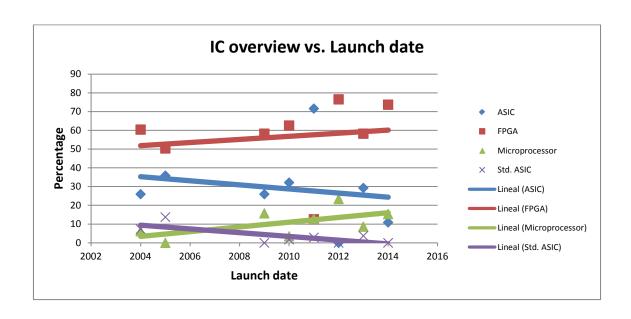

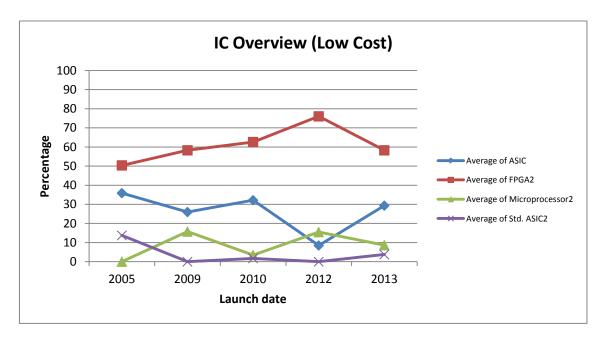

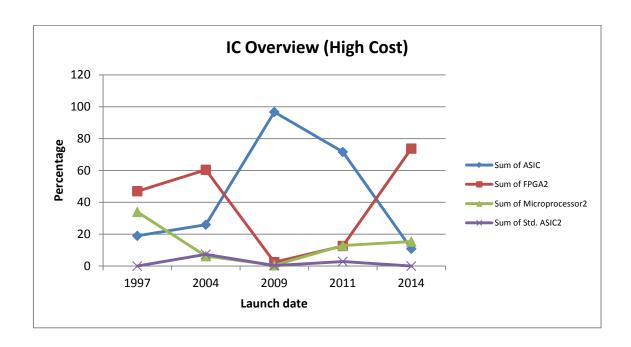

|     | 4.2.1                                                                                | Trends of use of AFMS technologies in space missions in the timeline             | 75  |

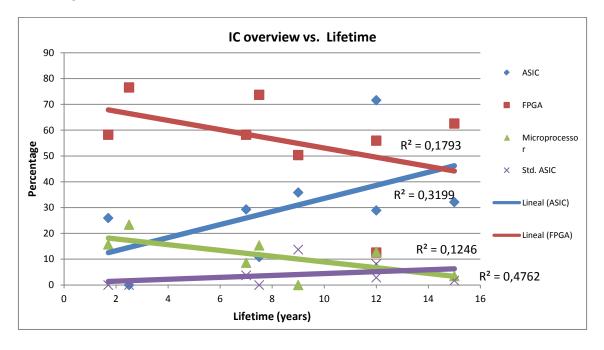

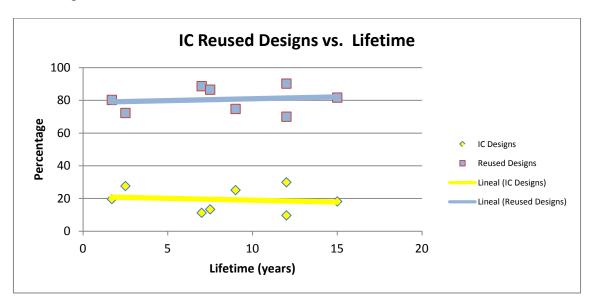

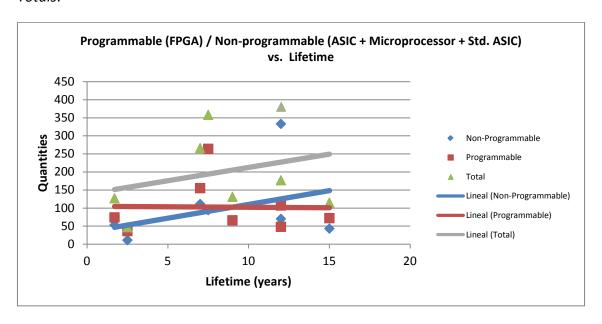

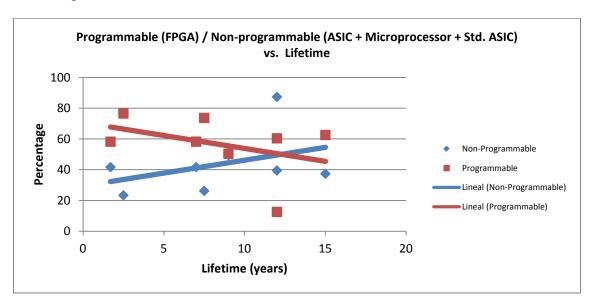

|     | 4.2.2                                                                                | Patterns of use of AFMS in space missions with respect to the mission lifetime   | :80 |

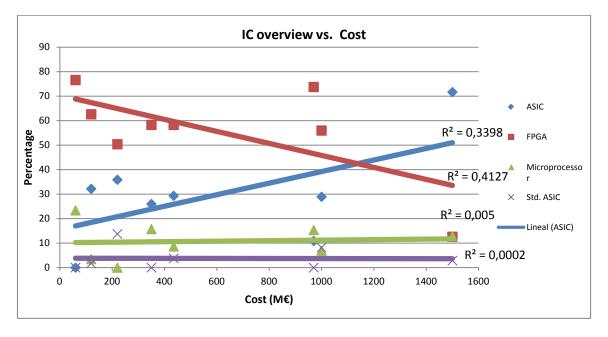

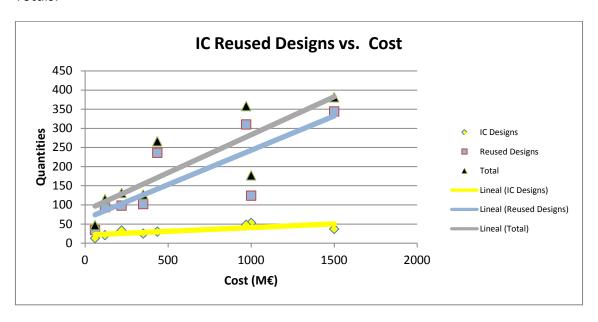

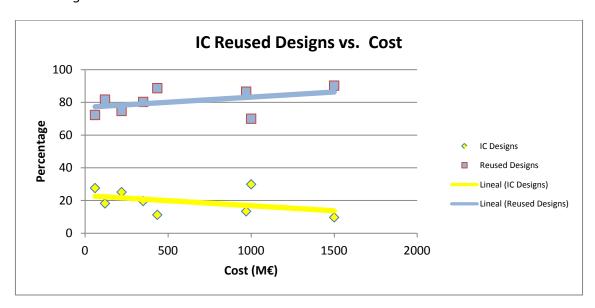

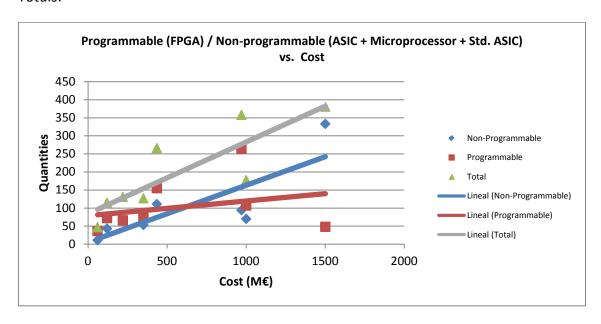

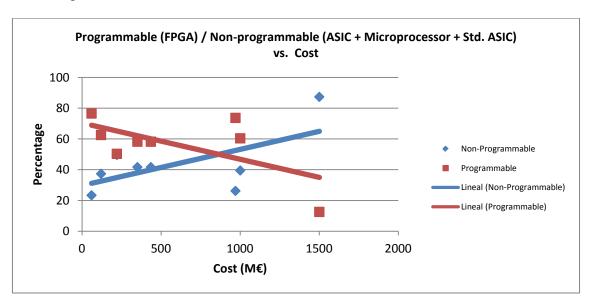

|     | 4.2.3<br>cost                                                                        | Patterns of use of AFMS in space missions with respect to the mission overall 81 |     |

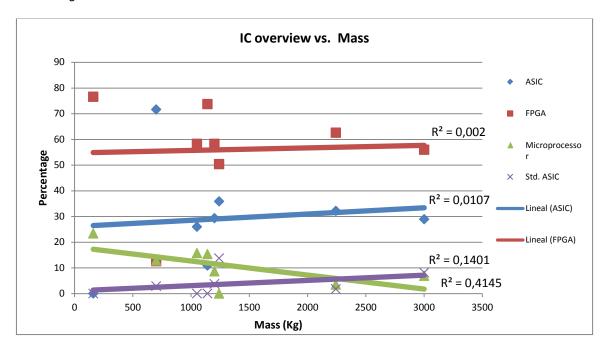

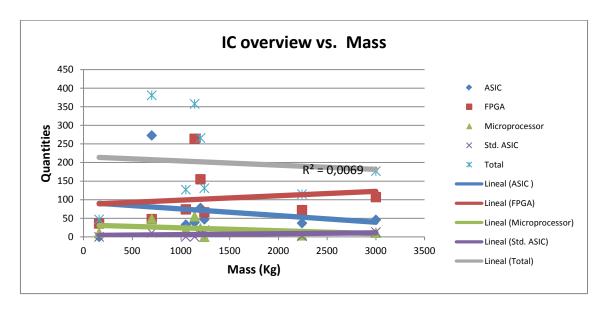

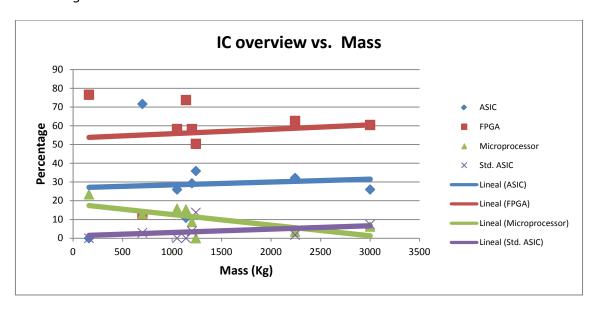

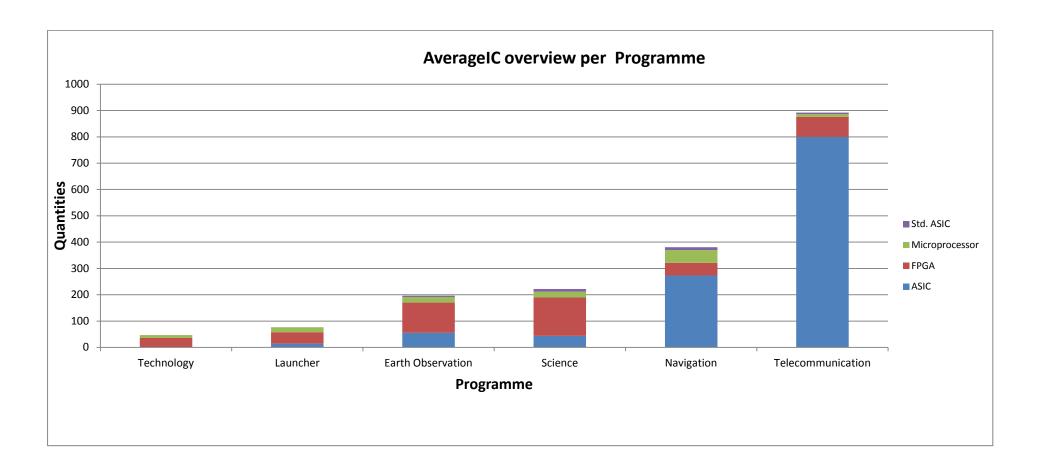

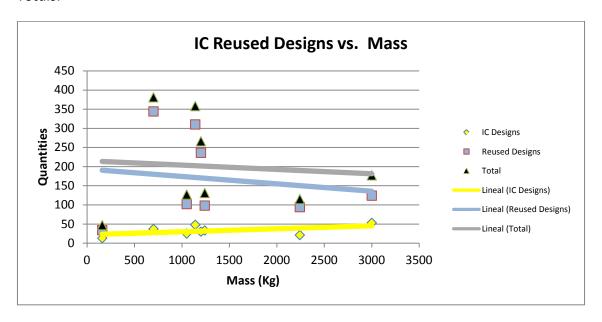

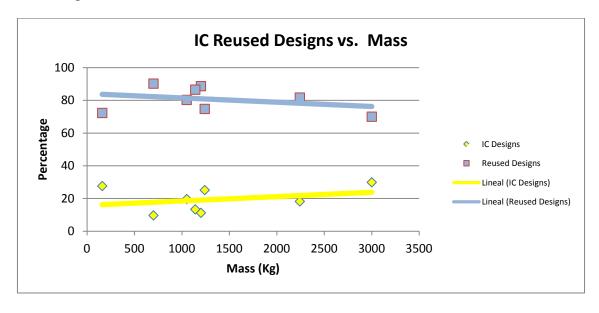

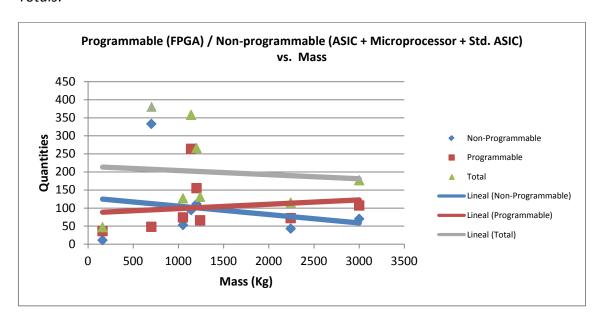

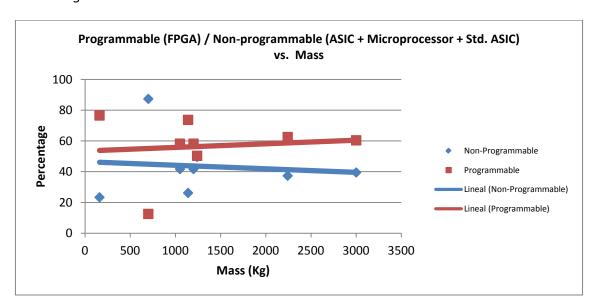

|     | 4.2.4                                                                                | Patterns of use of AFMS in space missions with respect to the satellite mass     | 82  |

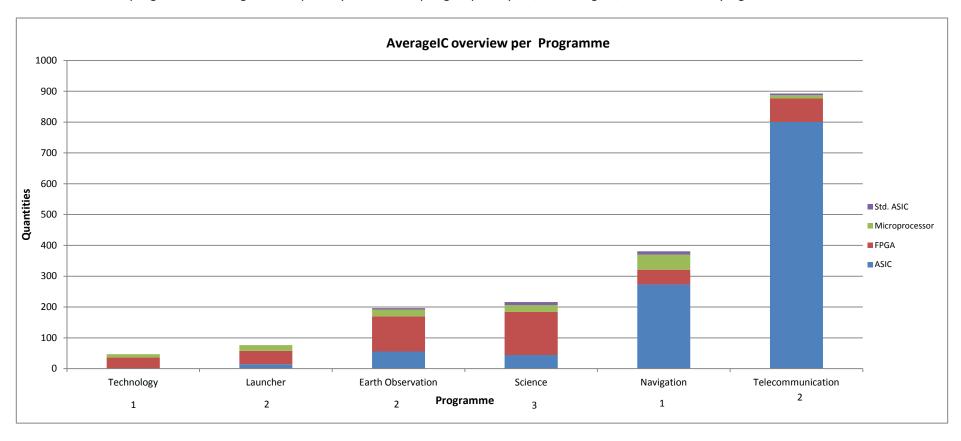

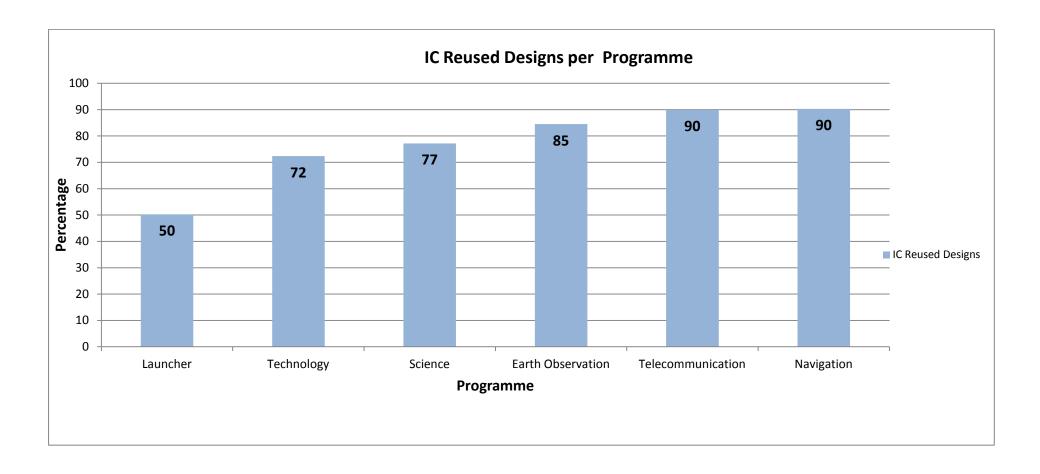

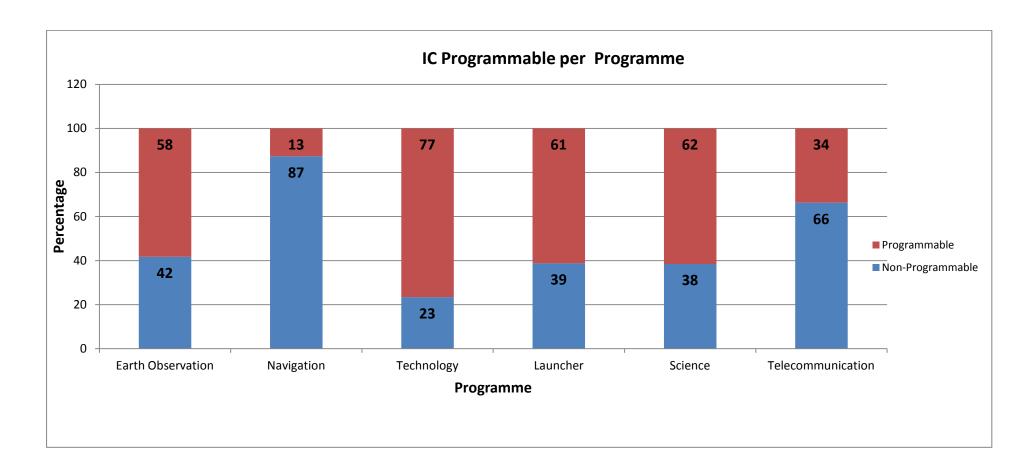

|     | 4.2.5 Patterns of use of AFMS in space missions with respect to the space programmes |                                                                                  | 83  |

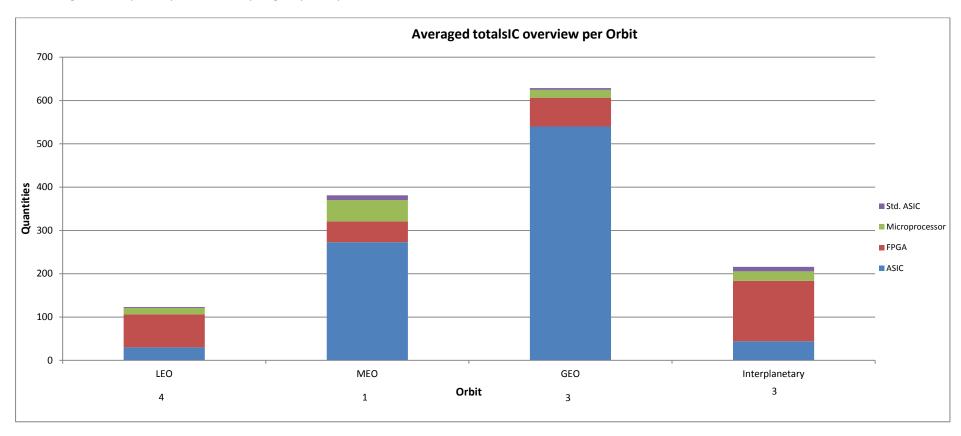

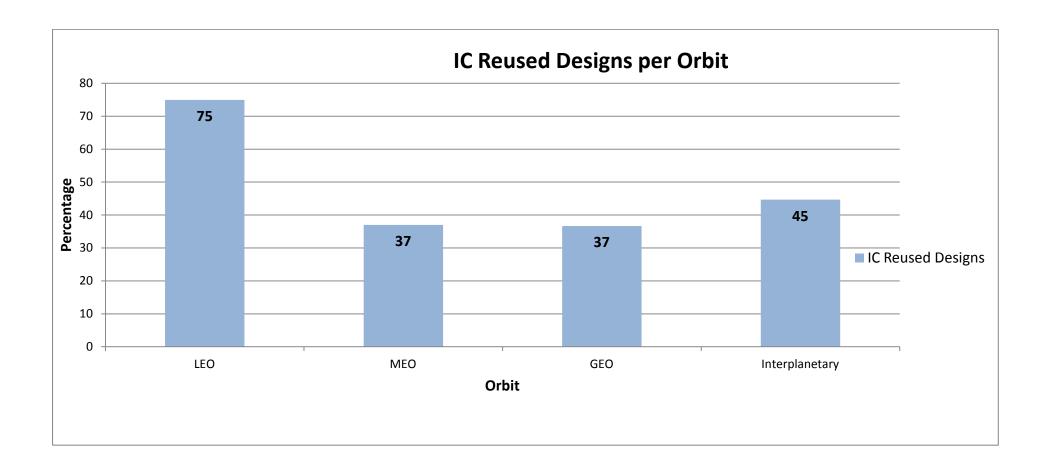

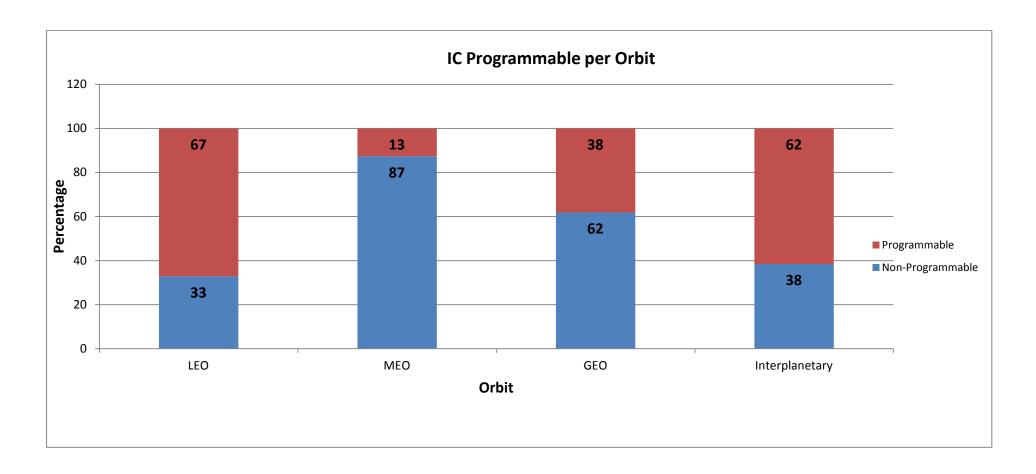

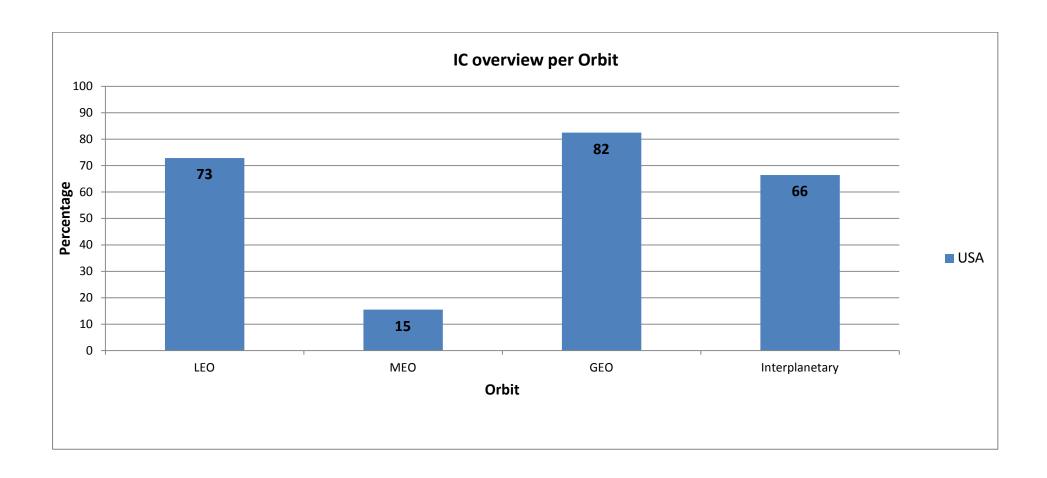

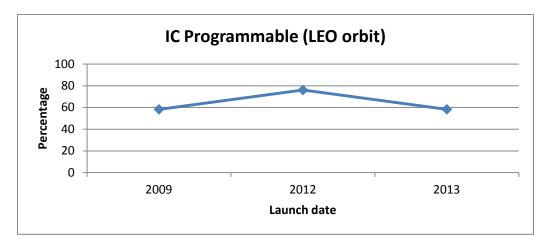

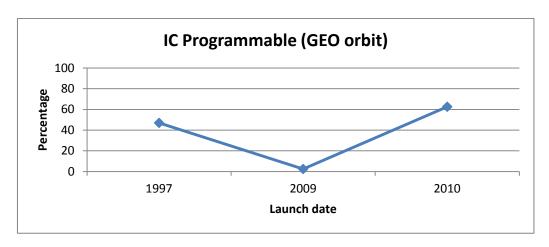

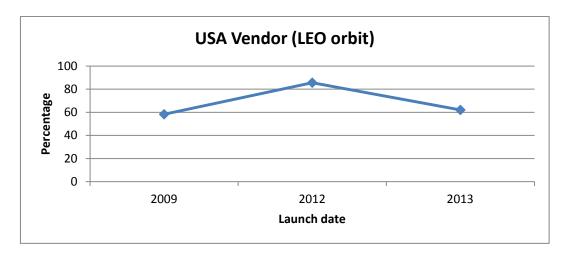

|     | 4.2.6                                                                                | Patterns of use of AFMS in space missions with respect to the satellite orbit    | 85  |

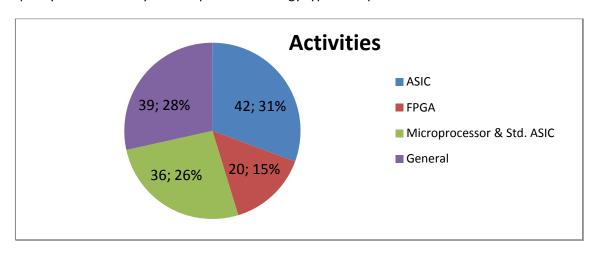

| 4.3 | Technologies prioritized in the ESA Microelectronics technology roadmap activities   |                                                                                  | 87  |

|     | 4.3.1                                                                                | Number of activities                                                             | 87  |

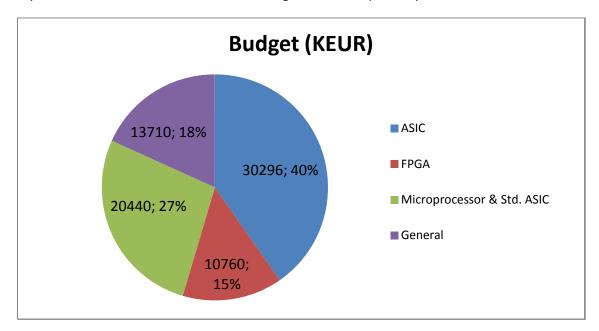

|     | 4.3.2                                                                                | Budget of activities                                                             | 88  |

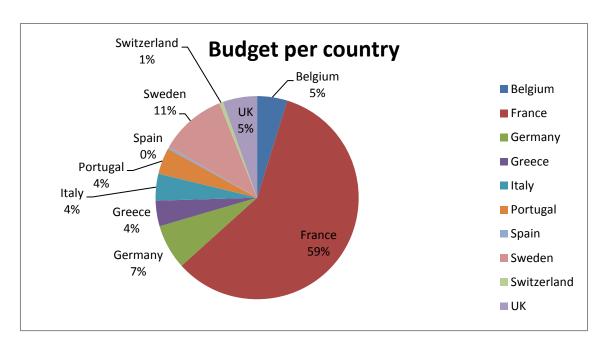

|     | 4.3.3                                                                                | Activities per country                                                           | 89  |

| 5   | EVALUAT                                                                              | TON AND VALIDATION OF RESULTS                                                    | 91  |

| 5.1 | Evalua                                                                               | tion of results                                                                  | 91  |

|     | 5.1.1<br>complex                                                                     | ESA Microelectronics Technology Roadmaps versus the measured use of ICs          | 91  |

|     | 5.1.2                                                                                | Suggestions for future Microelectronics technology roadmaps                      | 93  |

|     | 5.1.3                                                                                | Archiving and Managing data of EEE components used in ESA missions               | 95  |

| 5.2 | Validation of the research results98                                                 |                                                                                  | 98  |

|     | 5.2.1                                                                                | Statistical conclusion validity                                                  | 98  |

|     | 5.2.2                                                                                | Internal validity                                                                | 99  |

|     | 5.2.3                                                                                | Content validity                                                                 | .01 |

|     | 5.2.4                                                                                | External validity1                                                               | .02 |

| 6   | FUTURE \                                                                             | WORK1                                                                            | .03 |

| 6.1 | IC technical parameters10                                                            |                                                                                  | .03 |

| 6.2 | Space missions                                                                       |                                                                                  | .04 |

| 6.3 | Genera                                                                               | al review phase1                                                                 | .05 |

| 7   | CONCLUS                                                                              | SIONS                                                                            | .06 |

| 8   | REFEREN                                                                              | CES                                                                              | .08 |

| APPENDIX A: Graphs G1                                                      | 110 |

|----------------------------------------------------------------------------|-----|

| Ariane 5                                                                   | 110 |

| Rosetta                                                                    | 112 |

| Venus Express                                                              | 114 |

| GOCE 116                                                                   |     |

| Immarsat 4                                                                 | 118 |

| Hylas 120                                                                  |     |

| Galileo IOV                                                                | 122 |

| Vega 124                                                                   |     |

| Proba V                                                                    | 126 |

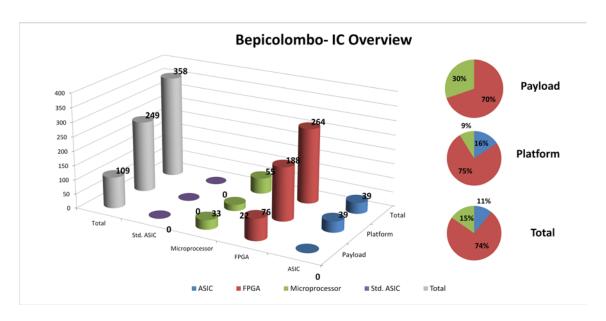

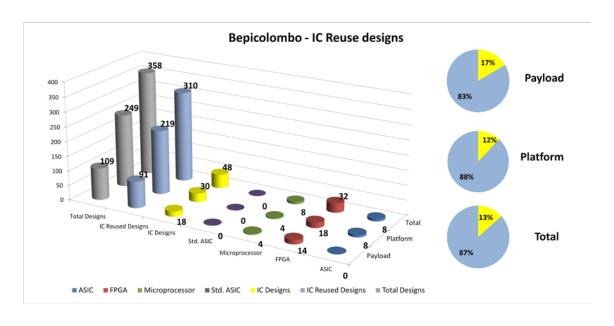

| Sentinel 2                                                                 | 128 |

| Bepicolombo                                                                | 130 |

| APPENDIX B: Graphs G2                                                      | 132 |

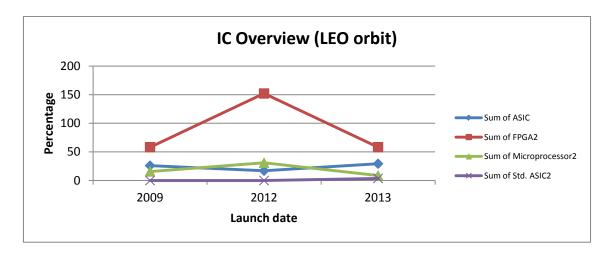

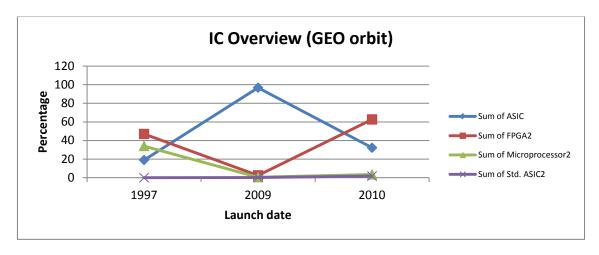

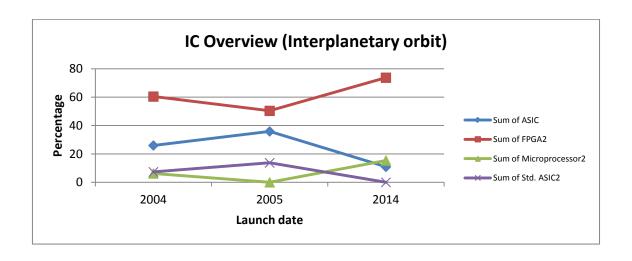

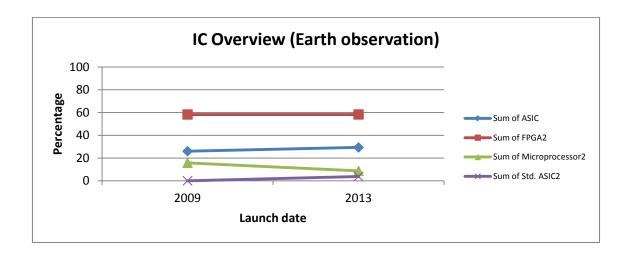

| IC Overview                                                                | 132 |

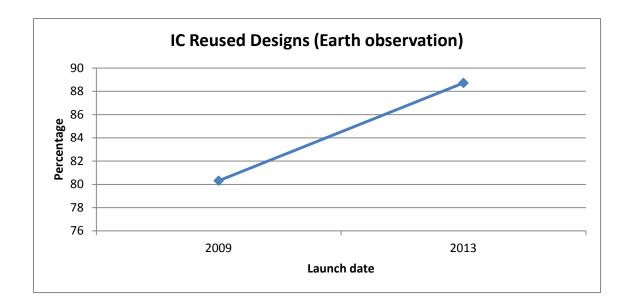

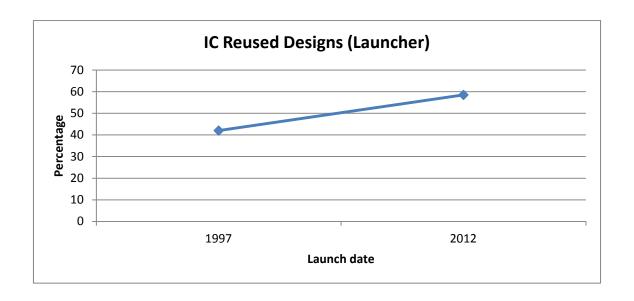

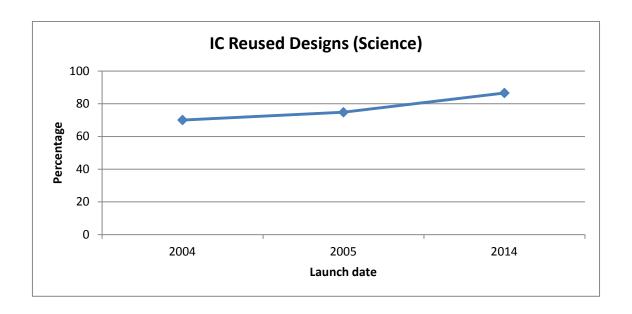

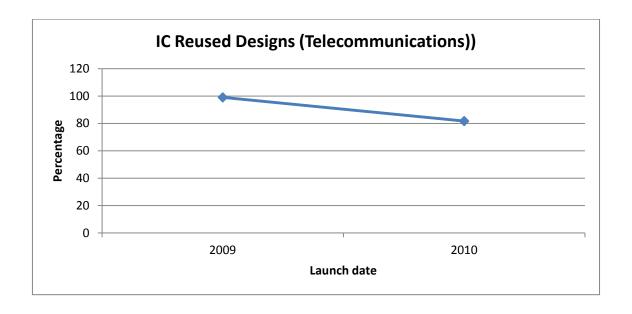

| Reused IC designs                                                          | 139 |

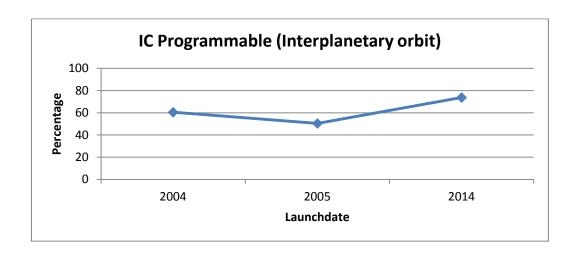

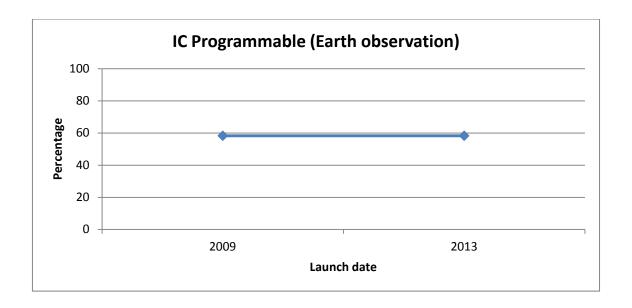

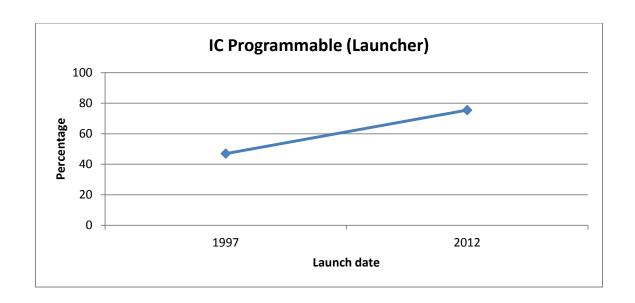

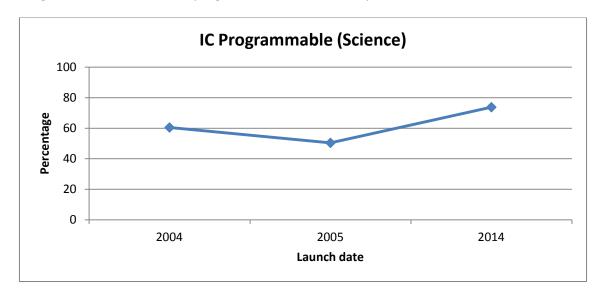

| Programmable (FPGA) / Non-programmable (ASIC + Microprocessor + Std. ASIC) | 146 |

| IC Technology vendor                                                       | 153 |

| APPENDIX C: Graphs G3                                                      | 160 |

| IC Overview                                                                | 160 |

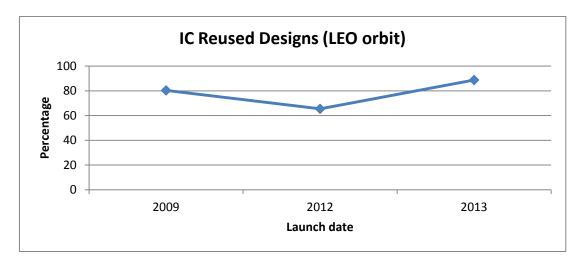

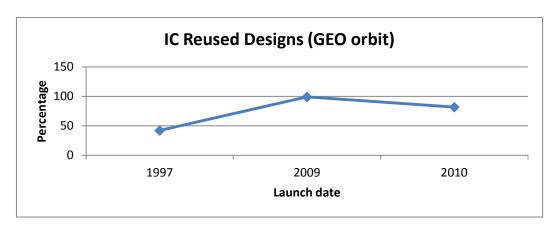

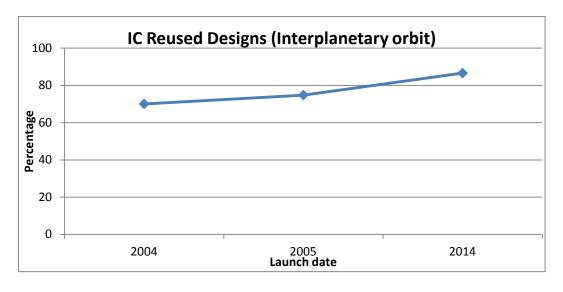

| Reused IC designs                                                          | 164 |

| Programmable (FPGA) / Non-programmable (ASIC + Microprocessor + Std. ASIC) | 168 |

| IC Technology vendor                                                       | 172 |

| APPENDIX D: Master Table                                                   | 176 |

| ADDENIDIX F. Data Collection Table                                         | 120 |

# **TABLE OF FIGURES**

| Figure 1: Trends in relative quantities of FPGA vs. ASICs used in space systems     | 2    |

|-------------------------------------------------------------------------------------|------|

| Figure 2: Integrated circuits for space applications                                | 8    |

| Figure 3: ASIC transistors and gates lay-out                                        | 9    |

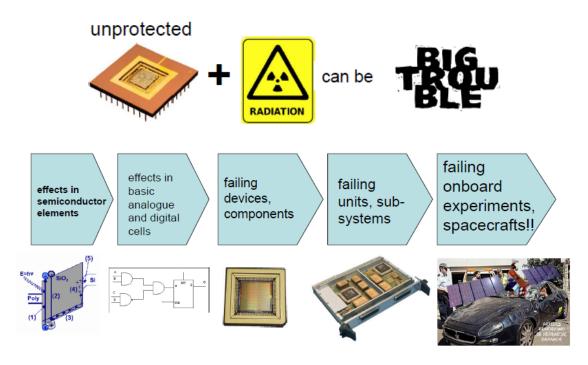

| Figure 4: Radiation effects                                                         | 10   |

| Figure 5: Space environment effects                                                 | 10   |

| Figure 6: ESA Matrix structure                                                      | 18   |

| Figure 7: Harmonisation Work plan                                                   | 20   |

| Figure 8: ITRS process                                                              | 26   |

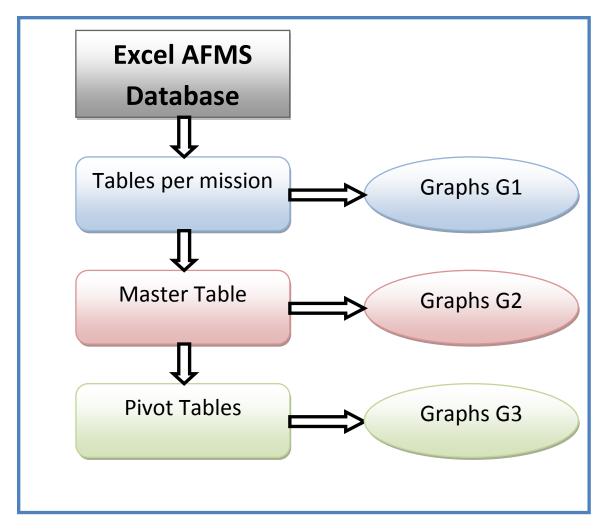

| Figure 9: Data collection process                                                   | 34   |

| Figure 10: DCL information                                                          |      |

| Figure 11: Linear snowball sampling                                                 | 37   |

| Figure 12: Exponential non-discriminative snowball sampling                         | 37   |

| Figure 13: Exponential discriminative snowball sampling                             | 38   |

| Figure 14: Space mission information process                                        | 39   |

| Figure 15: DCL Collection process                                                   | 40   |

| Figure 16: DCL Exploration process                                                  | 42   |

| Figure 17: Database completion process                                              | 45   |

| Figure 18: Subset of data fields selected                                           | 49   |

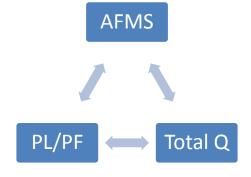

| Figure 19: AFMS- Payload/Platform- Total quantity                                   | 49   |

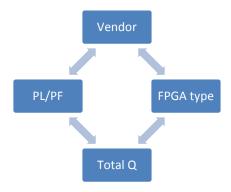

| Figure 20: Vendor-FPGA type-Payload/Platform-Total quantity                         | 51   |

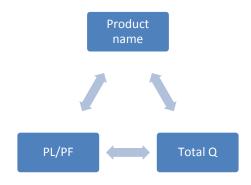

| Figure 21: Product name-Payload/Platform-Total quantity                             | 52   |

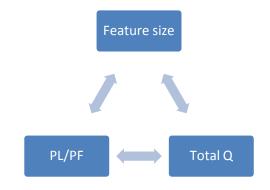

| Figure 22: Feature size-Payload/Platform-Total quantity                             | 52   |

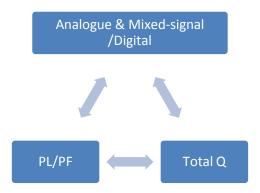

| Figure 23: Analogue & Mixed-signal /Digital-Payload/Platform-Total quantity         | 53   |

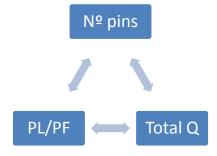

| Figure 24: Number of pins-Payload/Platform-Total quantity                           | 53   |

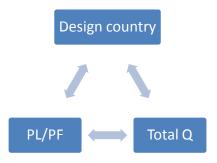

| Figure 25: Design country /Digital-Payload/Platform-Total quantity                  | 54   |

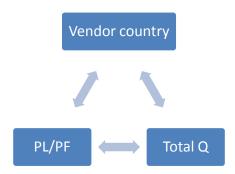

| Figure 26: Vendor country /Digital-Payload/Platform-Total quantity                  | 55   |

| Figure 27: Data exploration process                                                 | 56   |

| Figure 28: Microelectronics roadmap activities                                      | 61   |

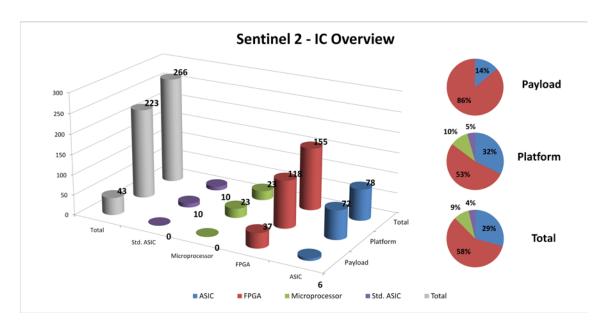

| Figure 29: IC Overview per missions (Totals)                                        | 64   |

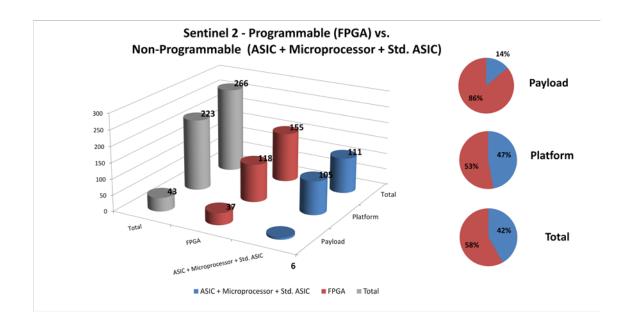

| Figure 30: Sentinel 2 - IC Overview                                                 | 65   |

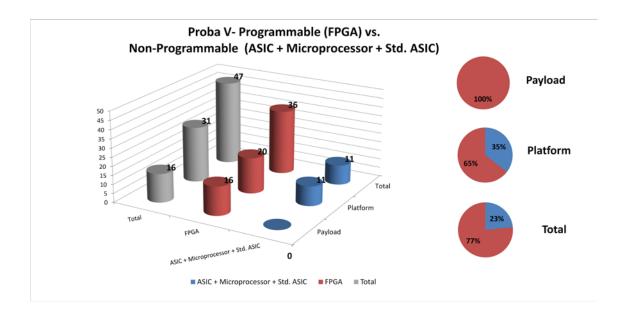

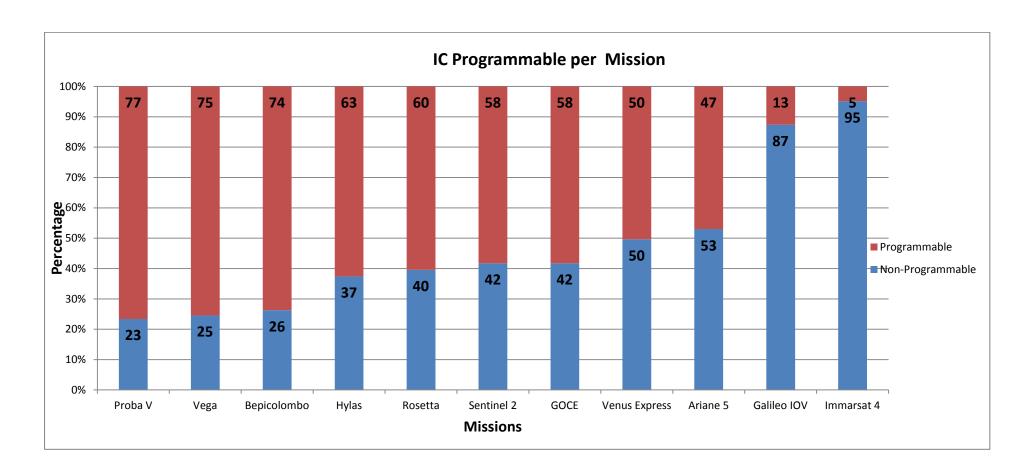

| Figure 31: Programmable/Non-programmable per Missions (Percentage)                  | 67   |

| Figure 32: Sentinel 2 Programmable (FPGA) vs. Non-programmable (ASIC + Microprocess | or + |

| Std. ASIC)                                                                          | 68   |

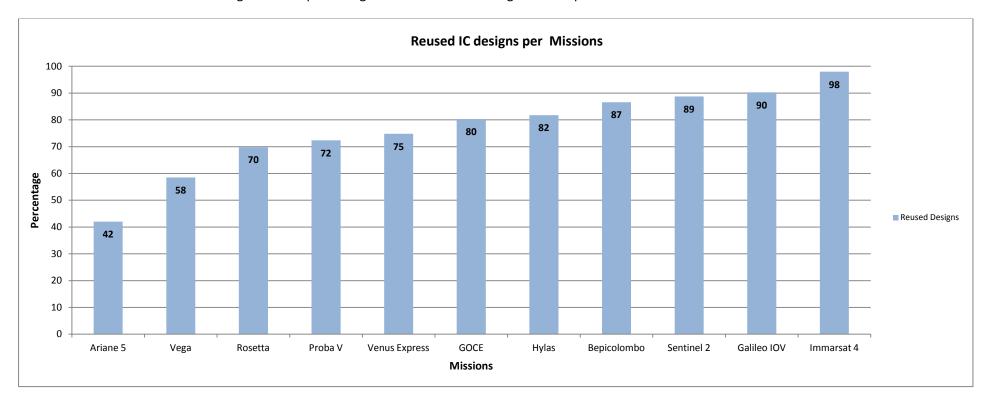

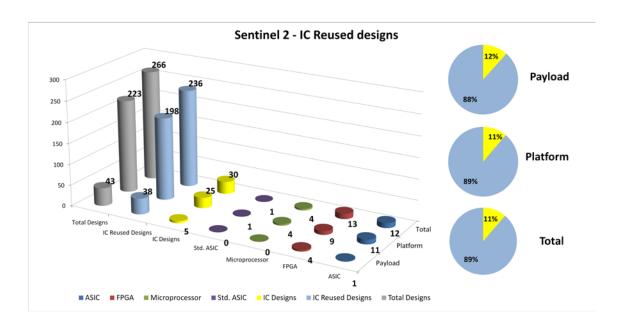

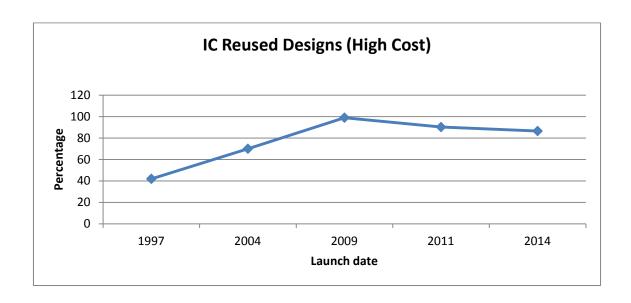

| Figure 33: Reused IC designs per Missions (Percentage)                              | 69   |

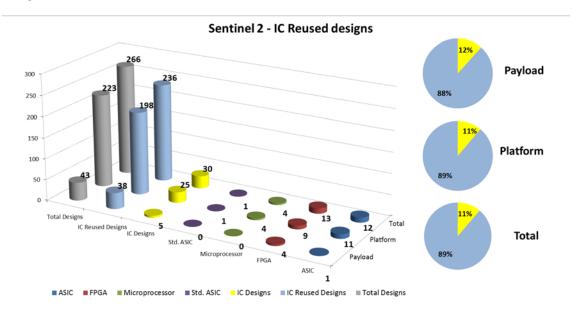

| Figure 34: Sentinel 2 Reused IC designs                                             | 70   |

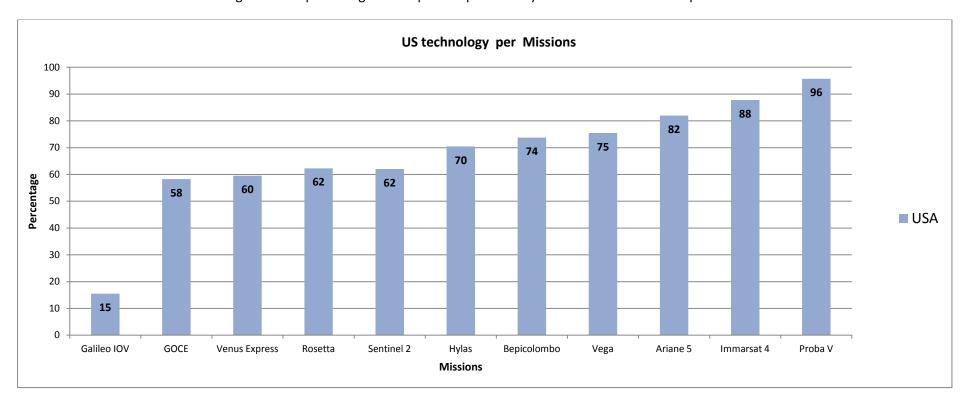

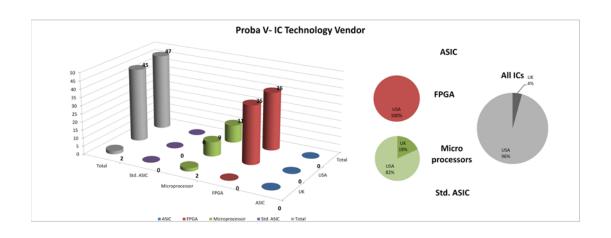

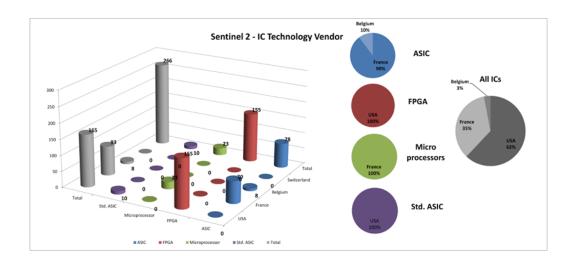

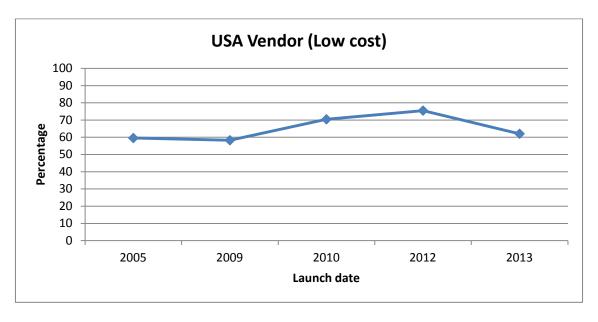

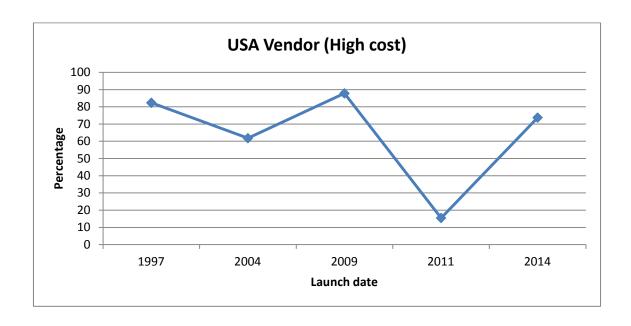

| Figure 35: IC Technology vendor per Missions (Percentage)                           | 71   |

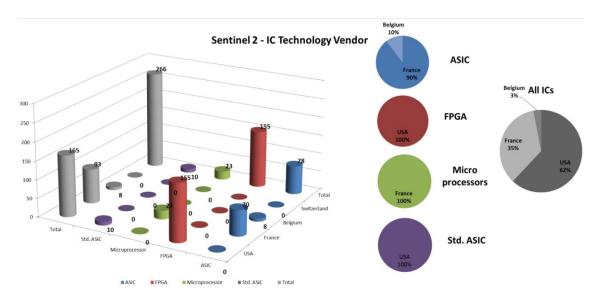

| Figure 36: Sentinel 2 IC Technology vendor country                                  | 72   |

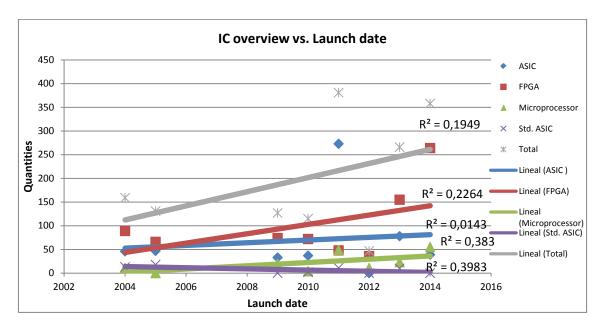

| Figure 37: IC Overview vs. Launch date (Totals)                                     | 75   |

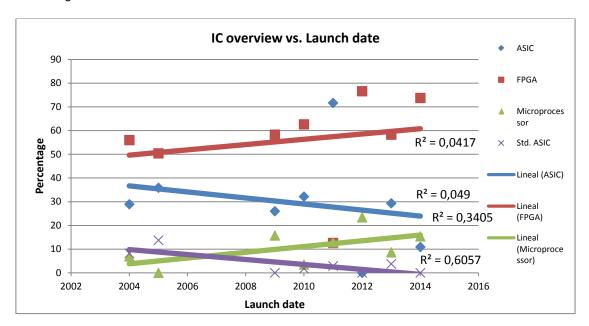

| Figure 38: IC Overview vs. Launch date (Percentage)                                 | 76   |

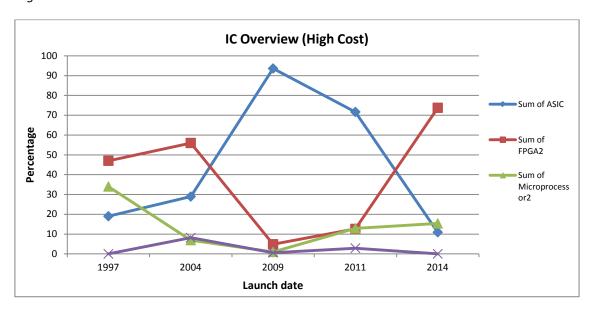

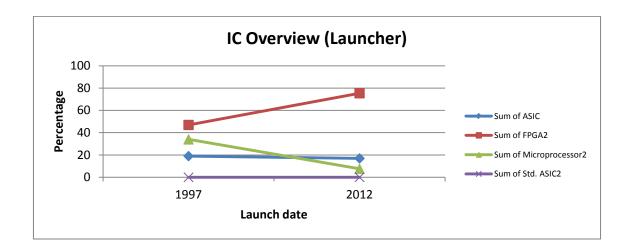

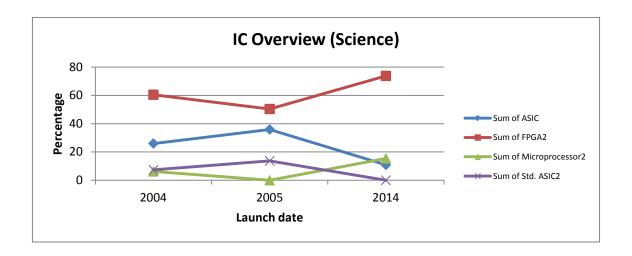

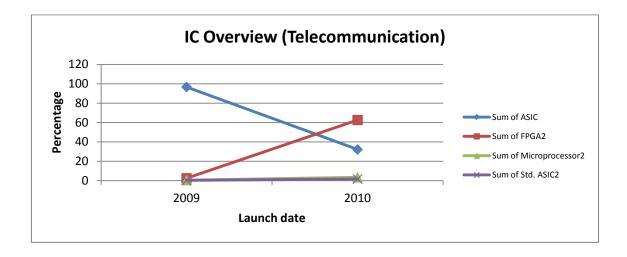

| Figure 39: IC Overview - High cost (Percentage)                                     | 76   |

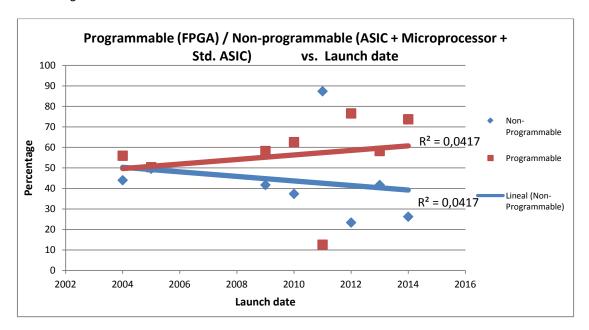

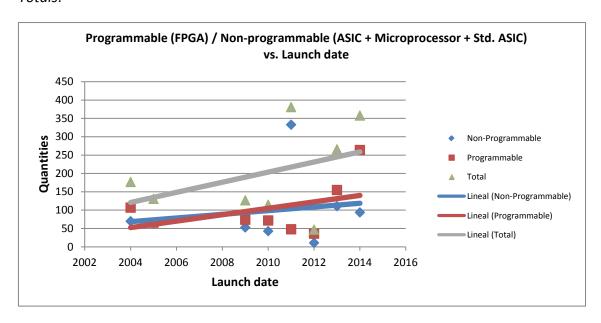

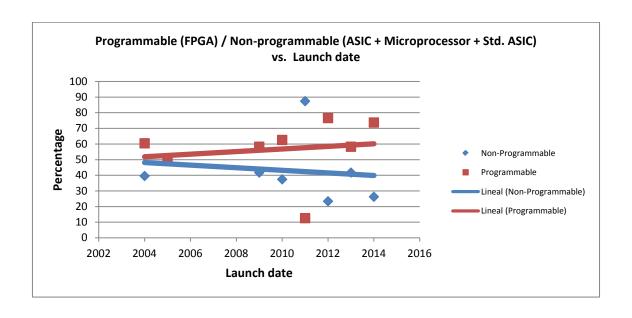

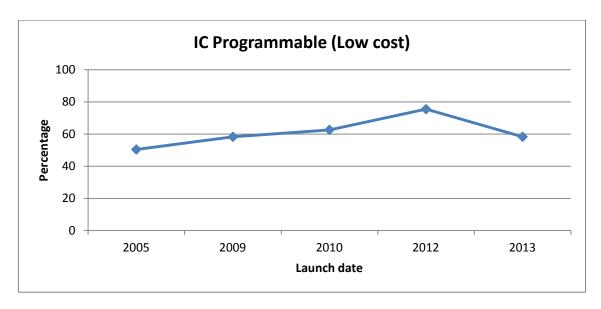

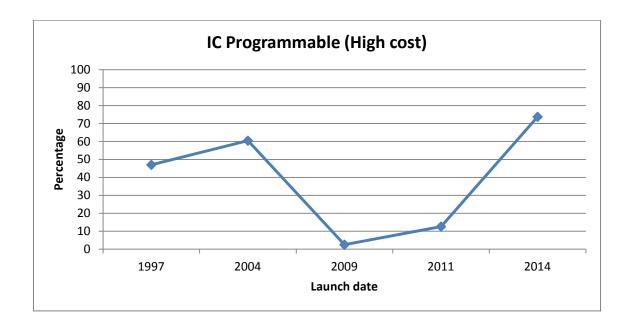

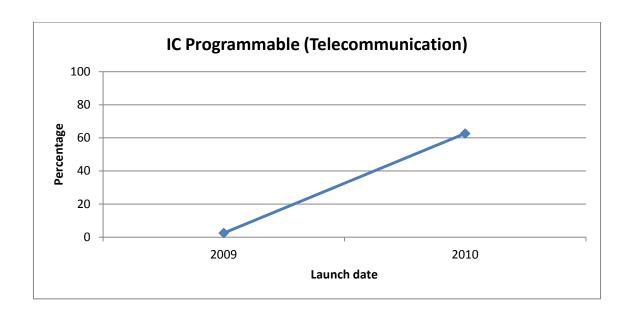

| Figure 40: Programmable/Non-programmable vs. Launch date (Percentage)               | 77   |

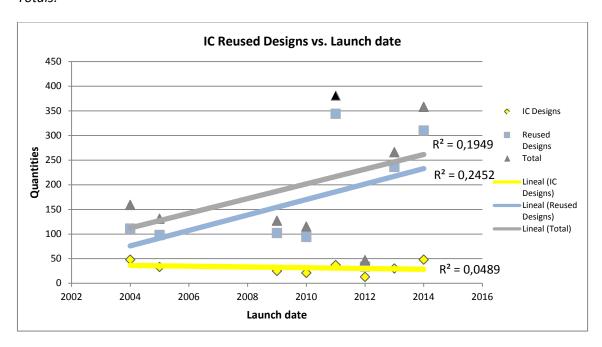

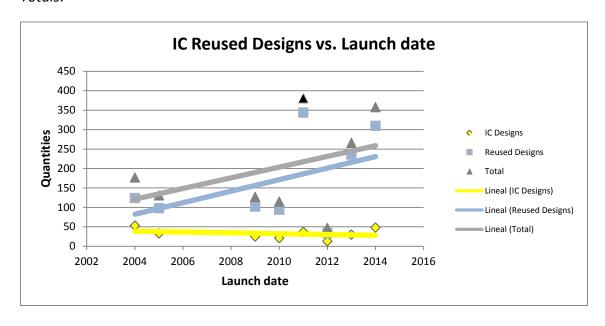

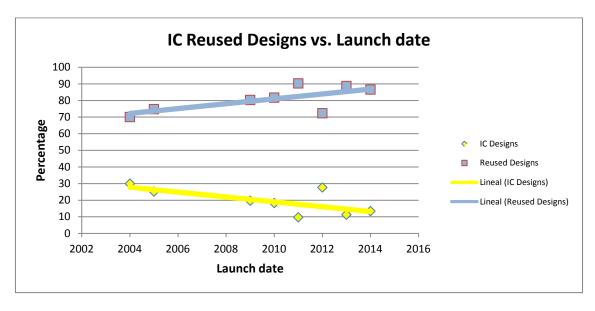

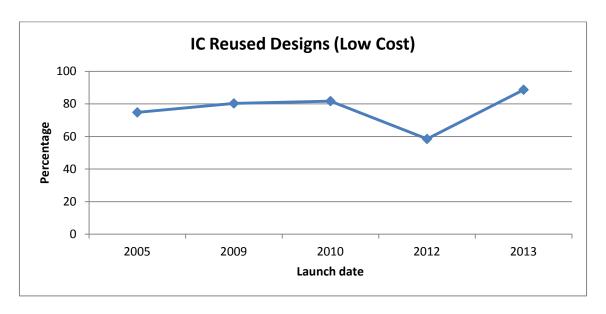

| Figure 41: Reused IC designs vs. Launch date (Totals)                               | 78   |

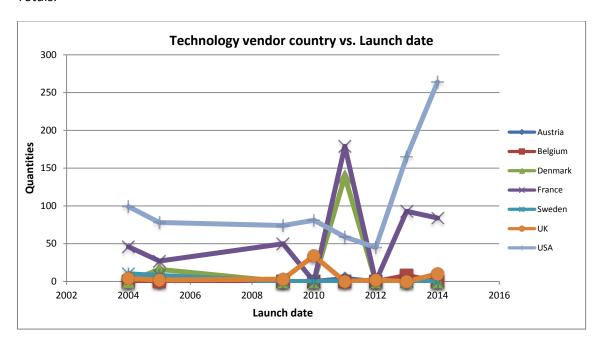

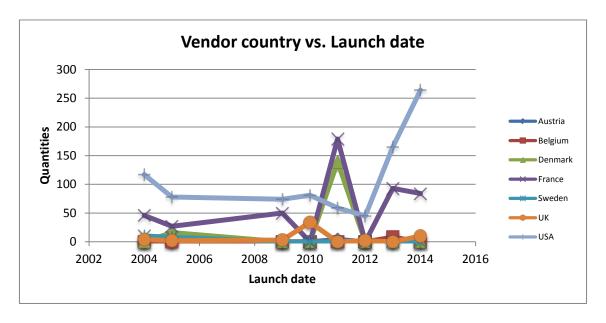

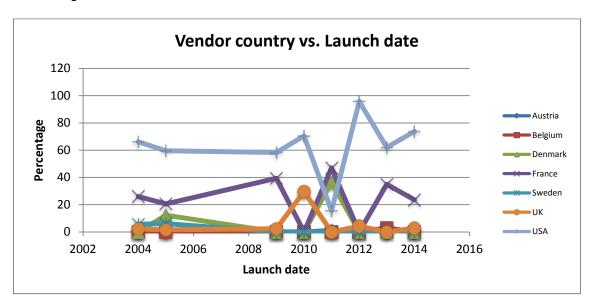

| Figure 42: IC Technology vendor vs. Launch date (Totals)        | 79 |

|-----------------------------------------------------------------|----|

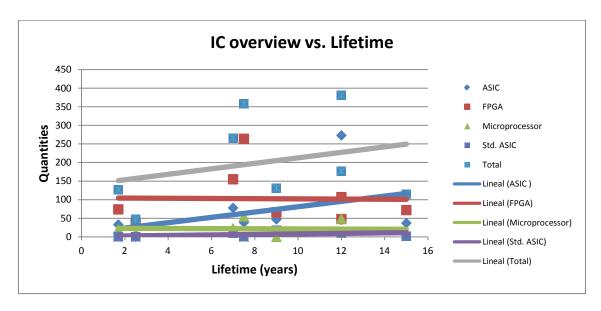

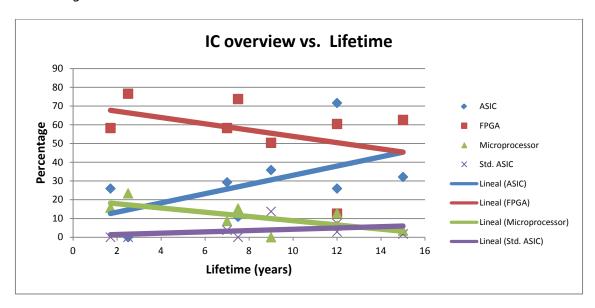

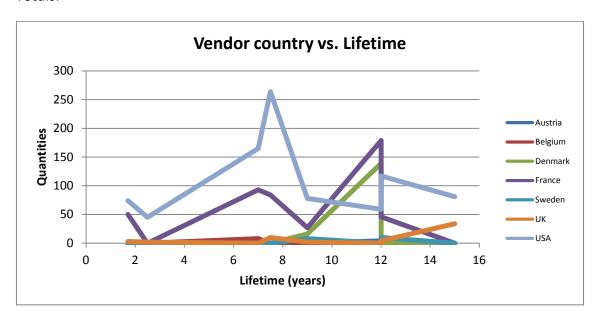

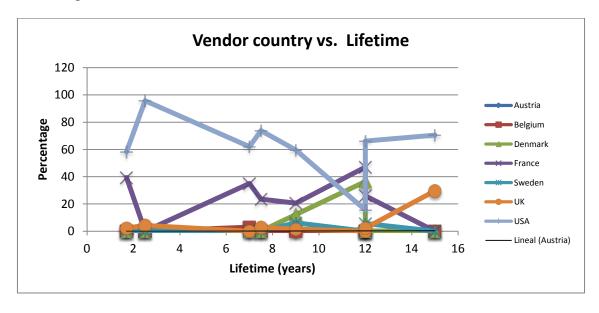

| Figure 43: IC Overview vs. Lifetime (Percentage)                | 80 |

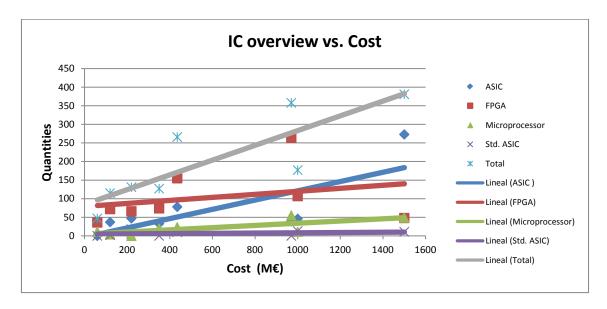

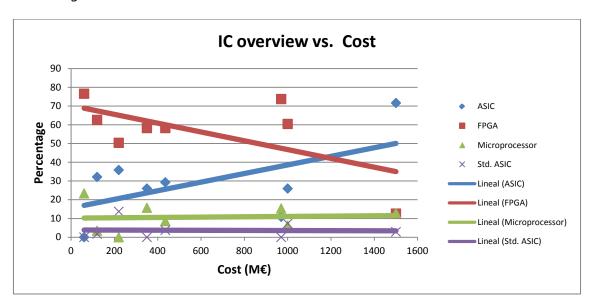

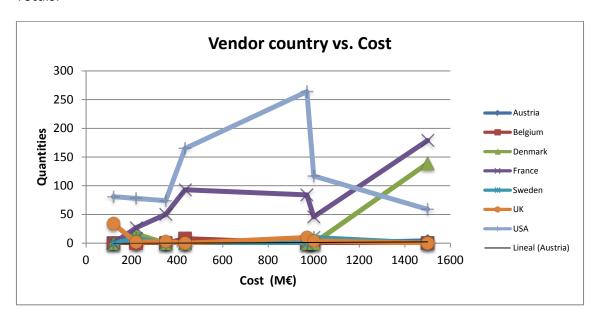

| Figure 44: IC Overview vs. Cost (Percentage)                    | 81 |

| Figure 45: IC Overview vs. Mass (Percentage)                    | 82 |

| Figure 46: IC Overview per Programme (Totals)                   | 83 |

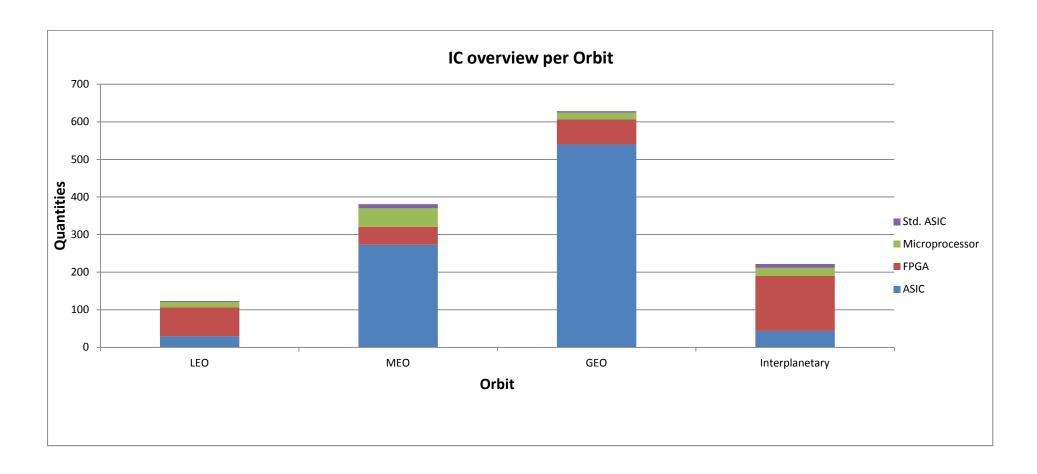

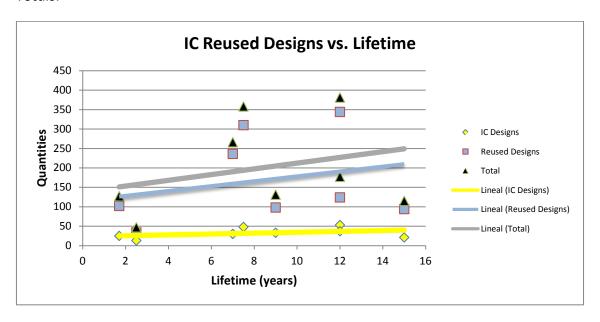

| Figure 47: IC Overview per Orbit (Totals)                       | 85 |

| Figure 48: Number of roadmap activities (Totals and Percentage) | 87 |

| Figure 49: Budget of roadmap activities (Totals and Percentage) | 88 |

| Figure 50: Roadmap activities budget per country (Percentage)   | 90 |

# **TABLE OF TABLES**

| Table 1: NASA Space technology roadmaps                                   | 25  |

|---------------------------------------------------------------------------|-----|

| Table 2: Top priority 17 space missions to be studied                     | 32  |

| Table 3: List of 11 space missions included in this research              | 32  |

| Table 4: Family Code (FC) and Group Code (GC)                             | 43  |

| Table 5: ASIC, FPGA, Microprocessor and Standard ASIC example known names | 43  |

| Table 6: Package type examples                                            | 44  |

| Table 7: ASIC, FPGA, Microprocessor and Standard ASIC main vendors        | 44  |

| Table 8: Sentinel 2 mission characteristics                               | 63  |

| Table 9: Comparison AFMS quantities used vs. budget assigned              | 93  |

| Table 10: Mission completeness status                                     | 104 |

# 1 INTRODUCTION

# 1.1 Motivation of research

ASIC and FPGA are key technologies in the development of space missions and perform the very hearts of the avionics control and the data processing systems of satellites[1]. They are complex and versatile integrated circuits which can implement large and complex functions. The main difference between these two technologies is that customers can buy "blank" FPGAs off the shelf and program them on their premises, while ASICs are integrated circuits (ICs) manufactured to a customer's specification[2]. Microprocessors and Standard ASICs are two other classes of complex integrated circuits that perform key control functions which are fundamental for the overall satellite operation.

It is difficult to define if ASIC and FPGA are competing technologies or if each one has its own market. Sometimes it is possible to use both integrated circuits for the same purpose so they compete, but in other cases the ASIC technology is the only one technically feasible due to its higher performance. The choice between both technologies is not only based on technical parameters but also on economic and logistic parameters like time to market, price or the user experience on each technology[1].

According to Paris-based Euroconsult's 12<sup>th</sup> World Market Survey, satellite manufacturers are at the beginning of a decade boom. It is expected that in the period to 2018, a 50 per cent more spacecrafts and satellites will be launched to the Earth orbit than in the preceding 10 years.

In addition, more hardware will be used in larger geostationary satellites as telecommunications companies try to pack in more channels and bandwidth[3]. These systems are becoming more complex and this trend will continue into the future so it will be required more complexity in the electronics and this can only be achieved by deploying highly integrated ASICs and FPGAs[4].

At the same time, the trend to use ASIC, FPGA, Microprocessor and Std. ASICs components is increasing as semiconductor integrated circuit technologies shrink in size and provide higher function densities and faster working speeds, while consuming less power and taking less area and weigh on the boards[5].

The main USA component suppliers to the space industry, Actel [6] and Xilinx[7], aim to benefit from this growth in two ways: through the increase in manufacturing and from a technology shift. Sharon Blades, Actel's senior regional sales manager for northern Europe, emphasises "It's big in Europe, America and India. The satellite business is a booming business – all sorts of satellites, whether for Earth monitoring, telecom or other applications. This has been our biggest year to date".

The technology shift is taking the market away from ASICs towards programmable and reprogrammable devices, FPGAs. ASIC offer higher logic densities and lower costs at higher

volumes, but demand serious upfront investment – known as non-recurrent engineering (NRE) - to make the masks that define the devices functions during manufacturing. "And customers don't want to commit to NREs if they don't have to" says Blades. On the other hand, Amit Dhir, senior director of Xilinx aerospace, defence and high performance computing business, says that the advantages of FPGAs are not just about the cost: "They allow customers to make changes right up to launch and they can get to market much quicker"[3].

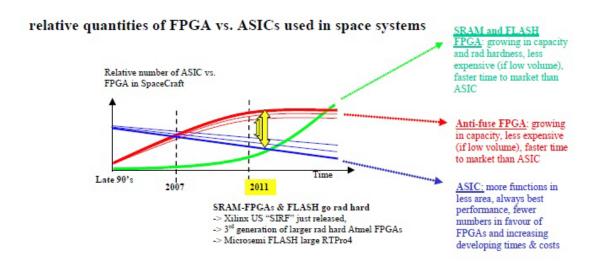

The graph below made by ESA Microelectronics Section show an approximation of the evolution of FPGA and ASIC use in space missions in the next years[5].

Figure 1: Trends in relative quantities of FPGA vs. ASICs used in space systems

However, the migration from ASIC to FPGA is not entirely simply for non-US satellite designers. All the major space FPGA suppliers are US companies, and as a consequence their space parts must be checked and sometimes explicitly approved for export under the US International Traffic in Arms Regulation (ITAR). If a part is protected by ITAR, much information about the technologies it contains is restricted to US citizens unless the Department of State grants an exemption. ITAR is an intend to stop American technology falling into enemy hands, but restrictions on military-grade chips can be an issue for non-US space organisations[3].

The European Space Agency has complained that these regulations further complicate project management. Wolfgang Veith, ESA's head of product assurance and safety, points out this issue:"It increases the risk, both programmatic and technological. It's programmatic risk because it inevitably leads to extended procurement times. And the lifecycle of each component must be tracked to a large level of detail, from design to integration to testing to launch."

In addition, restricted access to US technology makes failure analysis more difficult. "With European components, we have complete traceability and visibility. We have a deep insight", Veith says. "But that is not the case with US components. We are very often denied the detailed knowledge that we require. Generally, this is not a problem but if something goes wrong then it can be."

Europe has an strategic interest in developing, maintaining and improving the availability of European space ASIC, FPGA, Microprocessor and Std. ASIC technology (AFMS) in order to increase competitiveness of European satellite equipment manufacturers and minimize the dependency on export restrictions like US International Traffic in Arms Regulations[8].

The motivation of this research is to quantify the types of ASIC, FPGA, Microprocessors and Std. ASIC used in the last years in European space missions. This study will provide ESA and the European space community with better and more accurate information of the use of AFMS in European space mission that can help ESA policy managers to make more educated decisions and face in better conditions the new challenges of complex IC technologies in the space sector as the technology shift from ASIC to FPGA technology and the reduction of US components dependency.

# 1.2 Research objectives

The aim of this research is to quantify the number of ASICs, FPGAs, Microprocessors and Standard ASICs (AFMS) used in European satellites in the last years in order to show the trends and patterns of use of these technologies in space missions and try to give some conclusions that could have a positive impact in the future decisions and developments of complex integrated circuit technologies in the European space sector.

This study has never been done before and its results will help and contribute to make better strategic future and investment decisions of the European Space Agency and all European space community actors involved in the developing of these technologies, technology vendors and technology customers.

This project analyses the past, current and future situations of the use of these technologies in space missions in order to help ESA to make more educated decisions about future investments. The research compares and connects the results obtained in the data exploration with the current ESA Microelectronics technology roadmaps (MTR) activities [5] to see how ESA is supporting and helping to fund these technologies and if the current and estimated future use of these technologies is in good match with the priorities adopted in ESA's roadmaps.

In addition, this study suggests improvements at the present ESA mechanisms to collect and archive the electronic, electrical and electromechanical (EEE) components information used in space missions.

To achieve the objectives of this research, there are some research questions and subquestions that can help on defining the research strategy and putting some boundaries to the project.

The main research question is:

What are the trends and patterns of use of ASIC, FPGA, Microprocessor and Standard ASIC technologies in space missions and how are they reflected in the priorities of the European Space Agency for developing future integrated circuit technologies?

This main research question has been divided in some sub-questions in order to make the main objective more approachable:

- What quantities and types of AFMS have been used in space missions both in the payload and the platform in the last years?

- 1.1 What are the quantities of AFMS used in space missions?

- 1.2 What are the quantities of Programmable ICs (FPGA) versus Non-programmable ICs (ASIC, Microprocessors and Std. ASIC) used in space missions?

- 1.3 What is the rate of reuse of complex IC designs used in space missions?

- 1.4 What are the vendors and device families of the FPGAs more used in space missions?

- 1.5 What are the Microprocessors and Std. ASICs used in space missions?

- 1.6 What is the distribution of technology nodes (i.e. minimum feature size, normally measured as the transistor gate width) in complex ICs used in space missions?

- 1.7 What are the quantities of analogue/mixed-signal versus digital integrated circuits used in space missions?

- 1.8 What is the distribution of integrated circuit pin counts (number of pins in the package) in complex ICs used in space missions?

- 1.9 What countries design more complex integrated circuits for space missions?

- 1.10 What countries and vendors provide more complex integrated circuits technology for space missions?

These sub-questions aim to quantify the number and types of ASIC, FPGA, Microprocessor and Std. ASIC used both in the payload and the platform of each satellite looking for IC technical characteristics like the rate of reuse IC designs, IC technology nodes, IC pin count, etc.

- 2) What are the trends and patterns of use of AFMS technologies in space missions?

- 2.1 What are the trends of use of AFMS in space missions in the timeline?

What are the patterns of use of AFMS in space missions with respect to...

- *2.2* ...the mission lifetime?

- 2.3 ...the mission overall cost?

- 2.4 ...the satellite mass?

- 2.5 ...the space programmes?

- 2.6 ...the orbit?

This second group of sub-questions aims to use the information obtained in the first subquestion to look for trends and patterns in the use of complex integrated circuits from the space missions included in this research with respect to the launch date, lifetime, orbit, etc.

- 3) To which extent ESA Microelectronics technology roadmaps take into account the actual and future use of complex integrated circuits in space missions and how can the roadmaps be improved to better reflect that use and any identified trends and patterns?

- 3.1 What role plays the ESA MTR in ESA decision process for investing in developing and supporting these complex IC technology?

- 3.2 What technologies are prioritized in the ESA MTR activities?

- 3.3 To which extent is the use of complex ICs taken into account in the current development priorities of these MTR activities?

- 3.4 What improvements to the ESA MTR can be suggested in order to better reflect the current use and observed trends of these technologies?

These sub-questions aim to analyse what technologies are currently prioritized (in terms of number of activities and budget invested) in ESA MTR and compare these priorities with the

trends and patterns of use of complex ICs seen in the second sub-question in order to give some suggestions of what changes could be made in the roadmaps to better reflect the actual and anticipated future use of these technologies in space missions.

- 4) What are the weaknesses and strengths of the current data management system (DMS) used to collect and archive data on the use of electronic components in the European Space Agency?

- 4.1 How is the data about the use of electronic components archived and managed in ESA?

- 4.2 What improvements to the ESA data management system can be suggested in order to simplify the search of EEE components used in ESA missions in the future?

Finally, the fourth group of sub-questions aims to use the experience and knowledge learnt during the data collection process to explain the weaknesses and strengths of the current DMS used for controlling of the use of EEE components in ESA and to give some recommendations of how could it be improved.

# 1.3 Anticipated issues

This chapter explains the difficulties and issues that were identified before starting the research which could introduce complexity in the development of this study. They are presented in the next points:

#### Lack of in-house know-how

It is the first time that a study aims to quantify the ASIC, FPGA, Microprocessors and Std. ASIC used in ESA space missions. For this reason, there is no in-house reference to an appropriate methodology that could be used

#### Spread data and information

The data of the quantities of AFMS used in space missions is spread among many documents, people and databases both from ESA and European space industry. The lack of integrated database containing this information could make the data collection process very slow and complex.

# • Information stored in different formats, styles and physical supports

Beside the last point, there is not a standardized document that contains all the information requested in this research. It will be necessary to collect the data from documents with a diversity of formats, styles and physical supports.

# Availability of the information

As this information has never been searched before, there is no certainty that all this data will be available and possible to be collected. The results of this research will depend on the complexity of collecting and completing the data.

#### Confidentiality issues

Most of the data needed for this research is under confidentiality restrictions both from ESA and the Industry. As a consequence, it will be necessary to ask for special permissions which can take more time and efforts, and in the worst case, the data could not be available due to confidential restrictions.

#### Time limitations

The time to undertake this research is very limited, 5 months research, compared to the ambitious objectives it has. A first planning is scheduled to start with 3 months for data collection, 1 month for data exploration and 1 month to present and explain the results. The aim is to achieve as much as possible the objectives of the research but it is assumed that probably some of the objectives will not be achieved due to the complexity of the research and the issues commented above.

# 2 BACKGROUND INFORMATION

This chapter tries to compile all the information needed to understand the results of this research. It starts describing the AFMS technologies, continues presenting the main ESA information related to its organization, space missions, technology programmes and technology harmonisation, and finishes presenting the technology roadmapping tool.

# 2.1 ASIC, FPGA, Microprocessor and Standard ASIC technology

# a) ASIC and FPGA: Definition and characteristics

Application Specific Integrated Circuit and Field Programmable Gate Array are very complex and dense integrated circuits used to contain control and data processing functions[9].

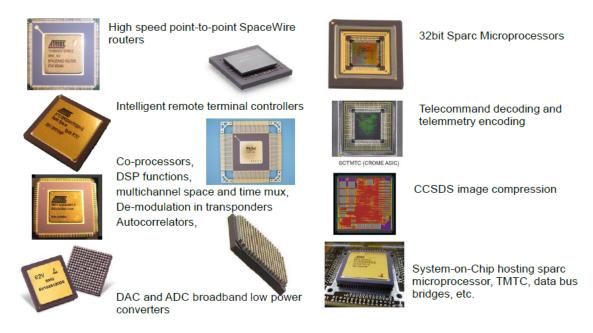

Figure 2: Integrated circuits for space applications

The complexity of these integrated circuits can be defined by the number of gates and the package number of pins. Today, space ASICs and FPGAs can have several million gates, track widths of 65 nm and packages with more than 1500 pins.

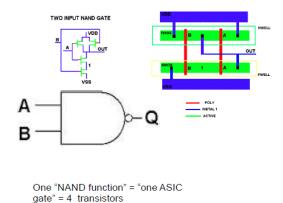

Figure 3: ASIC transistors and gates lay-out

ASICs and FPGAs are based in the same technology. They are built on silicon wafers, where circuits are chemically diffused with lithographic techniques, with very expensive, complex manufacturing tools and recipes, based on CMOS (Complementary Metal Oxide Semiconductor) technology. Moreover, both are designed by an expert team that generates the ASIC or FPGA circuit design using very similar standard CAD tools. However, the main difference between these technologies is that ASICs are unique types of integrated circuits meant for a specific application while FPGAs are reprogrammable integrated circuits[10].

On one hand, the advantage of ASIC technology lies in the performance as it has much denser layouts and interconnections that give a better speed and higher power performance than FPGA technology. On the other hand, ASICs are based on application specific customer designs and as consequence they have higher manufacturing costs and longer lead-times than FPGA technology[9].

In contrast, FPGAs are off-the-shelf components ready to be programmed with designs in a few minutes at designer's premises. They are normally cheaper for low production volumes and have shorter lead-times than ASICs. However, the fixed array structure of FPGAs limits their performance, size and power optimisation.

# b) ASIC and FPGA for space applications

Integrated circuits are of capital importance in order to achieve the necessary miniaturisation and performance levels that today and future space systems demand. Mask or field programmable integrated circuits implementing application specific functions are always one of the most critical microelectronics elements inside the space systems, as they normally host the heart of those systems (data processors, spacecraft controls)[5].

These custom ICs are possible thanks to the joint efforts and technology contributions of different companies and vendors: a design house, responsible for the actual design of the functions/circuit; design tool vendors, who provide the tools to do the designs; silicon technology manufacturers responsible for the technology where the functions will be implemented as hardware devices.

Although ASIC and FPGA follow a very strict and quality manufacturing process, there are some causes that can produce their failure:

Design mistake some nominal or corner cases never simulated

Manufacturing problem silicon wafer defects, badly calibrated machine, operator error, poor or insufficient error screening, etc.

System environment out of specification use

Aging effects electro migration, channel hot carriers, etc.

A part from these reasons, ASIC and FPGA used for space applications need to be more resistant due to the space environment effects:

- Vibration and mechanical shock

- Extreme temperatures

- Contamination effects

- Radiation effects

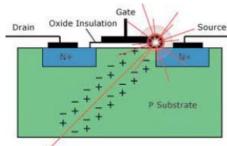

Figure 4: Radiation effects

Radiation effects are the main concern for ASIC and FPGA use in space because they can bring to temporary or permanent integrated circuit malfunctions, risk of mission failure or loss and in there is not option to on-board integrated circuit replacement or repair in space.

Figure 5: Space environment effects

ASIC and FPGA technologies for space applications follow special design process and are implemented with countermeasures to strength the protection against space radiation effects. These complex integrated circuits are requested to pass very strict and severe tests and simulations in order to be qualified for space applications.

Consequently, these technologies are very expensive to manufacture and test, and together with a very low volume market makes them a very special niche market that needs the support and funding from the European Space Agency for their research and development[1].

#### c) ASIC and FPGA vendors

There are several companies offering ASIC manufacturing service or operating as ASIC vendors in Europe. They offer a combined wide range of digital, analogue and mixed signal technology for custom and semi-custom ASICs and other specialised integrated circuits as memories, microprocessors, FPGAs, convertors, image sensors, digital and linear discrete. They have all already produced integrated circuits for space applications or are being evaluated for space IC production[5].

These are the main ASIC vendors in Europe:

| 0 | Atmel | France with corpo | oration HQ in USA |

|---|-------|-------------------|-------------------|

|---|-------|-------------------|-------------------|

Austria Micro systemsIHPInfineonAustriaGermanyGermany

LFoundry Germany and France

TI UK with corporation HQ in USA

Peregrine France with corporation HQ in USA

STMicroelectronics France, Italy and Netherlands

o X-FAB Germany

For FPGA technology, the only European supplier is ATMEL who in 2004 introduced its first FPGA for space applications manufactured with European technology.

The main vendors of FPGAs currently used in European space applications are MICROSEMI (who acquired ACTEL in 2011) followed by XILINX, both headquartered in USA, with a technology offer that is manufactured, assembled and tested in Asia and the USA.

In some exceptional cases, some commercial FPGA technologies (also non-European, e.g. Lattice) have been used in European space projects, normally after applying countermeasures against radiation effects. This usage is only limited to non-critical applications inside payload instruments whose eventual radiation effects can be tolerated and managed by the instrument, and do not endanger the global success of the mission.

# d) ASIC and FPGA: Trends and evolution

The current trend in space projects is to use more and more FPGA technology (whenever the application is not highly demanding in terms of power, speed and size). The FPGA approach is often a cheaper and faster development alternative to the ASIC approach, particularly for low volume integrated circuit needs. This is normally the case in space developments, with the exception, for example, of high telecom processing payloads where large arrays of ASICs are needed to implement the required processing capacity at an optimized power budget[5].

It is very difficult to quantify how much market share the FPGAs are taking over from the ASIC solution. At the beginning of the nineties FPGAs were hardly used inside space systems. Slowly, but steadily, FPGAs began to be introduced in the space units, taking place to ASICs. Reprogrammable FPGAs are finding their place in satellites and spacecraft, normally for non-mission critical applications, in the payload, where their higher sensitivity to radiation could be tolerated in exchange of having maximum flexibility to implement changes to the design without having to incur into lengthy and expensive redesign costs.

Some of the trends that make FPGAs a better alternative to ASICs for a growing number of higher-volume applications are [11][11][11][11]:

- Increasing integrated circuit design costs

- FPGA offers time-to-market advantage

- · Weak economy asking for low-cost technologies

- Reusability and lower non-recurring engineering costs

- Some FPGAs have the capability of partial re-configuration that lets one portion of the device be reprogrammed while other portions continue running

However, there are some disadvantages with FPGA:

- Not a right device for high volume applications

- Higher power consumption compared to ASIC

- Large configuration time and compilation time in FPGAs compared with generalpurpose processor

### e) Microprocessors

A microprocessor is an integrated circuit with very extended and versatile use. It is a multipurpose programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and provides results as output. Microprocessors operate in numbers and symbols represented in binary numeral system[12].

Microprocessors used for space applications need some improvements to prevent from the radiation effects. One of the main companies involved in developing these technologies is Atmel (France) who has been building rad-hard microprocessors for space for more than 16 years[13].

# f) Standard ASICs

Standard ASICs (also sometimes called "Application Specific Standard Products" or ASSPs) are catalogue products available off-the-shelf normally from the ASIC vendor which manufactured it. The advantage of Std. ASICs is that customers can reuse specific standard functions designed by the vendor using these components which save a lot of economic and time resources for the user.

In Europe, Atmel (France) and Dynex (UK) are the only companies that have a portfolio of Standard digital ASICs for space applications. This has been possible due to the dedicated ESA funded developments in order to have these ASICs available as Standard products for European space applications[5].

Microprocessors and Standard ASICs are very important and critical electronic components used in the avionics control and data processing systems in space missions and they are included in this research as a specific type of complex integrated circuits together with the ASIC and FPGA technology.

# 2.2 European Space Agency (ESA)

#### 2.2.1 ESA Facts

European Space Agency mission is to promote, for exclusively peaceful purposes, cooperation among European countries in space research and technology and their space applications[14].

ESA was established in 1975 and at this moment has 19 member states: Austria, Belgium, Czech Republic, Denmark, Finland, France, Germany, Greece, Ireland, Italy, Luxembourg, Netherlands, Norway, Portugal, Romania, Spain, Sweden, Switzerland and United Kingdom.

In addition, Canada takes part in some projects under a cooperation agreement and Hungary, Poland, Slovenia, and Estonia are participating in a Plan for European Cooperating States, while other countries are in negotiation about joining this initiative[15].

ESA is headquartered in Paris and has five other main establishments: ESTEC in Netherlands, ESRIN in Italy, ESOC and EAC in Germany and ESAC in Spain. The total staff of all the establishments is more than 2.000 people and the overall annual budget is about 4.000 million Euros (2012) [16].

Over the last 30 years, ESA has designed and tested more than 60 satellites, developed 5 types of launcher and made more than 180 launches to the space.

# 2.2.2 ESA space missions

ESA space missions can be classified by different parameters, one of the most representatives is the <u>space programme</u> they belong[15]:

#### a) Earth observation

Earth Observation space satellites are a powerful scientific tool used to learn more about our planet and understand better and improve the management of Earth and its environment. They not only provide information across space but also across time period so they can highlight environmental changes occurring gradually. In long term, monitoring Earth environment will give a reliable assessment of the global impact of human activity and the climate change extension.

# b) Human Spaceflight

Human Spaceflight programme has the aim to introduce Europe in the participation of the development of space infrastructure like the International Space Station, which allows conducting experiments in weightlessness environment. The purpose of this research and

technology development is to benefit people on Earth and prepare Europe for the new challenges of human space exploration.

# c) Launchers

Access to space brings many benefits and this is only possible by having launchers capable to place satellites in space. In the 30 years, Europe has made a big effort to guarantee the access of European satellites to space developing successful like Ariane or Vega. ESA, European research centres and aerospace industry are reviewing new technologies and propulsion systems to make access to space simpler and cheaper in the future.

# d) Telecommunications and navigation

ESA and the European Commission are developing the Galileo programme, a joint initiative in order to provide Europe with its own independent global satellite navigation system, compatible and interoperable with the existing American GPS and Russian Glonass military systems.

In addition, telecommunication satellites are a fundamental part of global communications network which represent an important commercial sector and provide all kind of services over almost every region in our planet. ESA supports the deployment of new satellites and programmes like Alphasat/Alphabus a large platform for high-power telecommunication satellites.

# e) Technology

ESA works together with European industry in developing and testing sophisticated technologies in order to make future space missions and applications possible. New technology products need to be proved in orbit to make sure there is no risk associated with the use of these technologies in Space. ESA is preserving and expanding the technology base of European industry to ensure its competitiveness and give rise to commercial products and services.

#### f) Science and robotic exploration

Space Science missions explore our Solar System and Universe to try to answer ultimate question like how did our Earth and Solar System evolve, where are we in the universe, where did the life come from and if we are alone in the universe. ESA is working now in a programme for the next twenty years with the aim to discover if other worlds exist and how life and the Universe evolved from the Big Bang to nowadays.

A part from the space program, ESA satellites can also be classified by their Earth orbit:

#### a) Low Earth Orbit (LEO)

LEO is defined as an orbit below an altitude of 2000 km from the Earth. For example, this is the orbit of the International Space Station and many Earth Observation satellites.

# b) Medium Earth Orbit (MEO)

MEO is the region of the space around the Earth above the LEO orbit (2000 Km) and below Geostationary Orbit (35786 Km). It is common for navigation satellites.

# c) Geostationary Earth Orbit (GEO)

GEO is a circular orbit at 35786 Km altitude from the Earth. An object in this orbit has an orbital period equal to the Earth rotational period (one day) so the object in the space looks motionless as a fix position in the sky. It is common for telecommunication satellites.

# d) Interplanetary

Interplanetary "orbit" is a trip of a satellite to another planet so it is not orbiting around Earth. Most science programme satellites fall in this orbit category.

# 2.2.3 ESA Technology Programmes

ESA technology programmes define and fulfil ESA's future technology needs and have the purpose of preserving and expanding the technology base of European industry, ensuring its competitiveness and giving rise to commercial products and services.

Technology is developed in ESA under several corporate and domain specific programmes. Some of them address all services and technology domain while some others are only addressed to specific technologies and levels of technology maturity.

These are the main ESA technology programmes that support the MTR activities promoted by ESA Microelectronics section[17]:

#### a) Technology Research Programme (TRP)

Technology Research Programme enables researchers to explore new ideas from the very early stages. TRP is the only ESA technology programme supporting all of ESA's fields of activity and providing the technological nucleus for most future developments.

Disruptive innovations are a special priority in current TRP activities. For example, microsystems and nanotechnology and ultra-light materials, can transform the way space missions are designed and run.

# b) General Support Technology Programme (GSTP)

General Support Technology Programme exists to convert promising engineering concepts into mature products right up to the spaceflights. It bridges the gap between having a technology

proven in fundamental terms and making it ready for ESA and national programmes, the open market and space itself.

#### c) Advanced Research in Telecommunication Systems (ARTES)

ESA Telecommunications programme aims to enhance the competitiveness of European industry by promoting the use of satellites in functions like broadcasting, multimedia and mobile communications, data relay, search and rescue and aviation services.

Telecommunications R&D is vital for the continuity of the sectors success. However, the risk inherent in advanced space projects is often a deterrent to private investors and individual governments are unable to support at this scale. Here is where ESA's direct financial contributions through programme lines like ARTES offsets the risk and fills the support gap.

# d) New Member States Industry Incentive Schemes

Industry Incentive Scheme is established to help the integration of new Member States, using part of their mandatory contribution. Currently, there are Industry Incentive Schemes for Greece, the Czech Republic and Romania. The Scheme for Portugal and Luxembourg has achieved their goals and was formally closed in 2008 and 2011 respectively[18].

# e) European Component Initiative (ECI)

The aim of the European Component Initiative is to reduce the dependence of Europe's space sector on non-European component suppliers focusing on the Electrical, Electronic and Electromagnetic components[14].

ESA, national space agencies and equipment and components manufacturers have identified a high risk of the European space industry becoming dependent on non-European sources for critical space components. In the long term this can lead to a reliance on products subject to export restrictions, such as the International Traffic in Arms Regulations or End User certificates.

# 2.2.4 ESA Organization

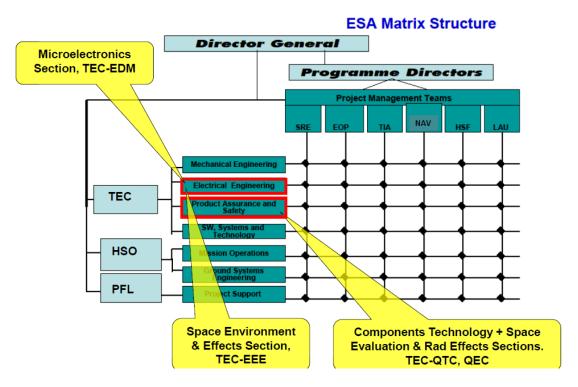

ESA is organized in directorates, departments, divisions and sections and has a matrix structure as it is shown in the figure below:

Figure 6: ESA Matrix structure

This research is conducted by the Microelectronics section which is located in the Directorate of Technical and Quality Management (D/TEC), Electrical Engineering department (TEC-E) and Data Systems division (TEC-ED).

The Directorate of Technical and Quality Management is a support directorate within the ESA matrix structure. It is responsible to provide high-tech engineering advice and assistance to ESA projects during their entire lifecycles.

More specifically, ESA Microelectronics section provides technical support and expertise in integrated circuits design and technology for spacecraft platform and payloads. This technical support extends to all programme directorates including Navigation (D/NAV) and Telecommunications (D/TIA), Earth Observation (D/EOP), Science (D/SRE), Human Space Flight (D/HSF and Launchers (D/LAU). One of the aims of the Microelectronics section is to define and launch internal and external activities to ensure the short, medium and long term availability of key components that are qualified for space.

These activities are defined in the European Space Technology Harmonisation process (explained below in chapter 2.2.5) which is driven by the Technology Strategy and Harmonization division (TEC-SH) in collaboration with ESA technology sections.

The TEC-SH division is responsible for:

- Preparing the ESA Technology Long-Term Plan in close cooperation with the D/TEC departments and with the ESA directorates and the other European actors (industry, space agencies, research institutes, European Commission, etc.)

- Organising the harmonisation process at European level leading to roadmaps agreed by national agencies and industry, and preparing the European Space Technology Master Plan

- Identifying needs for European technological independence

# 2.2.5 European Space Technology Harmonisation

# a) Introduction

ESA is the leader of a wide effort to harmonise space technology research and development activities in Europe. The European Technology Harmonisation Process analyses current technology needs and strategic gaps and works to fulfil them by coordinating European R&D around common development roadmaps. These roadmaps include agreed objectives, processes and interfaces. A European Space Technology Master Plan provides annually the overview of the R&D landscape of the continent[17].

To make possible the harmonisation of efforts in the implementation of the technology programmes an agreed strategy is needed. This means combining efforts in search of synergies from all the many players involved: ESA, National and European Agencies, Member States, industry and academia.

The harmonisation process is very dynamic with continuous meetings held and feedback received. The process it is completely voluntary and transparent and is based on sharing information, consultation and coordination between participants.

The technology roadmaps are prepared with a methodology of two meetings per technology. The first meeting objective is to map the technology as completely as possible by gathering information from all interested national institutional and industrial parties. The second meeting consist in discuss the detailed roadmap sequence, sources of finance and possibilities of sharing skills and resources during the technology's development. Roadmaps are revised every few years.

# b) The European Space Technology Harmonisation process

The Technology Harmonisation is a demanding process that involves the efforts of all actors (ESA, Member States, Industry, Research Institutes, etc.) and requires consensus, with natural difficulties regarding the implementation of the agreed roadmaps in ESA and National technology programmes.

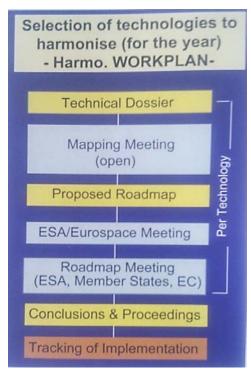

The yearly Harmonisation process consists of the following elements:

- The selection topics

- The two harmonisation cycles

- The approval of the documents

- The tracking of the roadmap implementation

The outputs per technology addressed are:

- Mapping of the situation inside and outside Europe, including identification of critical issues.

Technical Dossiers provide complete overview

- Technology Roadmaps agreed at European Level with ESA, National Delegations and Industry

- Recommendations agreed with ESA, National Delegations and Industry

Figure 7: Harmonisation Work plan

#### c) Selection of Harmonisation topics

The selection and definition of the scope of Harmonisation topics is a process that involves ESA experts, Industry and National delegations. The output is a work plan that defines the number, subject, and scope of the Harmonisation topics, which is approved by the ESA Industrial Policy Committee (IPC).

The first list of topics suitable for Harmonisation is based on the following criteria:

- Technology Maturity Level

- Strategic relevance for Europe

- Mission needs and market potential

- Technology gap or unnecessary duplication

- Need to Revisit Technology

The list is discussed by ESA experts and Industry and the results are presented to the Technology Harmonisation Advisory Group (THAG), an ESA body delegate whose function is to advise the IPC and to monitor the implementation of the harmonised technology roadmaps and conclusions. THAG decides which topics to propose for Harmonisation. ESA experts and Industry then work on the topics description and scope, which is finally decided by THAG.

# d) Harmonisation cycles

The Harmonisation process is divided in two overlapping cycles, each one covering half of the subjects selected. Each cycle has two main steps: the Mapping part and the Roadmap part.

## i. Mapping

The first part of the Harmonisation process is the mapping. Its goal is to arrive to a consensus on the landscape and situation of the technology that wants to be harmonised. A 1<sup>st</sup> issue draft Technical Dossier is prepared by ESA experts containing a summary of:

- A description of the topic state of the art, the exact scope of the harmonisation and the reason for it

- The list of main European players and their products

- The main players outside of Europe and a comparison between European products and non-European ones

- The mission needs, market perspective, technology trends and possibility of spin-out

This draft Dossier is distributed to THAG National Delegations and Industry for review, comments and input. After this review, a Mapping Meeting is held where every National Delegations presents its inputs. These inputs are then discussed to upload the Technical Dossier.

The data provided during the Mapping Meeting include:

- Comments on the draft Technical Dossier

- National interests requirements and mission needs

- National capabilities

- Past, on-going and planned national activities

- Recommendation for European roadmap

#### ii. Roadmap

The second part of the Harmonisation process is the preparation of the roadmap, taking into account the data provided during the Mapping Meeting. This roadmap covers all European activities from ESA, National Institutions and industry when the data is available.

The Roadmap presentation prepared by the ESA experts includes:

- The updated data from the Mapping Meeting useful for comprehension of the rationale behind the roadmap (European players, mission need, market perspective, requirements...)

- The roadmap, which presents on-going and future activities, based upon data received during the Mapping Meeting, including:

- Description of the activity (including beginning and end TRL, contribution to Non-Dependence, Building Block...)

- Status (on-going, already authorised, new proposal)

- Planned budget and schedule

- o Priorities (for new proposal only)

- Best Fit possible ESA programs for new proposals or actual program (ESA or not) in other cases

- o Link between proposed activities and official requirements

- A summary budget requested in the Roadmap in various breakdowns (time wise, per priority, per program...)

The presentation, after been reviewed by ESA programmes and Directorates is sent to Industry for comments and then is sent back to ESA and THAG. A roadmap Meeting is hold by THAG to decide and agree on all aspects of the Roadmap, as presented above. At the end, the roadmap is included in the final version of the Technical Dossier.

#### e) Conclusions approval

When the final version of the Technical Dossier and Roadmap presentation have been approved by THAG, for both cycles, a Conclusions document is prepared. This document covers all topics for Harmonisation presenting a summary of each one with:

- A short description of the topic

- The previous Harmonisation coverage, if applicable

- The main decisions taken

- The budget recommended for the roadmap

- The main aims and priorities defined

- The pending actions, if any

This document is presented to IPC for endorsement and their relevant extracts are included to finalise the Technical Dossier. The final updated set of documents is the made officially available and included in the next issue of the European Space Technology Master Plan.

# f) Harmonisation Roadmap Tracking

Every year there is a review of the status of all activities of the Roadmaps that should have been initiated. Its purpose is to report on the level of implementation of the Harmonised Roadmaps in ESA and Member State technology programmes.

#### g) Outcome of the Harmonisation process

The Harmonisation process for each Technology results is two main documents:

- Technical Dossier presents the mapping of the situation inside and outside Europe, including identification of critical issues

- Roadmap presentation contains the agreed roadmap

The roadmap agreed through the Harmonisation process is a recommendation, which is used as one important input for decision makers when preparing ESA and National work plans, but does not constitute a work plan itself. It is not guaranteed that the recommended budget will be available or that proposed activities will be started in the program. Its purpose is to present

the consensus of the community on the best way forward as can be foreseen when the Harmonisation cycle is run.

# h) European Non-Dependence Process

In regard to European Non-Dependence, ESA has been since 2002 monitoring areas that may be subject to dependency on Non-European sources. ESA General Director mentioned that: "ESA should contribute, in collaboration with other European institutional and commercial actors, to sustaining the full supply chain and provide non-dependent access to critical technologies, in particular basic supplies such as materials and EEE components. This does not require full European independence on all technologies, but unrestricted access to sources".

The Microelectronics Section is clearly involved in this process as complex integrated circuits, electrical, electronic and electromechanical (EEE) components, used in European space missions have a high dependence on USA technology.

# 2.3 Technology Roadmaps

## a) Definition, types and purposes of technology roadmaps

Technology roadmaps are used in industry, government and academia to give structural relationships among science, technology and applications. Roadmaps are instruments used to improve coordination of activities and resources in increasingly complex and uncertain environments[19].

Technology roadmapping has become one of the most used management tools for supporting innovation and strategy at firms, sector and national level. The main questions that roadmaps try to answer are: Where are we now? Where do we want to go? And how can we get there? [20]

The purpose of a roadmap is to align technological efforts with the sector trends. The development of successful roadmaps requires the involvement of key stakeholders and groups, often representing very different perspectives. Identifying appropriate participants to be involved, particularly in workshops, is a key consideration during the roadmap development process.

These are some applications that fit European Space Agency roadmap purposes[21]:

- To communicate to design and development engineers which technologies will be used in future products

- To communicate the research plans to business sponsors

- To help focus and prioritising research activities

- To identify where expert knowledge is required in the future

In addition, the roadmapping process improves communication and discussion within a creative workshop environment and the roadmap provides a framework for continuing this process in the future.

There are many types and different ways to classify roadmaps, these are some examples[19]:

- Science/research roadmaps (e.g., science mapping)

- Cross-industry roadmaps (e.g., Industry Canada initiative)

- Industry roadmaps ( e.g., SIA's International Technology Roadmap for Semiconductors)

- Technology roadmaps (e.g., aerospace, aluminium, etc.)

- Product roadmaps (e.g., Motorola, Intel and others)

- Product-technology roadmaps (e.g., Lucent technologies, Philips International)

- Project/issue roadmaps (e.g., for project administration)

The roadmaps used in the ESA Microelectronics section can be defined as technology roadmaps because they focus in a very specific technology, in this case, the development of complex integrated circuits for space applications.

The major uses and benefits of technology roadmapping are:

- Helping decision makers to achieve consensus about a set of technology needs

- Providing a mechanism to help experts forecast technology developments in targeted areas

- Presenting a framework to help plan and coordination technology developments at any level: within an organisation or company, throughout an entire discipline or industry, even at cross-industry/national or international levels.

In conclusion, the main benefit of technology roadmapping is to provide information that could help make better technology investment decisions.

#### b) Microelectronics technology roadmaps

This chapter acknowledges some technology roadmaps used in other organisations and space agencies to see what work is done in monitoring the use of microelectronic components for space applications.

#### NASA Space Technology Roadmaps

NASA is working on an integrated roadmap that meets both the near term space technology needs of the NASA mission directorates, as well as the longer term Space Technology Grand Challenges. This roadmap is an integrated set of fourteen technology area roadmaps, recommending the overall technology investment strategy and prioritization of NASA's space technology activities[22].

| Technical Area | Space Technology Roadmaps                                    |

|----------------|--------------------------------------------------------------|

| TA01           | Launch Propulsion Systems                                    |

| TA02           | In-Space Propulsion Systems                                  |

| TA03           | Space Power and Energy Storage                               |

| TA04           | Robotics, Tele-Robotics and Autonomous Systems               |

| TA05           | Communication and Navigation Systems                         |

| TA06           | Human Health, Life Support and Habitation Systems            |

| TA07           | Human Exploration Destination Systems                        |

| TA08           | Science Instruments, Observatories and Sensor Systems        |

| TA09           | Entry, Descent and Landing                                   |

| TA10           | Nanotechnology                                               |

| TA11           | Modelling, Simulation, Information Technology and Processing |

| TA12           | Materials, Structures, Mechanical Systems and Manufacturing  |

| TA13           | Ground and Launch Systems Processing                         |

| TA14           | Thermal Management Systems                                   |

Table 1: NASA Space technology roadmaps

As shown above, there is no technical area related to Microelectronics technology. However, a NASA Roadmap for Microelectronic Needs was presented in 1999 in the Electronics Radiation Characterization project. It discussed the key driving factors for NASA's microelectronics

needs, presented a sampling of the microelectronics needed to meet NASA's future missions, and acknowledge the effect emerging technologies may have on impacting satellite design[23]. In addition, The Electronics Radiation Characterization project of the NASA Electronic Parts and Packaging program, which is responsible for the research on microelectronics and photonics for NASA, presented a roadmap providing aid to NASA flight projects, technology developers and the aerospace community[24].

# • International Technology Roadmap for Semiconductors (ITRS)

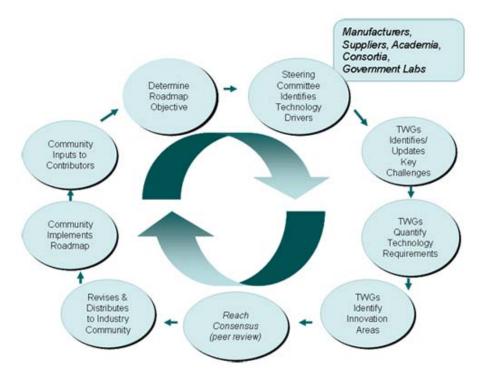

The ITRS is an organisation sponsored by the five leading chip manufacturing regions in the world: Europe, Japan, Korea, Taiwan and the United States. Its objective is to ensure advancements in the performance of the integrated circuits and the products that employ such devices, and continuing the health and success of the industry[25].

Figure 8: ITRS process

Global chip manufacturers, equipment suppliers and research communities work in cooperation in the Roadmap teams to identify critical challenges, encourage innovative solutions and welcome participation from the semiconductor community. Moreover, these teams join other strategic roadmapping efforts such as electronics and nanotechnologies, so the Roadmap effort comprehends the spectrum of needs for basic research capabilities and product potentials.

### European Space Components Coordination (ESCC)

The ESCC is an entity that aims to harmonise the efforts concerning the various aspects of electrical, electronic and electro-mechanical space components by ESA, European national and international public space organisations, the component manufacturers and the user industries[26].

EEE components play an essential role in the functional performance, quality, life cycle and costs of space systems. Their standardisation, product specification, development, evaluation, qualification and procurement needs to considerate the present and future European space policies and must be commensurate with user needs, market developments and technology trends.

The goal of the ESCC is to improve the availability of strategic EEE space components with the required performance and at affordable costs for institutional and commercial space programmes.

# 3 METHODOLOGY

# 3.1 Integrated circuit technologies and space missions studied

Ideally, this research would have included all integrated circuits used in all ESA satellites but due to time limitations, 5 months research, it has only focused in some specific types of technologies used in a selected number of space missions. This chapter describes the types of integrated circuit technologies studied and explains what space missions have been prioritized for this study.

# 3.1.1 Integrated circuit technologies subject of this research

The study focuses on high complexity and high effort design full-custom or semi-custom integrated circuits, which use digital, analogue or mixed-signal technology, both programmable and non-programmable. The specific types of complex integrated circuits included in this study are:

- ASIC (Application Specific Integrated Circuit): is an integrated circuit designed and

manufactured for a particular use, rather than intended for general-purpose use. This

study covers digital and mixed-signal ASICs, but focuses only on "high complexity"

ASICs, excluding from the analysis ASICs with less than 40 pins.

- FPGA (Field Programmable Gate Array): is a general purpose integrated circuit designed to be configured by the customer or designer after manufacturing. The configuration of the FPGA (also referred to as "programming" or "burning" the FPGA) is achieved by programming memory cells or fuses inside the chip that determine the internal connectivity of create the desire functions inside the FPGA. This study covers all the FPGA types that were found in the components lists of the satellites examined, without exclusions.

This research also distinguishes and compiles information of two other classes of integrated circuits that have a special interest in the ESA Microelectronics technology roadmaps:

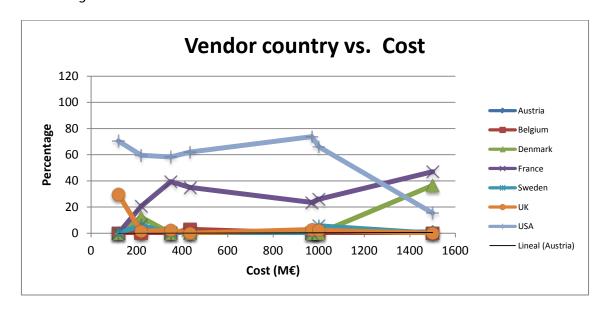

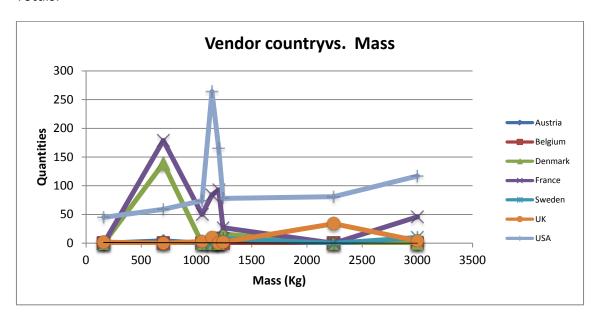

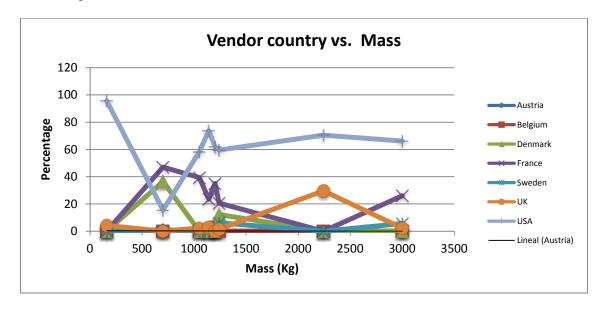

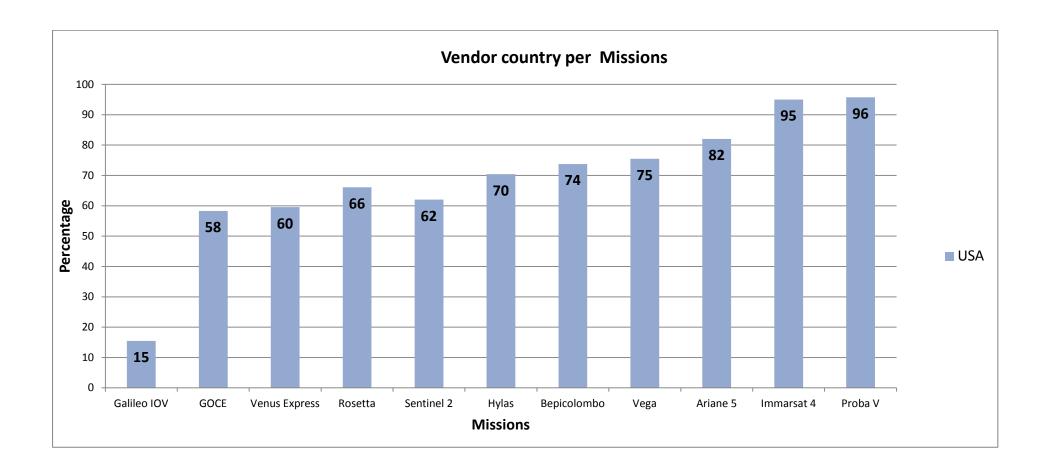

- Microprocessor: is a general purpose integrated circuit that incorporates the functions of a computer's central processing unit (CPU). It performs logical and arithmetic operations on the input data, as specified in the instructions created by the user ("software"), and produces output data. The data and instructions are normally stored in external memory chips. This study covers all microprocessors types that were found in the components lists of the satellites examined, without exclusions.