Escola Tècnica Superior d'Enginyeria Industrial de Barcelona

Universitat Politècnica de Catalunya

**Final Degree Project**

Design, Fabrication and Verification of a Mixed-Signal XY Zone Monitoring Circuit and its Application to a Phase Lock Loop Circuit

Álvaro Gómez Pau

Advisor: Joan Figueras Pàmies

> Barcelona June 2nd, 2010

# Resumen

El presente proyecto de final de carrera se centra en el diseño, análisis e implementación en silicio de una metodología de test/diagnosis basada en la comparación de firmas digitales generadas a partir de curvas de Lissajous. Se muestra su aplicación para testar la etapa de filtro de un circuito de bucle de enganche de fase (*phase lock loop*, PLL), así como los resultados experimentales de su implementación en tecnología CMOS de 65 nm.

La obtención de las firmas digitales se consigue mediante el uso de un circuito monitor, el cual, a partir de la composición de dos señales periódicas del circuito a analizar, genera, para cada punto de la curva de Lissajous, un valor digital. La utilización de varios monitores configurados de la manera adecuada permite una completa teselación del plano en diferentes zonas y por tanto, la generación de distintos códigos digitales (firma) a medida que la curva de Lissajous evoluciona en el tiempo.

El test del circuito y/o diagnosis del posible defecto se realiza mediante la comparación de la signatura golden o sin defecto y la signatura generada por el circuito testado. Para la comparación de firmas se emplea el concepto de distancia de Hamming entre códigos a modo de métrica de discrepancia. A partir de los valores precalculados de la métrica para cada posible valor del defecto se consigue realizar la diagnosis de este para el parámetro en estudio.

El trabajo se enmarca en el diseño de circuitos integrados de muy alta escala de integración usando una tecnología CMOS de actualidad (65 nm). Es por ello que se requieren técnicas de diseño analógico específicas, como lo son las estrategias centroidales para la elaboración de *layouts* o el correcto modelado de transistores nanométricos. Para esto último se hace uso del modelo Berkeley, el cual, debidamente ajustado a la tecnología empleada, proporciona aproximaciones muy aceptables y con relativa facilidad de uso.

Con el objetivo de verificar la metodología de test/diagnosis propuesta, se hace uso de una aplicación MATLAB que permite simular el comportamiento del circuito a testar en diferentes situaciones. Es posible excitar el circuito con distintas entradas, cambiar los parámetros de este, introducir defectos, o emplear distintos conjuntos de curvas para teselar el plano. La aplicación resulta fundamental para efectuar el proceso de diagnosis pues relaciona la cantidad de defecto con los valores de discrepancia obtenidos con la métrica definida.

Finalmente, se presentan los resultados experimentales obtenidos con el chip fabricado. Se constata el correcto comportamiento de este y la validez de la metodología de test/diagnosis propuesta.

# Contents

| Resur  | nen                                            | 3  |

|--------|------------------------------------------------|----|

| Forew  | ord                                            | 9  |

| 1. Int | roduction                                      | 11 |

| 1.1    | Objectives and Scope                           | 11 |

| 1.2    | Structure of the Project                       | 12 |

| 2. Tra | ansistor Modeling                              | 15 |

| 2.1    | . The Shichman-Hodges Model                    | 16 |

|        | 2.1.1. MOSFET Modeling Equations               | 16 |

|        | 2.1.2. Schicman-Hodges Model for Hand Analysis | 17 |

| 2.2    | . The Unified MOSFET Model                     | 20 |

|        | 2.2.1. MOSFET Modeling Equations               | 21 |

|        | 2.2.2. Model Fitting to CMOS 65 nm             | 21 |

|        |                                                |    |

| 7. | Con            | clusions and Future Work Outlines                         | 67 |

|----|----------------|-----------------------------------------------------------|----|

| 6. | $\mathbf{Exp}$ | erimental Results                                         | 61 |

|    |                | 5.2.2. Circuit Under Test Design                          | 57 |

|    |                | 5.2.1. Low-Pass Biquad Filter Theroy                      | 55 |

|    | 5.2.           | Circuit Under Test Design                                 | 55 |

|    | 5.1.           | Test Bench Design                                         | 53 |

| 5. | Test           | Bench and Circuit Under Test                              | 53 |

|    |                | 4.0.2. Parameter Verification Process                     | 48 |

|    |                | 4.0.1. Definition                                         | 47 |

| 4. | Met            | ric Definition                                            | 47 |

|    | 3.4.           | Layout Implementation                                     | 45 |

|    |                | 3.3.2. The small signal model applied to the second stage | 42 |

|    |                | 3.3.1. The small signal model applied to the first stage  | 37 |

|    | 3.3.           | The small signal model general theory                     | 36 |

|    |                | 3.2.2. Output Stage                                       | 35 |

|    |                | 3.2.1. Input Stage                                        | 30 |

|    | 3.2.           | Circuit Analysis                                          | 30 |

|    | 3.1.           | The XY Zoning Method                                      | 27 |

| Design, Fabrication and Verification of a Mixed-Signal XY Zone<br>Monitoring Circuit and its Application to a Phase Lock Loop Circuit | 7  |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Agradecimientos                                                                                                                       | 69 |

| Bibliography                                                                                                                          | 70 |

| A. Costs Evaluation                                                                                                                   | 73 |

| A.1. Human Resources Costs                                                                                                            | 73 |

| A.2. Chip Fabrication Costs                                                                                                           | 74 |

| A.3. Material Costs                                                                                                                   | 74 |

| A.3.1. Test Bench                                                                                                                     | 74 |

| A.3.2. Circuit Under Test                                                                                                             | 75 |

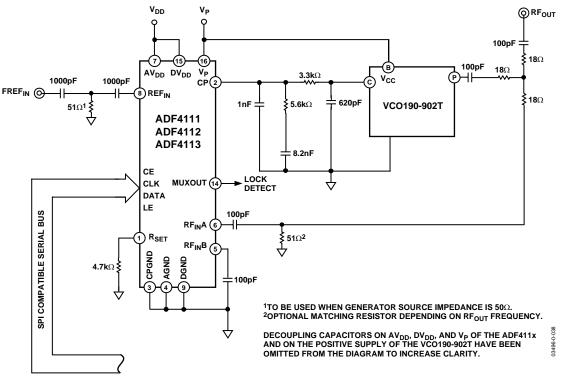

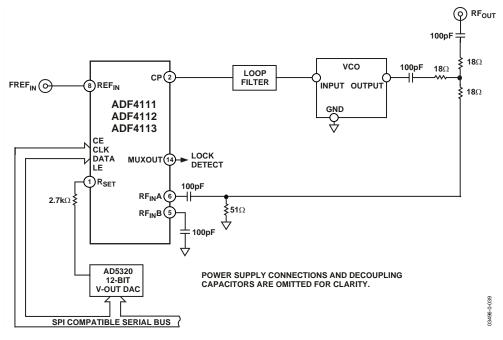

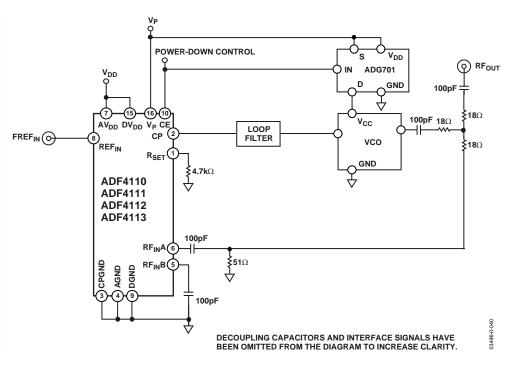

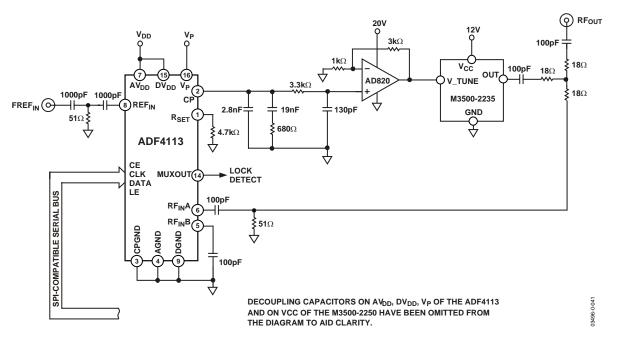

| A.3.3. PLL Evaluation Board                                                                                                           | 75 |

| A.4. Equipment and Software Costs                                                                                                     | 75 |

| A.5. Other Costs                                                                                                                      | 77 |

| A.6. Overall Project Costs                                                                                                            | 78 |

| B. Environmental Impact Assessment                                                                                                    | 79 |

| C. Orthogonal Projection                                                                                                              | 81 |

| C.1. Matrix of the Orthogonal Projection                                                                                              | 81 |

| D. Leasts Squares Fitting Method                                                                                                      | 85 |

| D.1. Linear Leasts Squares Method                                                                                                     | 85 |

| D.2. Generalised Leasts Squares Method                                                                                                | 86 |

| Е. | Estimation of Population Standard Deviation using Sample Data | 89  |

|----|---------------------------------------------------------------|-----|

| F. | Anderson-Darling Normality Test                               | 93  |

| G. | PLL Board Passive Filter                                      | 95  |

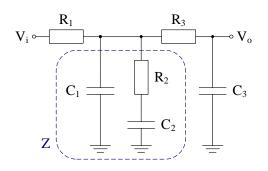

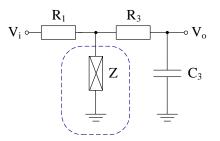

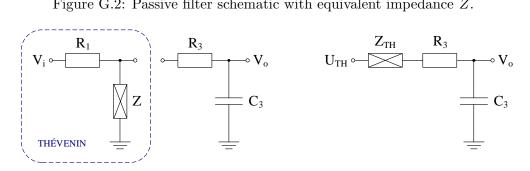

|    | G.1. Voltage-Voltage Transfer Function                        | 96  |

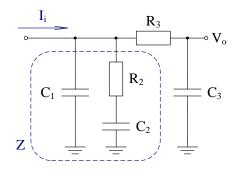

|    | G.2. Current-Voltage Transfer Function                        | 97  |

| н. | Matlab Codes                                                  | 99  |

| I. | Extra Stuff                                                   | 109 |

|    | I.1. Datasheets                                               | 109 |

|    | I.2. Published Papers                                         | 109 |

# Foreword

Current final project is the result of almost two years of work on analog and mixedsignal test and design of VLSI circuits at *Departament d'Enginyeria Electrònica* (UPC). I started as an undergraduate grant student researching on the topic of analog comparators, actually, analizing a very simple sense amplifier structure which has become the digital stage of the proposed monitor circuit in this project. Gradually, with the aid of my advisor, I started to work in a deeper and more serious research together with professors.

From this work, three conference papers have been published and presented. Also, some of the performed research, shapes the pages of the current project. The research has not finished yet, since any step reveals a vast and amazing field to focus on and look into.

At the present, I am enrolled in the master program in Electronic Engineering (UPC) and continuing the research at *Departament d'Enginyeria Electrònica*. The outlines of current research concentrate on multi-parameter defects diagnosis and on-chip low power design techniques.

> Álvaro Gómez Pau June 2nd, 2010

9

# Chapter 1

# Introduction

### 1.1. Objectives and Scope

Current thesis is framed in the design and test of VLSI (very large scale of integration) circuits. The pursued objective is to develop a low cost and simple BIST (built-in self-test) technique that could be directly applied to analog and mixed-signals integrated circuits testing. The developed methodology is aimed to be used beyond test and apply it to defective circuit parameter diagnosis.

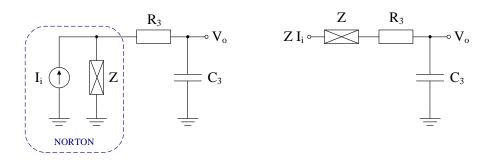

Project's starting point arises from a circuit studied by Ricard Sanahuja in his PhD thesis [1]. Sanahuja's circuit is a monitor circuit capable of composing two periodic signals and provide a differential output accordingly to a predefined monitor configuration. The presented testing method divides the plane into two zones using a straight line and checks whether the CUT remains in the specified zone or not. The differential output of the circuit should be transformed into a single ended digital signal.

The high end target of current project is, as said, to develop a reliable and low cost test/diagnosis methodology to be applied as a BIST technique. The objective is aimed to be achieved by analysing, designing and fabricating a CMOS version of the monitor circuit and use it to tesselate the XY plane into different zones. The composed signals generate a digital sequence (signature) which sould be compared to the free-defect one. This way, the study and definition of a suitable indicator of discrepancy between signatures is pursued too.

The nature of the project makes unavoidable the use of software tools (electrical or not) allowing the designer to check whether the proposed circuits/methodologies behave as expected or not. This drives to the importance of correct nanometric transistors models and accurate software simulation tools. A MATLAB application capable to emulate the tests/diagnosis methodology is also haunted.

The designed circuit is expected to be fabricated in a 65 nm CMOS technology and verified against a CUT with different levels of defects in order to show the final reliability of the proposed method on the fabricated chip.

### 1.2. Structure of the Project

The structure of project's memory has been organised accordingly to the chronological development of the project it describes. Several chapters recall specific and detailed information contained in the appendices. This way, the reader can go through the thesis in a straightforward way without delaying on demonstrations and detailed procedures.

Chapter 2 is devoted to transistor modeling. The classic quadratic Shichman-Hodges model is presented and discussed against current nanometric technologies for which it is not valid. The Unified MOSFET Model is introduced and fitted for ST-Microelectronics 65 nm transistors providing quite precise and manageable model for hand calculations.

In chapter 3, the monitor circuit that allows the composition of the Lissajous curves and generates the XY zonification is presented and analysed. Different analysis approaches are shown: overall operation, large signal, small signal,... Also, monitor's layout implementation is shown as well as the resulting switching curves from layout extraction simulations.

Chapter 4 presents the proposed metric definition in order to quantify signatures differences which allows the pass/fail test and parameter diagnosis (from the functional point of view). Also, its software implementation using a general purpose engineering oriented language like MATLAB is explained. The derived application capabilities are shown on a few examples of circuits with parameters out of tolerance ranges.

The test bench and circuit under test designs are detailed in chapter 5. Circuit design and layout of both PCBs are shown as well as a little theoretical approach to design of state

variable Biquad filters. Photographs of the obtained printed circuit boards are also displayed.

Chapter 6 is devoted to show the experimental results achieved once the monitor circuit has been fabricated and the developed methodology has been applied to a Biquad CUT (circuit under test). The results assert the reliability of the method and the correct monitor operaration as expected. The amount of defect of a CUT is succesfully diagnosed as the experimental results evidence.

Finally, in chapter 7 a recapitulation of the work is performed and some conclusions are drawn. Also, several future research paths are pointed out in order to improve the features of the presented circuits and methods.

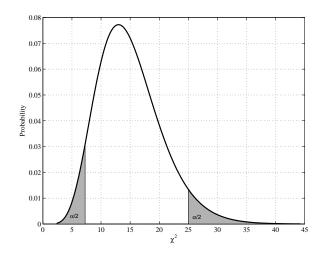

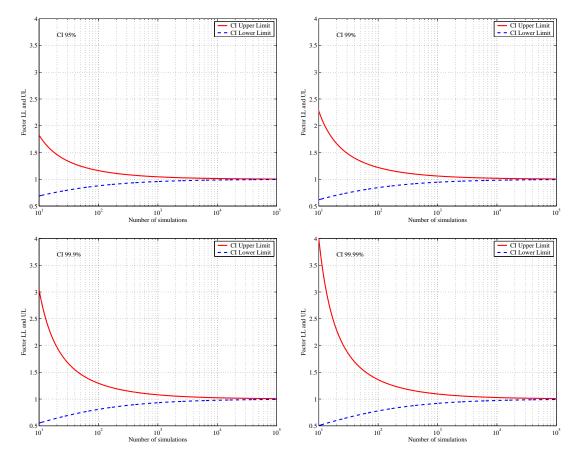

In the appendices, different extra information can be found. This way, in appendices A and B the economic evaluation of the project and environmental impact assessment are described. In appendices C and D the theory behind the generalised leasts squares method is reviewed. Appendices E and F contain statistical related stuff. The former shows an evaluation of the number of simulations to be done when using Monte Carlo methods and the latter depicts the Anderson-Darling normality test method. In appendix G, the transfer function of the passive filter used by default on the PLL evaluation board is derived. Appendix H contains the code (mainly MATLAB) that has been used un the thesis. It also contains the datasheet of some used components.

## Chapter 2

# **Transistor Modeling**

Current integrated electronic technologies would not be as laboured as they are today without the aid of software tools. Advanced EDA (electronic design automation) computer programs aid electronic engineers to efficiently design, verify and fabricate high performace circuits, simulate them and make conclusions about what is the best technique or methodology to meet the project goals.

The use of EDA tools allow engineers to obtain accurate simulation results without the need of fabricating the circuit. They are even able to simulate process and temperature variations via technology statistical characterization and therefore give off results about system performance under several realistic scenarios.

Although all the benefits mentioned above, there are several things which can not be made by a computer. The hand of the electronic engineer must be present along the whole design process in order to assure quality. Many times, experience, intuition and the hability to successfully catch up simulation results are the best aptitudes to obtain a good design. This is why dealing with equations and performing hand made calculations is the proper way to cope with design specificacions.

In the field of integrated analog and mixed-signal electronics<sup>1</sup>, the transistor is the most used device, so a model relating its electrical magnitudes is required to accomplish the design and analysis of any circuit. Of course, final calculations and design decisions will be

$<sup>^{1}</sup>$ The term *digital electronics* is just a level of abstraction, so do not exist itself, they are just well designed analog electronics.

made using simulated and experimental prototype results, but is extremely commendable to perform hand calculations in order to get the appropriate perspective of the overall bahaviour of the circuit.

### 2.1. The Shichman-Hodges Model

#### 2.1.1. MOSFET Modeling Equations

In 1968 Shichman and Hodges proposed a large signal model for field effect transistors [2]. This model is considered as the classical MOSFET model. It delivers a great intuitive idea of what is happening inside the transistor and is extremely simple and usefull. Its derivation can be seen in [3,4] as well as in the original article and almost in every textbook presenting analog electronic devices.

For an N-channel MOSFET transistor, the Shichman-Hodges model is,

$$I_{\rm D} = 0, \qquad V_{\rm GS} \le V_{\rm TH}$$

$$I_{\rm D} = k \frac{W}{L} \left( (V_{\rm GS} - V_{\rm TH}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right), \quad V_{\rm GS} > V_{\rm TH}, V_{\rm DS} < V_{\rm GS} - V_{\rm TH} \qquad (2.1)$$

$$I_{\rm D} = \frac{k}{2} \frac{W}{L} \left( V_{\rm GS} - V_{\rm TH} \right)^2, \qquad V_{\rm GS} > V_{\rm TH}, V_{\rm DS} \ge V_{\rm GS} - V_{\rm TH}$$

The three equations describe the behaviour of the device in the three possible working regions of the transistor: cut-off, ohmic (or linear) and saturation (or active). The magnitude  $I_{\rm D}$  is the drain-source current,  $V_{\rm TH}$  is the threshold voltage from which the transistor turns on and  $V_{\rm GS}$  and  $V_{\rm DS}$  are the voltages applied to gate and drain terminals. The quotient  $\frac{W}{L}$  is the aspect ratio of the transistor (width/length) and the k parameter is the so called transistor process transconductance,  $k = \mu C_{\rm ox}$ . Many times, the product  $k \frac{W}{L}$  is defined<sup>2</sup> as K, being simply called MOSFET transconductance. For a P-channel device the modeling equations are valid but inverting the side of the inequalities.

The classical MOSFET model is implemented in SPICE-like simulators under the name of SPICE Level 1 [5]. It means it is the most simple mathematical approach to the bahaviour

<sup>&</sup>lt;sup>2</sup>Depending on the author, parameters k and K can be seen written as  $\beta_{\Box}$  and  $\beta$  respectively.

of MOSFET transistors. Of course, more accurate models are available involving dozens of parameters in order to precisely model the real behaviour. These models are usually provided by the technology manufacturer [6], including extensive documentation and PVT variations characterization.

#### 2.1.2. Schicman-Hodges Model for Hand Analysis

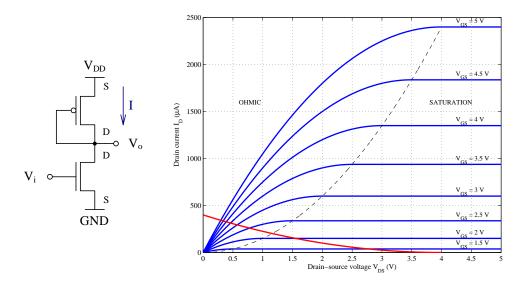

In order to show the usage of the Shicman-Hodges model, a simple NMOS inverter circuit will be analised (its transfer characteristic). Consider the active loaded inverter of Figure 2.1 with single supply of  $V_{\rm DD} = 5$  V and parameters of Table 2.1 for each device.

Figure 2.1: NMOS inverter schematic (left) and NMOS transistor DC characteristics with loading curve plotted (right).

The PMOS transistor has the drain and gate terminals shorted (diode configuration), so in inequality  $V_{\rm DS} \leq V_{\rm GS} - V_{\rm TH}$  from equations (2.1) for a PMOS, the terms  $V_{\rm DS}$  and  $V_{\rm GS}$ cancell to yield  $0 \leq -V_{\rm TH}$ , that is  $V_{\rm TH} \leq 0$ , which allways states for a P-channel transistor. This way, the PMOS transistor works in saturation and acts as a current source. The delivered current is, therefore,

$$I = \frac{K_p}{2} (V_o - V_{\rm DD} - V_{\rm TH}_p)^2$$

(2.2)

Depending on the working region of the NMOS transistor (which is function of its input

voltage  $V_i$ ) and applying KCL at the output node, the input-output transfer curve can be computed and traced.

- 1. For  $V_i \leq V_{\text{TH}n}$ , the driver transistor will be in cut-off, so I = 0, that is  $\frac{K_p}{2}(V_o V_{\text{DD}} V_{\text{TH}p})^2 = 0$ , from which  $V_o = V_{\text{DD}} + V_{\text{TH}p}$  is obtained. Numerically,  $V_o = 5 + (-1) = 4$  V.

- 2. For subsequent input voltages greater than  $V_{\text{TH}n}$ , the NMOS transistor will work in saturation (we will check that later on seeing  $V_o \geq V_i - V_{\text{TH}n}$ ). The KCL equation is now,  $\frac{K_p}{2}(V_o - (V_{\text{DD}} + V_{\text{TH}p}))^2 = I = \frac{K_n}{2}(V_i - V_{\text{TH}n})^2$ . Rooting this expression and solving for  $V_o$  yields,

$$V_o = V_{\rm DD} + V_{\rm TH}_p - \sqrt{\frac{K_n}{K_p}} (V_i - V_{\rm TH}_n)$$

(2.3)

This equation is a straight line with a negative slope value of  $\sqrt{\frac{K_n}{K_p}}$ . In our case example, the equation is  $V_o = 4 + \sqrt{6}(1 - V_i)$ .

The previous equation stands until the ohmic region is achieved. The boundary condition for this zone is  $V_o = V_i - V_{\text{TH}n}$ , so  $V_{\text{DD}} + V_{\text{TH}p} - \sqrt{\frac{K_n}{K_p}}(V_i - V_{\text{TH}n}) = V_i - V_{\text{TH}n}$ , from which easily can be obtained the limit input voltage to keep the NMOS transistor working in saturation region,

$$V_{\rm lim} = V_{\rm TH}_n + \frac{V_{\rm DD} + V_{\rm TH}_p}{1 + \sqrt{\frac{K_n}{K_p}}}$$

(2.4)

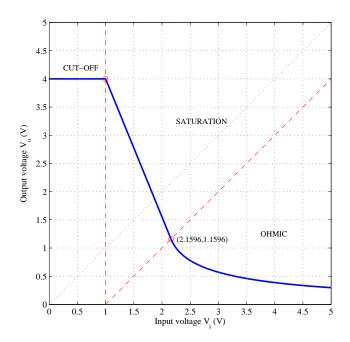

The limit input voltage for the example we are studying is  $V_{\text{lim}} = 2.15 \text{ V}$ . Check Figure 2.2 for details on the transfer characteristic.

3. For input voltages greater than  $V_{\text{lim}}$ , the driver transistor achieves ohmic region, so accordingly to Schicman-Hodges model the following equality states,

$$\frac{K_p}{2}(V_o - V_{\rm DD} - V_{\rm TH_p})^2 = K_n \left( (V_i - V_{\rm TH_n})V_o - \frac{V_o^2}{2} \right)$$

(2.5)

Which is a second order polynomial equation that can rearrenged as follows,

$$\left[1 + \frac{K_n}{K_p}\right] V_o^2 + \left[-2\left((V_{\rm DD} - V_{\rm TH}_p) + \frac{K_n}{K_p}(V_i - V_{\rm TH}_n)\right)\right] V_o + \left[(V_{\rm DD} - V_{\rm TH}_p)^2\right] = 0$$

(2.6)

Its solution is computed via the well known quadratic formula. The resulting expression is of the form  $A + B\sqrt{CV_i}$ , where A, B and C are constant values. Check Figure 2.2 to see the resulting rational function on the ohmic region of operation.

|      | $k\left(\frac{\mu A}{V^2}\right)$ | $\frac{W}{L}$ | $K\left(\frac{\mu A}{V^2}\right)$ | $V_{\rm TH}$ (V) |

|------|-----------------------------------|---------------|-----------------------------------|------------------|

| PMOS | 50                                | 1             | 50                                | -1               |

| NMOS | 100                               | 3             | 300                               | 1                |

Table 2.1: MOSFET parameters for Figure 2.1 NMOS inverter.

In order to compare the Schicman-Hodges model and the performed analysis with reallife transistors, a simulation of the circuit in Figure 2.1 has been made. It has been achieved using HSPICE simulator with an ST-Microelectronics 65 nm technology.

Figure 2.2: NMOS inverter transfer function determined via hand calculations and the Schicman-Hodges large signal MOSFET model.

As can be seen in Figure 2.2 and Figure 2.3, the two transfer characteristics highly differ. This fact strengths the need of obtaining a new model to be applied in hand calculations.

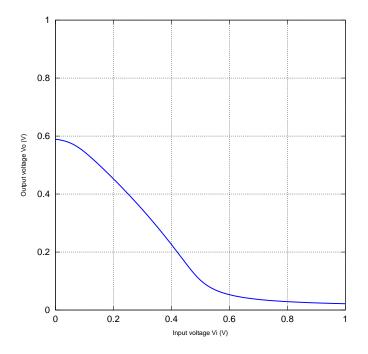

Figure 2.3: NMOS inverter simulated transfer function using ST 65 nm technology. For this technology,  $V_{\text{DD}}$  voltage is 1 V. The aspect ratio of the transistors have been kept identical to those considered in hand analysis.

### 2.2. The Unified MOSFET Model

Despite of its simplicity, the Shichman-Hodges Model does not match current transistors characteristic curves. This is due to second order effects, like velocity saturation or channel length modulation effects. For this reason, the following Berkeley model [7] is proposed and fitted using the generalised leasts squares method presented in appendix D.

Berkeley model equations are:

$$I_{\rm D} = 0 \qquad V_{\rm GS} \le V_{\rm TH}$$

$$I_{\rm D} = k \frac{W}{L} \left( (V_{\rm GS} - V_{\rm TH}) V_{\rm min} - \frac{V_{\rm min}^2}{2} \right) (1 + \lambda V_{\rm DS}) \quad V_{\rm GS} > V_{\rm TH}$$

$$(2.7)$$

#### 2.2.1. MOSFET Modeling Equations

As seen, Schichman-Hodges model is not suitable for modeling small transistors such as ST-65nm because it does not take in consideration second order effects like the channel length modulation or velocity saturation. Instead, the unified MOS model will be used. Accordingly to it, the drain current can be expressed as follows,

$$i_{\rm d} = k \frac{W}{L} \left( V_{\rm gt} V_{\rm min} - \frac{V_{\rm min}^2}{2} \right) \left( 1 + \lambda V_{\rm ds} \right)$$

Where  $V_{\min} = \min\{V_{gt}, V_{ds}, V_{dsat}\}$  and  $V_{gt} = V_{gs} - V_{TH}$ . The min function should be turned into a max function if a PMOS transitor is beeing modeled. The working region depends on the value of  $V_{\min}$  as shown in the following table (for NMOS),

| Region    | $V_{ m min}$                | Expanded model for $i_{\rm d}$                                                                                             |

|-----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Cut-off   | $(V_{\rm gs} < V_{\rm TH})$ | 0                                                                                                                          |

| Linear    | $V_{ m ds}$                 | $k\frac{W}{L}\left((V_{\rm gs} - V_{\rm TH})V_{\rm ds} - \frac{V_{\rm ds}^2}{2}\right)\left(1 + \lambda V_{\rm ds}\right)$ |

| Vel. Sat. | $V_{\rm dsat}$              | $k \frac{W}{L} \left( (V_{\rm gs} - V_{\rm TH}) V_{\rm dsat} - \frac{V_{\rm dsat}^2}{2} \right) (1 + \lambda V_{\rm ds})$  |

| Sat.      | $V_{ m gt}$                 | $\frac{k}{2}\frac{W}{L}\left(V_{\rm gs} - V_{\rm TH}\right)^2 \left(1 + \lambda V_{\rm ds}\right)$                         |

#### 2.2.2. Model Fitting to CMOS 65 nm

As can be seen, the unified MOS model depends on four parameters which have to be properly calibrated to approach the simulated curves (Spectre),

$$i_{\rm d} = f(V_{\rm TH}, k, V_{\rm dsat}, \lambda)$$

The direct analytical application of the leasts squares method is not suitable because of the nonderivability of the drain current function and the nonlinearity relations among the unknown parameters. It will be easier to find relations between the calibration parameters and then adjust de model empirically. These two criterion will be used:

CRITERION 1: The separation of curves  $i_{\rm d} = f(|V_{\rm ds}| = V_{\rm DD})$  at velocity saturation region must be constant since they grow linearly.

CRITERION 2: The maximum current for  $|V_{ds}| = |V_{gs}| = V_{DD}$  will be fixed and equaled to the obtained simulation current.

Note that the criterions have been taken in the velocity saturation region because it is the most important and is usually assumed to be the working region for hand analysis.

The first criterion stands,

$$\begin{split} i_{\mathrm{d1}} &= k \frac{W}{L} \left( (V_{\mathrm{gs}_{1}} - V_{\mathrm{TH}}) V_{\mathrm{dsat}} - \frac{V_{\mathrm{dsat}}^{2}}{2} \right) (1 + \lambda V_{\mathrm{ds}}) \\ i_{\mathrm{d2}} &= k \frac{W}{L} \left( (V_{\mathrm{gs}_{2}} - V_{\mathrm{TH}}) V_{\mathrm{dsat}} - \frac{V_{\mathrm{dsat}}^{2}}{2} \right) (1 + \lambda V_{\mathrm{ds}}) \end{split}$$

Just for convenience let define  $S = i_{d2} - i_{d1}$ , so their difference stablishes,

$$S = k \frac{W}{L} V_{\rm dsat} (V_{\rm gs_2} - V_{\rm gs_1}) (1 + \lambda V_{\rm ds})$$

From which  $V_{\text{dsat}}$  can be easily computed,

$$V_{\rm dsat} = \frac{S}{k\frac{W}{L}(V_{\rm gs_2} - V_{\rm gs_1})(1 + \lambda V_{\rm ds})}$$

The second criterion stands that,

$$i_{\rm dMAX} = k \frac{W}{L} \left( (V_{\rm gs} - V_{\rm TH}) V_{\rm dsat} - \frac{V_{\rm dsat}^2}{2} \right) (1 + \lambda V_{\rm ds})$$

where  $i_{\rm dMAX}$  will be defined as M. This way,  $\lambda$  parameter is written as,

$$\lambda = \frac{1}{V_{\rm ds}} \left\{ \frac{M}{k \frac{W}{L} \left( (V_{\rm gs} - V_{\rm TH}) V_{\rm dsat} - \frac{V_{\rm dsat}^2}{2} \right)} - 1 \right\}$$

substituting  $V_{\rm dsat}$  by the value finded previously and after a bit of algebra, the  $\lambda$  parameter yields,

$$\lambda = \frac{1}{V_{\rm ds}} \left\{ \frac{S^2}{2k\frac{W}{L}(V_{\rm gs_2} - V_{\rm gs_1})^2} \left( \frac{S(V_{\rm gs} - V_{\rm TH})}{V_{\rm gs_2} - V_{\rm gs_1}} - M \right)^{-1} - 1 \right\}$$

The calibration algorithm is listed below,

- 1. Compute from the simulated data the separation current at velocity saturation region and  $|V_{\rm ds}| = V_{\rm DD}$ , S and the maximum current given by the mosfet, M, when  $|V_{\rm gs}| = |V_{\rm ds}| = V_{\rm DD}$  ( $V_{\rm DD} = 1$  V in this technology).

- 2. Plot  $i_{\rm d} = f(V_{\rm gs})$  in order to estimate the threshold voltage  $V_{\rm TH}$ . This can be done by polynomial adjustment as well.

- 3. Define the value of the k parameter randomly so it will be adjusted empiricaly.

- 4. Compute the  $\lambda$  parameter using the derived expression.

- 5. Compute the  $V_{\text{dsat}}$  parameter using the derived expression.

- 6. Adjust the k parameter to meet the minimum error between the model and the simulated data.

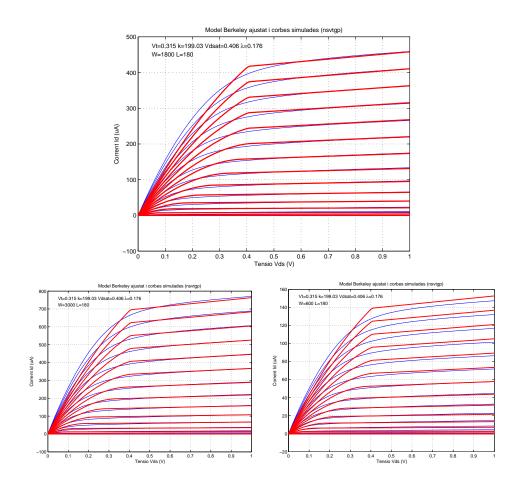

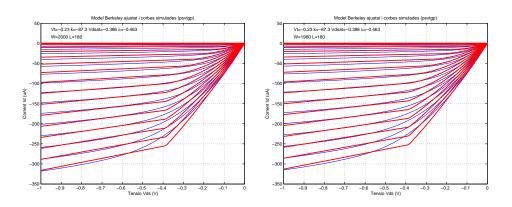

After the process of calibration depicted above, and the proper application of the generalisex leasts squares fitting method (with a good initial guess), the following adjusted curves are achieved for NMOS,

Where the first plot is the one that has been used to calibrate de model and the other two show the model adjusted to transistors with different aspect ratios.

The curves for PMOS transistors are,

As can be seen, in all the cases, a good current adjustment is achieved. The model is

25

suitable to be used in any hand analysis calculation, thus its simplicity and easy of use. Of course, the model does not present an outstanding precision<sup>3</sup>, but delivers a quite reasonable and intuitive values.

<sup>&</sup>lt;sup>3</sup>Simulation results have to be used for that.

# Chapter 3

# **Proposed Monitor Circuit**

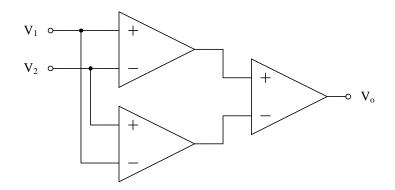

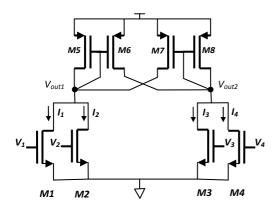

In this chapter, the monitor circuit used for the XY zone monitoring method is presented and analysed. The results shown are obtained from hand calculation analysis and layout software simulations. The monitor circuit is formed of two circuits:

- 1. The circuit which composes the two signals intended to be used for testing. Here after will be called the first stage or input stage circuit.

- 2. The circuit of a high gain output stage analog comparator. Here after will be called as the second stage or output stage.

The firsts studies, designs and analysis of the input stage circuit were presented by Ricard Sanahuja in [1].

### 3.1. The XY Zoning Method

The XY zoning method is based on the composition of two relevant signals of the circuit, x(t) and y(t) in the same way an oscilloscope represents the trace configured in XY mode. For many simple circuits, the most suitable signals to compose are the input excitation and the output response of the CUT.

If the input signal x(t) is formed by a finite spectrum of frequencies assuring rational reations among them and the signal is applied to a linear circuit, the input and response of the CUT, and therefore the composition, will be periodic. In such case, the resulting trace is called a Lissajous composition.

Of course, if the Lissajous compisition depends on the output of the CUT, a varied curve will be obtained if the circuit being tested is not operating inside the tolerance ranges. The discrepance of the golden and observed Lissajous curve is the fact that will allow to design a test and diagnosis method using such concepts.

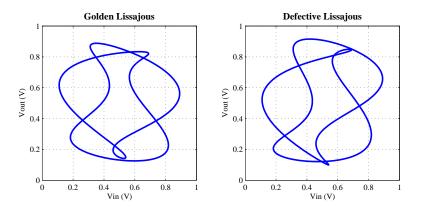

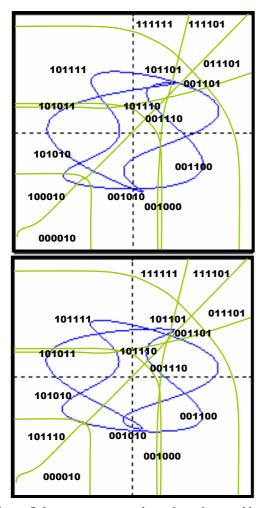

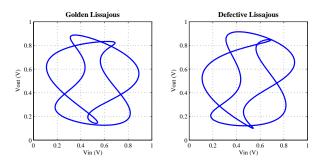

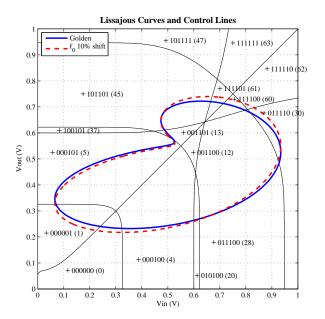

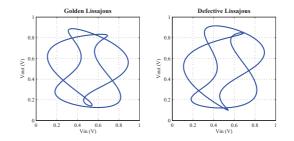

Figure 3.1: Golden and defective Lissajous.

In Figure 3.1 can be seen the response of a Biquad filter to a multitone input. On the left, the golden Lissajous is plotted. On the right, the characteristic filter frequency has been shifted 10% yielding therefore a slighly different Lissajous.

The main objective of the XY Zoning method is to test whether a circuit is ok or not by the comparison of a sequence of digital signatures generated by Lissajous composition analysis. In fact, the observed and defective Lissajous curves can be considered as the analog signature of the CUT, but these signature's comparison is hard to be accomplished in the analog world, so a digitalization of the information of each trace is required.

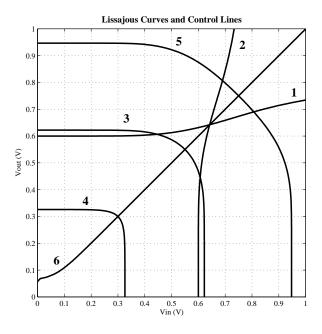

The dititalization of curve data is done by tesselating the XY plane in different regions and assigning a code to each zone. This way, the test procedure can be made just by checking whether the observed sequence of signatures are equal to those expected for a golden CUT or not. Figure 3.2 shows a possible tesselation of the XY plane using straight lines. Each line is a comparator that delivers a digital zero for one half of the plane and a digital one for the other half side.

Figure 3.2: Lissajous curves and straight switching curves.

The chosen codification criteria has been the green control line for the MSB bit, then the magenta, and then the black line for the LSB bit. In this case, the golden sequence signature is,

$$G = \{100, 101, 001, 101, 001, 000\}$$

$$(3.1)$$

and for the observed Lissajous which comes from a defective Biquad filter is,

$$O = \{100, 101, 111, 101, 001, 000, 100, 101, 001, 000\}$$

(3.2)

As can be checked, the signatures are very different (even in length), so the method yields a simple and reliable way to discriminate circuits which are out of tolerances ranges.

A great amount of catastrophic defects can be detected just by checking the golden and defective sequences.

### 3.2. Circuit Analysis

In this section, the proposed monitor circuit is presented and analysed. Mainly, the objective is to show how does the circuit behaves in large signal conditions and explain an overview of its operation.

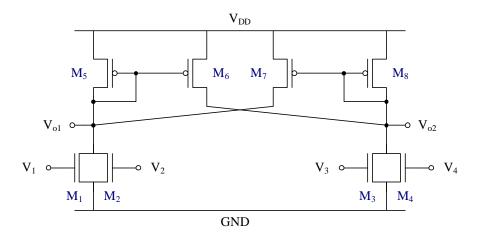

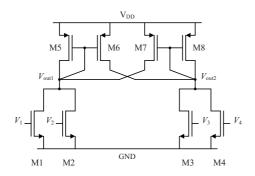

#### 3.2.1. Input Stage

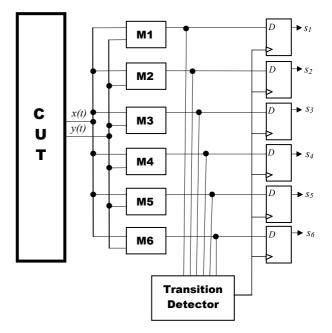

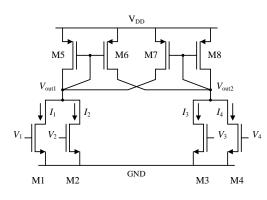

The previously explained XY zone monitoring method requires a simple and configurable nonlinear comparator to compose the pair of signals and provide a digital output. The first stage monitor circuit can be shown in Figure 3.3 [1,8]. It follows the structure of a CMOS pseudo-differential comparator whose driver transistors have been split into two in order to obtain multiple inputs. The structure can be generalized as needed by adding more transistors in parallel. The active loading with positive feedback helps to improve the gain<sup>1</sup> of the comparator.

The operation of the first stage of the monitor circuit of Figure 3.3 is easy. Two of the four voltages are used as the inputs x(t) and y(t) of the Lissajous trace (x(t) signal is, in general, a multitone function and y(t) is the transient response of the CUT to the input excitation) and the other two voltages are set to a DC voltage level in order to change the shape and parameters of the switching curve. The usage of several monitors with different setup allows a suitable tesselation of the plane for the expected traces.

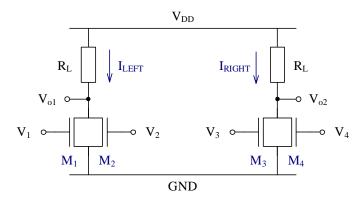

The active PMOS loading of the monitor input stage is absolutely symmetrical, so in order to simplify the analysis, pure resistive loading will be considered as shown in Figure 3.4. As the circuit being analysed is a comparator, the desired analysis will be performed arround the commutation point. As said, the active loading is symmetrical, son the commutation point (when the differential outputs crosses in the large signal analysis) takes place when

<sup>&</sup>lt;sup>1</sup>The structure allows to add hysteresis to the comparator but in this application is not suitable thus has been disabled by adequately sizing the feedback transistors aspect ratio.

Figure 3.3: First stage model.

output nodes voltages are equal, or what is the same, when the left and right currents in both branches are the same value.

Figure 3.4: First stage resistive loading model.

Using the Unified MOSFET model in saturation (not velocity saturation) region and applying KCL at the output nodes, the following equation state,

$$k\frac{W_1}{L_1}(V_1 - V_{\rm TH})^2 (1 + \lambda V_{o1}) + k\frac{W_2}{L_2}(V_2 - V_{\rm TH})^2 (1 + \lambda V_{o1}) = k\frac{W_3}{L_3}(V_3 - V_{\rm TH})^2 (1 + \lambda V_{o2}) + k\frac{W_4}{L_4}(V_4 - V_{\rm TH})^2 (1 + \lambda V_{o2}) \quad (3.3)$$

And because of the fact the analysis is being done at the commutation point,  $V_{o1} = V_{o2}$ , so the term  $1 + \lambda V_{DS}$  cancells out in both hand sides, as well as the process transconductance,

which can be constant for the same transistors. Just for convenience, the aspect ratio of the transistors will be indicated as  $S_i = \frac{W_i}{L_i}$ . Therefore, the resulting equation is,

$$S_1(V_1 - V_{\rm TH})^2 + S_2(V_2 - V_{\rm TH})^2 = S_3(V_3 - V_{\rm TH})^2 + S_4(V_4 - V_{\rm TH})^2$$

(3.4)

As stated, both of the  $V_i$ , k = 1, ..., 4, voltages will be acting as the x(y) and y(t) variables, so is evident that the resulting curves will be quite different whether the signals x and y are applied to the same side of the monitor or not. Each case will be discussed in the following two subsections.

For both situations, note that the stated equation is not valid for  $x, y < V_{\text{TH}}$ , because in subthreshold the transistor does not deliver current to the addition. The behaviour in such region is a straight line parallel to the axis whose variable makes the NMOS transistor operates in subthreshold.

#### Inputs at the Same Side

Suppose the input signals are applied at the same side of the monitor as  $V_1 = x$  and  $V_2 = y$ , and voltages  $V_3$  and  $V_4$  are set to a DC voltage level, then,

$$S_1(x - V_{\rm TH})^2 + S_2(y - V_{\rm TH})^2 = \underbrace{S_3(V_3 - V_{\rm TH})^2 + S_4(V_4 - V_{\rm TH})^2}_{\alpha}$$

(3.5)

The right hand side term has been recalled as a constant  $\alpha$  just for convenience. This way, dividing by  $\alpha$  (which can not be zero as is the sum of positive and nonzero quantities) the whole equation yields,

$$\frac{(x - V_{\rm TH})^2}{\frac{\alpha}{S_1}} + \frac{(y - V_{\rm TH})^2}{\frac{\alpha}{S_2}} = 1$$

(3.6)

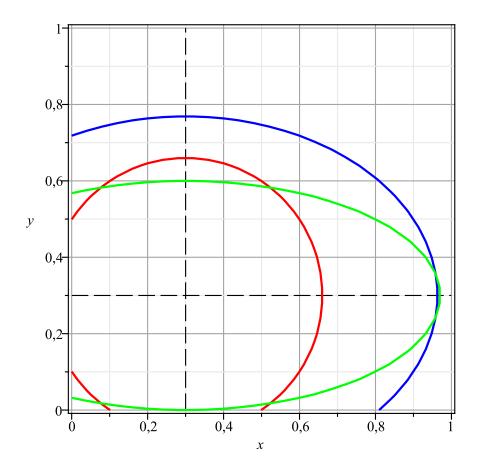

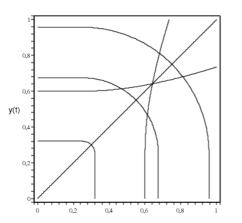

just the equation of an ellipse centered at  $(V_{\text{TH}}, V_{\text{TH}}) \in \mathbb{R}^2$  and with semi axis lengths  $a = \sqrt{\frac{\alpha}{S_1}}$  and  $b = \sqrt{\frac{\alpha}{S_2}}$ . In Figure 3.5 can be shown different ellipses generated with different transistors aspect ratios and DC voltages.

| Ellipse | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $V_3$ (V) | $V_4$ (V) |

|---------|-------|-------|-------|-------|-----------|-----------|

| Red     | 1     | 1     | 1     | 1     | 0.5       | 0.6       |

| Blue    | 2     | 4     | 1     | 2     | 0.7       | 0.9       |

| Green   | 1     | 5     | 1     | 1     | 0.6       | 0.9       |

Table 3.1: Ellipses parameters for curves in Figure 3.5.  $V_1$  and  $V_2$  are the x(t) and y(t) variables.

Figure 3.5: Different ellipses with parameters of Table 3.1.

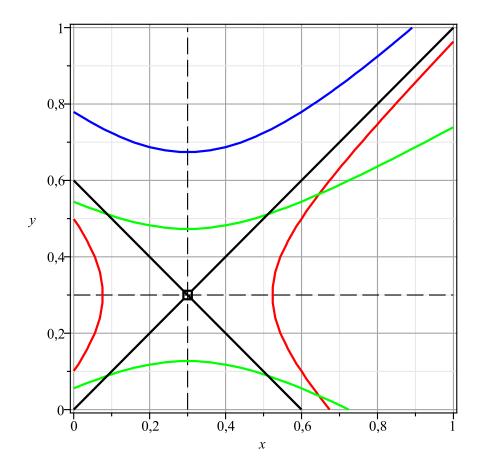

#### Inputs at Different Sides

Suppose now the input signals are connected to  $V_1 = x$  and  $V_4 = y$  which lay at different sides of the monitor input stage circuit. This fact forces some minor changes to the KCL equation as follows,

$$S_1(x - V_{\rm TH})^2 - S_4(y - V_{\rm TH})^2 = \underbrace{S_3(V_3 - V_{\rm TH})^2 - S_2(V_2 - V_{\rm TH})^2}_{\alpha}$$

(3.7)

Again, the constant term of the right hand side has been recalled as  $\alpha$ , but now  $\alpha$  is written as a difference and therefore can be positive or negative. Under the assumption of being positive, the equation can be written as,

$$\frac{(x - V_{\rm TH})^2}{\frac{\alpha}{S_1}} - \frac{(y - V_{\rm TH})^2}{\frac{\alpha}{S_4}} = 1$$

(3.8)

Which is the normalized equation of a hyperbola centered in  $(V_{\text{TH}}, V_{\text{TH}}) \in \mathbb{R}^2$  with parameters  $a = \sqrt{\frac{\alpha}{S_1}}$  and  $b = \sqrt{\frac{\alpha}{S_4}}$ . Note that due to the sign of  $\alpha$ , the equation can yield different parametrizations  $(t \ge 0)$ ,

$$x = V_{\rm TH} + a \cosh t$$

$$y = V_{\rm TH} + b \sinh t$$

$$x = V_{\rm TH} + a \sinh t$$

$$x = V_{\rm TH} + a \sinh t$$

$$y = V_{\rm TH} + b \cosh t$$

$$(3.9)$$

which are symmetrical having as symmetry axis the identity function y = x. Similarly as shown for same side inputs, several hyperbolas are plotted in Figure 3.6 with parameters in Table 3.2.

| Hyperbola | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $V_2$ (V) | $V_3$ (V) |

|-----------|-------|-------|-------|-------|-----------|-----------|

| Red       | 1     | 1     | 1     | 1     | 0.5       | 0.6       |

| Blue      | 2     | 4     | 1     | 2     | 0.7       | 0.9       |

| Green     | 1     | 5     | 1     | 3     | 0.6       | 0.9       |

| Black     | 1     | 1     | 1     | 1     | 0.5       | 0.5       |

Table 3.2: Hyperbolas parameters for curves in Figure 3.6.  $V_1$  and  $V_4$  are the x(t) and y(t) variables.

Special attention requires the degenerated black hyperbola. Note that due to the absolutely equilibrated monitor (equal aspect ratios and voltages of the transistors connected to DC levels), the resulting equation yields to,

Figure 3.6: Different hyperbolas.

$$S_1(x - V_{\rm TH})^2 - S_4(y - V_{\rm TH})^2 = 0$$

(3.10)

Rooting the equation, one finds the well known degenerated crossing straight lines centered at  $(V_{\text{TH}}, V_{\text{TH}}) \in \mathbb{R}^2$ ,

$$y = V_{\rm TH} \pm \sqrt{\frac{S_1}{S_4}} (x - V_{\rm TH})$$

(3.11)

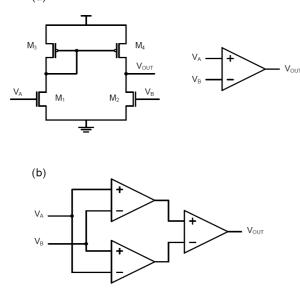

#### 3.2.2. Output Stage

The output stage of the monitor circuit is a plain comparator stage in order to dititalize the differential output from the first stage [8,9]. Second stage comparator is formed by a three

CMOS comparator structure as can be checked in Figure 3.7. Each of these stages is described by the schematic in Figure 3.8.

Figure 3.7: Second stage.

The aim of this structure is to increase the gain and therefore improve the digital output to be interpreted by the pad circuitry. The comparator is pretty simple to analyse due to the usage of a NMOS inverter in the left branch and the current mirror formed by M3 and M4 in order to equilibrate the branches.

Figure 3.8: Second stage.

## 3.3. The small signal model general theory

If a transistor is supposed to work in the surroundings of a fixed point (the quiscent point or simply the Q-point, also the biasing point) a linear aproximation can be taken as a good approach to the current function. That is, the first order Taylor polynomial for  $I_{\rm d} = f(V_{\rm gs}, V_{\rm ds})$  at  $Q = (V_{\rm GS}, V_{\rm DS})$ ,

$$I_d = I_D + \left( \begin{array}{cc} \frac{\partial I_d}{\partial V_{\rm gs}} & \frac{\partial I_d}{\partial V_{\rm ds}} \end{array} \right) \Big|_Q \left( \begin{array}{c} v_{\rm gs} \\ v_{\rm ds} \end{array} \right)$$

So the small signal amount of current is,

$$i_d = \frac{\partial I_d}{\partial V_{\rm gs}} \cdot v_{\rm gs} + \frac{\partial I_d}{\partial V_{\rm ds}} \cdot v_{\rm ds}$$

And defining, as usual,  $g_m = \frac{\partial I_d}{\partial V_{gs}}$  and  $g_o = \frac{\partial I_d}{\partial V_{ds}}$ , the small signal current can be rewritten as,

$$i_d = g_m v_{\rm gs} + g_o v_{\rm ds}$$

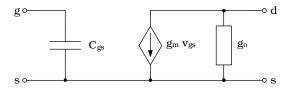

Accordingly to the previous calculations the following circuit is achieved,

#### 3.3.1. The small signal model applied to the first stage

In order to get a delay model of the circuit being studied, a small signal analysis will be performed. The model that will be used is the previously presented. Capacitance loading will be also considered to model the gate capacitance of the next stage.

Using the usual notation and referring to circuit components of presented first stage circuit, the nodal analysis yields the following system of equations,

$$\begin{bmatrix} g_{o1} + g_{o2} + g_{o5} + g_{o7} + s(C_{gs5} + C_{gs6} + C_{L1}) & 0 \\ 0 & g_{o3} + g_{o4} + g_{o8} + g_{o6} + s(C_{gs7} + C_{gs8} + C_{L2}) \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \begin{bmatrix} -g_{m1}V_1 - g_{m2}V_2 - g_{m5}V_{o1} - g_{m7}V_{o2} \\ -g_{m3}V_3 - g_{m4}V_4 - g_{m6}V_{o1} - g_{m8}V_{o2} \end{bmatrix}$$

(3.12)

Or what is the same,

$$\begin{bmatrix} g_{o1} + g_{o2} + g_{o5} + g_{o7} + g_{m5} + s(C_{gs5} + C_{gs6} + C_{L1}) & g_{m7} \\ g_{m6} & g_{o3} + g_{o4} + g_{o8} + g_{o6} + g_{m8} + s(C_{gs7} + C_{gs8} + C_{L2}) \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \begin{bmatrix} -g_{m1}V_1 - g_{m2}V_2 \\ -g_{m3}V_3 - g_{m4}V_4 \end{bmatrix}$$

(3.13)

Let us define,

$$G^{17} = g_{o1} + g_{o2} + g_{o5} + g_{o7} + g_{m5}$$

$$G^{38} = g_{o3} + g_{o4} + g_{o6} + g_{o8} + g_{m8}$$

$$C^{56} = C_{gs5} + C_{gs6} + C_{L1}$$

$$C^{78} = C_{gs7} + C_{gs8} + C_{L2}$$

So, under the above definitions, the problem is,

$$\begin{bmatrix} G^{17} + sC^{56} & g_{m7} \\ g_{m6} & G^{38} + sC^{78} \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \begin{bmatrix} -g_{m1}V_1 - g_{m2}V_2 \\ -g_{m3}V_3 - g_{m4}V_4 \end{bmatrix}$$

Which is a linear system of equations of the form Ax = b and its solution is given by

$x = A^{-1}b.$

Le us define, just for convenience,  $\Delta = \det A$ ,

$$\Delta = (G^{17} + sC^{56})(G^{38} + sC^{78}) - g_{m6}g_{m7}$$

And  $A^{-1}$  and b are,

$$A^{-1} = \begin{bmatrix} G^{38} + sC^{78} & -g_{m7} \\ -g_{m6} & G^{17} + sC^{56} \end{bmatrix} \qquad b = \begin{bmatrix} -g_{m1}V_1 - g_{m2}V_2 \\ -g_{m3}V_3 - g_{m4}V_4 \end{bmatrix}$$

This way, the solution is,

$$\begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \frac{1}{\Delta} \begin{bmatrix} -g_{m1}(G^{38} + sC^{78})V_1 - g_{m2}(G^{38} + sC^{78})V_2 + g_{m3}g_{m7}V_3 + g_{m4}g_{m7}V_4 \\ g_{m1}g_{m6}V_1 + g_{m2}g_{m6}V_2 - g_{m3}(G^{17} + sC^{56})V_3 - g_{m4}(G^{17} + sC^{56})V_4 \end{bmatrix}$$

In order to simplify the analysis, let us suppose that all the  $g_{mi}$ ,  $g_{oi}$  and  $C_{gsi}$  are equal. This assumption is valid because the analysis is taken place in the surroundings of the commutation point. This fact makes all the circuit balanced so currents are equal at the cross point of the outputs. The loading capacitances will be considered equal as well.

Under these conditions, the solution can be written as,

$$V_{o1} = \frac{-g_m(G+sC)}{\Delta} (V_1 + V_2) + \frac{g_m^2}{\Delta} (V_3 + V_4)$$

$$V_{o2} = \frac{g_m^2}{\Delta} (V_1 + V_2) + \frac{-g_m(G+sC)}{\Delta} (V_3 + V_4)$$

Beeing  $\Delta = (G + sC)^2 - g_m^2$  and  $G = G_m + 4g_o$ ,  $C = 2C_{gs} + C_L$ .

We note that there are two transfer functions to consider,

$$H_1 = \frac{-g_m(G+sC)}{\Delta} \qquad H_2 = \frac{g_m^2}{\Delta}$$

The denominator  $\Delta$  can be expanded and studied,

$$\Delta = \underbrace{G^2 - g_m^2}_{\Delta_0} + \underbrace{2GC}_{\Delta_1} s + \underbrace{C^2}_{\Delta_2} s^2$$

$$\Delta_0 = (g_m + 4g_o)^2 - g_m^2 = 8g_o(g_m + 2g_o) \approx 8g_m g_o$$

$$\Delta_1 = 2(g_m + 4g_o)(2C_{gs} + C_L) \approx 2g_m(2C_{gs} + C_L)$$

$$\Delta_2 = C^2 \approx 0$$

So,

$$\Delta \approx \underbrace{8g_m g_o}_{a_0} + s(\underbrace{2g_m(2C_{gs} + C_L)}_{a_1})$$

The simplifications made above, can be perfectly justified if the orders of magnitude are known. Gate capacitances are in the order of tenths of fF (10<sup>-14</sup>), the transconductance of the MOSFET is in the order of hundreds of  $\mu$ S (10<sup>-4</sup>) and the output conductance is about two orders of magnitude less than  $g_m$ , that is,  $\mu$ S (10<sup>-6</sup>).

The numerator of  $H_1$  is a first order polynomial in s, but it will be approximated by a first order one neglecting the term C in its transfer function.

Then, the system is governed by the following transfer functions,

$$H_1 = \frac{-g_m G}{a_0 + a_1 s} \qquad H_2 = \frac{g_m^2}{a_0 + a_1 s}$$

And under the same assumptions considered for G ( $G \approx g_m$ ),  $H_1$  and  $H_2$  become,

$$H_1 = \frac{-g_m^2}{a_0 + a_1 s} \qquad H_2 = \frac{g_m^2}{a_0 + a_1 s}$$

Which are identical unless its sign. These results match to the fact that the circuit beeing analyzed is a differential amplifier with splitted inputs,

$$V_{o1} = \frac{g_m^2}{a_o + a_1 s} \left( -(V_1 + V_2) + (V_3 + V_4) \right)$$

$$V_{o2} = \frac{g_m^2}{a_o + a_1 s} \left( +(V_1 + V_2) - (V_3 + V_4) \right)$$

The transfer function of the system, can be written in its canonical form as,

$$H = \frac{\pm A_{\rm DC}}{1 + \frac{s}{\omega_0}}$$

With,

$$A_{\rm DC} = \frac{g_m^2}{a_o} = \frac{g_m}{8g_o}$$

$$\omega_0 = \frac{a_0}{a_1} = \frac{4g_o}{2C_{gs} + C_L}$$

In order to estimate the delay of the whole monitor, only one input will be considered as variable, then

$$V_{o1} = -\frac{A_{\rm DC}}{1 + \frac{s}{\omega_0}} V_i$$

$$V_{o2} = \frac{A_{\rm DC}}{1 + \frac{s}{\omega_0}} V_i$$

Which its transient step response will be the typical of a first order system,

$$y(t) = A_{\rm DC}(1 - e^{-\omega_0 t})$$

The delay time will be defined as the time the switching (crossed outputs) takes place. Because of the two outputs are symmetrical, it will be at the time the half DC gain is achieved, so,

$$\frac{A_{\rm DC}}{2} = A_{\rm DC} (1 - e^{-\omega_0 t_\delta})$$

From where,

$$t_{\delta} = \frac{\ln 2}{\omega_0} = \frac{(2C_{gs} + C_L)\ln 2}{4g_o}$$

Note the independence of  $g_m$  from the delay expression.

#### 3.3.2. The small signal model applied to the second stage

The comparison stage is implimented using three CMOS differential amplifiers. The analysis will be performed the same way and also loading capacitances will be considered. The nodal analysis yields the following set of linear equations,

$$\begin{bmatrix} g_{o1} + g_{o3} + s(C_{gs3} + C_{gs4} + C_{L1}) & 0 \\ 0 & g_{o2} + g_{o4} + sC_{L1} \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \begin{bmatrix} -g_{m1}V_1 - g_{m3}V_{o1} \\ -g_{m2}V_2 - g_{m4}V_{o1} \end{bmatrix}$$

That is,

$$\begin{bmatrix} g_{o1} + g_{o3} + g_{m3} + s(C_{gs3} + C_{gs4} + C_{L1}) & 0 \\ g_{m4} & g_{o2} + g_{o4} + sC_{L1} \end{bmatrix} \begin{bmatrix} V_{o1} \\ V_{o2} \end{bmatrix} = \begin{bmatrix} -g_{m1}V_1 \\ -g_{m2}V_2 \end{bmatrix}$$

Beeing the solution,

$$V_{o1} = \underbrace{\frac{-g_{m1}}{g_{o1} + g_{o3} + g_{m3} + s(C_{gs3} + C_{gs4} + C_{L1})}_{\tilde{H}} V_{1}}_{\tilde{H}}$$

$$V_{o2} = \underbrace{\frac{-g_{m4}}{g_{o2} + g_{o4} + sC_{L2}}}_{H_{1}} \tilde{H} V_{1} + \underbrace{\frac{-g_{m4}}{g_{o2} + g_{o4} + sC_{L2}}}_{H_{2}} V_{2}$$

Note that only the output  $V_{o2}$  is used to load the following stage, so we are interested in its transfer functions  $H_1$  and  $H_2$  only. The previous statement stablishes that the consideration  $C_{L1} = 0$  is fasible.

Under the assumptions that the commutation takes place when the circuit is perfectly balanced, it is legal to suppose, as we did in the monitor circuit analysis, that all the transconductances and output conductances are equal as well as the gate capacitances.

This yields the following transfer functions,

$$H_1 = \frac{-g_m}{2g_o + sC_{L2}} \frac{-g_m}{2g_o + g_m + 2C_{gs}s} = \frac{g_m^2}{D(s)} \qquad H_2 = \frac{-g_m}{2g_o + sC_{L2}}$$

The denominator D(s) of  $H_1$  is aimed to be studied concisely,

$$D(s) = \underbrace{[2g_o(2g_o + g_m)]}_{a_0} + \underbrace{[4g_oC_{gs} + (2g_o + g_m)C_{L2}]}_{a_1}s + \underbrace{[2C_{gs}C_{L2}]}_{a_2}s^2$$

$$a_{0} = 2g_{o}(2g_{o} + g_{m}) \approx 2g_{m}g_{o}$$

$$a_{1} = 4g_{o}C_{gs} + (2g_{o} + g_{m})C_{L2} \approx 4g_{o}C_{gs} + g_{m}C_{L2} \approx g_{m}C_{L2}$$

$$a_{2} = 2C_{gs}C_{L2} \approx 0$$

And then,

$$H_1 = \frac{g_m^2}{2g_m g_o + g_m C_{L2} s} \qquad H_2 = \frac{-g_m}{2g_o + s C_{L2}}$$

So, with the exception of sign, they are identical, fact that matches with the assumption that the circuit beeing analyzed was a differential amplifier. So the transfer function of the circuit is,

$$H = \frac{g_m}{2g_o + sC_{L2}}$$

And the output is,

$$V_{o2} = H(V_1 - V_2)$$

Let us write the transfer function as is usual for a first order system,

$$H = \frac{A_{\rm DC}}{1 + \frac{s}{\omega_0}}$$

With  $A_{\rm DC} = \frac{g_m}{2g_o}$  and  $\omega_0 = \frac{2g_o}{C_{L2}}$ .

To estimate the delay time, the same methodology which has been applied to the first stage circuit will be considered here. The time to achieve the half of the DC gain is,

$$t_{\delta} = \frac{\ln 2}{\omega_0} = \frac{C_{L2} \ln 2}{2g_o}$$

Again, note the independence of  $g_m$  in the delay expression.

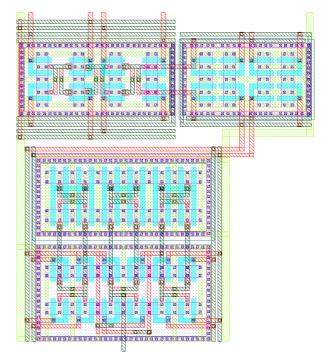

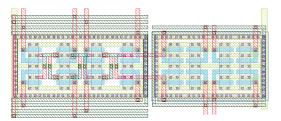

## 3.4. Layout Implementation

In analog electronics, and specially if using a small technolyy (65 nm), layout design is critical to meet circuit specifications. The studied monitor circuit layout has been carried out taking in consideration common centroid strategies [10] in order to minimize mismatch effects.

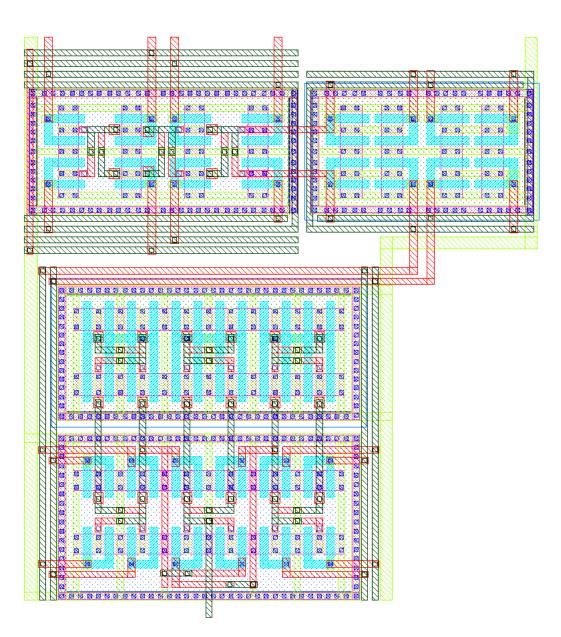

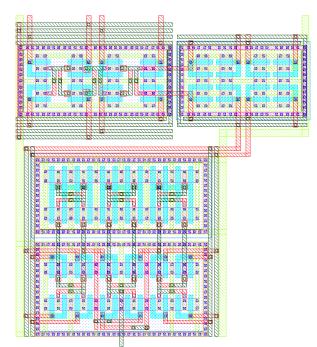

In Figure 3.9 can be appreciated the final layout design. It uses 5 metal layers, standard  $V_{\rm TH}$  and general purpose ST-Microelectronics transistors.

In order to achieve the final centroidal structure, any transistor has been splitted into four assuring this way a well-balanced structure.

Figure 3.9: Layout implementation in CMOS ST-Microelectronics 65 nm technology. The total area used per monitor is 116.1  $\mu m^2.$

## Chapter 4

# Metric Definition

## 4.0.1. Definition

In order to be able to compare the digital signatures generated by the circuit, an indicator of difference is required. Taking in consideration the zone codification, a possible choice is the following definition of a Normalized Discrepancy Factor,

$$NDF = \frac{1}{T} \int_0^T \operatorname{dist}(f, g) \, dt \tag{4.1}$$

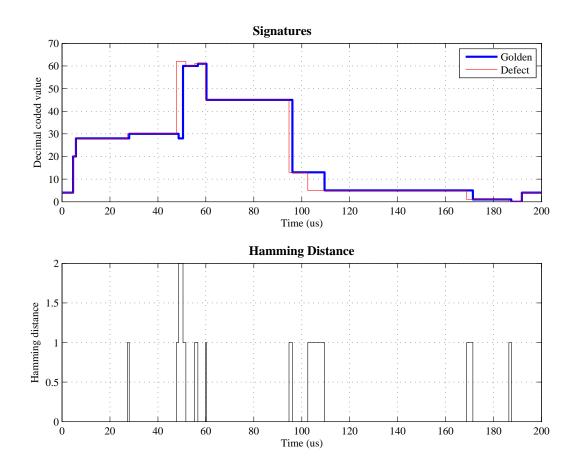

where the functions f(t) and g(t) respectively represent the defective and golden signatures defined within the period T of the Lissajous curves. Operator dist() is the Hamming distance of the codes at each time instant. The NDF parameter indicates the discrepancy of the defective and golden instantaneous codes weighted by the duration of interval in which the Lissajous curve remains in the same zone.

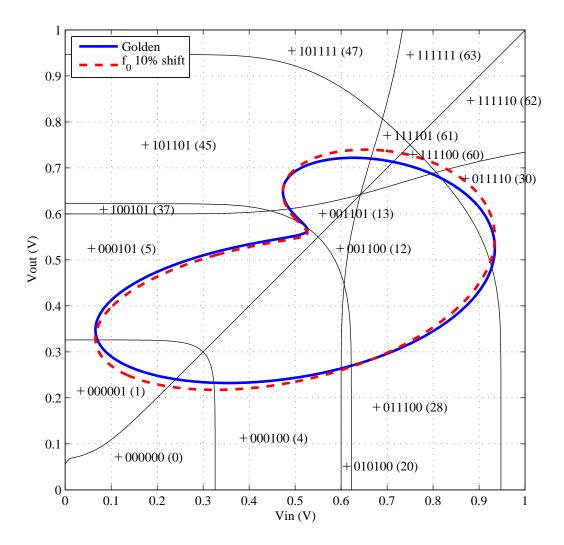

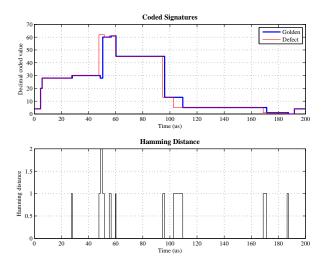

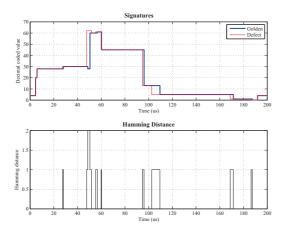

The previous definition matches the average value of the Hamming distance chronogram over the interval [0, T]. For the example of Figure 4.2, a NDF of 0.102102 is obtained.

Because of the the zone codification criterion, neighbouring zones only vary in one bit. This is why Hamming distance is suitable, as can be observed in the lower chronogram of Figure 4.2, where the Hamming golden-defect distance is plotted during a period. Note the achievement of 2 (in the sense of Hamming distance) in the interval [48, 50]  $\mu$ s. This is

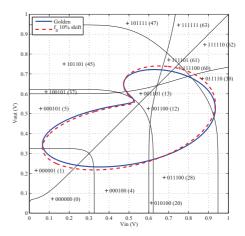

Figure 4.1: Control lines with zone codification and Lissajous compositions: golden and +10% shift in  $f_0$ .

because, in Figure 4.1, the faulty trace reaches zone  $111110_2(62_{10})$  instead of the sequence  $011110_2(30_{10})$ ,  $011100_2(28_{10})$ ,  $111100_2(60_{10})$ , which will define a free-defect Lissajous.

## 4.0.2. Parameter Verification Process

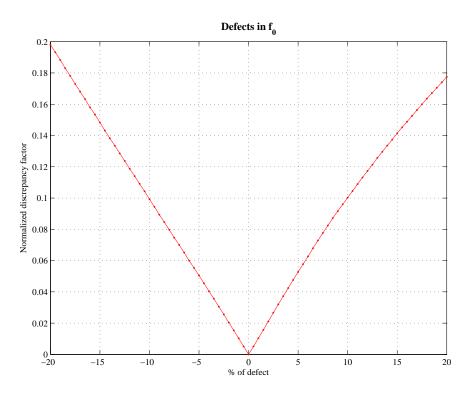

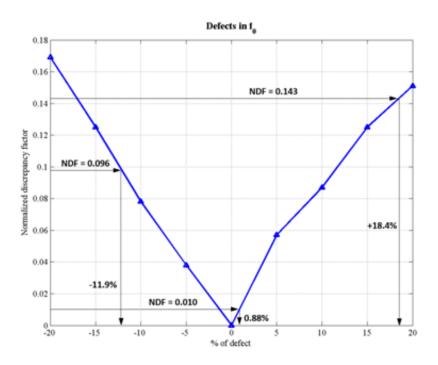

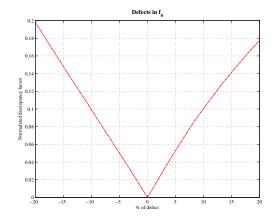

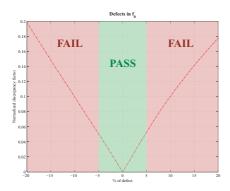

The NDF is used to evaluate the amount of deviation of the parameters under verification. Circuits with parameters satisfying specifications are expected to present small NDF values. To evaluate the NDF effectiveness, extensive software simulations have been performed on a Biquad filter circuit with different degrees of deviation in the natural frequency

Figure 4.2: Chronogram of digital signatures and Hamming distances for +10% shift in  $f_0$ . NDF = 0.102102.

of the filter. The discrepancy factor increases almost linearly with the amount of deviation and quite symmetrically with positive and negative parameter deviations, as can be seen in Figure 4.4.

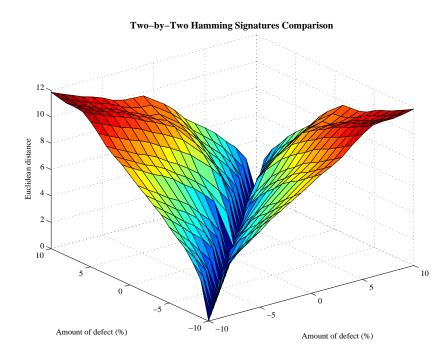

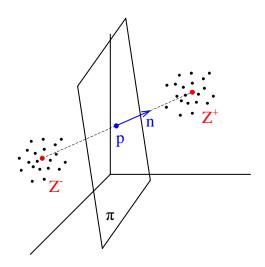

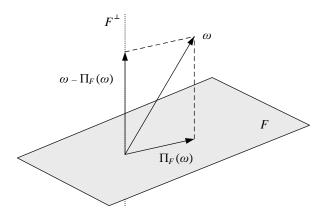

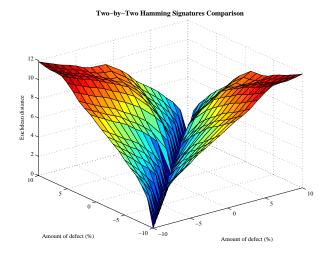

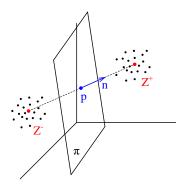

This metric detects discrepancies exceeding an absolute value over the nominal (golden) circuit parameter. In cases where the sign of the parameter deviation is required a data clustering procedure is used. To this purpose, distances between pairs of signatures are shown in Figure 4.5. This two-by-two comparison indicates that positive and negative defects lay separately in the N-dimensional space. Distances between same types of defects are also smaller than those mixing different types of defects.

A simple method to scatter the two groups of defects consists in computing a separation hyperplane. This data clustering method is performed by the calculation of the centre of gravity of every set and use it to define the hyperplane parameters. Let us respectively

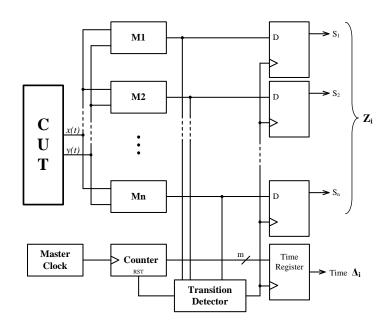

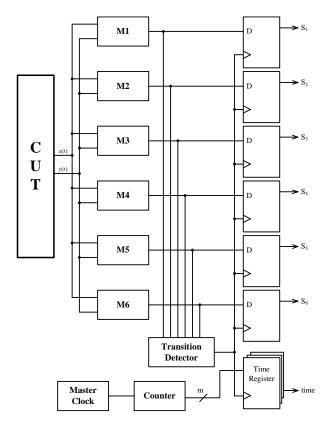

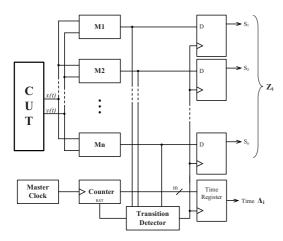

Figure 4.3: Asynchronous capturing module in order to generate the sigatures: the zone code and the time differences.

Figure 4.4: Normalized discrepancy factor for defects in  $f_0$ .

define  $z^+$  and  $z^-$  as the centre of gravity of the positive and negative set of defects. In an N-dimensional vector space, a hyperplane takes the form,

Figure 4.5: Distance between pairs of Hamming signatures.

$$\pi \equiv \sum_{i=1}^{N} n_i (z_i - p_i) = 0 \tag{4.2}$$

where  $n = (n_1, \ldots, n_N)$  is a vector normal to  $\pi$  and  $p = (p_1, \ldots, p_N)$  is any point within  $\pi$ . In this way, the following definitions become natural (see Figure 4.6),

$$n = z^{+} - z^{-}, \quad p = \frac{z^{+} + z^{-}}{2}$$

(4.3)

With the calculated  $\pi$ -hyperplane, parameter identification is easy because we only have to evaluate the resulting Hamming signature in the  $\pi$  equation. If the evaluation yields a positive number, the defect is positive whereas if it yields a negative value, the defect is negative. The amount of defect is determined with the graphical data of Figure 4.4.

Figure 4.6: Sketch of the separation plane in a three-dimensional vector space.

## Chapter 5

# Test Bench and Circuit Under Test

In order to check the designed monitor circuit and the developed test/diagnosis methodology, a test bench and a CUT are required. Both have been designed in single sided copper PCB with the aim to provide easy access to signals and components. This chapter shows the results on the fabrication and points out the objectives being pursued.

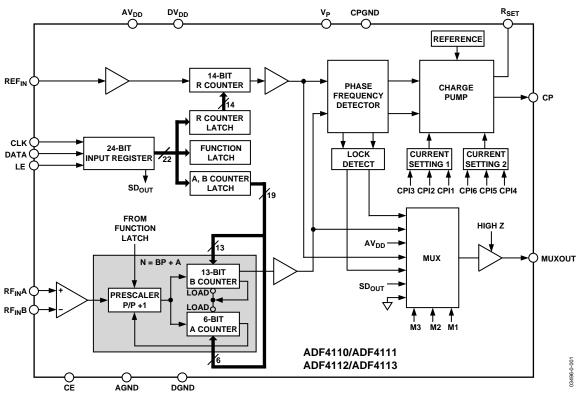

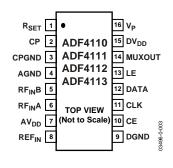

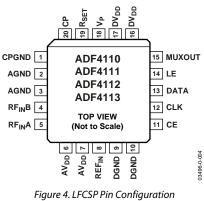

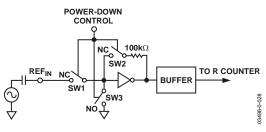

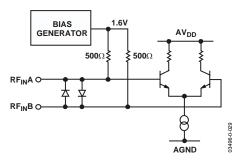

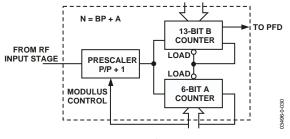

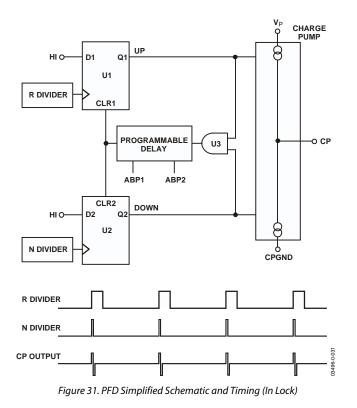

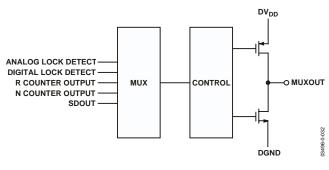

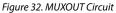

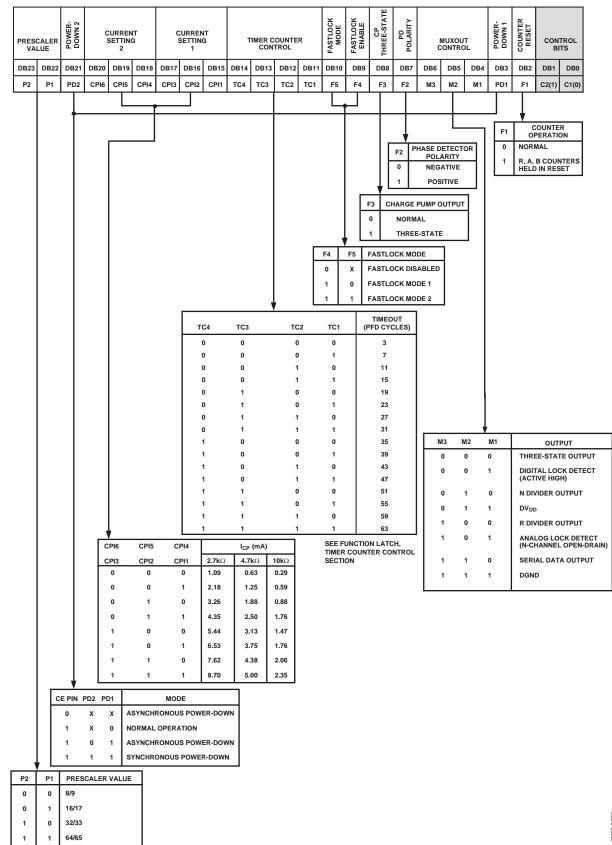

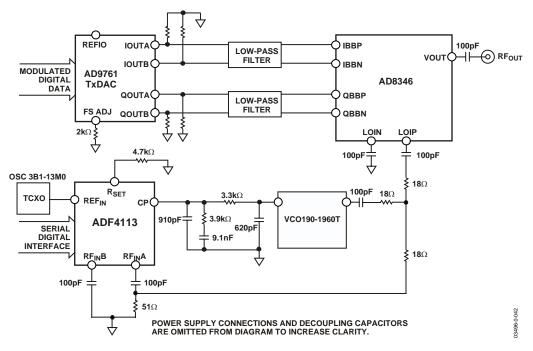

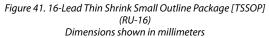

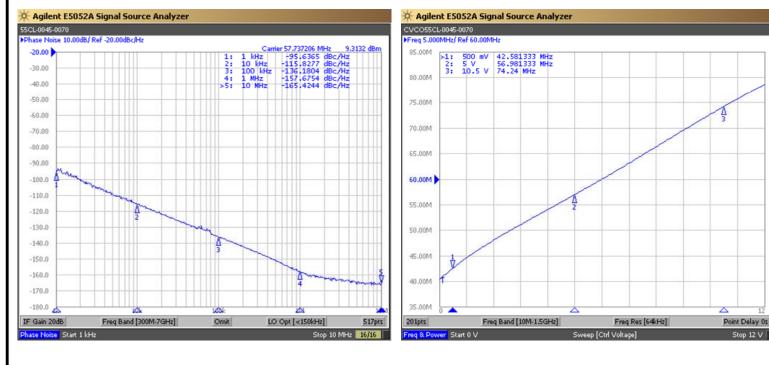

Originally, the goal was to use a PLL board at 55 MHz to test the fabricated monitor, but due to the results on frequency response of the monitor circuit, the decision to test only the filter part has been taken. In order to see details of the purchased PLL board and the associated VCO chip see appendix I.

## 5.1. Test Bench Design

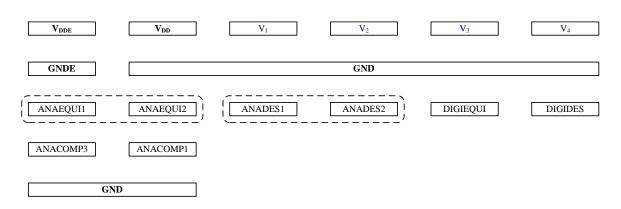

The fabricated monitor circuit has the following available signal connections:

- 1. Independent power supply for core and pads.

- 2. Four input voltages.

- 3. Two differential analog outputs from first stage (for each monitor).

- 4. One digital output from first stage (for each monitor).

- 5. One digital output from second stage (for each monitor).

Note that some of them are repeated for the balanced and unbalanced layouts that have been implemented.

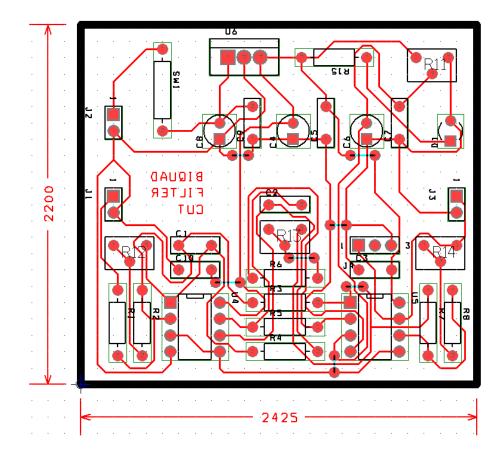

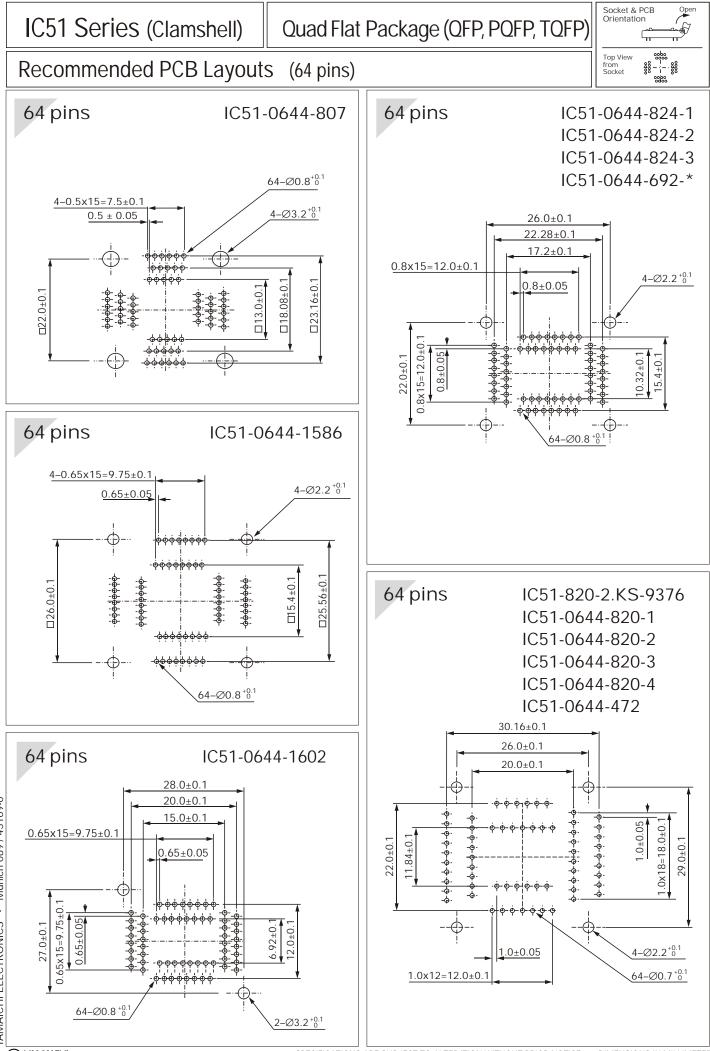

The designed test bench has been designed in order to gain easy access to each signal and allow extra components connections as decoupling capacitors, wiring, probes, buffer outputs, filtering, CUT connections,... A rough design of the layout can be seen in Figure 5.1.

Figure 5.1: Test bench schematized layout.

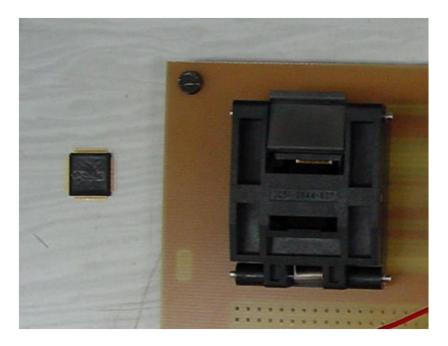

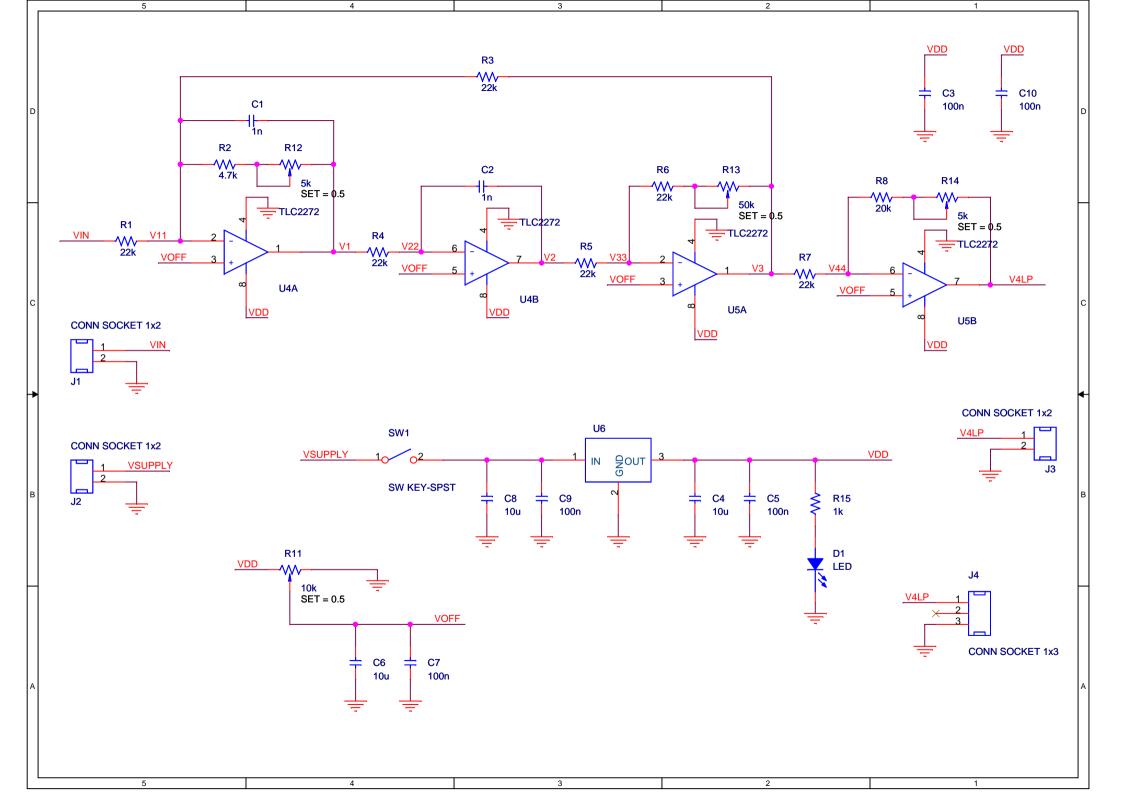

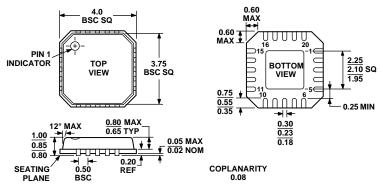

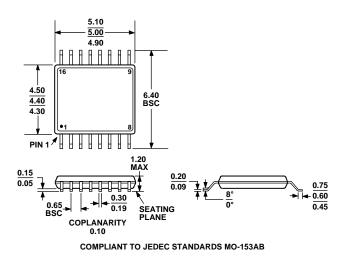

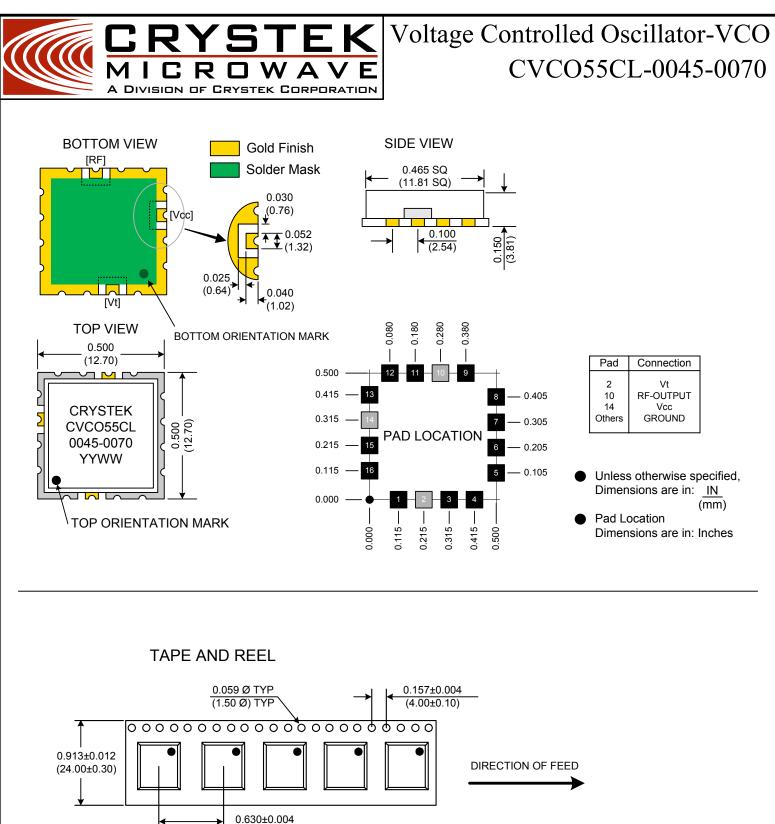

The fabricated chip packaging requires IC51-0644-807 socket (see appendix I for socket details). This is not a common socket that can be found in OrCAD Layout footprint libraries, so it has been to be hand designed accordingly to socket datasheet dimensions. In order to create footprint pins, a small script has been coded in Visual Basic to automate the process.

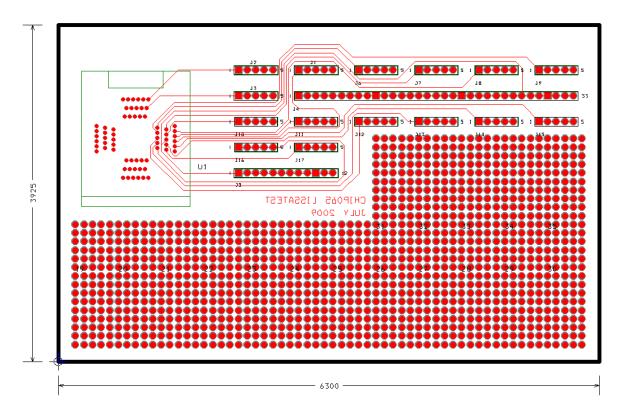

Test bench has been designed with OrCAD Layout and has been fabricated by CNC routing to *Taller Mecànic ETSEIB*. The final PCB layout can be seen in Figure 5.2. The PCB has been provided with an array of prototyping pins in order to use them to connect different auxiliary circuits.

Tracks widths of the design have been set to 12 mils and have been hand routed in order to optimize the design and avoid extra line capacitances and induced antenna behaviour.

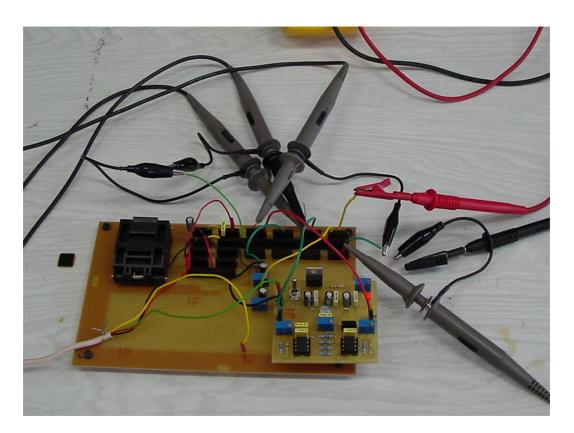

The designed test bench PCB has been sent for fabrication to *Taller Mecànic ETSEIB*. The final product can be seen in Figure 5.3. In the photograph also appears the chip socket, CUT circuit and connections.

Figure 5.2: Test bench layout designed with OrCAD Layout. The design has been sent to CNC fabrication at *Taller Mecànic ETSEIB*.

## 5.2. Circuit Under Test Design

As the low-pass filter of the PLL implementation can be of any kind [11] (the PLL board provides input and output pins in case of future connections intentions) a second order biquad filter implementation has been selected to test the fabricated monitor. In the following lines, a brief introduction theory of biquad filters and the fabricated filter itself will be shown.

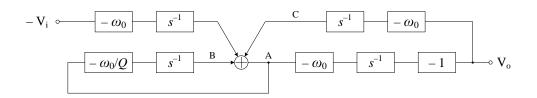

## 5.2.1. Low-Pass Biquad Filter Theroy

A second order low-pass Biquad filter [12] is a state variable filter which transfer function (relation between the input and the output signals) is described by the following expression (note that a cononical unity gain has been chosen for theoretical explanation),

Figure 5.3: Photograph of the machined PCB to lodge the IC socket, CUT circuit and connections between the modules and the oscilloscope and function generator. Power supply wires and signal probes can be seen too.

$$\frac{V_o}{V_i} = \frac{1}{\frac{s^2}{\omega_0^2} + \frac{1}{Q}\frac{1}{\omega_0} + 1}$$

(5.1)

From the above expression,  $\frac{s^2}{\omega_0^2}V_o + \frac{1}{Q}\frac{s}{\omega_0}V_o + V_o = V_i$  and multiplying by  $\frac{\omega_0}{s}$  and solving for  $\frac{s}{\omega_0}V_o$  yields,

$$\underbrace{\frac{s}{\omega_0}}_{A} = \frac{\omega_0}{s} V_i \underbrace{-\frac{1}{Q} V_o}_{B} \underbrace{-\frac{\omega_0}{s} V_0}_{C}$$

(5.2)

From the above equation, the block diagram of Figure 5.4 is obtained. Note that because the filter will be implemented using operationa amplifiers, it is easy to multiply by a negative constant.

Figure 5.4: Block diagram.

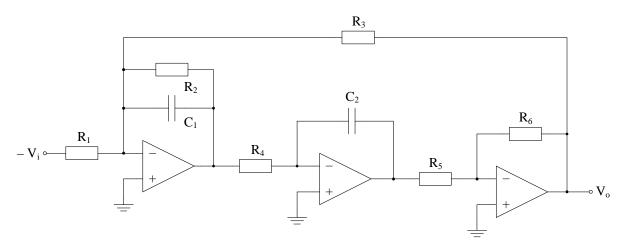

It is immediate to draw the corresponding schematic from the block diagrams shown in Figure 5.4 using opertational amplifiers in inverting configuration. As can be checked in Figure 5.5, summing inverter/integrating amplifiers has been used.

Figure 5.5: Biquad filter schematic.

Accordingly to the summing and integrating weights, the following equations state,

$$\omega_0 = \frac{1}{R_1 C_1}, \quad \frac{\omega_0}{Q} = \frac{1}{R_2 C_1}, \quad \omega_0 = \frac{1}{R_3 C_1}, \quad \omega_0 = \frac{1}{R_4 C_2}, \quad R_5 = R_6$$

(5.3)

Any circuit with the same structure of Figure 5.5 and accomplishing the previous set of equations will be Biquad filter.

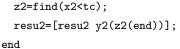

#### 5.2.2. Circuit Under Test Design

In order to generalize the results and understand the influence of each component on the different Biquad filter parameters, the structure of Figure 5.5 has been analysed without any restrictions on the components.

With a bit of algebra can be shown that the transfer function that steers the behaviour of Figure 5.5 circuit in the frequency domain is,

$$H(s) = \frac{-\frac{R_3}{R_1}}{1 + s(1 + sR_2C_1)R_4C_2\frac{R_3R_5}{R_2R_6}}$$

(5.4)

The denominator of the previous equation can be written in the form of  $as^2 + bs + 1$  and identifying the polynomial coefficients, yield  $a = \frac{R_3R_4R_5}{R_6}C_1C_2$  and  $b = \frac{R_3R_4R_5}{R_2R_6}C_2$ . For a filter with a denominator in the polynomial form presented earlier, its characteristic parameters are  $\omega_0 = \frac{1}{\sqrt{a}}$  and  $Q = \frac{\sqrt{a}}{b}$ . In the case of the filter being studied, these parameters are,

$$A_{\rm DC} = -\frac{R_3}{R_1}, \quad \omega_0 = \sqrt{\frac{R_6}{R_3 R_4 R_5 C_1 C_2}}, \quad Q = R_2 \sqrt{\frac{R_6 C_1}{R_3 R_4 R_5 C_2}}$$

(5.5)

With the aim of high performance and low distorsion and low noise in the signal levels, good quality operational amplifiers have been chosed. The Texas Instruments TLC2272 is a CMOS opamp with a typical offset voltage of 300 mV, input bias current as low as 1 pA, input impedance of about  $10^{12} \Omega$ , a high slew rate of 3.6  $\frac{V}{\mu s}$  and a CMRR and PSRR arround 75 and 90 dB respectively is the chosen solution.

In order to construct the filter, two dual TLC2272 have been used. Because of the dispose of four operational amplifiers, and extra one has been added at the end stage of the design as can be seen in the schematic in appendix I.

Accordingly to the previously presented equations, the components have been set to those presented in Table 5.1. All resistors (and potentiometers) values are in  $k\Omega$  and capacitor values in nF.

| $R_1$ | $R_2$ | $P_2$ | $R_3$ | $R_4$ | $R_5$ | $R_6$ | $P_6$ | $R_7$ | $R_8$ | $P_8$ | $C_1$ | $C_2$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 22    | 4.7   | 5     | 22    | 22    | 22    | 22    | 50    | 22    | 20    | 5     | 1     | 1     |

Table 5.1: Components values. Resistors in  $k\Omega$  and capacitors in nF.

The components have been calculated to allow the proper adejustment of the CUT parameters and to allow the inclusion of defects in the natural frequency of the filter. The potentiometers allow to achieve a  $\pm 20\%$  of variation in the characteristic frequency of the filter from its nominal value of 10 kHz.

There is one experimental operation handicap in the use of such Biquad filter. Filter parameters values are function of different components, so by varying one potentiometer, not only the center frequancy os varied but also the quality factor, so it is mandatory for each defect to setup the filter properly.

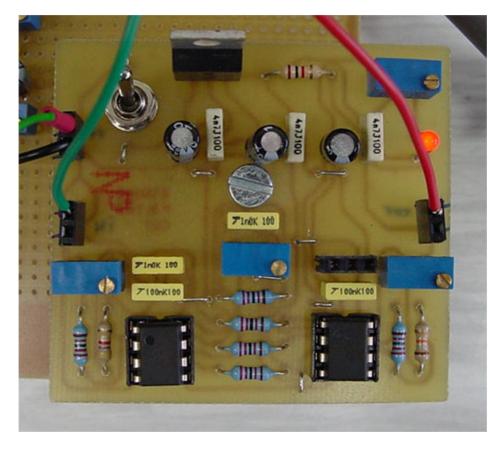

The filter has been implemented in one sided copper PCB using OrCAD Layout software. The resulting layout can be checked in Figure 5.6. The routed process has been automatically in 12 mils tracks in width. The layout design includes a 5 V regulator as a power supply and connectors for input and output signals. Also, has been included a connector for allowing the user to use diodes at the output in order to provent over voltages to be applied directly to the chip.

Figure 5.6: Biquad filter layout designed with OrCAD Layout.

In Figure 5.7 can be appreciated the resulting PCB. The fabrication technique has not been as laboured as test bench board since it has been homemade manufactured. The process consists on applying toner in order to define tracks and pads. Then an acid solution is applied

and after rinsing and removing the sticked toner, the PCB is finished. The method is only suitable for simple PCB (single sided and a few components).

Figure 5.7: Photograph of the fabricated PCB for the circuit under test. It is a tunable low-pass Biquad filter. Input and output signal wires can be checked at the picture.

## Chapter 6

# **Experimental Results**

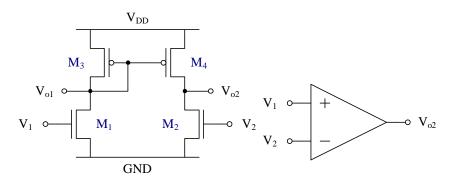

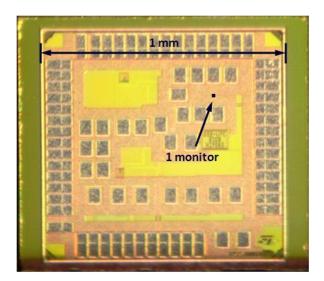

Once the chip has arrived from foundry (run S65C8\_6), it has been tested in order to check its behaviour and performance. In Figure 6.1 can be seen an augmented photograph of the fabricated die using a bulk CMOS process. It has  $1 \times 1 \text{ mm}^2$  of area and lodges many research projects from the different Department interests areas.

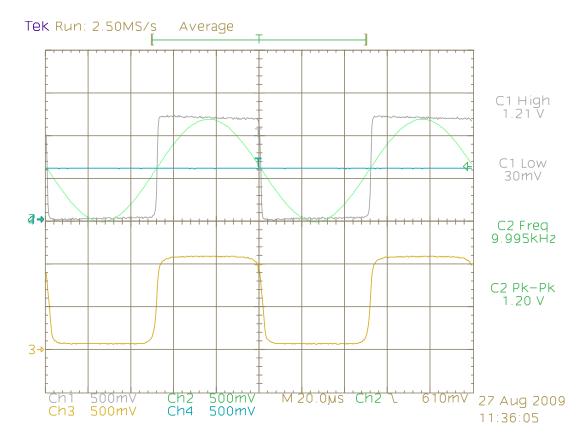

The first test that has been applied to the circuit consists in checking if it is behaving like a nonlinear comparator. For this purpose, different input signals has been considered and different control DC voltages have been tuned. This allows a good coverage of the XY plane tesselation. In Figure 6.3 can be appreciated the transient response of the comparator to an input sinusoid and a constant reference.

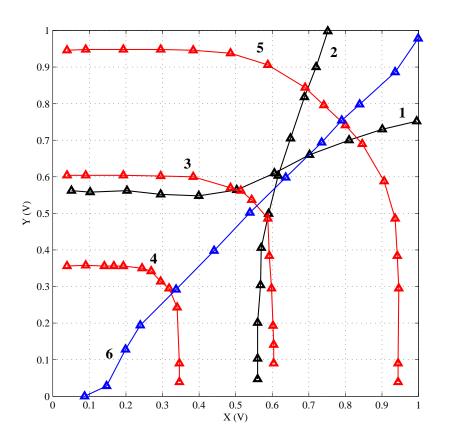

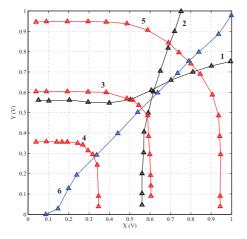

Once the functional behaviour of the second stage circuit is tested, the switching curve generation in the XY plane is studied. In order to obtain such results, a quasi-static transient analysis has been applied considering a ramp input for one of the axis while maintaining the other to a constant DC level. The trip point of the digital output determines uniquely each point and shape of the switching curves. With the aid of a voltmeter and a function generator, the observed switching curves can be seen in Figure 6.4. The shape of the lines match the theoretically and simulated predicted, within the technology variability specifications. The configuration parameters for each considered curve are those appearing in Table 6.1

A complete check of the proposed method with the case example of the Biquad filter has been performed. The CUT circuit has been properly tuned for different  $f_0$  shifts, which

Figure 6.1: Photograph of the die of the fabricated chip. The photograph marks the area occupied by a single monitor.

Figure 6.2: Detail of the IC socket (right) and the encapsulated chip (left).

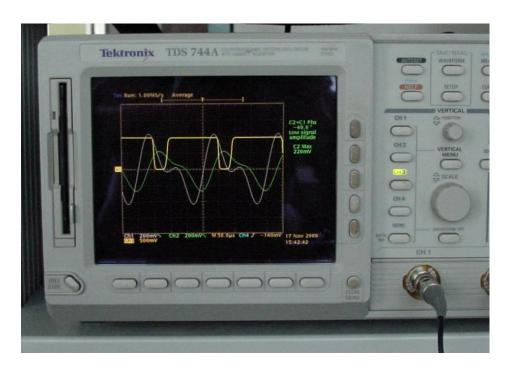

response has been composed with the monitor circuit. This way, different signatures, for each switching curve, have been obtained. In Figure 6.5, the multitone input signal and its low-pass filter response can be seen, as well as the monitor circuit periodic digital code. In Figure 6.6, the resulting Lissajous composition of the input multitone excitation and the CUT response can be appreciated.

Figure 6.3: Experimental transient switching assuring the corrent performance of the comparator module. Can be appreciated the one stage output and the one corresponding to the trimodular architecture.

|   | Т    |      | or width<br>m)<br>80 nm) | ns   | Applied input voltages (V) |        |        |        |  |

|---|------|------|--------------------------|------|----------------------------|--------|--------|--------|--|

|   | M1   | M2   | M3                       | M4   | $V_1$                      | $V_2$  | $V_3$  | $V_4$  |  |

| 1 | 3000 | 600  | 600                      | 3000 | Y axis                     | 0.2    | X axis | 0.6    |  |

| 2 | 3000 | 600  | 600                      | 3000 | 0.6                        | Y axis | 0.2    | X axis |  |

| 3 | 1800 | 1800 | 1800                     | 1800 | Y axis                     | X axis | 0.55   | 0.55   |  |

| 4 | 1800 | 1800 | 1800                     | 1800 | Y axis                     | X axis | 0.3    | 0.3    |  |

| 5 | 1800 | 1800 | 1800                     | 1800 | Y axis                     | X axis | 0.75   | 0.75   |  |

| 6 | 1800 | 1800 | 1800                     | 1800 | Y axis                     | 0      | X axis | 0      |  |

Table 6.1: Input transistor dimensions and applied voltages for the curves depicted in Figure 6.4.

With the aid of the developed software tool, the difference with the golden signature has been computed for all the applied  $f_0$  deviations. The obtained metric values are shown

Figure 6.4: Experimental switching curves.

in Figure 6.7. With this mapping, any defective (only  $f_0$  shifts) circuit can be diagnosed with the unique information of the resulting NDF factor.

As a case examples, three random  $f_o$  shifts (within the studied range of -20% to +20%) have been applied to the CUT in order to compute their digital signature. With the aid of the metric and the mapping, the results of Table 6.2 are obtained. As can be seen, the predicted  $f_0$  shifts are quite similar to the real ones, what validates the proposed method.

|           | CUT defect (%) | NDF   | Predicted defect (%) |

|-----------|----------------|-------|----------------------|

| Example 1 | -12            | 0.096 | -11.9                |

| Example 2 | +1             | 0.010 | 0.89                 |

| Example 3 | +18            | 0.88  | +18.4                |

Table 6.2: CUT experimental results on the diagnosis procedure.

Figure 6.5: Transient response of the monitor circuit to a multitone input. Fundamental frequency is 10 kHz.

Figure 6.6: Shot of the oscilloscope screen composing the multitone input signal and the resulting from the Biquad low-pass filter. The resulting shape matches with the previously calculated one.

Figure 6.7: Mapping between the amount of defect in the Biquad filter characteristic frequency and the NDF factor resulting from golden-defective metric comparison.

## Chapter 7

# Conclusions and Future Work Outlines

A CMOS 65 nm monitor circuit has been presented and analysed. The monitor circuit is a two stage design. The former stage compares the signals and provides the switching curve tessellation. The latter is a high gain stage that digitises the differential output from the first stage in order to perform the codification for each XY plane zone. Both stages analysis include DC large signal and small signal study. For the last, a delay model has been developed and checked against simulation and experimental results.

The theoretical switching curves generated by the first stage have been achieved by the use of the fitted Unified MOSFET Model to ST-Microelectronics 65 nm technology. The fitting methodology is the well known linear least squares method generalized to nonlinear functions via first order Taylor approximation. DC and transient simulations results, PVT variations have been also studied using Monte Carlo simulations and the developed model considering Gaussian parameter distribution. Both studies (simulation and theoretical) yield similar results of an average of 60 mV of  $6\sigma$  spread on switching curves.

The CMOS monitor circuit has been designed in ST-Microelectronics 65 nm technology by the use of common centroid analog design techniques in order to avoid (or at least minimize) mismatch effects. The layout has been included in a multiproject chip for fabrication.

A novel digital signature comparison and diagnosis method has been also presented.

The method takes advantage of the zone codification criteria which makes that neighbouring zones to be at Hamming-1. The discrepancy criterion is performed via the so defined Normalized Discrepancy Factor (NDF) as the average Hamming distance between the golden and the observed signatures over a period. Software simulations allow to determine the NDF factor as a function of the amount of defect allowing this way the diagnosis of a CUT. The mapping between NDF and the percentage of defect is a non one-to-one relation what makes necessary a statistical data clustering process using the fact that differences vectors lay in separately regions of the hyperspace.

In order to avoid the tedious statistical scattering process a new metric has been introduced. Its definition is similar to he former but uses two NDF, one for positive differences and one for negative differences. With the latter metric definition, the mapping of the amount of defect and the two NDF factors is performed in a straight forward way if the set of possible defects has been simulated.

The CUT diagnosis method shows high reliability and simple software implementation allowing to be directly applicable to any pair of signatures comparison in which Hamming distance makes sense of discrepancy. Experimental results have been presented showing that the developed method works as expected.

As a future work, a quantification of performance with noisy signal would be desirable. The method should consider switching bands and not thin curves. Under this assumption, the mapping between the NDF factor and the amount of defect will become into a statistical distribution function.

Also, a complete implementation of the method would be desirable, that is, not only the monitor circuit but also the CUT and the digital processing of signatures. This would require more silicon area but would be adequate in order to assess the reliability of the method under real circumstances.

More research in the method of generating the digital signatures would be a good starting point in order to go further in XY zoning methods. In the current project, two different methods have been presented: one for generating the digital signatures (XY plane tessellation) and one to perform the digital processing of the generated sequences. Both methods could be improved and tested experimentally over many fabricated circuits.

# Agradecimientos

En primer lugar, quisiera manifestar mi agradecimiento hacia Joan Figueras Pàmies, catedrático del Departamento de Ingeniería Electrónica (UPC) y director del presente proyecto. Su confianza, experiencia y sus siempre acertados comentarios me han guiado y ayudado en todo momento. Me ha brindado la oportunidad de trabajar, no solamente en mi proyecto de final de carrera bajo su dirección, sino también la de integrarme en su grupo de investigación y publicar y presentar los resultados en congresos especializados.