Escola d'Enginyeria de Telecomunicació i Aeroespacial de Castelldefels

UNIVERSITAT POLITÈCNICA DE CATALUNYA

# **MASTER THESIS**

TITLE: Programmable-System-on-Chip-based data acquisition system for educational purposes

MASTER DEGREE: Master in Science in Telecommunication Engineering & Management

**AUTHOR: Fernando Manzano Rubio**

**DIRECTOR: Ernesto Serrano Finetti**

DATE: April 23 th 2012

**Título:** Programmable-System-on-Chip-based data acquisition system for educational purposes

Autor: Fernando Manzano Rubio

Director: Ernesto Serrano Finetti

Fecha: 23 de abril de 2012

#### Resumen

El objetivo del proyecto es desarrollar un sistema DAS con fines docentes basándose en un PSoC DVK. El sistema está orientado principalmente a ser un soporte para desarrollar conocimientos básicos sobre la adquisición de señales, así como una herramienta para llevar a cabo medidas sencillas.

Para ello se ha implementado una parte hardware y una parte software. El hardware consiste en el PSoC DVK, el cual tiene las funciones de adquirir y generar señales AC y DC, mostrar información sobre la función seleccionada y sobre la señal adquirida mediante un display y transmitir las muestras adquiridas a través de una comunicación RS-232. El software permite la interacción con el PSoC así como la visualización de las muestras adquiridas tanto en función del tiempo como en un histograma.

El sistema ofrece la capacidad de seleccionar el tipo de ADC entre integrador, SAR y doble integrador; así como varias resoluciones y tasas de muestreo. Esto permite disponer de varias configuraciones, con el fin de estudiar algunas características del ámbito de la adquisición de señales como por ejemplo la capacidad del integrador para el rechazo de interferencias en comparación con el SAR y el testeo de circuitos analógicos mediante el doble integrador. Además, el sistema dispone de un DAC para la generación de señales AC y DC con amplitudes y frecuencias seleccionables, como fuente de señal para el testeo de los circuitos analógicos o el estudio de los ADCs.

Finalmente, el sistema permite seleccionar el número de muestras a adquirir entre varios tamaños predefinidos para poder observar con más o menos detalle la representación temporal de la señal, así como una opción de escalar la entrada para aprovechar la resolución del ADC en señales de baja amplitud. **Title:** Programmable-System-on-Chip-based data acquisition system for educational purposes

Author: Fernando Manzano Rubio

Director: Ernesto Serrano Finetti

Date: April, 23 th 2012

#### Overview

The project aims to implement a PSoC DVK based DAS system learning resource. The idea is to provide a way to develop signal acquiring basic knowledge, as well as a tool to implement simple measures.

In order to do it, hardware and software have been implemented. Hardware consists of PSoC DVK, which has the functions of AC and DC signal acquiring and generating, showing information about the selected function and the acquired signal through a display, and transmitting the acquired samples through the RS-232 communication. Software allows PSoC interacting and showing the acquired samples over the time and in a histogram.

The system provides the capability for selecting the ADC type between an integrating, a SAR and a dual integrating. Also, different resolutions and sample rates can be selected. This allows having several configurations in order to study some signal acquiring features, such as the interference rejection capability of the integrating ADC compared to the SAR and the analog circuit response, or to study each ADC type signal acquiring.

Finally, the system allows selecting the number of samples to be acquired between some preset quantities. It allows showing a detailed temporal representation of the samples acquired. Also, the input can be scaled in order to profit the ADC resolution for small amplitude signals.

# ACKNOWLEDGEMENTS

I would like to express my gratitude to my tutor Ernesto Serrano, whose expertise, understanding and time invested had helped me in all the time research for and writing of this project.

I must also acknowledge my family for the support they have provided me during the project development and the encouragement to going on in the hard moments.

# TABLE OF CONTENTS

| ACRO  | DNYN   | /IS LIST 1                                     |

|-------|--------|------------------------------------------------|

| 1. In | ntrodu | iction2                                        |

| 1.1   | Ot     | ojectives                                      |

| 1.2   | DA     | AS                                             |

| 1.3   | PS     | SoC 5                                          |

| 1.    | .3.1   | Why use a PSoC?5                               |

| 1.    | .3.2   | PSoC architecture7                             |

| 1.    | .3.3   | Technical specifications of resources needed12 |

| 1.    | .3.4   | Dynamic Reconfiguration 15                     |

| 1.    | .3.5   | PSoC DVK 15                                    |

| 2. D  | esigr  | and implementation of a PSoC-based DAS system  |

| 2.1   | Fu     | nctional description17                         |

| 2.2   | Gl     | obal resources                                 |

| 2.3   | RS     | S232 transmission 19                           |

| 2.4   | LC     | 20                                             |

| 2.5   | AD     | DC 21                                          |

| 2.    | .5.1   | PGA                                            |

| 2.    | .5.2   | SAR6                                           |

| 2.    | .5.3   | ADCINCVR                                       |

| 2.    | .5.4   | DUALADC                                        |

| 2.    | .5.5   | How the ADCs sample rates are obtained         |

| 2.    | .5.6   | ADCINCVR frequency rejection 27                |

| 2.6   | Te     | est of linear circuits                         |

| 2.    | .6.1   | How the DAC generates the signals              |

| 2.7   | PS     | SoC dynamic reconfiguration 31                 |

| 2.8   | De     | etected PSoC limitations                       |

| 3. U  | ser ir | nterface                                       |

| 3.1   | Fu     | nctional description                           |

| 3.2   | Im     | plementation                                   |

| 4. Exp | perimental results                      | 38 |

|--------|-----------------------------------------|----|

| 4.1    | Test of different ADC features          | 38 |

| 4.2    | Interference rejection                  | 40 |

| 4.3    | Test of DAC signal generation           | 42 |

| 4.4    | ADC and DAC working together            | 43 |

| 5. Cor | nclusions                               | 46 |

| BIBLIO | GRAPHY                                  | 47 |

| ANNEX  | A. HOW ADCINCVR MAKES THE CONVERSION    | 48 |

| ANNEX  | B. DATA FORMAT USED BY THE USER MODULES | 49 |

| ANNEX  | C. USER MODULES LIBRARY FUNCTIONS USED  | 50 |

| ANNEX  | D. TEST OF DAC GENERATION               | 53 |

| ANNEX  | E. PSoC AND USER INTERFACE SOURCE CODES | 56 |

# **ACRONYMS LIST**

ADC: Analog to Digital Converter. AC: Alternating Current. API: Application Programming Interface. **CPU: Central Processing Unit.** CRC: Cyclic Redundancy Check. DAC: Digital to Analog Converter. DAQ: Data acQuisition. DAS: Data Acquisition System. DC: Direct Current. DNL: Differential Non-Linearity. DTMF: Dual-Tone Multi-Frequency. DVK: DeVelopment Kit. EEPROM: Electrically Erasable Programmable Read-Only Memory. ENOB: Effective Number Of Bits. FSR: Full-Scale Range. GPIO: General Purpose Input/Output. I2C: Inter-Integrated circuit Communication. INL: Integral Non-Linearity. IO: Input/Output. IRDA: Infrared Data Association. ISSP: In-System Serial Programming. LCD: Liquid Cristal Display. LED: Light-Emitting Diode. LSB: Least Significant Bit. MCU: Micro-Controlling Unit. MIPS: Million Instructions Per Second. PGA: Programmable Gain Amplifier. PSRR: Power Supply Rejection Ratio. PRS: Pseudo-Random Sequence. PWM: Pulse-Width Modulation. RAM: Random-Access Memory. RMS: Root Mean Square. ROM: Read-Only Memory. RS232: Recommended Standard 232. SAR: Successive Approximation Register. SINAD: Signal to Noise And Distortion ratio. SPI: Serial Peripheral Interface. SQNR: Signal to Quantization Noise Ratio. SRAM: Static Random-Access Memory. UART: Universal Asynchronous Receiver Transmitter.

# 1. INTRODUCTION

# 1.1 Objectives

The main objective of this project is to implement a DAS learning resource based on a PSoC DVK for a wide variety of engineering students, from those closely related to electronic systems like telecommunications to those who need to understand the basic features of signal acquisition but only as a necessary tool to perform measurements. This learning resource will cover many basic features of a DAS such as ADC resolution and sampling rates, aliasing, particular characteristics of different ADC types, DAC AC-DC signal generation, data logging capability, noise and input/output characterization. Also, in this study the main PSoC limitations referring to dynamic reconfiguration or system resources will be assessed.

Finally, a user interface will be developed in order to interact with the PSoC. It will allow the configuration and running of the PSoC to work and test the previously mentioned DAS features.

# 1.2 DAS

In some areas, data of interest is present in the real world in a difficult manner to treat it. It is present as physical signals that, because of its nature, can be in a great quantity, with fast variations or small dimensions in order to appreciate the information they can give us.

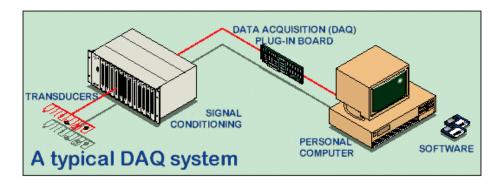

A DAS is a system designed to acquire these signals from the real world to a device. The main objective of this system is to measure, process or store these signals. Typically, the DAS needs some other elements to do it. These elements can be seen as stages, which everyone has a concrete task in the acquisition of the signal. **Fig. 1.1** shows the common stages in a DAS.

Fig. 1.1 A typical DAS system.<sup>1</sup>

Usually, the goal of a DAS is to acquire signals coming from one or more sensors which are used to get the real signal and to convert it to an electrical one, normally expressed as a voltage signal. Sensors can be classified in a great number of groups, depending on the way they sense the signal and the kind of output they provide. Alternatively, a DAS might be used together with well-known signals to study input/output characteristics of a certain electronic device or circuit.

Whatever its source, the signals will be converted into digital codes by an ADC which is the key component of the DAS. The signal is sampled and quantified and a binary value is assigned to each signal level, which represents the analog value in the digital world. This sampling is triggered by the DAS main clock at a periodic rate. So, the main characteristics of the DAS depend on the basic ADC performance parameters: the resolution, the full scale voltage and the sampling rate.

The resolution, determined by the number of bits (N) of the ADC, gives the number of levels that the analog signal can be quantified into. Therefore, the number of bits corresponds to the size of the digital code.

The voltage reference is a voltage in the system that determines the FSR and the dynamic range of the ADC, which is defined as the difference between the maximum and the minimum voltages that can be detected at the input. This one, altogether to the resolution, gives the minimum voltage variation that the system can detect in the analog signal at the input, named LSB and corresponds to:

$$1LSB = \frac{FSR}{2^N}$$

(1.1)

<sup>&</sup>lt;sup>1</sup> Source: <u>http://www.kostic.niu.edu/DAQ-LabVIEW.html</u>

From this parameter, another aspect of the DAS can be obtained, the quantization error  $(e_q)$ , expressed as:

$$e_q = \frac{1}{2} LSB \tag{1.2}$$

This error is the uncertainty between the levels that can be quantified by the ADC. It is usually regarded as noise (quantization noise) and therefore, its relation with the signal at the input can be calculated as:

$$SQNR = 6,02 \cdot N + 1,76$$

(1.3)

Also, if important levels of noise or distortion are present at the ADC input, some bits can be unavailable to represent the signal because they are masked. So, another parameter used to characterize the system, which also considers the quantization noise, is the ENOB. It specifies the number of bits in the digital signal above the noise floor and it is calculated as:

$$ENOB = \frac{SINAD - 1,76}{6,02} \tag{1.4}$$

Where the SINAD is a parameter that shows the relation between the signal and the noise and distortion present.

The sampling rate is the rate at which the quantization of the analog signal is done. In order to represent correctly the real signal in the digital world, it is mandatory to be greater than the double of the analog signal bandwidth.

Apart from this, the benefits of an ADC depend on the type of ADC. The most common are the Flash ADC, the SAR, the integrating ADC and the Sigma-Delta. The main difference between them is the way to implement the conversion, achieving different performance.

Another important step in the process of signal acquisition is signal conditioning, which adapts the electrical signal coming from the sensor to the DAS input to match dynamic range, offset, common mode and bandwidth to mention some of the key performance parameters. This stage is named the Analog Front End and it is previous to the DAS input. This adaptation is necessary to obtain the maximum quality in the conversion.

Filtering is done to attenuate noise and other unwanted signals in order to keep the noise floor as close as possible to keep the expected DAS resolution while also avoiding aliasing effects.

Amplifying or attenuating allows the level of the signal match the DAS dynamic range. This is usually done to take full profit of the number of bits offered by the DAS. For example, if only half the full scale voltage is used then the effective resolution will be one bit less than expected.

Offset shifts the average level of signal to match the maximum and minimum values accepted by the DAS input. For example, a signal might swing between -2 to 3 V while the DAS input might only accept values from 0 to 5 V. It is clear that a shift of 2 V is necessary for the signal to be accurately sampled.

Multiplexing the signal is a secondary aspect of adaptation that depends on the quantity of signals to acquire. It allows the DAS to acquire several signals in parallel.

Once the signal is adapted to the DAS input, it is converted to digital and is finally transferred to the final device. This device normally is referred to some kind of computer with powerful software that shows this data and allows processing it if needed in order to measure and study some processes. Also, more concretely systems can be used to store data for future manipulations.

## 1.3 PSoC

This section will explain some features about the PSoC, such as its description, the resources needed to implement the project, the Dynamic Reconfiguration and the DVK.

## 1.3.1 Why use a PSoC?

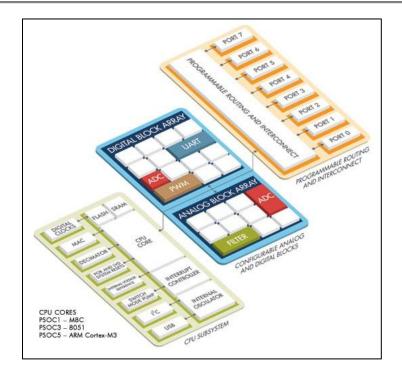

PSoC stands for Programmable System on Chip, and it is a variety of the Cypress programmable microcontrollers' family. It has a core, a configurable system integrated which includes mixed-signal arrays of configurable analog and digital blocks, and a programmable routing and interconnect. **Fig. 1.2** shows these parts.

Fig. 1.2 The PSoC main parts.<sup>2</sup>

These configurable blocks can be programmed as peripherals to perform a wide variety of functions, and then they can be interconnected to perform a specific task. Between these functions there are ADCs, PGAs, filters, DACs, counters or UART communication.

Furthermore, PSoC allows to create several configurations for different tasks, and to switch between them in real time. This characteristic, called Dynamic Reconfiguration, gives to the PSoC the main difference from other microcontrollers.

PSoC is programmed by a powerful software provided by the manufacturer, PSoC Designer. It has a graphic interface to configure the analog and digital blocks with user modules, which represents the peripherals such as ADC, PGA, DAC, etc. and their parameters. Also, parameters of the entire PSoC such as clocks, reference voltages, power, etc. and the device pins can be set through the software. Apart from this, the software allows to program the PSoC through C++ or assembler code. All user modules parameters and functions can be accessed through code, in order to achieve a more complexity configuration. To allow it, the manufacturer has implemented a series of libraries for each user module, which provides an API to configure them.

<sup>&</sup>lt;sup>2</sup> Source: <u>http://www.cypress.com</u>

Therefore, versatility and capability to switch between different tasks are the strengths of these microcontrollers. Aspects that make them a good choice to develop the functionality presented in this project.

# **1.3.2 PSoC architecture**

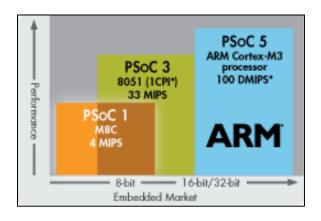

There are three families of PSoC: PSoC 1, PSoC 3 and PSoC 5. The principal difference is the MCU that feeds the core, which increases its performance in terms of clock rate and therefore the calculation rate. Also, the instruction length is incremented from 8 to 16 and 32 bits. **Fig. 1.3** shows a comparative between them. In this project we will work with a PSoC 1 because of its availability and technical support.

Fig. 1.3 PSoC family cores.<sup>3</sup>

Then, depending on the PSoC model, the digital and analog systems may have 16, 8, or 4 digital blocks and 12, 6, 4 analog blocks. Also, the number of pins and the memories size may differ from each other categories. To implement the project, a CY8C29x66 model of PSoC 1 has been chosen, which is powered by a M8C MCU of up to 24 MHz and 4 MIPS and has the capability of Dynamic Reconfiguration.

As mentioned earlier in this section for general PSoCs, PSoC 1 devices are formed by a core, a configurable system based on analog and digital blocks, and a programmable routing and interconnect.

The most important elements included in the core are CPU, memory, clocks, and configurable GPIOs. Memory refers to RAM memory and Flash memory to locate

<sup>&</sup>lt;sup>3</sup> Source: <u>http://www.cypress.com</u>

the firmware. PSoC uses 16 KB of flash for program storage, 256 bytes of SRAM for data storage, and up to 2 KB of EEPROM emulated using the flash.

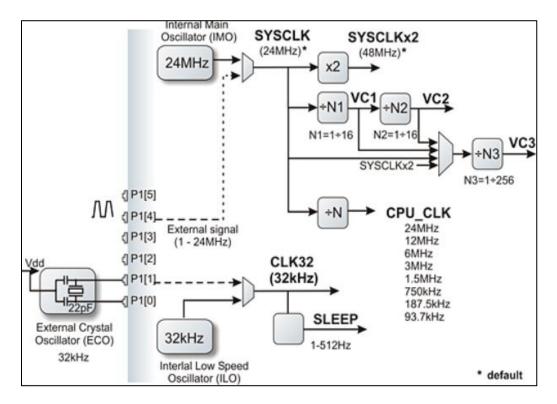

The clocks are used to synchronize the internal clock of the analog and the digital blocks. They are part of the PSoC global resources. PSoC has a wide variety of clock sources in order to increase the flexibility. They provide the following clocking signals:

- SYSCLK: Is the system main reference clocking signal, it can be created by the Internal Main Oscillator (IMO) which runs at 24 MHz or and external clock (EXTCLK).

- SYSCLKx2: Twice the frequency of SYSCLK.

- CPUCLK: Determines the speed of the CPU. It is created by SYSCLK divided down to one of eight possible frequencies.

- VC1, VC2 and VC3: Are Variable Clocks (VC), related between them, the SYSCLK and the SYSCLKx2 through a divisor.

- CLK32K: Can be created by the Internal Low Speed Oscillator or the External Crystal Oscillator (ECO).

- CLK24M: Is the internally generated 24 MHz clock by the IMO.

Fig. 1.4 shows the relationship between the different PSoC clocks.

**Fig. 1.4** Source clock PSoC internal distribution.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> Source: <u>http://www.psoc-chile.es.tl/Clock-y-Frecuenias.htm</u>

The GPIO blocks provide the interface between the CPU and the outside world. Each GPIO block is formed by different I/O pins, which have several drive modes, as well as and interrupt capabilities. They can be used for the following types of I/O:

- Digital I/O (used by the CPU to send out and get into information)

- Global I/O (digital PSoC block input and output)

- Analog I/O (analog PSoC block input and output)

The programmable routing and interconnect allows any connection between the configurable system and the GPIO. It is done through a series of global buses that can route any signal to any pin. The buses also allow signal multiplexing and performing logic operations.

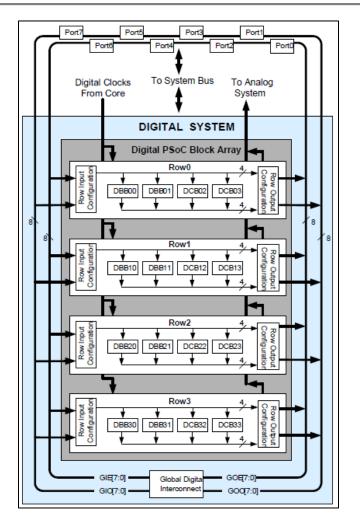

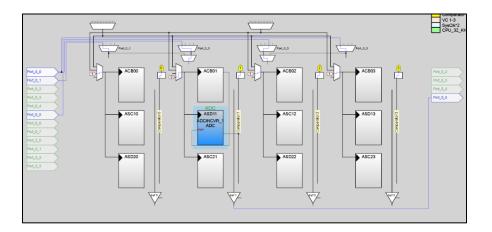

The digital part of the CY8C29x66 category configurable system is composed by 16 digital blocks provided in rows of four, where each row has two blocks for communication purposes (DCB) and two blocks for basic purposes (DBB). **Fig. 1.5** shows the digital system distribution.

Fig. 1.5 PSoC digital system distribution.<sup>5</sup>

These blocks can be used alone or combined with other blocks to form 8-, 16-, 24-, and 32-bit user modules. The user modules included are:

- PWMs (8- to 32-bit)

- PWMs with dead band (8- to 32-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit)

- UART 8-bit with selectable parity (up to 2)

- SPI slave and master (up to 2)

- I2C slave and multi-master (one available as a system resource)

- CRC generator (8- to 32-bit)

- IrDA (up to 2)

- PRS generators (8- to 32-bit)

<sup>&</sup>lt;sup>5</sup> Source: Cypress CY8C29x66 datasheet.

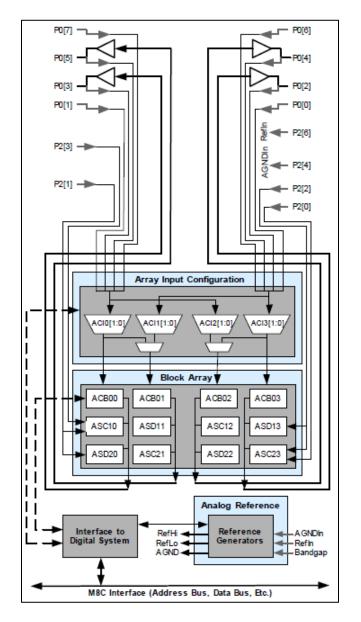

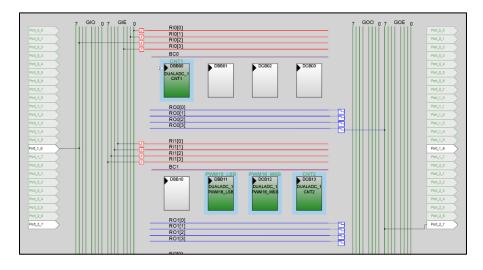

The analog part of the CY8C29x66 category configurable system is composed by 12 analog blocks provided in columns of three, where each column includes one continuous time (CT) and two switched capacitor (SC) blocks. **Fig. 1.6** shows the analog system distribution.

Fig. 1.6 PSoC analog system distribution.<sup>6</sup>

<sup>&</sup>lt;sup>6</sup> Source: Cypress CY8C29x66 datasheet.

These blocks, each containing an opamp circuit that allows the creation of complex analog signal flows, can be used as a wide variety of peripherals. The user modules that can be configured as these peripherals are:

- ADCs (up to 4, with 6- to 14- bit resolution; selectable as incremental, delta sigma, and SAR)

- Filters (2-, 4-, 6-, and 8-pole band pass, low pass, and notch)

- Amplifiers (up to 4, with selectable gain to 48x)

- Instrumentation amplifiers (up to 2, with selectable gain to 93x)

- Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6-bit to 9-bit resolution)

- Multiplying DACs (up to 4, with 6-bit to 9-bit resolution)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Etc.

Also, a reference voltage and a nominal operation voltage are needed for setting the analog ground and the peak-to-peak voltage limit of the analog system. They are provided by the  $V_{cc}$  and the Ref Mux parameters of the PSoC and also are part of the PSoC global resources together the clocks. The  $V_{cc}$  corresponds to the power supply voltage of the system.

#### **1.3.3 Technical specifications of resources needed**

As explained at the beginning of this chapter, the PSoC peripherals are represented by user modules. These user modules have a series of technical specifications that characterize them. To implement the different system functions some user modules are needed, as well as other resources considered global resources. The user modules needed, as well as their technical specifications, are shown below. They corresponds to a temperature of 25 °C, a system power supply of V<sub>cc</sub> = 5 V and a high power supply for analog blocks.

#### <u>UART</u>

- Asynchronous receiving and transmitting.

- RS-232 serial-data format.

- Burst rates up to 6 Mbps.

- Data frame composed by start, optional parity and stop bits.

- Optional interrupt on receive register full and/or transmit buffer empty.

- Parity, overrun and framing error detection.

#### <u>LCD</u>

- Requires seven I/O pins.

- Allows for printing RAM or ROM strings.

- Allows for printing numbers.

- Allows for displaying horizontal and vertical bar graphs.

#### <u>Counter</u>

- Up to 32-bit resolution.

- Source clock rates up to 48 MHz.

- Automatic reload of period on terminal count.

- Programmable pulse width.

- Selectable continuous counter operation.

- Optional interrupt on compare output or terminal count.

#### <u>DAC</u>

- 6-bit resolution.

- 2's complement, offset binary and sign/magnitude input data formats.

- Up to 250 ksps.

- Output voltage range depending on the system reference voltage.

- DNL of 0,09 LSB, INL of 0,07 LSB.

- Including reference gain error of 3,4 %FSR, excluding reference gain error of 0,45 %FSR.<sup>7</sup>

- Offset voltage of +- 7,5 mV.

- Output noise of 4,6 mV RMS.

#### <u>PGA</u>

- Thirty-three user-programmable gain settings with a maximum gain of 48,0.

- High impedance input.

- Input voltage range depending on the system reference voltage.

- PSRR of 73 dB.

- Slew rate (20% to 80%) of 9,5 V/µs.

- Settling time of 1 µs.

- Noise of 99 nV/√Hz.

#### <u>ADCINCVR</u>

- 7- to 13-bit resolution.

- 2's complement and unsigned output data format.

- Sample rates from 4 to 10 000 sps.

- Input voltage range depending on the system reference voltage.

- SNR of 77 dB.

- DNL of 0,4 LSB, INL of 1,0 LSB.

- Offset error of 9 mV.

- Including reference gain error of 2,0 %FSR, excluding reference gain error of 0,1 %FSR.

## <u>DUALADC</u>

- 7- to 13-bit resolution.

$<sup>^7</sup>$  Cypress condition: reference gain error measured by comparing the external reference to  $V_{\text{RefHigh}}$  and  $V_{\text{RefLow}}$  routed through the test mux and back out to a pin.

- 2's complement and unsigned output data format.

- Sample rates from 4 to 10 000 sps.

- Input voltage range depending on the system reference voltage.

- SNR of 77 dB.

- DNL of 2,0 LSB, INL of 1,0 LSB.

- Offset error of 9 mV.

- Including reference gain error of 3,0 %FSR, excluding reference gain error of 0,1 %FSR.

#### <u>SAR6</u>

- 6-bit resolution.

- 2's complement output data format.

- Internal update rate of 32 to 333 kHz.

- Input voltage range depending on the system reference voltage.

- DNL of 0,25 LSB, INL of 0,75 LSB.

- Offset error of 8 mV.

- Including reference gain error of 1,5 %FSR, excluding reference gain error of 0,4 %FSR.

The global resources needed, as well as their technical specifications are shown below.

#### <u>Clocks</u>

As introduced above in the section Basic explanation of the architecture, PSoC has a wide variety of clock sources in order to increase the flexibility. The clock sources needed for implementing the project are SysClk, VC1, VC2 and VC3.

- SysClk: It can be sourced by the IMO or an external clock (ExtClk pin). The frequencies to be selected from the IMO are 24 MHz and 6 MHz.

- VC1: Is sourced by SysClk. An integer from 1 to 16 divides down the frequency.

- VC2: Is sourced by VC1. An integer from 1 to 16 divides down the frequency.

- VC3: It can be sourced by the VC1, VC2, SysClk or SysClk\*2. An integer from 1 to 256 divides down the frequency.

#### Reference voltages

The reference voltages needed by the user modules are given by the Ref Mux and  $V_{cc}$  global resources parameters. They set the analog ground and the peak-to-peak voltage limits of the analog system.

-  $V_{cc}$ : Is the system supply voltage. It is selectable between 3,3 V and 5 V.

- Ref Mux: Sets the analog ground and the peak-to-peak voltage limits. The options offered are:

- $\circ$  V<sub>dd</sub>/2 +/- BandGap

- $\circ$  V<sub>dd</sub>/2 +/- V<sub>dd</sub>/2

- BandGap +/- BandGap

- 1,6 BandGap +/- 1,6 BandGap

- 2 BandGap +/- BandGap

- 2 BandGap +/- P2[6]

- P2[4] +/- BandGap

- P2[4] +/- P2[6]

#### **1.3.4 Dynamic Reconfiguration**

The Dynamic Reconfiguration is a technique developed by Cypress that allows PSoC 1 devices to reuse analog and digital resources to maximize the functionality. It consists in creating different layers, each of them with the user module configuration that have to work as a system.

The PSoC Designer allows easily the implementation of the Dynamic Reconfiguration by creating these layers in the user interface in a graphical way. These layers are located in the firmware and can be switched between and interacted with them at a firmware API levels. To do it there are some instructions in the code level that allow loading or unloading a concrete layer. Load a layer is referred to make it active and unload a layer is referred to make it inactive.

When the PSoC is started the boot code is executed. It includes loading the base configuration layer. This base layer must be always loaded. The rest of the layers are considered overlays. Apart from the base layer, more than one overlay can be loaded at the same time. So the user modules placed in these layers are always active. The digital and analog blocks used in these layers can't be used in other layers; otherwise they will be overlapped and as a consequence there will appear conflicts.

Global resources as reference voltages or clocks are set by the last loaded layer, so they may be reconfigured to accomplish with the user modules of the current layer. In this case, those resources used by other user modules already active have to be respected so that these user modules can work properly.

The result is a system composed by parallel systems that can be switched on and off at any time. And the blocks used at the same time by different layers can't be overlapped.

## 1.3.5 PSoC DVK

The PSoC DVK provides a common development platform, as well as optional peripherals such as RS-232, LCD, potentiometers and Input Peripherals, to help to prototype and to evaluate applications using a PSoC device. It is used to examine

and explore the peripherals and hardware features that are integrated into the PSoC device. Also, it allows programming the PSoC from the PSoC Designer.

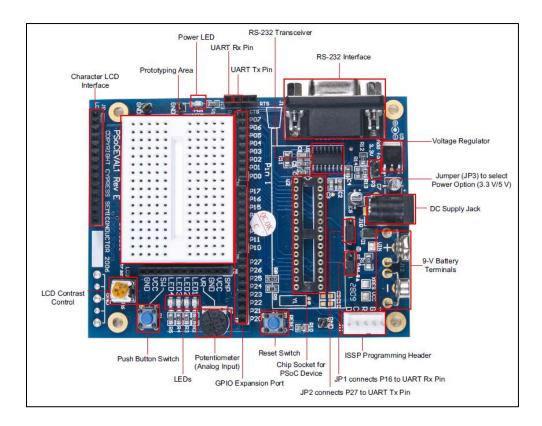

There are many PSoC DVKs, oriented to any PSoC family, which have more or less capabilities and other optional components. To implement this project, the CY3210 PSoCEval1<sup>8</sup> has been selected, which works with the PSoC 1 family. This evaluation kit demonstrates the function of PSoC 1 devices. It connects the device to onboard peripherals such as potentiometers, LEDs, LCD, and RS-232. It also has additional features such as a general prototype area of bread board and an ISSP programming header to program the PSoC through the MiniProg programming unit also included. **Fig. 1.7** shows the PSoCEval1 DVK and its main components.

Fig. 1.7 CY3210 PSoCEval1 DVK.9

<sup>&</sup>lt;sup>8</sup> Web reference: <u>http://www.cypress.com/?rID=2541</u>

<sup>&</sup>lt;sup>9</sup> Source: CY3210-PSoCEVAL1 PSoC 1 Evaluation Kit Guide.

# 2. DESIGN AND IMPLEMENTATION OF A PSOC-BASED DAS SYSTEM

This chapter will explain the system functions as well as each of its modules. Then, a detailed explanation about the design and the implementation of each module will be given.

# 2.1 Functional description

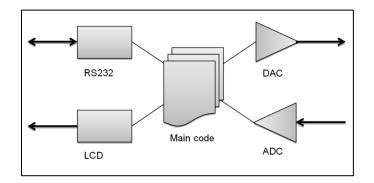

As it has been said in the introduction chapter, this project consists in the implementation of a PSoC-based DAS system for teaching purposes. For this reason the system has the functions of a DAS and also the capability to generate some test signals. These functions are: getting a signal from outside through different types of ADCs, generating test signals through a DAC, showing some basic information about the process by an LCD display and finally providing a way to interact and transmit the data through the RS232 interface of the board.

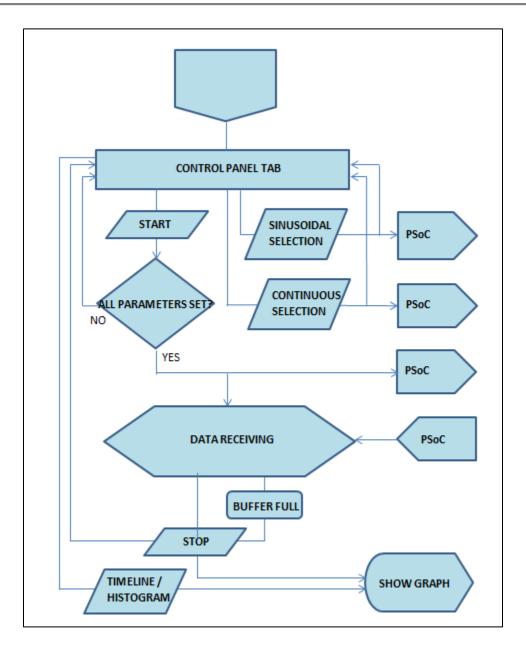

In order to choose one of them, the PSoC have a main code to process all the external user interactions<sup>10</sup>. This code activates the proper layer with the global resources defined and allows setting the desired parameters through the user modules libraries<sup>11</sup>. **Fig. 2.1** shows a diagram of the main code with the different system functions.

Fig. 2.1 System general functions diagram.

The functional description of these functions is explained below.

First, the communication between the user and the system is made through the RS232 interface in the board. In order to achieve that, the UART user module is

<sup>&</sup>lt;sup>10</sup> See the source code in the annex.

<sup>&</sup>lt;sup>11</sup> See the user modules library functions used in the annex.

used in the PSoC. It is the responsible for transmitting the signal information gathered by the PSoC to the RS232 and then outside and of allowing the user to send the proper command for switching between the system functions.

The LCD shows information about the active function and the set parameters. Depending on the function it also shows information about the signal that is being acquired.

The ADCs are the main objective of the project. This part is composed by several ADCs types and configurations in order to compare their results and to study the main aspects of signal acquiring. Resolution and sample rates can be selected, as well as the ADC type between integrator and SAR. These configurations can be switched from outside, and their results are sent out to make the appropriate comparisons. Also this part includes a dual ADC in order to test the response of analog circuits external to the PSoC. In this case, two signals are acquired at the same time by the two ADC present in the dual ADC. In this case the resolution and the sample rate are fixed.

The DAC allows obtaining test signals to do the ADC comparisons by the generation of AC and DC signals. Amplitude and frequency can be set. It provides some autonomy to the system because is not necessary the use of external signal generators.

The main code makes possible to switch between these functions. It depends on the RS232 communication. When a command is received from the user, the code goes to the function called, sets the parameters desired, or loads the proper layer. Also, it is responsible for transmitting the signal information through the RS232.

All functions of the system are provided by the PSoC, through the different user modules loaded. So, the PSoC is the principal process unit in the DVK board, the rest of the board only provides connectivity between PSoC ports as well as inputs and outputs such as the RS232 transceiver, the potentiometer or the LCD display.

The design and implementation of these functions are explained below.

## 2.2 Global resources

As it has been explained before, the most important global resources for the project are the clocks and the reference voltages.

They define the internal clock of the analog and the digital blocks and the reference voltage of the analog system. Consequently, parameters of the user modules such as ADCs sample rates and input ranges, DAC frequency or UART bitrate are also defined.

These global resources are set by the V<sub>cc</sub>, Ref Mux and clocks parameters. V<sub>cc</sub> is set to 5 V. It corresponds to the PSoC power supply, so it is always the same value. Ref Mux is always set to V<sub>dd</sub>/2  $\pm$ V<sub>dd</sub>/2. They give a ground of 2,5 V and an input range of  $\pm$ 2,5 V to the ADCs. Also, it determines the DAC output range to 0 to 5 V. The clocks parameters used are SysClk, VC1, VC2 and VC3. They are taken as follows:

- SysClk is set to 24 MHz. It corresponds to the PSoC CPU clock, so is always the same value.

- VC2 is divided down from VC1, and this is divided down from the SysClk. They are combined in order to obtain the sample rates for the converters. They change for every overlay loaded in order to provide the sample rate desired.

- VC3 can be used only for digital blocks, so it is used as a fixed resource for digital blocks-based user modules that are always active, for example UART and the counter. It is derived directly from the SysClk to be independent from the variable VC1 or VC2 parameters.

# 2.3 RS232 transmission

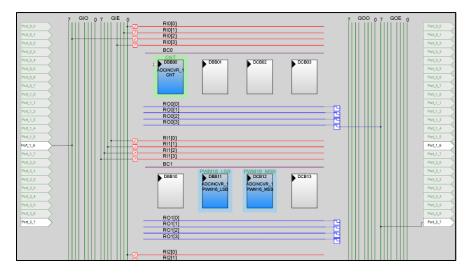

The RS232 transmission is implemented by the UART user module, which needs two communication type digital blocks, one of them for receiving and the other for transmitting. Finally, these blocks are connected to the external pins through the digital interconnect rows.

Fig. 2.2 shows the UART blocks and the way they are connected to the outside.

Fig. 2.2 UART digital blocks.

The UART user module is located in the base layer in order to be active at any moment because it transmits data and listens for a command continuously. Its parameters set are a bit rate of 115 384 bps and none parity; a start bit, a stop bit and 8 data bits are used as default set. The bit rate has been chosen in order to provide enough bandwidth for transmitting the fastest ADC, which is 7 500 samples per second at 7 bits per sample that it corresponds to a 52 500 bps of output. A more accurate bit rate isn't possible as it has discrete values because it is divided down from other clock, it can't be finely adjusted and in addition, it has to match with a preset bit rate is the VC3 set directly from the SysClk. No interrupts are used with the UART user module.

# 2.4 LCD

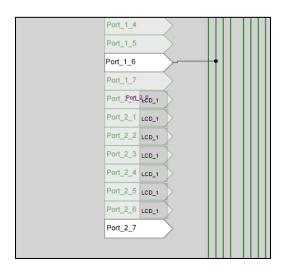

The LCD is represented by the LCD user module, which no needs any digital or analog block to be implemented. The user module only includes the LCD parameters to be set. It allows setting the pin port where the display is connected. **Fig. 2.3** shows the pins used for the LCD display.

Fig. 2.3 Pins used by the LCD user module.

It is located in the base layer in order to be accessible at any moment because is the way to show the PSoC state. The LCD user module doesn't need any interruption and clock signal for running.

<sup>&</sup>lt;sup>12</sup> Windows recognizes the serial port as a COM device with a preset bit rates list. The PSoC bit rate has to match with it.

# 2.5 ADC

The ADC function offers acquiring a signal through two ADC types: SAR and integrating, and testing analog circuits through the dual ADC, composed by two integrating ADC.

The SAR ADC compares the input signal to a voltage level produced by an internal DAC. Depending on if it is higher or lower, the DAC voltage is incremented or decremented and the corresponding bit is added to the digital output. This type of ADC usually has a medium-high resolution and sample rates under other types of ADC. Its strength is its low power consumption and its size.

The integrating ADC uses an integrator to convert an input voltage into its digital representation. The one provided by the PSoC is algorithmically equivalent to the dual-slope ADC architecture. The conversion process of this architecture consists in two phases, the run-up and the run-down. In the run-up phase, the input signal voltage is integrated during a predetermined period of time. In the run-down phase, the input switches to a known reference voltage and a counter measures the period of time that the integrator takes to return a zero value. Finally, the input voltage is calculated from the run-up phase period of time, the reference voltage and the measured run-down phase period. This ADC type can achieve high resolution trading off its speed, and as consequence decreasing its bandwidth. Other advantages are accuracy, a good noise performance and the frequency rejection capability.

The ADC function is implemented by three different user modules: SAR6, ADCINCVR and DUALADC. Any ADC user module has to acquire their signal through a PGA user module of unit gain.

## 2.5.1 PGA

The PGA user module provides the signal to the ADC from outside. It also allows amplifying the input signal by a predetermined selected value of 1, 2 or 8 in order to optimize the ADC resolution. To do it, the Reference parameter is set to  $V_{ss}$  in order to amplify ranges from 0 V to  $V_{dd}$ .

This user module needs a continuous time type analog block to be implemented. It is connected to the analog column multiplexers, which drive the signal from the input pin to the proper block, and to the analog column clock to be synchronized. **Fig. 2.4** shows this user module. As the PGA is common to the all ADCs and it can

be always active, is located in the base layer. No interrupts are needed for running this user module.

Fig. 2.4 PGA analog block.

## 2.5.2 SAR6

The SAR6 user module only needs a switched capacitor type analog block to be implemented. Its source signal is provided by the PGA and the clock signal is provided by the analog column clock. **Fig. 2.5** shows the SAR6 user module.

Fig. 2.5 SAR6 analog block.

This user module is located in an overlay in order to be activated or inactivated when desired. SAR6 has a resolution of 6 bits and a 2's complement value data format predetermined<sup>13</sup>. Sample rate is set to 3 900 samples per second. It is given by the VC2. No interrupts are used to run this user module.

<sup>&</sup>lt;sup>13</sup> See annex: Data format used by the user modules.

#### 2.5.3 ADCINCVR

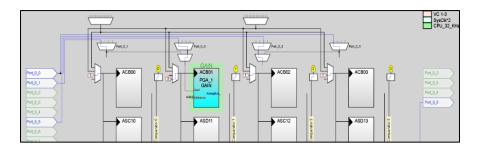

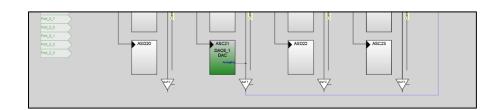

The ADCINCVR needs more than one block to be implemented. On one hand, a switched capacitor analog block is needed for getting the signal from the outside. On the other hand, three digital blocks are needed to obtain the digital value: one for a counter and two to form a 16-bit PWM. The source signal for the analog block is provided by the PGA, and its clock signal is provided by the analog column clock. For the digital blocks, which also need to be synchronized, is done through the counter source clock input. **Fig. 2.6** and **Fig. 2.7** show the ADCINCVR user module.

Fig. 2.6 ADCINVR digital blocks.

Fig. 2.7 ADCINCVR analog block.

The ADCINCVR is located in four overlays in order to be activated or inactivated when desired. These overlays have different configuration. They are explained below. The first overlay provides a selectable resolution of 7, 10, and 13 bits with a sample rate of 6, 50 and 400 samples per second respectively. These resolutions can be selected through the properly function from the user module library. The sample rates change because they depend on the resolution and the analog column clock, which is given by the VC2 clock, fixed to the layer loaded.

The second, third and fourth overlays have the same fixed resolution, set to 7 bits, and only the sample rates change from each other, which are 2 000, 5 000 and 7 400 samples per second respectively. These sample rates are also given by the VC2 clock<sup>14</sup>. The ADCINCVR user module needs that the interruptions are enabled in order to generate the digital value for the current sample. Also, it is needed for detecting the end of the sample conversion<sup>15</sup>. All the four overlays return the sample value in an unsigned data format<sup>16</sup>.

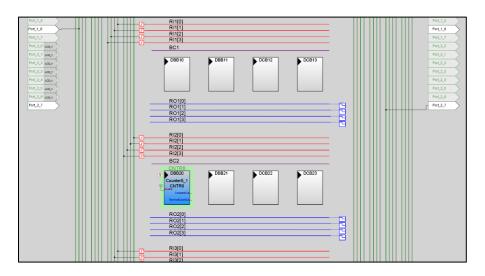

## 2.5.4 DUALADC

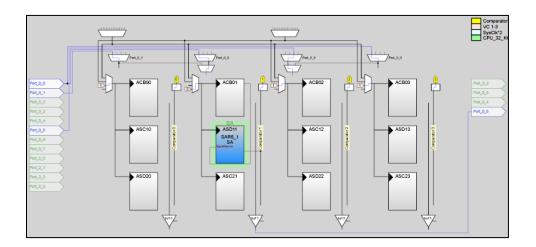

The DUALADC user module consists of two ADCINCVR because it performs two conversions at the same time. It needs two switched capacitor analog blocks and four digital blocks to be implemented. The analog ones in order to acquire the two different signals and the digital ones in order to obtain the two digital values: two for two counters and two more to form the 16-bit PWM.

Each of the two analog blocks must be in a different column and can't share a column with another switch cap block that connects to the comparator bus. They are connected to two different PGA and their clock is provided by the analog column clock. The two counters may be placed in any digital block, but the pulse width modulator has to be placed in any two consecutive digital blocks. They are synchronized through the first counter source clock input. Fig. 2.8 and Fig. 2.9 show the DUALADC user module.

This user module only has a configuration, so is placed in one overlay. It has a fixed resolution of 10 bits and a sample rate of 1 000 samples per second, given by the VC2 clock. The DUALADC user module needs that the interruptions are enabled in order to generate the digital value for the current samples. Also, it is needed for detecting the end of the samples conversion. It returns the sample value in an unsigned data format<sup>17</sup>.

<sup>&</sup>lt;sup>14</sup> The way to change them is explained in this section: How the ADCs sample rates are obtained. <sup>15</sup> See annex: How ADCINCVR makes the conversion.

<sup>&</sup>lt;sup>16</sup> See annex: Data format used by the user modules.

<sup>&</sup>lt;sup>17</sup> See annex: Data format used by the user modules.

Fig. 2.8 DUALADC digital blocks.

Fig. 2.9 DUALADC analog blocks.

## 2.5.5 How the ADCs sample rates are obtained

The ADCs user modules analog block has an internal clock in order to acquire the samples. It needs an external clock signal in order to synchronize the internal clock, as well as any user module implemented by analog blocks. This external clock is provided by the analog column clock, which is obtained from the system main clock SysClk through the different variable clock used for this purpose: VC1 and VC2. So, the sample rate for these peripherals will be given by these clocks.

Apart from this, depending on the ADC type, there are other parameters that influence in the sample rate calculation, they are explained below.

#### <u>ADCINCVR</u>

The ADCINCVR sample rate (SR) is given by the DataClock (DC), the resolution (N) and the CalcTime (CT) parameters, as the equation (2.1) shows.

$$SR = \frac{DC}{2^{N+2} + CT}$$

(2.1)

DataClock is the name for the analog block internal clock, which is actually composed by two clocks,  $\phi_1$  and  $\phi_2^{18}$ , with a frequency of one fourth the analog column clock frequency. The resolution gives the integrate time and the CalcTime defines the time to do the result calculations, which can be selected from a minimum required in order to optimize the sample rate. This minimum value can be calculated as follows in the equation (2.2) and its units are DataClock cycles. **Table 2.1** shows the values used for these parameters in each ADCINCVR.

$$CT \ge \frac{180 \cdot DC}{CPU\_Clock}$$

(2.2)

| User module | SysClk [MHz] | VC1 [Hz]  | DC (VC2) [Hz] | N [bits] | CT <sub>min</sub> | СТ  | SR [sps] |

|-------------|--------------|-----------|---------------|----------|-------------------|-----|----------|

| ADCINCVR_1  | 24           | 1 846 153 | 205 128       | 7        | 1,53              | 2   | 399      |

| ADCINCVR_1  | 24           | 1 846 153 | 205 128       | 10       | 1,53              | 2   | 50       |

| ADCINCVR_1  | 24           | 1 846 153 | 205 128       | 13       | 1,53              | 2   | 6,25     |

| ADCINCVR_2  | 24           | 2 000 000 | 2 000 000     | 7        | 15                | 488 | 2 000    |

| ADCINCVR_3  | 24           | 3 000 000 | 3 000 000     | 7        | 22,5              | 88  | 5 000    |

| ADCINCVR_4  | 24           | 4 000 000 | 4 000 000     | 7        | 30                | 31  | 7 366    |

Table 2.1 Parameters values used for each ADCINCVR.

#### <u>DUALADC</u>

The DUALADC user module is composed by two ADCINCVR analog blocks. By this reason, the sample rate calculation is done as the same way that for the ADCINCVR. The only difference is that the minimum CalcTime needed corresponds to 260 CPU cycles instead of 180 needed by the ADCINCVR. So, the equation is:

$$CT \ge \frac{260 \cdot DC}{CPU\_Clock}$$

(2.3)

<sup>&</sup>lt;sup>18</sup>  $\phi_1$  and  $\phi_2$  are the phase clocks used to acquire and transfer the signal.

Table 2.2 shows the values used for the implementation of this user module.

| User module | SysClk [MHz] | VC1 [Hz]  | DC (VC2) [Hz] | N [bits] | CT <sub>min</sub> | СТ | SR [sps] |

|-------------|--------------|-----------|---------------|----------|-------------------|----|----------|

| DUALADC_1   | 24           | 4 000 000 | 4 000 000     | 10       | 44                | 45 | 966      |

#### <u>SAR6</u>

The SAR6 sample rate is given by the SampleClock. It is the analog block internal clock name; which is actually composed by two clocks,  $\phi_1$  and  $\phi_2^{19}$ , with a frequency of one fourth the analog column clock. On the other hand, the SAR6 needs six times the period of the sample clock to perform the sample total conversion. The equation (2.4) shows the SAR6 Conversion Time calculation.

Conversion Time =

$$6 \cdot \frac{1}{f_{sample clock}} = 6 \cdot 4 \cdot \frac{1}{f_{analog column clock}}$$

(2.4)

Finally, the sample rate corresponds to:

Sample Rate =

$$\frac{f_{sample clock}}{6} = \frac{f_{analog column clock}}{24}$$

(2.5)

So, the values used for the implementation of the SAR6 are 93 750 Hz for the analog column clock and a sample rate of 3 906 samples per second.

#### 2.5.6 ADCINCVR frequency rejection

The ADCINCVR user module is able to reject interferences added to the signal of interest due to its integrating architecture. To reject a frequency, the integration time must be equal to the interference integral cycle that corresponds to its period. It implies that the harmonics will be also rejected. To reject more than one interference and their harmonics the integration time must be an integral cycle of both interferences.

<sup>&</sup>lt;sup>19</sup>  $\phi_1$  and  $\phi_2$  are the phase clocks that control each successive approximation step.

For this project, the first ADCINVR configuration layer has been designed in order to reject the 50 Hz power supply interferences, so the integration time must be equal to 20 ms. This parameter is given by the ADCINCVR DataClock and the resolution (N) as the equation **(2.6)** shows.

$$Integration time = \frac{2^{N+2}}{DataClock}$$

(2.6)

The selected resolution chosen is 10 bits, so the DataClock has to be 204,800 Hz. As this clock signal is given by the discrete parameter VC2, the nearest value achieved is 205 128,205 Hz, so the final integrate time will be 19,968 ms. Then, selecting the proper CalcTime, the ADCINCVR sample rate will be obtained as explained in the previous section.

# 2.6 Test of linear circuits

The system also has a function to generate some signals in order to do the ADC comparisons or to test analog circuits. This function needs two user modules to be implemented: a DAC and a counter. They are placed in a switched capacitor analog block and in a digital block, respectively. The DAC is connected to the analog out bus to output the corresponding signal voltage level, and its clock signal input is connected to the analog column clock. The counter is synchronized through its source clock input. **Fig. 2.10** and **Fig. 2.11** show these two user modules.

Fig. 2.10 Counter digital block.

Fig. 2.11 DAC analog block.

These modules are located in the base layer in order to be available at any moment. The signals implemented are a sinusoidal with three selectable frequencies and a continuous one. Both of them have a  $V_{dd}/4$  to  $V_{dd}$  amplitude, selectable in steps of ¼. A 64-samples lookup table is needed for generating the sinusoidal signal. Every time that the counter arrives to the value of period set it sends to the DAC the next sample from the table and this sets the voltage level corresponding to the sample. The frequency of the sinusoidal signal is 57, 100 and 200 Hz. It is defined by the internal clock of the counter, the period of the lookup table and the period of the counter, which can be selected to obtain the sinusoidal frequency desired<sup>20</sup>.

The ground and the amplitude of the generated signal, either continuous or sinusoidal are given by the reference voltage set for the analog system in the global resources. The internal clock of the counter is sourced by the VC3, and the DAC is sourced by VC2. The DAC user module doesn't need any interruption for running. The counter needs an interruption for generating the sinusoidal signal. The data format for the DAC input is set to offset binary<sup>21</sup>.

## 2.6.1 How the DAC generates the signals

As explained through the report, the DAC6 user module is used to generate continuous and sinusoidal signals. This user module is implemented by an analog block.

It has an internal clock to update the output analog voltage level with the current digital code value. It needs an external clock signal in order to synchronize the internal clock. This external clock is provided by the analog column clock, which is obtained from the system main clock SysClk through the different variable clocks used for this purpose: VC1 and VC2. These variable clocks haven't a concrete value for the DAC because they are used by the last loaded ADC overlay and the DAC is located in the base layer. The reason is that the DAC function must be available at any moment to provide the signal and so, it can't have an own overlay

<sup>&</sup>lt;sup>20</sup> See annex: How the DAC generates the signals.

<sup>&</sup>lt;sup>21</sup> See annex: Data format used by the user modules.

for setting these parameters. Also, the Counter8 user module is needed for generating the sinusoidal signal. This user module provides a counter that sets the proper sample from a look up table in the DAC6. This look up table looks like as follows.

int SINtable[SIN\_PERIOD] = {31, 33, 36, 39, 41, 44, 46, 49, 51, 53, 55, 56, 58, 59, 59, 60, 60, 60, 59, 59, 58, 56, 55, 53, 51, 49, 47, 44, 42, 39, 36, 33, 31, 28, 25, 22, 19, 16, 13, 11, 9, 7, 5, 3, 2, 1, 0, 0, 0, 0, 1, 2, 3, 4, 6, 7, 10, 12, 14, 17, 20, 23, 26, 29};

The Counter8 has an internal clock to increment the counter and a Period parameter that defines the counter maximum value. When the counter reaches the Period parameter value set, an interruption is triggered and the next value in the look up table is set in the DAC6. Its internal clock and the counter period ( $T_{counter}$ ) give the Counter8 sample rate (SR) as the equation (2.7) shows.

$$SR = f_{internal \, clock} \cdot \frac{1}{T_{counter}}$$

(2.7)

So, the sinusoidal signal frequency  $f_{out}$  is given by the Counter8 sample rate and the look up table number of samples (*N*). The equation (2.8) shows the relation between these parameters.

$$f_{out} = Sample \ Rate \cdot \frac{1}{N}$$

(2.8)

The internal clock is synchronized through the variable clock VC3. This clock is also needed for the UART user module, so the value is set by this one because is more restrictive in order to set the bitrate of the RS232 transmission. **Table 2.3** shows the values used to obtain the three sinusoidal frequencies used in the system.

| Table 2.3 | /alues | used for | or ge | nerating | the thr | ree sinus | soidal | signals. |

|-----------|--------|----------|-------|----------|---------|-----------|--------|----------|

|           |        |          |       |          |         |           |        |          |

| f <sub>internal clock</sub> [Hz] | T <sub>counter</sub> [cycles] | SR [sps]   | N [samples] | f <sub>out</sub> [Hz] |

|----------------------------------|-------------------------------|------------|-------------|-----------------------|

| 923 076,923                      | 255                           | 3 619,909  | 64          | 56,56                 |

| 923 076,923                      | 144                           | 6 410,256  | 64          | 100,16                |

| 923 076,923                      | 72                            | 12 820,512 | 64          | 200,32                |

For the sinusoidal signal generation, the value of the variable clocks VC1 and VC2 may limit the sinusoidal frequency if the DAC6 internal clock was slower than the Counter8 sample rate. This isn't the case because the slowest DAC6 internal clock is 205 128 Hz and the fastest Counter8 sample rate is 3 619,909 Hz. This means that the DAC6 analog block always has a new sinusoidal sample to output, and that the frequency is respected.

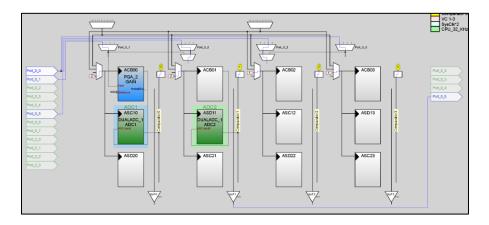

## 2.7 PSoC dynamic reconfiguration

PSoC dynamic reconfiguration has been used to reuse digital and analog resources in order to provide all the proposed functions. It has been done as follows.

Blocks from functions that are always activated, such as UART for communicating, LCD for displaying information and PGA for giving the input signal to the ADCs, and blocks from functions that may be used parallel to other functions, such as the DAC and the counter for generating signals, are located in the base layer, which is always loaded. Other blocks from functions that are not always active are located in different overlays. The main code loads the proper overlay corresponding to the function selected. Blocks that are always loaded must use different parameters than the blocks that are activated and inactivated in order not to interference each other. The global resources parameters used by the blocks that are always loaded are Ref Mux used by the PGA and VC3 used by the counter and the UART. They must have always the same value, so these parameters must remain unaltered in each overlay. The global resources parameters used by the blocks that are activated are VC1 and VC2, used by the different ADCs configurations. They change its value depending on the configuration selected, so these parameters must have its proper value in each overlay.

Global resources are defined in each layer, so the last loaded overlay will reset the current parameters. By this reason, these parameters must be set carefully to avoid that the functions which are always loaded remain without configuration.

## 2.8 Detected PSoC limitations

The first detected limitation is referring to the clock resources. All the digital or analog blocks need a clock signal to be synchronized. They are provided by a limited number of sources, which are basically the VC1, VC2 and VC3 parameters from the global resources. In this project, the sample rate of the different ADC configurations is given by a combination of these clock sources in order to obtain a range of different sample rates.

The need to have some user modules always active requires not having some resources available for the rest of the user modules. The UART for communicating, the LCD for displaying information or the counter for generating the AC test signals require that VC3 global resource clock parameter has always the same value in order to this functions work properly at any time. This implies that ADC obtains its clock source only from the VC1 and the VC2, and consequently to have a more limited range for their sample rates. Also, another consequence is that the DAC generated AC signals frequency is limited by the UART bit rate, which predetermines the VC3.

Another limitation is given by the CPU processing time. The user modules implementation has been done through the libraries provided by Cypress. They consist of a group of C++ functions in order to control and configure the user module. These functions, formed by different assembly instructions, need for some CPU cycles to be executed. Depending on the C++ function complexity, the number of CPU cycles may vary. When the ADC sample rate is increased, the time between two adjacent samples is decreased. This means that the sample processing is limited in time and therefore, the number of functions to be executed after getting the sample must be the smallest as possible in order to, for highest sample rates, leave the CPU free to acquire the next sample. Acquiring a sample. displaying it on the LCD and transmitting it through the RS232, hold the CPU for a time that limits the sample rate. By this reason, for all the ADC configurations except the ADCINCVR 1, the LCD displaying has been needed to avoid. Also, for ADCINCVR\_3, ADCINCVR\_4 and SAR6, the sample transmission is done in blocks of 100 samples. For it, a predetermined number of samples are acquired continuously before transmitting them through the RS232. So, the sampled signal is transmitted in blocks. This avoids the displaying and transmitting CPU tasks between samplings.

Also, a detected limitation is that SAR6 can't acquire properly 100 and 200 Hz AC signals generated by the DAC. The reason is that due to its architecture, it requires 100 % of the PSoC CPU during the sample conversion<sup>22</sup> and the DAC needs a CPU interruption to generate the AC signal.

<sup>&</sup>lt;sup>22</sup> As explained in the Cypress Application Note 2239: Analog – ADC selection, (<u>http://www.cypress.com/?rID=2641</u>)

# 3. USER INTERFACE

The last stage of the system is a personal computer with a software that provides a user interface for the system.<sup>23</sup> It is used to show the signal information and to interact with the system. The next section explains its different functions in detail.

## 3.1 Functional description

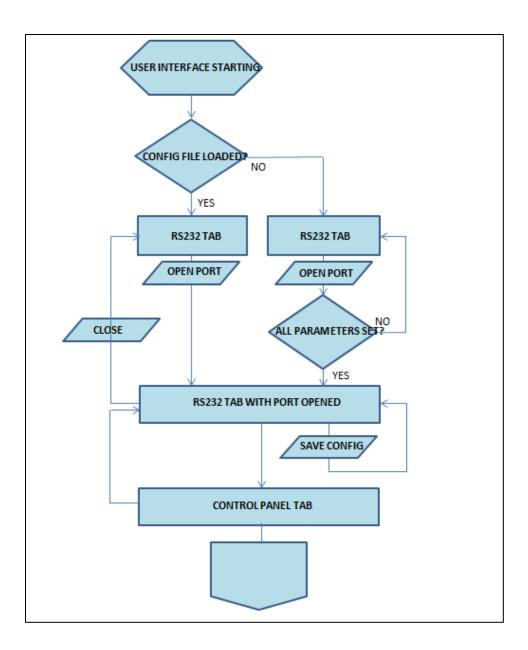

The user interface can be divided in two different parts: the configuration area, which is composed by a tab for the RS232 communication and a tab for the system control panel, and the visualization area.

The RS232 communication tab allows setting the RS232 communication between the system and the personal computer. When all the communication parameters <sup>24</sup>are set the Open communication option is enabled. When the communication is opened, the Close communication option becomes visible in order to close it. Also, an option to save the set parameters is provided. **Fig. 3.1** shows a screenshot of the RS232 communication tab.

| 🔜 User interface    |             |                     | <u> </u> |

|---------------------|-------------|---------------------|----------|

| RS232 Control panel |             | Visualization area: |          |

| Port:               | COM7 💌      |                     |          |

| Bit rate:           | 115200 💌    |                     |          |

| Data bits:          | 8           |                     |          |

| Parity:             | None        |                     |          |

| Stop bits:          | 1           |                     |          |

| Flow control:       | None        |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

|                     |             |                     |          |

| Open port           | Save config |                     | Timeline |

|                     |             |                     |          |

Fig. 3.1 RS232 communication tab screenshot.

<sup>&</sup>lt;sup>23</sup> See the source code in the Annex.

<sup>&</sup>lt;sup>24</sup> Parameters: 115 200 bps, 8 data bits, no parity, 1 stop bits and no flow control.

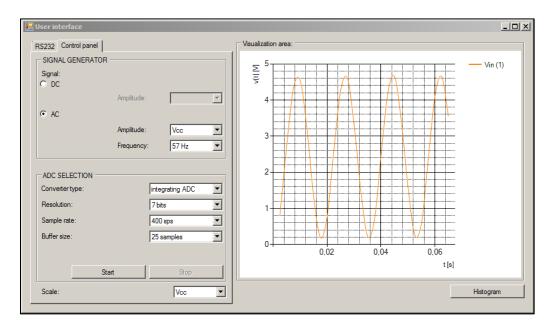

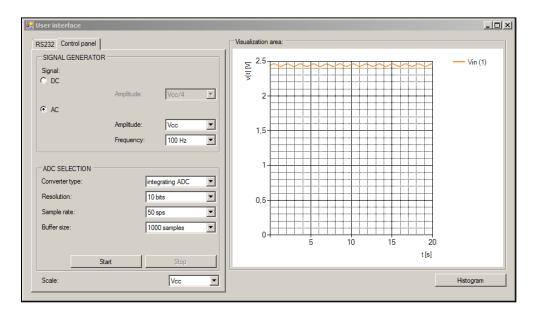

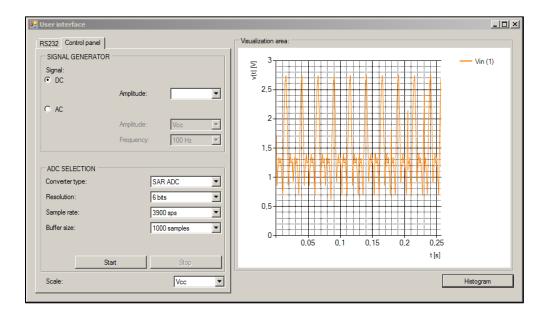

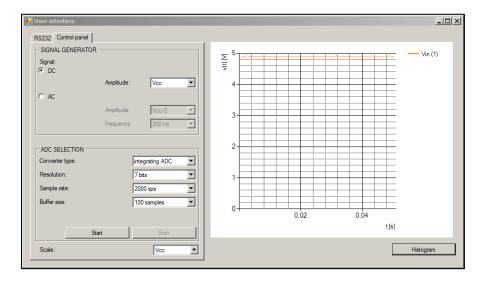

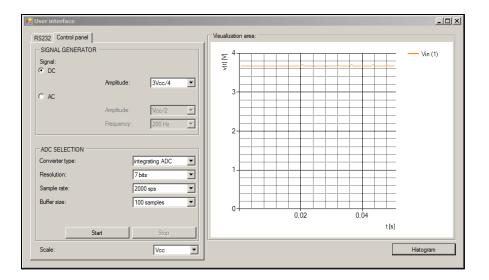

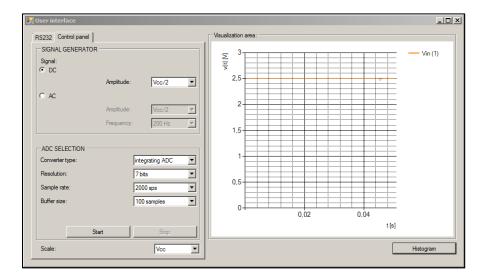

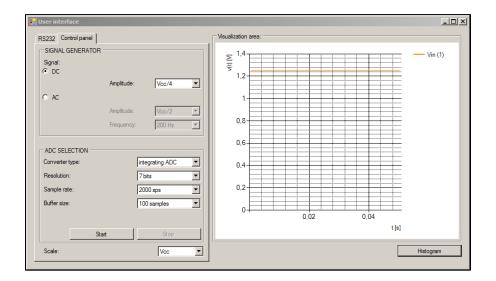

The system control panel tab is enabled only if the communication is opened. This tab allows configuring the system and powering on and off. It has two separated parts: the signal generator and the ADC selection. The first one activates the signal generation, allows selecting the signal type and setting its frequency and amplitude. The second one allows setting the type of converter, the resolution, the sample rate and the number of samples to acquire. Also, there is an option to select the scale for the signal acquired. With this function the resolution of the ADCs is optimized for small signals.

When the parameters corresponding to the ADC selection are set, the button Start is enabled and the process of acquiring the signal can be started. In this moment, the Stop button is enabled and all the parameters including the RS232 communication tab are blocked. The process can be stopped at any moment or it will be stopped automatically when all the samples indicated in the buffer size are get. **Fig. 3.2** shows a screenshot of the system control panel tab.

| User interface                          | <u>_                                    </u> |

|-----------------------------------------|----------------------------------------------|

| RS232 Control panel Visualization area: |                                              |

| SIGNAL GENERATOR                        |                                              |

| Signal:                                 |                                              |

| Amplitude:                              |                                              |

| ○ AC                                    |                                              |

| Amplitude:                              |                                              |

| Frequency:                              |                                              |

| ADC SELECTION                           |                                              |

| Converter type:                         |                                              |

| Resolution:                             |                                              |

| Sample rate:                            |                                              |

| Buffer size:                            |                                              |

|                                         |                                              |

| Start Stop                              |                                              |

| Scale:                                  | line                                         |

Fig. 3.2 System control panel tab screenshot.

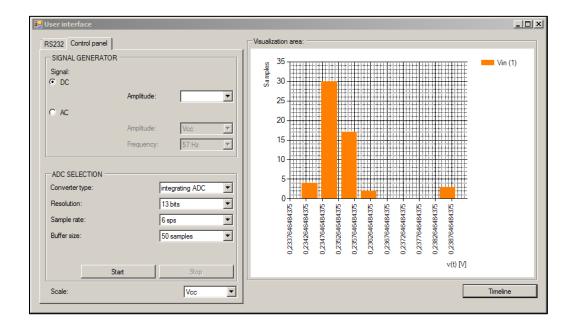

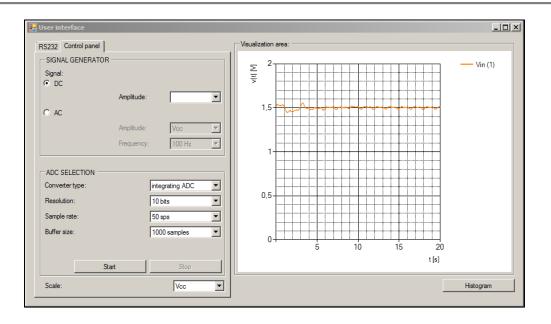

When the process of acquiring the signal is finished, the signal is visualized along the time in the visualization area. The visualization area is the space from the interface where the signal is shown. Two types of visualizations can be selected: the signal along the time and a histogram of the acquired samples. The button under the visualization area allows switching between them. **Fig. 3.3** and **Fig. 3.4** show a screenshot with an example of these visualizations: a continuous signal represented along the time and its histogram, respectively.

Fig. 3.3 Visualization area in time respresentation mode.

Fig. 3.4 Visualization area in histogram mode.

## 3.2 Implementation

The user interface is implemented in C# language for Windows. For the RS232 communication the COM serial ports from Windows have been used. C# provides a library to manage these ports in several ways.

For visualizing the signal along the time and the histogram, the MSChart library from Microsoft has been used. It allows several types of graphs and a lot of ways to configure them. **Fig. 3.5** shows the software flowchart.

Fig. 3.5 User interface software flowchart.

## 4. EXPERIMENTAL RESULTS

### 4.1 Test of different ADC features

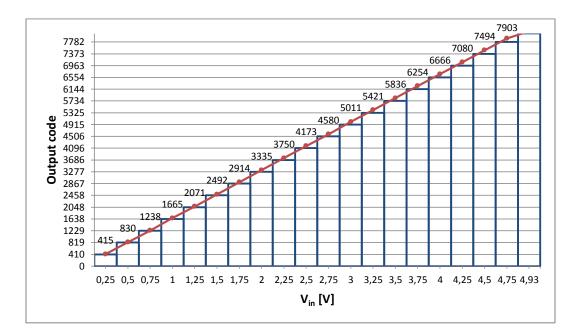

To observe the ADC linearity the 13-bits integrating ADC is used because its higher resolution is better to represent this characteristic. To see this characteristic, the ADC transfer curve is needed. It is obtained applying different DC voltage levels to the ADC input. The onboard potentiometer connected to the V<sub>cc</sub> pin is used to obtain these DC voltage levels, previously measured with a tester of up to 200 mV scale.

The output code is compared with the ideal output (n) given by the equation (4.1), where  $V_{in}$  is the voltage level applied, FSR is equal to 5 V and N are the 13 bits.

$$n = \frac{V_{in}}{FSR} \cdot 2^N \tag{4.1}$$

The voltage level applied as well as its ideal output code (y-axe values) and its real output value (labels values) is given in the **Fig. 4.1**.

Fig. 4.1 ADC transfer curve.

To test the experimental dynamic range the input is connected to the board ground in order to measure the noise floor present in the device. Then, the noise RMS ( $x_{RMS}$ ) is calculated from the histogram obtained. Finally, the experimental dynamic range can be obtained from this parameter.

To show the noise floor, the 13-bits integrating ADC is used with a sample rate of 6 sps and an integration time of 19,968 ms. The test is done with a buffer size of 1 000 samples. The noise floor histogram obtained is shown in the **Fig. 4.2**.

Fig. 4.2 Noise floor histogram for a 13-bits integrating ADC.

The histogram shows a Gauss distribution of media  $\mu$  equal to 24,4 mV (value corresponding to the decimal code 40, obtained by the LCD display). It means that there is an offset between the ADC internal ground and the on board ground pin where the ADC input is connected. Also, a noise variation of ±1 LSB can be seen, equal to ±0,61 mV, value given by the resolution and the FSR which corresponds to 5 V.

An approximation of the  $V_{n,RMS}$  noise value can be obtained from this distribution, applying the equation **(4.2)**. Where N are the total of samples acquired, corresponding to the buffer size and  $x_i$  is the voltage value corresponding to the different obtained codes. The  $V_{n,RMS}$  value obtained is 1,337 mV.

$$V_{n,RMS} = \sqrt{\frac{1}{N} \sum_{i=1}^{N} x_i^2}$$

(4.2)

And the corresponding ADC dynamic range can be estimated through the equation (4.3), where the  $V_{in,RMS}$  is equal to 3,125 V, a value that corresponds to a FSR amplitude sinusoidal signal. The expected DR is equal to 67 dB.

$$DR = SNR = 20 \log \frac{V_{in,RMS}}{V_{n,RMS}}$$

(4.3)

### 4.2 Interference rejection

This section aims to show the main power line 50 Hz interference rejection capability of the integrating ADC, the design to this purpose of which is explained in the section 2.5.6 ADCINCVR frequency rejection.

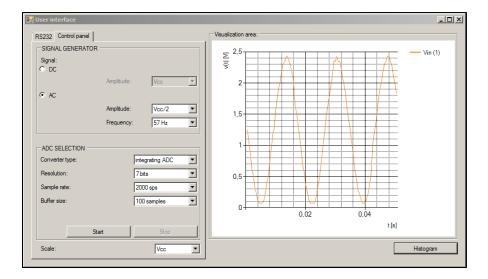

To do it, the AC signals generating system function is used in order to generate a 100 Hz AC signal, which is a proper signal for the test because it is a 50 Hz signal harmonic. Also, the integrating type ADC and the 10 bits resolution (with restrings the sample rate to 50 sps) are selected in the user interface, parameters that provide the proper integration time, equal to 19,968 ms. The samples acquired are 1 000 samples that gives the 20 seconds of acquisition time. The **Fig. 4.3** shows the acquired signal.

Only a signal approximated to a 2,5 V DC voltage level is shown. The reason is that the sinusoidal integration operation gives its average value, which corresponds to its DC voltage component or offset value. For this case, the generated AC signal reference voltage has a ground of  $V_{dd}/2$ , which is given by the system in order to generate both positive and negative semi-cycles. For a 0 V based-ground, the interference would be attenuated to the 0 V value.

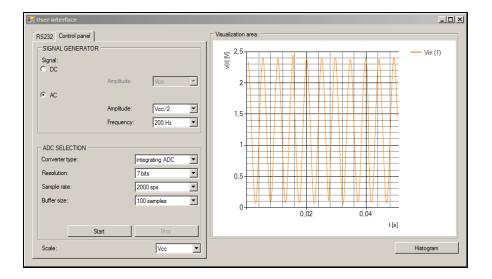

Also, another test to check the rejection is to try to get some main power line interference leaving opened the ADC input and acquiring it with the SAR type ADC. If a main power line is near to the input the acquired signal looks like the **Fig. 4.4**.

Fig. 4.3 Integrating ADC acquired signal.

Fig. 4.4 User interface with the SAR ADC selected.

An interference with an approximated frequency of 50 Hz can be seen. The **Fig. 4.5** shows the input with the same conditions that the last test, but for an integrating ADC with 20 ms of integration time instead of the SAR type. The figure shows that the interference is not present.

Fig. 4.5 User interface with the integrating ADC selected.

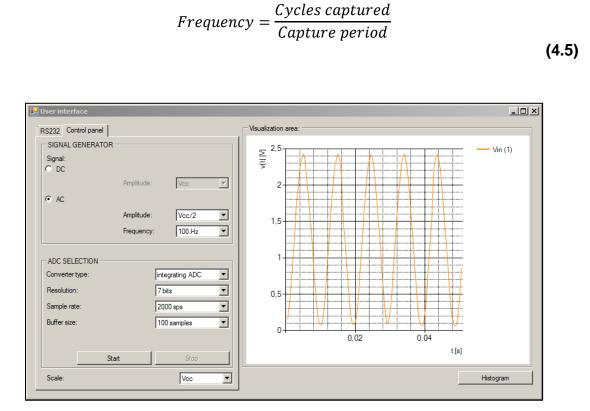

## 4.3 Test of DAC signal generation

This section shows the different signals that can be obtained from the DAC. The user can select between AC signals with an amplitude of 1,25, 2,5, 3,75 and 5 V and DC signals with a voltage level of 1,25, 2,5, 3,75 and 5 V. For the AC signal, the frequencies are 57, 100 and 200 Hz. To show it, the user interface has been used, although previously they have been already tested through an oscilloscope. Only the 100 Hz AC signal with an amplitude of 2,5 V will be analyzed in the section in order to not extend the report, the rest of the screenshots can be seen in the annex. The **Fig. 4.6** shows it.

An integrating ADC converter has been used to acquire the signal. The sample rate is set to 2 000 sps and the buffer size to 100 samples, which provide the shown capture of 50 ms, calculation given by the equation (4.4).

$$Capture \ period = \frac{Buffer \ size}{Sample \ rate}$$

(4.4)

To calculate approximately the signal frequency the equation **(4.5)** can be used. The 5 cycles that can be shown in an approximate period of 44 ms are divided by this period, it corresponds to 113 Hz.

Fig. 4.6 100 Hz AC signal generation.

## 4.4 ADC and DAC working together

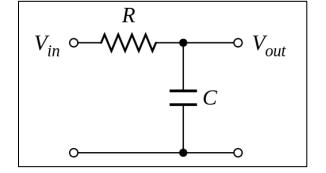

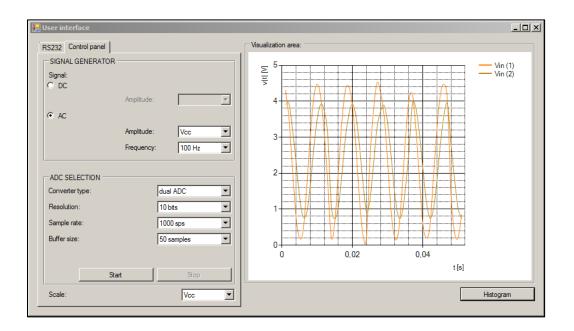

The ADC and DAC working together are tested through a RC circuit designed as a first order low-pass filter, as **Fig. 4.7** shows. In order to do this test, the dual ADC is needed for comparing the amplitude and phase of the two signals present in the filter. It is configured with the only parameters available that are 10 bits and a sample rate of 1000 sps.

The test consists in generating a 100 Hz AC signal with amplitude of 5 V. This signal is output from the DAC through the P05 PSoC pin to the circuit and to the P00 dual ADC input 1 pin. The circuit is formed by a resistor of resistance R and a

capacitor of capacity C, with the input  $V_{in}$  and the output  $V_{out}$ . The circuit output is connected to the P01 dual ADC input 2 pin.

This circuit configuration behaves as a first order low-pass filter, which attenuates the amplitude of the input signal  $f_c$  frequency to the 70,7 % of the maximum (the signal power is attenuated 3 dB) and changes its phase -45°. This frequency characterizes the circuit and is given by the resistance and capacitor values as the equation (4.6) shows.

$$f_c = \frac{1}{2 \cdot \pi \cdot R \cdot C} \tag{4.6}$$

Fig. 4.7 RC filter schematic.<sup>25</sup>

In order to attenuate the 100 Hz AC signal, R is calculated through the equation **(4.6)** when C is fixed to 1  $\mu$ F. Its value is to 1 591  $\Omega$ , but the nearest commercial resistor value is 1 500  $\Omega$ , with an experimental resistance of R = 1 493  $\Omega$ , so the final  $f_c$  is 106,6 Hz.

The **Fig. 4.8** shows the relation between the filter input signal  $V_{in}(1)$  and the filter output signal  $V_{in}(2)$ .

<sup>&</sup>lt;sup>25</sup> Source: <u>http://es.wikipedia.org/wiki/Filtro paso bajo</u>

Fig. 4.8 Signals input in the dual ADC.  $V_{in}(1)$  from the DAC and  $V_{in}(2)$  from the filter output.

As can be seen, the filter output signal is dephased near to the expected 45° and the maximum voltage is decreased from 4,5 V to 3,8 V, which corresponds to 84 % of attenuation. These values are not exactly the expected due to mainly the ADC internal impedance which hasn't been taken into account.

# 5. CONCLUSIONS

The project main objective has been achieved; the system has the capabilities of acquiring a signal allowing a variety of configurations including the ADC type selection. Also generating AC and DC signals is provided. The interface allows interacting with the system and showing the results. Also, PSoC advantages and some limitations have been detected.

With the PSoC families of chip, Cypress provides a powerful tool in order to implement a high variety of devices; although the main advantage is the chip capability to be reconfigured into several preloaded systems. This capability is the key to implement the DAS system, not only for switching between peripherals if not for reusing the global resources. Several configurations which need for the same resources can be activated or not from the same firmware and in real time.

Despite of this, the global resources are the principal limitation detected in the DAS implementation. Concretely, the three variable clocks must be specifically distributed for the user modules in order to be available for the rest of the user modules. This makes that the entire variety of ADC sample rates can't be achieved. Also by this reason, the generated AC signals have an important restriction in their generated frequencies, which are limited to some hundreds of hertz. A possible future work could be to study and design a better reuse of the global resources in order to obtain more performance from the user modules implemented.

Another point to be considered is the CPU use for the expected tasks. Some difficulties to sample the input signal properly have been found when using the LCD, generating a DAC AC signal and transmitting the sample one by one at highest sample rates. This presents a future work in order to optimize the PSoC firmware using the assembler language for programming it instead of using the C++ libraries provided by Cypress for each user module.

In terms of environment, it is important to say that it has not been a point to consider in this project due to its educational objectives. In the expected conditions the main power line can be present, so it is not necessary to maximize the DAS system autonomy, a feature that would be a trade off with the system performance, for example limiting the sample rates.

# BIBLIOGRAPHY

[1] Bertran Albertí, E., *Procesado digital de señales,* Edicions UPC, Barcelona (2006)

[2] Halámek, J., Viscor, I., Kasal, M., "Dynamic range and acquisition system", *Measurement science review*, Institute of Scientific Instruments, Královopolská (2001)

[3] Drake Moyano, J. M., "Ruidos e Interferencias: Técnicas de reducción", *Instrumentación electrónica de comunicaciones,* Escuela Técnica Superior de Ingenieros Industriales y de Telecomunicación, Cantabria (2005)

[4] Garcimartín Montero, A., *Sistemas de medida y adquisición de datos,* DPTO. De Física y Matemática Aplicada, Navarra.

[5] Gómez, J., ¿Cómo controlar el puerto serie usando C#?, Escuela Técnica Superior de Telecomunicaciones, Bilbao.

[6] Mićaković, P., *Architecture and Programming of PSoC Microcontrollers,* Free online book mikroElektronika, <u>http://www.easypsoc.com/book/</u>