## Rapid Evaluation of Requirements for Vector Micro-Architectures

Milan Stanic

Barcelona School of Informatics (FIB)

Universitat Politècnica de Catalunya

A thesis submitted for the degree of Master of Information Technology 21th of September, 2011

Advisor: Adrian Cristal

Tutor: Alejandro Ramirez Bellido

#### Abstract

Power consumption has become one of the dominant issues in processor design, especially important in embedded systems and data centers. One of possible solution that can address this issue and provide higher performance for existing applications and new capabilities for future applications used in hand-held devices and data centers is to use vector processor.

This thesis presents the design and implementation of a vector library that enables the vectorization of the target applications and allows to characterize them.

We also present the ETModel: a simple trace-driven simulator for vector processors. It is used to analyse the micro-architectural requirements of the vectorized applications.

We show that the target applications are highly vectorizable with a degree of vectorization from 62.9% for H264ref to 91% for ECLAT. Detailed instruction level characteristics such as the distribution of vector instructions, the distribution of vector lengths, etc. are also presented in the thesis.

The thesis contains detailed timing analysis of the vectorized applications for different micro-architectural configurations of a vector processor. We measured the execution time for the different configurations of cache hierarchy, main memory latencies, maximum vector lengths and configuration of functional units, as well as the usage of functional units. All these help in understanding the behavior of the vectorized applications and requirements of vector micro-architecture.

## Acknowledgements

I would like to thank my supervisors and tutor, for their guidance of this thesis and their support. I am especially grateful to Oscar Palomar for many insightful discussions and for his patience in reading my manuscripts. I would also like to thank all my colleagues in the Microsoft Research Center for their unselfish support.

Special thanks go to my parents, Zivorad and Svetlana, my sister Marija, my girlfriend Suzana and all my family for their love and support. I would not be here today without their dedication and encouragement.

## Contents

| 1 | Wo  | rk Presentation                                 | 1          |

|---|-----|-------------------------------------------------|------------|

|   | 1.1 | Motivation                                      | 1          |

|   | 1.2 | Project Objectives                              | 2          |

|   | 1.3 | Project Objectives                              | 3          |

| 2 | Vec | tor Processors                                  | 4          |

|   | 2.1 | Advantages of Vector Processors                 | 5          |

|   | 2.2 | Relevant techniques and concepts                | 6          |

|   |     | 2.2.1 Chaining                                  | 6          |

|   |     | 2.2.2 Multiple Lanes                            | 7          |

|   |     | 2.2.3 Death time or recovery time               | 8          |

|   |     | 2.2.4 Masking                                   | 9          |

|   | 2.3 | Existing implementations                        | 10         |

| 3 | Vec | tor library                                     | 1 <b>2</b> |

|   | 3.1 | Configurable vector register file               | 12         |

|   | 3.2 | Vector ISA                                      | 13         |

|   |     |                                                 | 14         |

|   |     | 3.2.2 Memory Instructions                       | 15         |

|   |     | 3.2.3 Reduction Instructions                    | 16         |

|   |     | 3.2.4 Bit and element manipulation instructions | 18         |

|   | 3.3 |                                                 | 21         |

|   | 3.4 |                                                 | 22         |

|   | 3.5 |                                                 | 23         |

|   | 3.6 |                                                 | 23         |

CONTENTS

| 4 | ETI | Model   |                                                                                    | <b>25</b> |

|---|-----|---------|------------------------------------------------------------------------------------|-----------|

|   | 4.1 | Micro-  | Architecture                                                                       | 26        |

|   | 4.2 | Top-Le  | evel Model                                                                         | 28        |

| 5 | Vec | torizat | ion                                                                                | <b>31</b> |

|   | 5.1 | Metho   | dology                                                                             | 31        |

|   | 5.2 | Vector  | ized applications                                                                  | 32        |

|   |     | 5.2.1   | SPEC2006 Sphinx3 benchmark                                                         | 32        |

|   |     | 5.2.2   | SPEC2006 H264ref benchmark                                                         | 33        |

|   |     | 5.2.3   | SPEC2006 Hmmer benchmark                                                           | 33        |

|   |     | 5.2.4   | SPEC2000 FaceRec benchmark                                                         | 33        |

|   |     | 5.2.5   | ECLAT MineBench                                                                    | 33        |

|   | 5.3 | Vector  | ized kernels                                                                       | 34        |

|   |     | 5.3.1   | Sphinx3                                                                            | 34        |

|   |     |         | $5.3.1.1  \text{Kernel 1. vector\_gautbl\_eval\_logs3} \; \dots \; \dots \; \dots$ | 34        |

|   |     |         | 5.3.1.2 Kernel 2. subvq_mgau_shortlist                                             | 36        |

|   |     |         | $5.3.1.3$ Kernel 3. mdef_sseq2sen_active                                           | 37        |

|   |     |         | 5.3.1.4 Kernel 4. dict2pid_comsenscr                                               | 38        |

|   |     |         | $5.3.1.5$ Kernel $5.$ approx_cont_mgau_frame_eval                                  | 40        |

|   |     | 5.3.2   | FaceRec                                                                            | 40        |

|   |     |         | 5.3.2.1 Kernel 1. passb4                                                           | 40        |

|   |     |         | 5.3.2.2 Kernel 2. gaborTrafo                                                       | 41        |

|   |     |         | 5.3.2.3 Kernel 3. TopCostFct                                                       | 43        |

|   |     | 5.3.3   | ECLAT                                                                              | 44        |

|   |     | 5.3.4   | Hmmer                                                                              | 44        |

|   |     | 5.3.5   | H264ref                                                                            | 44        |

|   |     |         | $5.3.5.1  \text{Kernel 1. FastFullPelBlockMotionSearch} \ . \ . \ . \ .$           | 45        |

|   |     |         | 5.3.5.2  Kernel 2. SubPelBlockMotionSearch  .  .  .  .                             | 47        |

|   | 5.4 | Instru  | etion level characterization                                                       | 49        |

|   |     | 5.4.1   | Degree of Vectorization                                                            | 51        |

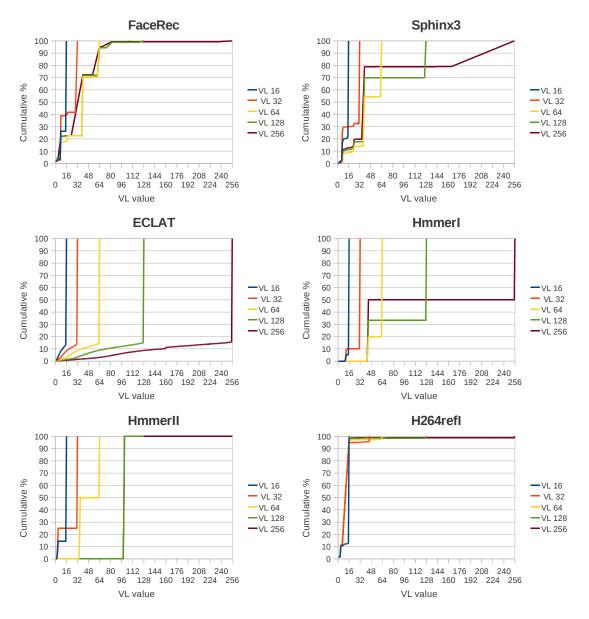

|   |     | 5.4.2   | Distribution of Vector Lengths                                                     | 52        |

|   |     | 5.4.3   | Distribution of Vector Memory and Computation Instructions                         | 55        |

|   |     | 5.4.4   | Distribution of Data Types                                                         | 62        |

| CONTENTS | CONTENTS |

|----------|----------|

|          |          |

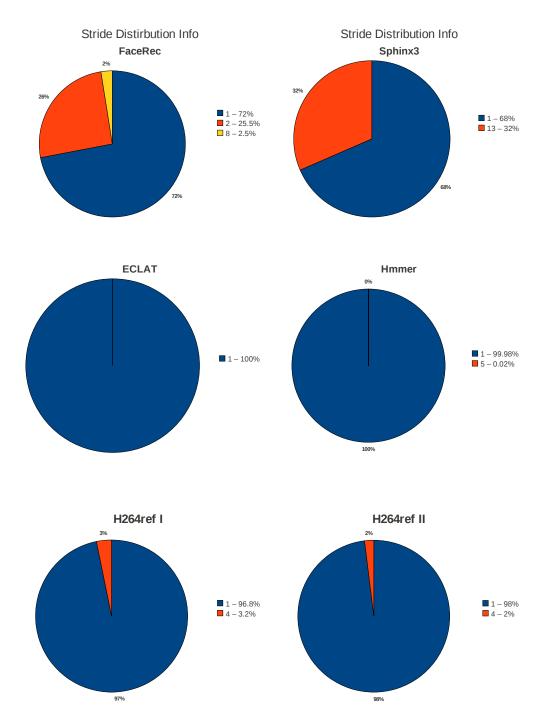

|   |      | 5.4.5 Vector    | Stride Distrib | oution .   |         |      |    |  |  |   |   | 62        |

|---|------|-----------------|----------------|------------|---------|------|----|--|--|---|---|-----------|

|   |      | 5.4.6 Impact    | of maximum     | vector re  | gister  | leng | th |  |  | • |   | 65        |

| 6 | Tim  | ing Analysis    |                |            |         |      |    |  |  |   |   | <b>68</b> |

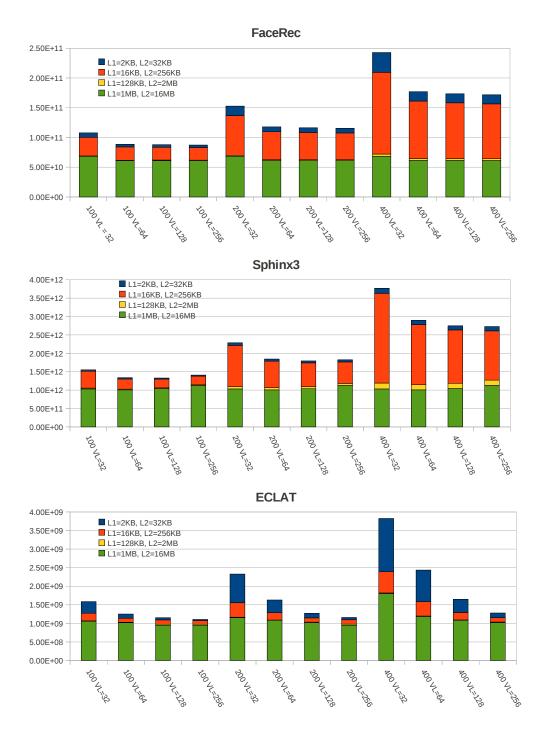

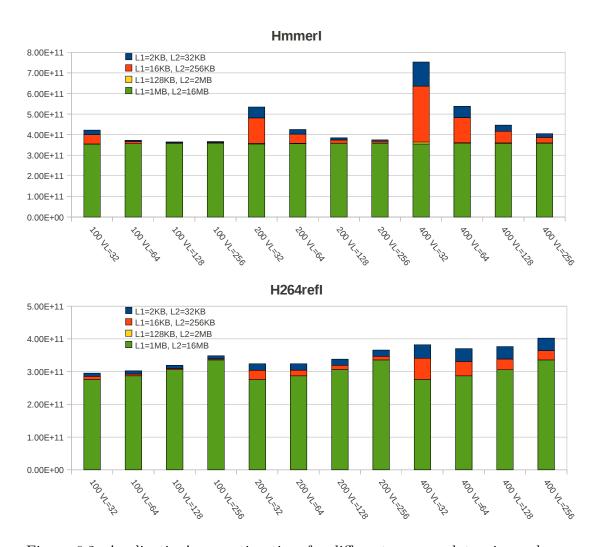

|   | 6.1  | Memory latence  | ey and cache   | configurat | tions . |      |    |  |  |   |   | 68        |

|   | 6.2  | Functional uni  | ts             |            |         |      |    |  |  |   | • | 76        |

| 7 | Rela | ted Work        |                |            |         |      |    |  |  |   |   | 83        |

|   | 7.1  | Profiling and c | haracterizatio | on of worl | kloads  |      |    |  |  |   |   | 83        |

|   | 7.2  | Vector ISA and  | d vector micro | o-architec | ture.   |      |    |  |  |   |   | 84        |

|   | 7.3  | Analytical mod  | delling        |            |         |      |    |  |  | • |   | 84        |

| 8 | Con  | clusion and F   | uture Work     |            |         |      |    |  |  |   |   | 86        |

|   | 8.1  | Contributions   |                |            |         |      |    |  |  |   |   | 86        |

|   | 8.2  | Conclusions .   |                |            |         |      |    |  |  |   |   | 87        |

|   | 8.3  | Future Researc  | eh             |            |         |      |    |  |  |   |   | 88        |

# List of Figures

| 2.1 | Comparison of a scalar instruction and a vector instruction           | 5  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Timings for a sequence of dependent vector instructions ADDV          |    |

|     | and MULV, both unchained and chained                                  | 7  |

| 2.3 | Using multiple functional units to improve performance of a single    |    |

|     | vector add instruction, $C = A + B$                                   | 8  |

| 2.4 | Structure of a vector unit containing four lanes                      | 9  |

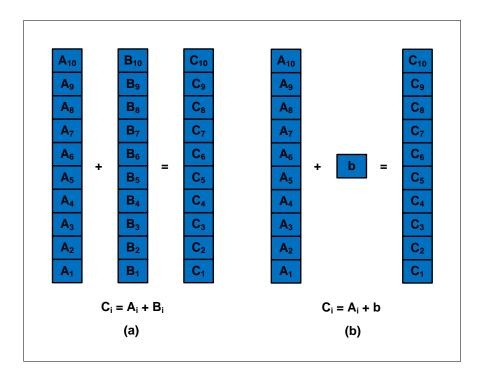

| 3.1 | Two modes of vector instruction: (a) vector-vector and (b) vector-    |    |

|     | scalar                                                                | 14 |

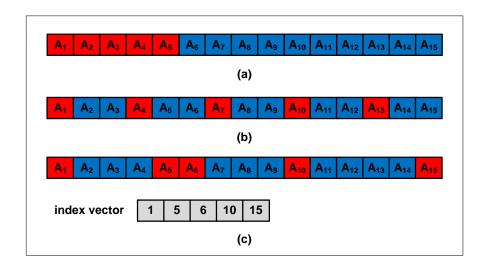

| 3.2 | Different types of memory instructions: (a) unit-stride, (b) strided, |    |

|     | and (c) indexed                                                       | 16 |

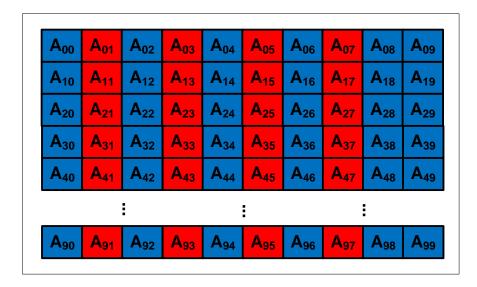

| 3.3 | An example of vector memory shape instructions where red ele-         |    |

|     | ments are loaded from matrix                                          | 17 |

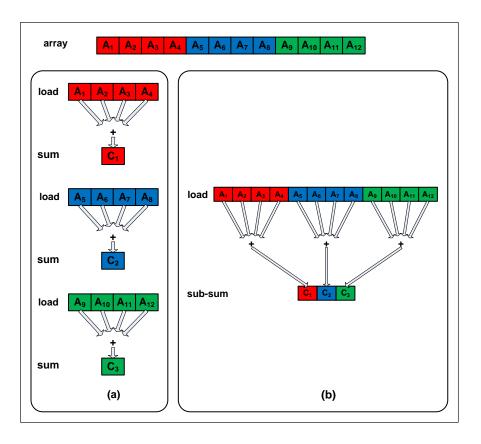

| 3.4 | An example of performing sum for sub-sets of array using: (a)         |    |

|     | reduction instruction $sum$ and (b) new reduction instruction $sub$ - |    |

|     | sum                                                                   | 18 |

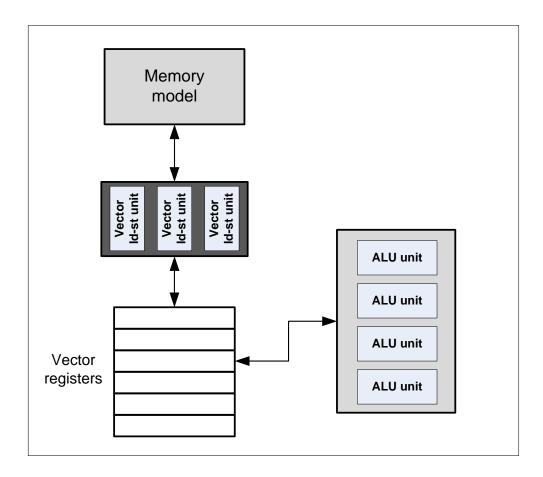

| 4.1 | The basic structure of model register-based vector architecture       | 27 |

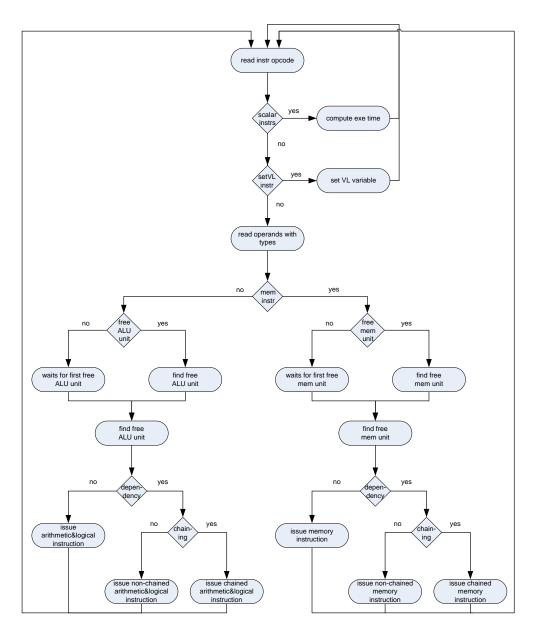

| 4.2 | Diagram of algorithm used to compute execution time in the ET-        |    |

|     | Model                                                                 | 30 |

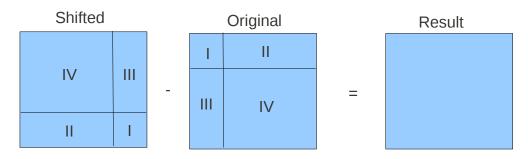

| 5.1 | Subtraction of shifted version of $Kernel$ and the original version   | 42 |

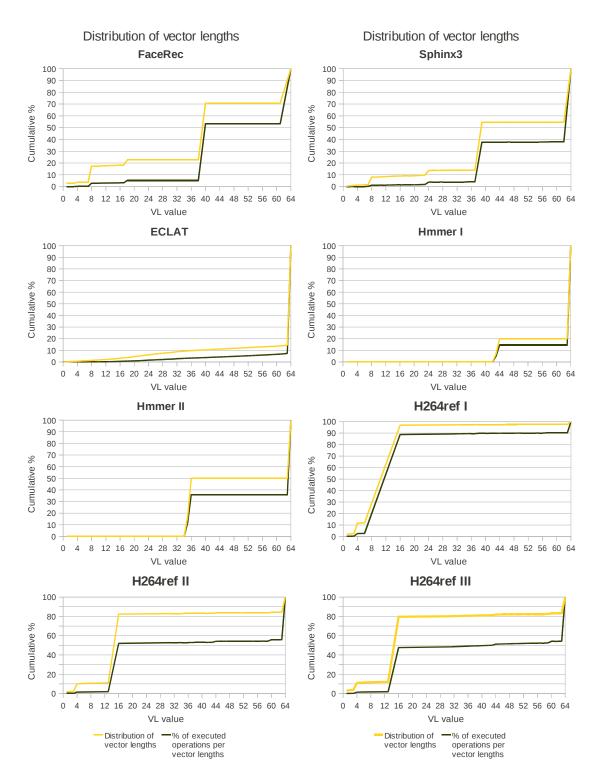

| 5.2 | Distribution of vector lengths. X-axis is the VL value and Y-axis     |    |

|     | is a cumulative percentage distribution                               | 54 |

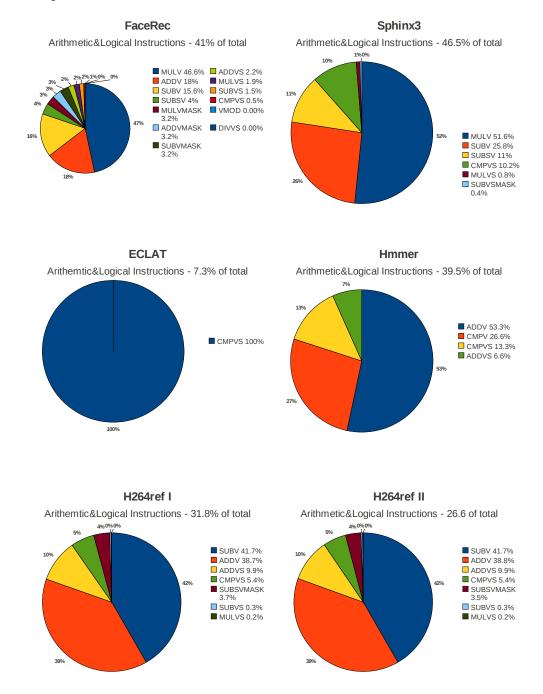

| 5.3 | Distribution of arithmetic and logical vector instructions            | 57 |

| 5.4 | Distribution of vector memory instructions                            | 58 |

#### LIST OF FIGURES

#### LIST OF FIGURES

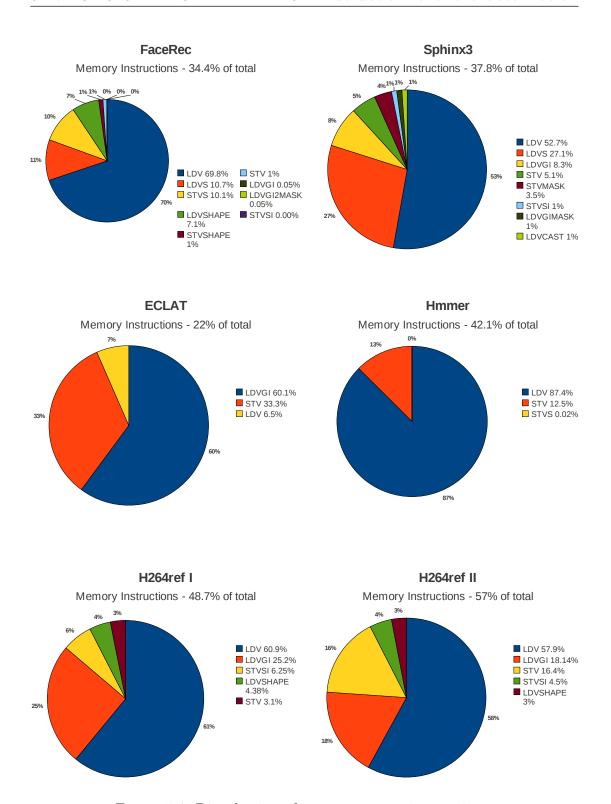

| 5.5 | Distribution of vector reduction instructions                       | 60         |

|-----|---------------------------------------------------------------------|------------|

| 5.6 | Distribution of vector bit and element manipulation instructions    | 61         |

| 5.7 | Distribution of strides for vector memory instructions              | 64         |

| 5.8 | Vector length distribution for different maximum vector lengths     | 67         |

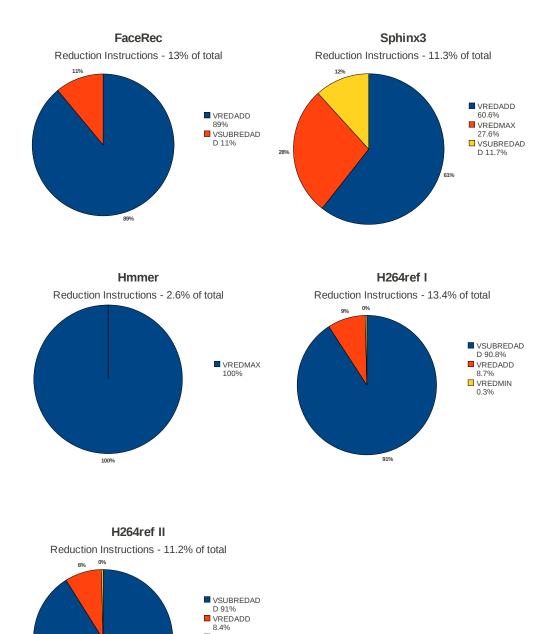

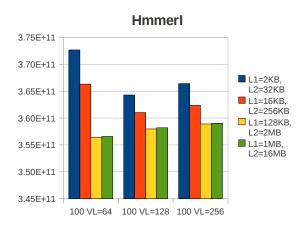

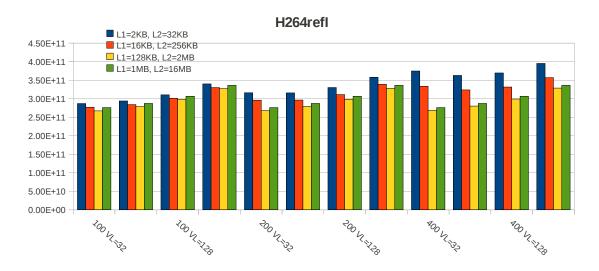

| 6.1 | Application's execution time for different memory latencies and     |            |

|     | configurations of cache hierarchy for FaceRec, Sphinx3 and ECLAT.   | 71         |

| 6.2 | Application's execution time for different memory latencies and     |            |

|     | configurations of cache hierarchy for HmmerI and H264refI           | <b>7</b> 2 |

| 6.3 | Execution time for HmmerI application                               | 75         |

| 6.4 | Execution time for H264refI application                             | 75         |

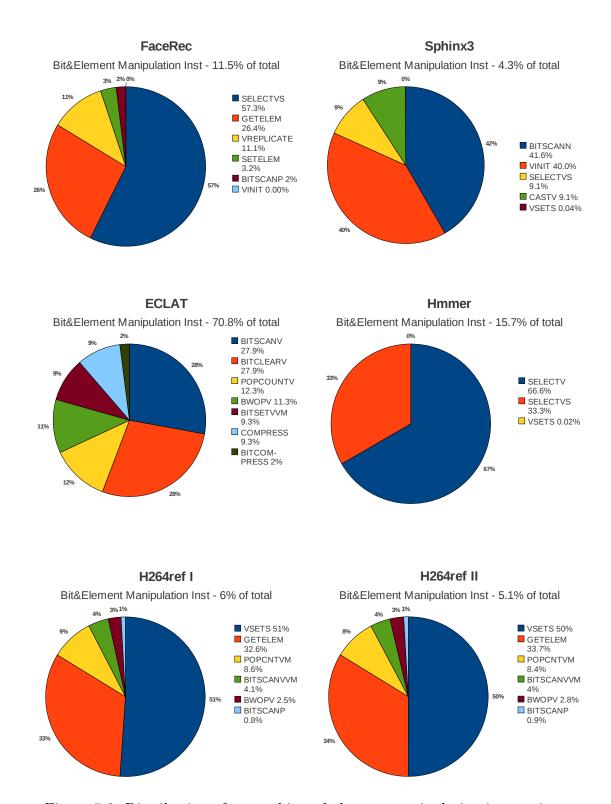

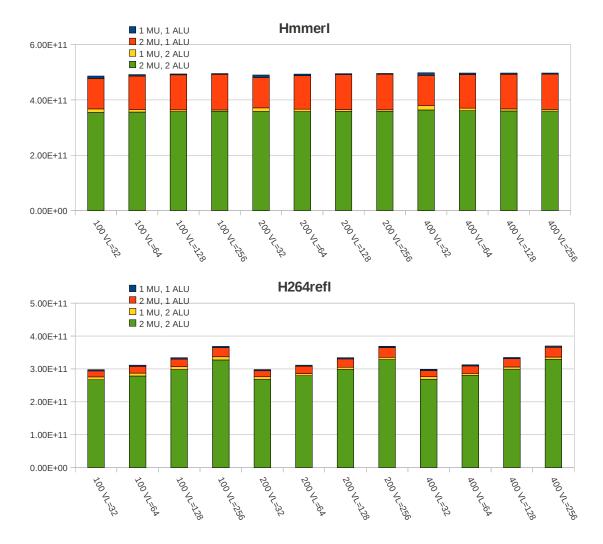

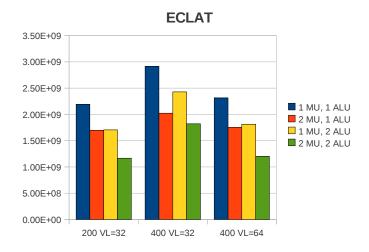

| 6.5 | Application's execution time for different configurations of func-  |            |

|     | tional units for FaceRec, Sphinx3 and ECLAT                         | 77         |

| 6.6 | Application's execution time for different configurations of func-  |            |

|     | tional units for HmmerI and H264refI                                | 78         |

| 6.7 | ECLAT's execution time for configurations of functional units where |            |

|     | the second configuration is betther then the third                  | <b>7</b> 9 |

|     |                                                                     |            |

# List of Tables

| 1.1 | Project roadmap activities                                                                                                        | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Implemented vector arithemetic, logical, memory and reduction instructions in the vector library. V-V is vector-vector, while V-S |    |

|     | is vector-scalar                                                                                                                  | 19 |

| 3.2 | Implemented vector bit and element manipulation instructions in                                                                   |    |

|     | the vector library                                                                                                                | 20 |

| 5.1 | The degree of vectorization for the set of vectorized applications                                                                | 52 |

| 5.2 | Distribution of vector memory and computation instructions and                                                                    |    |

|     | operations                                                                                                                        | 55 |

| 5.3 | Distribution of data types for computational vector instructions                                                                  | 63 |

| 5.4 | Distribution of data types for memory vector instructions                                                                         | 63 |

| 5.5 | Degree of vectorization for different maximum vector register lengths.                                                            | 66 |

| 6.1 | Different configurations of cache hierarchy                                                                                       | 69 |

| 6.2 | Statistics for Sphinx3 application with two ALU and two memory                                                                    |    |

|     | units                                                                                                                             | 74 |

| 6.3 | Statistics for Sphinx3 application with four ALU and two memory                                                                   |    |

|     | units                                                                                                                             | 74 |

| 6.4 | Different configurations of functional units                                                                                      | 78 |

| 6.5 | The usage of of ALU and memory units for the different configu-                                                                   |    |

|     | rations of functional units                                                                                                       | 82 |

## Chapter 1

## Work Presentation

#### 1.1 Motivation

Over the last few years, power consumption has become one of the dominant issues in processor design. This issue is especially important in embedded systems such as cellular phones, pagers, PDAs, digital cameras, DVDs, game consoles, etc. in which battery life becomes a major concern, but also in tremendous data centers that consume a large amount of power. At the same time, a new design should provide higher performance for existing applications and new capabilities for future applications that will be used in hand-held devices or data centers.

Vector processors are one possible solution to address this issue because they can express data level parallelism where it exists in a very efficient way. They fetch fewer instructions and therefore reduce the fetch and decode bandwidth requirements.

In order to help us to define a new vector architecture, we should discover which are the characteristics at the instructions level of the target applications (once they have been vectorized) (e.g. degree of vectorization in application, distribution of vector lengths, distribution of instruction types, etc.) and also which new vector instructions we will need in order to vectorize these applications in an efficient way. We also want to know which will be the micro-architectural requirements for implementing such a vector ISA and estimate the execution time of vectorized applications.

Some of these questions are addressed by Espasa [15, 40] using traces from vectorized CONVEX binaries and simulating them. Currently we do not have access to any compiler that performs automatic vectorization of our target applications. To overcome this problem, in this project we have chosen to develop a vector library and a model for execution time that addresses the issues mentioned above.

### 1.2 Project Objectives

The main goals of the project are:

- To develop a vector library that implements a vector ISA similar to VMIPS<sup>1</sup> [20]. The vector library will also contain some additional instructions that are useful or required to vectorize our target applications. The vector library will be parameterizable: size of vector register file, register length, etc. The library will collect results and statistics at runtime from vectorized applications. It will also provide support to generate instruction and address traces of the vectorized applications to allow further analysis (e.g. a model for execution time). The vector library will also provide support to allow the vectorization of applications written in C, C++ and FORTRAN.

- To choose several modern applications that can be used in handheld devices or data centers, profile them and vectorize them by hand if they are suitable for vectorization. Another sub-goal is to generate statistics that will provide information about instruction level characterization of these applications. These statistics will be generated through traces that will feed the model for execution time.

- To develop a trace-driven model for execution time (ETModel), motivated by work presented by Karkhanis & Smith [23] and Hennessy & Patterson [20]. The model will be parameterizable (e.g. number of lanes, number of ALU units, LD/ST units, start-up latencies, memory bandwidth, etc.).

<sup>&</sup>lt;sup>1</sup>RISC-like a vector ISA and register based

• To analyze the results. Gathered results and statistics will be used to analyze the micro-architectural requirements to implement the proposed vector ISA. In particular, we wish to study the impact of the parameters of the model on an application's execution time.

## 1.3 Project Objectives

The following table summarizes the distribution of the time used to develop the different activities in this project.

| # | Activity                            | Time (hours) |

|---|-------------------------------------|--------------|

| 1 | Vector library implementation.      | 240          |

| 2 | Benchmark vectorization.            | 320          |

| 3 | ETModel implementation and testing. | 200          |

| 4 | Results collecting.                 | 120          |

| 5 | Results analyzing.                  | 40           |

| 6 | Final report.                       | 100          |

|   | Total                               | 1020         |

Table 1.1: Project roadmap activities.

## Chapter 2

## Vector Processors

This chapter presents vector processors in general, the advantages of vector processors and vector instruction set architecture (ISA), reviews existing implementations and gives definitions of some terms used in the rest of the thesis. Patterson & Hennessy [20] gives more details about vector processors as well as Asanovic [3].

Various forms of parallelism have been exploited in computer architecture to provide increases in performance. The three major categories are: **instruction-level parallelism** (ILP), **thread-level parallelism** (TLP) and **data-level parallelism** (DLP). ILP allows simultaneous execution of multiple instructions from one instruction stream (superscalar processors). TLP allows simultaneous execution of multiple instruction streams (Simultaneous Multi Threading - SMT). DLP allows simultaneous execution of the same operations on arrays of elements (Single Instruction Multiple Data - SIMD).

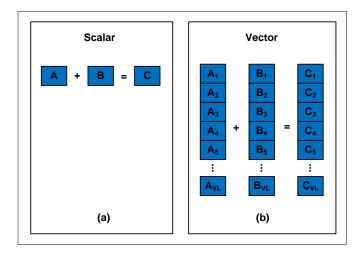

A vector processor implements a type of data-level parallelism. Vector processors typically contain vector registers that hold multiple values instead of single-value registers as in super-scalar processors. They provide vector instructions that operate on all values of the registers, in conceptually simultaneous manner. For example, a scalar addition instruction would take values from two scalar registers A and B, and produce a result stored in scalar register C, as figure 2.1 (a) shows. A vector addition instruction would take two vectors A and B, and produce a resulting vector C, as in figure 2.1 (b), where VL is vector length.

Figure 2.1: Comparison of a scalar instruction and a vector instruction.

## 2.1 Advantages of Vector Processors

As it is emphasized in previous work [3, 20, 22], vector processors and vector ISAs have several advantages:

- A single vector instruction specifies N operations, where N represents tens or hundreds of operations. It dramatically reduces instruction fetch bandwidth, which is a bottleneck of conventional processors, particularly in terms of power consumption [29, 42].

- These N operations are independent. There is no need for checking data hazards within a vector instruction. It allows simultaneously execution of all operations in an array of parallel functional units, or in a single very deeply pipelined functional unit, or in any intermediate configuration of parallel and pipelined functional units.

- Reduced control logic complexity. Hardware needs only check for data

hazards between two vector instructions once per vector operand, not once

for every element within the vectors. Therefore, the dependency checking

logic required between two vector instructions is approximately the same as

that required between two scalar instructions, but now many more elemental

operations can be in flight.

#### 2. VECTOR PROCESSORS 2.2 Relevant techniques and concepts

- Vector instructions that access memory have a known access pattern. A

memory system can implement important optimizations if it has accurate

information on the address stream. In particular, a stream of unit-stride

accesses can be performed very efficiently using large block transfer. Also

in case main memory accessed, the high latency of initiating access versus

accessing a cache is amortized, because a single access is initiated for entire

vector rather than to a single word.

- Reduced control hazards from loops, because an entire loop can be replaced by a vector instruction whose behaviour is predetermined.

### 2.2 Relevant techniques and concepts

In this section, we describe techniques and concepts that have been used in vector architectures, relevant for this thesis.

#### 2.2.1 Chaining

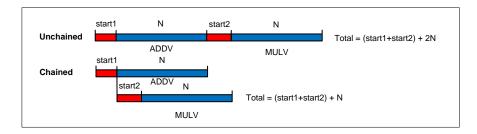

Some vector architectures have to complete a vector instruction before starting the next vector instruction. Chaining is a technique that allows overlapped execution of two dependent instructions. It means that next vector instruction can start execution before current vector instruction is completed. Consider the simple vector sequence:

```

addv R1, R2, R3 mulv R4, R1, R5

```

We want to add vector registers R2 and R3 and to store results into vector register R1. After that, we multiply vector registers R1 and R5 and store result into vector register R4. Figure 2.2 shows the timing of chained and an unchained version of the above pair of vector instructions with a vector length of N. In an unchained version two vector instructions are computed serially. We have the start-up time to compute the first element in the first vector instruction and then n cycles to compute the whole vector and then the same for second vector instruction. In a chained version, second vector starts execution when the first

#### 2. VECTOR PROCESSORS 2.2 Relevant techniques and concepts

element in the first vector instruction is computed. Generally, chaining allows a vector operation to start as soon as the individual elements of its vector source operand become available.

Figure 2.2: Timings for a sequence of dependent vector instructions ADDV and MULV, both unchained and chained.

It is obvious that chaining plays an important role in boosting vector performance. In fact, chaining is so important that every modern vector processor supports chaining [20].

#### 2.2.2 Multiple Lanes

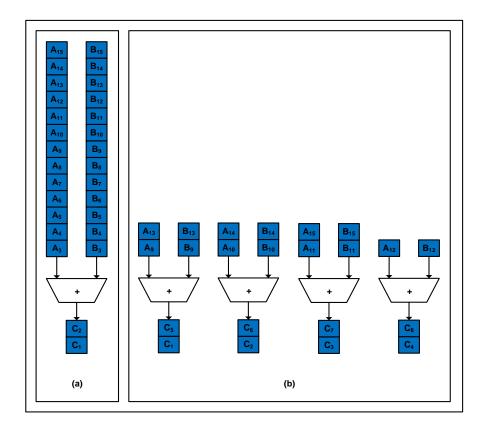

As mentioned above, a vector instruction specifies a number of independent operations that can be executed in parallel. This semantics of a vector instruction allows using an array of parallel functional units, or a single very deeply pipelined functional unit, or any intermediate configuration of parallel and pipelined functional units. Vector performance can be improved by using parallel and pipelined units. For example, figure 2.3 (a) shows a vector unit that has a single pipeline and can complete one addition per cycle. The figure 2.3 (b) shows a vector unit that has four add pipelines and can complete four additions per cycle. The elements within a single vector add instruction are interleaved across the four pipelines.

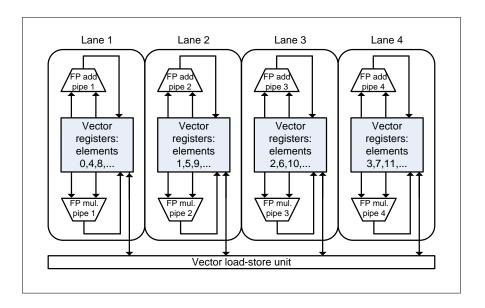

The construction of parallel vector unit is simple because all vector arithmetic instructions only allow element N of one vector register to take part in operations with element N from other vector registers. Parallel vector unit can be structured as multiple parallel *lanes*. Patterson and Hennessey [20] give one example of a four lane vector unit (figure 2.4). The vector-register storage is divided across

Figure 2.3: Using multiple functional units to improve performance of a single vector add instruction, C = A + B.

the lanes, with each lane holding every fourth element of each vector register. There are three vector functional units shown, an FP add, an FP multiply, and a load-store unit. Each of the vector arithmetic units contains four execution pipelines, one per lane, that act in concern to complete a single vector instruction. Implementation of instructions that require communication across lanes is more complex.

### 2.2.3 Death time or recovery time

Adding multiple lanes increases performance, but still there are start-up overhead and power consumption concerns. It is possible to reduce start-up overhead allowing the start of one instruction to be overlapped with the completion of preceding vector instructions. It increases the complexity of control logic and

Figure 2.4: Structure of a vector unit containing four lanes.

some vector machines require some recovery time or death time in between two vector instructions dispatched to the same vector unit.

#### 2.2.4 Masking

Programs that contain conditional (if) statements cannot be vectorized using the basic memory, arithmetic and logical instructions which are sufficient for vectorizing many straight-line loops. Consider the following loop:

```

for( i = 1, i <= looplen, i++){

if (a[i] == b[i])

c[i] = a[i] + b[i];

}</pre>

```

This code cannot normally be vectorized because of the conditional execution of the body. J. E. Smith et al [37] examined a number of vector instruction set alternatives for implementing conditional loops. The paper concludes that "the best approach is to use masked instructions. Masked instruction uses a Boolean vector of maximum vector length (MVL) to control the execution of a vector instruction just as conditionally executed instructions use a Boolean condition to determine whether an instruction is executed. When the vector-mask register

is enabled, any vector instructions executed operate only on the vector elements whose corresponding entries in the vector-mask register are 1".

Masking allows higher level of vectorization and it is critical in achieving the large difference between vector and scalar mode [20].

### 2.3 Existing implementations

Vector processors have a long and successful history in supercomputers where they are used for large scientific and engineering applications. The first vector architecture were memory based with instructions that operate on memory-resident vectors [21, 41]. Cray [35], register-based vector machines were the first commercially successful supercomputers [15]. They provide arithmetic instructions that operate on vector registers, while separate vector load and store instructions move data between vector registers and memory. Several modest mini-supercomputers [32, 33] were released in the mid 80s.

Vector processors have found their place in microprocessors. Vector microprocessors have been constructed to support vector instructions [4, 31]. Torrent-0 and IRAM are an example of vector microprocessors developed as part of academic research. Espasa et al [16] developed Tarantula, a vector extension to the Alpha architecture.

Vector extensions, such as MAX[26], MMX[30], SSE[39], AVX[9], AltiVec[19], 3DNow![28], etc., are very popular in desktop processors of all of the major vendors. These vector extensions do not implement all traditional vector instructions and operate on much shorter vectors (4-8 elements) than in old vector architectures because one of goals is to minimize additional chip area.

Vector processors are also used in special purpose hardware such as video cards and game consoles. One of example is the Sony Playstation II [38].

"Knight's Corner" is an upcoming massively parallel x86 microprocessor designed by Intel Corporation. It is based on the cancelled Larrabee [36] GPU that contains a 512-bit vector processing unit in each core, able to process 16 single precision floating point numbers at a time.

#### 2. VECTOR PROCESSORS

Vector register architecture has several advantages over memory-memory architectures [3]. A vector register architecture reduces temporary storage requirements, memory bandwidth, and inter-instruction latency compared to vector memory-memory architecture because vector register architectures can keep intermediate results while memory-memory architecture has to write all intermediate results to memory and then must read them back from memory. Also if the result of a vector instruction is needed by multiple other vector instructions, a memory-memory architecture must read it from memory multiple times, whereas a vector machine can reuse the value from vector registers, further reducing memory bandwidth requirements. For these reasons, vector register machines have proven more effective in practice. In the rest of this thesis, I restrict the discussion to vector register architectures.

## Chapter 3

## Vector library

One of the objectives in this thesis is designing and implementing a vector library that will help us to vectorize and analyse target applications. The vector library is implemented in C++ and has the following features:

- It collects results and statistics at runtime from the vectorized application.

- It implements a configurable vector register file.

- It implements vector ISA similar to VMIPS [20] plus extensions.

- It generates instruction and address traces of the vectorized application, that enable further analysis.

- Provides wrapper functions for applications written in C and FORTRAN.

### 3.1 Configurable vector register file

The vector library implements a configurable vector register file. The number of vector registers and the maximum number of elements per vector register are parameters of the vector library. This allows us to use different configuration of the vector register file and to specify different maximum vector lengths (MVL) of the vector register.

Each register holds a set of values and they can be one of several data types:

- signed or unsigned integer (16, 32 and 64 bits),

- double (floating-point double precision: 64 bits),

- float (floating-point single precision: 32 bits) or

- char (8 bits).

#### 3.2 Vector ISA

The vector library implements a vector ISA similar to VMIPS [20]. Most instructions are RISC-like and register-based. The implemented vector ISA consists of:

- arithmetic and logical instructions,

- memory instructions,

- reduction instructions and

- bit and element manipulation instructions.

Most implemented instructions are usually found in any register-based vector ISA, but there are some not so common instructions that are useful or required to vectorize our target applications. Following subsections give more details.

Tables 3.1 and 3.2 show the vector instructions implemented in the vector library. The first column contains the type of instruction. The second column is the opcode of instruction. Arithmetic and logical instructions have suffix S in opcode (sixth column gives information if a particular arithmetic or logical vector instruction supports vector-scalar mode) if one operand is scalar, or suffix MASK if it is executed over vector mask register, or SMASK if one of the operands is scalar and it is executed over vector register. Third and fourth columns give information related with source and destination vector registers used by vector instruction. Fifth column contains information related with vector mask register. If an instruction contains x in masking column, it means that there are an available instruction that can be executed over the vector mask register (arithmetic

Figure 3.1: Two modes of vector instruction: (a) vector-vector and (b) vector-scalar.

and logical and memory instructions) or one operand is a vector mask register (bit and element manipulation instructions). Availability of an instruction with scalar operand is displayed in the sixth column. The last column contains a short description of the implemented vector instruction.

### 3.2.1 Arithmetic and Logic Instructions

The vector library implements all common arithmetic and logic instructions such as addition, multiplication, subtraction, logical bitwise operations, etc. Instructions can operate in vector-vector or vector-scalar mode. In vector-vector mode, an arithmetic or logic instruction has two vector source registers and performs arithmetic or logic operations on all elements of vector in a pairwise fashion, as figure 3.1 (a) shows. In vector-scalar mode, an arithmetic or logic instruction has one vector source register and one scalar source value and performs arithmetic or logic operations between all elements of vector register and scalar value, as is

shown in figure 3.1 (b).

The vector library also supports masking. It means that implemented arithmetic or logic instructions can be optionally executed over vector mask register (see Section 2.2.4).

#### 3.2.2 Memory Instructions

Common vector memory instructions such as unit-stride and strided memory instructions as well as indexed memory instructions (scatter and gather) are implemented in the vector library. In unit-stride memory access, consecutive elements are accessed, as in figure 3.2 (a). In strided memory accesses, elements are accessed with a constant stride, as is shown in figure 3.2 (b). With indexed memory access elements accessed randomly using there indices stored in the vector register, as figure 3.2 (c) shows.

Some of these instructions are implemented with support for masking. These instructions are useful in kernels where we have to store or load some elements of a stream depending on some condition. For example, in code below we store only those elements from array b to array c if the corresponding element in array a is greater than constant value con.

```

for( i = 1, i <= looplen, i++){

if (a[i] > con)

c[i] = b[i];

}

```

If we have memory instructions with support for masking, the code above is vectorized in the following way:

```

ldv VR1, a // load from array a to // vector register VR1 cmpvsqt VMR, R1, con // compare vector register VR1 and // scalar value con; store results // in vector mask register VMR ldvmask VR2, b, VMR // load over VMR from array b // and store to VR2 stvmask VR2, c, VMR // store to array c from VR2 over VMR

```

The example above clearly show the importance of memory instructions with support for masking.

Figure 3.2: Different types of memory instructions: (a) unit-stride, (b) strided, and (c) indexed.

The vector library also implements uncommon memory shape instructions, similar to the one introduced by RSVP [13]. The vector is described by the address of the first element and three scalar values: *stride*, *span* and *skip*. Stride describes the spacing between each loaded/stored element (inclusive of element). Span describes how many elements to access at stride spacing before applying the second-level skip offset. For example, we want to load four elements from the first row, but only every second element (Figure 3.3), then do the same for the second row, etc. Using memory shape load instruction with stride equal 2, span equal 4 and skip equal 3 we can load elements with only one memory instruction.

Memory shape instructions allow vectorization of previously non-vectorized kernels or to increase average vector length of vectorized applications (see Chapter 5) and decrease the number of vector instructions used to vectorize some kernels.

#### 3.2.3 Reduction Instructions

Reductions (such as sum) are often not available in some architectures. The library provides supports for:

- Sum computes the sum of all elements in a vector register.

- Max finds maximum element in a vector register.

Figure 3.3: An example of vector memory shape instructions where red elements are loaded from matrix.

• Min - finds minimum element in a vector register.

The library also implements new reduction instruction called *sub-reduction* add or *sub-sum*. This instruction performs the sum for sub-sets in a vector register. For example, we want to sum group of 3 elements of an array, the first 3 elements, then next 3, etc. We can do it with the existing sum instruction, but we will have short vectors and several load instructions, as figure 3.4 (a) illustrates. Using sub-sum, we just need two instructions instead: one to load the vector and for another to perform sub-reduction, as it is shown in figure 3.4 (b). With this approach, the number of vector instructions is decreased and the average vector length is increased.

Figure 3.4: An example of performing sum for sub-sets of array using: (a) reduction instruction sum and (b) new reduction instruction sub-sum.

### 3.2.4 Bit and element manipulation instructions

Standard bitwise instructions such as OR, AND, etc. are implemented in the vector library. The library also provides instructions that manipulate individual elements of vector registers such as getelem, setelem, select, init, etc. Getelem gets a particular element from the specified source register, while setelem sets a particular element of vector destination register with specified scalar value. Select instruction is related with masking (see Section 2.2.4) and selects elements from one or other source depending on the value in vector mask register. Init or iota has two operands, base and stride, and creates the following array:

base +

$$j*$$

stride, where  $j = 0, 1, 2...$  vl-1.

| type       | opcode     | source regs | dest reg    | masking | scalar | description                                           |

|------------|------------|-------------|-------------|---------|--------|-------------------------------------------------------|

|            | ADDV       | 2           | 1           | X       | X      | V-V or V-S addition optionally over VMR.              |

| Arithmetic | SUBV       | 2           | -           | ×       | ×      | V-V or V-S subtraction optionally over VMR.           |

|            | MULV       | 2           |             | ×       | ×      | V-V or V-S multiplication optionally over VMR.        |

|            | DIVV       | 2           | $\vdash$    |         | ×      | V-V or V-S division.                                  |

| and        | VMOD       | 1           | <b>←</b>    |         | ×      | Modulo instruction.                                   |

|            | LOGOPV     | 2           | <b>⊢</b>    |         | ×      | V-V or V-S logical instructions.                      |

|            | CMPV       | 2           |             | ×       | ×      | V-V or V-S compare instructions.                      |

| Logical    | CMPVMR     |             |             | ×       |        | Compare instructions use VMR registers as sources.    |

|            | LD         |             |             |         |        | Memory load vector instruction.                       |

|            | LDCAST     |             | <del></del> |         |        | Memory load vector instruction with cast.             |

|            | A          | 1           |             | ×       |        | Memory store vector instruction, optionally over VMR. |

|            | LDVS       |             | $\vdash$    |         | ×      | Strided memory load vector instruction.               |

| Memory     | STVS       | 1           |             |         | ×      | Strided memory store vector instruction.              |

|            | LDVGI      | 1           | <b>—</b>    | ×       |        | Indexed memory load vector instruction,               |

|            |            |             |             |         |        | optionally over VMR.                                  |

|            | STVGI      | 2           |             |         |        | Indexed memory load vector instruction.               |

|            | LDVSHAPE   |             |             |         | ×      | Memory load vector instruction with shape.            |

|            | STVSHAPE   | 1           |             |         | ×      | Memory store vector instruction with shape.           |

|            | VREDADD    | 1           |             |         | X      | Reduction sum instruction.                            |

| Dodugtion  | VSUBREDADD | 1           |             |         |        | Sub-reduction sum instruction.                        |

| reduction  | VREDMIN    | П           |             |         | ×      | Find minimum instruction.                             |

|            | VREDMAX    | 1           |             |         | X      | Find maximum instruction.                             |

Table 3.1: Implemented vector arithemetic, logical, memory and reduction instructions in the vector library. V-V is vector-vector, while V-S is vector-scalar.

| type         | opcode      | source regs | dest reg | masking | scalar | description                                              |

|--------------|-------------|-------------|----------|---------|--------|----------------------------------------------------------|

|              | VSHIFT      | 1           | 1        |         | ×      | Vector shift instruction.                                |

|              | VINIT       |             | 1        |         | ×      | Vector initialization instruction.                       |

|              | VSETS       | 1           |          |         | ×      | Sets all elements of vector to value from scalar.        |

|              | BITSCANP    |             |          | ×       | ×      | finds position of first set bit in VMR.                  |

|              | BITSCANN    |             |          | ×       | ×      | finds position of first zero bit in VMR.                 |

| Bit          | SELECTV     | 2           | 1        | ×       | ×      | Vector-vector or vector-scaler select instruction.       |

|              | BWOPV       | 2           | 1        |         | ×      | Vector-vector or vector-scaler bitwise instructions.     |

|              | CASTV       | 1           |          |         |        | Vector cast instruction.                                 |

|              | GETELEM     | 1           |          |         | ×      | Get element from vector register.                        |

|              | SETELEM     |             | П        |         | ×      | Set element to vector register.                          |

|              | VREPLICATE  | П           | 1        |         | ×      | Replicate vector coresponding number of times.           |

| and          | INSERTVM    | 1           | 1        | ×       | ×      | Copy the content of a vector mask register               |

|              |             |             |          |         |        | as one or more elements of a vector register.            |

|              | BITSCANV    | 1           | 1        |         |        | Generate indexes of all bits sets in a vector register.  |

|              | BITSCANVVM  |             | 1        | ×       |        | Generate indexes of all bits sets in a VMR.              |

|              | BITSETVVM   | 1           | 1        | ×       |        | Set bits indicated by an index VMR.                      |

|              | POPCOUNTVM  |             |          | ×       | ×      | Count the number of set bits in a VMR.                   |

| Element      | POPCOUNTV   | 1           |          |         | ×      | Count the total number of set bits in a vector register. |

|              | POPCOUNTVV  | П           | 1        |         |        | Count the number of set bits in                          |

|              |             |             |          |         |        | a vector register (per element).                         |

|              | POPCOUNTVVM | 1           |          | ×       |        | Count the number of bits set up to a each position       |

|              |             |             |          |         |        | in a vector mask.                                        |

|              | BITCLEARV   | 1           |          |         |        | Clear the bits in a vector register as indicated         |

| Manipulation |             |             |          |         |        | by an index vector.                                      |

|              | BITCOMPRESS | 2           | 1        |         |        | Copy the bits of source vector register 1 according to   |

|              |             |             |          |         |        | the set bits of source vector register 2. Copied bits    |

|              |             |             |          |         |        | are stored consecutively in destination vector register. |

|              | COMPRESS    | 1           |          | ×       |        | Copy the elements of source vector register according    |

|              |             |             |          |         |        | to the set bits of vector mask. Copied elements          |

|              |             |             |          |         |        | are stored consecutively in destination vector register. |

Table 3.2: Implemented vector bit and element manipulation instructions in the vector library.

#### 3.3 Results and Statistics

One of the purposes of the vector library is to generate results and statistics from vectorized applications. The library collects following statistics:

- Percentage of vectorized code. It tells us what is the degree of vectorization in an application; number of operations executed in the vectorized code and the number of operations executed in scalar code. The PAPI library [7] is used to count the number of instructions executed in the scalar code (for more details see Section 3.6).

- Instruction type statistics. It gives us information about distribution of the vector instructions; how many times each instruction is executed and how many operations are executed per vector instruction.

- Distribution of vector lengths. This information tells us how many instructions are executed for every vector length up to maximum vector length and helps to determine the utilization of the vector register file.

- Algorithmic vector lengths. Lengths of arrays (vectors) in algorithms are sometimes longer than the maximum vector length. The library collects these statistics optionally and it is done manually during the process of vectorization.

- Stride distribution information. It tell us how many memory instructions are executed with the corresponding stride and it helps to determine the dominant memory access patterns.

- Information related with the vector mask registers. The vector library supports masking and also collects statistics related with masking. It tells us how many instructions and operations are executed over a vector mask register and how many operations are really executed (operations for which bit in the vector mask register was set).

If more information needs to be harvested, the vector library can be easily extended to collect desired statistics.

#### 3.4 Instruction and address traces

The library has the support to generate a trace of executed vector instructions as well as a trace of addresses for each memory vector instruction. The traces are used as inputs in the ETModel to estimate the execution time of the vectorized application (see Chapter 4). The traces can be generated in binary format, textual or both.

The instruction trace has the following format:

```

[Num_of_scalar_ins] [Set_VL] Block_of_vector_ins

```

$Num\_of\_scalar\_ins$  is the number of scalar instructions between two blocks of vector instructions;  $Set\_VL$  is the vector length used in the following block of vector instructions; and  $Block\_of\_vector\_ins$  is a block of vector instructions. Each instruction in the block is represented by the *instruction opcode*, *destination* and *source registers* with their types. The PAPI library is used to automatically count the number of scalar instructions between two blocks of vector instructions.

Square brackets mean that  $num\_of\_scalar\_ins$  and  $set\_VL$  are optional. Sometimes there are no scalar instructions between two blocks of vector instructions, they are just executed with different vector lengths or two blocks are executed with the same vector length and between them there is some scalar code.

In order to reduce the size of the address trace, it does not always contain the addresses of all locations in memory accessed by a vector memory instruction. In general, it contains information that are sources of the memory instructions: opcode, type of accessed data, base address, number of accessed elements, etc. Different types of vector memory instructions have different formats.

Unit-stride vector memory instruction has the following format:

```

opcode type start_address num_elems

```

where *opcode* identifies particular instruction which accesses *num\_elems* elements of type *type* starting from address *start\_address*. These four parameters are enough to generate addresses of all elements accessed by an unit-stride vector memory instruction.

Strided vector memory instruction needs a small addition to the format of unit-stride vector memory instruction:

```

opcode type start_address num_elems stride

```

where *stride* is the distance between two accessed elements. Again this is enough to generate all addresses for strided vector memory instructions.

Vector memory shape instructions need more information than unit-stride or strided vector memory instructions. The format is following:

```

opcode type start_addr num_elems stride 1st_span span skip

```

where opcode identifies particular instruction which loads-stores num\_elems elements of type type starting from address start\_addr. Stride describes the spacing between each accessed element. Span describes how many elements to accessed at stride spacing before applying the second-level skip offset. 1st\_span is related with strip-mining (see section 5.1). Sometimes a memory shape instruction does not access all elements in first span group, because some number of elements were accessed in previous stripe of strip-mined loop. This is the reason for adding 1st\_span into the address trace for vector memory shape instructions.

The most problematic instructions are indexed and instructions executed over a vector mask register. For an indexed vector memory instruction the address trace contains the indices of all accessed elements and the base address:

```

opcode type start_address num_elems array_of_indices

```

For vector memory instruction executed over vector a mask register, the trace contains only those addresses for which the corresponding bit in the vector mask register is set:

```

opcode type start_address num_elems array_of_accessed_addr

```

### 3.5 Wrappers

Some benchmarks were written in C or FORTRAN. The library contains wrapper functions that allow vectorization of applications written in FORTRAN and C.

### 3.6 Implementation details

Most code in the library is implemented in C++ using templates. Templates are very well suited for our implementation because vector registers and implemented

vector instructions have to support different data types. Several optimization techniques such as in-lining, macros, etc. are applied. It allow us to have compact and optimized code.

As mentioned above, the PAPI library is used to count scalar instructions between blocks of vector instructions. The idea is to count operations between calls to functions of the vector library that simulate vector instructions. If there are two consecutive function calls to the vector library without scalar code between them, the PAPI library should still count some number of operations, which is overhead of calling functions of the vector library. After some experiments, we set a fixed threshold that is used to determine if two vector instructions are from the same block or the obtained number of operations using PAPI represents scalar code between two blocks of vector instructions. The threshold is highly dependent on the host ISA and compiler.

We used Dell sever with four cores as evaluation environment for generating instruction traces and collecting statistics. Each core is Xeon Dual-Core 5160 @ 3.00GHz with 4MB of cache and 16GB of RAM. All applications were compiled with gcc compiler (version 4.4.3), except the FaceRec which was compiled with icc compiler (version 12.0.2).

-O3 optimization flag is used for all applications, except for the FaceRec. -xSSE3 -fast -no-scalar-rep -unroll1 optimizations flags are used for the FaceRec.

The overhead of the vector library to the original application's execution time depends on the mode in which the library is run. The basic version of vector library just collects results for the instruction level characterization. It can count the scalar operations using the PAPI library and generate instruction and address traces.

For example, the execution time of the original version of the Sphinx3 is sixteen minutes. The basic version is less than four times slower than the original version. The version than counts the scalar operations is 200 times slower because the PAPI library adds a lot of overhead. The version that collects instruction trace is 400 times slower because it has to write trace into a named pipe, while the second process compresses that named pipe.

The vector library adds a lot overhead, but still it is less than a simulator.

## Chapter 4

## **ETModel**

The target applications can be vectorized using the vector library and statistics such as instruction level characterisation can be obtained but there is no information related with execution time on a vector architecture. Detailed simulators are very often used to evaluate performance of a processor. Although it is accurate, this method is time-consuming, both to create the simulator and to run the simulations. Our idea was to have fast results and to a perform preliminary evaluation and early parameter exploration.

The ETModel is a simple trace-driven simulator for vector processors based on the work presented by Karkhanis & Smith [23] and Hennessy & Patterson [20]. Karkhanis & Smith [23] propose analytical performance model for superscalar processors, while Hennessy & Patterson [20] describe basic vector architecture as well as techniques and concepts that help in enhancing vector performance. The model consists of a component that models the micro-architecture of the desired vector processor and methods that apply chaining and other implementation features as described in section 2.2. The model uses an instruction trace, optionally an address trace and IPC of scalar code as inputs to estimate execution time of the vectorized application. Instruction and address traces are generated by the vectorized application using the vector library (see Section 3.4).

#### 4.1 Micro-Architecture

The ETModel models a parametrizable in-order vector architecture similar to the architecture presented in [20]. It consists of basic units such as a vector register file, ALU units, vector load/store units and a memory hierarchy (figure 4.1). The model is parametrizable because we can specify how many instances of any unit are available in the model (e.g. number of lanes, number of ALUs, LD/ST units, etc.). All units are also parametrizable:

- Number of vector registers and size of vector register for the vector register file.

- Types of instructions and types of data that each ALU unit supports (e.g. FP multiply unit, logical unit, etc.).

- Types of memory instructions that each vector load/store unit support.

Memory can be modeled in two different ways: simple and detailed. In the simple approach, the memory is simply modeled with parameters such as cache miss rates, bandwidths and latencies for each type of memory instruction. L1 and L2 cache misses are uniformly modeled using cache miss rates. For example if L1 cache miss rate is 10%, every tenth access to L1 cache will be modeled as miss. This approach is fast but has low accuracy.

In the second approach, a more accurate memory model is used. A trace of addresses of vector memory instructions is generated by vector library and a simple cache simulator is implemented based on the memory model of SimpleScalar [8]. For each vector memory instruction from the instruction trace, the address trace contains all necessary information to generate all accessed addresses.

In both memory models, different types of vector memory instructions are modeled separately. For the unit-stride memory instruction, we can load/store a whole L1 cache line with only one access, while for all other types, only one element per access is loaded/stored.

All the parameters mentioned above help us to analyse a broad range of different configurations of vector processors ranging from very simple vector processors with only one lane, one vector load/store unit and a small number of functional

Figure 4.1: The basic structure of model register-based vector architecture.

units, to very complex vector processor with multiple lanes, several vector load-/store units and a rich set of functional units.

Beside the concept of multiple lanes, other important techniques such as chaining and pipelined instruction start-up (dead time or recovery time) are also included into the model.

The ETModel also provides detailed statistics of the resource usage. For the cache hierarchy, the ETModel collects the following:

- Total number of L1 accesses, the number of L1 miss (miss rate) and hit (hit rate) accesses.

- Total number of L2 accesses, the number of L2 miss (miss rate) and hit (hit rate) accesses.

- Total number of cycles spent in the memory hierarchy.

- Average memory access time per access.

- The number of L1 accesses per memory unit.

For every functional unit, there is information about its usage; the number of the cycles that particular functional unit was busy. There is also information about dependent vector instructions: the number of vector instructions executed using chaining or without chaining, as well as the number of cycles waiting for a free ALU or memory unit. The distribution of data types (see section 5.3.4) was collected using the ETModel.

All these statistics help us to better understand the obtained results and the behavior of the vectorized applications.

## 4.2 Top-Level Model

For reasoning about vector processor operation, we utilized vector execution time and enhancing vector performance models from [20] to create the algorithm of execution in ETModel as shown in figure 4.2. The model reads the instruction trace sequentially. Each opcode is loaded from the instruction trace and fit as one of three possibilities:

- 1. The number of scalar instructions between two blocks of vector instructions.

The execution time for these scalar instructions is computed using the input parameter scalar IPC (number of scalar instructions divided by IPC). We assume that there is no overlapping between scalar and vector instructions.

- 2. A set vector length instruction.

The VL register is set for following vector instructions.

3. A vector instruction.

First, operands and type of operands are read from the instruction trace file. After that, the model checks if it is a memory or arithmetic/logic

### 4. ETMODEL

instruction. In both cases, the model tries to find a free vector load/store or ALU unit. If there isn't a free unit, memory or arithmetic/logic instruction waits for the first free load/store or ALU unit. Finally, when memory or arithmetic/logic instruction finds free load/store or ALU unit it checks for dependency and if there is no dependency the memory or arithmetic/logic instruction is issued. Otherwise, the model checks for chaining and if it is possible it issues chained memory or arithmetic/logic instruction. If it is not possible, the memory or arithmetic/logic instruction is issued in non-chained mode. It means that current instruction will be issued when the previous instruction, from which the current instruction depends, is finished.

Figure 4.2: Diagram of algorithm used to compute execution time in the ET-Model.

# Chapter 5

# Vectorization

Our target applications are chosen from a range of applications that are used or will be used in handheld devices or data centers. This range includes computer vision, speech recognition, face recognition, 3D graphics and video media, console games, database management systems, etc. Asanovic et al. [5, 6] identify 13 "dwarfs", which each capture a pattern of computation and communication common to a class of important applications. We also tried to cover several dwarfs choosing the applications that contain different dwarfs.

## 5.1 Methodology

The process of vectorization contains the following steps:

- Profiling. The goal of profiling is to find kernels that consume the most execution time. Applications are profiled using standard Unix profiler called gprof and/or using Intel's performance analyzer called VTune.

- Kernel testing on vectorization. Kernels that consume the most of execution time are examined for vectorization (e.g. does kernel contain loops, dependency, what is the size of loop, etc.), and if they are suitable for vectorization vectorized pseudo-code is written.

- Vectorization of kernels and applying strip-mining. The kernels are vectorized using functions from the vector library. The actual vector length

required by an algorithm (the number of iterations of a loop) is usually larger than maximum vector length (MVL) supported by the architecture and often unknown at compile time. Strip-mining is a technique that allows operating on "stripes" of the data of length less or equal to MVL. Strip-mining is applied in all vectorized kernels in order to support vectorization of loops that are longer than the size of vector register. It also allows changing the maximum size of vector register in the vector library without modification in the vectorized application. MVL is a parameter of the vector library that is set at compilation time.

- Collecting and analysing results. In this step, the vectorized application is run and statistics are collected. The percentage of vectorized code, average vector register length, etc. are analysed.

- Performing additional modifications of the vectorized code. If the collected results are not satisfying, additional code modifications are performed in order to improve the average vector length (longer vectors) or the percentage of vectorized code, if it's possible.

## 5.2 Vectorized applications

This section describes applications that have been vectorized. They are chosen from several areas such as speech recognition, face recognition, data-mining, graphical models and video compression. These applications also cover several dwarfs such as dense linear algebra, sparse linear algebra, graphical models and finite state machine.

## 5.2.1 SPEC2006 Sphinx3 benchmark

Sphinx3 is a widely known speech recognition system from Carnegie Mellon University. It includes both an acoustic trainer and various decoders, e.g., text recognition, phoneme recognition, N-best list generation, etc. Sphinx3 adopted the prevalent continuous hidden Markov acoustic model (HMM) representation

and has been used primarily for high-accuracy, non-real-time recognition. The benchmark is written in C.

## 5.2.2 SPEC2006 H264ref benchmark

H264ref is a reference implementation of H.264/AVC (Advanced Video Coding), the latest state-of-the-art video compression standard. The standard is developed by the VCEG (Video Coding Experts Group) of the ITU (International Telecommunications Union and the MPEG (Moving Pictures Experts Group) of the ISO/IEC (International Standardization Organization). This standard replaces the currently widely used MPEG-2 standard, and is being applied for applications such as the next-generation DVDs (Blu-ray and HD DVD) and video broadcasting. This benchmark is written in C.

#### 5.2.3 SPEC2006 Hmmer benchmark

Hmmer benchmark searches a gene sequence database. It applies profile Hidden Markov Models (profile HMMs), statistical models of multiple sequence alignments, which are used in computational biology to search for patterns in DNA sequences.

The technique is used to do sensitive database searching, using statistical descriptions of a sequence family's consensus. It is used for protein sequence analysis. It is written in C.

### 5.2.4 SPEC2000 FaceRec benchmark

This is an implementation of the face recognition system described in [24]. It is an object recognition system based on the Dynamic Link Architecture, which is an extension to classical Artificial Neural Networks. The benchmark is written in FORTRAN.

## 5.2.5 ECLAT MineBench

ECLAT is an application from the data-mining realm. In particular, it implements a known algorithm for frequent itemset mining. The original implementa-

tion was borrowed from NU-Minebench [27]. The most relevant operation consists in the intersection of large sparse sets. The Minebench implementation has been modified to use another data structure more suitable for vectorization, based on bitmaps. The benchmark is written in C++.

## 5.3 Vectorized kernels

The vectorization of some kernels is neither obvious nor trivial. It requires a lot of effort, deep understanding of kernels, sometimes algorithm modification or introducing new vector instructions. In this section, we explain the process of vectorization for some kernels that was not trivial.

In all vectorized kernels, the left-most operand is the destination register if an instruction has a destination operand. The letter R represents a vector register, while MV represents a vector mask register.

If a kernel contains a loop with a constant number of iterations during the execution of application, this number is included in the loop condition. In order to simplify the process of vectorization, we do not present strip-mining in the most kernels.

## 5.3.1 Sphinx3

The Sphinx3 application contains several kernels that are difficult to vectorize.

#### 5.3.1.1 Kernel 1. vector\_gautbl\_eval\_logs3

The source code of this kernel is shown above. This function takes 42.22% of execution time. As we can see the function contains two loops, the inner loop always has 13 iterations and the outer loop has 4,096 iterations for the ref data input set. In the outer loop, three vectors are loaded and in the inner loop it is performed some computation on all the elements in the vectors.

```

float32 *m, *v; // local variables

float64 dval, diff; // local variables

float32 *x, *score; // functions arguments

```

```

double f = log_to_logs3_factor();

for (r = 0; r < 4096; r++){

m = gautbl->mean[r];

v = gautbl->var[r];

dval = gautbl->lrd[r];

for (i = 0; i < 13; i++){

diff = x[i] - m[i];

dval -= diff * diff * v[i];

}

if (dval < gautbl->distfloor)

dval = gautbl->distfloor;

score[r] = (int)(f * dval)

}

```

The first and obvious approach is to vectorize the inner loop, but in that case, we will have very short vectors (length of thirteen) and reduction that is an expensive instruction. Our approach is to vectorize the outer loop and in this case, we will have vectors with length 4,096, but we will load them with a stride of 13. The code below is the pseudo code of vectorized version. We ignore strip-mining here.

```

ldv R1, gautbl->lrd

```

```

for (i = 0; i < 13; i++){

ldvs R2, gautbl->mean[i], 13;

subsv R3, R2, x[i];

mulv R4, R3, R3;

ldvs R5, gautbl->var[i], 13;

mulv R6, R4, R5;

subv R1, R1, R6;

}

cmpvs_gt MR1, R1, gautbl->distfloor;

selectvs R7, R1, gautbl->distfloor, MR1;

mulvs R8, R7, f;

```

```

castv_int32_db R9, R8;

stv R9, score;

```

## 5.3.1.2 Kernel 2. subvq\_mgau\_shortlist

In this kernel, the elements of the array map are used as indices to access elements from the array vqdist. A partial sum of the array vqdist is computed for groups of three elements. All the sums are stored in the array gauscore and the maximum of them is computed. Finally, for any element from array gauscore that is greater or equal to threshold th, its index is stored into the array sl.

```

int32 *vqdist;

int32 *map;

bv = MAX_NEG_INT32;

for (i=0; i<8; i++){}

v = vqdist[*(map++)];

v += vqdist[*(map++)];

v += vqdist[*(map++)];

gauscore[i] = v;

if (bv < v)

bv = v;

}

th = bv + beam; nc = 0;

for (i=0; i<8; i++){

if (gauscore[i] >= th)

sl[nc++] = 1;

}

sl[nc] = -1;

```

This kernel can be vectorized using reduction instructions, but the vector length will be very short (just three elements). In order to improve vector length, we introduced a new vector instruction called *subreduction* (see section 3.2.3) that performs the sum of sub-sets in a vector register. With this instruction, we can vectorize the kernel with a vector length of 24. The mnemonic used for this instruction is *vsubredadd*. The vectorized pseudo-code is shown below.

```

ldv R1, map;

ldvgi R2, R1, vqdist;

vsubredadd R3, R2, 3;

vredmax scalar, R3;

stv R3, gauscore;

th = scalar + beam;

cmpvs_ge MR1, R3, th;

vinit R4, 0, 1;

stvmask R4, MR1, vq->mgau_sl;

popcountvm temp, MR1;

sl[temp] = -1;

```

## 5.3.1.3 Kernel 3. mdef\_sseq2sen\_active

In this kernel, all elements of the array sswq are compared with zero in the outer loop. Then for all non-zero elements of the array sswq, their positions are used as indices to access an array of three elements from matrix mdef-sseq. After that the three elements of the array are used to index the array sen. All accessed elements of the array sen are set to one.

```

int16 *sp;

for (ss=0; ss<32639; ss++){

if (sswq[ss]){

sp = mdef->sseq[ss];

for (i=0; i<3; i++)

sen[sp[i]] = 1;

}

}</pre>

```

In this kernel, the inner loop can be vectorized easily, but vectors will be very short. We decided to vectorize the outer loop. We load elements from array sswq and compare with zero. We detected that this array contains a lot of zeros. This is the reason why we count how many elements are different from zero using the instruction popcountvm. If this number is equal to zero, we skip the rest of the computation. Otherwise, we vectorize the kernel as it is shown below. vinit

instruction creates index vector. The first element is i and every next element is incremented for three. We could use here a different approach: if the scalar value is lower than some threshold then execute the loop in scalar mode. To do it, we need some experimental results to choose the proper threshold.

```

vsets R0, 1;

ldv R1, sswq;

smpvs_ne MR1, R1, 0;

popcountvm MR1, scalar;

if (scalar != 0){

for (i = 0; i < 3; i++){

vinit R2, i, 3;

ldvgimask R3, R2, MR1, mdef->sseq[0];

stvsi R0, R3, sen;

}

}

```

## 5.3.1.4 Kernel 4. dict2pid\_comsenscr

In the kernel below, the elements of the array *comstate* are used as indices to access the array *senscr*. The inner loop is particularly interesting because we do not know the number of iterations until execution time. It uses the *break* keyword to exit the inner loop when it finds the first negative element in the array *comstate*.

```

int16 *comstate;

for (i=0; i<873; i++){

comstate = d2p->comstate[i];

best = senscr[comstate[0]];

for (j=0; ; j++){

k = comstate[j];

if (k < 0)

break;

if (best < senscr[k])</pre>

```

```

best = senscr[k];

}

comsenscr[i]=best+d2p->comwt[i];

}

```

We decided to vectorize this kernel in the following way. The code below presents a vectorized version of the kernel using strip-mining, because it is easier to understand. We load maximum vector length (MVL) elements from array comstate and compare if these elements are greater or equal to zero. Then we try to find the position of the first negative element in the vector (bitscann finds position of the first zero in the vector mask register). If this number is equal to MVL, we perform the computation on all elements. Otherwise, we perform the computation just on all positive elements until the first negative element. The pseudo-code below presents the vectorized kernel. We assume that the size of comstate is a multiple of MVL and all memory accesses would be valid. If it is not possible, we can check at the beginning if we have to use a smaller VL.

```

VL = MVL;

temp = VL;

for (i=0; i<873; i++) {

iter = 0;

temp = VL;

best = INT32_MIN;

while(temp == VL){

setvl VL;

ldv R1, (d2p->comstate[i] + iter * VL);

cmpvs_ge MR1, R1, 0;

bitscann temp, MR1;

if (temp != 0)

setvl(temp);

ldvgi R2, R1, senscr;

vredmax scalar, R2;

if (best < scalar)</pre>

best = scalar;

```

```

iter++;

}

comsenscr[i] = best + d2p->comwt[i];

}

```

## 5.3.1.5 Kernel 5. approx\_cont\_mgau\_frame\_eval

The code below is just a part of the kernel  $approx\_cont\_mgau\_frame\_eval$ . For all the elements of array  $sen\_active$  that are different from zero, best is subtracted to the corresponding elements in array senscr.

```

for (t = 0; t < 6144; t++) {

if(sen_active[s])

senscr[s]-=best;

}</pre>

```

The vectorized kernel is shown in the code below.

```

ldv R1, sen_active;

cmpvs_ne MR1, R1, 0;

ldv R2, senscr;

subvsmask R2, R2, R1, MR1;

stv R2, senscr;

```

## 5.3.2 FaceRec

The four most executed kernels for FaceRec application have been vectorized. In the first version of the vectorized code, the average vector length was very short. We spent a lot of time improving the average vector length.