# Design and Implementation of an Envelope Tracking Power Amplifier Using Switched Amplifiers and Slow Envelopes

Author: Pedro Vizarreta Advisors: Gabriel Montoro López Pere Gilabert Pinal

A thesis submitted in fulfillment of the Degree of Master of Science in Research of Information and Communication Technologies

Control Monitoring and Communications Group Department of Signal Theory and Communications UNIVERSIDAD POLITÉCNICA DE CATALUÑA

Barcelona, July 2011

To my beloved family and my adored girl

# Acknowledgment

This thesis was done at Universidad Politécnica de Cataluña and written under the cooperation project with the Spanish Ministry of Science and Innovation (MINCINN - *Ministerio español de Ciencia e Innovación*) and FEDER.

I would like to gratefully and sincerely thank to my academic advisors Gabriel Montoro and Pere Gilabert for their abundant help and their prolific suggestions during the development of this project.

Pedro Vizarreta, Barcelona 2011

# Abstract

This master thesis presents the design and implementation of an Envelope Tracking (ET) transmitter including an envelope amplifier based on switched power amplifiers and algorithms for slew-rate and bandwidth reduction. The ET transmitter here presented constitutes a research environment that will allow investigate possible solutions to solve the linearity-efficiency trade-off of the power amplifiers. The design and implementation of the envelope amplifier includes commercial switching devices driven by pulsed signals generated by a Field Programmable Gate Array (FPGA). The pulsed signals are modulated using Pulse Width Modulation (PWM) and Delta-Sigma Modulation ( $\Delta - \Sigma$  M) aimed to achieve a high efficient amplification. The signals, amplitudes, modulation frequencies and bandwidths used during the design and implementation are compatible with current communications standards.

This master thesis also presents a new algorithm for reduction of the envelope bandwidth as well as improvements over the existing slew-rate reduction algorithm presented in [1]. These improvements were implemented in the FPGA and validated in the implemented transmitter.

Results show that switching amplification is limited by the availability of current technologies in this field and the algorithms for reducing slew rate and bandwidth of the envelope are suitable to overcome this limitation while new technologies allow higher switching frequencies.

# Contents

| С  | over     |                                                                    | i       |  |  |  |  |

|----|----------|--------------------------------------------------------------------|---------|--|--|--|--|

| D  | edica    | tory                                                               | i       |  |  |  |  |

| A  | cknov    | vledgment                                                          | iii     |  |  |  |  |

| A  | Abstract |                                                                    |         |  |  |  |  |

| In | dex      |                                                                    | v       |  |  |  |  |

| Li | st of    | Figures                                                            | viii    |  |  |  |  |

| Li | st of    | Tables                                                             | xi      |  |  |  |  |

| Li | st of    | Appendices                                                         | xii     |  |  |  |  |

| AI | brev     | iations and notations                                              | xiv     |  |  |  |  |

| 1  | Intr     | oduction                                                           | 1       |  |  |  |  |

|    | 1.1      | Linearity-efficiency problem for PA in current communication stand | lards 2 |  |  |  |  |

|    | 1.2      | Contributions of this master thesis                                | 3       |  |  |  |  |

|    | 1.3      | Organization of this master thesis                                 | 4       |  |  |  |  |

| 2  | Stat     | te of the Art of Power Amplification Strategies for Wireless Com   | mu-     |  |  |  |  |

|    | nica     | tions                                                              | 5       |  |  |  |  |

|    | 2.1      | Power amplifiers                                                   | 5       |  |  |  |  |

|    |          | 2.1.1 Linear amplifiers                                            | 5       |  |  |  |  |

|    |          | 2.1.2 Non-linear amplifiers                                        | 8       |  |  |  |  |

|    | 2.2      | Dynamic supply for high efficient RF amplification                 | 9       |  |  |  |  |

|    |          | 2.2.1 Envelope Elimination and Restoration (EER)                   | 11      |  |  |  |  |

|    |          | 2.2.1.1 Issues and drawbacks                                       | 12      |  |  |  |  |

|    |          | 2.2.2 Envelope Tracking (ET)                                       | 15      |  |  |  |  |

|   |     |                        | 2.2.2.1 Issues and drawbacks                                    | 16 |

|---|-----|------------------------|-----------------------------------------------------------------|----|

|   | 2.3 | High                   | efficient envelope amplification                                | 17 |

|   |     | 2.3.1                  | Class G architecture                                            | 17 |

|   |     | 2.3.2                  | Class S amplifier                                               | 18 |

|   | 2.4 | Modu                   | lations for switched amplification                              | 19 |

|   |     | 2.4.1                  | Pulse Width Modulation (PWM)                                    | 19 |

|   |     | 2.4.2                  | Delta Sigma Modulation $(\Delta - \Sigma)$                      | 20 |

|   | 2.5 | Digita                 | al Pre-Distortion (DPD)                                         | 22 |

| 3 | Env | elope <sup>-</sup>     | Tracking design and implementation                              | 23 |

|   | 3.1 | Requi                  | red structure and technical details                             | 23 |

|   | 3.2 | Envir                  | onment description                                              | 24 |

|   | 3.3 | Slew-1                 | rate reduction algorithm                                        | 28 |

|   | 3.4 | $\operatorname{Pulse}$ | Width Modulator                                                 | 29 |

|   |     | 3.4.1                  | Implementation on the FPGA                                      | 29 |

|   |     | 3.4.2                  | Simulation results                                              | 30 |

|   | 3.5 | Delta                  | -Sigma Modulator                                                | 32 |

|   |     | 3.5.1                  | Implementation on the FPGA                                      | 32 |

|   |     | 3.5.2                  | Simulation results                                              | 33 |

|   | 3.6 | A nev                  | v algorithm for bandwidth reduction                             | 35 |

|   |     | 3.6.1                  | Mathematical formulation                                        | 37 |

|   |     | 3.6.2                  | Simulation results using Pulse Width Modulation                 | 42 |

|   |     | 3.6.3                  | Simulation results using Delta-Sigma Modulation                 | 43 |

|   | 3.7 | Modif                  | fications over the slew-rate reduction algorithm                | 44 |

|   |     | 3.7.1                  | Mathematical formulation                                        | 44 |

|   |     | 3.7.2                  | Implementation on the FPGA                                      | 46 |

|   |     | 3.7.3                  | Simulation results using Pulse Width Modulation and Delta Sigma |    |

|   |     |                        | Modulation                                                      | 47 |

|   | 3.8 | Swite                  | hing amplifier and filter design                                | 49 |

|   |     | 3.8.1                  | Switching amplifier selection                                   | 49 |

|   |     | 3.8.2                  | Filter design                                                   | 51 |

|   | 3.9 | Samp                   | ling I-Q components at IF and image spectrum suppression at RF  | 54 |

|   |     | 3.9.1                  | Mathematical formulation                                        | 55 |

|   |     | 3.9.2                  | Implementation on the FPGA                                      | 56 |

| 4 | Mea | asurem                 | ents and experimental results                                   | 58 |

|   | 4.1 | Testin                 | ng the image spectrum suppression at RF                         | 58 |

|   | 4.2 | Testin                 | ng the envelope amplifier                                       | 60 |

|   |     | 4.2.1                  | Implementation using Pulse Width Modulation                     | 60 |

|   |     | 4.2.2                  | Implementation using Delta-Sigma Modulator                      | 65 |

vi

|    | 4.3        | Experimental results employing the complete testbed | 67 |  |

|----|------------|-----------------------------------------------------|----|--|

| 5  | Con        | clusions and future work                            | 70 |  |

| Re | References |                                                     |    |  |

# List of Figures

| 2.1  | Class A amplifier                                                                          | 6              |

|------|--------------------------------------------------------------------------------------------|----------------|

| 2.2  | Class B amplifier                                                                          | $\overline{7}$ |

| 2.3  | Class AB amplifier                                                                         | 8              |

| 2.4  | Static and dynamic power supply                                                            | 10             |

| 2.5  | Envelope Elimination and Restoration (EER) transmitter architecture                        | 11             |

| 2.6  | Polar transmitter architecture                                                             | 12             |

| 2.7  | Bandwidth expansion phenomenon for a 16-QAM signal                                         | 14             |

| 2.8  | Envelope Tracking transmitter architecture                                                 | 15             |

| 2.9  | Pulse width modulator block diagram                                                        | 20             |

| 2.10 | First and second order delta-sigma modulators block diagram                                | 21             |

| 2.11 | Noise shaping on a delta-sigma modulator                                                   | 21             |

| 2.12 | Pre-distortion concept block-diagram                                                       | 22             |

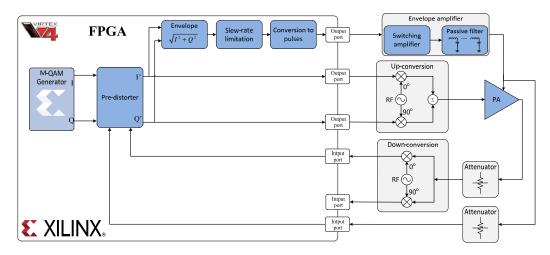

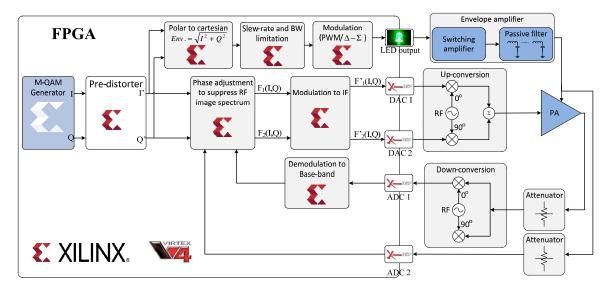

| 3.1  | General scheme of the initial design for the ET transmitter                                | 24             |

| 3.2  | Use of the input/output ports of the $\mathrm{FPGA}$                                       | 26             |

| 3.3  | Up-converter block diagram (TRF372017EVM)                                                  | 26             |

| 3.4  | Down-converter block diagram (TRF371125EVM)                                                | 27             |

| 3.5  | Time and frequency representation for a 16-QAM signal and its slew-rate $\label{eq:alpha}$ |                |

|      | limitation.                                                                                | 29             |

| 3.6  | Block diagram of the implemented PWM                                                       | 30             |

| 3.7  | Modulation using PWM and a slew-rate limited envelope                                      | 31             |

| 3.8  | Demodulation using PWM and a slew-rate limited envelope                                    | 32             |

| 3.9  | Block diagram of the second-order Delta Sigma modulator implemented                        |                |

|      | on the FPGA                                                                                | 34             |

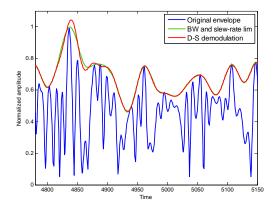

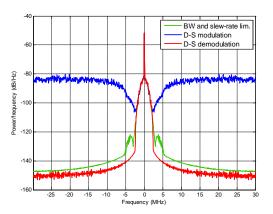

| 3.10 | Modulation using $\Delta - \Sigma M$ and a slew-rate limited envelope                      | 34             |

| 3.11 | Demodulation using $\Delta - \Sigma M$ and a slew-rate limited envelope                    | 35             |

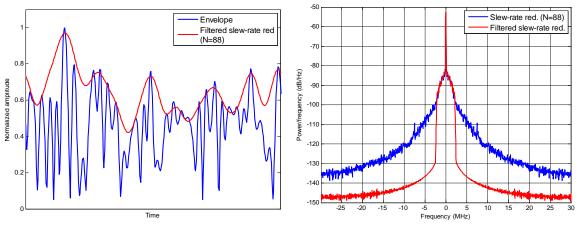

| 3.12 | Time and frequency representation for a 16-QAM signal and its slew-rate $\label{eq:alpha}$ |                |

|      | limitation filtered.                                                                       | 36             |

| 3.13 | Averaging process                                                                          | 40             |

|      |                                                                                            |                |

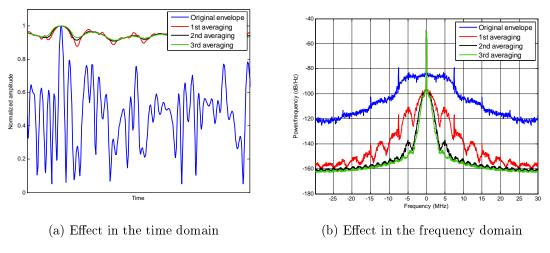

| 3.14 | Effect of the number of averages in one iteration                                         | 41 |

|------|-------------------------------------------------------------------------------------------|----|

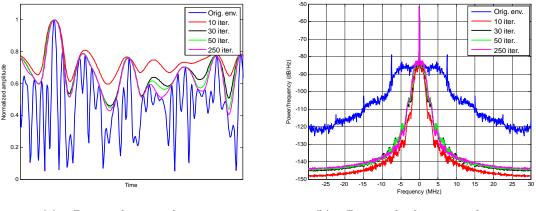

| 3.15 | Effect of the number of iterations using five averages                                    | 41 |

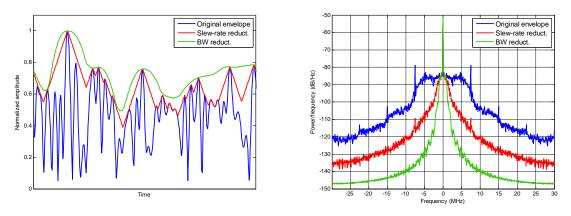

| 3.16 | Comparison between the slew-rate reduction algorithm and the band-                        |    |

|      | width reduction algorithm                                                                 | 42 |

| 3.17 | Modulation using PWM and the bandwidth reduction algorithm                                | 43 |

| 3.18 | Modulation using $\Delta\Sigma M$ and the bandwidth reduction algorithm                   | 44 |

| 3.19 | Sampling replication process                                                              | 46 |

| 3.20 | Block diagram of the implemented slew-rate/band-limitation process                        | 47 |

| 3.21 | Comparison between the slew-rate reduction algorithm and the slew-                        |    |

|      | rate/band-limited envelope.                                                               | 48 |

| 3.22 | Modulation using PWM and the slew-rate/band-limitation process                            | 48 |

| 3.23 | Modulation using $\Delta - \Sigma \mathrm{M}$ and the slew-rate/band-limitation process   | 49 |

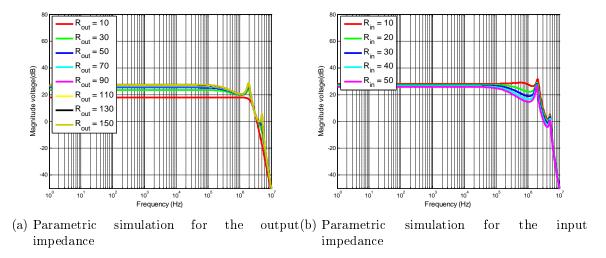

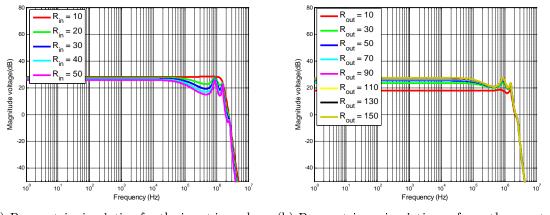

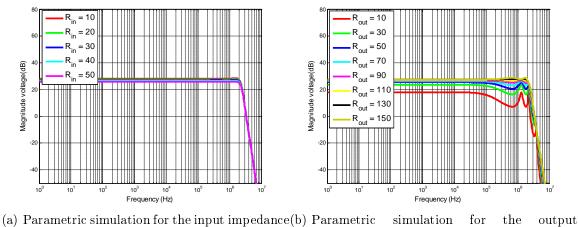

| 3.24 | Scheme to estimate the output impedance of the SPA                                        | 52 |

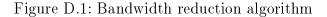

| 3.25 | An 8th order filter circuit schematic                                                     | 53 |

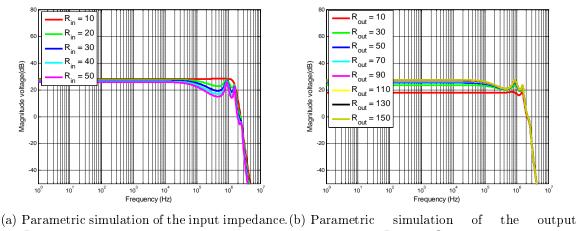

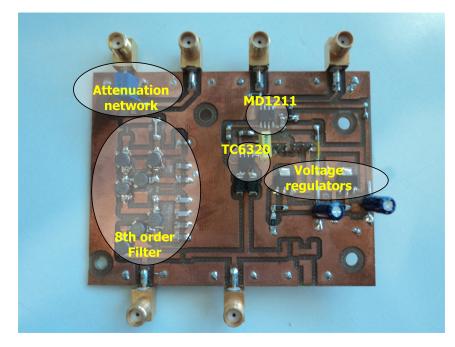

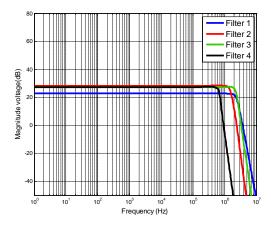

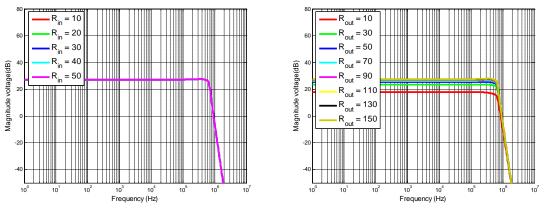

| 3.26 | Parametric simulation for an $8^{th}$ order filter                                        | 53 |

| 3.27 | Photo of a assembled printed circuit including the SPA and $8^{th}$ order                 |    |

|      | demodulation filter                                                                       | 54 |

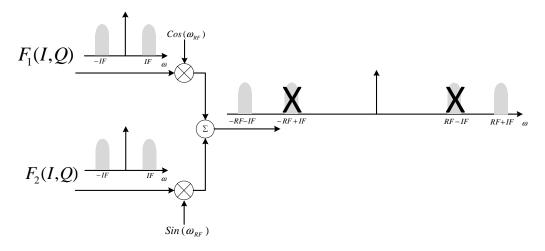

| 3.28 | Principle of the RF image spectrum suppression                                            | 55 |

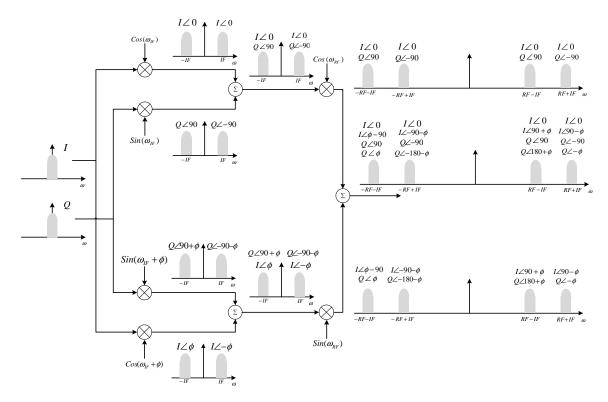

| 3.29 | Complete diagram of the RF image spectrum suppression                                     | 56 |

| 3.30 | Block diagram of the implemented RF image spectrum suppression                            | 57 |

| 4.1  | Block diagram of the implmented ET transmitter                                            | 59 |

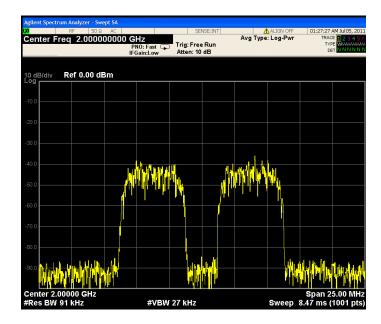

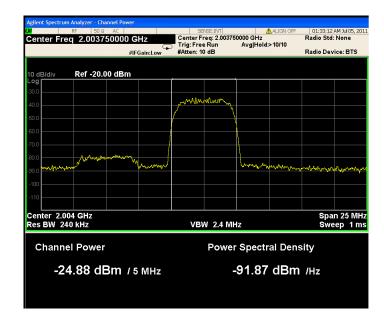

| 4.2  | Spectrum of a 16-QAM signal without RF image spectrum suppression                         | 60 |

| 4.3  | Channel power in the non-suppressed spectrum                                              | 61 |

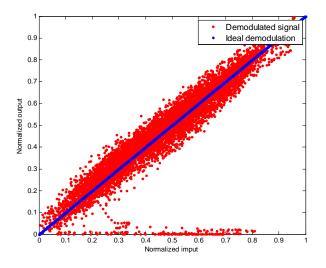

| 4.4  | $\mathrm{AM}/\mathrm{AM}$ curve for up and down conversion without RF amplification       | 61 |

| 4.5  | Amplification of the PWM signal generated by the FPGA running at                          |    |

|      | 60MHz. No load placed                                                                     | 62 |

| 4.6  | Amplification of the PWM signal generated by the FPGA running at                          |    |

|      | 20MHz. No load placed                                                                     | 62 |

| 4.7  | Slew-rate/band-limited signal and its amplification using PWM. FPGA $$                    |    |

|      | working at 60MHz,                                                                         | 63 |

| 4.8  | Slew-rate/band-limited signal and its amplification using PWM. FPGA $$                    |    |

|      | working at 20MHz,                                                                         | 63 |

| 4.9  | Spectrum of the amplified envelope captured by the FPGA when PWM                          |    |

|      | is used                                                                                   | 64 |

| 4.10 | Amplification of the $\Delta - \Sigma M$ signal generated by the FPGA running at          |    |

|      | 20MHz. No load placed                                                                     | 65 |

| 4.11 | Slew-rate/band-limited signal and its amplification using $\Delta-\Sigma \mathrm{M.FPGA}$ |    |

|      | working at 20MHz                                                                          | 66 |

| 4.12 | Spectrum of the amplified envelope captured by the FPGA when $\Delta - \Sigma M$ |    |  |  |

|------|----------------------------------------------------------------------------------|----|--|--|

|      | is used                                                                          | 66 |  |  |

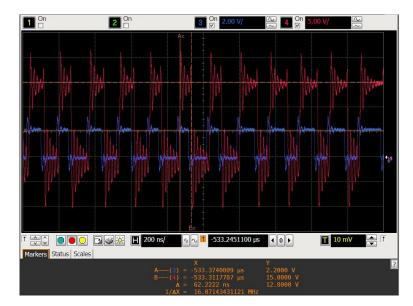

| 4.13 | Synchronization of the slow-envelope and the RF signal                           | 67 |  |  |

| 4.14 | Spectrum of the transmitted/received signal                                      | 68 |  |  |

| 4.15 | Data acquired by the FPGA                                                        | 69 |  |  |

| A.1  | PWM algorithm                                                                    | 80 |  |  |

| B.1  | Delta-Sigma modulation algorithm                                                 | 82 |  |  |

| С.1  | Slew-rate reduction algorithm                                                    | 83 |  |  |

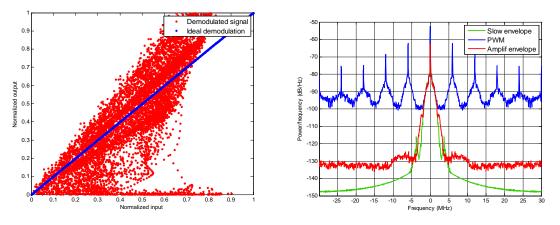

| D.1  | Bandwidth reduction algorithm                                                    | 85 |  |  |

| D.2  | Bandwidth reduction algorithm (continuation)                                     | 86 |  |  |

| E.1  | General schematic considered in the filter design                                | 87 |  |  |

| E.2  | Original design of the filters                                                   | 88 |  |  |

| E.3  | Parametric simulation for Filter 1                                               | 88 |  |  |

| E.4  | Parametric simulation for Filter 2                                               | 89 |  |  |

| E.5  | Parametric simulation for Filter 3                                               | 89 |  |  |

| E.6  | Parametric simulation for Filter 4                                               | 89 |  |  |

# List of Tables

| 1.1 | Comparison of the modulation characteristics and bandwidths of typical mo- |    |  |

|-----|----------------------------------------------------------------------------|----|--|

|     | bile wireless transmitters and communications standards $[2]$              | 1  |  |

| E.1 | Component values for the designed filters                                  | 87 |  |

# List of Appendices

| Α | Pulse Width Modulation                  | 79 |

|---|-----------------------------------------|----|

| В | Delta Sigma modulation                  | 81 |

| С | Slew-rate reduction algorithm           | 83 |

| D | Bandwidth reduction algorithm           | 84 |

| Е | Filters implementations and simulations | 87 |

# Abbrevations and notations

- $\Delta$ - $\Sigma$  M Delta-Sigma Modulation

- ADC Analog to Digital Converter

- DAC Digital to Analog Converter

- DPD Digital Pre-Distortion

- DSP Digital Signal Processor

- DVB-H Digital Video Broadcasting Handheld

- DVB-T Digital Video Broadcasting Terrestrial

- EA Envelope Amplifier

- EDGE Enhanced Data Rates for GSM Evolution

- EER Envelope Elimination and Restoration

- ET Envelope Tracking

- FPGA Field Programmable Gate Array

- GSM Global System for Mobile Communications

- HSDPA High Speed Downlink Packet Access

- IF Inter-medium Frequency

- IF Intermediate Frequency

- LED Light-Emitting Diode

- LO Local Oscillator

- LO local oscillator

- LTE Long Term Evolution

- OFDM Orthogonal Frequency Division Multiplexing

- PAPR Peak to Average Power Ratio

- PWM Pulse Width Modulation

- RF Radio Frequency

- RF Radio Frequency

- RFPA Power Amplifier

- SPA Switched Power Amplifier

- SPA Switched Power Amplifier

WCDMA FDD Wideband Code Division Multiple Access - Frequency Division Duplex

WIMAX Worldwide Interoperability for Microwave Access

# Chapter 1

# Introduction

The necessity for high speed data rates and high spectral efficiency in communications technologies is pushing new communications standards to use linear modulations schemes like band-limited BPSK, QPSK, and multilevel QAM in combination with techniques as Orthogonal Frequency Division Multiplexing (OFDM). On the one hand, OFDM offers high data transmission rate (several Mega bauds) and is robust on multipath scenarios. However, as a counterpart for its transmission, the modulated radio signal exhibits rapid envelope variations.

|                | Standard             | Launch<br>year | Typical carrier<br>BW (MHz) | Typical spectral efficiency (bit/sec/Hz) | Approximated<br>PAPR (dB) |

|----------------|----------------------|----------------|-----------------------------|------------------------------------------|---------------------------|

| 2G cellular    | $\operatorname{GSM}$ | 1991           | 0.2                         | 0.17                                     | 0.0                       |

| Digital TV     | DVB-H                | 2007           | 8.0                         | 0.28                                     | 8.0                       |

| 2.75G cellular | EDGE                 | 2003           | 0.2                         | 0.33                                     | 3.5                       |

| 3G cellular    | WCDMA FDD            | 2001           | 5.0                         | 0.51                                     | 7.0                       |

| Digital TV     | DVB-T                | 1997           | 8.0                         | 0.55                                     | 8.0                       |

| Wi-Fi          | IEEE 802.11 $a/g$    | 2003           | 20                          | 0.90                                     | 9.0                       |

| WIMAX          | IEEE 802.16d         | 2004           | 20                          | 1.20                                     | 8.5                       |

| Wi-Fi          | IEEE 802.11n         | 2007           | 20                          | 2.40                                     | 9.0                       |

| 3.5G cellular  | HSDPA                | 2007           | 5.0                         | 2.88                                     | 8.0                       |

| 3.9G cellular  | LTE                  | 2009           | 20                          | 8.00                                     | 10.0                      |

Table 1.1: Comparison of the modulation characteristics and bandwidths of typical mobile wireless transmitters and communications standards [2]

These envelope variations produce an average value lower than its peak value. Having in mind that this signal goes through the power amplifier (PA), this implies an average output power lower than its maximum peak output power. The ratio between this two is known as the Peak to Average Power Ratio (PAPR), and as Table 1.1 shows, for newer communications standards their PAPR values are becoming higher, in fact, the better the spectral efficiency is the higher the PAPR is.

# 1.1 Linearity-efficiency problem for PA in current communication standards

When a linear PA -class A, AB, B- is used to amplify the radio signal, high PAPRs values force to operate the PA at high back-off levels to avoid distortions on the linear modulations. Such approach implies a poor efficient amplification, since the PA amplifies a signal below the maximum possible and therefore, spends more time operating below its maximum efficiency. The non-used energy on the amplification is dissipated as heat reducing the life time of the battery, in the case of mobile devices, and increasing the costs due to the additional cooling system that is required, in the case of base stations.

On the other hand, a high efficient amplification could be achieved using switched PA (SPA) (Class C, D, E, F). In this case, it is possible to reach (theoretically) 100% efficiency. However, switched amplification is highly non-linear and therefore, matter of concern because the newer generation standards use linear modulations schemes that should be linearly amplified. In this way arises a trade-off between efficiency and linear amplification. It could be achieved either a highly linear amplification with poor efficiency or a high efficient amplification with non-linear distortions.

The linearity-efficiency problem has been widely studied on the literature. Given the fact that SPAs are highly efficient, but non-linear, some structures try to take advantage of this, creating configurations to achieve a linear amplification. This is the case of architectures like *Linear Amplification Using Non-Linear Components* (LINC) [3], *Combined Analog Locked Loop Universal Modulator* (CALLUM) [4], and *Envelope Elimination and Restoration* (EER) [5]. On the other hand, other architectures use linear power amplifiers under specific configurations in order to achieve a high efficient amplification, this is the case of architectures like *Envelope Tracking* (ET) [6] and all those architectures based on dynamic supply. However, it is important to mention that the power amplifier architectures are not limited to use purely linear, or non-linear amplificient and linear amplification. These architectures include the *Doherty Power Amplifier* (DPA) which is widely deployed in current radio-base stations working in L-S-C bands with time varying envelope signals as WiMax, WLAN, etc. Using the DPA drain efficiencies up to 70% have been reported for output powers between 5 W

and 10 W [7, 8, 9, 10], whereas the efficiency achieves values around 50% for 250 W [11].

From the above mentioned architectures EER and ET are two promising amplifiers for the newer generation radio signals [12, 13]. Omitting the fact that these architectures use different PA classes, both architectures use dynamic power supply to achieve a high efficient amplification. However, both amplifiers share a common drawback as well: They require an envelope amplifier (EA), capable to provide high efficiency and linearity in a wide bandwidth in order to be able to follow accurately the rapid envelope changes. Such task becomes even more complex when dealing with high PAPR signals, where the envelope bandwidth extends, theoretically, throughout the spectrum (in practice between 5 and 7 times the bandwidth of the base-band complex modulated signal) [14, 15]. However, recently an approach based on the slew-rate limitation [1] and bandwidth reduction [16] of the envelope have been proposed to overcome this problem, moreover, this technique has shown promising results [17, 18, 19].

## **1.2 Contributions of this master thesis**

Despite of the results presented in the literature using bandwidth and slew-rate reduction algorithms [17, 18, 19], there is not yet a transmitter implementing these techniques in combination with switched amplification. Furthermore, the method for bandwidth reduction proposed in [16] has the main drawback to be an iterative algorithm and therefore, it is not a real time implementable technique. On the other hand, the method of slew-rate limitation proposed in [1] is a real-time algorithm, but the resulting signal does not have a clear spectral limitation, which may cause problems when highly-efficient switched techniques are used.

This master thesis presents the design and implementation of an ET transmitter including an envelope amplifier based on switched amplification and algorithms for slew-rate and bandwidth reduction of the amplified envelope. The transmitter presented in this master thesis constitutes a research environment that will allow investigate possible solutions to solve the linearity-efficiency trade-off of the power amplifiers. The design and implementation of the EA includes commercial switching devices driven by pulsed signals generated by a Field Programmable Gate Array (FPGA) and modulated using Pulse Width Modulation (PWM) and Delta-Sigma Modulation ( $\Delta - \Sigma$  M) to achieve an efficient amplification. The signals, amplitudes, modulation frequencies and bandwidths are compatible with current communications standards. This master thesis also presents a new algorithm for reduction of the envelope bandwidth as well as improvements over the slew-rate reduction algorithm presented in [1]. These improvements were implemented in a FPGA and validated in the implemented transmitter.

# 1.3 Organization of this master thesis

In addition to this chapter, this master thesis includes the following content:

**Chapter 2** includes the state-of-the-art of power amplification architectures for wireless communications. Here, a detailed explanation of the treated power amplifier architecture as well as its problems and limitations is presented. This chapter provides the required theoretical background necessary to understand the development of this project.

**Chapter 3** gives a full description of the design and implementation of all the parts that comprises the envelope tracking transmitter. This chapter starts giving a list of the requirements to fulfill, and continues with the description of the existing problems at each stage of the design. Simulations, partial results and proposed solutions to overcome the difficulties are fully described for independent parts of the ET transmitter.

**Chapter 4** presents the final design of the transmitter. Further tests and limitations are presented before to integrate all the parts that comprises the ET. This chapter concludes presenting the final implementation and some results that show the reliability of the design.

**Chapter 5** includes the findings and the conclusions extracted from the development of this project, as well as possible improvements and further work.

**Appendices** include a description of tools used during the development of this project and some simulations results.

# Chapter 2

# State of the Art of Power Amplification Strategies for Wireless Communications

# 2.1 Power amplifiers

In general, a power amplifier (PA) is defined as a device that increases the power of an arbitrary input signal. The added power is exhibited at the output signal and is taken from a DC-input power. PA are classified depending on the architecture used to perform the amplification. Moreover, each of these configurations led to different outputs waveforms and efficiencies.

The classification of the existing PA architectures is referred in the literature as *classes*, existing class A,B,C,D,E and F [20]. All these classes, except the class A, employ various nonlinear, switching, and wave-shaping techniques in order to provide a linear and efficient amplification. However, not all these classes provide a linear amplification, allowing their classification in two main groups namely, the linear amplifiers and the non-liner amplifiers. Besides, the PA are also classified depending on the conduction angle, making reference to the angle when the amplifier starts to work if a sinusoid is considered at its input.

#### 2.1.1 Linear amplifiers

The linear amplifiers include the classes A and B, although some authors also include the class AB as an intermedium class between classes A and B [21]. These configurations are considered linear because the phase and the amplitude of the output signal is linearly related with the amplitude and phase of the input signal. In the following, a brief description of these topologies is addressed.

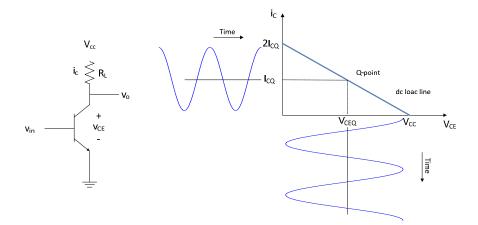

#### Class A

The general class A amplifier is shown in Figure 2.1. In the class A topology the amplifier remains biased in the active region during all normal operating conditions. This condition implies that the device is always ready to amplify the input signal but also that the nominal bias current is nonzero, therefore, there is always some power dissipation in the device.

The configuration showed in Figure 2.1 reaches a maximum theoretical efficiency of 25 % for an ideal PA, however in RF configuration the resistor  $R_L$  is replaced by an inductor, rising its theoretical efficiency up to 50 %. The low efficiency of the class A amplifier is mainly due to its never-zero I-V product during its operation, in fact, the lowest efficiency is reached when there is no signal in the input port, in which case all the power is dissipated in the device.

Despite its low efficiency, the class A power amplifier behaves as an ideal power amplifier regarding its input/output relation. Since the transistor is all the time in the active region, the amplification of the signal is performed over an specific load line which design is relative linear to minimize distortion between the input and the output.

Due to the high linearity of this class of amplifier and its low efficiency this amplifiers is widely used in applications requiring low power, high linearity and where the efficiency is not critical.

Figure 2.1: Class A amplifier

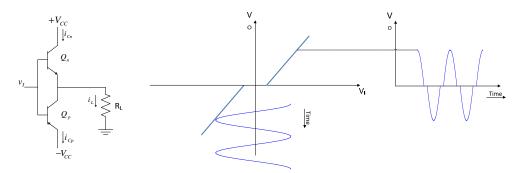

#### Class B

In the class B architecture the power amplifier is not in the active region when the input signal is zero. This sets its quiescent current to zero and there is no power dissipation in absence of input. The amplifier enters in the active region when the input signal crosses the conduction threshold. As result, the amplification is linear just after crossing the threshold.

The classical class B amplifier is an emitter-follower (actually this is the most used configuration on RF applications), however, it is also used in a push-pull configuration as Figure 2.2 shows. By using this configuration when the input signal has both positive and negative values, it is possible the amplification of both semi-cycles.

The instantaneous efficiency changes with the output voltage and reaches a maximum theoretical value of 78.5 % for an ideal PA. This efficiency is considerably greater than the exhibited by the class A amplifier, however the main drawback of this architecture is the crossover distortion caused by the non-conduction region as Figure 2.2 shows.

Figure 2.2: Class B amplifier

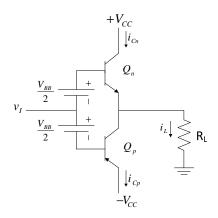

#### Class AB

The class AB attempts to solve the distortion of the crossover region that the class B amplifier exhibits. The crossover distortion is virtually suppressed establishing the biasing of the PA right at the threshold of its operation. As in the case of the class B, this architecture is used either as a emitter-follower or in a push-pull configuration (see Figure 2.3) ,to allow amplification of signals with positive and negative values. Nevertheless, it has to be pointed out that distortion can still occur produced by disparities between the amplifiers. The class AB reaches efficiency values between 50 % and 78 % and is used in

audio as well as applications of low, medium, high and very high frequencies [22] when variations are introduced over its classical configuration.

Figure 2.3: Class AB amplifier

### 2.1.2 Non-linear amplifiers

In those applications where the linearity is not critical and the efficiency is the main concern, the non-linear amplifiers are widely used. In contrast to the linear amplifiers, the non-linear amplifiers don not exhibit a linear relation between the phase and amplitude of the input and output. The non-linear amplifiers includes the class C, D, E and F; in the following, a brief description of this amplifiers is addressed.

## Class C

In class C the amplifier is biased and controlled by a conduction angle which is set such that the amplifier is active for less than half of the waveform described by a sinusoid. However, the load of the amplifier should be tuned to provide a full cycle of output signal for the fundamental, or resonant frequency. The use of this amplifiers is, therefore, limited for a fixed frequency and produces the lost of the linearity in the amplification process. Nevertheless, its theoretical efficiency tends to 100 % when the conduction angle tends to zero. Unfortunately, 100 % efficiency is physically unreachable by the amplifier and a typical compromise lead to efficies around 85 %

#### Class D

This class of amplifier employs at least two active elements whose operate as switches to create a square signal at the output. The generated signal is then low pass filtered passing the first harmonic to the load. As the current is driven just by the switched-on active element, then the theoretical efficiency is 100 % for an ideal PA. Nevertheless, due to losses associated to saturation, switching speed and junction capacitances, the practical efficiency is less than 100 % and is inversely proportional to the switching frequency.

The class D amplifier is widely used in audio applications where efficiencies of more than 90% have been reported for output powers around 10 W [23]. However due to the degradation of its efficiency when the swhitching frequency increases this topology is not used in high frequency applications.

## Class E

In the class E amplifier the active device is used as a switch. Its configuration includes an RF-choke inductor used as a pull up device and operates as a current source. The goal in this class of amplifiers is to design the load network to reduce the I-V product over the active device allowing the efficiency of an ideal amplifier approach to 100 %.

## Class F

Class F amplifiers are also based on the tuning of its load to reduce the I-V product over the active device. In this class of amplifier a resonator is used to block some, or all, the odd harmonics of the output current. By doing this, a square wave voltage out-of-phase with the current is created at the output. The voltage output exhibits a square waveform as well as the current. Therefore, (ideally) the device switch its state yielding a zero I-V product and so reaching 100% ideal efficiency.

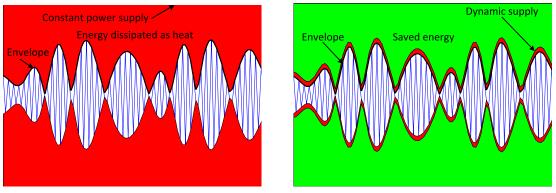

# 2.2 Dynamic supply for high efficient RF amplification

In wireless communications a high efficient amplification directly implies an efficient use of batteries, in the case of mobile devices, and less energy consumption, in the cases of fixed radio bases. On the other hand, the transmitted signals of newer communications standards are exhibiting higher PAPR as Table 1.1 shows. Moreover, the new standards are using linear modulations in the transmitted signals, making these signals very susceptible to non-linear distortions.

With linearity and efficiency being crucial aspects in newer communications standards, using the classical high efficient amplifiers presented in the previous section is not a viable solution becasue the linearity is completely lost. Regarding the linear amplifiers, they fulfill the linearity requirement but its efficiency is poor. Moreover, in the presented linear amplifiers the efficiency is reduced even more when the amplified signal exhibits high PAPR. As Figure 2.4a shows, when linear amplifiers are used to amplify signals below its maximum output voltage, the energy that was not used on amplification is wasted as heat. A suitable solution to overcome this problem is to use an amplifier whose voltage supply is dynamically adjusted depending on the required output voltage. This approach is illustrated in Figure 2.4b and is know in the literature as "dynamical supply". By implementing this approach, it is saved most of the energy previously wasted as heat, increasing the total efficiency of the radio transmitter in about 20 %-30 % [24].

(a) Static power supply

(b) Dynamic power supply

Figure 2.4: Static and dynamic power supply

Two of the more promising amplifier architectures for the newer generation radio signals implementing the dynamic supply are the Envelope Tracking (ET) and the Envelope Elimination and Restoration (EER) architectures [12, 13]. These two architectures try to achieve a linear and efficient amplification by using different PA classes, nevertheless, these architecture face problems in their implementation that are worth of mention.

#### 2.2.1 Envelope Elimination and Restoration (EER)

The EER technique was one of the first architectures implementing the separation of the amplitude and phase information. This technique is also known as Khan technique, making reference to L. R. Khan who introduced this concept for the first time in 1952 [5]. Originally this architecture was developed to solve the problem of high cost and low efficiency in single-sideband transmitters where typically a series of cascaded linear PA were required.

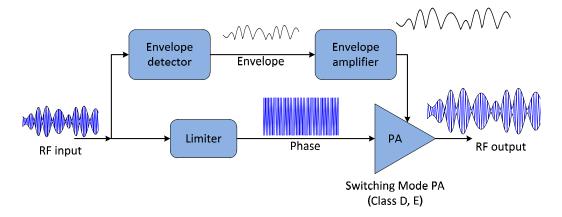

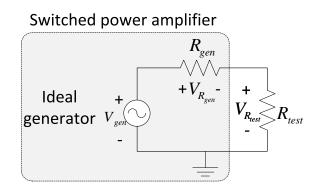

Figure 2.5 shows the block diagram of the EER architecture. It is basically composed by two paths, namely the amplitude and the Radio Frequency (RF) paths. In the first one, a limiter is used to obtain the zero-crossing of the RF signal. By doing this, the envelope of the signal is removed while the phase information is preserved. This turns the PA input into a constant envelope signal, allowing a high-efficient amplification using a Switched Power Amplifier (SPA) (Class C,D,E,F). On the other hand, in the amplitude path the envelope of the RF signal is extracted using an envelope detector. This envelope is then amplified proportionally to the RF output using an Envelope Amplifier (EA). As final step, the amplitude information dynamically supplies the RFPA voltage, "restoring" the amplitude information. Examples of classic EER systems can be found in [25, 26, 27].

Figure 2.5: Envelope Elimination and Restoration (EER) transmitter architecture

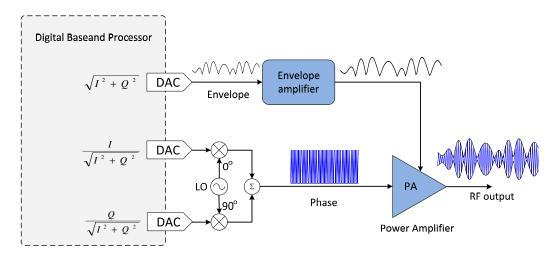

In modern EER, usually a Digital Signal Processor (DSP) is used to generate the envelope and the I-Q components [28, 13, 19] as Figure 2.6 shows. The phase information is obtained modulating to RF the scaled I-Q components. Such configuration avoids the use of an envelope detector and makes easier the adjustment of possible misalignment between the two paths. Nevertheless, in this case the EER becomes a misnomer because there is not elimination of the envelope. However, the name is still in use [2, 29], although some authors call this configuration polar transmitter [30, 31, 32]. Anyhow, despite the misnomer, in general the term EER is referred to any system where the phase-modulated RF signal is amplified through a nonlinear amplifier and the envelope signal is used to modulate and amplify the phase-modulated RF signal whereas polar transmitter refers to all those architectures where amplitude and phase information are used in the amplification process.

Figure 2.6: Polar transmitter architecture

## 2.2.1.1 Issues and drawbacks

#### **Delay mismatch**

Of crucial importance in this architecture is the synchronization between the input RF signal and the supply voltage of the RFPA. As shown in Figure 2.5 and Figure 2.6 this architecture performs the product of the envelope and phase inside the PA, therefore, these signals should be properly aligned, otherwise it will imply a miss correspondence between amplitude and phase for each transmitted symbol, which will be exhibited as non-linear distortion at the output that cannot be corrected even using Digital Pre-Distortion (DPD).

Simulations presented in [14] indicate that synchronization accuracy around  $\pm 20$  ns is required for every 1 MHz of RF bandwidth to meet linearity requirements. However, despite of the importance of the alignment, nowadays delay mismatch is not a mayor issue due to the wide use of FPGAs and DSP on the transmitter architectures [28, 13, 19]. These processors facilitate the correction of temporal misalignment in the generated data.

#### Bandwidth expansion and linear amplification

The definition of constellation as well as the transmission of the signals is usually done in terms of Cartesian coordinates. However, any signal could be represented using either Cartesian or polar coordinates. The Cartesian representation is shown in equation 2.1, where I(t) represents the In-phase component, Q(t) represents the Inquadrature component and  $\omega_c$  represents the carrier frequency. On the other hand, the polar representation is shown in equation 2.2, where A(t) represents the amplitude, or envelope, of the signal,  $\phi(t)$  represents the phase and  $\omega_c$  the carrier frequency.

$$s(t) = I(t)sin(\omega_c t) - Q(t)cos(\omega_c t)$$

(2.1)

$$s(t) = A(t)\cos(\omega_c t + \phi(t))$$

(2.2)

The relation between equations 2.1 and 2.2 is ruled by:

$$A(t) = \sqrt{I(t)^2 + Q(t)^2}$$

(2.3)

$$\phi(t) = \tan^{-1} \left( \frac{Q(t)}{I(t)} \right) \tag{2.4}$$

As can be appreciated from equations (2.1) and (2.2), the relation between the polar and Cartesian representations is not linear. In fact, when a transformation from Cartesian to Polar is performed, the non-linear relationship between them causes the polar vectors to lose the band-limited property held on the Cartesian representation. That is, after a Cartesian to polar conversion, the bandwidths of the envelope and phase signals are different, actually wider, than the corresponding bandwidths of I and Q signals.

This phenomena is termed "bandwidth expansion" and turns out to be theoretically infinite, i.e. the bandwidth expansion is extended theoretically throughout the spectrum. For example, consider a two tone signal with carrier frequency  $\omega_c$  and modulation frequency  $\omega_m$ . The RF signal has a defined and finite bandwidth around  $\omega_m$ , but its envelope contains frequency components at dc,  $2\omega_m$ ,  $4\omega_m$ ,  $6\omega_m$ ,  $8\omega_m$ , ..... etc. However, in practical implementations the bandwidth is considered at least 5 to 6 times larger than the Cartesian bandwidth signal [14, 15] in order to avoid significant distortion at the output. In general, it could be stated that such bandwidth truncation is restricted by the maximum allowed distortion at the final output.

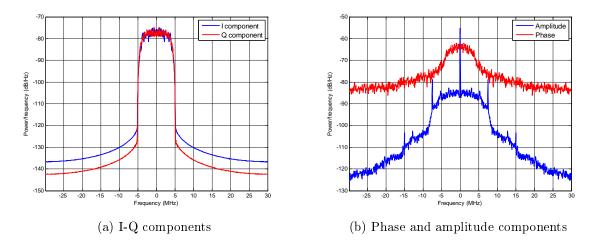

To illustrate the bandwidth expansion phenomenon in a practical case, consider the 16-QAM signal in Cartesian representation exhibiting a 5 MHz bandwidth. Such signal is represented on the left side in Figure 2.7a, notice that such Cartesian representation have a clear and well defined bandwidth spectrum. On the right side, in Figure 2.7b is shown the equivalent polar representation. Notice that the resulting amplitude (in blue) and phase (in red) signals do not have a well defined bandwidth spectrum any longer. Moreover, the spectrum is wider and, as mentioned before, a good approximation could be considering a bandwidth expansion about 5-6 times the original bandwidth, i.e. around 25 MHz.

Figure 2.7: Bandwidth expansion phenomenon for a 16-QAM signal

The distortion caused over the output signal occurs because the information originally contained on the I-Q signals is now split into two other signals, namely the envelope and the phase. These signals should be completely preserved in order to avoid any loss of information, because such losses imply distortion at the output.

In those cases where the envelope and phase signals are directly synthesized by digital processors (Figure 2.6), the bandwidth expansion could represent an issue due to the necessity to sample the signal at least twice its bandwidth (in order to hold the Nyquist criteria). However the developments achieved in DACs and digital processing allow to overcome this difficulty.

On the other hand, the main problem caused by the bandwidth expansion is in the implementation of dynamic power supply because the information of the amplitude is used in this process. Therefore, the envelope amplifier should provide a fast enough dynamic response. Such requirement is not easy to fulfill, and the task becomes even harder when the efficiency is considered.

DC-DC converters satisfying the bandwidth, output power, linearity and efficiency requirements are still matter of study. Current solutions achieve just hundreds of KHz with output power in the order of mW or several tens of watts in the best cases [26]

## 2.2.2 Envelope Tracking (ET)

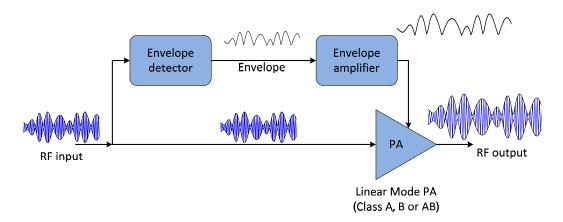

A block diagram of the ET architecture is shown in Figure 2.8. This architecture is usually included in the group of polar architectures. However, strictly speaking, the ET does not belong to this group because the RFPA input signals are not the phase and amplitude. Instead, its inputs are the RF signal and the envelope of the signal used to dynamically supply the voltage to the RFPA.

As Figure 2.8 shows, the RFPA input signal is non-constant. This forces to use a linear PA (Class A, B, AB) in order to avoid distortion on the linear modulated signal. Given the fact that linear PA are not highly efficient, this architecture attempts to achieve a high efficient amplifications relying on the dynamic power supply. The maximum power saving occurs when the supply is adjusted to the minimum level where the power amplifier is still linear. In some cases, the PA could even operates at weak compression.

Figure 2.8: Envelope Tracking transmitter architecture

Since ET and EER use a similar signal processing, these architectures face common problems. However, tt is important to remark that the ET technique has been proposed to improve the efficiency of the linear PAs (Class A, B, AB, C) by adapting its power supply voltage. On the other hand, the EER technique is aimed to improve the efficiency by using a high-efficient non-linear PA that processes a constant envelope phase modulated signal. In any case, both techniques behave ideally like a highly-efficient linear PA.

#### **Delay mismatch**

Similar to the EER architecture, in the ET architecture the synchronization between the envelope and the RF input signal of the PA is important even when the product of the envelope and the phase is not performed inside the PA. The reason is because the PA should be kept away from the compression point. If there exist a misalignment such that the compression point is crossed, then it will occur linear distortion in all those points where the compression point is exceeded. However, if the RFPA never goes beyond the compression point there is no non-linear distortion, which makes the ET architecture more robust to delay mistmatch, compared with the EER architecture.

As also occurs in the EER architecture, nowadays delay mismatch is not a mayor issue due to the wide use of FPGAs and DSP on the transmitter architectures [28, 13, 19] which facilitate the correction of temporal misalignment in the generated data.

#### Dynamic supply voltage distortion

In the dynamic supply, the maximum power saving occurs when the supply voltage is adjusted to the minimum level where the PA is still linear, that is, as close as possible to the compression point. However, a constant adjustment of the power supply implies a repeatedly change on the PA bias conditions, or equivalently, a repeatedly change on its input/output relation because the load line is changed. Those changes on the PA's input/output relation, induces non-linear distortion in the output signal.

Fortunately, the distortion induced by the dynamic supply is not a major issue. The inclusion of feedback control loops combined with Digital Pre-Distortion (DPD) techniques allow to compensate the changes in order to achieve a linear amplification [33, 34, 35, 36, 37].

#### Bandwidth expansion and linear amplification

This architecture shares the problem of DC-DC converters with the EER architecture: The bandwidth expansion resulting from the Cartesian to Polar conversion makes difficult to perform the amplification of the envelope efficiently and provide good linearity and high voltage outputs simultaneously. DC-DC converters satisfying these characteristics are still matter of study.

# 2.3 High efficient envelope amplification

The straightforward approach to amplify the envelope of in architectures like EER and ET is to use a linear regulator to adjust the supply voltage of the RFPA [38]. The use of linear regulator topology achieves wide bandwidth and good noise performance, nevertheless, as a counterpart, this solution brings down the efficiency achieved using dynamic supply.

Two of the main attempts to improve efficiency are the multilevel converter [39] (Class G modulator) and the buck converter (Class S modulator) [40].

## 2.3.1 Class G architecture

The approach of the class G is to use a linear amplifier provided with more than one power level supply. In order to reduce the power consumption, the class G is provided with two or more voltage supply power levels and switch between them as the output signal approaches to each one. That is, if the input signal remains at low levels, the power supply is adjusted to a level that allows linear amplification, reducing this way the power consumption. This approach is similar to use dynamic supply but it is adapted just to few discrete levels.

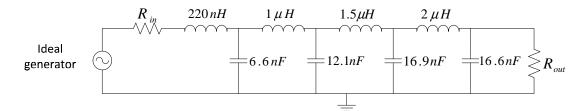

The main concern with this amplifier is the introduction of linear distortion during the commutation from one level to another. However, nowadays the class G amplifiers is firmly established in powered subwoofers, and current applications use this class in ADSL telephone-line drivers [41]. The class S architecture attempts to achieve high efficiency using switched amplifiers. The input signal is encoded using a modulation to turn the input signal into a pulsed signal. The pulsed signal is efficiently amplified using a switched amplifier and is later recovered using a passive filter at the output of the amplifier. Classical S architecture employs PWM or  $\Delta - \Sigma M$  to modulate the signal.

The theoretical efficiency of this architecture is 100 %, because the I-V product tends to zero in the device. However, there exist switching losses when the commutation between *on* and *off* states is performed, which means that its efficiency is reduced as the switching frequency increases.

The main drawback of the class S amplifier is the switching frequency necessary to amplify the input signal because this frequency should be several times the bandwidth of the signal to be amplified [42]. However, in practice the switching frequency goes up to five times the bandwidth of the input signal [24]. Such task becomes complex when this class of amplifier is used to amplify the envelope of the signal because this is, in general, a wide bandwidth signal, for example for a 4 MHz bandwidth signal in the Cartesian format, its envelope bandwidth has around 20 MHz, requiring at least a switching frequency of around 100 MHz.

Another matter of concern is the filter used at the output. This filter should be selective depending on the modulation used as well as provide a high attenuation in the rejected band in order to eliminate the switching noise. On the other hand, the introduction of a filter in the architecture induces a delay that should be taken into account for the alignment of the RFPA input signals.

DC-DC converters satisfying the bandwidth, output power and efficiency requirements are still matter of study. Current solutions achieve just hundreds of KHz with output power in the order of mW or several tens of watts in the best cases [26]. In the mean time, partial solutions like bandwidth and slew-rate envelope reduction [19, 17] have been proposed in the literature as an alternative to fulfill the mentioned requirements in bandwidth and output voltage.

## 2.4 Modulations for switched amplification

The procedure to perform switched amplification consists in first converting, or modulating, the signal to be processed into pulses. If a class S amplifier is considered, the pulses are amplified using a PA on switched mode and as final step the amplified output is filtered using a passive filter. The output of the filter is (ideally) an amplified version of the input signal.

Regarding the initial modulation necessary to amplify the signal, two of the more used modulation techniques are the Pulse Width Modulation (PWM) and the Delta Sigma modulation ( $\Delta - \Sigma M$ ). Having in mind the final application, an envelope amplifier, these techniques presents advantages and drawbacks that will be shortly addressed.

## 2.4.1 Pulse Width Modulation (PWM)

Pulse width modulation is a well-known technique that has found applications on time division multiplexers [43, 44], radio frequency transmitters [20], optical data storage [45], control of AC–DC power converters, and the like. Moreover, there exists many variations regarding the output format and carrier used to modulate the input signal. However, the following explanation does not address all these possibilities, instead it is focused on the suitability of the PWM to develop an envelope amplifier. Further explanations and a deep analysis can be found in [46]

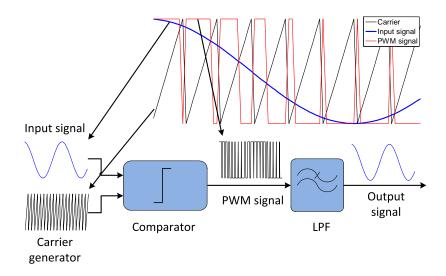

A block diagram of the PWM technique is shown in Figure (2.9). A carrier is generated and used as reference by a comparator to produce either a "high" or "low" output. As the graphic above the block diagram shows, the comparator yields a "high" output (in red) if the input signal (in blue) is above the carrier (in black), otherwise a "low" level is exhibited at the output. If an efficient switched amplification of the signal wants to be performed, it has to be done between the PWM output and the low pass filter. This sequence represents the basic modulation process behind the PWM, nevertheless as possible variations the carrier, here showed as a sawtooth signal, could be a triangular as well or any other variation of these two. Regarding the comparator output, there exist variations including three or more levels. Anyhow, each of these approaches yields a different spectrum output.

The PWM is a nonlinear process, in fact, once the demodulation is performed, the overall process results in distortion of the modulating (input) signal. That is, the

Figure 2.9: Pulse width modulator block diagram

output signal is never going to be the same like the input signal. A particular problem on the PWM is its inherent noise in the modulated signal, which spectrum resembles white noise.

Regarding the spectrum of the modulated signal, it is important to point out that the higher the frequency of the carrier is the further is the first spectrum replica of the base band, and so a less selective filter is needed to recover the signal. Moreover, higher carrier frequencies yields better resolution in the modulated signal. This facts imposes the main limitation on applications where it is required to implement this architectures on a digital signal processor, because the sampling frequency is limited by the maximum clock speed of the processor. This limitation results in a trade-off between the resolution and the frequency of the carrier because increasing the number of points that conforms the carrier implies a reduction of its frequency. Not to mention the resolution losses associated to the number of bits to represent the signal.

The design of the filter require special attention because its response should be flat and the rejected band should has enough attenuation to remove the undesired noise introduced by the carrier replicas and the switching noise

## 2.4.2 Delta Sigma Modulation ( $\Delta - \Sigma$ )

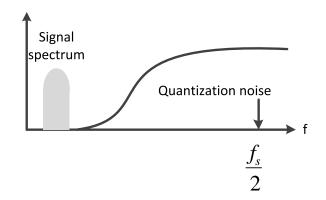

This modulation technique is very popular in audio applications and Digital to Analog Converters (DAC) and Analog to Digital Converters (ADC). Different to PWM where the switching noise spectrum resembles white noise, the delta sigma modulator distributes the quantization error, or noise, such that it is very low in the band of interest. This characteristic is partially introduced by the oversampling principle which is the act of sampling the input signal at a frequency higher than the Nyquist frequency (twice the input signal bandwidth).

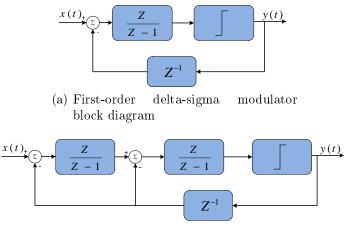

(b) Second-order delta-sigma modulator block diagram

Figure 2.10: First and second order delta-sigma modulators block diagram

Figure 2.10 shows the block diagram of a first order Delta-Sigma modulator. The input signal enters in the system via a summing junction. Then the signal goes through an integrator which feeds a comparator that performs the one-bit quantization. The output of the comparator is then fed back to the input summing junction, and is also the resulting output. Including more integrators in the structure changes the noise shaping of the modulator. Figure 2.10b shows a second order Delta-Sigma modulator. Higher order are also possible but not always stable as the first and second order showed in the above figures.

An analysis of the frequency response of the modulator lead to the noise shape showed in Figure 2.11. As can be observed in this figure, the quantization noise is high pass filtered, pushing it towards the sampling frequency. Increasing the order of modulator increases the order of this filtering effect.

Figure 2.11: Noise shaping on a delta-sigma modulator

The characteristic noise shaping exhibited by the Delta-Sigma modulator allows to relax the order of the filter used in the demodulation comparing with the required in the PWM. Moreover, other Delta-Sigma configurations allow to modulate signals, not just in base-band but also at other frequencies.

# 2.5 Digital Pre-Distortion (DPD)

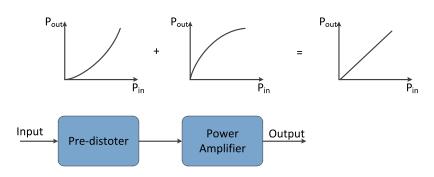

The basic idea of Pre-distortion is to build a correction module that compensates the non-linearity of the power amplifier, in this sense, a pre-distorter tries to invert the nonlinear function of the PA such that, the cascade responses of both PA and pre-distorter results in a linear response as Figure 2.12 illustrates.

Figure 2.12: Pre-distortion concept block-diagram

The procedure to include a pre-distorter comprise modeling the power amplifier by taking samples of the inputs and the output of the power amplifier. Based on these samples a mathematical model is developed and then inverted to produce the opposite distortion of the exhibited by the power amplifier. This model is then placed at the input of the amplifier resulting in a linear amplification.

The modeling step is a complex task and several mathematical approaches can be found in the literature. These approaches include Nonlinear Auto-Regressive Moving Average (NARMA)[47], Volterra series (or pruned Volterra) [48], memory polynomials, Wienner-Hammerstein models [49] and neural networks among others.

# Chapter 3

# **Envelope Tracking design and implementation**

During the design and implementation process of the envelope amplifier, more than one possible solution was tried in order to achieve the best performance in the final testbed. This chapter addresses a detailed description of the procedure followed to achieve the final design and the limitations found during the process.

This chapter starts giving a full description of the desired structure of the Envelope Tracing as well as the technical details that have to be accomplished in the design. Given the fact that during the development limitations related with the available resources appeared, the subsequent section gives a brief description of the available resources to develop this project. The following sections include a full description of the design and implementation as well as simulations results of the partial stages.

# 3.1 Required structure and technical details

The design of the envelope tracking testbed had to include a reliable and robust configuration because the structure will be used to develop research activities. Due to its end use, the testbed should allow to work with real and recent communications standards. As initial requirement the following technical details were considered:

- The envelope amplifier should include a switched amplifier aimed to achieve a high efficient amplification

- Modulation at RF using a 2GHz carrier exhibiting a bandwidth of around 5 MHz in order to simulate real communications standards.

- The envelope amplifier should provide peak voltage levels around 30V with currents up to 2A to the RFPA drain in order to accomplish real radio-base stations transmission power.

- The structure has to incorporate digital pre-distortion to the RFPA using an FPGA. So the RFPA inputs and output should be able to be monitored. Moreover, as an innovative research work, the design will include the slew-rate reduction algorithm described in Section 3.3.

Having in mind the above described restrictions, a general block diagram of how the testbed should looks like is shown in Figure 3.1

Figure 3.1: General scheme of the initial design for the ET transmitter

# 3.2 Environment description

During the design and implementation processes, some limitations related with the available resources where faced at different stages. For this reason, it is worth mentioning the main available resources as well as their advantages and disadvantages in the completeness of the final test bench. The following section gives such description focusing on the specifications related with the development of this project.

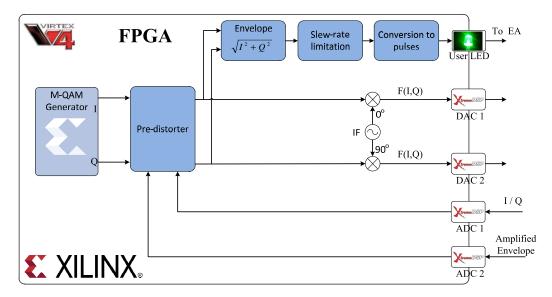

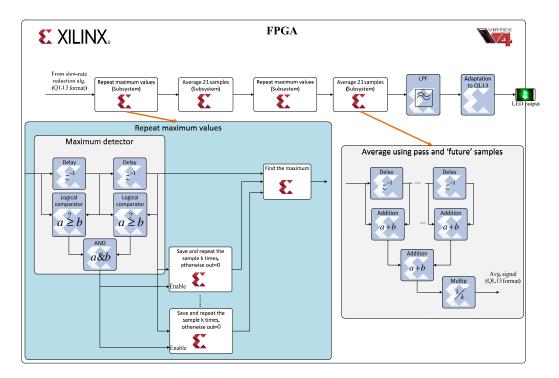

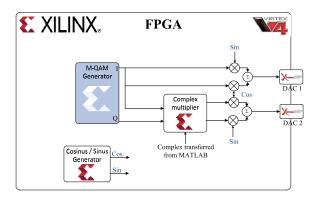

#### Field Programmable Gate Array (FPGA)

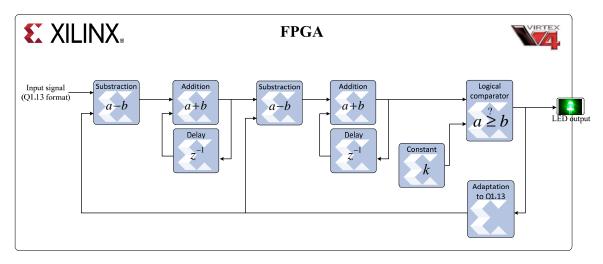

The available FPGA is a Virtex 4 developed by Xilinx Inc, which programming environment is the Xilinx ISE. This FPGA includes two Digital to Analog Converters and two Analog to Digital Converters. The DAC should be driven by a 14-bit fixed-point signal with the binary point at the position 13 while the input ADCs is restricted in the range  $\pm 1$ V. The four converters are restricted to work with a clock speed lower than 64 MHz. On the other hand, the internal clock is able to work at predefined frequencies, these frequencies include 20 MHz; 25 MHz; 30 MHz; 33.33 MHz; 40 MHz; 45 MHz; 50 MHz; 60 MHz; 66.66 MHz; 70 MHz; 75 MHz; 80 MHz; 90 MHz; 100 MHz and 120 MHz. However, since converters are needed then this list is limited to the first eight frequencies.

The number of DACs and ADCs imposed a primary limitation over the implementation: Since it was desired to implement an envelope tracking amplifier with possibilities to use pre-distortion, it was necessary to monitor the inputs and the output of the power amplifier. The inputs comprise the dynamic voltage supply, i.e. the amplified envelope, and the RF signal, which is composed by the I and Q components. On the other hand, the output is the RF amplified signal, composed by the amplified versions of the I and Q components. Such monitoring would require three outputs and three inputs from the FPGA point of view, which was not straightforward.

The two DACs would be used to generate the I and Q components, but one more would be missing to generate the envelope signal. To get around this difficulty, it was created an output from a Light-Emitting Diode (LED) whose status could be controlled from the programming environment. This LED was removed from the FPGA board so its output could be used to generate a two levels signal. The measured voltage at this output was 0V on the *off* state and 3.3 V on the *on* state. This new output would allow to generate the pulsed envelope signal.

A similar approach to the above described could not be used for the ADCs. To solve the problem of monitoring three signals, one ADC was used to sample the envelope while the other had to be used to monitor the I and Q components simultaneously. The last was possible by sampling the signal at Frequency (IF) instead of doing it at baseband. The theoretical explanation and practical implementation of the IF sampling is fully described in 3.9.

A better understanding about the usage of the FPGA inputs/outputs can be achieved by means of figure (3.2) which shows a scheme of the inputs/outputs and the signal handled by each port.

Figure 3.2: Use of the input/output ports of the FPGA

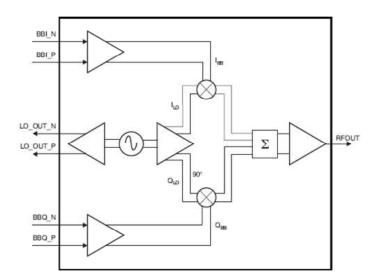

## Up-conversion to RF

The up-conversion to RF was performed using a direct up-conversion device from Texas Instrument model TRF372017EVM. A general block diagram of this up-converter is shown in Figure (3.3). As the block diagram shows, the up-converter includes its own local oscillator (LO), moreover this LO could be used on the demodulation to achieve a coherent demodulation. Further details about this device can be found in [50, 51]

Figure 3.3: Up-converter block diagram (TRF372017EVM)

#### **RF** power amplifier

The amplified envelope supplied dynamically the voltage to a RFPA included on a Cree Inc. Eval. Board CGH40010-TB (GaN HEMT transistor, 10 W CW). Specific details about this amplifier could be found in [52]

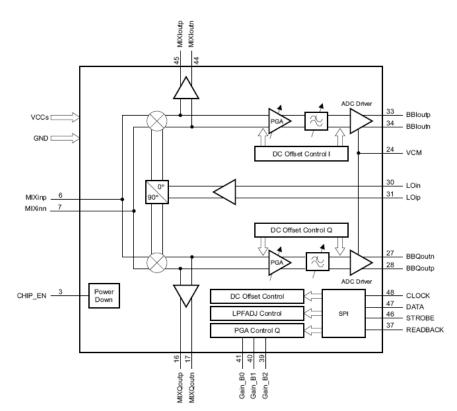

#### **Down-conversion**

The down-conversion using a receiver direct down-converter quadrature demodulator from Texas Instrument. This down-converter is present on the evaluation module TRF371125 and includes programmable base-band filters, adjustable dc offset correction, and buffer amplifiers to directly drive ADCs. The basic block diagram of this down-converter is shown in Figure (3.4). Further details regarding this device can be found in [53, 54]

Figure 3.4: Down-converter block diagram (TRF371125EVM)

#### Measurement equipment

The measurement equipment consisted on an *Agilent Infinium* oscilloscope model DSO90404A for sampling the input and output signals at 2GHz. An Agilent N2783A

probe for measuring the transistor drain current. An *Agilent* spectrum analyzer to visualize the spectrum of the signals. Additionally other general oscilloscopes, voltage sources and laboratory material were employed.

## 3.3 Slew-rate reduction algorithm

The slew-rate parameter defines the maximum possible slope that the PA is able to follow. Low values in this parameter limits EAs to follow the rapid changes on the envelope of the signal; if the envelope has a very wide spectrum bandwidth, it means that the signal contains high frequency components, whose changes the EA is not able to follow. It does not exist a formal correspondence between the slew-rate and the bandwidth of any signal, however as will be shown a limitations on the slew-rate implies a limitation on the bandwidth and vice-verse.

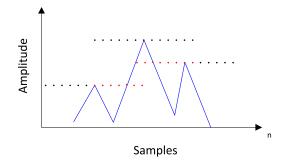

The slew-rate envelope reduction algorithm is fully described in [1]. In short the algorithm could be described as follows: The envelope signal is processed in real time to obtain a reduced bandwidth version of it. This processing is based on present and future values of the original envelope occasioning an small delay that could be compensated like any other misalignment in the signal paths of either EER or ET architectures. The algorithm defines four parameters: The maximum slew rate  $(\pm \Delta_M)$ , the minimum number of steps for going from 0 to 1 on a one-normalized excursion  $(N = \Delta_M^{-1})$ , the original envelope signal (E(n)) and the reduced bandwidth envelope  $(E_s(n))$ . Moreover the following conditions must be hold:

- At time n, the generated envelope E<sub>s</sub>(n) must be at least E(n+k)−kΔ<sub>M</sub>in order to hold E<sub>s</sub>(n + k) > E(n + k) at any subsequent time n + k

- $E_s(n-1) \Delta_M < E_s(n) < E_s(n-1) + \Delta_M$  in order to limit the slew rate variations

By using a intermediate variable y(n) representing an upper bound of E(n) and a lower bound of  $E_s(n)$ , the algorithm (in its causal version) could be written as:

$$y(n-N) = \max_{i=0,1,2\dots,N} \{ E(n-N+i) - i\Delta_M \}$$

(3.1)

$$E_s(n-1) - \Delta_M < E_s(n) < E_s(n-1) + \Delta_M$$

(3.2)

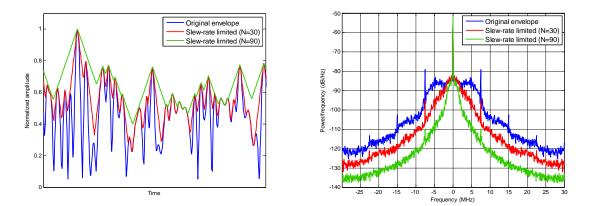

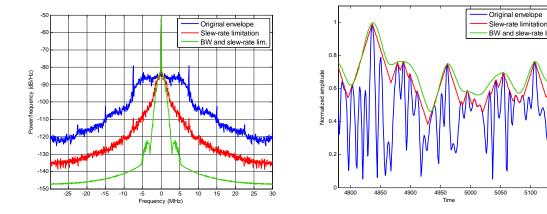

Figure (3.5) shows the time and spectral representations of the envelope and its reduced. As could be observed in this figure, the smaller is the maximum slewrate allowed the narrower the bandwidth of the resulting signal is, therefore it exists a direct relationship between these two parameters.

(a) Time representation for the original envelope(b) Frequency representation for the original en-(blue), and two different slew-rate limitations.

velope (blue), and two different slew-rate limitations.

Figure 3.5: Time and frequency representation for a 16-QAM signal and its slew-rate limitation.

# 3.4 Pulse Width Modulator

#### 3.4.1 Implementation on the FPGA

The main limitation of the pulse width modulator concerning its implementation on the FPGA was the clock speed of the processor. As explained in Section 2.4.1, in order to achieve a good result, the clock speed is desired to be as high as possible. In this way, it would be possible for a fixed bandwidth signal, to achieve a good resolution in the modulated signal and its first replica would be away from base-band in the frequency spectrum. Nevertheless, the necessity to use both the DAC and ADC, imposes a maximum clock speed of 60 MHz (see Section 3.2). On the other hand, even if higher frequencies were allowed on the FPGA clock speed, it wouldn't be possible to work using those frequencies because the hardware of the envelope amplifier also imposes limitations. Current technology allow to amplify just few MHz signals when tens of volts are desired at the output.

In order to simulate quickly and accurately the results that could yield the FPGA, initially a MATLAB script was developed. This script is shown in Figure A.1

on Appendix A and considers the signal processing involved in the modulation as well as the FPGA clock limitation.

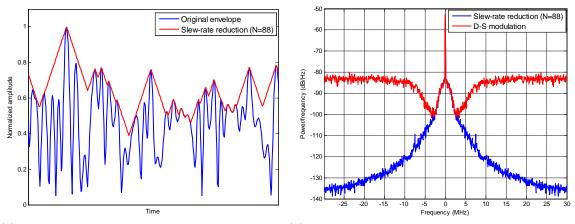

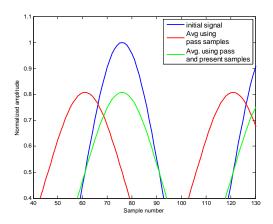

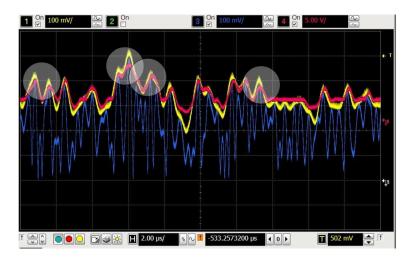

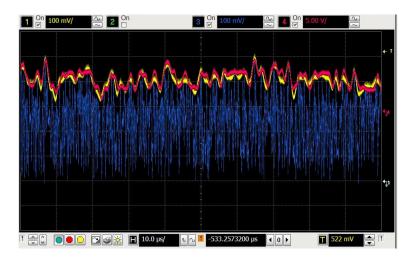

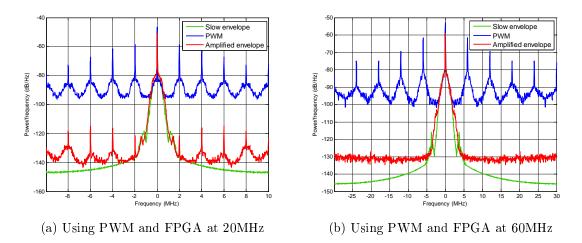

By using a 60 MHz clock and different input signals, it was determined that the maximum possible useful bandwidth could be around 2 MHz when a 6 MHz sawtooth carrier is used. This fact led to use the algorithm presented in Section 3.3, in order to reduce the envelope slew-rate up to the point when approximately a 2 MHz bandwidth envelope was achieved. Such reduction was obtained using N = 88 in the algorithm.

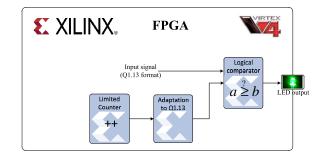

A block diagram of the implemented pulse with modulator is shown in Figure (3.6). For a correct functioning, the input should be limited in the interval [0 1) and should be represented using a 14-bit fixed-point signal with the binary point at the position 13 (Q1.13). As Figure 3.6 shows, the carrier is generated using an incremental one step counter. This counter is limited in the interval [0 9] yielding a frequency of  $f_{carrier} = 60 \text{ MHz}/10 = 6 \text{ MHz}$ . Its output is multiplied by a constant to limit it in the interval [0 9] and allow its representation using a Q1.13 signal. As final step, a logical comparator is used to determine whether the signal is above or below the carrier, yielding "high" or "low" respectively and so producing the modulated signal.

Figure 3.6: Block diagram of the implemented PWM

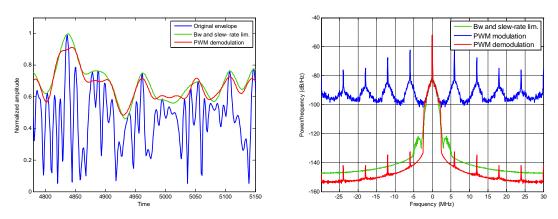

### 3.4.2 Simulation results

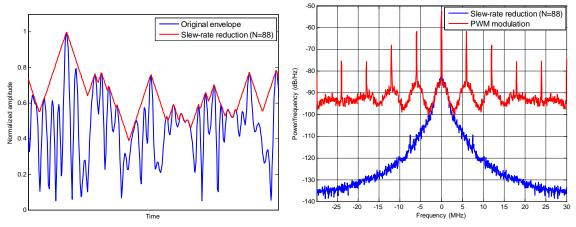

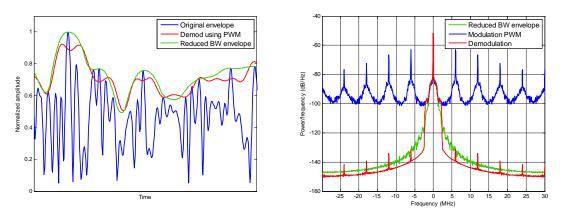

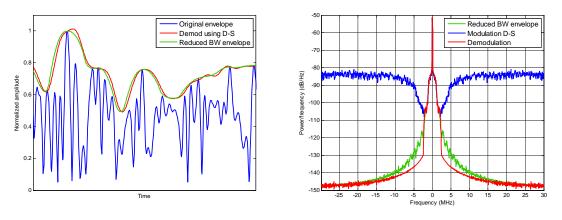

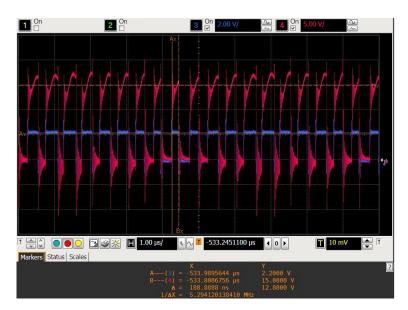

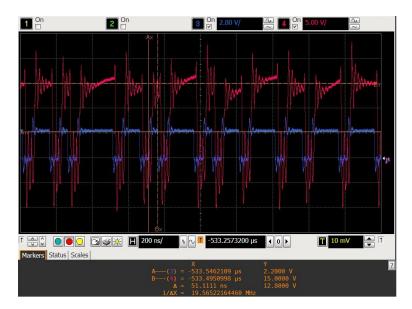

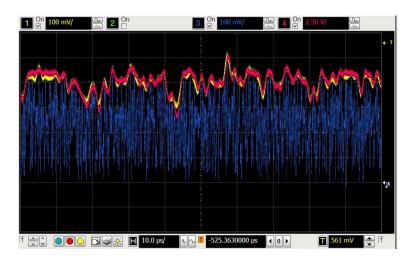

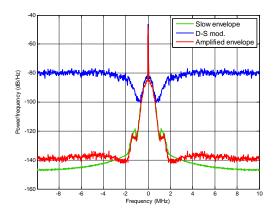

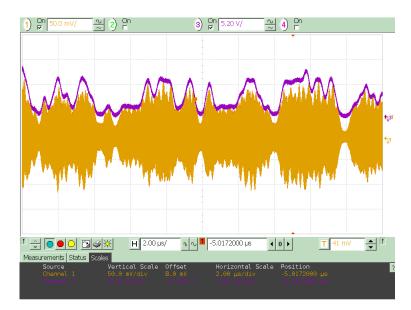

Figure 3.7 shows the graphics obtained using the pulse width modulator implemented on the FPGA. Figure 3.7a shows the envelope of a 16-QAM signal (in blue) and its reduced slew-rate version (in red) in time domain, whereas Figure 3.7b shows the spectrum of the reduced slew-rate envelope (in blue) and its modulation using PWM (in red). As can be observed, it is possible to recover only an spectrum bandwidth of around 2 MHz. Other combination of shapes and frequencies of the carrier and input signal bandwidthl lead to worse results.

Despite the limitation of the input signal bandwidth above explained, it is important to remark that variations on the PWM technique offers the possibility to

31

(a) Time representation of the original envelope(b) Frequency representation of the slew-rate lim (blue) and its slew-rate limited version (red)

ited envelope (blue) and its PWM modulation (red)

Figure 3.7: Modulation using PWM and a slew-rate limited envelope

generate pulses exhibiting more than two levels at the output, which led to better results. However since a LED was used as output to the signal, the only possibility was to implement the two level approach.

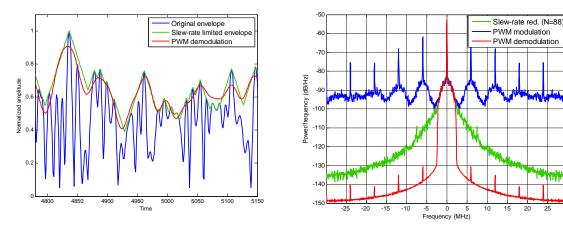

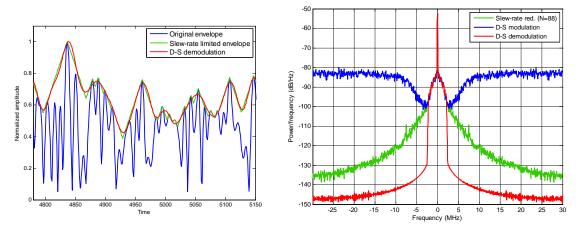

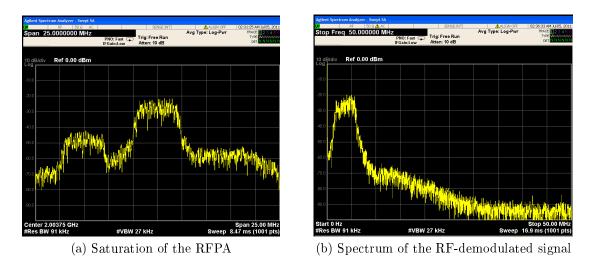

Regarding the demodulation of the signal, a simple low pass filter is enough to recover the original signal, or a similar version, since it is impossible to exactly recover the original one. A digital low pass filter was synthesized to have an idea about the appearance of the signal once amplified and demodulated. At this point it is worth mentioning that even if the precise demodulator filter was found in this step, it is not possible to reproduce in the analog domain the same filter. There exist many methods to go from analog to digital domain and vice-verse(e.g. bi-linear transform, etc.), nevertheless none of them offers exactly the same response, there are always changes on the phase and magnitude margins in addition to the errors associated with the circuit components values. However, filtering on the digital domain could give a good idea about the final output in the analog domain. Figure 3.8 shows in time and frequency representation of the pulse width modulation and demodulation process. Figure 3.8a shows the original envelope (in blue), the slew-rate limited envelope (in green) and the resulting signal once the demodulation have been performed (in red). Notice that the recovered signal is not very similar to the original one in the time domain. This difference would not be so crucial if the recovered signal was always above the original envelope, but if this is not the case, then the PA would be beyond the compression point. In other words, if the recovered signal was below the envelope it would mean that the requested output signal is greater than the supply voltage and therefore the PA becomes unable to amplify its input appearing non-linear distortion at the output.