# Design and Implementation on DSP of the ETSI GSM Adaptive Multi-Rate Vocoder

by

# Javier Martínez Morales

Supervisor:

Joan Serrat Fernández

# Contents

| Chapter 1 - Introduction                                            | 5  |

|---------------------------------------------------------------------|----|

| 1.1 Foreword                                                        | 5  |

| 1.2 Project objectives and methodology                              | 6  |

| 1.3 Memory structure                                                |    |

| Chapter 2 - GSM Adaptive Multi-Rate Vocoder                         |    |

| 2.1 Origins and present situation                                   |    |

| 2.2 Adaptive Multi-Rate (AMR) coding: general description           |    |

| 2.3 GSM AMR speech encoder.                                         |    |

| 2.3.1 Principles                                                    |    |

| 2.3.2 Pre-processing                                                |    |

| 2.3.3 Linear prediction analysis and quantization                   |    |

| 2.3.4 Open-loop pitch analysis                                      |    |

| 2.3.5 Impulse response computation                                  |    |

| 2.3.6 Target signal computation                                     |    |

| 2.3.7 Adaptive codebook                                             |    |

| 2.3.8 Algebraic codebook                                            |    |

| 2.3.9 Quantization of the adaptive and fixed codebook gains         |    |

| 2.3.10 Memory update                                                |    |

| 2.4 GSM AMR speech decoder                                          |    |

| 2.4.1 Principles                                                    |    |

| 2.4.2 Decoding and speech synthesis                                 |    |

| 2.4.3 Adaptive post-filtering                                       |    |

| 2.4.4 High-pass filtering and up-scaling                            |    |

| 2.5 Support functions                                               |    |

| 2.5.1 Discontinuous transmission (DTX)                              | 27 |

| 2.5.2 Voice Activity Detection (VAD)                                |    |

| 2.5.3 Comfort noise insertion.                                      |    |

| 2.5.4 Lost speech frame substitution and muting                     |    |

| 2.5.5 Adaptive multi-rate codec homing                              | 29 |

| Chapter 3 - Workspace: hardware and software development tools      |    |

| 3.1 General description                                             |    |

| 3.2 ADSP-2181 processor from Analog Devices                         |    |

| 3.2.1 General description                                           |    |

| 3.2.2 Architecture                                                  |    |

| 3.2.3 Instruction Set.                                              |    |

| 3.3 Running, debugging and analyzing the assembling code: VisualDSP |    |

| 3.3.1 VisualDSP interface                                           |    |

| 3.3.2 I/O streaming                                                 |    |

| 3.3.3 Profiling                                                     |    |

| Chapter 4 - Implementation and optimization                  | 44 |

|--------------------------------------------------------------|----|

| 4.1 Methodology                                              | 44 |

| 4.1.1 Preparation.                                           |    |

| 4.1.2 Procedure                                              |    |

| 4.2 Cases of special interest                                |    |

| 4.2 Cases of special interest.<br>4.2.1 Sum of products      |    |

|                                                              |    |

| 4.2.2 Common mistake: testing a memory value                 |    |

| 4.2.3 Testing 32-bit values                                  |    |

| 4.2.4 Saving one cycle per iteration in long loops           |    |

| 4.2.5 Common mistake: initializing variables in subroutines  |    |

| 4.2.6 Analog Devices bug! Use of constants in ALU operations |    |

| 4.2.7 Reutilization of memory for different buffers          |    |

| 4.2.8 Multiplication of fractional 1.15 numbers              |    |

| 4.3 Project results                                          | 54 |

| Chapter 5 - Conclusions                                      |    |

| 5.1 Project objectives accomplished                          |    |

| 5.2 Future perspectives                                      |    |

| Appendix A – Speech production and coding                    |    |

| A.1 Speech production                                        |    |

| A.2 Speech coding                                            |    |

| A.2.1 LPC-10 algorithm                                       |    |

| A.2.2 Residual excited linear prediction vocoder             |    |

| A.2.3 Multipulse LPC vocoder                                 |    |

| A.2.4 Code-excited linear prediction vocoder                 |    |

| Appendix B – Simplified instruction set for the ADSP-2181    |    |

| B.1 Assembly language overview                               |    |

| B.2 ALU, MAC & Shifter instructions                          |    |

| B.2.1 ALU Group                                              |    |

| B.2.2 MAC Group                                              |    |

| B.2.3 Shifter Group                                          |    |

| B.3 MOVE: read and write.                                    |    |

| B.4 Program flow control                                     |    |

| B.5 Multifunction instructions                               |    |

| B.5 Wultifunction instructions                               |    |

| Appendix C – Implementation of the Levinson-Durbin algorithm |    |

| C.1 ETSI ANSI-C code                                         |    |

| C.2 Implemented ADI code                                     |    |

| Bibliography                                                 |    |

| Terms & Acronyms                                             | 92 |

## **Chapter 1**

# Introduction

#### 1.1 Foreword

With the current focus on high-speed packet data transmission, it is easy to forget that the primary purpose of GSM digital telecommunication systems was speech transmission. The general perception is that the complexity of the overall system is associated with the management of the transmission link. However, there is a great deal of complexity in the compression and decompression of the audio captured by the microphone. Speech must be captured at a high enough sample rate and resolution to allow clear reproduction of the original sound and compressed in such a way as to maintain the fidelity of the audio over a limited bit rate, error-prone wireless transmission channel.

The way in which the human hearing system works allows the coder to create a perceptually similar result at the earpiece of the remote phone. The key principle behind the coders used in the GSM system is the mathematical modeling of the human vocal tract, leading to an efficient compression method for transmitting speech. A vocoder (combination of voice and coder) is used to describe these systems tailored for the compression of speech.

There are four codecs in use within the GSM that perform the compression operation. These are full rate, enhanced full rate (EFR), adaptive multi-rate (AMR) and half-rate speech codecs. The full-rate codec is a fairly computationally-efficient method of transmitting speech, but through the use of more intensive algorithms the quality of the speech can be improved. The full-rate codec was first implemented on the DSPs of the early 1990s and at that time it was not economically viable to use a better quality but more intensive algorithm. In the mid-1990s this was no longer an issue with the availability of higher power DSP cores, and so the EFR codec started to appear in handsets.

Full-rate and EFR codecs allow for good reproduction of speech when all their parameters can be decoded. Due to the redundancy on the transmission channel, many of the raw bits can be in error, but the parameters are still recoverable. However, when the parameters are lost or erroneous, the quality of the received signal decreases rapidly. It is this problem that the AMR codec attempts to resolve. By specifying a set of eight vocoders all sharing common mathematical components and operating at different rates, the amount of redundancy on the channel can be changed. This way, the quality of speech transmission can be slightly degraded by dropping to a lower coding rate, but with an increased confidence of recovering the coding parameters. The result is a better-perceived signal quality in the presence of increased interference on the carrier.

The speech coding functionality is riddled with mathematically intensive processes such as convolution, and as such is best implemented on dedicated digital signal processors with instructions to handle this type of computation. But, even with these specialized DSPs, optimization techniques are still necessary in the implementation of a stable speech codec with real-time performance.

#### 1.2 Project objectives and methodology

This project has a clear goal. The Adaptive Multi-Rate (AMR) vocoder, as defined by ETSI (European Telecommunications Standards Institute) in the GSM 6.90 standard [14], has to be implemented into a specialized digital signal processor. It has to be a "bit-exact" implementation, as defined by ETSI, and it has to be fast enough so as to work in "real-time".

The ADSP-2181 processor, by Analog Devices, is the DSP chosen for the implementation. The use of a specialized DSP is a must. Although it would be possible to implement the vocoder on a general-purpose processor, the clock speed should be orders of magnitude faster to match the same execution speed [9]. Another important decision about the processor is choosing between a floating-point or a fixed-point computational core. Although very fast implementations are available for processors that offer floating-point support within the core [11], these implementations are not bit-exact, meaning that they do not result in the exact mathematical results as the fixed-point reference implementations do. So, being the ADSP-2181 a specialized, fixed-point, digital signal processor, it fulfills all the requirements for the project.

A first, simple, approach would be trying to accomplish the implementation by only using the development tools of the processor manufacturer, in this case Analog Devices. Provided that ETSI includes C-language code together with the AMR vocoder documentation, the Analog Devices' C compiler could be used to get a straight conversion from the C code into the assembling code of the DSP [7]. The problem is the compiler is not remotely good enough for this purpose. As the same manufacturer reckons, the compiler is able to translate simple functions with good results, but using it to translate the huge amount of code of the vocoder would produce unexpected results, illegible code and poor performance. And that supposing that the vocoder worked at all. So we will have to write the whole program in assembling code, from the first to the last function of the AMR vocoder.

We can list then, in a more detailed way, the main objectives of the project as follows:

• The first objective is to study the Adaptive Multi-Rate vocoder standard, provided by ETSI. All the documentation they include has to be studied, but also the theoretical background behind it. That includes the study of voice production, voice coding and the history of the different vocoders that preceded the AMR vocoder. Throughout the implementation process, the translation of that theory to programming code will also have to be understood.

- The second objective is the study of the digital signal processor ADSP-2181, from Analog Devices, to be able to implement the AMR Vocoder into it. Part of this objective will be studying how DSP's are specialized in signal processing algorithms, and how we can take profit of the dedicated instructions to optimize the program.

- The third objective seems to be the most important objective and the main purpose of the project: the bit-exact implementation of the vocoder. Not only has our vocoder to work, but it also has to pass all the official tests provided by ETSI to guarantee that the encoded and decoded signals it produces are, bit by bit, identical to the ones expected.

- The last objective is to obtain a "real-time" implementation, that is, the time the vocoder needs to process the voice signal has to be less than the signal duration itself. Otherwise, we wouldn't get a working stable system. As we have just seen, this objective has had a first implication: the C compiler provided by Analog Devices is not good enough to be used. But there's probably a second implication: even our ownmade assembling code will have to follow a strong optimization process.

Now that we have written the main objectives of the project, let's see how they have been developed, beginning with a brief description of how this report will be organized.

#### **1.3 Memory structure**

Immediately after this introductory chapter, where we have seen the purpose of the project, in chapter 2, "GSM Adaptive Multi-Rate Vocoder", the most theoretical chapter, the study of the AMR vocoder is presented. It is one of the objectives of the project, so a detailed description is given, beginning with its "Origins and present situation". A general view is offered in "Adaptive Multi-Rate (AMR) coding: general description", and then special focus on the encoding and decoding parts is put, respectively, in "GSM AMR speech encoder" and "GSM AMR speech decoder". Finally, some additional parts of the vocoder are studied in "Support functions".

Chapter 3, "Workspace: hardware and software development tools", will describe the material, documentation, software and, in general, everything that will be necessary to develop the project. The chapter begins with "General description", where a justification of the workspace needed is presented. It follows with "ADSP-2181 processor from Analog Devices", an in-depth description of the digital signal processor that will be used to implement the AMR vocoder, with the main characteristics that made it suitable for this purpose. Finally, an important tool among the tools used throughout the project is given special attention in "Running, debugging and analyzing the assembling code: VisualDSP".

Chapter 4 is titled "Implementation and optimization" and is the most practical of all chapters. The first part, "Methodology", describes the "day-by-day" realization of the project. Then, "Cases of special interest" shows concrete situations encountered during the implementation that require a detailed explanation, and the solutions applied. Lastly, "Project results" presents the complete work done, with some numeric results that are analyzed altogether with more subjective impressions.

The last chapter, "Conclusions", tries to wrap up the project discussing about the "Project objectives accomplished" and the "Future perspectives".

There are three appendixes accompanying the five main chapters. Appendix A, "Speech production and coding" is a theoretical background to the study of the AMR vocoder, giving information about the voice signals, how are they produced and how can they be coded. Appendix B, "Simplified instruction set for the ADSP-2181", explains the basics of the assembling programming language that will be used in the implementation. Appendix C, "Implementation of the Levinson-Durbin algorithm", transcribes the complete source code of one of the functions of the vocoder (the well-known Levinson-Durbin algorithm), first the C source code, provided by ETSI as a guidance, and then the assembling code, implemented during the project.

Finally, the bibliography and a quick reference for terms and acronyms used or related to the text are included.

## **Chapter 2**

# **GSM Adaptive Multi-Rate Vocoder**

#### 2.1 Origins and present situation

In this chapter, we will focus on the study of the GSM Adaptive Multi-Rate (AMR) vocoder, which is one of the purposes of this project.

Adaptive Multi-Rate (AMR) is an audio data compression scheme optimized for speech coding. AMR operating at various bit rates is built into every GSM and WCDMA phone, ensuring that content generated by AMR can be played by virtually any wireless phone in the world, including hundreds of millions of new phones every year.

AMR was adopted as the standard speech codec by 3GPP (3<sup>rd</sup> Generation Partnership Project) in October 1998 and is now widely used in GSM and UMTS [22]. It offers substantial improvement over previous GSM speech codecs in error robustness by adapting speech and channel coding depending on channel conditions.

Initially developed for the GSM system, the single most deployed 2G mobile telecommunication system worldwide, AMR was also standardized by the European Telecommunications Standards Institute (ETSI) in 1999 and adopted by the 3GPP as the mandatory codec for narrow-band telephony in 2.5G/3G wireless systems based on evolved GSM core networks (WCDMA, EDGE, GPRS). It is also the mandatory codec for 3G

(H.324M) terminals supporting video telephony and the default codec for Multimedia Messaging Services (MMS) as defined by the Open Mobile Alliance (OMA).

Due to its great success, its scope went beyond the bounds of speech communication in telephony systems, and we can now find AMR in a number of applications: multimedia services, voice over IP, Wi-Fi telephony, portable audio devices, Internet applications, digital radio broadcasting and many more. A recent remarkable example is that, in 2006, it was included in the PacketCable 2.0 specification, an important international project that seeks for interoperable interface specifications in order to deliver real-time multimedia services over two-way cable networks.

AMR has also become a well-known file format for storing spoken audio using the AMR codec. Many modern mobile telephone handsets allow to store short recordings in the AMR format. The common filename extension is .amr.

We will here study the Adaptive Multi-Rate vocoder as defined by the GSM 6.90 standard. This European standard was produced by ETSI Technical Committee Special Mobile Group (SMG). The complete description of the GSM AMR can therefore be found in the documents provided by ETSI.

#### 2.2 Adaptive Multi-Rate (AMR) coding: general description

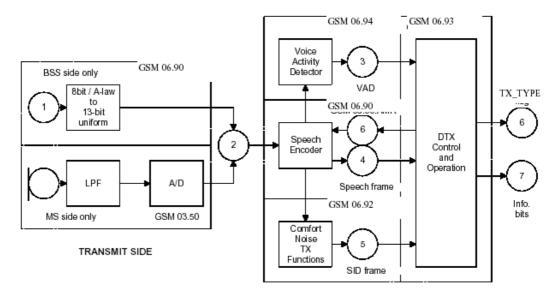

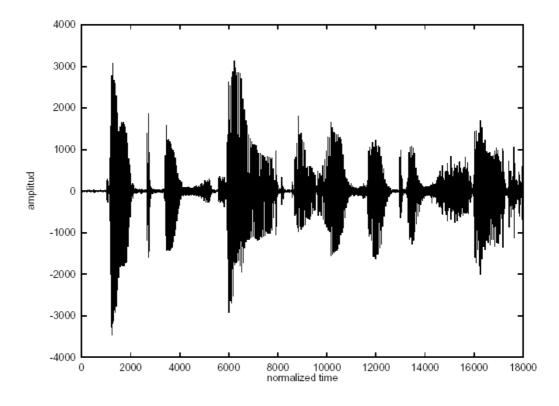

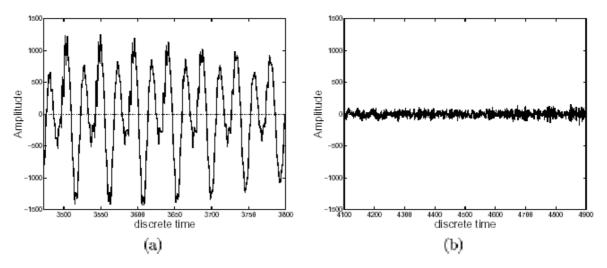

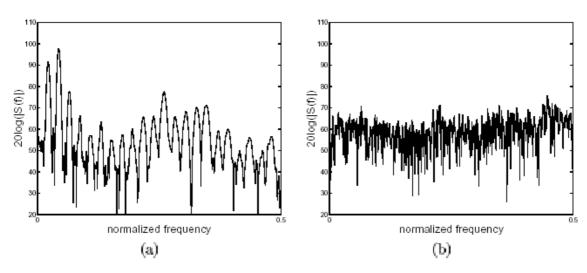

The GSM Adaptive Multi-Rate (AMR) vocoder belongs to the Algebraic Code-excited linear prediction (ACELP) vocoders. The bit-rates of the source codec for the adaptive multi-rate are: 4.75, 5.15, 5.90, 6.70, 7.40, 7.95, 10.2 or 12.2 kbit/s. Basic theoretical background concerning voice production, voice coding and the different types of vocoders can be found in the Appendix A, so here we will focus on the specific details concerning the ETSI standard [14]. Figures 2.1 (a) and 2.1 (b) present a reference configuration where the various speech processing functions are identified. In these figures, the relevant documents for each function are also indicated. The audio parts including analogue to digital and digital to analogue conversion are included, to show the complete speech path between the audio input/output in the Mobile Station (MS) and the digital interface of the PSTN (Public Switched Telephone Network). These aspects are only considered to the extent that the performance of the audio parts affect the performance of the speech transcoder.

Figure 2.1 (a): Overview of audio processing functions (transmit side)

Figure 2.1 (b): Overview of audio processing functions (receive side)

1) 8-bit A-law or μ-law PCM (ITU-T recommendation G.711), 8 000 samples/s;

2) 13-bit uniform PCM, 8 000 samples/s;

3) Voice Activity Detector (VAD) flag;

4) Encoded speech frame, 50 frames/s, number of bits/frame depending on the AMR codec mode;

5) Silence Descriptor (SID) frame;

6) TX\_TYPE, 2 bits, indicates whether information bits are available and if they are speech or SID information;

7) Information bits delivered to the radio subsystem;

8) Information bits received from the radio subsystem;

9) RX\_TYPE, the type of frame received quantized into three bits

As shown in figure 2.1 (a), the speech encoder takes its input as a 13-bit uniform Pulse Code Modulated (PCM) signal either from the audio part of the Mobile Station or on the network side, from the Public Switched Telephone Network (PSTN) via an 8-bit A-law or  $\mu$ -law to 13-bit uniform PCM conversion. The encoded speech at the output of the speech encoder is then delivered to the channel coding function.

In the receive direction, the inverse operations take place. GSM 06.90 describes the detailed mapping between input blocks of 160 speech samples in 13-bit uniform PCM format to encoded blocks (in which the number of bits depends on the used codec mode) and from these to output blocks of 160 reconstructed speech samples.

#### 2.3 GSM AMR speech encoder

#### 2.3.1 Principles

The AMR codec uses eight source codecs with bit-rates of 12.2, 10.2, 7.95, 7.40, 6.70, 5.90, 5.15 and 4.75 kbit/s [15]. The codec is based on the code-excited linear predic-

tive (CELP) coding model. A 10th order linear prediction (LP), or short-term, synthesis filter is used which is given by:

$$H(z) = \frac{1}{\hat{A}(z)} = \frac{1}{1 + \sum_{i=1}^{m} \hat{a}_{i} z^{-i}},$$

where  $\hat{\mathbf{a}}_i$ , i = 1,...,m, are the (quantified) linear prediction (LP) parameters, and m = 10 is the predictor order. The long-term, or pitch, synthesis filter is given by:

$$\frac{1}{B(z)} = \frac{1}{1 - g_p z^{-T}},$$

where *T* is the pitch delay and  $g_p$  is the pitch gain. The pitch synthesis filter is implemented using the so-called adaptive codebook approach.

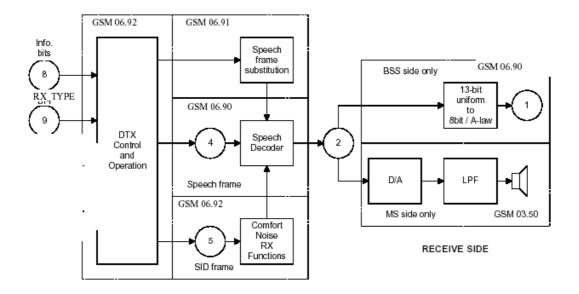

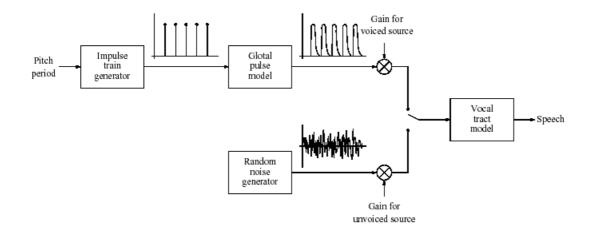

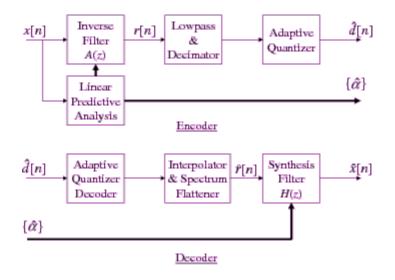

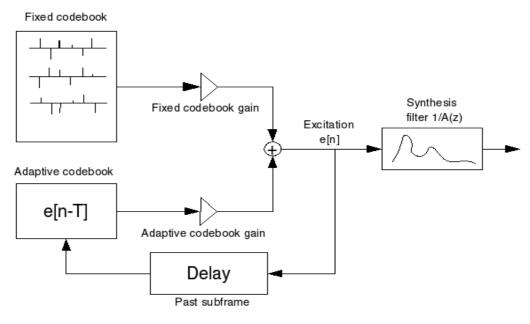

The CELP speech synthesis model is shown in figure 2.2. In this model, the excitation signal at the input of the short-term LP synthesis filter is constructed by adding two excitation vectors from adaptive and fixed (innovative) codebooks. The speech is synthesized by feeding the two properly chosen vectors from these codebooks through the short-term synthesis filter.

Figure 2.2: Simplified block diagram of the CELP synthesis model

The optimum excitation sequence in a codebook is chosen using an analysis-bysynthesis search procedure in which the error between the original and synthesized speech is minimized according to a perceptually weighted distortion measure. The perceptual weighting filter used in the analysis-by-synthesis search technique is given by:

$$W(z) = \frac{A(z/\gamma_1)}{A(z/\gamma_2)},$$

where A(z) is the unquantized LP filter and  $0 < \gamma_2 < \gamma_1 \le 1$  are the perceptual weighting factors. The values  $\gamma_1 = 0.9$  (for the 12.2 and 10.2 kbit/s mode) or  $\gamma_1 = 0.94$  (for all other modes) and  $\gamma_2 = 0.6$  are used. The weighting filter uses the unquantized LP parameters.

The coder operates on speech frames of 20 ms corresponding to 160 samples at the sampling frequency of 8000 sample/s. At each 160 speech samples, the speech signal is analysed to extract the parameters of the CELP model (LP filter coefficients, adaptive and fixed codebooks' indices and gains). These parameters are encoded and transmitted. At the decoder, these parameters are decoded and speech is synthesized by filtering the reconstructed excitation signal through the LP synthesis filter.

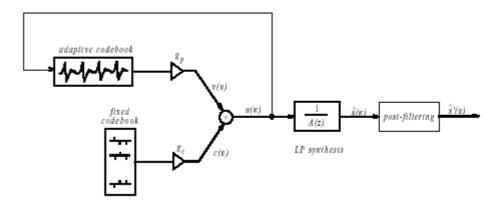

The signal flow at the encoder is shown in figure 2.3.

LP analysis is performed twice per frame for the 12.2 kbit/s mode and once for the other modes. For the 12.2 kbit/s mode, the two sets of LP parameters are converted to line spectrum pairs (LSP) and jointly quantized using split matrix quantization (SMQ) with 38 bits. For the other modes, the single set of LP parameters is converted to line spectrum pairs (LSP) and vector quantized using split vector quantization (SVQ). The speech frame is divided into 4 subframes of 5 ms each (40 samples). The adaptive and fixed codebook parameters are transmitted every subframe. The quantized and unquantized LP parameters or their interpolated versions are used depending on the subframe. An open-loop pitch lag

is estimated in every other subframe (except for the 5.15 and 4.75 kbit/s modes for which it is done once per frame) based on the perceptually weighted speech signal.

Figure 2.3: Block diagram of the GSM adaptive multi-rate encoder

Then the following operations are repeated for each subframe:

- The target signal *x*(*n*) is computed by filtering the LP residual through the weighted synthesis filter *W*(*z*)*H*(*z*) with the initial states of the filters having been updated by filtering the error between LP residual and excitation (this is equivalent to the common approach of subtracting the zero input response of the weighted synthesis filter from the weighted speech signal).

- The impulse response, h(n) of the weighted synthesis filter is computed.

- Closed-loop pitch analysis is then performed (to find the pitch lag and gain), using the target x(n) and impulse response h(n), by searching around the open-loop pitch lag. Fractional pitch with 1/6th or 1/3rd of a sample resolution (depending on the mode) is used.

- The target signal x(n) is updated by removing the adaptive codebook contribution (filtered adaptive codevector), and this new target,  $x_2(n)$ , is used in the fixed algebraic codebook search (to find the optimum innovation).

- The gains of the adaptive and fixed codebook are scalar quantified with 4 and 5 bits respectively or vector quantified with 6-7 bits (with moving average (MA) prediction applied to the fixed codebook gain).

- Finally, the filter memories are updated (using the determined excitation signal) for finding the target signal in the next subframe.

The bit allocation of the AMR codec modes is shown in table 2.1. In each 20 ms speech frame, 95, 103, 118, 134, 148, 159, 204 or 244 bits are produced, corresponding to a bit-rate of 4.75, 5.15, 5.90, 6.70, 7.40, 7.95, 10.2 or 12.2 kbit/s. Note that the most significant bits (MSB) are always sent first.

| Mode        | Parameter      | 1st<br>subframe | 2nd<br>subframe | 3rd<br>subframe | 4th<br>subframe | total per frame |

|-------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|             | 2 LSP sets     |                 |                 |                 |                 | 38              |

| 12.2 kbit/s | Pitch delay    | 9               | 6               | 9               | 6               | 30              |

| (GSM EFR)   | Pitch gain     | 4               | 4               | 4               | 4               | 16              |

|             | Algebraic code | 35              | 35              | 35              | 35              | 140             |

|             | Codebook gain  | 5               | 5               | 5               | 5               | 20              |

|             | Total          |                 |                 |                 |                 | 244             |

|             | LSP set        |                 |                 |                 |                 | 26              |

| 10.2 kbit/s | Pitch delay    | 8               | 5               | 8               | 5               | 26              |

|             | Algebraic code | 31              | 31              | 31              | 31              | 124             |

|             | Gains          | 7               | 7               | 7               | 7               | 28              |

|             | Total          |                 |                 |                 |                 | 204             |

|             | LSP sets       |                 |                 |                 |                 | 27              |

| 7.95 kbit/s | Pitch delay    | 8               | 6               | 8               | 6               | 28              |

|             | Pitch gain     | 4               | 4               | 4               | 4               | 16              |

|             | Algebraic code | 17              | 17              | 17              | 17              | 68              |

|             | Codebook gain  | 5               | 5               | 5               | 5               | 20              |

|             | Total          |                 |                 |                 |                 | 159             |

|             | LSP set        |                 |                 |                 |                 | 26              |

| 7.40 kbit/s | Pitch delay    | 8               | 5               | 8               | 5               | 26              |

| (DAMPS EFR) | Algebraic code | 17              | 17              | 17              | 17              | 68              |

|             | Gains          | 7               | 7               | 7               | 7               | 28              |

|             | Total          |                 |                 | •               |                 | 148             |

|             | LSP set        |                 |                 |                 |                 | 26              |

| 6.70 kbit/s | Pitch delay    | 8               | 4               | 8               | 4               | 24              |

|             | Algebraic code | 14              | 14              | 14              | 14              | 56              |

|             | Gains          | 7               | 7               | 7               | 7               | 28              |

|             | Total          |                 |                 |                 |                 | 134             |

|             | LSP set        |                 |                 |                 |                 | 26              |

| 5.90 kbit/s | Pitch delay    | 8               | 4               | 8               | 4               | 24              |

| 0.00 801.0  | Algebraic code | 11              | 11              | 11              | 11              | 44              |

|             | Gains          | 6               | 6               | 6               | 6               | 24              |

|             | Total          |                 |                 |                 |                 | 118             |

|             | LSP set        |                 |                 |                 |                 | 23              |

| 5.15 kbit/s | Pitch delay    | 8               | 4               | 4               | 4               | 20              |

| 5.15 KDII/S | Algebraic code | 9               | 9               | 9               | 9               | 36              |

|             | Gains          | 6               | 6               | 6               | 6               | 24              |

| ł           | Total          | -               | _               | _               | -               | 103             |

|             | LSP set        |                 |                 |                 |                 | 23              |

| 4.75 kbit/s | Pitch delay    | 8               | 4               | 4               | 4               | 20              |

|             | Algebraic code | 9               | 9               | 9               | 9               | 36              |

|             | Gains          | -               | 8               | -               | 3               | 16              |

|             | Total          |                 | ~               |                 | -               | 95              |

|             | Totai          |                 |                 |                 |                 | 33              |

Table 2.1: Bit allocation of the AMR coding algorithm for 20ms frame

#### 2.3.2 Pre-processing

Two pre-processing functions are applied prior to the encoding process: high-pass filtering and signal down-scaling.

Down-scaling consists of dividing the input by a factor of 2 to reduce the possibility of overflows in the fixed-point implementation. The high-pass filter serves as a precaution against undesired low frequency components. A filter with a cut off frequency of 80 Hz is used.

#### 2.3.3 Linear prediction analysis and quantization

#### 12.2 kbit/s mode

Short-term prediction, or linear prediction (LP), analysis is performed twice per speech frame using the auto-correlation approach with 30 ms asymmetric windows. No lookahead is used in the auto-correlation computation.

The auto-correlations of windowed speech are converted to the LP coefficients using the Levinson-Durbin algorithm. Then the LP coefficients are transformed to the Line Spectral Pair (LSP) domain for quantization and interpolation purposes. The interpolated quantified and unquantized filter coefficients are converted back to the LP filter coefficients (to construct the synthesis and weighting filters at each subframe).

#### 10.2, 7.95, 7.40, 6.70, 5.90, 5.15, 4.75 kbit/s modes

Short-term prediction, or linear prediction (LP), analysis is performed once per speech frame using the auto-correlation approach with 30 ms asymmetric windows. A look- ahead of 40 samples (5 ms) is used in the auto-correlation computation.

The auto-correlations of windowed speech are converted to the LP coefficients using the Levinson-Durbin algorithm. Then the LP coefficients are transformed to the Line Spectral Pair (LSP) domain for quantization and interpolation purposes. The interpolated quantified and unquantized filter coefficients are converted back to the LP filter coefficients (to construct the synthesis and weighting filters at each subframe).

#### 2.3.4 Open-loop pitch analysis

Open-loop pitch analysis is performed in order to simplify the pitch analysis and confine the closed-loop pitch search to a small number of lags around the open-loop estimated lags.

Open-loop pitch estimation is based on the weighted speech signal  $s_w$  (*n*) which is obtained by filtering the input speech signal through the weighting filter

$$W(z) = A(z|\gamma_1) / A(z|\gamma_2).$$

That is, in a subframe of size L, the weighted speech is given by:

$$s_w(n) = s(n) + \sum_{i=1}^{10} a_i \gamma_1^i s(n-i) - \sum_{i=1}^{10} a_i \gamma_2^i s_w(n-i), \quad n = 0, \dots, L-1$$

#### 2.3.5 Impulse response computation

The impulse response, h(n), of the weighted synthesis filter

$$H(z)W(z) = A(z\gamma_1) / [\hat{A}(z)A(z\gamma_2)]$$

is computed each subframe. This impulse response is needed for the search of adaptive and fixed codebooks. The impulse response h(n) is computed by filtering the vector of coefficients of the filter  $A(z / \gamma_1)$  extended by zeros through the two filters  $1 / \hat{A}(z)$  and  $1 / A(z / \gamma_2)$ .

#### 2.3.6 Target signal computation

The target signal for adaptive codebook search is usually computed by subtracting the zero input response of the weighted synthesis filter from the weighted speech signal  $s_w(n)$ . This is performed on a subframe basis.

An equivalent procedure for computing the target signal, which is used in this standard, is the filtering of the LP residual signal  $res_{LP}(n)$  through the combination of synthesis filter  $1 / \hat{A}(z)$  and the weighting filter  $A(z/\gamma_1) A(z/\gamma_2)$ .

After determining the excitation for the subframe, the initial states of these filters are updated by filtering the difference between the LP residual and excitation.

The residual signal  $res_{LP}(n)$  which is needed for finding the target vector is also used in the adaptive codebook search to extend the past excitation buffer. This simplifies the adaptive codebook search procedure for delays less than the subframe size of 40 as will be explained in the next clause. The LP residual is given by:

$$res_{LP}(n) = s(n) + \sum_{i=1}^{10} \hat{a}_i s(n-i).$$

#### 2.3.7 Adaptive codebook

Adaptive codebook search is performed on a subframe basis. It consists of performing closed-loop pitch search, and then computing the adaptive codevector by interpolating the past excitation at the selected fractional pitch lag.

The adaptive codebook parameters (or pitch parameters) are the delay and gain of the pitch filter. In the adaptive codebook approach for implementing the pitch filter, the excitation is repeated for delays less than the subframe length. In the search stage, the excitation is extended by the LP residual to simplify the closed-loop search. The average adaptive codebook gain is calculated if the *LSP\_flag* is set and the unquantized adaptive codebook gain exceeds the gain threshold  $GP_{th}=0.95$ .

The average gain is calculated from the present unquantized gain and the quantized gains of the seven previous subframes. If the average adaptive codebook gain exceeds the  $GP_{th}$ , the unquantized gain is limited to the threshold value and the  $GpC_flag$  is set to indicate the limitation.

#### 2.3.8 Algebraic codebook

The algebraic codebook is searched by minimizing the mean square error between the weighted input speech and the weighted synthesized speech. The target signal used in the closed-loop pitch search is updated by subtracting the adaptive codebook contribution.

The algebraic structure of the codebooks allows for very fast search procedures since the innovation vector contains only a few nonzero pulses.

#### 2.3.9 Quantization of the adaptive and fixed codebook gains

If the  $GpC_flag$  is set, the limited adaptive codebook gain is used in the gain quantization. The quantization codebook search range is limited to only include adaptive codebook gain values less than  $GP_{th}$ . This is performed in the quantization search for all modes.

The fixed codebook gain quantization is performed using MA prediction with fixed coefficients. The 4th order MA prediction is performed on the innovation energy.

After the gain quantization, the buffer with past adaptive codebook gains is updated, regardless of the value of the  $GpC_flag$ .

#### 2.3.10 Memory update

An update of the states of the synthesis and weighting filters is needed in order to compute the target signal in the next subframe.

#### 2.4 GSM AMR speech decoder

#### 2.4.1 Principles

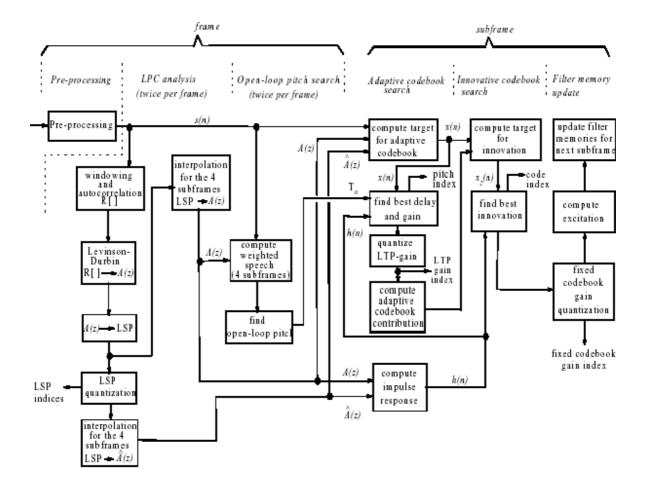

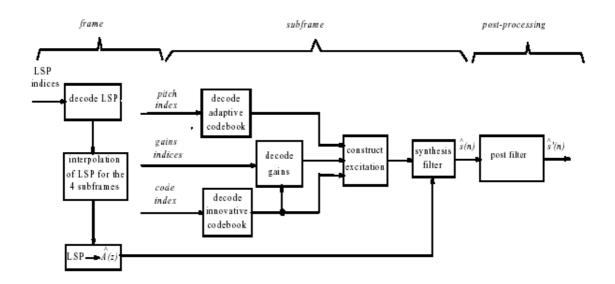

The signal flow at the decoder is shown in figure 2.4. At the decoder, based on the chosen mode, the transmitted parameters are decoded from the received bitstream at each transmission frame [15]. These parameters are the LSP vectors, the fractional pitch lags, the innovative codevectors, and the pitch and innovative gains. The LSP vectors are converted to the LP filter coefficients and interpolated to obtain LP filters at each subframe. Then, at each 40-sample subframe:

- the excitation is constructed by adding the adaptive and innovative codevectors scaled by their respective gains;

- the speech is reconstructed by filtering the excitation through the LP synthesis filter.

Finally, the reconstructed speech signal is passed through an adaptive postfilter.

Figure 2.4: Block diagram of the GSM adaptive multi-rate decoder

#### 2.4.2 Decoding and speech synthesis

The decoding process begins with the decoding of LP filter parameters: the received indices of LSP quantization are used to reconstruct the quantified LSP vectors. An interpolation is then performed to obtain 4 interpolated LSP vectors (corresponding to 4 sub-frames). For each subframe, the interpolated LSP vector is converted to LP filter coefficient domain  $a_k$ , which is used for synthesizing the reconstructed speech in the subframe.

The following steps are repeated for each subframe:

1) **Decoding of the adaptive codebook vector:** The received pitch index (adaptive codebook index) is used to find the integer and fractional parts of the pitch lag. The adaptive codebook vector v(n) is found by interpolating the past excitation u(n) (at the pitch delay).

2) **Decoding of the innovative codebook vector:** The received algebraic codebook index is used to extract the positions and amplitudes (signs) of the excitation pulses and to

find the algebraic codevector c(n). If the integer part of the pitch lag, T, is less than the subframe size 40, the pitch sharpening procedure is applied.

3) **Decoding of the adaptive and fixed codebook gains:** In case of scalar quantization of the gains (12.2 kbit/s and 7.95 kbit/s modes) the received indices are used to readily find the quantified adaptive codebook gain and the quantified fixed codebook gain correction factor from the corresponding quantization tables. In case of vector quantization of the gains (all other modes), the received index gives both the quantified adaptive codebook gain and the quantified fixed codebook gain correction factor.

4) Smoothing of the fixed codebook gain (10.2, 6.70, 5.90, 5.15, 4.75 kbit/s modes): An adaptive smoothing of the fixed codebook gain is performed to avoid unnatural fluctuations in the energy contour. The smoothing is based on a measure of the stationarity of the short-term spectrum in the **q** domain. The smoothing strength is computed from this measure.

5) Anti-sparseness processing (7.95, 6.70, 5.90, 5.15, 4.75 kbit/s modes): An adaptive anti-sparseness postprocessing procedure is applied to the fixed codebook vector c(n) in order to reduce perceptual artifacts arising from the sparseness of the algebraic fixed codebook vectors with only a few non-zero samples per subframe. The anti-sparseness processing consists of circular convolution of the fixed codebook vector with an impulse response. Three pre-stored impulse responses are. The selection of the impulse response is performed adaptively from the adaptive and fixed codebook gains.

6) **Computing the reconstructed speech:** The excitation at the input of the synthesis filter is given by:

$$u(n) = \hat{g}_{p}v(n) + \hat{g}_{c}c(n).$$

Before the speech synthesis, a post-processing of excitation elements is performed. This means that the total excitation is modified by emphasizing the contribution of the adaptive codebook vector.

Adaptive gain control (AGC) is used to compensate for the gain difference between the non-emphasized excitation and emphasized excitation.

7) Additional instability protection: An additional instability protection is implemented in the speech decoder which is monitoring overflows in the synthesis filter. If an overflow has occurred in the synthesis part, the whole adaptive codebook memory is scaled down by a factor of 4, and the synthesis filtering is repeated using this down-scaled memory.

#### 2.4.3 Adaptive post-filtering

The adaptive postfilter is the cascade of two filters: a formant postfilter, and a tilt compensation filter. The postfilter is updated every subframe of 5 ms. The formant postfilter is given by:

$$H_f(z) = \frac{\hat{A}(z|\gamma_n)}{\hat{A}(z|\gamma_d)}$$

where  $\hat{A}(z)$  is the received quantified (and interpolated) LP inverse filter (LP analysis is not performed at the decoder), and the factors  $\gamma_n$  and  $\gamma_d$  control the amount of the formant post-filtering.

Finally, the filter  $H_t(z)$  compensates for the tilt in the formant postfilter  $H_f(z)$  and is given by:

$$H_t(z) = 1 - \mu z^{-1}$$

where  $\mu$  is a tilt factor.

#### 2.4.4 High-pass filtering and up-scaling

The high-pass filter serves as a precaution against undesired low frequency components. A filter cut-off frequency of 60 Hz is used.

Up-scaling consists of multiplying the post-filtered speech by a factor of 2 to compensate for the down-scaling by 2 which is applied to the input signal.

#### **2.5 Support functions**

#### 2.5.1 Discontinuous transmission (DTX)

During a normal phone conversation, the participants alternate so that, on the average, each direction of transmission is occupied about 50 % of the time. Discontinuous transmission (DTX) is a mode of operation where the transmitters are switched on only for those frames which contain useful information. This may be done for the following two purposes:

1) in the MS, battery life will be prolonged or a smaller battery could be used for a given operational duration;

2) the average interference level over the air interface is reduced, leading to better Radio Frequency (RF) spectrum efficiency.

The overall DTX mechanism is implemented in the DTX handlers (Transmit (TX) and Receive (RX)) and requires the following functions [18]:

- a Voice Activity Detector (VAD) on the TX side;

- evaluation of the background acoustic noise on the TX side, in order to transmit characteristic parameters to the RX side;

generation of comfort noise on the RX side during periods where the radio transmission is turned off.

The transmission of comfort noise information to the RX side is achieved by means of a Silence Descriptor (SID) frame. A SID frame is transmitted at the end of speech bursts and serves as an end of speech marker for the RX side. In order to update the comfort noise characteristics at the RX side, SID frames are transmitted at regular intervals also during speech pauses. This also serves the purpose of improving the measurement of the radio link quality by the radio subsystem (RSS).

The 2 bit field TX\_TYPE indicates whether information bits are speech or SID information or if there is no information. The TX\_TYPE field is calculated from the VAD flag by the TX DTX handler. When SID information is transmitted the operation of the speech encoder is modified to reduce the remaining computation for that frame.

#### 2.5.2 Voice Activity Detection (VAD)

The input to the VAD is a set of parameters computed by the adaptive multi-rate speech encoder defined in GSM 06.90 [19]. The VAD uses this information to decide whether each 20 ms speech coder frame contains speech or not. Note that the VAD flag is an input to the TX DTX handler and does not need to control the transmitter keying directly.

#### 2.5.3 Comfort noise insertion

When switching the transmission on and off during DTX operation, the effect would be a modulation of the background noise at the receiving end, if no precautions were taken. When transmission is on, the background noise is transmitted together with the speech to the receiving end. As the speech burst ends, the connection is off and the perceived noise would drop to a very low level. This step modulation of noise may be perceived as annoying and reduce the intelligibility of speech, if presented to a listener without modification.

This "noise contrast effect" is reduced in the GSM system by inserting an artificial noise, termed comfort noise, at the receiving end when speech is absent. The comfort noise processes are as follows [17]:

- the evaluation of the acoustic background noise in the transmitter

- the noise parameter encoding (SID frames) and decoding;

- and the generation of comfort noise in the receiver.

#### 2.5.4 Lost speech frame substitution and muting

In the receiver, frames may be lost due to transmission errors or frame stealing. Some actions have to be taken in these cases, both for lost speech frames and for lost SID frames in DTX operation.

In order to mask the effect of an isolated lost frame, the lost speech frame is substituted by a predicted frame based on previous frames. Insertion of silence frames is not allowed. For several subsequent lost frames, a muting technique shall be used to indicate to the listener that transmission has been interrupted. [16]

#### 2.5.5 Adaptive multi-rate codec homing

The GSM adaptive multi-rate speech transcoder, VAD, DTX system and comfort noise parts of the audio processing functions (shown in figures 2.1 (a) and (b) ) are defined in bit exact arithmetic. Consequently, they shall react on a given input sequence always with the corresponding bit exact output sequence, provided that the internal state variables are also always exactly in the same state at the beginning of the experiment. The input test sequences provided in GSM 06.74 shall force the corresponding output test sequences, provided that the tested modules are in their home-state when starting. The modules may be set into their home states by provoking the appropriate homing-functions. This is normally done during reset (initialization of the codec).

Special in band signaling frames (encoder-homing-frame and decoder-homing-frame) have been defined to provoke these homing-functions also in remotely placed modules. This mechanism is specified to support three main areas:

- type approval of mobile terminal equipment;

- type approval of infrastructure equipment;

- remote control and testing for operation and maintenance.

At the end of the first received homing frame, the audio functions that are defined in a bit exact way shall go into their predefined home states. The output corresponding to the first homing frame is dependent on the codec state when the frame was received. Any consecutive homing frames shall produce corresponding homing frames at the output.

### **Chapter 3**

# Workspace: hardware and software development tools

#### 3.1 General description

As we mentioned in the introduction chapter, the purpose of the project was the implementation of the AMR vocoder into the ADSP-2181 processor from Analog Devices. Furthermore, we would have to accomplish, if possible, two objectives: it should be a "bit-exact" implementation and it had to run in "real-time". Let's study what kind of material we needed so as to begin with the implementation.

The vocoder description was provided by ETSI specifications. All the related documentation was available in their web site [23]. In the "ETSI EN 301 704" standard and the related documents, a complete description of the vocoder can be found (and we dedicated the whole previous chapter to study it), but, concerning the implementation, the more important document was the "ETSI EN 301 712: ANSI-C code for the AMR speech codec" [20], which provided a complete C language implementation of the vocoder. It had to be the key reference in the process of implementing the vocoder into the ADSP-2181. Finally, if a bit-exact implementation was to be accomplished, some way of verifying that exactitude was necessary, a set of speech samples to test the vocoder in all possible situations, and their coded and decoded results to compare with the obtained with our implementation. That is exactly what we got with "ETSI EN 301 713: Test sequences for the Adaptive Multi-Rate (AMR) speech codec" [21].

With all the written material, the next step was to get the necessary software tools. C code had been provided by ETSI, so a C compiler was required, as it would be necessary to run the test vectors on the official implementation of the vocoder and extract intermediate results at specific points. Those results could then serve as a reference to compare them with the results obtained from the assembling code. A good debugging environment would also be appreciated, to set breakpoints in the code and be able to examine the values of different variables. The Visual Studio 6.0, from Microsoft Corporation, was chosen. It included Visual C++ (compatible with ANSI C) and also a great deal of debugging tools.

Finally, we needed the digital signal processor itself or, better, a simulation software close enough to it that let us work most of the time fast and easily on the PC. The ADSP-2181 is supported with a complete set of software and hardware development tools. Specifically, the EZ-KIT Lite provided by Analog Devices contained all we needed [7]:

- System Builder—Defines the architecture of the hardware system.

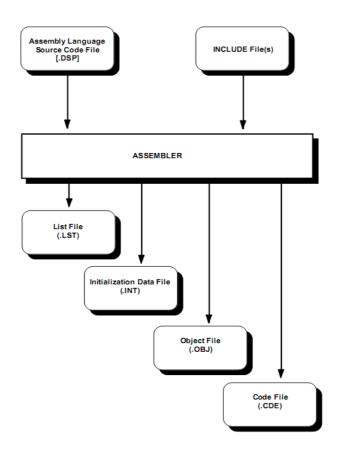

- Assembler—Assembles the source code and data modules (there was no specific source code editor, so a standard editor was used to write the code). It produces object and some other intermediate files, as shown in figure 3.1:

Figure 3.1: Assembler process

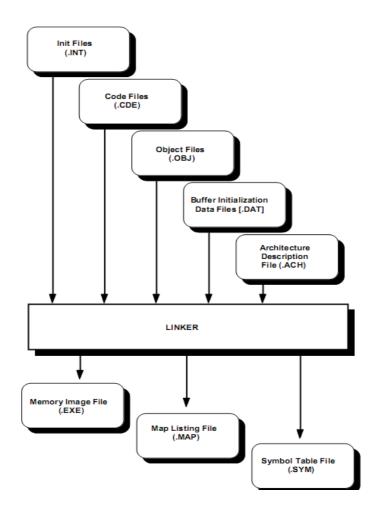

• Linker—Links separately assembled modules. It maps the linked code and data output to the target system hardware, as specified by the System Builder output. It is the module that produces the executable, as shown in figure 3.2:

Figure 3.2: Linker process

- VisualDSP—Runs, debugs and analyzes the executable program. Its importance during the development was so high that we will dedicate chapter 3.3 to examine this tool in depth.

- PROM Splitter—This module reads the Linker output and generates PROM programmer compatible files.

- ADSP-2181 EZ-LAB evaluation board—The hardware component, with the ADSP-2181 processor, where the PROM file can be loaded and the program can physically run.

#### 3.2 ADSP-2181 processor from Analog Devices

#### 3.2.1 General description

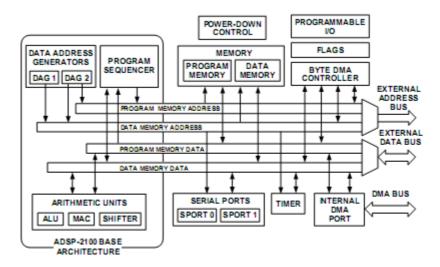

The ADSP-2181 is a programmable single-chip microprocessor optimized for digital signal processing (DSP) and other high-speed numeric processing applications. It belongs to the ADSP-2100 processors family from Analog Devices. It combines the ADSP-2100 family base architecture (three computational units, data address generators and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory.

The ADSP-2181 integrates 80K bytes of on-chip memory configured as 16K words (24-bit) of program RAM, and 16K words (16-bit) of data RAM.

Fabricated in a high speed, double metal, low power, CMOS process, the ADSP-2181 operates with a 25 ns instruction cycle time. Every instruction can execute in a single processor cycle [5].

#### **3.2.2** Architecture

Figure 3.3: ADSP-2181 architecture

- Computational Units—Every processor in the ADSP-2100 family contains three independent, full-function computational units: an arithmetic/logic unit (ALU), a multiplier/accumulator (MAC) and a barrel shifter. The computational units process 16-bit data directly and also provide hardware support for multi precision computations.

- Data Address Generators & Program Sequencer—Two dedicated address generators and a program sequencer supply addresses for on-chip or external memory access. The sequencer supports single-cycle conditional branching and executes program loops with zero overhead. Dual data address generators allow the processor to generate simultaneous addresses for dual operand fetches. Together the sequencer and data address generators keep the computational units continuously working, maximizing throughput.

- Memory—The ADSP-2100 family uses a modified Harvard architecture in which data memory stores data, and program memory stores both instructions and data. All ADSP-2100 family processors contain on-chip RAM that comprises a portion of the program memory space and data memory space. The speed of the on-chip memory allows the processor to fetch two operands (one from data memory and one from program memory) and an instruction (from program memory) in a single cycle.

- Buses—The processor has five internal buses. The program memory address (PMA) and data memory address (DMA) buses are used internally for the addresses associated with program and data memory. The program memory data (PMD) and data memory data (DMD) buses are used for the data associated with the memory spaces. The buses are multiplexed into a single external address bus and a single external data bus; the BMS, DMS and PMS signals select the different address spaces. The R bus transfers intermediate results directly between the various computational units.

- Serial Ports—The serial ports (SPORTs) provide a complete serial interface with hardware companding for data compression and expansion. Both μ-law and A-law companding are supported. The SPORTs interface easily and directly to a wide variety of popular serial devices. Each SPORT can generate a programmable internal clock or accept an external clock. SPORT0 includes a multichannel option.

- Timer—A programmable timer/counter with 8-bit prescaler provides periodic interrupt generation.

- DMA Ports—The ADSP-2181's Internal DMA Port (IDMA) and Byte DMA Port (BDMA) provide efficient data transfers to and from internal memory. The IDMA port has a 16-bit multiplexed address and data bus and supports 24-bit program memory. The IDMA port is completely asynchronous and can be written to while the ADSP-2181 is operating at full speed. The byte memory DMA port allows boot loading and storing of program instructions and data.

The ADSP-2181 architecture exhibits a high degree of parallelism, tailored to DSP requirements. In a single cycle, it can:

- Generate the next program address.

- Fetch the next instruction.

- Perform one or two data moves.

- Update one or two data address pointers.

- Perform a computation.

- Receive and/or transmit data via the serial ports.

- Receive and/or transmit via the DMA ports.

# 3.2.3 Instruction Set

The assembly language of the ADSP-2181 is often referred as simply "ADI". It's a language that, unlike many other assembly languages, uses an algebraic syntax for readabil-

ity and ease of coding. Because some assembly code will be shown in chapter 4, a brief description of the assembly language of the ADSP-2181 will be included in the Appendix B. Here, some features will be highlighted because they had an impact over the development of the project, or at least made it a little easier the always difficult task of programming in assembly language.

The instruction set is quite appropriate to the computation-intensive algorithms of the AMR vocoder. For example, sustained single-cycle multiplication/accumulation operations are possible. The instruction set provides full control of the processors' three computational units: the ALU, MAC and Shifter. Arithmetic instructions can process single-precision 16-bit operands directly and provisions for multi-precision operations are available. A 40-bit accumulator provides eight bits of protection against overflow in successive additions to ensure that no loss of data or range occurs; 256 overflows would have to occur before any data is lost [6].

There is no performance penalty for the high-level syntax of ADSP-2181 language: each program statement assembles into one 24-bit instruction which executes in a single cycle. There are no multi-cycle instructions in the instruction set.

In addition to JUMP and CALL, the instruction set's control instructions support conditional execution of most calculations and a DO UNTIL looping instruction. Return from interrupt (RTI) and return from subroutine (RTS) are also provided.

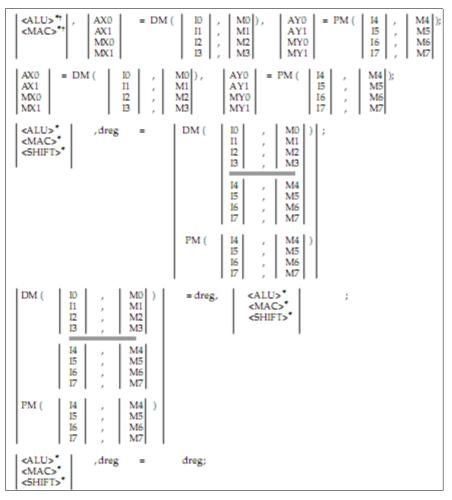

As a consequence of the high degree of parallelism of the ADSP-2181 architecture, seen in the previous section, and the 24-bit instruction words, the instruction set allows for single-cycle execution of any of the following combinations [5]:

- any ALU, MAC or Shifter operation (conditional or non-conditional)

- any register-to-register move

- any data memory read or write

- a computation with any data register to data register move

- a computation with any memory read or write

- a computation with a read from two memories

Lastly, but equally remarkable, ADI allows maximum flexibility moving data. It provides moves from any register to any other register, and from most registers to/from memory.

# 3.3 Running, debugging and analyzing the assembling code: VisualDSP

The implementation and testing of the vocoder required an absolute control over the data at every step of the execution process. Firstly, we needed a tool to execute the program without uploading it into the DSP itself, that is, in order to accelerate the testing process and being more productive we needed a PC simulator. Secondly, without the proper tool to debug the code it would have been impossible to accomplish the "bit-exact" goal. If the program does not function correctly, the ability to step through code or to run to a predetermined line and halt are very useful features. Each time the program halts, you can examine registers and memory to determine the source of errors. From the typical programming errors to the, more difficult to detect, overflow situations, they all needed a step-by-step code revision to find the exact line of the assembly program where the error was generated. Lastly, the "real-time" implementation goal required the proper tool to analyze the processor use and performance. All three requirements were met by the tool we are now presenting: the VisualDSP debugger.

The VisualDSP debugger (which we'll often call "Simulator") gives several options for running and observing program execution:

- Examining and changing the contents of memory and register windows

- Setting breakpoints to control program execution

- Defining watch points to capture program activity

- Tracing functions in the program to determine which paths are taken during specific activities

- Profiling the application's performance within defined memory ranges

- Streaming data from the test vector into the program to watch the results

# 3.3.1 VisualDSP interface

Figure 3.4 shows the distribution of VisualDSP debugger windows that was used most of the time during the development process.

| 🗯 Analog Devices VisualDSP Debugger 🛛 (Dbg Target:to   | utor) 📃                                                                             |     |

|--------------------------------------------------------|-------------------------------------------------------------------------------------|-----|

| Eile Session View Register Memory Debug Settings Wi    | indow <u>H</u> elp                                                                  |     |

| <b>***</b> *********************************           | T () *) & Q (Q (                                   |     |

| Program Memory                                         |                                                                                     | 믜즤  |

| PM [ 000060 ] uuuuuuuuuuuuuuuuuuuuuuuuuu               | Il uuuuuuu Mi uuuuuuu L                                                             | 1   |

| PM [000061] αυατασταταστασταστασταστασταστασταστασταστ |                                                                                     |     |

| PM [000063] uuuuuuuuuuuuuuuuuuuuuuuuuuuuuuuuuuuu       | I5 uuuuuu M5 1 L                                                                    | 5 🔳 |

| PM[000064]nop<br>PM[000065]nop                         |                                                                                     |     |

| PM[000066]nop<br>PM[000067]nop                         | AX0 1 AX1 uuuuuuu                                                                   | 믜즤  |

| PM[000068]nop                                          | AYO 11 AYI uuuuuuu<br>MXO uuuuuuu MXI uuuuuuu                                       |     |

| Program Control                                        | MYO uuuuuuu MY1 uuuuuuu                                                             |     |

| PC 39<br>CNIR 9                                        | MR2 uuuuu MR1 uuuuuuu<br>SR1 uuuuuuu SR0 uuuuuuu                                    | Ľ   |

| CYCLES 104                                             |                                                                                     |     |

| PM_ADDR 100                                            | 🖬 Disassembly 📃 🖬                                                                   | ۰×  |

| DM_ADDR 14336                                          | [00000023] 15 = 0x0000<br>[0000024] cntr = 0x0009<br>[00000025] ax0 = dm(i2,m0), ay |     |

|                                                        | [00000026] do ADD_LOOP until co<br>[00000026] do ADD_LOOP until co                  | 8   |

|                                                        | ADD_LOOP                                                                            |     |

| Ready Halted                                           | 27 00000068 NUM                                                                     |     |

Figure 3.4: Common VisualDSP interface

The "Disassembly" window shows the code of the program with the instruction currently executing highlighted.

"Computational" and "DAG" are used to check registers status, which was very useful to trace the data changes involved in every action.

Another important window is "Program Control". It shows some general indicators that help keep track of execution loops, for example.

Lastly, another not so often used, but also useful, windows include: "Program Memory" and "Data Memory" (to check at a very low level the content of any address in program or data memory) and "Call Stack" (to follow the execution path when using subroutines).

### 3.3.2 I/O streaming

Most of the time, it was necessary to use data input (often one of the test vectors provided by ETSI) to follow the data processing throughout the program. It was then appropriate to use the "streaming" option of the debugger. As shown in the figure 3.5, there is an option to choose sources and a destinations for the data entering and exiting the processor. They can be physical devices or, as in our case, data files.

| Streams                                                                                              | ×                                                                                                                |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| New Active                                                                                           |                                                                                                                  |

| Source<br>© Debug Target<br>SHARC Debug Target Component<br>Device: RX0<br>Address:<br>Mem Type: N/A | Destination<br>Debug Target:<br>SHARC Debug Target Component<br>Device: RX0<br>Address: Browse<br>Mem Type: N/A. |

| O File:                                                                                              | • File:                                                                                                          |

| Browsg                                                                                               | Browse                                                                                                           |

| Format: Hexadecimal                                                                                  | Format: Hexadecimal                                                                                              |

| Circ <u>u</u> lar                                                                                    | Connect                                                                                                          |

| OK                                                                                                   | Cancel Apply Help                                                                                                |

Figure 3.5: Stream configuration

## 3.3.3 Profiling

To analyze the executable program runtime behavior, the "profiling" function was used. This feature allows to select areas of code and obtain its performance on program execution, as shown in figure 3.6.

| Pr | ofile Ranges           |                          |                            | ? ×                                   |

|----|------------------------|--------------------------|----------------------------|---------------------------------------|

|    | New Profile Rang       | e                        |                            | ок 1                                  |

|    | Start Address:         | _main                    | Browse                     | Cancel                                |

|    | End Address:           | found_end                | Br <u>o</u> wse            |                                       |

|    | Memory Type:           | Program(PM)              |                            | <u>A</u> dd                           |

|    | <u>P</u> rofile        |                          |                            |                                       |

|    | Start Address<br>_main | End Address<br>found_end | Memory Type<br>Program(PM) | <u>R</u> emove<br>Remo <u>v</u> e All |

|    | 1                      |                          |                            |                                       |

Figure 3.6: Profile definition

We were especially interested in seeing the processor cycles consumption of the vocoder, divided into its different modules. That would make it possible to evaluate the optimization level of the assembly code, and if we would be able to accomplish one of our main objectives: the real-time operation of the system.

Once a profile have been defined, the program (or the part of it we are interested in) can be run and the performance results are shown, as in figure 3.7.

| 🚞 Profile  |           |        |          |            |            | _ 🗆 🗵       |

|------------|-----------|--------|----------|------------|------------|-------------|

| Start Addr | End Addr  | Memory | Exec %   | Exec Count | Read Count | Write Count |

| _main      | found_end | Progra | 80.18472 | 20382      | 22327      | 0           |

| 4          |           |        |          |            |            | F           |

Figure 3.7: Profiling results

The "Exec Count" parameter shows the number of executions of any instruction belonging to the profile, and the "Exec %" is the percentage over the total number of instructions executed. As we learned previously in this chapter, the processor executes any instruction in one cycle, so these parameters tell us the number of processor cycles used in any part of the program that we want to evaluate. We will come back to the performance issue in the next chapter, when we study some numeric results of the vocoder implementation.

# **Chapter 4**

# **Implementation and optimization**

# 4.1 Methodology

#### 4.1.1 Preparation

A simple first view to the C source code provided by ETSI [20] made it clear it was not going to be an easy, nor short, development. The vocoder was implemented into 113 ".c" code files (with their respective ".h" header files) and 22 ".tab" files for the numeric tables. Further examining the ".c" files, they contained 27636 lines of source code. It was clear that different phases had to be established: concentrating into smaller objectives would make it easier to organize and evaluate the progress of the project.

But something had to be done first. The code provided by ETSI had to work, that is, compiled, linked and executed in a PC. As it has been commented before, it would serve as a reference to verify the implementation in ADI: coding a speech sample with the "C vocoder" would give us, at any point of the process, the "officially" expected result to be compared with the one obtained with our "ADI vocoder" at the same point.

Being standard ANSI-C, it shouldn't be difficult to make the code work in our Visual C++ environment. And it wasn't. With a small change in the file "typedefs.h", to specify the platform we were working with, we got executable files, both for the encoder and the decoder. We tried then to encode and decode a real speech sample.

The file "spch\_dos.inp" is provided by ETSI together with the source code. It had to be passed through the encoder, with the file "allmodes.txt" specifying the AMR mode for each frame (in this case it switches between all possible modes) and the coded file should be identical to the "spch\_dos.cod", also provided. We performed the test and the result was the expected. Then we tried to pass the just encoded sequence to the decoder and compared it with the "spch\_dos.out" file provided. Again, they were identical.

We also wanted to perform this first test to get an idea (to some extent) of the degree of optimization it was going to be necessary in the project. The time the encoder needed to process the speech frames was an important indicator (the decoder would be much faster). With the Pentium III processor we were using, and the standard voice test sample "spch\_dos.inp", it took a little more than 10 sec. to complete the encoding of the 8.5 sec. sample (425 speech frames, at 20 msec. per frame). The PC processor couldn't make it in real time. It confirmed the demanding algorithm we were dealing with, and also confirmed that an optimization process was going to be needed when we implemented it into the ADSP-2181 [9].

With all the previous considerations, we could make a decision about the methodology we were going to follow.

#### 4.1.2 Procedure

• To divide the large implementation into smaller, more affordable, modules, we decided to follow the logical flow of the functions of the program. Beginning with the first function the speech sequence would "encounter" when entering the vocoder, that is, the "Main" function of the encoder ("Speech\_Encode\_Frame"), we would follow the same path as the speech frames, implementing the functions in the same order we found them. That way, any moment we could test the work done, from the beginning to the last point implemented. Of course, a first division was clear between the encoder and the decoder, but then we had to take our way down into lower levels. Table 4.1 shows the code hierarchy (for clarity, only the encoder is shown, with functions up to level 4, basic routines avoided).

Following the table, the order would be to begin with "Speech\_Encode\_Frame", then to "Pre\_Process", "cod\_amr", "Copy"... and so on.

| Speech_Encode_Frame | Pre_Process |                          |                   |

|---------------------|-------------|--------------------------|-------------------|

|                     | cod_amr     | Сору                     |                   |

|                     |             | Vad1                     | filter bank       |

|                     |             |                          | vad decision      |

|                     |             | Tx_dtx_handler           |                   |

|                     |             | Lpc                      | Autocorr          |

|                     |             | · ·                      | Lag window        |

|                     |             |                          | Levinson          |

|                     |             | Lsp                      | Az_lsp            |

|                     |             |                          | Q plsf 5          |

|                     |             |                          | Int lpc 1and3 2   |

|                     |             |                          | Int lpc 1and3     |

|                     |             |                          | Q_plsf_3          |

|                     |             |                          | Int lpc 1to3 2    |

|                     |             |                          | Int lpc 1to3      |

|                     |             |                          | Сору              |

|                     |             | dtx buffer               | Сору              |

|                     |             |                          | Log2              |

|                     |             | dtx_enc                  | Lsp lsf           |

|                     |             |                          | Reorder Isf       |

|                     |             |                          | Lsf_lsp           |

|                     |             | Set zero                 |                   |

|                     |             | lsp_reset                | Сору              |

|                     |             | lop_root                 | Q_plsf_reset      |

|                     |             | CI Itp reset             | Pitch fr reset    |

|                     |             | check lsp                |                   |

|                     |             | pre_big                  | Weight Ai         |

|                     |             | pre_big                  | Residu            |

|                     |             |                          | Syn_filt          |

|                     |             | ol_ltp                   | Pitch ol          |

|                     |             | oi_itp                   | Pitch ol wgh      |

|                     |             | vad pitch detection      | T iten_or_wgit    |

|                     |             | subframePreProc          | Weight Ai         |

|                     |             | subtramerreproc          | Syn filt          |

|                     |             |                          | Residu            |

|                     |             |                          | Сору              |

|                     |             | cl_ltp                   | Pitch fr          |

|                     |             | Ci_itp                   | Pred It 3or6      |

|                     |             |                          | Convolve          |

|                     |             |                          | G pitch           |

|                     |             |                          | check gp clipping |

|                     |             |                          | q gain pitch      |

|                     |             | Cbsearch                 | y gain_piton      |