# The implementation of an LDPC decoder in a Network on Chip environment

Author: Massimo Camatel

Tutor : Antoni Gelonch

thanks to: Ismael Gomez, Guido Masera, Fabrizio Vacca

In collaboration with *Politecnico di Torino*

# Index

| 1. | Abstract                                            | 4  |

|----|-----------------------------------------------------|----|

| 2. | Introduction.                                       | 5  |

|    | 2.1 The Flexible Radio Concept                      | 5  |

|    | 2.1.1 The Definition of Flexibility                 |    |

|    | 2.2 The WiMAX Standard                              |    |

|    | 2.2.1 The WiMAX main features                       |    |

|    | 2.2.2 The WiMAX physical system                     |    |

|    | 2.2.3 The 802.16e standard                          |    |

|    | 2.2.4 The error correction system                   |    |

|    | 2.2.5 Implementation Issues                         |    |

| 3. | LDPC Concepts                                       |    |

|    | 3.1 Introduction                                    |    |

|    | 3.2 Detailed Concepts                               | 11 |

|    | 3.3 LDPC Decoder Conceptual Architecture            | 15 |

|    | 3.3.1 Architecture Needs.                           |    |

|    | 3.3.2 Proposed Architecture based on NoC            | 16 |

|    | 3.3.2.1 The NoC interfaces                          | 17 |

|    | 3.3.2.2 The Master Control                          | 20 |

| 4. | PHAL Concepts                                       | 21 |

|    | Implementation                                      |    |

|    | 5.1 The PHAL Component                              | 23 |

|    | 5.1.1 The Time Slot Management                      | 23 |

|    | 5.1.2 The PHAL Architecture                         | 24 |

|    | 5.1.3 The FIFO Component                            | 24 |

|    | 5.1.4 The Deamon Components                         | 25 |

|    | 5.2 LDPC Components: VN, CN                         | 28 |

|    | 5.2.1 The ASIP Architecture                         | 28 |

|    | 5.2.1.1 The memory set                              | 28 |

|    | 5.2.1.2 The pipeline                                | 31 |

|    | 5.2.1.3 The whole block and the external interfaces | 32 |

|    | 5.2.1.4 The automatically performed instructions    | 33 |

|    | 5.2.2 The instruction set                           | 35 |

| 5.2.2.1 The main algorithm instructions              | 35 |

|------------------------------------------------------|----|

| 5.2.2.1.1 Create VN                                  | 36 |

| 5.2.2.1.2 Send VN                                    | 36 |

| 5.2.2.1.3 Create CN                                  | 37 |

| 5.2.2.1.4 Send CN                                    | 37 |

| 5.2.2.2 Other ASIP instructions.                     |    |

| 5.2.2.2.1 Charge input                               | 38 |

| 5.2.2.2 Send output                                  |    |

| 5.2.3 The ASIP main assembler program code           |    |

| 5.2.3.1 The C code and the loading connections up    |    |

| 5.2.3.2 The core of the program                      |    |

| 5.3 Tools: LisaTek, Processor Designer, ISE (Xilinx) |    |

| 5.3.1 The LisaTek Coware Tool                        |    |

| 5.3.1.1 The Processor Designer                       |    |

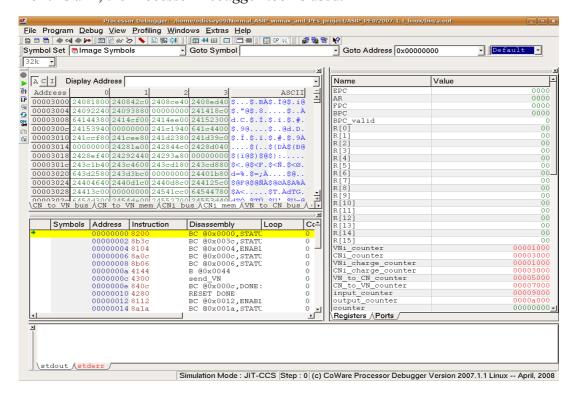

| 5.3.1.2 The Processor Debugger                       | 44 |

| 5.3.1.3 The Processor Generator                      |    |

| 5.3.2 The ISE (Xilinx) Tool                          | 45 |

| 6. Simulation Scenario and involved Platforms        |    |

| 6.1 Full Flexible Scenary                            | 46 |

| 6.1.1 Virtualization Requirements                    |    |

| 6.1.2 Resource Management                            |    |

| 6.1.3 Proposed Virtualized Environment               |    |

| 6.1.4 Current Development Status                     |    |

| 6.1.5 ALOE-based flexible LDPC decoder               |    |

| 6.2 Following the steps for simulation               | 53 |

| 6.3 The Xilinx Virtex-5 Family                       |    |

| 6.3.1 The XC5VFX70T component                        | 55 |

| 7. Results and Conclusions.                          |    |

| 7.1 The ASIP Resources Occupation                    | 57 |

| 7.2 Limitations and future improvements              |    |

| 7.2.1 Parameters Limitations                         | 59 |

| 7.2.2 View to future improvements                    | 60 |

| 8. Appendix A (main.lisa)                            |    |

| 9. Appendix B (instructions.lisa)                    |    |

| 10. Appendix C (progr_main.asm)                      |    |

| 11. Appendix D (progr_main.cmd)                      |    |

| 12. Bibliography                                     |    |

|                                                      |    |

# 1. Abstract

The proposed project takes origin from a cooperation initiative named NEWCOM++ among research groups to develop 3G wireless mobile system. This work, in particular, tries to focuse on the communication errors arising on a message signal characterized by working under WiMAX 802.16e standard. It will be shown how this last wireless generation protocol needs a specific flexible instrumentation and why an LDPC error correction code suitable in order to respect the quality restrictions. A chapter will be dedicated to describe, not from a mathematical point of view, the LDPC algorithm theory and how it can be graphically represented to better organize the decodification process.

The main objective of this work is to validate the PHAL-concept when addressing a complex and computationally intensive design like the LDPC encoder/decoder. The expected results should be both conceptual; identifying the lacks on the PHAL concept when addressing a real problem; and second to determine the overhead introduced by PHAL in the implementation of a LDPC decoder.

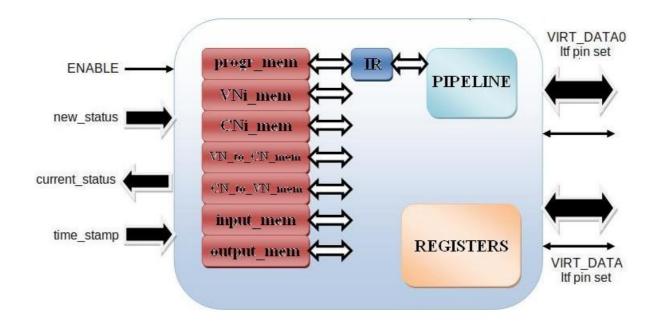

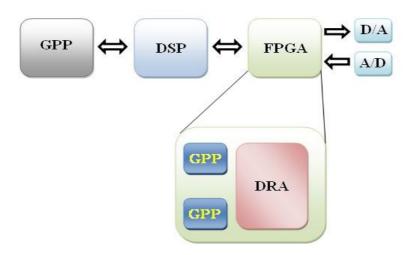

The mission is to build a NoC (Network on Chip) able to perform the same task of a general purpose processor, but in less time and with better efficiency, in terms of component flexibility and throughput. The single element of the network is a basic processor element (PE) formed by the union of two separated components: a special purpose processor ASIP, the responsible of the input data LDPC decoding, and the router component PHAL, checking incoming data packets and scanning the temporization of tasks execution.

Supported by a specific programming tool, the ASIP has been completely designed, from the architecture resources to the instruction set, through a language like C. Realized in this SystemC code and converted in VHDL language, it's been synthesized as to fit onto an FPGA of the Xilinx Virtex-5 family. Although the main purpose regards the making of an application as flexible as possible, a WiMAX-orientated LDPC implemented on a FPGA saves space and resources, choosing the one that best suits the project synthesis. This is because encoders and decoders will have to find room in the communication tools (e.g. modems) as best as possible.

The whole network scenary has been mounted through a Linux application, acting as a master element. The entire environment will require the use of VPI libraries and components able to manage the communication protocols and interfacing mechanisms.

# 2. Introduction

# 2.1 The Flexible Radio Concept

In the mid 80's, began the research of an increasingly efficient mobile communication technique, a phenomenon that continued to grow during the 90's. At the beginning there were only wired connections but the potential of wireless communication soon became evident and then, thanks to the advance of technology, the transmission of information via Wi-Fi became a reality. Since then, the demand for ever newer and more complex services for the user, required the implementation of new wireless standards. And these new standards were designed to accomplish these service requirements, such as higher bit rate/bandwidth and even more strict QoS (Quality of Service) parameters than the established standards of GSM, GPRS or UMTS.

The new standards have a double purpose; the first objective is to offer better services than those of wired connections; the second one tries to overcome the WiFi limitations due to its technological nature by offering these services even in extreme difficult conditions.

A standard, like WiFi or WiMAX, not only has to establish some restrictions and parameters and manage services for a medium. A very important feature should be to satisfy a wide description of the equipment needed for installation. Therefore, the most recent standards require a *flexible* equipment, which must be able to adapt to different conditions that may occur during their operation.

# **2.1.1** The Definition of Flexibility

The definition of flexibility in a radio context is described by four major features that a device should have. These are the following:

- **adaptivity**: literally it's the radio system automatic response to some changes in the circuit behavior by the modification of the numerical value of a set of parameters. This adaptive reaction is provided by a control feedback over some change-status signals, constantly monitored, and then by a subsequent action of an arbitrator on a number of signals;

- **reconfigurability**: it's the ability of reconfigure at a structural or architectural level some of its modules without causing a significant change to the set of parameters;

- **modularity**: describes the degree of separation and recombination of components in a system. All components can be decomposed into smaller sub-systems, faciliting the process of planning, reviewing and debugging. This way you can also have a better control of the more complex block, just by making sure that the simpler blocks work correctly separatly;

- **scalability**: is the property to handle large amounts of work when required and to maximize by combining with hardware components.

All these features, or at least some of them, are necessary to deal with all the standard requests and any inconvenience that may arise from the environment.

In fact, every standard has different restrictions and parameters about location of the terminal, its speed if moving and the quality of the required service. Joining different features services implies using different standards. If we'd want to apply to different services which exploit different standards and we are employing a terminal carrying a single standard, we should change machine

whenever we must change service.

Furthermore, many services, especially as regards the most recent ones, such as video streaming and broadcasting or high-speed internet, exploit more than one standard simultaneously (e.g., WiFi for video, UMTS for voice). For this reason too, the equipment must implement several standards or a standard flexibility way of thinking.

For this reason, to ensure flexible working and the means to support the services is something must be done. Every component related to the WiMAX technology must implement a flexible architecture or, such as in our case, a flexible processing algorithm, that could work with different codes or in different working conditions.

Finally, the speed rate of innovations in wireless standards requires an improvement of equipment capacity, through the upgrading of new software and various applications.

# 2.2 The WiMAX standard

In the new generation standard, we focused on the WiMAX, a technology for transmitting wireless network, based on the IEEE 802.16 standard. This is not a new technology, besides is a more innovative and commercially viable adaptation of a technology already in use to deliver broadband wireless services in private facilities around the globe.

It's very important for the components making part of the WiMAX equipment to respect the flexibility characteristic, since this standard will provide many new services in the most extreme conditions, like, as it'll be shown, the high-speed mobil connection (for a standard extension) and the connections in presence of particular kind of obstacles. In addition to that, since the nature of WiMAX wireless communication system is based on broadband signals, the connection of several users and lots of working transactions will be performed, increasing network traffic and requiring an efficient routing device.

WiMAX standard has the advantage of allowing a wireless connection between a Base Transceiver Station (BTS) and thousands of receiver points without requiring a direct line of sight (NLOS, Non Line Of Sight). Actually, WiMAX can overcome only small barriers, such as trees or buildings, although the supply of bandwidth turns out to be limited to 20 Mbit/s. It will never be able to overcome hills or mountains.

It can be used within a wide range of plane territories such as metropolitan areas, where it could reach the 70 Mbit/s throughput. Indeed, when the standard was developed it was thought that the transmission of broadband could reach the distance of 50 Km. But the amount of tests carried out revealed that, at the frequency of 3.5 GHz, the performance was acceptable only through few kilometres, before it started to lose efficiency. Neverthless, it's important to remember that the transmission power used (the EIRP, Equivalent Isotropically Radiated Power) during the experiments was limited to the value of 36 dBm, i.e. 4 Watts. In any case the network's coverage can be considered efficient enough.

## 2.2.1 The WiMAX main features

The main advantages making the WiMAX technology a very competitive hope for the foreseeable future in the wireless communication environment, can be sumed up as:

• **flexibility**: as the definition of flexibility assures, it's the ability of adaptation of a device or environment against a change of the whole system conditions. Or in other words, the ability to work under different working conditions or parameters;

- **security**: provides models of encryption, authentication services and security guarantees;

- **quality of service:** it's measured. The QoS parameters are latency, jitter and packet loss numerical coefficients. The WiMAX presents very low latency across the wireless span (many has less then 10 milliseconds), but also jitter tolerance and low percentage of packet loss:

- **throughput**: the IEEE 802.16 modulation system can transport a large amount of network traffic with high spectrum efficiency and excellent tolerance to reflected signals;

- **installation**: only a simple antenna is required for the basic equipment;

- **interoperability**: since WiMAX is a standard, it is independent from the apparatus or the provider;

- **mobility**: because of the 802.16e standard, the connections are available even on mobile environment at 120 Km/h;

- **cost/coverage ratio**: the economy scale of components production, in addition to the open character of the standard allows the cost reduction with the implementation of a high-speed bandwidth;

- **NLOS** (not line of sight): initially, the particular modulation performed in the WiMAX standard was used to create a wireless connection between two points that are not exactly having a direct contact sight, but within a parcially obstructed environment. Actually, some experiments revealed the decrease of bandwidth and performance: only with the advent of the 802.16e standard, the efficiency in this exceptional situation has improved, though less than expected.

These and other potential of the WiMAX brought this new technology to be used in many other fields, such as Wi-Fi hotspots connection, xDSL technology and mobile phone high velocity services and connection.

# 2.2.2 The WiMAX physical system

A WiMAX 802.16 standard network is simply made of 3 elements:

- Base Station (BS): this fixed wireless station receiver, amplifies and retransmits the signals coming from other stations faraway;

- Subscriber Station (SS): it's connected to one Base Station, with which exchanges data signal;

- *Terminal Equipment (TE)*: it's the final apparatus, by which the user is connected to the network and is able to send/receive messages.

An example of how the WiMAX network works is shown in the picture below.

The Base Station represents the gateway allowing all the users connection to the WiMAX network: it provides coverage to all the Subscriber Stations in their area of influence and manages the traffic to and from these. The Terminal Equipment (e.g., a personal computer) is connected to the Subscriber Station to deliver it via packet traffic to the Base Station that will care to send it to the final recipient.

The biggest rival technologies, we may compare the WiMAX with, are the 3G systems, such as UMTS and CDMA2000. The WiMAX appears to be superior to the previously cited technologies in speed of transmission and range of cell coverage.

For all practical purposes, a conflict has no reason to exist because WiMAX is designed to connect distant points between them, with applications as external networks that have great coverage through licensed spectrum, while on the other hand Wi-Fi has a short range (like ten meters) with no licensed spectrum, suitable only for providing a good service for a local home network.

## **2.2.3** The **802.16e** standard

The standard 802.16e was born in october 2005 to give the possibility of a mobile connection. According to the characteristics mentioned in the IEEE package documentation, this standard should help mantain the connection, while sending and receiving information, of a terminal moving up to a speed of 120 Km/h.

Basically they can be resumed as:

- band coverage of radio frequencies (2.3 GHz 2.5 GHz 3.3 GHz 3.5 GHz 3.8 GHz);

- a multiple acces OFDM (Orthogonal Frecuency Division Multiplexing) modulation splits the spaces of frecuency in several sub-carriers, reducing the interferences for terminals with omnidirectionals antennas;

- **occupation channels scalability** in order of disponibility of band;

- **better handover management**, i.e. the passage of a terminal from a base station to another holding the connection;

- roaming management.

Besides all the equipments and fixed stations already showed, the mobile 802.16e standard is provide of others apparatus, as:

- Access Service Network Gateway (ASN GW): it's the network equipment assembled with all the base stations in the coverage area. It controls the authentication functionality, managing the QoS parameters, besides of dealing with the accounting procedures and holding the encryption keys. It's in charge of the mobile IP registration, so it's mandatory for a terminal moving through different base stations be furnished with this apparatus;

- *Home Agent Mobile IP (HA)*: it supports the mobility of a terminal through differents ASN GW and the IP address changing;

- AAA server: the authentication server AAA realizes the authentication of the user through username and password or smartcard to complete the connection operations.

All these features should allow a terminal on a moving vehicle to keep the connection, as we said, up to a speed of around 120 km/h, limited by the constraints of the *handover* protocol under the QoS (Quality of Service) range. Indeed, exceeded the speed limit, the power of signal and signal to noise ratio no longer meet the requirements of quality, resulting in the inmediate disconnection of the terminal.

This leads to an handicap of the WiMAX for a user traveling at a higher speed (like on a high-speed train); at least until the improvement of IEEE 802.16 standard parameters, such as technic of modulation, bandwidth and others features of transmissing channels.

## 2.2.4 The error correction system

An essential service for the transmission that must be considered and developed as best as possible is the error correction system. Through a wireless connection, it's likely that data is corrupted and the information received is different from the original broadcast. The channel introduces errors in the information bits and the WiMAX technology has to manage a system to correct as much errors as possible, because it's not able to control the communication channel. That's true for every kind of communication technologies already in use. But since WiMAX exploits services requiring a very high quality of service, it must implement a very efficientcoding/decoding error correction system.

For that reason, redundancy of no-information bits is introduced in the information words and at the time of transmitting and receiving a decoder block uses this redundancy to correct errors.

Hence, the standard suggests the use of the following coding methods:

- Convolutional Code (CC);

- Convolutional Turbo Code (CTC);

- Low-Density Parity-Check (LDPC).

CC is now considered obsolete for the applications requiring high performances, where the CTC and LDPC codes are used. However, the complexity of CTC and LDPC codes is much higher then the CC codes, which makes it suitable for small applications where benefits are not so strict parameters.

Within the category of high-performance codes, the LDPC is, without doubts, the best choise, since there are many advantages that lead over CTC. First of all, they are characterized by the need of a fewer amount of resources, for the same quality of encoding/decoding operations, and thus a smaller amount of area occupied. Furthermore, carrying large quantities of information, LDPC shows the greatest encoding codeword length, up to 2304 bits compared to 960 bits of the CTC.

The LDPC code is based on the use of SISO (Soft-Input Soft-Output) decoders, that differ in many aspects from the oldest ECC (Error-Correcting Control) decoders. Indeed, the ECC system implements a low complexity to achieve high code rate. SISO decoders have probabilistic inputs and outputs, rather than bit frames, which forces the use of digital signal processing (DSP) to obtain useful information, resulting in greater complexity; nevertheless, they gain in code rate over the ECCs.

The DSP used for the decoding operations implements a passing iterative algorithm, a powerful error correction method for an improvement in bit error rate. Basically, this type of algorithm receives an encoded input as a frame of bit with a certain amount of redundancy. Therefore, this is used to create some messages that are internally exchanged between two sets of processing elements, called *nodes*; these instruments should be implemented in a software or a hardware. The nodes are the representation of the raw and columns of the parity check matrix used to create the code word from the original message. The exchanging of messages and the parity control done by the nodes allow to correct the errors in the code word and to extract the original message.

Hardware implementation implies that the nodes would be single blocks able to receive messages

from the other ones, process the data and eventually return them to the other nodes. In addition, since the work of the two sets must be fully separated, there should be a control unit, as a FSM (Finite State Machine) controlling and determining the temporization.

## 2.2.5 Implementation Issues

There are several ways to implement the LDPC decoder. All these methodologies have their pros and cons. There are already several solutions to the problem of LDPC decoding, each one using different technologies and different approximations. As will be discussed in the concluding part, some devices of the state-of-the-art, thought reaching excellent performances, completely lost for what concerns the characteristic of flexibility, in this case regarded as the ability for the decoder to obtain the original information by working with different LDPC codes.

In the project carried out, the importance of the characteristic of flexibility for the LDPC decoder is likely to influence the choice of hardware platform. Thus a preferred software solution is not so much a question of resources available: the algorithm structure becomes suitable to changes of the LDPC code.

The software solution, that's been adopted in this project, consists in writing a code dedicated to implement the LDPC algorithm. But in this way, the resources involved would no longer be controlled, at least not with the normal high level programming languages, such as C or C++. However, through the use of particular types of languages, such as the SystemC programming language, this is made possible.

The processor chosen to perform the passing iterative algorithm of the LDPC code is a special instruction set one, hence able to perform only a specific program code. This so called ASIP, is not meant to be for general purpose use, since the instructions, although their assembler nature, are created ad-hoc. The ASIPs are used to improve performance for a very specific application.

By the SystemC language, which is a mixture between C and the assembler code, it's performed the implementation of a dedicated assembler instruction set into the ASIP processor, customized for our purposes, in a language like C. These instructions will be executed into the main code program of the processor, the one that will represent the algorithm. Not only the instructions are implemented by the user, but every other resource in the processor is declared there, in order to avoid wastage of memory area.

The LDPC algorithm created in the software way, implemented on the program main code of an ASIP approach solution, is the better choice in order of efficiency and performance. As the number of processant nodes is relevant, in case it meants to share the nodes between different ASIPs, it will be necessary to foresee some routing operation into the ASIP instruction set. Therefore, to avoid too much work to the ASIP and mantain it effective for the algorithm purpose, it should be associated with a component managing the communications with the outside world, the PHAL. The PHAL would help the ASIP to perform the Tanner graph node operations by synchronize the steps and managing the messages delivering.

The whole LDPC encoding system will be a network of Processor Elements (PE), formed by the union of ASIP and PHAL, a so called Network on Chip (NoC).

# 3 LDPC Concepts

## 3.1 Introduction

The LDPC codes (Low-Density Parity-Check) are particular linear corrector block codes, used to correct errors of bit information transmission through channels of communication.

The name means that the code is based on a little distribution of 1's in his parity check matrix H; in other words, this matrix has a very small number of 1's in each row and column respect to the number of 0's.

This type of code was invented in 1960 by Robert Gallager during his doctorate, but since it required a computation of great complexity and since in the same years the Reed-Solomon codes, considered very suitable for error control coding, came out, the LDPC code remained unused for long time. Only from 1998, thanks to MacKay and Richardson/Urbanke the potentiality of this instrument was rediscovered and it began to get used for control purposes.

# 3.2 Detailed Concepts

The main feature of the code is the H matrix; it's been said that it has very few 1's, so if it's possible to say that H is a matrix *nxm*, it has a number of Wc 1's per raws and Wr 0's per columns, where

$$Wc \ll n$$

$Wr \ll m$

If the number of 1's in the columns and in the rows is constant, the code is regular, whether it's irregular if not.

An LDPC code is always managed starting from its H matrix, by which its manipulation it's possible to reach the generator matrix G, that permits the creation of coded informations. In fact, merging the H matrix, this is representable as

$$H = /P^T | I |$$

and then it's easy to obtein the generator matrix G as

$$G = /I | P/I$$

Therefore, using this one, the coding phase of the LDPC code involves multiplying the original message for the matrix to obtain the coded message to send:

$$c = xG$$

like all the corrector codes that add redundancy; x is the message to codify and c the encoded message to send. Since the encoding operation add some bits to better control the correction of errors, the encoded message c is bigger than the original one c; so if for example c is of 3 bits and the encoding adds 3 bits, making c of 6 bits, the code will be a c0, c0 one, ie with a c1 code rate. In the presented case, the LDPC decode is performed with a (2304, 1152) code, so it can be said that the code doubles the number of bits of information, with the same type of c1/2 code rate.

Basically there are two manner to describe this kind of code; one is the previous matrix representation, that's quite heavy having to manage very big matrices, being a 1152x2304. The other better way is a graphical representation. This is based upon a bipartite graph called *Tanner Graph*. The reason of the name is that the graph is organized in two sets of nodes and each node can be connected only to a node of the other set; the sets are

- Variable Nodes (VN): N nodes that represent the N bits of a codeword;

- Check Nodes (CN): M nodes that implement the parity-check calculation.

A VN node can be connected only with others CN nodes and a CN node only with others VN nodes. The connection among them and their number depends from the H matrix: in fact, there are *m* VN nodes, as the number of columns in the H matrix and *n* CN nodes, as the number of rows. There's a directly correspondence with the previous matrix representation because the previous (6, 3) code, for example, would be implemented through 6 Variable Nodes and 3 Check Nodes; so the same for ASIP approach to the LDPC decoding, will be implemented 2304 VN nodes and 1152 CN nodes.

A connection between the *i-th* VN node and the *j-th* CN node exists only if the bit in the H matrix at the *i-th* column and *j-th* raw is 1:

$$VN(i) \leftrightarrow CN(j)$$

if  $H(i, j) = 1$

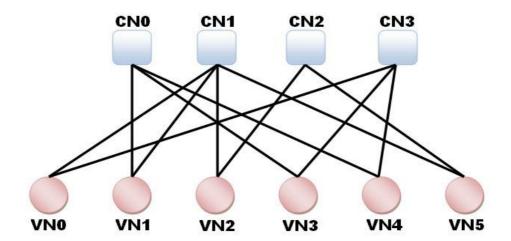

Here it's possible to see an example of Tanner Graph, although it's not a perfect example of "low density" because of the little size of the H matrix, that should be larger to respect the definition.

$$H = \begin{bmatrix} 0 & 1 & 0 & 1 & 1 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 \end{bmatrix}$$

How it's shown, there are two groups of nodes; 4 CN nodes, as the number of rows and 6 VNs as the number of columns. And there's a connection between nodes CN and VN depending on the H matrix: CN0, representing the first row, is connected to VN1, VN3 and VN4 because in those

columns of H, representing the VN nodes, there are 1's, while in the first column, for example (VN0), there's a 0 and so CN0 is not connected to VN0.

Finally, the CNs have a different number of VNs connected to its (CN0 to three VNs, CN1 to four VNs, CN2 to two VNs, ...) so this code is not a regular one.

What it's of most importance for the project aim, it's the LDPC decoding operation, by which, from a coded message, the original message transmitted must be extracted. There are many possible executable algorithms for that purpose, but the better onewhich is the considered on this work, is the *Message Passing Algorithm*. This process is based upon the continuos exchange of messages between the two sets of nodes connected to each others; the nodes are seen as computational points able to manipulate, and then send, data received in the previous phase, stored in appropriated cells of memories. The computational and sending operation phase of a group of node must be strictly separated from the other set one.

The VN nodes contain the original information, the LLR (Log-Likelihood Ratio) input as a logarithmic representation of the encoded bit. Every time space, in its computational phase, each  $Vn_j$  node, generate a message  $Q_{ji}$  for every  $CN_i$  connected to and a unique output to be stored in the memory, using all the messages previously received from the CNs:

$$output_j^{[k]} = \lambda_j + \sum R_{lj}^{[k-1]}$$

$$Q_{ji}[k] = \lambda_j + \sum (R_{lj}^{[k-1]}) - R_{ij}^{[k-1]}$$

where  $\lambda_j$  is the LLR input of the Vn<sub>j</sub> node and *l* represent the index of all the CN nodes connected to the node VN<sub>j</sub>. Here's indicated the *k* iteration and *k-1* represent the previous one.

So the output data for a node  $VN_j$  is calculated as the sum of its  $\lambda_j$  input and of all the  $R_{ij}$  messages previously received from all the  $CN_i$  nodes connected to its.

On the other hand, the  $Q_{ji}$  message for one  $CN_i$  is the sum of the  $\lambda_j$  input plus all the  $R_{ij}$  messages, except the one received from the  $CN_i$  to which the message is directed.

During the following stage of the process, every  $CN_i$  node will have been received all the  $Q_{\beta i}$  messages from the VNs; when the computational step will begin it'll elaborate the  $R_{ij}$  next messages to deliver to each  $VN_j$  connected to it, performed as follows

$$R_{ij}^{[k]} = \psi^{-1} [P_i - \psi(Q_{ji}^{[k-1]})]$$

where  $P_i = \sum (\psi(Q_{\beta i}^{[k-1]}))$

As well as the VN node one, the CN message depends on the sum of all the previously received messages except for the one come from the VN node the message is directed too. But still, now a non linear function is involved, that makes all more difficult.  $\psi(x)$  is a non-linear, non-limited function defined as:

$$\psi(x) = -\ln(\tanh\left|\frac{x}{2}\right|) = \ln\left(\frac{1 + e^{-|x|}}{\left(1 - e^{-|x|}\right)}\right)$$

Working with this function carries a lot of mathematical problems and makes the processor much more complex and heavy. Since the complexity of this function, a lot of approximations have been developed. For this implementation, the minsum approximation will be used, that simply consider the least one among all the  $Q_{\beta i}$  messages received, except the one  $Q_{ji}$  previously received from the  $VN_i$  to which the message is directed:

$$R_{ij}^{[k]} = \min_{\beta/j} |\mathbf{Q}_{\beta i}^{[k-1]}|$$

That's clearly the simpliest approximation might be used.

Summarily, the LDPC algorithm here implemented is composed by two different and sequential phases and it's for that reason called *Two Phases Message Passing* (TPMP) algorithm too:

- 1. firstly, all the VN nodes send the first message, composed only by the LLR inputs, to all the CNs connected to them;

- 2. the CN nodes, having received the Q messages from the VN nodes, elaborate the data and create an R message for each VN connected to them, then send it to all the VN nodes;

- 3. the VN nodes, having received the R messages from the CN nodes, combine the data with the input associated to each one creating the output, that will be stored in a dedicated memory, and new Q messages to send to all the CN nodes;

- 4. the process follows at point 2.

All the enumerated phases must be fully separated without overlapping, to ensure the correct execution of the algorithm.

This exchanging mechanism continues till the convergency of the algorithm and so the correction of the data input. Sometimes the convergency is puntual, so after a number more or less big of iterations, the result will arrive at a unique solution; other times the convergency is asymptotic, so the result oscillates between two values. In this case is sufficient to let the algorithm execute for a large time and then to take the obteined result.

At the end of the iterations, the Message Passing performs a large amount of data output, since the precision used for the ecoded bit is a 6-bits data information cell for each VN, i.e. 2304 bytes for WiMAX case. In fact, the encoded bit contained in the VN node is represented as the sign bit (the most significative one) in a 6-bit data information format.

Finally, when all the obtained 2304 bits are taken out, it's mandatory to remember that the nature of the LDPC code is a (2304, 1152) one: from the encoded 2304 bits will be obtain 1152 bits of decoded information, by multipling them with the H matrix:

$$x = cH$$

it's easy to demontrate this relationship. Therefore, the encoded message came from multipling the x message with the generator matrix G(c = xG), so to come back to x from the code c it's necessary to reverse the G matrix,

$$G = [I \mid P] = >^{(-I)} [P^T \mid I] = H$$

and the reverse of G is the H parity-check matrix.

# 3.3 LDPC Decoder Conceptual Architecture

## 3.3.1 Architecture needs

Once studied the Message Passing algorithm that exploits the Tanner graph, the approach that should be applied to solving the problem must be specified. In the case of a hardware approach to the graph, then by using the physical creation of its nodes and interconnections between them, the number of resources would be very substantial, given the size of the matrix H. The project was thought by a software approach, in which the nodes are not physically built into the architecture.

What is needed in the architecture of the processor ASIP thus depends on the particular variety of tasks performed. It is seen as the Message Passing algorithm performs calculations internally to nodes, such as sending and receiving packets of data, creation of output and processing input data.

Regarding the management of data packets, this function is performed entirely by the component PHAL, which should be composed of multiple functional blocks, because it also has other tasks: the package management control and synchronization, mapping of the network, ...

The ASIP, however, will be responsible for receiving and storing messages contained in the packages into dedicated memory. Since the approach focuses on flexibility, as mentioned above, the nodes contained inside the ASIP can be anyone, thus they're not tied to a single array H. The ASIP will receive and send packets with data and indications of the source node and destination node, which will interpret to deposit it in different memories depending on the buffer fields and algorithm step.

Will then be needed, apart from a program memory in which to store the main program that performs the Message Passing algorithm, other memories as separate. Besides this, of course, the architecture of the parallel type is provided, then served by a system of pipelines. Several buffers will be used to temporarily contain the input or output or for purpose of calculation. For the messages calculation will be necessary to use an arithmetic logic structure, in this context having the form of a DSP (Digital Signal Processing) located inside the platform.

| LDPC algorithm functionalities                                | Processor Involved | Architecture Resource                                                    |

|---------------------------------------------------------------|--------------------|--------------------------------------------------------------------------|

| Control and synchronization packages management               | PHAL               | FIFOs, ALU                                                               |

| Network mapping                                               | PHAL               | FIFOs, ALU                                                               |

| Message packages forwarding                                   | PHAL               | FIFOs, ALU                                                               |

| Creation messages by data messages and data input elaboration | ASIP               | Memories, buses, temporary registers, DSP                                |

| Creation output                                               | ASIP               | Memories, buses, temporary registers, DSP                                |

| Algorithm code flow                                           | ASIP               | Program Memory, program memory bus, pipeline, customized instruction set |

| FIFO-based communications                                     | ASIP, PHAL         | FIFO-based interfaces                                                    |

Therefore, in summary, the feature set provided by each processor element (PE) of the network, divided for PHAL and ASIP, as the LDPC decoding algorithm has been thought, is composed by all the components shown in the table above.

The PHAL component only needs of several FIFO where to store the incoming packets and an ALU system, because it has only to check the fields of the buffer to interpret, thus to forward it through the correct destination. Was chosen to use a standard FIFO-based communication system made of data buses and control signal for comfort of use: its operation will be explained later.

The ASIP has much more duties and responsabilities into the LDPC decodification, since it must keep memory of the incoming messages to then process them and create new messages and output. So it will need several memories where to store data messages and the origin/destination nodes information and DSPs to perform calculations. Finally, since the Message Passing algorithm is exploited through an assembler instruction set code, must be given an extra memory where to save the code and a set of instructions that performs the algorithm.

## 3.3.2 Proposed Architecture based on NoCs

The Message Passing algorithm operations, the LDPC decoder requires, are very heavy to support. This depends on the fact that a large amount of data must be elaborated: the H matrix of the WiMAX case is 1152x2304, so the Tanner Graph system needs 2304 VN nodes and 1152 CN nodes. By using a single processor element to perform the algorithm, all the nodes should be allocated in only one component. This approach would occupy a great bandwidth and a lot of resources, with the consequence to be very slow and to consume a lot of energy.

The idea is to split the nodes among more processors ASIP, as reduce the complexity and the power consumption (joined to the time of execution) of each one. There will be no longer a unique Processor Element (PE) but different PEs connected in a dedicated network, or a Network on Chip (NoC). In advance, this would be a specific NoC, because the protocol of communication and the performed operations are specific for the LDPC decoding algorithm aim, becoming an ASNoC (Application Specific NoC).

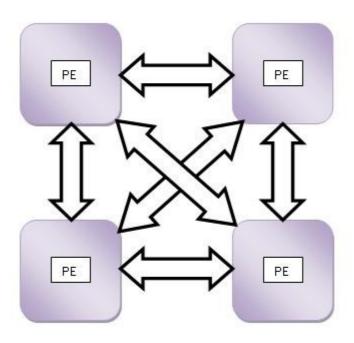

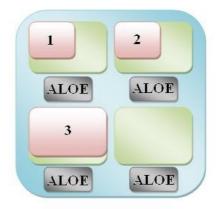

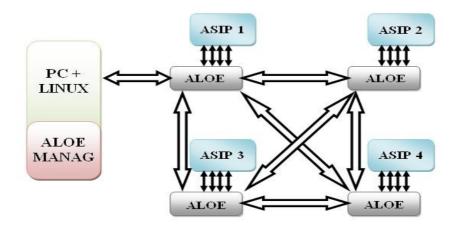

The entire structure can be illustrated like an all-connected network of equal elements in the figure below.

The network is composed by 4 PE interconnected each others by 2 pair of buses, including a 32-bit word through which the data will be delivered plus some singol bit control signals. All the components have a unique clock, distributed by an external Linux master controller that delivers its control message packets via synchronization and control interfaces.

Every PE is formed by the union of 2 separeted components, as already said: one ASIP, that contains a part of VN nodes and a part of CN nodes and it's responsible of the calculation tasks and output storing; one PHAL, a processor working as a router, whose duty is to deliver messages and to manage packets through the network.

#### 3.3.2.1 The NoC interfaces

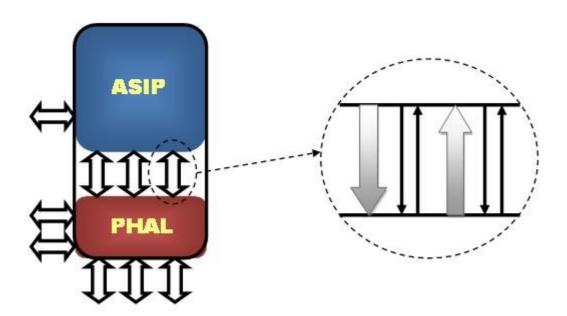

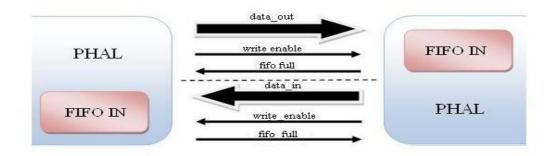

The PHAL is the only part of the PE responsible to communicate with the ASIP and with all the others processor PHALs; a simple scheme is shown in figure below.

Every ASIP has 3 interfaces with its PHAL, one for each PE to which the message can be delivered; in this manner, the PHAL can be built with an easier logic, since it automatical knows that if a word came from a virtual interface (the connection ASIP-PHAL), it must be sent to a particular output interface (the conection PHAL-PHAL). Hence the PHAL needs only a simple routing map associating one virtual interface with one and only one data output interface.

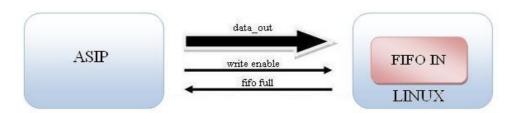

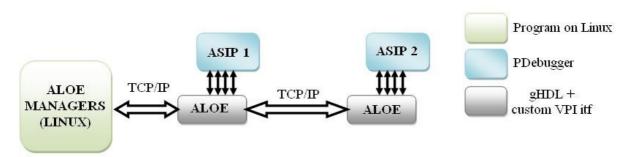

There are different type of interfaces; indeed, there's an interface ASIP-PHAL, one ASIP-Linux, a PHAL-PHAL interface and a PHAL-Linux one.

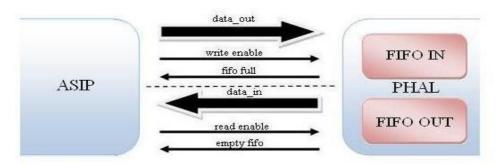

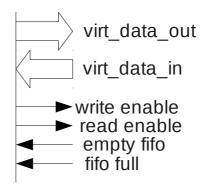

Every interface as a behaviour different from the others but the common thing is that each one is made of two 32-bits word bus data, one for the input and one for the output, plus four control signal, two for each data bus (one empty-fifo controller and one read-enable for the output plus a fifo-full controller and a write-enable for the input).

The distinction between the interfaces depends on how these signals affect the logic of each component.

Before to explain the way of working of the different interfaces is important to describe the storing method. The ASIP interfaces aren't fifo register systems; they don't have temporary registers where to store information packets to deliver, because they process the arriving data and they need it for a longer time. Because of that, they have several memories where to store data bytes. Instead, every

PHAL has a complex fifo interface system: two fifos (one for input and one for output) for data packets to and from each ASIP interface; one input fifo for the data arriving from other PEs; two fifos for the control and two fifos for the synchronization interfaces.

Let's see all:

• **ASIP-PHAL**: the ASIP doesn't have fifos, so it has to store the input data directly in memory; similarly, when it has data to send, it must throw it out immediately. So, the PHAL must have two fifos where to store data temporarly.

If the ASIP needs to send data, looking the fifo full control signal from the PHAL output fifo for that it doesn't get filled, it set the write enable and put the word in the output 32-bit bus. Meanwhile, when the PHAL input fifo contains some data word for the ASIP, it puts low the empty fifo control signal; in that manner, the ASIP will know that there's some data to adquire. By settin the read enable control signal it will get the word to be stored in its memory.

• **PHAL-PHAL**: two PEs exchange data word informations through its PHAL. Since the operationws are managed by only one FSM each component, when data's arriving it might be performing other tasks. For that, it's fitted with an input fifo, so that the output data can be throw out anytime it's desired: although the PHAL is doing other tasks and it can't look at the input interfaces, incoming data is stored in the fifo registers and the PHAL will check the packet later, when it'll have time to do it.

The signals are the same but are managed in a different way. The data sending out is performed by each PHAL as the ASIP does: it throws out words through the 32-bit data out bus and setting the write enable, checking the fifo doesn't get filled. But for the reading phase, the PHAL doesn't look at the control input signals. In fact, the PHALinput interface has an incorporated fifo working alone, storing data input in its registers. The PHAL looks directly at its empty fifo signal to obtein incoming packets.

• **ASIP-Linux**: between each ASIP and the Linux Controller, there's a particular communication chanel (*virtual interface 0*) dedicated to the exchange of initialization and final information data packets. In this case, in which the initialization is performed statically, this interface is used only by the ASIP sending the output data words to the Linux Controller at the end of the LDPC decoding iterations.

When the ASIP arrives at the last operation step, delivering out the algorithm results, it sends to the Linux Controller the data in as well as all the other interfaces, through a 32-bit width bus and setting the write enable.

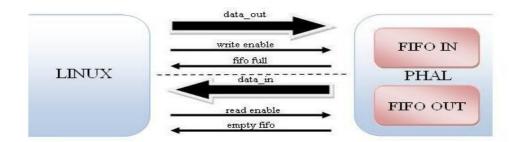

• **PHAL-Linux**: the aim of the PHAL is primarly to monitor the correct execution of every process task. It has to receive orders from the master and report the status of the algorithm, so it needs two interfaces to the Linux Controller, one to and one from that. In advance, the synchronization Deamon in the PHAL needs a periodical communication with its master, to request the correct time and synchronize it to one unique time clock; so it needs two more interfaces to the Linux Controller.

The Linux master controller has to face with many duties and tasks. It will not be always able to check incoming pakcets form the PEs. Therefore, the ideal way of exchanging information is that the master could decide each time when do adquire the informations contained in the PHAL fifos by controlling the fifo full signals. Each PHAL will store data in an output fifo connected to the master and input data information form the master will be stored in an input fifo internal the PHAL component. In total, the PHAL, with two register fifos for control operations and two for synchronization operations, will be able to manage all the communications with the master control.

The Linux Controller is directly controlling the exchanging performance with the PHAL, while this is only concern of watching constantly at the fifo input and charging the fifo output with data to throw out.

#### 3.3.2.2 The Master Control

Theoretically, one of the four PE should act as the master, ie set a master clock time to synchronize all the other elements and manage the execution orders of the LDPC algorithm. In practice, as the NoC has been implemented with all-similar PEs, neither of the processing elements has the power to influence the instruction flow. The role of arbiter is played by an external Linux-based controller inglobing all the network and acting for the components from an higher point of view.

Communicating rather with the PHAL then the ASIP, it requires the commands to manage the execution by delivering some information packets to each PHAL. So the Linux external controller take in charge when loading the applications onto the ASIPs, when beginning the initialization procedure and running up. Eventually, as the figure of a user, it makes the LDPC algorithm converging, establishing how much time slot cycles are necessary for the error correction system.

The only real function dedicated to the PHAL is the time slot division, being up to this component setting the ENABLE time slot signal to the ASIP. Actually, the time slot duration has been previously decided by the PHAL code programmer.

There might be a future improving implementation. One another possibility, in fact, could be that the Linux (like any other) master controller, during the initialization phase send to each PHAL the time slot duration required by the LDCP complexity. Other still better solution could be to make it *flexible*, i.e. let the PHAL change the time slot duration value. With an additional part, the PHAL could check if all messages are sent in time before the beginning of the next time slot, and so to lengthen or to shorten this time dinamically.

It'll be explained, in later chapters, as the external control relies on VPI libraries to function and to communicate with the various elements of the network.

# **4 PHAL Concepts**

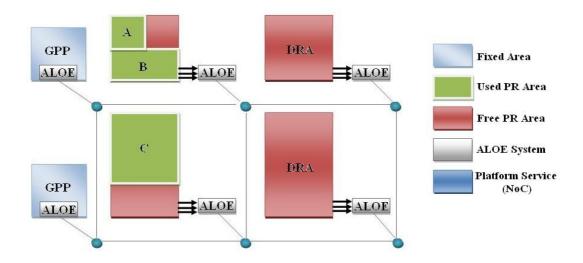

The PHAL concept tries to address the main issues related with the Software Radio technology. It assumes the need of supporting reconfiguration of the radio processing chain, the need to deploy the radio application onto a heterogeneous hardware platform capable to assume the high computing requirements of modern wireless systems, the need to assure strong real-time execution constraints, the need to easily develop and integrate software modules and the possibility to execute them in different types of processors assuming an easy portability.

One of the most relevant objectives in the process of defining a common framework to develop and deploy software radio applications is to eliminate platform (hardware and support software) dependencies. On the other hand, radio applications are built through a set of software modules (hardware or software based) that communicates among them. The common used terms denominates such modules as "objects". Therefore each one of such objects are signal processing blocks, some of them with important requirements in terms of computing resources, that needs to acquire/deliver information from/to other objects through proper interfaces. Nevertheless, one of the most relevant assumptions of PHAL-OE is that such interfaces between objects are unknown at object development time. Only at execution time all the required objects will be integrated and the entire radio application will be built.

All these objectives have pushed us to define and develop a multi-platform software abstraction layer and execution environment, ALOE (Abstraction Layer & Operating Environment), capable to provide such features. The list of the main functionalities where the PHAL-OE must provide support on includes:

- **Flexibility:** the framework must efficiently implement the flexibility concept required by SDR. It is assumed to be based in the capacity to facilitate the reconfiguration as the basic mechanism providing flexibility;

- **Execution control management :** the coordinated execution of the whole system must be assured;

- Hide the platform heterogeneity to the radio application: abstraction layers are required are basic mechanisms to provide such feature;

- **Computing resource management :** under a scenario with limited computing resources the need of a specific mechanism to manage the available resources promotes the efficiency in the whole system and extends its interactions with the radio resources management part. In addition it is capable to assure the overcoming of the real-time constraints;

- Data packet oriented messaging: not processor (device) oriented communication mechanisms. Data packet oriented communication network among the heterogeneous processors is built;

- Parameter or variable (signals) evolution capture during the execution of the application;

- Processing resource parameters evolution captured for autonomous management or control;

- **Auto-learning/cognitive capabilities** for the internal resource management can be easily incorporated:

- Support to the Cognitive Radio strategies thanks to the capacity to capture, in a

coordinated way, relevant information from different layers of the radio and computing system;

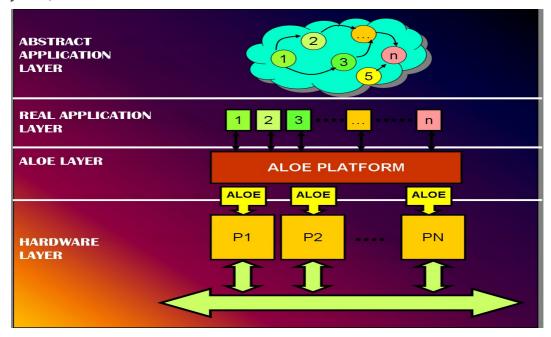

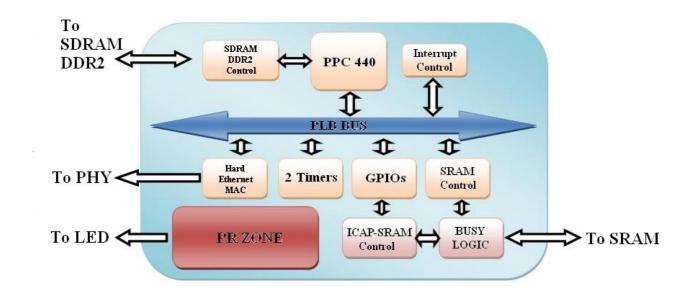

Previouse figure tries to illustrate the PHAL-OE concept. On the bottom we can see the Hardware Layer where we can found several processors or Processing Elements (PE) physically interconnected among them. On top of the figure we can see the Abstract Application Layer where a graph of a radio application tries to define the required tasks (objects) and the data flow among them. In the Real Application Layer we can see the previous tasks but using the services or functionalities provided by PHAL-OE to build coherently the radio application. On the PHAL-OE Layer we observe that from the point of view of the tasks (objects) conforming the radio application all them only see the same platform, the PHAL-OE Platform, not being aware of any detail related with the hardware. On such layer, but from the hardware point of view, we can find the specific implementation of the PHAL-OE functions for each one of the processors used to build the entire Hardware Layer.

# 5 Implementation

# **5.1 The PHAL Component**

Let's focus on this section of the whole PE. The PHAL component is the peripheral part of the Processing Element or it can be better considered as the interface between the ASIP (ie the real processing part) and the external world. Indeed, it's basically responsible of the routing operations, since it controls the packet traffic to and from the ASIP component, and so permitting the data exchanging through the entire network.

Plus, the PHAL has the duty to manage the control and synchronization packets coming from a master that's been controlling the LDPC decoding operation: if the entire system was a network made of several elements, it would have to control and synchronize it.

## 5.1.1 The Time Slot Management

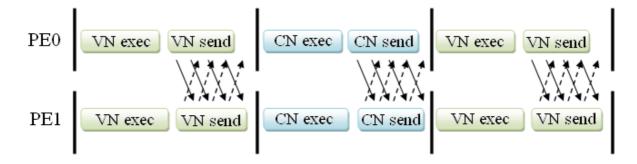

As it's been said, each ASIP in the PE must be able to execute the VN node operations and the CN operations alternatively. Since the two operations must be performed separately, it's mandatory to implement a time slot, in which each operation node phase is alternately executed without overlapping: for this reason, the PHAL has a timer inside that scan the enable execution time of each operation.

Each time slot, the ASIP, alternately, performs the node operation (Variable or Check) as a calculation phase and then sends all the messages created through its data interfaces. The associated PHAL gets these messages and delivers it into the network.

The time slot must be calculated for there will be time enough to perform the node calculation and sending operations. In fact, at the beginning of the next time slot and so of another calculation step, all the data must already be arrived to destination and stored in memory.

The PHAL, following the master directive, worries that its ASIP does its job and does it in a resonable time; it controls the change of status of the ASIP and the time partitioning of all the system, including the time slots.

## **5.1.2** The PHAL Architecture

Unlike the ASIP, that's a SystemC code based processor, the PHAL has been created using the VHDL hardware code (Vhsic Hardware Description Language). That's because this part wasn't thought to be too large, being only a router component and the idea of using an ASIP-like microprocessor, with dedicated resources and instructions, seemed a waste of space.

On the contrary, a VHDL-based architecture allows to have a FSM with very few resources and the possibility to join different pieces; finally, all the component is implementable on a FPGA board with the characteristics shown in the table below:

| Number of Registers     | 9193        |

|-------------------------|-------------|

| Number of Look Up Table | 6561        |

| Number of IOs           | 583         |

| Minimum Clock Period    | 4.828 ns    |

| Maximum Frequency       | 207.108 MHz |

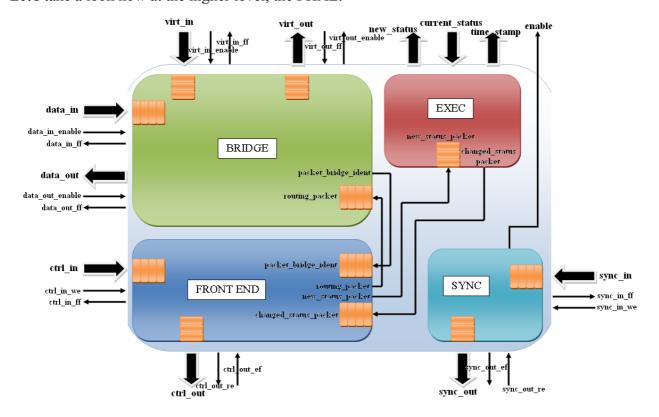

It's possible to see in the figure in the following pages that the whole PHAL system is formed by the union of different blocks joined together to perform all the basic communication and control tasks. The fundamental idea is the modularity feature, hence the possibility to add or remove blocks, adding operations (such as the statistical one) or removing its from the scenario. There's no danger of signal conflicts because each input/output and each register is managed by only one block at a time.

A block unit is thought to act as a Deamon, performing a specific task and aim, capable to control only a part of the input/output signals and of the resources, but responsible of an entire process. They're composed, each one in a different way, by a finite state machine (FSM) having the role of signal managing, data processing and output delivering. The interface mechanism of each Deamon block is fifo-based: all the signals moving through the network from or to other Processing Elements are stored in fifo registers controlled by the FSM in each block through the signals in the fifos. The number of fifos and kind of interchanging between blocks will be discussed in an other chapter.

## **5.1.3** The FIFO Component

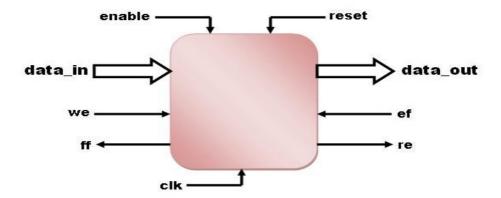

The fifos used in the PHAL component belong to the same model, with the same mode of function. The main shape of this component is shown in a figure of the next page.

The considered component is more then a fifo, because it manages a real complex storing function. It's composed mainly by a parallel-in-parallel-out collection of registers, in the format of 32-bits words. There's only one clock signal entering, so that it's completely synchronous, with the same temporization for the Writing process and for the Reading process. It has an asynchronous reset input, connected to the outsider general reset that clean all the registers and set its to an all-zeros value. Plus, even if not essential, it's performed an enable input that actives the fifo when pulled at a high level.

For the operations of writing and reading, the system manages the parallel data input and the parallel data output (of a word dimension) with a write enable and a read enable and two others wire reporting the state of the fifo (full in one case and empty in the other one).

When the write enable is pulled up, the fifo block gets the word that finds at the data in

input and stores it into the first free register, once every clock period (on the rising edge) until the write enable (*we*) is at logic '1'; for sure, when in the fifo there will be no free space, the fifo full output (*ff*) will be internally pushed to high level. For that reason, the external agent pushing data into the component must control that signal and stops in case of fifo full to prevent the overwrite of informations already stored in the register memory.

On the other side, the fifo is always pushing out on the *data\_out* output pin the first word in the registers, but till the read enable (*re*) will not be pulled up to '1', it will not throw out anything.

Generally, monitoring the empty fifo signal (*ef*), the outside agent can realice when information data is stored, put the read enable input to '1' and start catching words, one for each clock period. Every time that the read enable is put to '1' the data is thrown out and borrowed from the internal registers. When, finally, the fifo will not have more words, the empty fifo will be put to '0'.

# **5.1.4 The Deamon Components**

Let's take a look now at the higher level, the PHAL.

The actual version is made of 4 main blocks:

• FRONT END: it's responsible of the command and control operations of the whole system. It receives the command packets from the master controller, that are stored in a dedicated fifo. Moreover, the outgoing packets are not sent directly to the master, but they're stored in another fifo so that, when the master could, it will catch it in order to obtain the PHAL informations.

It has two other fifos, by which it can receive informations from other blocks of the PHAL and so better manage the correct execution of the algorithm. One of these fifo receives the informations on the changing status process from the EXEC block. Each time the status of the ASIP has been changed by the EXEC Deamon, this has to make known the FRONT END of the new status. It does it by sending a packet to this fifo.

The other fifo is done to contain the packet received by the BRIDGE block during the bridge identification operation.

There's only one FSM controlling the execution of all the commands in the entire Deamon. After an initial reset, to make the machine began in a known status, the "Registration to the master" packet is built. It carryes the ID randomly proposed, so the fifo *ctrl\_out* is filled with all the packet, waiting for the master removing all.

Then, the FSM remains in a waiting state, monitoring the empty fifo signal of each fifo from where new packets could come: the *ctrl\_in*, the *packet\_bridge\_ident* or the *changed\_status\_packet* one. And every time one of this contains a packet information, the FSM flow follows a different operation branch.

When the *packet\_bridge\_ident* fifo is no longer empty, it means that the bridge identification operation must be performed. The FSM takes all that packet, put a header and send it by the *ctrl out* interface to the master.

In the other case, when the EXEC block responds to a changing status process and returns the actual status of the ASIP by the *changed\_status\_packet* fifo, the FRONT END communicate it to the master, by building the "Watch object status change" packet and sending it through the *ctrl out* interface.

When's arriving a packet from the *ctrl\_in* interface, the PHAL firstly realizes two control packet operations: checking the first word (must be the HEADER MAGIC constant value, otherwise the packet is trashed) then controlling the size of the received packet having the same of the one reported in the header. Finally it looks at the type of command and executes:

- 1. FRONTEND\_REGISTER\_ACK: it's the response of the master to the request of an ID made at the boot. The FRONT END changes the ID and communicates it to the BRIDGE;

- 2. EXEC\_SETSTATUS: it's the command to change the ASIP status. The information of the new status is sent by the *new\_status\_packet* output by filling the fifo in the EXEC block;

- 3. BRIDGE\_ADDITF: this packet containes the field to create the routing table of input (external to virtual interface) and output (virtual to external interface) in the BRIDGE component. The four words in the packet with the routing informations (input/output, header, virt\_itf and ext\_itf) are then sent to the fifo in the BRIDGE block;

- 4. BRIDGE\_IDENT: when receiving this command, the FRONT END advertises the bridge that must deliver a packet through each *data\_out*, to make known all its neighbours of its presence. And to avoid the waste of another dedicated fifo, a single

word packet is sent to the routing fifo of the bridge, that'll be aware of this command because of its format.

• SYNC: the synchronization component is made of two fifos, connected to the interfaces <code>sync\_in</code> and <code>sync\_out</code> allowing the communication with the master, and one timer counter. This is the only block controlling the temporization and the time slots. In fact, synchronous with the clock, it punctuates the time and returns to the system the count of microseconds and seconds. But its main task involves the indication of a new time slot beginning to the ASIP via the ENABLE pin activation.

Because of inaccuracies, the timer watch is subject to drift; to avoid this problem, the SYNC block periodically sends to the master a synchronization request, to which the master will responde with its master time. This will be used to correct each SYNC Deamon time.

The FSM of the SYNC block provides, like the one of the FRONT END, a boot stage. During this first step, it creates the "Register to sync\_master" packet and send it through the *sync\_out* interface. Then it just lays in a waiting step, while it keeps monitoring if something arrives through the *sync\_in* interface. In this case, when a packet arrives from the master control, it's the "Synchronization Acknowledgment Packet", containing the master time to correct the SYNC timer. Otherwise, periodically, the SYNC creates the "Synchronization Request" packet with the own timer time and sends it through the *sync\_out* interface to the master.

- EXEC: the EXEC block manages the changing status operations of the ASIP. It's furnished with only one fifo to receive the packet from the FRONTEND, with the order for the new status to the ASIP. The FSM is always waiting for a new status notification arriving into the fifo and when it happens, it collects the basic informations (object, status and time stamp) and transmits the new status to the ASIP. Then, it waits the ASIP updating its current status and communicates it to the EXEC. When the EXEC will receive the current status of the ASIP LDPC algorithm, it will communicate it to the FRONT END block, this last in charge of submit the status to the external master.

- BRIDGE: it's in charge of deliver the packets arriving from the external interfaces to the correct virtual interface and vice versa. It has one fifo for each virtual input interface (data arriving from the ASIP to send outside) and one for each external input interface (data arriving from outside to deliver to the ASIP), plus one by which the informations on how to build the routing tables from the FRONT END arrives.

- It does nothing but to keep controlling the empty fifo signal of all the input data fifos, checking if there's a packet arriving:

- 1. If something arrives into the routing parameters fifo, it could be the BRIDGE IDENTIFICATION COMMAND or the parameters to fill a routing table. In the first case, it throw out through all the *data\_out* interface a packet for the identification process; if it's for a routing table, it fills the right table (input or output is indicated in the arrived packet) with the informations of destination and header;

- 2. If there's a data input fifo not empty, it goes catching the packet, it looks at the header, searches in the routing table input the corresponding virtual interface and forward through it the information;

- 3. If there's a virtual input fifo not empty, it goes catching the packet, it searches in the routing table output the header which corresponds to that virtual interface and deliver outside all through the data out interface indicated.

PHAL tasks are completely indipendent from the ASIP purposes. As a matter of fact, the ASIP depends on PHAL performance and operation managing. This makes the PHAL the most important device into a NoC. Furthermore, the ASIP task, as implementing the message passing algorithm, is partitioned into time slots and it's not able to begin the execution phase without an ENABLE activation, performed by the PHAL component. On the other hand, PHAL is always executing and checking the network functionality on one side, while scanning the ASIP operations and managing its packet delivering on the other.

# 5.2 LDPC Components: VN, CN

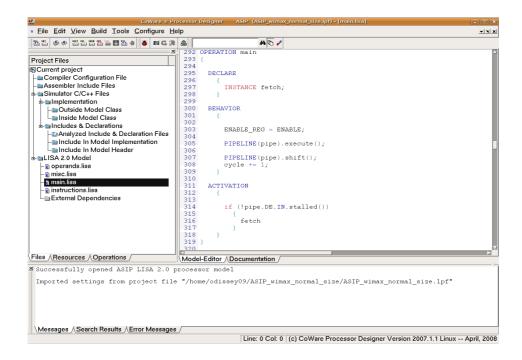

ASIP is the acronym of Advanced-Special Instruction Processor, a customized microprocessor designed to perform only a specific kind of instruction set internally to the program main code. Its architecture and instructions are built for a specific purpose, not for general use. The software instrument by which the processor's been developed is the LisaTek Coware programmer device. This framework provides the possibility to declare all the needed resources, as registers, memories, pipelines and so on, plus to implement and describe the instructions that permit to realize the desired aim. By this tool it's possible to declare the instruction set to better perform the LDPC algorithm minimizing the resource allocation.

## **5.2.1** The ASIP Architecture

The CoWare working platform is composed by several fields, each one with different features; the principal one is the *main*, reported in the Appendix A. Into this area, takes room the resources declaration, the main and reset part of execution code, the different groups of instructions and the instructions automatically executed during the fetch part of the decoding operation.

## 5.2.1.1 The memory set

Let's begin seeing at the resources declaration of the memory set.

It's mandatory to specify every memory, comprised the program code one. Joint to the memory, the respective bus must be allocated, one for memory, to carry data words during either reading and writing operations. The LDPC decoding ASIP has a set of memories with different purposes; each one of them it's thought to host a specifical kind of data and data bit format. The great amount of memories (normally should be one for the program code and one for the data) will require a lot of heavy logic to be managed. Though it might be better organized in a unique whole memory, to reduce the access logic, it's now necessary because of the access to memory limited to one acces for cycle period.

Substantially there's a program memory, where the program code executed for the

algorithm purpose is stored and others six memories containing different nature data:

• **VNi\_mem**: it contains the connections between each VN node and the CN nodes, with the data processed by the VN to be sent to the relative CN.

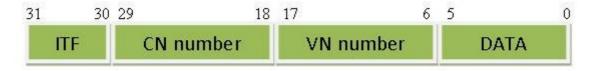

Each bus number addresses a block of 32 bits, divided into several fields.

Each connection, in a word, is represented by indicating the pair of nodes (the VN one and the CN one) joined together and the information data.

The interface field indicates through which virtual interface this word must be sent. It requires only 2 bits because the NoC provides 4 PEs and each interface is directed to one of the other three PEs. Besides, the interface "00" doesn't indicate an external PE destination, but the same of the origin. In this case the target lays in the same PE of origin and it won't be delivered outside but directly stored in memory.

The VN node field indicates the number by which is performed the identification of each VN in the entire network.

The CN node field shows the CN node joined to the VN.

The data field is occupied by the Q message, elaborated by the VN in the word and directed to that specific CN. In the beginning, it will be filled with the input LLR data, the same data message to all the CNs connected to the same VN.

There's a dedicated interface (*virtual data 0*), connecting the ASIP and the Linux controller, by which it'll be possible, in a future expansion, to charge this memory (and the CNi\_mem too), during the initialization stage, with the node connections expressed in the Tanner Graph. Right now, the data connection (with input LLR in the VNi\_mem) is stored in the static way, by evocation in the main program code.

The format choice is due to the 32-bit word standard of use. The VN and CN nodes, in the WiMAX standard implementation, are expressed by identification numbers representable in a 12-bit format. Indicating the origin node and the destination one occupies 24 bit. Other 6 bits are mandatory to carry the message data. 2 bits lack to fill the entire buffer and they're dedicated to the interface number.

Surely, if the NoC were composed by more then four PE or the Tanner Graph were made of a greater number of nodes, no longer expressable on 12 bits, a single 32-bits buffer wouldn't be enough and a longer one would be necessary. Or another field buffer organization should be performed. Neverthless, this project is customized to the WiMAX requirements, not to other ones. The ASIPs don't know which nodes they contein, so in every data packet is necessary to indicate origin and destination. Furthermore, only the PHAL knows how to deliver packets in the network but it doesn't own the indication of every node's position: it only knows by which interface they came from and the interface field helps the delivering task.

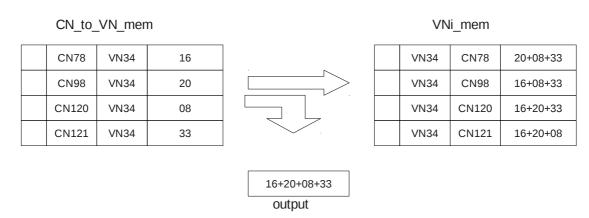

• **CNi\_mem**: it's basically organized as the VNi\_mem, except for the field order (it contains the connections between each CN node and the VN nodes with the R messages).

Each bus number addresses a block of 32 bits, divided into several fields,

The data field is filled by the R message produced by CN to the VN. In the beginning, this field is empty (there are zero bits) because no messages were exchanged yet; in fact, the first operation is the VN input sending and only then the CN nodes will elaborate and replace the message.

For this memory too, the connection storage will be made statically.

- VN\_to\_CN\_mem: it has the same format of the VNi\_mem, because it contains the Q messages received by the VNs from other PEs and directed to the CNs contained in the PE of this memory.

- The difference with the VNi\_mem is that, into this memory, messages are ordered by increasing number of CN. That's because of comfort: when, during the creating R message operations by the CN nodes, it will be necessary to obtain the Q messages in the VN\_to\_CN\_mem, the LDPC algorithm in the ASIP will know exactly where to find each message related to a known CN.

- CN\_to\_VN\_mem: it has the same format of the CNi\_mem, because it contains the R messages received by the CNs from other PEs and directed to the VNs contained in the PE of this memory.

- The difference is that, into this memory, these messages are ordered by increasing number of VN. That's because of comfort: when, during the creating Q message operations by the VN nodes, it will be necessary to obtain the R messages in the CN\_to\_VN\_mem, the LDPC algorithm in the ASIP will know exactly where to find each message related to a known VN.

- Input memory: it was thought as a 8-bit width RAM because of the standard memory size based on multiples of 8 bit cells. Neverthless, only 6 bit will be important, since it must contain the input LLR 6-bits data of the VN nodes. Actually, in the beginning, the data is already contained in each connection word of the VNi\_mem memory. The reason why it's been decided to dedicate an entire memory to these data is that every VN calculation phase, the VN node needs its LLR to perform the next step messages and they can't be borrowed by newest incoming messages. Therefore, in the initialization step, the ASIP gets the input data (ones each VN) and stores it in this memory.

- Output memory: created as 8-bit width RAM for the same reason of the VNi\_mem, conteins the refreshed output of each VN execution iteration.

From those data will be delivered the sign bit to the control master through the virtual data 0

interface, at the end of all the requested iterations.

It's important to underline that, except for the input and output ones, in which each VN occupies only one byte cell, all the memories allocate more than one cell dedicated to each VN (in the VNi\_mem and in the CN\_to\_VN\_mem cases) or CN. That's mandatory, thinking that every memory describes the connections among VNs and CNs: each VN node might be connected to other 6 CN nodes and each CN node to 7 VN nodes, in the WiMAX implementation. But, since the

WiMAX standard implements an irregular LDPC decoding algorithm, those indicated are the maximum numbers of connections. And since it has never known how much node, each node is connected to, 6 word cells for each VN in the VNi\_mem and in the CN\_to\_VN\_mem and 7 word cells for each CN in the CNi\_mem and in the VN\_to\_CN\_mem must be reserved, although not all of them will be filled with a message.

On the other hand, this make the algorithm execution easier, because, since the maximum number of CN and VN in each PE is well known, the procedure can be, simply, scanning 6 or 7 words for VN or CN, knowing that they contain an all-zeros value if they're empty (there are no more connections, i.e. less than 6 or 7), in this way creating an automatic control cryteria.

For that reason too, in the beginning of the main program code, when the memories are filled with the words representing the connections, all the 6 reserved words for the VNs and the 7 reserved words for the CNs will be filled. If the nodes don't reach the maximum number of connections, the word will be filled with an all-zeros word.