UNIVERSITAT POLITÈCNICA DE CATALUNYA Escola Tècnica Superior d'Enginyeria de Telecomunicació Departament d'Enginyeria Electronica

MASTER THESIS

# Ubichip Virtual Machine and visualization of Spiking Neural Network Parameters

Author: Jan Budzisz

Supervisor: Prof. Jordi Madrenas

January 26, 2010

#### Abstract

Since ages people have been wondering the inner workings of brain. There is more and more information about processes involving particular brain regions, yet synthesizing neural-networks in a large scale has always been a problem. Despite the fact that the popular desktop computer is becoming more powerful, simulating massively parallel computations aways proved to be a challenge. Due to its genericness, in very specialized work, such as neural networks, it is far better to design and use dedicated array of processors.

Such approach has been used in development of the Ubichip – a device designed specifically for such purposes. The design goal was to simplify the execution elements to suit the needs of efficient neuron model algorithms emulation.

As with every development cycle of a complex tool there are many tasks that may be carried out in parallel. This, of course, effects in allowing the development team to shorten the cycle and provide the solution faster. This however, requires a set of tools that will allow to prototype and verify work progress against some set of basic rules.

The Ubichip was already supported by a toolkit named SpiNDeK, that allowed to create networks and with the use of ModelSim simulate the code. This solution for proof-checking the algorithms however proved to be cumbersome and due to many levels of indirection – slow. To increase efficiency when working with code, the programmer should not have to wait endlessly watching the progress bars. To remedy this, improve efficiency and encourage more precise tuning and development of new neuron-model algorithms the Ubichip Virtual Machine was born.

At first it was just meant to be a simple visualization tool, but as it turned out there was a missing link in the chain of tools available for the Ubichip, which had to be filled.

Thus, in this work a virtual machine for the Ubichip has been developed, as well as a visualization tool that enables a convenient display of the evolution of spiking neurons in a network.

## Acknowledgements

First of all I would like to sincerely thank my supervisor, prof. Jordi Madrenas for his support of the project, guidance and discussions about possible improvements and new features of the Virtual Machine, the support throughout entire semester and for providing useful tips during my stay at the UPC.

I am also grateful to Giovanny Sánchez Rivera, for testing the VM as well as providing few useful pointers as my development went on.

This great opportunity would not be possible without the support from dr Małgorzata Napieralska at Technical University of Łódź, which I am very thankful for answering many questions and guiding me through the process of dealing with all paperwork for the Erasmus program.

Finally, I owe a debt of gratitude to my beloved girlfriend and my parents for providing me with support and encouragement over my whole studies.

## Glossary

#### AER

Address Event Representation

#### ALU

Arithmetic Logic Unit

### $\mathbf{CAM}$

Content Addressable Memory

## $\mathbf{CIL}$

Common Intermediate Language

#### $\mathbf{CPU}$

Central Processing Unit

## $\mathbf{GC}$

Garbage Collector

### GUI

Graphical User Interface

#### HTML

HyperText Markup Language

## JIT

Just-in-Time compiler

#### $\mathbf{LSB}$

Least Significant Bit

### MSB

Most Significant Bit

### $\mathbf{MSIL}$

Microsoft Intermediate Language

#### $\mathbf{OS}$

Operating System

### $\mathbf{PC}$

Program Counter

### $\mathbf{PE}$

Processing Element

#### $\mathbf{RPN}$

Reverse Polish Notation

## SIMD

Single Instruction Multiple Data

#### $\mathbf{SYA}$

Shunting-yard algorithm

## UI

User Interface

#### $\mathbf{V}\mathbf{M}$

Virtual Machine

#### $\mathbf{XML}$

eXtensible Meta Language

## Contents

| 1        | Intr            | oduction                                                              | 1  |

|----------|-----------------|-----------------------------------------------------------------------|----|

|          | 1.1             | Objectives                                                            | 2  |

| <b>2</b> | $\mathbf{Spil}$ | king Neural Networks                                                  | 3  |

|          | 2.1             | Classic neuron model                                                  | 3  |

|          | 2.2             | Bioinspired spiking neuron model                                      | 5  |

| 3        | Ubi             | chip                                                                  | 7  |

|          | 3.1             | Hardware                                                              | 7  |

|          |                 | 3.1.1 PE array                                                        | 8  |

|          |                 | 3.1.2 Sequencer                                                       | 9  |

|          | 3.2             | Working cycle                                                         | 9  |

| 4        | The             | e Virtual Machine                                                     | 11 |

|          | 4.1             | The main idea                                                         | 11 |

|          |                 | 4.1.1 The Real World                                                  | 11 |

|          |                 | 4.1.2 SpiNDeK tool                                                    | 11 |

|          |                 | 4.1.3 Research                                                        | 12 |

|          | 4.2             | Differences from the hardware implementation of Ubichip $\ . \ . \ .$ | 13 |

|          | 4.3             | Assembly language                                                     | 14 |

|          | 4.4             | Assembler                                                             | 15 |

|          | 4.5             | Memory layout file                                                    | 16 |

|          |                 | 4.5.1 Necessity is the mother of invention                            | 17 |

|          |                 | 4.5.2 Layout section explained                                        | 18 |

|          |                 | 4.5.3 Options section explained                                       | 20 |

|          | 4.6             | Boosting execution speed                                              | 22 |

| 5 | Use | er interface             | 23        |

|---|-----|--------------------------|-----------|

|   | 5.1 | Main window              | 23        |

|   |     | 5.1.1 Main tab           | 23        |

|   |     | 5.1.2 Debug tab          | 23        |

|   |     | 5.1.3 Log tab            | 26        |

|   |     | 5.1.4 Options            | 26        |

|   |     | 5.1.5 Spike propagation  | 26        |

|   |     | 5.1.6 Variable access    | 29        |

|   | 5.2 | Open VM dialog           | 29        |

|   | 5.3 | Plot window              | 31        |

|   | 5.4 | Editing plot             | 31        |

|   | 5.5 | Spike window             | 33        |

| 6 | Imp | plementation details     | <b>34</b> |

|   | 6.1 | .NET Framework           | 35        |

|   | 6.2 | Decision-making process  | 35        |

|   | 6.3 | UbichipVM Namespace      | 36        |

|   | 6.4 | UbichipVM.code Namespace | 37        |

|   |     | 6.4.1 Ubichip            | 37        |

|   |     | 6.4.2 VM                 | 39        |

|   |     | 6.4.3 Memory             | 40        |

|   |     | 6.4.4 Memory.Variable    | 41        |

|   | 6.5 | Code                     | 41        |

|   | 6.6 | Challenges               | 42        |

| 7 | Simulation results                  | 43        |

|---|-------------------------------------|-----------|

| 8 | Conclusions and future work         | 48        |

|   | 8.1 Conclusions                     | 48        |

|   | 8.2 Possible future extensions      | 49        |

| A | Supported opcodes                   | 51        |

| в | Compiler supported constructs       | 56        |

| С | Detailed VM namespace class diagram | 60        |

| D | The Expression Parser               | 61        |

| Е | Assembly Example                    | 64        |

| F | Basic algorithm memory layout       | 73        |

| G | Layout File Examples                | <b>74</b> |

# 1 Introduction

Rapidly changing world around requires us to constantly adapt and solve increasingly demanding tasks. Methods of labor and design have changed many times during the last decade, only to create new challenges. In late 1980's computers began to play more important role, as Computer-aided Design software emerged and allowed us to carry out more and more complex tasks, by managing growing number aspects of design by itself, allowing designers to concentrate on function and key feature optimizations. Many simulation frameworks came along with CAD software. At first they were relatively very limited due to hardware constrains. Yet with the development of modern CPUs the power to simulate became very cheap. But, as stated in the beginning, with new knowledge new questions arose, which required other approach – an approach that is no longer one domain specific, is not strictly tailored towards certain problem solving, and is flexible and self-adaptable.

The nature itself seems to be the best answer. Many patterns found in the world surrounding us were developed over million years, taking it from simple yet brilliant ideas into almost pure perfection. Evolution observed among all living beings allows to optimize key aspects of life to preserve fitness and self-adapt to changes in the surrounding world. One such brilliant idea of Mother Nature is the brain which essentially has simple principles of operation, but put together its size and complexity and we have the most capable problem solving tool known to man. Its brilliance is the inherent ability to adapt, tolerate faults, precisely interpret incoming stimulus and to match or even guess patterns.

First attempts to create a working model of a neural network were done by Rosenblatt in 1957[11]. These was a primitive electro-mechanical device that was meant to recognize symbols, but as it turned out it was not working for more complex symbols and was also sensitive to position of it and the size on the viewing field. Next successiful concept was proposed by Bernard Widrow in 1960. It was a network built from many electro-chemical elements called Adaline (Adaptive linear element)[1].

No wonder that with growing availability of tools the drive to simulate and understand better neural networks was propelled. Such simulations, however, seemed and still are a very demanding task. The previously mentioned computers, despite their increasing computation capabilities, still did not provide sufficient processing power to simulate large scale neural networks in real time. The key word here is "simulation" – which means that there are levels of indirection. This effectively means that instead of harnessing full available CPU power, we must sacrifice some of it to do some management and translation of hardware features. The more complex and more flexible the simulation software is, the more levels of indirection it may have leading to inferior performance.

If the simulation of neural network is such an ineffective task on generic CPUs why not create a tailored design suited to resolve the problem of performance?

The first effort to create a solution for building more sophisticated networks at UPC and several other European universities, was project POETIC. It was based around a notion of building chip containing directly mapped neurons. However building larger networks would require enormous amounts of chips and managing its interconnections would be a error prone and mundane task. The concepts, experience and the conclusions helped other projects.

## 1.1 Objectives

The initial objective of my project was to deliver a tool for visualize some aspects of Spiking Neural Networks simulated by the Ubichip. Yet with the ongoing development, the focus has shifted from this visualization tool to a high level of abstraction software implementation of Ubichip that is coupled with GUI (Graphical User Interface) capable of presenting graphically its results. This software implementation, referred further as Virtual Machine, became the main concept around which this work is based.

# $2~~{ m Spiking \ Neural \ Networks}$

For years scientists have studied human brains. First through extracting tissue from animals and analyzing samples under a microscope, then by isolating single fibers and applying small currents to it, finally trying to sample currents on a living animal and also applying small currents to stimulate different brain areas. The ongoing research on human brain allows us to deeper understand its inner workings and how to create better models.

Use of modern computers capable of simulation of a discrete set of neuron and synapse properties allowed to gain further understanding of their interaction. Biological discoveries, careful study and observation led to derivation of mathematical models – starting from simplified versions – created to allow fast and simple computations of larger neural networks, to more elaborate description – used in smaller networks, but geared towards deeper understanding of processes involved, with a whole range of models available in between those two.

Currently a handful of different neural network models exists, each focusing on different features of their functioning. The European Perplexus project concentrates on the emulation of large-scale Spiking Neural Networks, which fall into the third generation of neural network models, taking into account not only neuronal and synaptic state but also the concept of time. This approach, contrary to typical perceptron networks, means that the neurons do fire only when its membrane potential<sup>1</sup> reaches a specified threshold value. The signal emitted by the neuron causes the change of potentials of other connected neurons. This model was proposed in 1952 by Alan Lloyd Hodgkin and Andrew Huxley[15], and has been successively refined. The spiking neuron model used in the Perplexus project was proposed by Iglesias and Villa[6].

## 2.1 Classic neuron model

A neuron or nerve cell is an element from which the nervous system is built – this includes brain, spinal cord and connections to and between other tissues

$<sup>^1\</sup>mathrm{Membrane}$  Potential – an intrinsic quality of the neuron related to its membrane electrical charge

like muscles. Neuron cell is responsible for transmitting as well as for processing informations. It is excitable by external electrical currents, but there are also some neurons that are self-excitable and spike regularly. The information between cells is transmitted through with involvements of electrochemical methods.

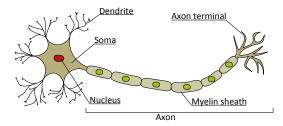

Figure 1: Overview of nerve cell

The neuron (as seen on Figure 1) may be divided into three functional parts. First one is the cell body, also called soma, which contains the nucleus that produces the most of RNA used to produce proteins. Its membrane integrates input stimuli from other neurons and fires (produces a spike), when the membrane potential rises over a threshold. Second part are the dendrites through which the neuron receives the impulses called spikes. The last part is the axon ending with axon terminals that transmit the impulse through synapses – connections with nearby cells. There are also cells that are wrapped around axon, and act as a insulator as well as greatly increase the speed of information transfer, this is called myelin sheath produced by Schwann cells.

A single neuron transmits impulses from dendrites to axons. With some careful observations and experiments a simple mathematical model can be proposed which acts as a base for our further study.

$$s_j = \Phi\left(\sum_i w_{ji} s_i\right) \tag{1}$$

This is a basic equation for evaluation of simple artificial neurons output or, more precisely, its post-synaptic spike  $(s_j)$ , based on inputs – pre-synaptic spikes  $(s_i)$ . The  $w_{ji}$  provides a synaptic weights table and  $\Phi$  is an activation function.

Neural networks are made of vast numbers of interconnected neurons. There are of course no synaptic weights and activation function which are just abstracts of more complex processes involved in the workings of a neuron and its interaction. The model above was used and extended by scientists until more sophisticated kinetic models were developed, such as Hodgkin-Huxley model, but it still is useful for basic understanding of neuron workings.

## 2.2 Bioinspired spiking neuron model

The neuron model used in the Perplexus project is more complicated that the one shown in the previous section. The basic model uses only current states of input and has no memory effect. This effectively disables it from achieving more accurate results and with availability of more advanced models should be avoided unless used for a specific purpose.

The model used in the Perplexus project was proposed by Javier Iglesias and Alessandro E.P. Villa[6] and uses more complex equations for both postsynaptic spike and synaptic weight. All neurons are simulated using leaky-integrate-andfire model.

Each time step the membrane potential is calculated using following equation:

$$V_{i}(t+1) = V_{rest[q]} + B_{i}(t) + (1 - S_{i}(t)) \times \left( \left( V_{i}(t) - V_{rest[q]} \right) k_{mem[q]} \right) + \sum_{j} w_{ji}(t) \quad (2)$$

where  $V_{rest[q]}$  is the resting potential value,  $B_i$  is the background activity,  $S_i$  is the state of the unit,  $k_{mem[q]} = e^{\frac{-1}{\tau_{mem[q]}}}$  is the leakage constant,  $w_{ji}$  are post-synaptic potentials (see equation 4).

The units state  $S_i$ , as used in the Perplexus project, is a function of membrane potential  $V_i$  and is defined as:

$$S_i(t) = \mathcal{H}\left(V_i(t) - \Theta_{[q]_i}\right), \quad \text{where} \quad \mathcal{H}(x) = \begin{cases} 0, & x < 0\\ 1, & x \ge 0 \end{cases}$$

(3)

The post-synaptic potential  $w_{ji}$  is a function defined as:

$$w_{ji}(t+1) = S_j(t)A_{ji}(t)P_{[q_j,q_i]}$$

(4)

where  $S_j$  is state of pre-synaptic unit,  $P_{[q_j,q_i]}$  defines type of synapse and  $A_{ji}$  is its activation level.

The activation level is defined by following expression:

$$A_{ji} = \begin{cases} 0, & (A_{ji} = 1) \land (L_{ji} < L_{min}) \\ 1, & (A_{ji} = 0) \land (L_{ji} < L_{max}) \lor (A_{ji} = 2) \land (L_{ji} < L_{min}) \\ 2, & (A_{ji} = 1) \land (L_{ji} < L_{max}) \lor (A_{ji} = 3) \land (L_{ji} < L_{min}) \\ 4, & (A_{ji} = 2) \land (L_{ji} < L_{max}) \\ A_{ji}, & (L_{ji} \ge L_{max}) \land (L_{ji} \le L_{min}) \end{cases}$$

(5)

where  $L_{max}$  and  $L_{min}$  are user-defined boundaries and  $L_{ji}$  is real-valued variable used to implement plasticity rule. This variable is defined as

$$L_{ji}(t+1) = L_{ji}(t) \times k_{act[q_j,q_i]} + (S_i(t)M_j(t)) - (S_j(t)M_i(t)),$$

where  $k_{act[q]} = e^{\frac{-1}{\tau_{act[q]}}}$  (6)

where  $M_j$  and  $M_i$  are memories of latest spike interval expressed by following equations:

$$M_j(t+1) = S_j(t)M_{max[q_j]} + (1 - S_j(t))M_j(t)k_{syn[q_j]}$$

(7)

$$M_i(t+1) = S_i(t)M_{max[q_i]} + (1 - S_i(t))M_i(t)k_{syn[q_i]}$$

(8)

The P defines the so-called type of synapse that is a potential value expressed in mV that causes depolarization or hyperpolarization. Background activity is simulating noise that is generated by firing of nearby neurons as well as other phenomenon.

This complex algorithm has been already implemented (see Appendix E) and its results are shown in Section 7. Because of the programmability of both the hardware implementation of Ubichip and the VM the current algorithm can be further extended or replaced by another one completely.

# **B** Ubichip

An integrated circuit targeted to support the real-time emulation of large scale spiking neural networks was developed with the Perplexus project as a EUfunded project in collaboration with other European universities. The socalled Ubichip supports in its current implementation the emulation of 100 neurons and 300 synapses per neuron. The architecture allows emulation of a network consisting from at least 10,000 neurons. Each of the participating universities contribute different experience to the project. The Université Joseph Fourier Grenoble (UJF), France, provide mathematical model of the biologically-inspired spiking neurons. At Universitat Politècnica de Catalunya (UPC), Spain, the Advanced Hardware Architectures Group develops the Ubichip architecture – the custom-designed processor for parallel computations. Closely to UPCs work, Politechnika Łódzka (TUL), Poland, verifies and synthesizes the hardware Ubichip models from VHDL descriptions.

The main focus has been placed on building a scalable platform of wirelessly connected units, to execute and observe inner workings of neural network. Unlike computer-based projects, utilizing generic CPUs like x86 or ARM architecture, Perplexus focuses on the use of custom built hardware tailored for execution of vast amount of parallel operations.

## 3.1 Hardware

Better execution speed was achieved by deferring parallel computations to a large yet simple array of execution units which is governed by a Sequencer unit both dispatching instructions to Processing Elements (PE) and executing control instructions. Such separation of tasks allowed to simplify the required hardware for each PE while allowing certain degree of flexibility and superior performance to more generic solutions.

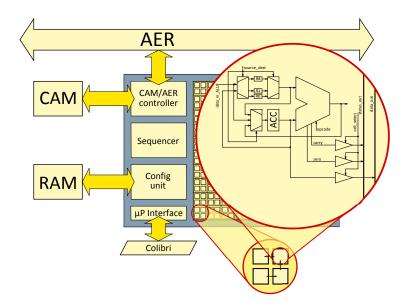

Figure 2: Detailed Ubichip architecture (multiprocessor mode)

#### 3.1.1 PE array

The Ubichip processes data in digital domain with neuron-level parallelism. Contrary to generic CPUs which are able to process data in series only, or given array of CPUs or multi-core processor, computations could be carried out in parallel, but it would be done with high overhead cost for thread synchronization, the Ubichip is a simple yet efficient SIMD processor tailored for such operation. Furthermore, as it is fully programmable, it may be used with different algorithms.

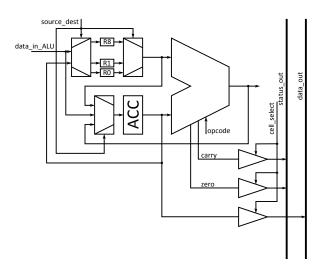

On Figure 2 the Ubichip architecture is shown in detail. Each PE is made of four macrocells, 4 bits each, making PE a 16-bit unit. Each macrocell architecture is shown on Figure 3.

Each macrocell is capable of 4-bit computations. While it may seem to be a low value compared to nowadays 64-bit CPUs in desktop computers or 128-bit ones in gaming consoles or GPUs, its strength lies in the capability to group together macrocells, creating effectively PEs of desirable bit size. What is also important is that high precision is not required in bioinspired neural networks. Grouping macrocells together is done by configuring border routing, so that e.g. carry and zero bits are being propagated accordingly. It can be adapted to the precision requirements for the algorithm to be executed.

Figure 3: Macrocell logical overview

## 3.1.2 Sequencer

The governor for all PEs is the Sequencer unit which executes control and management instructions while dispatching all arithmetics to the array. This way the whole processor works on a SIMD scheme (Single-Instruction Multiple-Data). Such approach separates more complex control and memory access instructions and encapsulates them in one unit. There are, of course, drawbacks of this concept – e.g. there are no conditional instruction like the ones used in most assembler codes or higher level programming languages – instead a notion of FREEZE/UNFREEZE was introduced. It offers certain benefits over branching instructions, like e.g. a steady number of cycles per execution phase, which results in simplification of cross-chip synchronization.

## 3.2 Working cycle

The code execution is divided into two stages – execution phase, referred further as phase 1, and CAM controller mode phase, referred as phase 2. During the first phase, as the name implies, the algorithm code is executed, until STOP or HALT opcode is encountered. Because the second opcode effectively stalls all further processing we will consider only STOP to be the way to enter into phase 2. Second stage is meant for exchanging spikes between neurons and synapses. This is done by a simple bus called AER (Address-Event Representation). During this phase CAM controller scans through all PEs (neurons) for occurring spikes, to be broadcasted by means of the AER bus. To identify incoming spikes clearly the information encoding each spike contains unique chip id, as all Ubichips have a unique id number assigned during setup, along with x and y positions. Then each spike on the AER bus is compared against CAM memory of each Ubichip and if pattern is matched, the spike is stored in the right place in the SRAM.

When all PEs have been scanned and spikes transfered, Ubichips enter phase 1 and the execution is resumed. This closes the cycle.

# 4 The Virtual Machine

## 4.1 The main idea

#### 4.1.1 The Real World

The notion of virtualizing is widely used nowadays. From small and simple scripting languages like Ruby[5] using specialized virtual execution units, through more advanced environments like older versions of Java[13] (the newer ones use JIT (Just-In-Time) compilation), to full fledged virtualization software like VMWare ESX[14]. All of these are built for different purposes, but they allow easy creation of hardware-independent feature-rich execution enviroments. This simplifies both development and deployment of software. Tools like VMWare Workstation or Sun VirtualBox[12] allow to use server hardware more efficiently, thus effectively giving opportunities for reducing costs. It is achieved by paralellizing multiple tasks and OSes (Operating Systems) on single hardware.

These practices are very often used in modern web infrastructures – because a web server only responds to request sent by users, most of the time it is idle. Using one machine solely for this purpose would incur much waste of resources. This is where virtualization technologies start to become useful. They allow to setup multiple "guest" OSes, so they do not interfere with each other providing high security through separation, on a single hardware, thus utilizing it more efficiently. More advanced solutions allow managing larger infrastructures of hardware hosts, even with seamless switching virtual machines between hosts to distribute the load.

#### 4.1.2 SpiNDeK tool

With development of Ubichip hardware, a tool to automate building of binary code and all other necessary files like contents of CAM memory were required. A toolkit called SpiNDeK was developed as a part of Master Thesis of Michael Hauptvogel[4]. It is created and tailored towards use with a specific simulation algorithm developed along with it. With a relatively simple GUI (Graphical User Interface) it allows range of tasks to be carried out. Most important of them are:

- setting of various neuron parameters,

- generating a neural network of user-specified size and interconnections using models for connection-type and length distribution,

- generating data segment for RAM memory contents,

- joining generated data section with existing algorithm,

- assembling code and storing result in a VHDL array for simulation,

- invoking ModelSim to carry out simulation and parse the results into a HTML table.

#### 4.1.3 Research

The SpiNDeK tool has been used to create neural networks and the digital VHDL simulation is being carried by ModelSim. The simulation however is slow, because for every change of parameters the whole model must be recompiled. When this process is over, the simulation itself takes significant amount of time, as the ModelSim simulates not only the actual code but also the FPGA underneath. To add even more complexity the output is a simple text table with a lot of data. This of course is not very helpful and is hard to read by us, humans. There is too much information at any given moment. It would be much easier to be able to graphically express these values. This is where the idea of building a VM for the Ubichip came into being.

At first, as mentioned above, the sole effort was put into increasing of code execution speed, thus allowing faster viewing of the results and developing the visualization software. However as this concept expanded it became clear that it may deliver substantial benefits for code developers allowing them to instantaneously monitor all available parameters in an easy manner. Instead of searching through one big result table the VM is able to display the variables in one specific place, so that it may be observed separately.

## 4.2 Differences from the hardware implementation of Ubichip

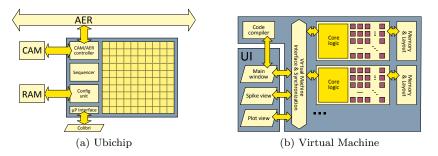

To achieve performance required to execute Ubichip code the architecture could not be just copied and implemented exactly as in hardware version. Such approach would incur too much overhead as well as cause problems with maintainability. To overcome this, the chip design was divided into its logical elements and only these were implemented. To see the differences it is best to show them as a graphical representation.

Figure 4: Comparison of Ubichip and Virtual Machine architecture

Most visible difference is that the architecture presented on 4 is open and is extended just by adding other elements, which are then joined by AER bus. On the other hand the VM is self-contained and may not be extendable in a way the Ubichip does. It may be possible to integrate with other system by either extending VM class to act as an extension to other AER buses or subclassing Ubichip class, when the computer should act as a master for synchronization and controlling external units. Both methods provide different benefits, but due to object-oriented approach they should be easily implementable with the use of existing code. More detailed information on the extension possibilites may be found in section 8.2.

There are also differences that are not visible in the provided picture. One of the most significant distinction is that the Ubichip processing macrocells are composed of four smaller parts called ubicells, which are the actual processing elements of the array. Because the VM is aimed at (relatively to previous simulation method) fast throughput, a different approach had to be taken. The single instance of virtual chip contains only the actual processing elements. There is an ongoing architecture development to enable Ubichip to be reconfigurable, so the macrocells can be merged into processing elements of varying bit-sizes (though they will be multiples of four). As mentioned earlier this is not directly possible because of different architecture. In order to achieve similar functionality in the VM a feature had been proposed by the promoter to allow setting configurable register size, which effectively is the bit-size of the processing element. However due to the fact that internal processing is done on the 32-bit variables, this value is the limiting factor while configuring VM. For more details refer to Section 4.5 on page 16.

Another difference is that the responsibility for data exchange between chips belongs to the main class which also governs the work of every single virtual chip, whereas AER bus is responsible solely for data exchange. Such approach allows to easily simulate multiple chips and track the results of their interactions.

## 4.3 Assembly language

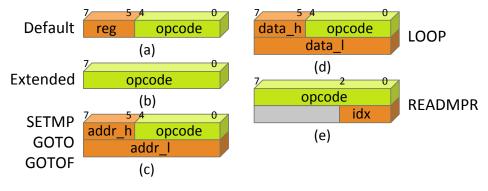

Because of the unorthodox instruction set, which does not directly support conditional branching, the most effective way to program the Ubichip is to use the low-level assembly. This compared to most high-level programming languages seems to be a hard and mundane task, but in the end the code fragments generated by hand usually execute faster or at least at the same speed as code generated by a compiler. And since the whole idea of Ubichip is geared towards just the simulation of neurons the actual code that needs to be written is only the algorithm, which usually is not very long. The complete instruction set available can be found in Appendix A.

The assembler file consists of three parts:

- definitions,

- data-segment and

- code.

The first section is used to define values of certain labels that can be later used multiple times when providing parameter for assembly command.

Next section being with a .data label and provides a way to define data needed for the algorithm. Separate data fields are stored in a key/value pair. The key can be used later in the code section.

In the last section the actual code is located, hence it begins with .code label. It may be divided into different code blocks by placing code-labels beginning with a dot. These labels can be then used with GOTO and GOTOF commands. Each individual opcode may only take one parameter, but both VMs and SpiNDeKs compiler support extended syntax (see Appendix B). For examples of assembly code see Appendix E.

## 4.4 Assembler

To allow the user to view the results more rapidly after each code change the VM is reading source code from a text file, which then is assembled into bytecode. The bytecode is then being embedded in the same way as it would be expected to be by the Ubichip:

- 1. Instruction Pointer

- 2. Data pointers

- 3. Code

- 4. Data.

The class responsible for the assembly process also reads additional segments of code – the defines from which the main application gets the values for size of the array and number of synapses. Its use is pretty straightforward and comes down to supplying the source file to the constructor of the class. The result can be then fetched from the Bytecode property of the object instance as array of bytes.

Besides the native assembly code defined in Appendix A, the code generator supports all command shorthands listed in Appendix B. The assembly process is split into three phases. During the first phase the source file is tokenized. The definition section is read and a dictionary based on defined symbols is created. The data is also read and stored internally along with its labels. Finally, each line with command is split into command name and its list of parameters. The complex commands are then split into sub-commands.

After that, in the second phase, the memory layout is created – placeholders for pointers are created, and code is being translated into actual opcodes. Parallel to this process a list of label addresses is being built and every appearance of GOTO or GOTOF command is being tracked, for later step. Then the data is appended after the code which leads to beginning of third pass.

The last step is only used to fill the placeholders for the data pointers with appropriate addresses and writing code label addresses for GOTO and GOTOF instructions.

The Code class also contains a helper method for retrieving commands from the memory, which is being used by the code execution methods in the Ubichip class.

## 4.5 Memory layout file

Due to the ever-changing and evolving nature of every development cycle my attempt was to create a VM that is as flexible as it was possible to be done in time I was given for this project. With such capabilities and tweaking options the configuration may prove to be much complicated – each degree of flexibility adds complexity both to the application code and the setup, making the usage learning curve slower for the user.

In a simple project aimed at performing simple tasks many elements may be hard-coded. It simplifies the development, allows rapid prototyping and often also increases application performance. Such tools however, are very limited and every change usually requires changing the code and recompiling whole project. This, of course, is inconvenient, slow and prone to errors. So as long as project is tuned to handle one specific task such approach may be sufficient. As the project grows larger and is used by multiple users with different needs a different solution must be used.

#### 4.5.1 Necessity is the mother of invention

First version of the VM was aimed at using rigid memory layout defined by previous developers of algorithm. Soon however it became clear that work on other algorithms needed different memory layout. This is when the idea of memory layout file was introduced. At first it was primarily aimed just at providing the structure of RAM contents, but soon adopted a few configuration options which allow changing of PE registers size, pointer size and its step as well as spike routing options to allow creator to specify its parametrized source and destination.

The layout configuration is stored as a XML file – which is both easily readable by humans and plenty of frameworks support it, allows hierarchical structures and navigating though it is usually simple, yet efficient. Because the VM is written in .NET Framework, which supports XML as its native configuration format, it made implementation of configuration code an easy task.

The basic structure of the layout file is as follows:

```

<MemoryLayout>

<Options>

<!-- Options go here -->

</Options>

<Layout>

<Item>

<Segment>

</Segment>

</Item>

</Layout>

</MemoryLayout>

```

#### 4.5.2 Layout section explained

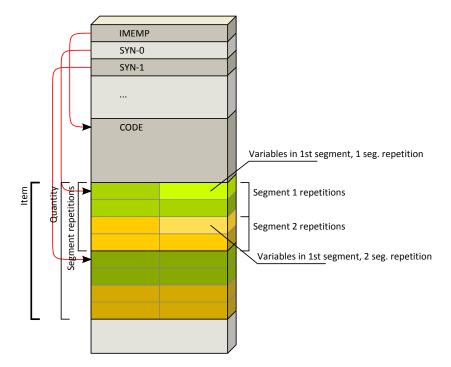

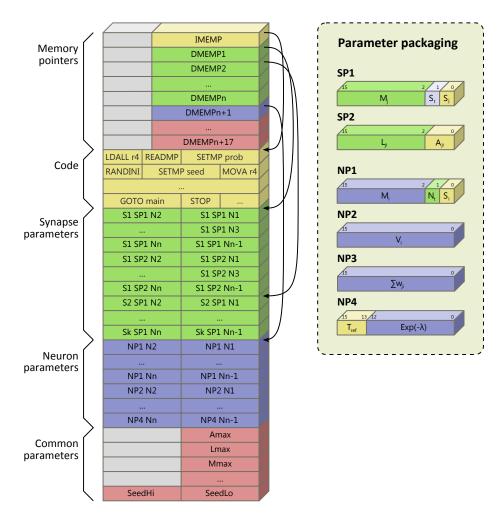

The Layout section defining the memory structure consists of many Items, each being representation of one or few pointers located at the beginning of RAM contents. The sequence in which Item elements appear should match exactly the sequence in which they occur in memory.

The Segment element describes one memory segment. Data available at each memory pointer is distributed equally among all declared segments, i.e.: basic memory layout (which is included in Appendix F for reference) consists two different declared segments for synapses, and each segment is repeated the number of neurons times.

Let's assume we have 4 neurons, each having only one synapse. If each synapse requires two segments to store all the necessary data this effectively means that we have 8 segments in total. First half of this memory is then used as a sequence of repeated variables declared in first segment (4 SP1 for different neurons) and the other half as repeated variables of the second segment (four SP2s, one for each neuron).

Each segment is divided into Variables, which define the name, size and offset of the variable in each segment.

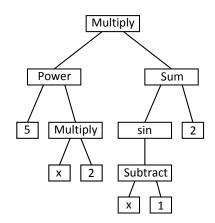

Because this may seem to be confusing at first, and a picture may be worth thousand words its best to look at the graphical explanation of this concept visible in figure 5.

Figure 5: Memory layout explained

Each Item may have additional attributes:

#### name

Specifies the name of the element.

#### size

Specifies size of one segment in bits. Must be a multiple of 8.

#### quantity

Number of whole item repetitions, each repetition is using one pointer. Default: 1.

#### segments

Sum of number of repetitions of every segment.

The last two of these attributes are expressions evaluated during setup. Available variables are: synapses, neurons.

Variables attributes:

#### name

Specifies the name of the variable. This field to be accessible for spike routing or by plot expressions should begin with a character and be followed by alphanumerics. This value has to be unique among other Variable elements.

#### offset

Specifies the offset in bits from the LSB. Default: 0.

#### size

Specifies size of the variable in bits. May not be greater than 32 bits.

#### 4.5.3 Options section explained

In the Options section one can define using elements:

#### RegisterSize

Width of PE's register. Range: 1–32.

#### PointerSize

Bit width of pointers located at the beginning of memory. Must be a multiple of 8, but not larger than 32 bits.

#### PointerStep

Bit step occurring with unitary change of the pointer. Must be a multiple of 8.

#### SpikeSource

See below.

#### SpikeDest

See below.

The SpikeSource and SpikeDest share the same node layout and attributes. The source attribute specifies the behaviour of each spike accessors. You may use memory, accumulator or none as its value depending on your specific needs. If memory option is chosen, you have to define Item, Index, Segment and Variable elements. The value of the first and the last is treated respectively as Item and Variable name attributes defined in the Layout section, while the other two define expressions that are evaluated during each access. Available variables: synapses, neurons, synapse, neuron. Using basic memory layout the spike should be transfered to a specific  $S_j$  (refer to section 2.1), so the SpikeDest may look similar to example below.

```

<SpikeDest>

<Item>synapses</Item>

<Index>synapse</Index>

<Segment>neuron</Segment>

<Variable>Sj</Variable>

</SpikeDest>

```

For a spike source one may want to use the PEs Accumulators LSB, or LSB of R0, first register. This can be easily achieved by using following code.

```

<SpikeSource source="accumulator" />

```

For the more adventurous, who want to test different aspects of their algorithms none set as source may prove useful e.g. for generating spikes. Basic setup of none outputs a 0 every time when read, and discards every write when set as a destination. The first of this behaviours can be altered by entering an expression which is evaluated for every neuron/synapse read and if the evaluation value is non-zero it is treated as a spike. The expression should be entered into a Expression node, like in the code below.

```

<SpikeSource source="none">

<Expression>1*(neuron-2)*(synapse-1)</Expression>

</SpikeSource>

```

This feature, however, is experimental and should be currently treated as such.

For working examples see Appendix G.

## 4.6 Boosting execution speed

The virtualization techniques proved to be very promising for both efficiency and flexibility. The two versions of execution engines were developed as a proofof-concept, to showcase the benefits within this technology. First and currently used engine is a bytecode parser which can execute code on a reference computer with an equivalent of about 1MHz. During the development a second engine was created to achieve even better efficiency. The bytecode parser was replaced by a translation of Ubichips native code into CIL (Common Intermediate Language)[8, 7] code, which upon execution is JIT compiled to the native code of executing machine. This version has outperformed the basic one four times yielding 4MHz virtualized processing power with use of a simple chip array (4 chips, 8x8 neurons each).

# User interface

The UI (User Interface) plays an enormous role in most of current programs. This is because the graphical information is easily understood by us, in comparison to pure text output which is harder to interpret and draw conclusion from. Each UI is designed towards achieving of some more specific objective, but it is meant to provide means of control and provide feedback to the user.

## 5.1 Main window

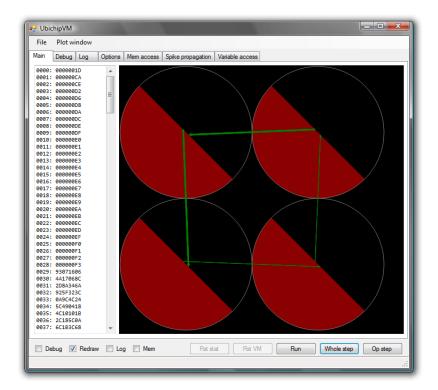

Main window (Fig. 6) is the main working space of the application. This window integrates a lot of features and provides a way to control the VM. On the top side of the window a menu bar provides user with options to create a new VM, by opening assembly source file and providing path for CAM files.

#### 5.1.1 Main tab

Main tab (Fig. 6) is divided into two sections – first showing current memory contents of first chip, and the second one representing neuron layout graphically, their excitement state (green when firing, red when not) and their connections with other neurons. Unfortunatley, it cannot be distinguished which of the synapses are excitatory and which are inhibitory. Clicking on the neuron adds it to or removes from the list of tracked neurons. When at least one neuron is on the list a window described in Section 5.5 is shown. When user removes last neuron from this list the additional window is closed.

#### 5.1.2 Debug tab

Debug tab (Fig. 7) presents values of various registers showing state of Sequencer and individual Processing Elements. The number of visible columns can be changed via Options tab described in section 5.1.4. The register values are fetched after instruction execution, so results of every command is in the same line, contrary to the output of SpiNDeK, which aligns differently opcode and register data – in SpiNDeK the register data after opcode execution is shown in the line following current, or to put it differently, register data is aligned with a new opcode that is about to be executed.

Figure 6: Main window tab

| Debug | Log Options | Mem access | Spike p | propagation | Variable a | ccess |      |      |      |       |   |

|-------|-------------|------------|---------|-------------|------------|-------|------|------|------|-------|---|

| PC    | _opcode     | 0:R0       | 0:R1    | 0:R2        | 0:R3       | 0:R4  | 0:R5 | 0:R6 | 0:R7 | 0:Z   |   |

| 2     | SETMP 22    | 0000       | 0000    | 0000        | 0000       | 0000  | 0000 | 0000 | 0000 | False |   |

| 3     | READMP 0    | 0000       | 0000    | 0000        | 0000       | 0000  | 0000 | 0000 | 0000 | False | Τ |

| 4     | LDALL R4    | 0000       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Τ |

| 5     | MOVA R4     | 1FFF       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Τ |

| 7     | SETMP 23    | 1FFF       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 8     | RANDINI     | 1FFF       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Τ |

| 9     | RANDON      | 1FFF       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 10    | LOAD R1     | 1FFF       | D800    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 11    | RANDOFF     | 1FFF       | D800    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 12    | AND R1      | 1800       | D800    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 13    | MOVR R1     | 1800       | 1800    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 14    | SWAP R1     | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 658   | GOTO A658   | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 414   | GOTO A414   | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | 1 |

| 415   | SWAP R6     | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 417   | SETMP 5     | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | 1 |

| 418   | READMP 0    | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Ť |

| 419   | LOAD R6     | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | E188 | 0000 | False | 1 |

| 420   | SWAP R6     | 1800       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | T |

| 421   | SWAP R0     | 0000       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Ţ |

| 423   | SETMP 6     | 0000       | 0000    | 0000        | 0000       | 1FFF  | 0000 | 0000 | 0000 | False | Ţ |

| -     |             | 1          |         | m           | 1          |       | 1    |      |      | 1     | Þ |

Figure 7: Debug tab

### 5.1.3 Log tab

| 県 Ubio           | hipVM                                                                                                                          |                                                                                        |                                                               |            |                   |               |    |     |            |         | x   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------|------------|-------------------|---------------|----|-----|------------|---------|-----|

| File             | Plot wi                                                                                                                        | ndow                                                                                   |                                                               |            |                   |               |    |     |            |         |     |

| Main             | Debug                                                                                                                          | Log                                                                                    | Options                                                       | Mem access | Spike propagation | Variable acce | SS |     |            |         |     |

| SPIKE(<br>SPIKE( | chip_1<br>chip_1<br>(1. 0x1) -><br>chip_1<br>chip_1<br>(1. 1x0) -><br>chip_1<br>chip_1<br>(1. 1x1) -><br>chip_1<br>(1. 1x1) -> | N 1, S<br>N 1, S<br>N 1, S<br>N 3, S<br>N 3, S<br>N 3, S<br>N 0, S<br>N 0, S<br>N 0, S | 1<br>2<br>0<br>1<br>2<br>0<br>1<br>2<br>0<br>1<br>2<br>0<br>1 |            |                   |               |    |     |            |         | *   |

| De               | bug 🔽                                                                                                                          | Redraw                                                                                 | v 🔽 Log                                                       | Mem        | Rst st            | at Rst        | VM | Run | Whole step | Op step | .:: |

Figure 8: Log tab displaying routing of spikes

The log tab (Fig. 8) displays spike signals that are sent along the virtual AER bus and which synapses receive these signals.

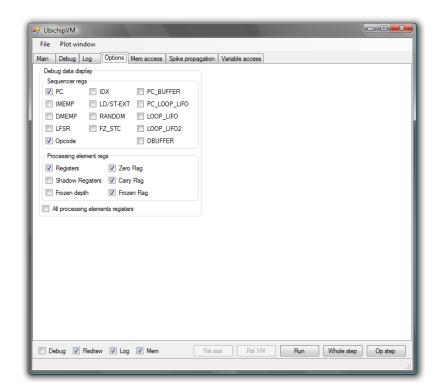

## 5.1.4 Options

Options tab (Fig. 9) enables to choose which column user wants to display – allowing to focus on particular register.

## 5.1.5 Spike propagation

Spike propagation tab (Fig. 10) allows to juxtapose all presynaptic and postsynaptic spikes. The values are added at ending of each phase.

Figure 9: Options tab

| Main |          |        |            | Calles and |      |                 | 1      |        |      |        |   |

|------|----------|--------|------------|------------|------|-----------------|--------|--------|------|--------|---|

|      | Debug Lo |        | Mem access | 1          |      | Variable access |        |        |      |        | _ |

|      | Phase    | N0S1Sj | N0S2Sj     | N0S3Sj     | NOSi | N1S1Sj          | N1S2Sj | N1S3Sj | N1Si | N2S1Sj |   |

| •    | 1        | 0      | 0          | 0          | 0    | 0               | 0      | 0      | 0    | 0      | ( |

|      | 2        | 0      | 0          | 0          | 0    | 0               | 0      | 0      | 0    | 0      | ( |

|      | 1        | 0      | 0          | 0          | 0    | 0               | 0      | 0      | 0    | 0      | ( |

|      | 2        | 0      | 0          | 0          | 1    | 0               | 0      | 0      | 1    | 0      |   |

|      |          |        |            |            |      |                 |        |        |      |        |   |

|      |          |        |            |            |      |                 |        |        |      |        |   |

Figure 10: Spike propagation tab

#### 5.1.6 Variable access

| 🖳 UbichipVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| File Plot window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

| Main Debug Log Options Mem access Spike propagation Variable access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| Si 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Get     |

| SI0. 2] = 1         SI0. 2] = 1         Amax = 3         SeedLo = 57736         SeedLo = 57736 <td></td> |         |

| Debug 🗹 Redraw 🕼 Log 🕼 Mem Rst stat Rst VM Run Whole step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Op step |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

Figure 11: Variable access tab

Variable access tab (Fig. 11) enables user to view values of variables defined in the Memory Layout file. User may specify additional numbers for reading variable from specific segment and index.

# 5.2 Open VM dialog

The dialog shown in figure (Fig. 12) is used for creating a new virtual Ubichip infrastructure. By providing the assembly file and path to folder containing **\*.mif** files. The number of neurons on every chip is determined from the **define** section of code, while the number of Ubichips equals the number of **\*.mif** files.

| Assembly code:                                  |                          |

|-------------------------------------------------|--------------------------|

| C:\Users\iscaryoth\Desktop\SpiNDeK_1.993\sim\re | esult\assembly.asm       |

| Cam files directory:                            |                          |

| C:\Users\iscaryoth\Desktop\SpiNDeK_1.993\sim\e  | xport 🔄 Browse           |

| No. of CAM files: 9                             |                          |

| Chip size x Chip size y Synapses/Neuron         | Chip configuration       |

| 8 🐳 8 🐳 30 🜩                                    | layout-16bit-basic xml 🔻 |

| V                                               | Cancel                   |

Figure 12: Open VM dialog

Figure 13: Plot window

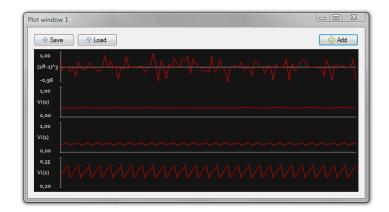

### 5.3 Plot window

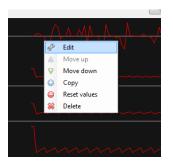

Plot window (Fig. 13) displays time plots drawn using expressions defined by the user. Because creating complex expressions is a non trivial task, the user may save specific configuration of plot expressions to a file, for later use with similar project. New plots may be added by clicking on the "Add" button or copying existing ones. The second option is achieved by right-clicking on one plot and choosing "Copy" from the menu (Fig. 14). Existing plots can be altered by either double-clicking or choosing "Edit" from context menu. Other options of the menu allow simple management of plots.

Figure 14: Plot context menu

## 5.4 Editing plot

Plot editing window (Fig. 15) allows definition of displayed plot name (for informative purposes only), its expression, as well minimum and maximum value (but it may be changed upon to accomodate showing of new sample). The "Digital" checkbox enables better visibility of signals that are inherently digital or are otherwise limited to a discrete set of values, and present the value in a stepped way. In the read-only textbox below all accessible parameters are displayed along with possible parameter ranges. Ranges are sets closed on both sides. The valid operations are listed in Appendix D and few examples are provided in Section 7.

| Name             | ation on now to ac      | cess in memory van           | ables refer to the manual. |        |

|------------------|-------------------------|------------------------------|----------------------------|--------|

| (2R-1)^3         |                         |                              |                            |        |

| Min              | Max                     |                              |                            |        |

| -0,9624418100    | 3950 1                  |                              |                            |        |

| Expression       |                         |                              |                            |        |

| (2*random(       | )-1)^3                  |                              |                            |        |

| Digital          |                         |                              | 🔗 ОК 🛛 🚺                   | Cancel |

| Available variat | oles:                   |                              |                            |        |

|                  |                         | s = [0, 2] a                 |                            |        |

|                  |                         | s = [0, 2] a<br>s = [0, 2] a |                            |        |

|                  |                         |                              | and n = [0, 3]             | E      |

| Lji([u, [s       | , [n]]]) wher           | es=[0,2]                     | and n = [0, 3]             |        |

|                  | ]) where n =            |                              |                            |        |

| Nt([u, [n]       | ]) where n =            | [0, 3]                       |                            |        |

| Mi(fu, fn]       | <pre>]) where n =</pre> | [0, 3]<br>[0, 3]             |                            |        |

Figure 15: Plot edit window

Figure 16: Spike window

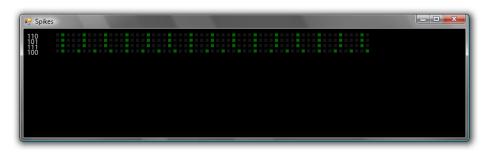

# 5.5 Spike window

Spike window (Fig. 16) is a simple and easily readable form of displaying neurons that fired.

# 6 Implementation details

The main project objective was to deliver a tool that would allow a developer to monitor various artificial network parameters. Initially it was meant to fetch the data from the hardware instance of Ubichip. The VM was developed primarily as an aid in the development of the actual tool, but soon it became a larger project of its own. At first, the VM was meant to increase the speed of development process of the actual tool, but soon enough, after realizing the potential it had, it became the main objective.

Nowadays programmers can choose from magnitude of high level languages designed for fast application development and easy deployment. Also the number of additional libraries and tools provided by both community and language/framework developers is astonishing. All this is meant to increase developer productivity by providing means to allow immediate application creation with ready made components and help or even eliminate the possibility of writing insecure or faulty code. When choosing specific language many different aspects should be considered. Beside the language itself one should also take into account:

- compiler, speed of its code,

- the framework,

- available libraries,

- IDE,

- debugging capabilities and

- portability.

## 6.1 .NET Framework

Due to the numerous reasons I will try to explain later, I have chosen C# as my projects development language. It is object-oriented language, which is actively developed by Microsoft and was designed as a language for their .NET Framework. This framework consists of CLI (Common Language Infrastructure) which is a stack-based code execution environment and variety of compilers. The source code is compiled into a intermediate language called CIL (Common Intermediate Language), which upon first execution is JIT compiled into native code. .NET Framework makes extensive use of object references and GC (Garbage Collector).

The language is placed as a rival to Sun Java, as it shares many similarities. There are, of course, differences both in the syntax and in functionalities. The main differences between their respective execution environments are that the CLI was designed from ground up to host multiple languages, while Java Virtual Machine was initially meant for Java only and was extended recently to support other languages.

.NET is very rapidly expanding. It is being used for server-side dynamically create web pages, as standalone desktop applications, services or components, with the use of Compact Framework it may be used on smart phones or other personal devices, and recently as client-side rich web application Silverlight[9].

### 6.2 Decision-making process

There are many reasons that contribute to the overall decision why have I chosen this particular language. To name the most important arguments (in no particular order):

availability of great tools – most importantly Visual Studio which is famous not only for Intellisense technology that suggest use of possible methods, properties, classes, etc., but also provides extensive debugging capabilities that are very helpful and provide deep insight on the program inner workings; VS supports also some other neat features like code refactoring;

- extensive collection of libraries, both built in the BCL and provided by users;

- GC the CLI handles freeing of resources,

- easy and powerful syntax (delegates, anonymous functions, lambda expressions),

- JIT good execution speed, which can be further improved by building dynamic methods suited for specific purposes,

- easy deployment should easily run in any environment supporting .NET Framework,

- some degree of portability with improvements being done on Mono[10] or DotGNU[2] projects.

What played a crucial role in this decision-making process was my professional work experience which allowed me to start writing this project faster because of my knowledge about both the framework and the language itself. Due to this, the learning curve of new tools and techniques was very fast and allowed me to focus on the project and its functionality.

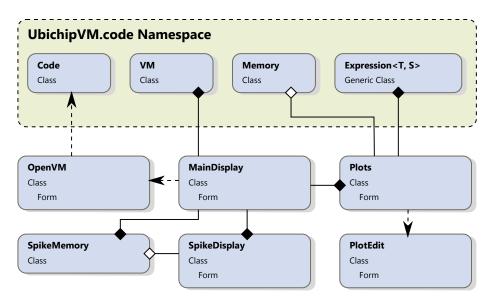

# 6.3 UbichipVM Namespace

The code layout of UI is simple and makes use of VM interfacing classes. The general overview of classes and their respective connections are shown in Figure 17.

- MainDisplay is main UI (User Interface) class. It acts as the primary user interface window. Manages VM and plot/spike windows.

- **OpenVM** acts as advanced "open virtual machine" dialog. Allows user to setup code file, CAM files directory, desired memory layout and network organization.

- SpikeMemory is a helper class for storing spikes. MainDisplay provides the data, while SpikeDisplay provides graphical output.

Figure 17: General class overview

SpikeDisplay graphically represents spikes.

**Plots** provides a window for drawing plots from used defined expressions.

**PlotEdit** handles the editing of plotting expressions.

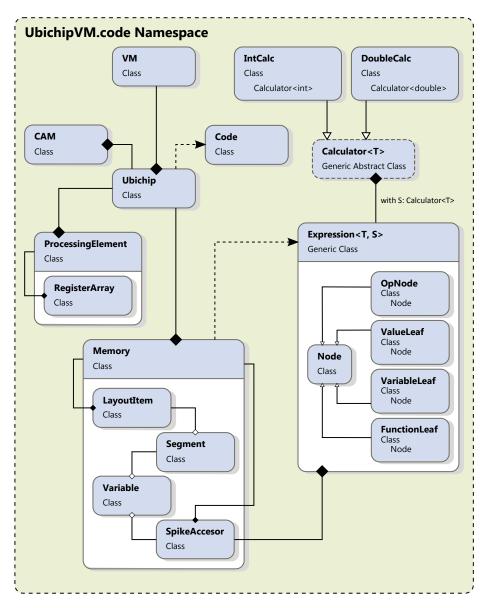

# 6.4 UbichipVM.code Namespace

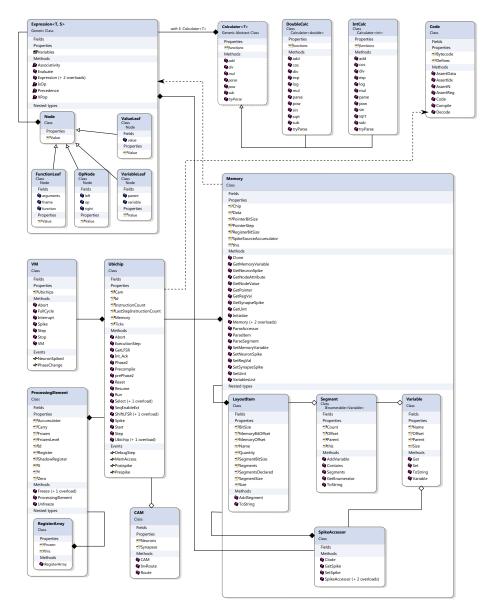

While UI Namespace is straightforward, the code namespace is fairly complex. There are a lot of associations, aggregations and compositions most of which are shown on the class diagram shown in Figure 23.

In the following sections I will try to provide an overview of this namespace most significant classes.

#### 6.4.1 Ubichip

The most important class is the Ubichip class – it acts as a single instance of realworld Ubichip: handles execution of code, memory controller (for phase 1) and signaling external "devices" for synchronization. It provides also some statistics about code execution – number of instructions executed and virtual clock cycles per phase.

Figure 18: Virtual Machine code namespace class overview; for more detailed diagram see Appendix C.

- Ubichip (VM vm, Memory mem, CAM cam, int id, int width, int height, int synapses) the constructor requires a valid reference to VM and Memory classes, because of that it is meant to be instantiated by the VM class. Nevertheless it may be created by hand for special purposes. id is the identification number that will be used when a spike is generated for broadcasting. The last three arguments define basic organization information.

- Ubichip (VM vm, Memory mem, CAM cam, int id, int width, int height, int synapses, int version) extended version of constructor meant for choosing behaviour of certain opcodes. Possible values: 0, 1

- **ProcessingElement Select** (int x, int y) method for retreiving an instance **ProcessingElement** class encapsulating state of single PE.

- **ProcessingElement Select** (int n) same as above, but treats PEs layout as an array instead of a matrix.

- void Start () starts continuous execution. The execution takes place in a different thread.

- void Reset () disables execution and resets Sequencer registers.

- void Resume () resumes previously stopped execution.

- void Int\_Ack () disables execution.

- void Phase2 () scans the PEs array and notifies associated VM of them.

- void Spike (int id, int x, int y) handles storing incoming spike.

- void Abort () aborts currently executing thread. This is meant for use when application request quitting.

#### 6.4.2 VM

VM is a simple class that manages underlying virtual Ubichip structure, synchronizes them and acts as the AER bus for spike exchange.

VM (int nchips, int nx, int ny, int synapses, Memory mem, CAM[] cams) constructor that besides the organization information requires instance of Memory class and same number of CAM objects for routing as specified by nchips parameter

- void Spike (int id, int x, int y) used to broadcast spike signal across

virtual AER bus.

- void Stop (Ubichip sender) used by connected Ubichips to signal that they

have reached a STOP opcode. Once all chips reach this stop, the VM initiates

phase 2.

- void FullCycle () continues execution for phase 1 and then performs phase

2.

- **void Step** () in phase 1 executes one instruction, for phase 2 performs all necessary operations in single methods call.

void Abort () sends Abort signal to all PEs.

#### 6.4.3 Memory

The Memory class was developed to allow modifications to memory layout. Its structure is described in Section 4.5 on page 16. It uses an XML file as an input. This particular format was chosen because of following reasons:

- human-readable,

- hierarchical,

- availability of parsing components,

- easy to use,

- flexible.

- Memory (XmlDocument layout, byte[] contents, int nneurons, int nsynapses) constructor that takes an XML document, SRAM contents and basic structure organization required while parsing layout file for dynamic structrues evaluation.

- List<string> VariablesList () returns list of available variables

- Memory Clone () returns cloned Memory object. Used for instancing multiple virtual Ubichips.

What is more, Memory class implements this[string name] property which returns Variable object, which can be used for storing or retrieving variables in memory of particular Ubichip instance.

#### 6.4.4 Memory.Variable

This class provides a simple functionality for accessing memory variables. It supports both storing and retrieving values from any given segment and whole block repetition (e.g. multiple occurrences of synapse parameters block defined by default memory layout). To use it you must retrieve this object from an instance of Memory class and use one of following functions:

- uint Get (int index, int segment) as the name suggest it retreives value

of variable at specified index and segment,

- void Set (int index, int segment, uint value) method for storing value

into variable located at index and segment.

# 6.5 Code

A class responsible for compiling code and used by Ubichip for decoding instruction bytecodes.

- **Code** (string code) constructor that takes source code as a string. After that the memory contents that are produced can be retreived through Bytecode property, along with define values accessible with Defines property.

- Code.Instruction Decode (byte [] code, uint addr) decodes instruction at a specified address in memory. The Code.Instruction is a simple selfexplanatory structure that contains opcode value, its parameteres and size of instruction that is used for advancing PC. This is a static method.

# 6.6 Challenges

During the development cycle a few essential decisions had to be made. During this project they were motivated by a desire to extend flexibility, prolonging the life of VM. Flexibility however, introduces many implementation challenges.

The primary example would be the implementation of easily accessible memory layout file. It was driven by the need to modify memory structure. Its shape was proposed entirely by me as a result of searching for best way to encapsulate current working model, as well as research of possible memory construct accessible from the Ubichip code. Also its implementation proved to be a challenge, but the outcome surpassed the expectations providing an easy way of accessing specific memory regions of a running VM and thus enabling easy construction of plots to visualize how the algorithm works.

Other important code fragments include the compiler, whose implementation was very helpful for understanding of the opcodes and basic memory structure. Although it was not a trivial task it enabled me to easily and almost instantly code the code execution section.

Designing the class layout and interaction required understanding of Ubichip interface and the way it communicates with other devices. I was able to break down the Ubidule into logical section that later were implemented as VM's classes.

# 7 Simulation results

Because the initial idea was to create a visualization-only tool, the plots play a vital role by visualizing the changes occurring in the neural network. Due to this I have performed a simulation to present the capabilities of this module. For this section all simulations were carried out on a network made of 9 Ubichips, each simulating an 8x8 array of neurons, each having 30 synapses.

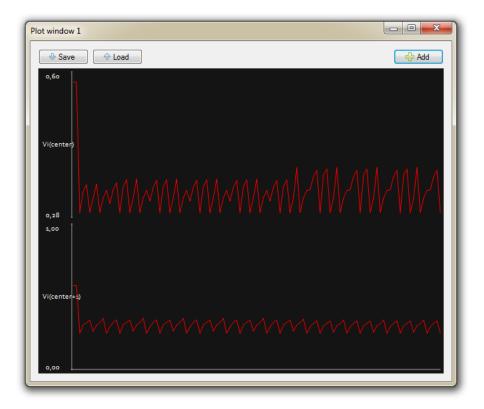

One of basic plot is showing membrane potential  $(V_i)$  for two neurons. One in the center of the network, and another one just next to it. From the plot one can read that that in 2/3 of the time it shows there is a slight increase in maximum oscillation value for first neuron potential.

$$Vi(center) = Vi(4, 0, 32)$$

(9)

$$Vi(center + 1) = Vi(4, 0, 33)$$

(10)

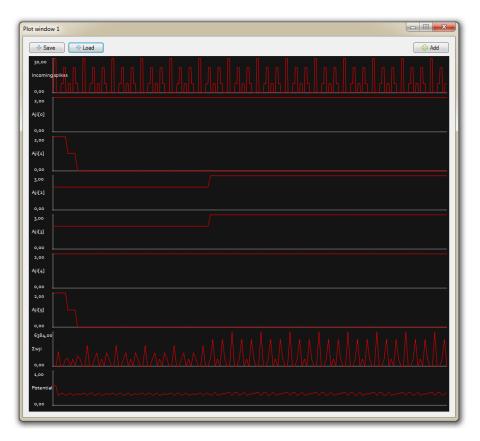

To better understand what happens at this moment we should add more plots to our window. At the top of Figure 20 plot of potential value is shown with 17 more plots showing  $A_{ji}$  – activation level value for 17 synapses connected to this particular neuron. It is clearly visible that activation level of few synapses drops rapidly at the beginning reaching level 0. Shortly after the half of time shown on the plot, activation level of few more synapses rise. This increase has an effect on potential value which begins oscillating reaching higher levels. Such behaviour is expected and is showing adaptability of this network.

$$Vi(center) = Vi(4, 0, 32)$$

(11)

$$A0 = Aji(4, 0, 32) \tag{12}$$

- A1 = Aji(4, 1, 32)(13)

- ... (14)

In the last figure (21) a more advanced use of plot window is employed. The first plot shows sum of all incoming spike signals, next 6 plots present activation level,

Figure 19: Visualization of potential value oscillations in a relatively large network (576 neurons, 30 synapses each)

| t window 1                 |        |         |

|----------------------------|--------|---------|

| 🖑 Save                     | ⊕ Load | 🕂 🕂 Add |

|                            |        |         |

| 40000,00<br>Vi<br>18000,00 |        |         |

|                            |        |         |

| A0<br>0,00                 |        |         |

| 2,00<br>A1                 |        |         |

| 0,00                       |        |         |

| A3 00 -                    |        |         |