# PROJECT: TERASCALE RELIABLE ADAPTIVE MEMORY SYSTEMS FP7-INFSO-IST-248789

# PROCESS VARIABILITY IN SUB-16nm bulk CMOS technology

Acronym TRAMS

Project name Terascale Reliable Adaptive Memory Systems

Grant agreement number 248789

Call FP7-ICT-2009-4

Coordinator Universitat Politècnica de Catalunya (UPC)

Partners University of Glasgow (UOG), Imec, Intel Corporation Iberia

Start date of the project 01.01.2010

Duration 36 months, until 31.12.2012

Project web site trams-project.eu

Target dissemination level Public

Authors: Antonio Rubio, Joan Figueras, Iana Vatajlu, Ramon Canal

© 2012 TRAMS Project Consortium, All Rights Reserved. For the TRAMS Project Consortium, see the www.trams-project.eu web-site.

# **Table of Contents**

| 1. | In           | troductiontroduction        | 1 |  |  |

|----|--------------|-----------------------------|---|--|--|

| _  |              |                             | _ |  |  |

| 2. | V            | ariability scenarios        | 4 |  |  |

|    | 2.1.         | Objectives and introduction | 2 |  |  |

|    |              |                             |   |  |  |

|    | 2.2.         | Variability scenarios       | 2 |  |  |

| 3. | . References |                             |   |  |  |

## 1. Introduction

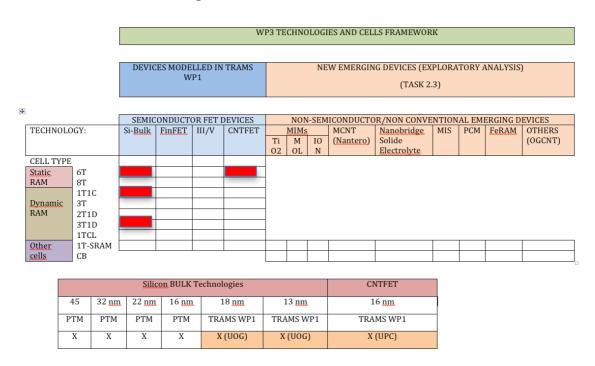

The aim of WP3 is to deliver key mechanisms to mitigate and reduce variability and increase reliability at layout, circuits and system level, as well as to determine and propose innovative compensating and fault tolerant techniques considering the PVT variability and corresponding yield impact. The key effects of that environmental fluctuations and process variations are exposed in this deliverable. These objectives will be developed during the second and third year of the project, milestones 4 to 8. Figure 1 shows the global framework of technologies and cell type objective of Work Package 3 (WP3). At device level we differentiate between devices modelled by TRAMS whose characteristics as well as variability and reliability performances are a goal of the project (Bulk CMOS is scheduled for M12 (Milestone MS2), Finfets for M18 (Milestone MS3), CNT for M18, the rest for M30 (Milestones MS5,6)) and medium/long term technology devices with promising characteristics for memory systems that although they are not objective of device modelling in TRAMS they will be considered at a exploratory level at circuit and system level (Task 2.3, M36). In this last set of technologies we will include Metal-Insulator-Metal devices (MIMs) [1], RRAM [2], electromechanical CNT arrays (MCNT) [3], Nanobridge devices [4], Metal-Insulator-Semiconductor (MIS) [5], Phase change memories (PCM) [6], Ferromagnetic RAMs [7], MRAM [8] and other devices. The objective of T2.3 will be the analysis of new memory cells such as 1T-SRAM and CB. In this first year and in relation with deliverable D3.6, Task 3.1 has been dedicated to evaluate the impact of the PVT variations in a set of SRAM and DRAM cells (red boxes in Figure 1), using device models previously available (PMT for Silicon and Stanford for CNTFET) and including the new and original results from WP1 with the device modelling and variability evaluation from 18 and 13 bulk CMOS technologies.

Figure 1. Framework of technologies and memory cells considered in WP3. Red boxes show the technologies and cell considered in this deliverable.

## 2. Variability scenarios

#### 2.1. Objectives and introduction

The aim of this document is the analysis of the environmental (power supply voltage and temperature) fluctuations, the process variability for different technology nodes including sub-22nm as well as BTI degradation and SEU impact on memory circuits. We will evaluate basic 6T, 1T1C and 3T1D bit cells, and 32KB and 4MB cache memory circuits for 6T and 3T1D and we consider the following Si-bulk CMOS technologies 45, 32, 22, 18, 16, 13 and CNT (equivalent to 16nm node). Device models for 45, 32, 22 and 16 nm are the ones known as Predictive Technology Models (University of Arizona [9]), the models for 18 and 13 nm are results of WP1, and the CNT analysis uses a modification of the models of Stanford (see section 8) with preliminary results about variability from TRAMS WP1..

Section 4 is dedicated to SRAM memories characterized by the 6T memory cell. Section 4.1 analyses the impact of VT and node variations on speed parameters and energy consumption, and in section 4.2 the robustness of the cell in front of process parameter variations is presented.

Section 5 analyses DRAM memories, characterized by 1T1C in section 5.1 and 3T1D in the rest. Section 5.2 analyses the impact of VT and node variations on speed parameters. In section 5.3 the robustness of the 3T1D cell in front of process variation is investigated and in section 5.4 the analysis of the impact of BTI degradation of 3T1D on memory performances and yield is presented. The impact of the process variation on the cache memory performances (both 6T and 3T1D) are analysed in Section 6. In section 7 the impact of SEU on the memories reliability is investigated, and in Section 8 the performances of CNT in comparison with the rest of Si-bulk technologies are presented (for the 6T cell).

#### 2.2. Variability scenarios

The margin of temperature variation considered in this document is, in general, the range 25  $^{\circ}$ C to 110  $^{\circ}$ C. The margin of V<sub>DD</sub> variations due to RI and RdI/dt has been considered as a +/-10% of the nominal power supply used in each technology. For process variation we have considered the following different models:

#### **Process variation model used for PTM technologies**

For the four Si-bulk CMOS technologies, 45, 32, 22 and 16 nm, covered by PTM we have considered the process variations of the threshold voltage of the devices ( $V_{th}$ ) and the device geometry (L and W).

For the Vth we have assumed a Gaussian distribution and independent components for random variation (due to random dopants distribution, RDD and line edge roughness, LER) and correlated Gaussian for systematic variations. Geometry variations have been modelled as systematic Gaussian distributions. In all the analysis at system level (cache) both systematic and random variations have been considered and in the case of analysis at cell level, only Vth random variations are contemplated. For each technology we have considered different variation scenarios, standard for 45nm, moderated and high for 32nm and moderated, high and very high for 22 and 16nm. Table 1 shows the standard deviations or second moment of the respective

distributions. The levels of variability assumed in the high and very high variability scenarios are consequent with that observed and deduced for 18 and 13 nm technologies, result of Work Package 1.

| Technology | Scenario  | total systematic  | random(*)(**)     | Geometry          |

|------------|-----------|-------------------|-------------------|-------------------|

|            |           | 100 x 1 σ/nominal | 100 x 1 σ/nominal | 100 x 1 σ/nominal |

|            |           | Vth               | Vth               | L,W               |

| 45 nm      | standard  | 2%                | 4%                | 2%                |

| 32nm       | moderated | 3%                | 6%                | 2%                |

|            | high      | 4%                | 15%               | 2%                |

| 22nm       | moderated | 4%                | 8%                | 2.5%              |

|            | high      | 4%                | 15%               | 2.5%              |

|            | very high | 5%                | 30%               | 2.5%              |

| 16nm       | moderated | 5%                | 10%               | 3%                |

|            | high      | 5%                | 20%               | 3%                |

|            | very high | 6%                | 40%               | 3%                |

<sup>(\*) (</sup>random dopants distribution, RDD, and line edge roughness, LER), non correlate (\*\*) for minimum size, for general case correct with /sqrt(WL)

Table 1. Process variation model for the analysis with PTM technologies

#### Process variation model used for WP1 technologies

Devices models for 18 and 13 nm technologies provided by WP1 present a very high variability on  $V_{th}$ , caused by RDD and LER mechanisms. The standard deviations have been obtained from WP1 analysis and are given in Table 2.

#### Process variation model used for CNT technology

The process variation model for CNTFET technology is part of the work done in WP1 (Task 1.1), an introduction to the variation model used is presented in Section 8.

| device    | σ Vth  | 100xσ/nominal |

|-----------|--------|---------------|

| 18nm NMOS | 66.7mV | 33%           |

| 18nm PMOS | 116mV  | 58%           |

| 13nm NMOS | 78.8mV | 39%           |

| 13nm PMOS | 116mV  | 58%           |

(\*) (random dopants distribution, RDD, and line edge roughness, LER), non correlate (\*\*) for minimum size, for general case correct with /sqrt(WL)

Table 2. Vth process variation model for analysis with 18 and 13 nm CMOS devices (VDD=0.9 volts).

#### 3. References

- [10] J. Deng and H.-S. P. Wong., "A compact SPICE model for carbon-nanotube field- effect transistors including nonidealities and its application Part II: Full device model and circuit performance benchmarking," *IEEE Transaction on Electron Devices*, vol. 54, 2007.

- [11] J. Deng and H.-S. P. Wong, "A compact SPICE model for carbon nanotube field-effect transistors including nonidealities and its application Part I: Model of the intrinsic channel region," *IEEE Trans. Electron Devices*, vol. 54, 2007.

- [12] Neil H. E. Weste and David Harris, *CMOS VLSI Design, A circuits and Systems Perspective*.: Pearson International Edition, 2005.

- [13] Y Toasaka et al., "Measurement and Analysis of Soft Errors in Sub-Half Micron CMOS Circuits," *IEEE Transactions on Electronic Devices*, p. 1453, 1998.

- [14] N Seifert et al., "Radiation Induced Soft Error Rates of Advanced CMOS bulk Devices," in *44th Annual International Reliability Physics Symposium*, San Jose, 2006, pp. 217-225.

- [15] C. T. Sah, "Characteristics of the metal-oxide-semiconductor transistors," *IEEE Transactions on Electron Devices*, vol. 11, no. 7, pp. 324-345, 1964.

- [16] Jan M Rabaey, Anantha Chandrakasan, and Borivoje Nikolic, *Digital Integrated Circuits, A design perspective*.: Prentice Hall, Pearson International Edition, 2003.

- [17] H. Niederreiter, "Random number generation and Quasi-Monte Carlo methods," in *Society for Industrial and Applied Mathematics*, 1992.

- [18] Riaz Naseer, Younes Boulghassoul, Jeff Draper, Sandeepan DasGupta, and Art Witulski, "Critical Charge Characterization for Soft Error rate Modelling in 90nm SRAM," in *IEEE International Symposium on Circuits and Systems*, New Orleans, LA, 2007, pp. 1879 1882.

- [19] S Mukhopadhyay, H Mahmoodi, and K. Roy, "Modeling of failure probability and statistical design of SRAM array for yield enhancement in nanoscaled CMOS," *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on*, vol. 24, no. 12, pp. 1859-1880, 2005.

- [20] W.K. Luk, J. Cai, R.H. Dennard, M.J. Immediato, and S.V. Kosonocky, "A 3-transistor DRAM cell with gated diode for enhanced speed and retention time," in *IEEE Symposium on VLSI Circuits. Digest of Technical Papers*, 2007, pp. 184-185.

- [21] K. Lovin, B.C. Lee, X. Liang, D. Brooks, and G.Y. Wei, "Empirical performance models for 3T1D memories," in *IEEE International Conference on Computer Design*, 2010, pp. 398-403.

- [22] X. Liang, R. Canal, G.Y. Wei, and D. Brooks, "Process variation tolerant 3T1D-based cache architectures," in *Annual IEEE/ACM International Symposium on Microarchitecture*, 2007, pp. 15-26.

- [23] S.V. Kumar, C.H. Kim, and S.S. Sapatnekar, "Adaptive techniques for overcoming performance degradation due to aging in digital circuits," in *IEEE Proceedings of the 2009 Asia and South Pacific Design Automation Conference*, 2009, pp. 284-289.

- [24] K. Kang, M.A. Alam, and K. Roy, "Characterization of NBTI induced Temporal Perfromance Degradation in Nano-Scale SRAM array using IDDQ\*," in *International Test Conference*, vol. 1, 2007, p. 278.

- [25] Norman P Jouppi and Steven J E. Wilton, "An Enhanced Access and Cycle Time Model for On-Chip Caches," Palo Alto, California, 1994.

- [26] E. Hoff, "Silicon-gate Dynamic CMOS Crams 1024 Bits on a Chip," Electronics, pp. 68-73, 1970.

- [27] Tino Heijmen, Damien Giot, and Philippe Roche, "factors that impact the critical charge of memory elements," *Proceedings of the 12th IEEE international On-Line Testing Symposium*, September 2006.

- [28] Peter Hazucha, Christer Svensson, and Stephen A Wende, "Cosmic-Ray Soft Error Rate Characterization of a Standard 0.6um CMOS Process," *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, 2000.

- [29] Balkaran S Gill, Chris Papachristou, and Francis G Wolf, "A new Asymmetric SRAM Cell to Reduce Soft Errors and Leakage Power in FPGA," in *Design, Automation & Test in Europe Conference & Exhibition*, Nice, 2007, pp. 1-6.

- [30] A. Genz, "Numerical computation of multivariate normal probabilities," *Journal of Computational and Graphical Statistics*, pp. 141-149, 1992.

- [31] R. Fernandez et al., "AC NBTI studied in the 1 Hz--2 GHz range on dedicated on-chip CMOS circuits," in *IEEE International Electron Devices Meeting*, 2007, pp. 1-4.

- [32] S. Drapatz, G. Georgakos, and D. Schmitt-Landsiedel, "Impact of negative and positive bias temperature stress on 6T-SRAM cells," *Advances in Radio Science-Kleinheubacher Berichte*, vol. 7, 2009.

- [33] Paul E Dodd and Lloyd W Massengill, "Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics," *IEEE TRANSACTIONS ON NUCLEAR SCIENCE*, June, 2003.

- [34] R. Degraeve et al., "Review of reliability issues in high-k/metal gate stacks," in *IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits*, 2008, pp. 1-6.

- [35] V Degalahal, N Vijaykrishnan, and M J Irwin, "Analyzing Soft Errors in Leakage Optimized SRAM Design," in *16th International Conference on VLSI Design*, 2003, pp. 227-233.

- [36] F. Crupi et al., "Positive bias temperature instability in nMOSFETs with ultra-thin Hf-silicate gate dielectrics," *Microelectronic Engineering*, vol. 80, pp. 130-133, 2005.

- [37] Y Cao, T Sato, D Sylvester, M Orshansky, and C Hu. http://ptm.asu.edu/.

- [38] P. Avouris, "Molecular electronics with carbon nanotubes," *Accounts of Chemical Research*, vol. 35, pp. 1026–1034, 2002.

- [39] K. Agarwal, S. Nassif, "The impact of random device variation on SRAM cell stability in sub-90-nm CMOS technologies," *IEEE Transctions on VLSI Systems*, vol. 16, no. 1, pp. 86-97, 2008.

- [40] A. J. Bhavnagarwala, X. Tang and J. D. Meindl, "The impact of intrinsic device fluctuations on CMOS SRAM cell stability," *IEEE Journal of Solid-State Circuits*, vol. 36, no. 4, pp. 658-665, 2001.

- [41] E. Seevinck, F. J. List and J. Lohstroh, "Static-noise margin analysis of MOS SRAM cells," *IEEE Journal of Solid-State Circuits*, vol. sc-22, no. 5, pp. 748-754, October 1987.

- [42] S. Srivastava and J. Roychowdhury, "Rapid estimation of the probability of failure due to MOS threshold variations," in *Proceedings of Custom Integrated Circuits Conference*, 2007.

- [43] F. Gong, H. Yu, Y. Shi, D. Kim, Y. Ren and L. He, "QuickYield: an efficient global-search based parametric yield estimation with performance constraints," in *Design Automation Conference*, 2010, pp. 392-397.

- [9] Predictive Technology Model. [Online]. http://ptm.asu.edu/

- [44] R. Kanj, R. Joshi and S. Nassif, "Mixture Importance Sampling and its applications to the analysis of SRAM designs in the presence of rare failure events," in *IEEE Design Automation Conference*, 2006, pp. 69-72.

- [45] S. Mukhopadhyay, Q. Chen and K. Roy, "Memories in scaled technologies: a review of process induced failures, test methodologies and fault tolerance," in *Design and Diagnostics of Electronic Circuits and Systems (DDECS)*, 2007, pp. 1-6.

- [46] (2009) International Technology Roadmap of Semiconductors. [Online]. http://www.itrs.net/

- [47] T.S.Doorn, E.J.W. ter Maten, J.A. Croon, A. Di Bucchianico, O. Wittich, "Importance Sampling Monte Carlo simulations for accurate estimation of SRAM yield," in *European Solid-State Circuits Conference*, 2008, pp. 230-233.

- [48] C.-T. Chuang, S. Mukhopadhyay, J.-J. Kim, K. Kim, R. Rao, "High-performance SRAM in nanoscale CMOS: Design challenges and techniques," in *IEEE International Workshop on MTDT*, 2007, pp. 4-12.

- [49] C. Gu and J. Roychowdhury, "An efficient, fully nonlinear, variability-aware non-Monte-Carlo yield estimation procedure with applications to SRAM cells and ring oscillators," in *Proceedings of ASP-DAC*, 2008.

- [50] D. E. Hocevar, M. R. Lightner, and T. N. Trick, "A study of variance reduction technique for estimating circuit yields," *IEEE Transactions on Computer-Aided Design*, vol. CAD-2, no. 3, July 1983.

- [51] X. Du and W. Chen, "A Most Probable Point Based Method for Uncertainty Analysis," Journal of Design

- and Manufacturing Automation, vol. 4, pp. 47-66, 2000.

- [52] Brian Cline, Kaviraj Chopra, David Blaauw, Andres Torres, and Savithri Sundareswaran, "Transistor-specific delay modeling for SSTA," in *Design, automation and test in Europe (DATE '08)*, New York, 2008, pp. 592-597.

- [53] R.H. Dennard W.K.Luk, "A Novel Dynamic Memory Cell with Internal Voltage Gain," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 4, pp. 884-894, April 2005.

- [1] A. Chen et al., "Switching characteristics of Cu2O metal-insulator-metal resistive memory," *Applied Physics Letters*, vol. 91(12), pp. 123517-3, 2007.

- [54] A. Sekijama et al., "A 1V operating 256kbit CMOS SRAM," in *IEEE Symposium on VLSI Circuits*, 1990, pp. 53-54.

- [55] X. Brooks and D. Liang, "Mitigating the impact of process variations on processor register files and execution units," in *IEEE International Symposium on Microarchitecture*, 2006.

- [56] H. Calhoun et al., "Digital Circuit Design Challenges and Opportunities in the Era of Nanoscaled CMOS," *Proceedings of the IEEE*, vol. 96, no. 2, pp. 343-365, 2008.

- [57] DE. Khalil et al., "Accurate Estimation of SRAM Dynamic Stability," *IEEE Transactions on VLSI Systems*, vol. 16, no. 12, pp. 1639-1647, December 2008.

- [4] M. Hickey et al., "Spin-transfer torque efficiency measured using a permalloy nanobridge," *Applied Physics Letters*, vol. 97(20), pp. 202505-3, 2010.

- [6] H. Wong et al., "Phase change memory," *Proceedings IEEE*, vol. 98(12), pp. 2201-2227, 2010.

- [58] F. Gong, Y. Shi, H. Yu, and L. He, "Parametric yield estimation for SRAM cells: concepts, algorithms and challenges," in *Design Automation Conference, Knowledge Center Article*, 2010.

- [2] H. Wan et al., "Electrical and testing reliability of CuxO based RRAM," in *IEEE International Conference on Solid-State Integrated Circuit Technology*, 2010, pp. 1100-1102.

- [8] R. Nebashi et al., "A 90nm 12ns 32Mb 2T1MTJ MRAM," in *IEEE International Solid-State Circuit Conference*, 2009, pp. 462-463.

- [5] S. Williams, M.F. Mabrook, and D.M. Taylor, "Floating-gate memory based on an organic metal-insulator-semiconductor capacitor," *Applied Physics Letters*, vol. 95(9), pp. 093309-3, 2009.

- [7] Y. Nagano et al., "0.18nm SBT-based embedded FeRAM operating at a low voltage of 1.1 V," in *IEEE Symposium on VLSI Technology*, 2003, pp. 171-172.

- [3] T. Rueckes et al., "Carbon nanotube-based nonvolatile random access memory for molecular computing," *Science*, vol. 289, pp. 94-97, July 2000.

- [59] J.A. Croon, S. Decoutere, W. Sansen, and H.E. Maes, "Phisical modeling and prediction of the matching proprieties of MOSFETs," in *ESSDERC*, 2004, pp. 193-196.

- [60] J. Barth et al., "A 500 MHz Random Cycle, 1.5 ns Latency, SOI Embedded DRAM Macro Featuring a Three-Transistor Micro Sense Amplifier," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 1, pp. 86-93, January 2008.

- [61] G. Wang et al., "A 0.127 um2 High Performnace 65nm SOI Based embedded DRAM for on-processor Applications," in *Electron Devices Meeting*, 2006.

- [62] S.Wind et al., "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes," *Appl. Phys. Lett.*, vol. 80, pp. 3817–3819, 2002.

- [63] A. Javey et al., "Self-aligned ballistic molecular transistors and electrically parallel nanotube arrays," *Nano Letters*, vol. 4, no. 7, pp. 1319–1322, 2004.

- [64] X. Liu et al, "Detailed analysis of the mean diameter and diameter distribution of single-wall carbon nanotubes from their optical response," *Phys. Rev. B*, vol. 66, no. 4, 2002.

- [65] Li Y. et al., "Preferential Growth of Semiconducting Single-Walled Carbon Nanotubes by a Plasma Enhanced CVD Method," *Nano Letters*, vol. 4, pp. 317-321, 2004.

- [66] D. Feng, and L. Dai L. Qu, "Preferential Syntheses of Semiconducting Vertically Aligned Single-Walled Carbon Nanotubes for Direct Use in FETs," *Nano Letters*, vol. 8(9), pp. 2682-2687, 2008.

- [67] N. Park. J. H. Ko, and W. park D. Kang, "Oxygen-induced p-type doping of a long individual single-walled carbon nanotube," *Nanotechnology*, vol. 16, pp. 1048-1052, 2005.

- [68] C. Klinke. A. Afzali, and P. Avouris J. Chen, "Self-aligned carbon nanotube transistors with charge transfer doping," *Appl. Phys. Lett.*, vol. 86, no. 477, 2005.

- [69] S. Kang at al., "High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes," *Nature Nanotecnology*, vol. 2, pp. 230-236, 2007.

- [70] J. Deng, S. Mitra, and H.-S. Wong N. Patil, "Circuit-level performance benchmarking and scalability analysis of carbon nanotube transistor circuits," *Nanotechnology*, vol. 8, no. 1, pp. 37-45, 2009.

- [71] M. Meterelliyoz, J.P. Kulkarni, and and K. Roy, "Analysis of SRAM and eDRAM Cache Memories Under Spatial Temperature Variations," *Computer-Aided Design of Integrated Circuits and Systems*, vol. 29, no. 1, pp. 2-13, 2010.