# Modeling of Linear–Assisted DC–DC Converters

## Herminio Martínez, Alfonso Conesa

College of Industrial Engineering of Barcelona (EUETIB). Department of Electronic Engineering

Technical University of Catalonia (UPC)

C/ Comte d'Urgell, 187. E–08036. Barcelona, Spain

{herminio.martinez, alfonso.conesa}@upc.edu

Abstract—This paper shows the modeling of a linear-assisted or hybrid (linear & switching) DC-DC converters. In this kind of converters, an auxiliary linear regulator is used, which objective is to cancel the ripple at the output voltage and provide fast responses for load variations. On the other hand, a switching converter, connected in parallel with the linear regulator, allows to supply almost the whole output current demanded by the load. The objective of this topology is to take advantage of the suitable regulation characteristics that series linear voltage regulators have, but almost achieving the high efficiency that switching DC-DC converters provide. Linear-assisted DC-DC converters are feedback systems with potential instability. Therefore, their modeling is mandatory in order to obtain design guidelines and assure stability of the implemented power supply system.

### I. Introduction

Series linear regulators have been structures widely used in power supply systems for decades, providing supplies with low or moderate currents and consume [1], [2]. This kind of voltage regulators has several advantages that lead their use. However, in spite of these advantages, linear regulators suffer from some serious drawbacks. As a result, they are not recommendable in some supply systems, especially for high power. The alternative, DC–DC switching converters [3], [4], has evident advantages opposite to linear regulators. However, the design and implementation of this sort of converters is a more complex process than in linear regulators, especially their control loops when both line and load regulations are desired. Furthermore, the intrinsic switched nature of these converters produces ripples in the output voltage and an increment of the EMIs in neighboring electronic systems.

The use of *linear–assisted hybrid DC–DC converter* (or *linear–switching hybrid DC–DC converter*) takes advantages of previous alternatives [5]–[7]. Apart from this, some of the aforementioned drawbacks are minimized as, for instance, the low efficiency and the high power dissipation in linear regulators, or the complexity in the design of the control for switching converters.

In this article, a proposal of variable frequency linear–assisted hybrid DC–DC converter (or linear–switching hybrid

*DC–DC converter*) and its modeling is presented. The system has a control loop to maintain a constant output voltage that could induce instabilities as a function of the values of the circuit components and the values of the load (in a similar way that linear regulators). Thus a stability study is necessary to obtain design guidelines for this kind of DC–DC converters and assure the stability of the implemented power supply system.

## II. STRUCTURE OF A LINEAR-ASSISTED CONVERTER

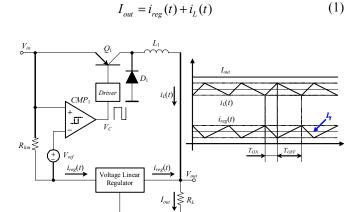

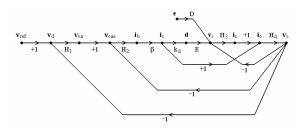

The proposed configuration makes use of an analog comparator that controls the conduction or cut of the transistor  $Q_1$ , just as it can be seen in figure 1, and fixes the switching frequency. Note that the objective of the switching converter is to provide the excess of current that the linear regulator does not supply. Consequently:

Figure 1. Basic structure of a self–switched hybrid regulator that supplies a load  $R_L$ , and currents through  $R_L$ , inductance  $L_1$  and linear regulator in the steady state.

Just not considering in a first approximation any hysteresis in the comparator  $CMP_1$ , the operation of the circuit is just as it is explained as follows: if the load current is below a boundary current value, that we name as threshold switching current,  $I_{\gamma}$ , the output of  $CMP_1$  is held low. Thus the switching

converter will be disabled and  $I_L$  will be zero. As a result, the linear regulator supplies the load  $R_L$ , providing all the output current ( $I_{reg}=I_{out}$ ). However, in the moment that load current increases and goes slightly beyond this limit current  $I_\gamma$ , the comparator output will pass to high level, increasing  $I_L$  in a linear form. Taking into account expression (1) and that the load current is constant (equal to  $V_{out}/R_L$ ),  $i_{reg}(t)$  will tend to decrease also linearly (figure 1), just reaching a value below  $I_\gamma$ . In this moment, the comparator changes its output from high to low level, cutting  $Q_1$  and forcing  $I_L$  to decrease. Then, when the current in the inductance decreases to a value in which  $i_{reg}(t) > I_\gamma$ , the comparator changes from low to high level, repeating the cycle again.

$V_{ref}$  and  $R_{lim}$  determine the value of the threshold switching current  $I_{\gamma}$  according to  $R_{lim} = V_{ref}/I_{\gamma}$ . With the objective of reducing the value of the dissipated power by the internal transistor of the linear regulator to the utmost, this current  $I_{\gamma}$  has to be the minimum and necessary in order to make the linear regulator work properly, without penalizing its good regulation characteristics. It will also increase the efficiency of the system, even with significant load currents.

The delays of the electronic circuits determine a little hysteresis that limits the maximum value of the switching frequency. Nevertheless, with the objective of fixing the maximum value of this switching frequency to a suitable value, it is convenient to add a hysteresis to  $CMP_1$ .

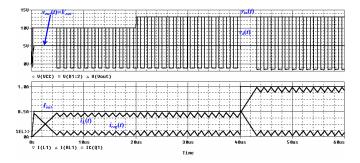

A practical implementation of the self–switched hybrid regulator presented in figure 1 can be found in [8]. Figure 2 shows the transient of a variable–frequency linear–assisted converter with  $V_{in}$ =10 V. Having into account that the upper and lower switching threshold levels of the comparator (Schmitt trigger) are  $V_H$  and  $V_L$ , respectively, the switching frequency is given by:

$$f = \frac{R_{\text{lim}}}{L_1} \frac{V_{out}}{V_H - V_L} \left( 1 - \frac{V_{out}}{V_{in}} \right)$$

(2)

Figure 2. Transient response of the variable–frequency linear–assisted converter with  $V_{in}$ =10 V. It can be seen the response of the circuit to an input step from 10 V to 13 V in t=20  $\mu$ s, and when there is a decrement of the load resistance from 10  $\Omega$  to 5  $\Omega$  in t=40  $\mu$ s.

#### III. MODELING OF HYBRID CONVERTERS

It is important to highlight that in previous discussion the effect of an output capacitance has not been considered.

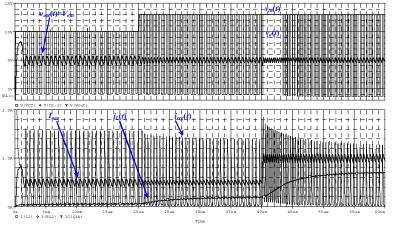

Effectively, these linear–assisted converters work properly when the load capacitance is null. In spite of this, some capacitance can be suitable in order to eliminate possible transitory peaks in the output voltage when the converter supplies variable loads (that is, high slew–rate in the output current). This output capacitor improves the response of the converter appreciably. However, the effect of an output capacitor in parallel with the load, a parasitic output capacitance or a capacitance load induces a trend to instability. These instabilities produce and important and considerable increment of the output–voltage ripple around the desired average output voltage that is observed in the linear–assisted converters.

Figure 3 shows a transient response of the linear–assisted converter in the same conditions that figure 2 but with an output capacitance  $C_L$ =100 nF and an equivalent series resistance (ESR) equal to 10  $m\Omega$ . Note that, with these conditions, expression (1) is not satisfied due to the inclusion of the  $C_L$  network. So the obtained waveforms in the circuit are not as the reflected in figure 2. In addition, the current  $i_{reg}(t)$  increases and thus the efficiency of the converter is reduced significantly.

Figure 3. Transient response of the linear–assisted converter with an output capacitance  $C_L$ =100 nF. It can be seen the response of the circuit to an input step from 10 V to 13 V in t=20  $\mu$ s, and when there is a decrement of the load resistance from 10  $\Omega$  to 5  $\Omega$  in t=40  $\mu$ s.

Therefore, the  $C_L$  has to be an agreement value. This value must be high enough but providing stability of the supply system. Even more, the authors have observed that in a linear–assisted converter, the frequency response of the system (and thus the stability conditions) is highly sensitive to the load conditions and the output capacitor connected (or parasitic capacitance existing) in parallel with the load resistor. Some parameters determine the aforementioned instabilities. However, the most important are the values of the output capacitance  $C_L$ , its equivalent series resistance, the load resistor  $R_L$  and the inductor  $L_1$ .

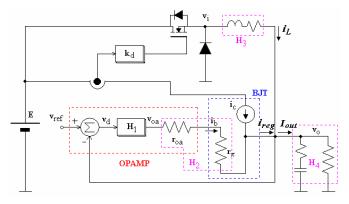

All these points make necessary to analyze the converter in order to obtain design approaches that guarantees its stability. The model of the linear–assisted DC–DC converter is presented in figure 4. For the operational amplifier is considered its low–pass response in block  $H_1$ , with a

differential gain  $(A_d)$  and a dominant pole  $(\omega_O)$ , and its output resistance  $(r_{oa})$ . For transistor (working in its linear zone) is considered the base–emitter dynamic resistance  $(r_{\pi})$  and a current gain  $(\beta)$ . Thus the block  $H_2$  contains only the association of resistors  $r_{oa}$  and  $r_{\pi}$ .

Figure 4. Proposed model of the hybrid converter.

The  $r_{\pi}$  value is calculated as usual from equation (3):

$$r_{\pi} = \frac{dv_{be}}{di_b} = \frac{\beta}{I_{Ca}} \frac{v_T}{\lambda}$$

(3)

The  $k_d$  block makes sense of collector current and obtain the conducting ratio of switching transistor as equation (4).

$$k_d = \frac{\Delta d}{\Delta i_c} = \frac{1}{i_{c,\text{max}}} \tag{4}$$

The inductor small signal voltage is  $v_i$  and defined as usual:

$$v_i = (d \cdot E + e \cdot D) - v_o \tag{5}$$

The inductor current ( $i_L$  in figure 4) is obtained thanks to the voltage  $v_i$  and the block  $H_3$ , which models the inductor and its series resistance. Finally, with output current ( $i_{out}$ ) and block  $H_4$ , the output voltage ( $v_o$ ) is obtained. In the block  $H_4$  the load resistance and output capacitor with its ESR is modeled.

In figure 6 is presented the flow graph of the modeled linear–assisted converter. Applying the Mason rule we obtain the transfer function given by:

$$G(s) = \frac{v_o(s)}{v_{ref}(s)} \tag{6}$$

In table I the Maple<sup>®</sup> code is presented in order to obtain the transfer function of equation (6). Subsequent to this, the result is simulated with Matlab<sup>®</sup> to obtain the poles zeros map of the system (*pzmap* function). The used simulation values are close to the experimental values of the implemented prototype (table II).

Figure 5. Proposed model of the hybrid converter.

TABLE I. MAPLE  $^{\oplus}$  CODE USED TO OBTAIN THE TRANSFER FUNCTION GIVEN IN EQUATION (6) FOR THE LINEAR—ASSISTED DC—DC CONVERTER

TABLE II. SIMULATION VALUES USED IN THE OBTAINED MODEL

| Parameter       | Value                    | Parameter | Value  | Parameter               | Value                                      |

|-----------------|--------------------------|-----------|--------|-------------------------|--------------------------------------------|

| $A_{oa}$        | 2·10 <sup>5</sup><br>V/V | $R_L$     | 2 Ω    | $I_{cq}$ = $I_{\gamma}$ | 50 mA                                      |

| ω <sub>oa</sub> | 2·π·10<br>rad/s          | $L_1$     | 100 μΗ | β                       | 100                                        |

| $r_{oa}$        | 100 Ω                    | $v_t$     | 25 mV  | $r_d$                   | $(\beta \cdot v_t)/(\lambda \cdot I_{cq})$ |

| E               | 12 V                     | λ         | 1      | $k_d$                   | $1/100 \cdot 10^{-3}$                      |

It is observed that the system can be stable or unstable with different values of the load resistor, the inductance  $L_1$ , the load capacitance  $C_L$  and its ESR.

#### IV. SIMULATION AND EXPERIMENTAL RESULTS

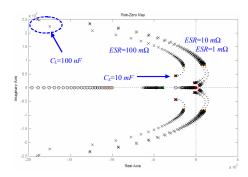

Using the model proposed in previous section, some interesting simulations have been carried out in order to determine the stability of the system as a function of different circuit's parameters. In figure 6 the root locus diagram is presented. In particular, we can find three curves for three different values of the capacitor's ESR (1  $m\Omega$ , 10  $m\Omega$  and 100  $m\Omega$ ). In the three plots, the capacitor values goes from  $C_L$ =100 nF to  $C_L$ =1000  $\mu F$ . Note that when the ESR has a low value, the system tends easily to the instability when the capacitance value is higher than 1  $\mu F$ . On the other hand, when the capacitor's ESR is relatively high the stability of the system is assured, even when output capacitance is high.

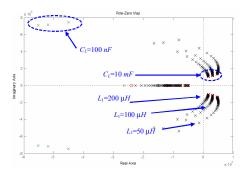

In figure 7 a root locus diagram is shown for three different values of the inductor  $L_1$  (200  $\mu H$ , 100  $\mu H$  and 50  $\mu H$ ). As previous two figures, in the three plots the capacitor values goes from 100 nF to 1000  $\mu F$ . Note that when the load resistor has a high value, the system tends also to the instability when the capacitance value increases.

Figure 6. Root locus diagram for different values of capacitor ESR and output capacitance  $C_L$ .

Figure 7. Root locus diagram for different values of the inductor  $L_1$  and output capacitance  $C_L$ .

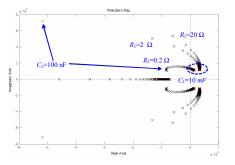

Finally, in figure 8 other root locus diagram is shown for three different values of the inductor  $R_L$  (0.2  $\Omega$ , 2  $\Omega$  and 20  $\Omega$ ). As previous figure, in the three plots the capacitor values goes from 100 nF to 1000  $\mu F$ . Note that when the inductance has a low value, the system tends also easily to the instability when the capacitance value increases.

Varying different circuit parameter, other set of plots can be obtained in the same way that the obtained in previous figures. However, the aforementioned parameters ( $C_L$ , capacitor's ESR,  $L_1$  and load resistance) are the four more important that determine the stability of the linear–assisted converter. Other parameters as, for instance, the inductor's series resistance, the open loop gain of the op–amp, or its output resistance have an effect on the dynamics of the converter but actually do not lead the converter to the instability.

#### V. CONCLUSIONS

In this article, the modeling of a linear—assisted converter has been shown. The converter has a control loop to maintain a constant output voltage that could induce instabilities as a function of the values of the circuit components and the load, in a similar way that others converters. The analysis done reveals that  $C_L$ , capacitor's ESR, inductance  $L_1$  and load resistance are the four more important parameters that determine the stability of the linear—assisted converter. Also, from the proposed study we can improve the stability of the converter and obtain the influence of its different parameters.

#### ACKNOWLEDGMENT

This work has been partially funded by project TEC2004–05608–C02–01 (-02) from the Spanish MCYT and EU FEDER funds.

Figure 8. Root locus diagram for different values of the load resistor  $R_L$  and output capacitance  $C_L$ .

Figure 9. Photography of the linear–assisted converter prototype that has been used to validate the proposed structure.

## REFERENCES

- R. K. Dokania, and G. A. Rincón-Mora. "Cancellation of Load Regulation in Low Drop-Out Regulators". *Electronic Letters*, vol. 38 (nº 22): pp. 1300–1302, 24<sup>th</sup> October, 2002.

- [2] V. Grupta, G. A. Rincón-Mora, and P. Raha. "Analysis and Design of Monolithic, High PSR, Linear Regulator for SoC Applications". Proceedings of the IEEE International SoC Conference: pp. 311–315, 2004.

- [3] R. W. Erickson and D. Maksimovic. "Fundamentals of Power Electronics". 2<sup>nd</sup> edition, Ed. Kluwer Academic Publishers, 2001.

- [4] J. G. Kassakian, M. F. Schlecht, and G. C. Verghese. "Principles of Power Electronics". Ed. Addison-Wesley, 1991.

- [5] G. Villar, E. Alarcón, F. Guinjoan, and A. Poveda. "Efficiency— Oriented Switching Frequency Tuning for a Buck Switching Power Converter". *IEEE International Symposium on Circuits and Systems* (ISCAS'05): 2005.

- [6] X. Zhou, P. L. Wong, P. Xu, F. C. Lee, and A. Q. Huang. "Investigation of Candidate VRM Topologies for Future Microprocessors". *IEEE Transactions on Power Electronics*, vol. 15 (nº 6): pp. 1172–1182, November 2000.

- [7] H. Ertl; J. W. Kolar; F. C. Zach. 'Basic Considerations and Topologies of Switched-Mode Assisted Linear Power Amplifiers'. *IEEE Transactions on Industrial Electronics*, vol. 44 (no 1): pp. 116– 123. February 1997.

- [8] A. Conesa, H. Martínez and J.M. Huerta. "Modeling of Linear & Switching Hybrid DC–DC Converters". 12<sup>th</sup> European Conference on Power Electronics and Applications (EPE 2007). In press. September 2007.