### SAKARYA UNIVERSITY INSTITUTE OF SCIENCE AND TECHNOLOGY

# DESIGN OF DISCRETE TIME CONTROLLERS FOR DC-DC BOOST CONVERTER

# M.Sc. THESIS

## MOHAMMED F. M. ALKRUNZ

| Department<br>Field of Science |   | ELECTRICAL & ELECTRONICS<br>ENGINEERING<br>ELECTRICAL |

|--------------------------------|---|-------------------------------------------------------|

| Supervisor                     | : | Assist. Prof. Dr. Irfan YAZICI                        |

June 2015

### SAKARYA UNIVERSITY INSTITUTE OF SCIENCE AND TECHNOLOGY

# DESIGN OF TISCRETE TIME CONTROLLERS FOR DC-DC BOOST CONVERTER

### **M.Sc. THESIS**

#### MOHAMMED F. M. ALKRUNZ

Department

**Field of Science**

Supervisor

: ELECTRICAL & ELECTRONICS ENGINEERING: ELECTRICAL

: Assist. Prof. Dr. Irfan YAZICI

This thesis has been accepted unanimously by the examination committee on 05.06.2015

Assist. Prof. Dr Irfan VAZICI Head of Jury

Assist. Prof. Dr.

Faruk VALÇIN Jury Member

ssist. Prof. Dr.

Burhanettin DURMUŞ Jury Member

## DECLARATION

I declare that all the data in this thesis was obtained by myself in academic rules, all visual and written information and results were presented in accordance with academic and ethical rules, there is no distortion in the presented data, in case of utilizing other people's works they were refereed properly to scientific norms, the data presented in this thesis has not been used in any other thesis in this university or in any other university.

Mohammed ALKRUNZ

05.06.2015

#### A CKNOWLEDGMENTS

First and foremost, I would like to thank my lovely university and my teaching staff for their support, outstanding guidance and encouragement throughout my study. Also I am heartily thankful to the government of Turkey about their financial support.

I would like to express my graduate and appreciation to my supervisor Dr. Irfan YAZICI for all the help, advice, and guidance he provided throughout the period of this research work. It has been a privilege working with him.

I am extremely grateful to my lovely family, especially my parents and my big brother Rami, for their encouragement, patience, and assistance overall years. I am forever indebted to them, who have always kept me in their prayers.

Finally, I express gratefulness to my friends who provided enthusiasm and empathy to complete my research work successfully. Above all I thank Almighty for His Blessings for making this thesis a successful one.

# TABLE OF CONTENTS

| DECLARATION                       | ii    |

|-----------------------------------|-------|

| ACKNOWLEDGEMENTS                  | iii   |

| TABLE OF CONTENTS                 |       |

| LIST OF SYMBOLS AND ABBREVIATIONS | viii  |

| LIST OF FIGURES                   |       |

| LIST OF TABLES                    | xvii  |

| SUMMARY                           | xviii |

| ÖZET                              | xix   |

## CHAPTER 1.

| INTRODUC | CTION                         | 1 |

|----------|-------------------------------|---|

| 1.1.     | Introduction                  | 1 |

| 1.2.     | Problem Statement             | 7 |

| 1.3.     | Research Objectives           | 8 |

| 1.4.     | Overview of the Research Work | 8 |

## CHAPTER 2.

| AN OVERVIEW OF POWER SUPPLIES |                                                  |    |

|-------------------------------|--------------------------------------------------|----|

| 2.1.                          | Classification of Power Supplies                 | 10 |

| 2.2.                          | Voltage Regulator Basic Functions                | 13 |

| 2.3.                          | Power in DC Voltage Regulators                   | 14 |

| 2.4.                          | DC Voltage Gain of DC Voltage Regulators         | 15 |

| 2.5.                          | Static Characteristics of DC Voltage Regulators  | 16 |

| 2.6.                          | Dynamic Characteristics of DC Voltage Regulators | 18 |

| 2.7.                          | Linear Voltage Regulators                        | 22 |

|      | 2.7.1. | Series voltage regulators | 22 |

|------|--------|---------------------------|----|

|      | 2.7.2. | Shunt voltage regulators  | 23 |

| 2.8. | PWM I  | DC-DC Converters          | 26 |

| 2.9. | Power  | and Energy Relationships  | 28 |

## CHAPTER 3.

| BOOST PWM DC-DC CONVERTER |      |          | 30                               |    |

|---------------------------|------|----------|----------------------------------|----|

|                           | 3.1. | Introduc | ction                            | 30 |

|                           | 3.2. | Operatir | ng Principles & Circuit Analysis | 30 |

|                           |      | 3.2.1.   | Assumptions                      | 34 |

|                           |      | 3.2.2.   | Time interval $0 < t < dT_s$     | 34 |

|                           |      | 3.2.3.   | Time interval $dT_s < t < T_s$   | 35 |

|                           |      | 3.2.4.   | DC voltage gain for CCM          | 37 |

|                           |      | 3.2.5.   | Inductor design & selection      | 38 |

|                           |      | 3.2.6.   | Capacitor design & selection     | 39 |

|                           |      | 3.2.7.   | Power switch selection           | 40 |

|                           |      | 3.2.8.   | Power diode selection            | 42 |

|                           |      | 3.2.9.   | Ripple voltage for CCM           | 43 |

|                           |      | 3.2.10.  | Power loss & efficiency for CCM  | 44 |

#### CHAPTER 4.

| MODELING OF BOOST CONVERTER |      |         | 47          |                                      |    |

|-----------------------------|------|---------|-------------|--------------------------------------|----|

|                             | 4.1. | Introdu | ction       |                                      | 47 |

|                             | 4.2. | State S | pace Mode   | ling of Boost Converter              | 47 |

|                             |      | 4.2.1.  | ON-State    | interval                             | 48 |

|                             |      | 4.2.2.  | OFF-State   | e interval                           | 49 |

|                             | 4.3. | State S | pace Avera  | ging Method                          | 50 |

|                             |      | 4.3.1.  | Average l   | arge signal model of boost converter | 51 |

|                             |      | 4.3.2.  | Steady sta  | ate model of boost converter         | 53 |

|                             |      |         | 4.3.2.1.    | Output DC value derivation           | 54 |

|                             |      | 4.3.3.  | Small sig   | nal model of boost converter         | 55 |

|                             | 4.4. | Transfe | er Function | Derivation from State Space          | 58 |

|                             |      |         |             |                                      |    |

### CHAPTER 5.

| CONTROL SYSTEMS |                                              |    |  |

|-----------------|----------------------------------------------|----|--|

| 5.1.            | 5.1. Introduction                            |    |  |

| 5.2.            | Control System Definition                    | 61 |  |

| 5.3.            | Closed-loop & Open-loop Control System       | 64 |  |

| 5.4.            | Advantages of Control Systems                | 66 |  |

| 5.5.            | 5.5. Control Systems Design & Compensation   |    |  |

|                 | 5.5.1. Performance specifications            | 66 |  |

|                 | 5.5.2. System compensation                   | 68 |  |

|                 | 5.5.3. Design procedures                     | 68 |  |

| 5.6.            | Computer Controlled Systems                  | 69 |  |

| 5.7.            | Digital Controller Design                    | 72 |  |

| 5.8.            | Stability and Transient Response in z-domain | 75 |  |

| 5.9.            | Discrete Root Locus                          | 76 |  |

#### CHAPTER 6.

| DESIG | DESIGN VIA ROOT LOCUS |                                                     |    |

|-------|-----------------------|-----------------------------------------------------|----|

| (     | 6.1.                  | Introduction                                        | 78 |

| (     | 6.2.                  | Improving Transient Response                        | 78 |

| (     | 6.3.                  | Improving Steady State Error                        | 80 |

| (     | 6.4.                  | Controller Design via Root Locus                    | 80 |

|       |                       | 6.4.1. Boost converter under continuous time domain | 81 |

|       |                       | 6.4.2. Boost converter under discrete time domain   | 87 |

| (     | 6.5.                  | Result and Discussion                               | 92 |

#### CHAPTER 7.

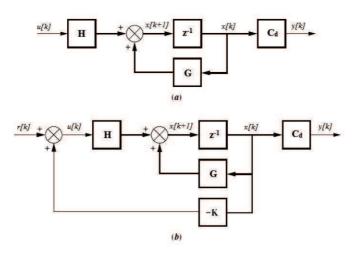

| DESI | GN VI | A STATE SPACE                                    | 96 |

|------|-------|--------------------------------------------------|----|

|      | 7.1.  | Introduction                                     | 96 |

|      | 7.2.  | Stability                                        | 97 |

|      | 7.3.  | Controllability & Obervability                   | 97 |

|      | 7.4.  | Full State Feedback Control                      | 99 |

|      | 7.5.  | Controller Design using Pole Placement Technique | 99 |

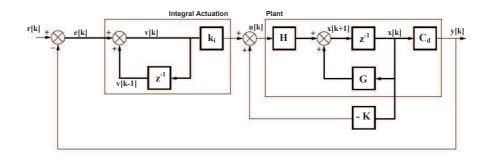

|      | 7.5.1.  | Digital controller design for boost converter | 103 |

|------|---------|-----------------------------------------------|-----|

| 7.6. | Contro  | ller Design using LQR Technique               | 107 |

|      | 7.6.1.  | Controller design for boost converter         | 111 |

| 7.7. | Results | s and Discussion                              | 114 |

|      | 7.7.1.  | Controller using pole placement               | 115 |

|      | 7.7.2.  | Controller using LQR                          | 117 |

### CHAPTER 8.

| CONCLUSIONS AND FUTURE WORK |              | 120 |

|-----------------------------|--------------|-----|

| 8.1.                        | Conclusions  | 120 |

| 8.2.                        | Future works | 121 |

|                             |              |     |

| REFERENC                    | CES          | 123 |

| ANNEX                       |              |     |

| RESUME .                    |              | 134 |

# LIST OF SYMBOLS AND ABBREVIATIONS

| v              | : Actuating Error Vector                 |       |

|----------------|------------------------------------------|-------|

| ARE            | : Algebraic Riccati Equation             |       |

| AC             | : Alternative Current                    |       |

| $T_A$          | : Ambient Temperature                    |       |

| ADC            | : Analog to Digital Converter            |       |

| BJT            | : Bipolar Junction Transistor            |       |

| С              | : Capacitor                              |       |

| I <sub>C</sub> | : Capacitor Current                      |       |

| r <sub>C</sub> | : Capacitor Equivalent Series Resistance |       |

| $P_{C(loss)}$  | : Capacitor Power Loss                   |       |

| V <sub>C</sub> | : Capacitor Voltage                      |       |

| $\Delta Q$     | : Change in Capacitor Charge             |       |

| $\Delta P_D$   | : Change in Power Dissipation            |       |

| r              | : Command Input Vector                   |       |

| CMOS           | : Complementary Metal-Oxide Semicondu    | ictor |

| ССМ            | : Continuous Conduction Mode             |       |

| $C_M$          | : Controllability Matrix                 |       |

| i(t)           | : Current                                |       |

| ζ              | : Damping Ratio                          |       |

| $R_{in(DC)}$   | : DC Input Resistance                    |       |

| K <sub>d</sub> | : Derivative Gain                        |       |

| DAC            | : Digital to Analog Converter            |       |

| D              | : Diode                                  |       |

| $I_D$          | : Diode Current                          |       |

| $R_F$          | : Diode Forward Resistance               |       |

|                |                                          |       |

| $V_{F(diode)}$  | : | Diode Forward Voltage                      |

|-----------------|---|--------------------------------------------|

| $V_F$           | : | Diode Forward Voltage                      |

| $P_{R_F(loss)}$ | : | Diode Power Loss due to $R_F$              |

| $P_{V_F(loss)}$ | : | Diode Power Loss due to $V_F$              |

| $P_{D(loss)}$   | : | Diode Total Power Loss                     |

| $V_D$           | : | Diode Voltage                              |

| DC              | : | Direct Current                             |

| DCM             | : | Discontinuous Conduction Mode              |

| $V_{DO}$        | : | Drop-Out Voltage                           |

| η               | : | Efficiency                                 |

| W               | : | Energy Dissipation                         |

| ESR             | : | Equivalent Series Resistance               |

| е               | : | Error Signal                               |

| $V_{o(FL)}$     | : | Full-load Output Voltage                   |

| K <sub>e</sub>  | : | Gain Matrix                                |

| GTO             | : | Gate Turn Off Thyristors                   |

| L               | : | Inductor                                   |

| $I_L$           | : | Inductor Current                           |

| $r_L$           | : | Inductor Equivalent Series Resistance      |

| $P_{L(loss)}$   | : | Inductor Power Loss                        |

| $V_L$           | : | Inductor Voltage                           |

| x <sub>o</sub>  | : | Initial State                              |

| I <sub>in</sub> | : | Input Current                              |

| u               | : | Input or Control Vector                    |

| P <sub>in</sub> | : | Input Power                                |

| V <sub>in</sub> | : | Input Voltage                              |

| $V_g$           | : | Input Voltage                              |

| $W_C(t)$        | : | Instantaneous Energy Stored in a capacitor |

| $W_L(t)$        | : | Instantaneous Energy Stored in an inductor |

| p(t)            | : | Instantaneous Power                        |

| IGBT            | : | Insulated-Gate Bipolar Transistors         |

| K <sub>i</sub>  | : | Integral Gain                              |

|                 |   |                                            |

| LHP               | : | Left Half Plane                                   |

|-------------------|---|---------------------------------------------------|

| LQR               | : | Linear Quadratic Optimal Regulator                |

| LTI               | : | Linear Time Invariant System                      |

| $I_R$             | : | Load Current                                      |

| $R_L$             | : | Load Resistor                                     |

| R                 | : | Load Resistor                                     |

| LDO               | : | Low Drop-Out Voltage Regulator                    |

| I <sub>Lmax</sub> | : | Maximum Inductor Current                          |

| I <sub>omax</sub> | : | Maximum Output Current                            |

| MOSFET            | : | Metal Oxide Semiconductor Field Effect Transistor |

| ms                | : | millisecond                                       |

| C <sub>min</sub>  | : | Minimum Capacitor Value                           |

| I <sub>Lmin</sub> | : | Minimum Inductor Current                          |

| $V_{in(\min)}$    | : | Minimum Input Voltage                             |

| I <sub>omin</sub> | : | Minimum Load Current                              |

| MCT               | : | MOS-Controlled Thyristors                         |

| $P_{DS(loss)}$    | : | MOSFET Conduction Loss                            |

| $r_{DS}$          | : | MOSFET On-Resistance                              |

| Co                | : | MOSFET Output Capacitance                         |

| $P_{s(loss)}$     | : | MOSFET Total Power Loss                           |

| MIMO              | : | Multiple Input-Multiple Output Systems            |

| $\omega_n$        | : | Natural Frequency                                 |

| $V_{o(NL)}$       | : | No-load Output Voltage                            |

| V <sub>onom</sub> | : | Nominal Output Voltage                            |

| n                 | : | Number of State Variables                         |

| $O_M$             | : | Observability Matrix                              |

| t <sub>off</sub>  | : | Off-Time Interval                                 |

| t <sub>on</sub>   | : | On-Time Interval                                  |

| Io                | : | Output Current                                    |

| $P_o$             | : | Output Power                                      |

| $V_r$             | : | Output Ripple Voltage                             |

| у                 | : | Output Vector                                     |

| $V_o$                                                                    | : | Output Voltage                                    |

|--------------------------------------------------------------------------|---|---------------------------------------------------|

| $V_{o(minL)}$                                                            | : | Output Voltage at the Minimum Load Current        |

| $P_{T(loss)}$                                                            | : | Overall Power Loss of the Boost Converter         |

| $V_{pk}$                                                                 | : | Peak Value                                        |

| %OS                                                                      | : | Percentage Overshoot                              |

| J                                                                        | : | Performance Index or Cost Function                |

| Q, R                                                                     | : | Positive Definite Symmetric Constant Matrices     |

| pnp                                                                      | : | Positive-Negative-Positive Transistor             |

| PBJT                                                                     | : | Power Bipolar Junction Transistor                 |

| P <sub>loss</sub>                                                        | : | Power Loss                                        |

| $P_{R_s}$                                                                | : | Power Loss in the Shunt Resistor                  |

| $P_{TS}$                                                                 | : | Power Loss in the shunt-transistor                |

| PSRR                                                                     | : | Power Supply Rejection Ratio                      |

| $K_p$                                                                    | : | Proportional Gain                                 |

| PID                                                                      | : | Proportional Integral Derivative                  |

| $V_{GS}$                                                                 | : | Pule Train Signal                                 |

| PWM                                                                      | : | Pulse Width Modulation                            |

| V <sub>oref</sub>                                                        | : | Reference Output Voltage                          |

| RHP                                                                      | : | Right Half Plane                                  |

| rms                                                                      | : | Root Mean Square                                  |

| Т                                                                        | : | Sampling Time                                     |

| S                                                                        | : | Second                                            |

| $t_s$                                                                    | : | Settling Time                                     |

| $R_s$                                                                    | : | Shunt Resistor                                    |

| SCR                                                                      | : | Silicon Controlled Rectifier                      |

| ^                                                                        | : | Small Variation                                   |

| Р                                                                        | : | Solution of Algebraic Riccati Equation            |

| $A_{Off}, B_{Off},$<br>$C_{Off}, D_{Off}$                                | : | State Space Matrices During Off-State Interval    |

| A <sub>ON</sub> , B <sub>ON</sub> ,<br>C <sub>ON</sub> , D <sub>ON</sub> | : | State Space Matrices During On-State Interval     |

| A, B, C, D                                                               | : | State Space Matrices under Continuous Time Domain |

| $A_d, B_d, C_d, D_d$ | : | State Space Matrices under Discrete Time Domain           |

|----------------------|---|-----------------------------------------------------------|

| x                    | : | State Vector                                              |

| SITH                 | : | Static Induction Thyristors                               |

| SIT                  | : | Static Induction Thyristors                               |

| S                    | : | Switch                                                    |

| Is                   | : | Switch Current                                            |

| $T_s$                | : | Switch Cycle Period                                       |

| SMPS                 | : | Switch Mode Power Supplies                                |

| $f_s$                | : | Switching Frequency                                       |

| $P_{sw(loss)}$       | : | Switching Loss                                            |

| I <sub>AV</sub>      | : | The Average Value of Current                              |

| $V_{AV}$             | : | The Average Value of Voltage                              |

| G <sub>IDC</sub>     | : | The Current DC Gain                                       |

| d                    | : | The Duty Cycle                                            |

| i <sub>Cmax</sub>    | : | The Root Mean Square value of Capacitor Maximum Current   |

| i <sub>Cmin</sub>    | : | The Root Mean Square value of Capacitor Minimum Current   |

| I <sub>rms</sub>     | : | The Root Mean Square value of Current                     |

| $I_{D(rms)}$         | : | The Root Mean Square value of diode Current               |

| I <sub>s(rms)</sub>  | : | The Root Mean Square value of switch Current              |

| V <sub>rms</sub>     | : | The Root Mean Square value of Voltage                     |

| $V_s$                | : | The Switch Drop Voltage                                   |

| $G_{VDC}$            | : | The Voltage DC Gain                                       |

| I <sub>C</sub>       | : | Transistor's Collector Current                            |

| V <sub>CE</sub>      | : | Transistor's Collector to Emitter Voltage                 |

| TTL                  | : | Transistor-Transistor Logic                               |

| $R_T$                | : | Variable Resistor                                         |

| v(t)                 | : | Voltage                                                   |

| V <sub>rc</sub>      | : | Voltage across the Capacitor Equivalent Series Resistance |

| $V_{R_s}$            | : | Voltage across the Shunt Resistor                         |

| ZOH                  | : | Zero Order Hold                                           |

|                      |   |                                                           |

# LIST OF FIGURES

| Figure 2.1.  | Classification of power supply technologies                      | 10 |

|--------------|------------------------------------------------------------------|----|

| Figure 2.2.  | Block diagrams of AC-DC power supplies. (a) With a linear        |    |

|              | regulator. (b) With a switching-mode voltage regulator           | 11 |

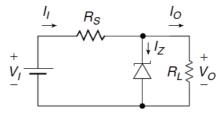

| Figure 2.3.  | Zener diode voltage regulator                                    | 13 |

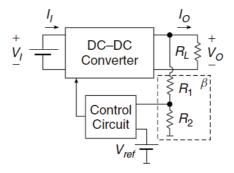

| Figure 2.4.  | Voltage regulator with negative feedback                         | 13 |

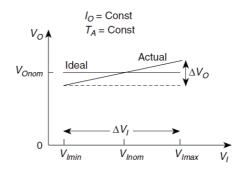

| Figure 2.5.  | Output voltage versus input voltage for voltage regulator        | 16 |

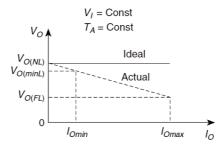

| Figure 2.6.  | Output voltage versus output current for voltage regulator       | 17 |

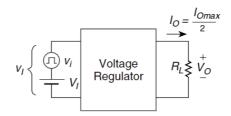

| Figure 2.7.  | Circuit for testing the line transient response of voltage       |    |

|              | regulators                                                       | 19 |

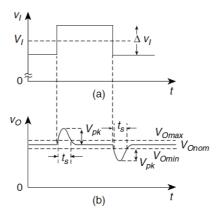

| Figure 2.8.  | Waveforms illustrating line transient response of voltage        |    |

|              | regulators (a) Waveform of input voltage. (b) Wave form of the   |    |

|              | output voltage                                                   | 20 |

| Figure 2.9.  | Circuit for testing the load transient response using an active  |    |

|              | current sink                                                     | 20 |

| Figure 2.10. | Circuit for testing the load transient response using a switched |    |

|              | load resistance                                                  | 20 |

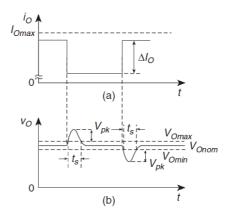

| Figure 2.11. | Waveforms illustrating load transient response of voltage        |    |

|              | regulators. (a) Waveform of load current. (b) Wave form of the   |    |

|              | output voltage                                                   | 21 |

| Figure 2.12. | Series Voltage Regulator                                         | 23 |

| Figure 2.13. | Shunt Voltage Regulator                                          | 24 |

| Figure 2.14. | The switching converter, a basic power processing block with a   |    |

|              | control circuit                                                  | 26 |

| Figure 2.15. | Single ended PWM DC-DC non-isolated and isolated converter.      | 27 |

| Figure 2.16. | Multiple-switch isolated PWM DC-DC converters                    | 28 |

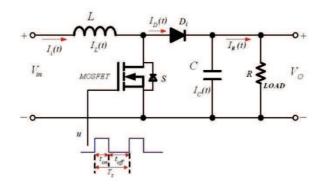

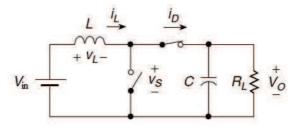

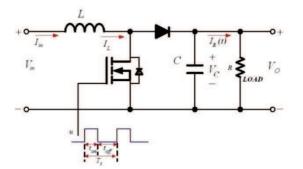

| Figure 3.1.  | Basic circuit of Boost Converter                             | 3 |

|--------------|--------------------------------------------------------------|---|

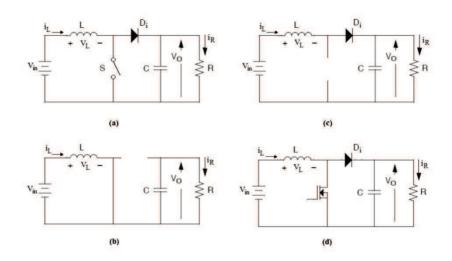

| Figure 3.2.  | Basic Boost Converter circuit topology in CCM                | 3 |

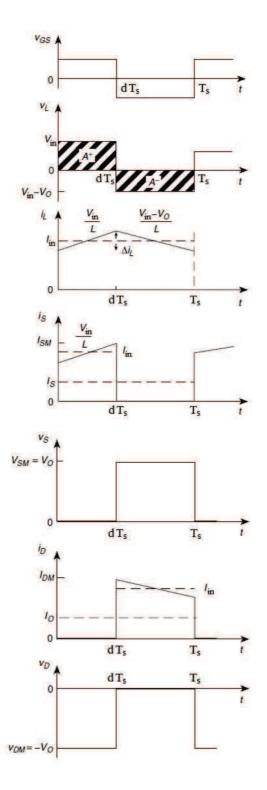

| Figure 3.3.  | Idealized current and voltage waveforms in the PWM Boost     |   |

|              | Converter for CCM                                            | 3 |

| Figure 3.4   | Equivalent circuit when the switch is ON and diode is off    | 3 |

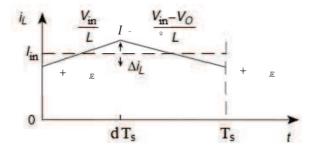

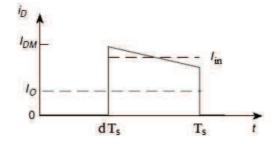

| Figure 3.5.  | Inductor current waveform during one switching cycle for CCM | 3 |

| Figure 3.6.  | Equivalent circuit when the switch is Off and diode is ON    | 3 |

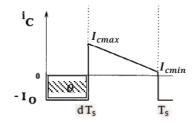

| Figure 3.7.  | Capacitor current waveform during one switching cycle        | 3 |

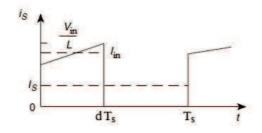

| Figure 3.8.  | Power switch current waveform during one switching cycle     | 4 |

| Figure 3.9.  | Power diode current waveform during one switching cycle      | 4 |

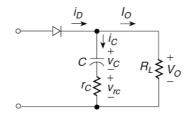

| Figure 3.10. | Equivalent circuit of the output part of the Boost Converter | 4 |

| Figure 3.11. | Waveforms illustrating the ripple voltage in the PWM Boost   |   |

|              | Converter                                                    | 4 |

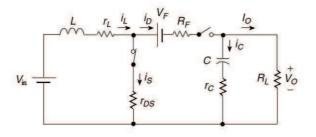

| Figure 3.12. | Equivalent circuit of the Boost Converter with parasitic     |   |

|              | resistances                                                  | 4 |

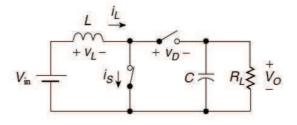

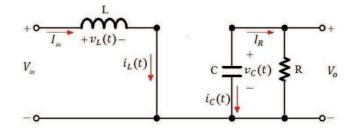

| Figure 4.1.  | Basic circuit of Boost Converter                             | Z |

| Figure 4.2.  | Equivalent circuit of Boost Converter during the ON-State    |   |

|              | interval                                                     | 4 |

| Figure 4.3.  | Equivalent circuit of Boost Converter during the OFF-State   |   |

|              | interval                                                     | 4 |

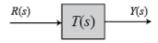

| Figure 4.4.  | Block diagram of a transfer function                         | 5 |

| Figure 5.1.  | Simplified Description of Control System                     | 6 |

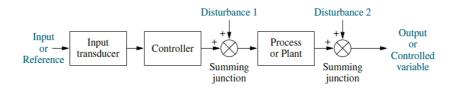

| Figure 5.2.  | Block diagram of open loop Control System                    | e |

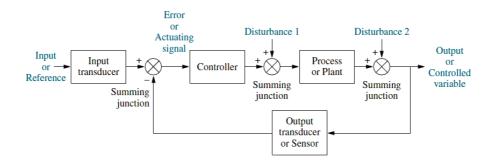

| Figure 5.3.  | Block diagram of closed loop Control System                  | 6 |

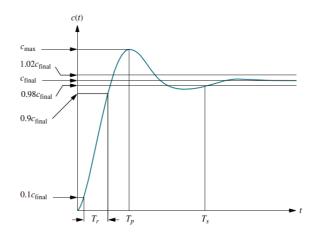

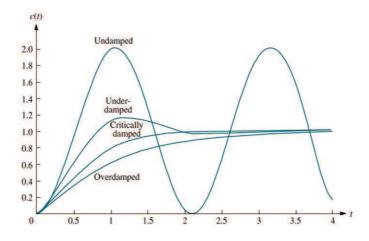

| Figure 5.4.  | Second order under-damped response specification             | 6 |

| Figure 5.5.  | Step response for second order system damping cases          | 6 |

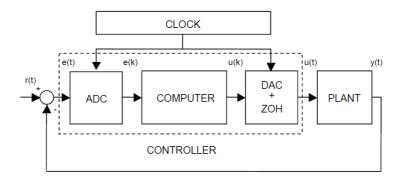

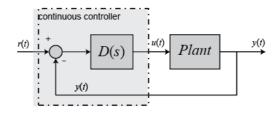

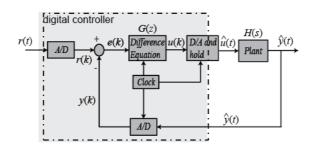

| Figure 5.6.  | Digital realization of an analog type controller             | 7 |

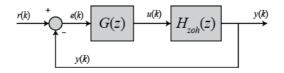

| Figure 5.7.  | Digital Control System                                       | 7 |

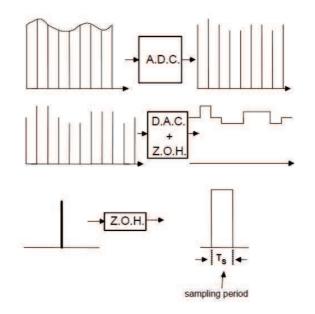

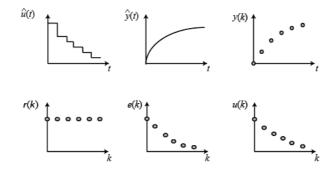

| Figure 5.8.  | Operation of ADC, DAC and ZOH                                | 7 |

| Figure 5.9.  | A typical Continuous Feedback System                         | 7 |

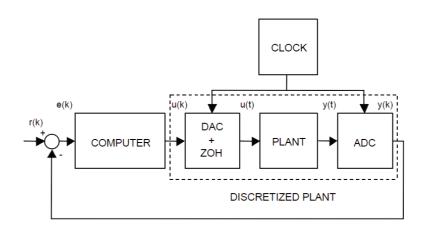

| Figure 5.10. | A typical Discrete Feedback System                           | 7 |

| Figure 5.11. | Different types of signals in a digital schematic            | - |

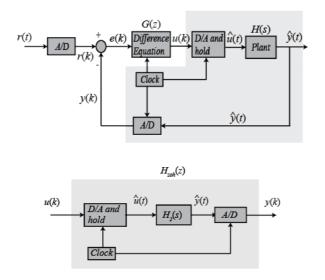

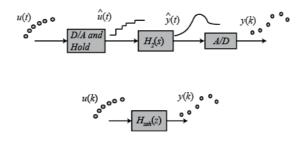

| Figure 5.12. | Zero-Hold equivalence for the system plant                   | 7 |

| Figure 5.13. | Zero-Hold Order principle                                        | 74 |

|--------------|------------------------------------------------------------------|----|

| Figure 5.14. | Full discrete feedback system                                    | 74 |

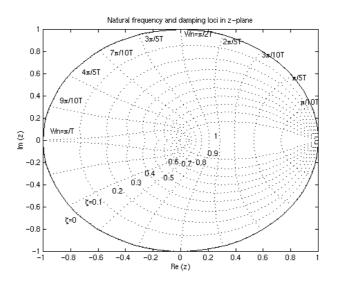

| Figure 5.15. | Natural frequency and damping ratio in z-plane                   | 75 |

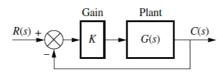

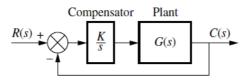

| Figure 6.1.  | Close loop system with K controller                              | 78 |

| Figure 6.2.  | (a) Root locus sample plot. (b) Transient responses from poles   |    |

|              | A and B                                                          | 79 |

| Figure 6.3.  | Block diagram for the closed loop of the Boost Converter         |    |

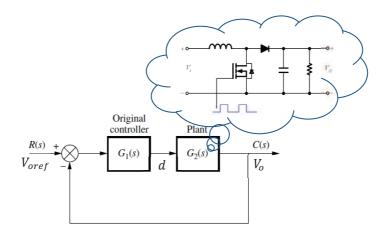

|              | system                                                           | 81 |

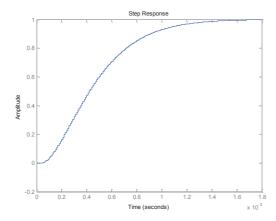

| Figure 6.4.  | Open loop step response of the system in continuous time         |    |

|              | domain                                                           | 83 |

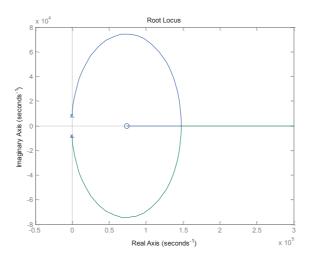

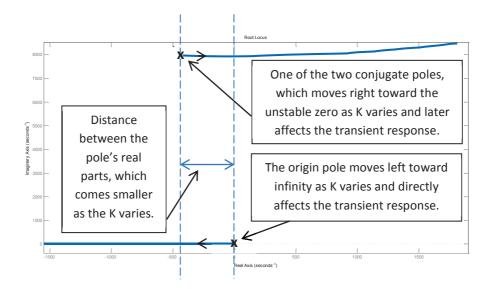

| Figure 6.5.  | Root locus plot for the Boost Converter system in s-domain       | 84 |

| Figure 6.6.  | Block diagram of the system with integral compensator            | 85 |

| Figure 6.7.  | Root locus plot for the compensated Boost Converter system in    |    |

|              | s-domain                                                         | 85 |

| Figure 6.8.  | Root locus plot for the compensated Boost Converter system       |    |

|              | with a zoom to the open loop poles                               | 86 |

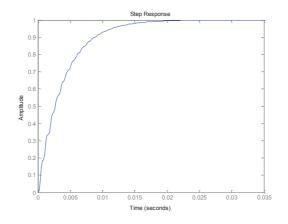

| Figure 6.9.  | Step response for the Boost Converter system with integral       |    |

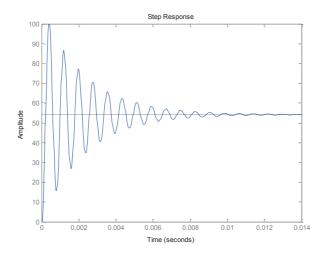

|              | controller in continuous time domain                             | 87 |

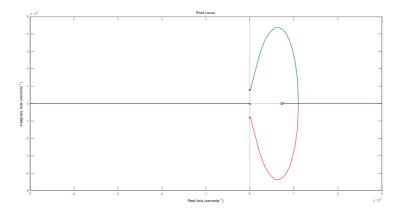

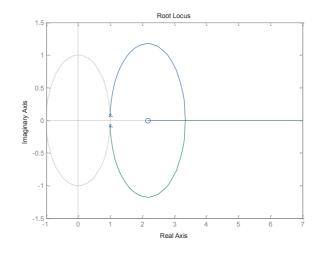

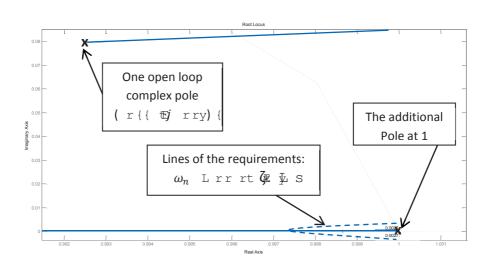

| Figure 6.10. | Root locus plot for the Boost Converter system in z-domain       | 88 |

| Figure 6.11. | Root locus plot for the compensated Boost Converter system in    |    |

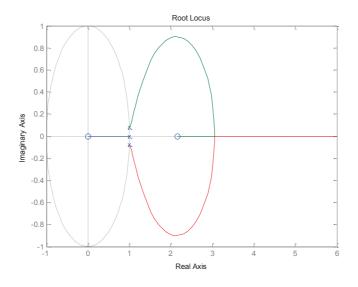

|              | z-domain                                                         | 89 |

| Figure 6.12. | Root locus plot for the compensated Boost Converter system       |    |

|              | with a zoom to the lines of damping ratio and natural frequency. | 90 |

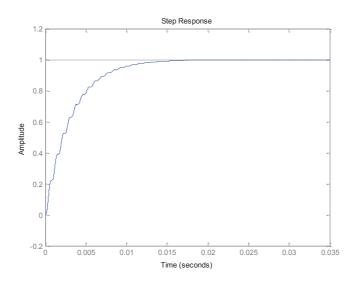

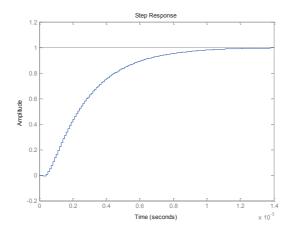

| Figure 6.13. | Step response for the Boost Converter system with integral       |    |

|              | controller in discrete time domain                               | 91 |

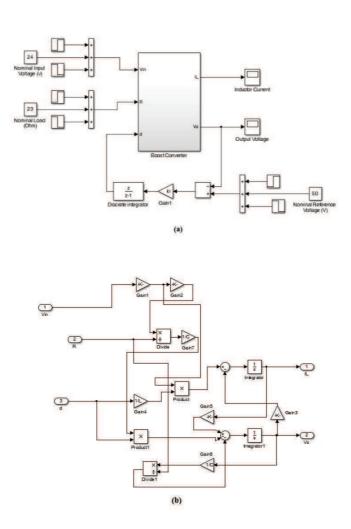

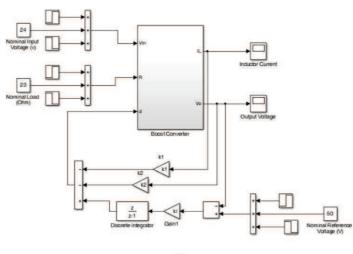

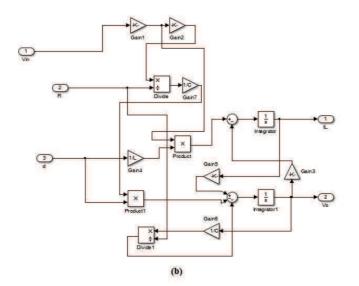

| Figure 6.14. | (a) Simulink Model of the I-controlled Boost Converter. (b) The  |    |

|              | constructed Boost Converter block in Simulink Model              | 92 |

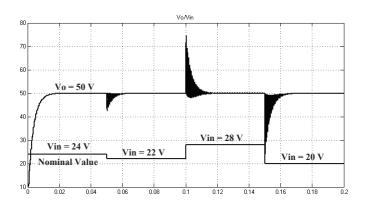

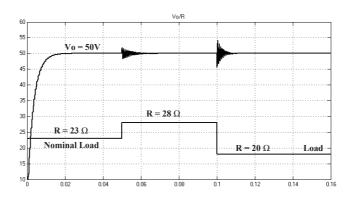

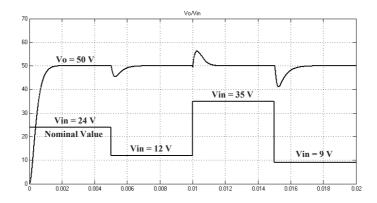

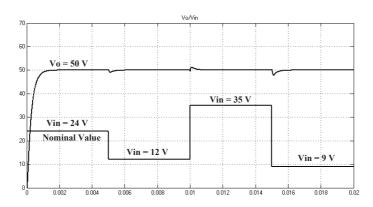

| Figure 6.15. | Simulation results for I-Controlled Boost Converter's output     |    |

|              | response under input voltage variations                          | 93 |

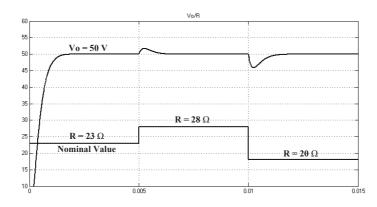

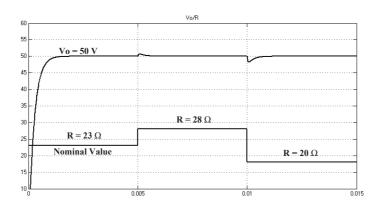

| Figure 6.16. | Simulation results for I-Controlled Boost Converter's output     |    |

|              | response under load variations                                   | 94 |

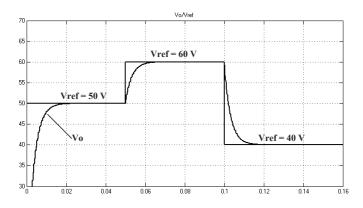

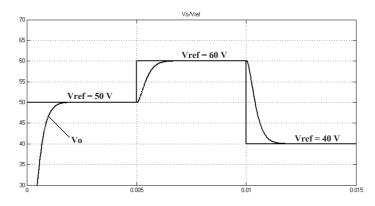

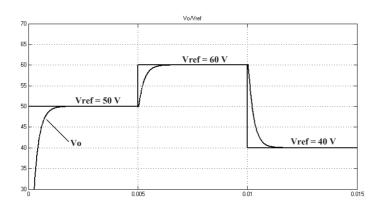

| Figure 6.17. | Simulation results for I-Controlled Boost Converter's output     |    |

|              | response under reference voltage variations                      | 94 |

| Figure 7.1.  | State space of a plant, (b) Plant with full-state feedback         | 99  |

|--------------|--------------------------------------------------------------------|-----|

| Figure 7.2.  | Basic State-feedback with integral actuation                       | 101 |

| Figure 7.3.  | Step response for the boost converter system with pole             |     |

|              | placement method                                                   | 106 |

| Figure 7.4.  | Step response for the boost converter system with LQR method.      | 112 |

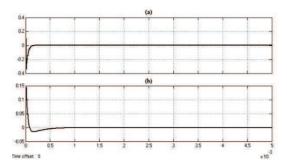

| Figure 7.5.  | Estimations of the system's state variables: (a) State variable 1. |     |

|              | (b) State variable 2                                               | 113 |

| Figure 7.6.  | (a) Simulink Model of the state feedback controlled Boost          |     |

|              | Converter. (b) The constructed Boost Converter block in            |     |

|              | Simulink Model                                                     | 114 |

| Figure 7.7.  | Simulation results for the Boost Converter with pole placement     |     |

|              | method under input voltage variations                              | 115 |

| Figure 7.8.  | Simulation results for the Boost Converter with pole placement     |     |

|              | method under load variations                                       | 116 |

| Figure 7.9.  | Simulation results for the Boost Converter with pole placement     |     |

|              | method under reference voltage variations                          | 116 |

| Figure 7.10. | Simulation results for the Boost Converter with LQR method         |     |

|              | under input voltage variations                                     | 118 |

| Figure 7.11. | Simulation results for the Boost Converter with LQR method         |     |

|              | under load variations                                              | 118 |

| Figure 7.12. | Simulation results for the Boost Converter with LQR method         |     |

|              | under reference voltage variations                                 | 119 |

# LIST OF TABLES

| Table 6.1. | Design values of the boost converter                               | 82  |

|------------|--------------------------------------------------------------------|-----|

| Table 6.2. | Performance parameters of boost converter with integral controller |     |

|            | in discrete time domain                                            | 93  |

| Table 7.1. | Design values of the boost converter                               | 104 |

| Table 7.2. | Performance parameters of boost converter with pole placement      |     |

|            | method                                                             | 115 |

| Table 7.3. | Performance parameters of boost converter with LQR controller      | 117 |

# SUMMARY

Keywords: DC-DC Boost Converter, Small Signal Model, Pole Placement, LQR.

DC-DC converters are extensively used in modern power electronic devices due to their high efficiency, high power density, high power levels, low cost, and small size. In general, they can be step-up, step-down or step-up/down converters and can have multiple output voltages. Boost converter, (also known as a step-up converter) is a type of switched-mode dc-dc converter which produces output voltage that is greater than input voltage.

A small signal modeling based on state space averaging technique for DC-DC Boost converter is carried out. Discrete time controller is designed using two design techniques; frequency domain and state space methods. Root locus technique is used to design an integral controller. A state feedback gain matrix is designed by pole placement technique and Linear Quadratic Optimal Regulator (LQR) methods. The performance of the controlled boost converter are investigated and verified through MATLAB/SIMULINK simulation.

Comparison between the designed controllers related to the design methodology, implementation issues and performance is carried out. It is seen that the designed controllers yielded comparable performances.

In this study, it is aimed to design a controller for DC-DC boost converter to provide satisfactory performance in term of static, dynamic and steady-state characteristics.

# YÜKSELTİCİ TİP DC-DC DÖNÜŞTÜCÜLER İÇİN AYRIK-ZAMAN KONTROLÖR TASARIMI

# ÖZET

Anahtar kelimeler: Yükseltici tip DC-DC dönüştürücüler, Küçük-İşaret Modeli, Kutup Yerleştirme, LQR.

Güç elektroniği, süreç kontrolü ve elektrik enerjisinin elektronik ekipmanlar, makineler ve diğer cihazlar tarafından kullanılmak için uygun bir forma dönüştürülmesi için yarı iletken cihazları içeren yöntemler kullanan teknoloji olarak tanımlanabilir.

Güç elektroniği devrelerinde, diyot gibi bazı elementler herhangi bir kontrol sinyali olmadan güç devresiyle kontrol edilebilir ve SCR (silikon kontrollü doğrultucu) gibi bazı elementlerin AÇIK konuma getirilmesi için bir kontrol sinyaline ihtiyaç duyulurken, bunlar güç devresi ile KAPALI konuma getirilebilir. Aynı zamanda MOSFET gibi bazı elementler hem AÇIK konuma hem de KAPALI konuma getirilmek için bir kontrol sinyaline ihtiyaç duyar.

Bilimsel üretimdeki hızlanmayla ilişkili olarak, kontrol sinyali ve güç cihazları enerji işleme devrelerinin tasarımı için aynı yarı iletken içinde bulunabilir. Böylelikle güç elektroniği mühendisleri ile dijital olarak entegre devre tasarımcıları arasında tasarım metodolojisinde büyük farklılıklar söz konusu olmaz. Bu yüzden güç elektroniği devrelerinin kontrol sorunu için geniş dijital çözümlerin önümüzdeki yıllarda bulunması beklenmektedir.

DC-DC dönüştürücüler güç elektroniği alanı için çok önemli olan DC gerilim kaynağının farklı gerilim seviyelerine dönüştürülmesi açısından endüstriyel uygulamalarda yaygın bir şekilde kullanılır. DC-DC dönüştürücüler yüksek verimlilikleri, yüksek güç yoğunlukları, yüksek güç seviyeleri, düşük maliyetleri ve küçük boyutlarından dolayı dağıtılmış güç tedarik sistemlerinde ve modern güç elektroniği cihazlarında kapsamlı bir şekilde kullanılır. Aynı zamanda Kesintisiz güç kaynaklarında, güç katsayısını geliştirilmesinde, harmonik eliminasyon, yakıt hücresi uygulamalarında ve fotovoltaik dizilerde kapsamlı olarak kullanılır. Bunların aynı zamanda pille çalışan araçlarda, tramvaylarda, cer motoru kontrollerinde ve DC motorları kontrollerinde kullanımlarına da rastlamak mümkündür.

DC-DC Dönüştürücüler yükseltici ve alçaltıcı dönüştürücüleri olarak kullanılabilir ve çoklu çıkış gerilimine sahip olabilir. Alçaltıcı dönüştürücülerinde, çıkış gerilimi giriş geriliminden daha düşükken, yükseltici dönüştürücülerinde çıkış gerilimi giriş geriliminden daha yüksektir. Bazı dönüştürücüler hem yükseltici hem alçaltıcı

dönüştürücüleri olarak ayarlanabilir. Ayrıca DC-DC dönüştürücüleri tek bir çıkışa sahip olabileceği gibi, çoklu çıkışlara da sahip olabilir. Aynı zamanda çıkış gerilimi sabit veya ayarlanabilir olabilir. Bu yüzden DC-DC dönüştürücü teknolojisi birçok farklı türde topoloji kullanır. Elektrik ve elektronik devre ve sistemlerde her durum için ayrı bir uygulama mevcuttur.

DC-DC dönüştürücülerin tasarımı güç elektroniği anahtarlama unsurlarından birinin MOSFET'ler, çift kutup yüzeyli güç transistörleri (BJT) veya IGBT'leri olarak kullanılmasıyla elde edilebilir. Bu anahtarlama unsurları yüksek verim, hızlı dinamik yanıt, sorunsuz kontrol, küçük boyutlar, düşük maliyet ve bakım sağlayabilir. Dönüştürücünün çıkış gerilimi bu güç anahtarlarının Açma-Kapama aralığının ayarlanmasıyla kontrol edilir. Yani bu ana anahtarlama cihazları arzu edilen görev döngüsüyle çalıştırılır.

Görev döngüsü Açık sürenin toplam anahtarlama süresiyle arasındaki orandır. Görev döngü kontrolü konusunda kullanılabilecek iki farklı kontrol stratejisi söz konusudur. Bunlar oran kontrol ve akım sınırlaması kontrolüdür. Süre oranı bir sabit frekans işletimi veya değişken frekans işletimi kullanılarak gerçekleştirilebilir. Aynı zamanda PWM (sinyal genişlik modülasyonu) tekniği olarak da bilinen sabit frekans tekniğinin kullanılması durumunda, AÇIK süre değişiklik gösterir ve anahtarlama frekansı sabit tutulur. Aynı zamanda frekans modülasyon tekniği olarak da bilinen değişken frekans tekniğinin kullanılması durumunda ise, anahtarlama frekansı değişiklik gösterir ve AÇIK frekans sabit tutulur. Frekans modülasyonu, anahtarlama frekansında geniş değişiklikler esnasında doğru kontrol gerektirdiğinden farklı dezavantajlara sahiptir. Bu yüzden tasarımcılar cihazın KAPALI süresinin yüksek bir değere çıkarılması halinde filtre tasarımının gereklilikleri, sinyalde parazit ve kesintili yük akımı gibi sorunlarla karşılaşabilir. Akım sınır kontrolü, yükler gibi enerji depolama unsurları kullanan uygulamalarla kullanılmaktadır. Daha sonra ACMA-KAPAMA aralık süresi anahtarı yük akımının maksimum ve minimum arzu edilen değerlerine ilişkin olarak kontrol edilir.

Bu dönüştürücülerin görev döngülerinin kontrol edilmesi için bir geribesleme devresine ihtiyaç duyulur. Bu konuda yaygın bir kullanıma sahip meşhur geribesleme devresi referans gerilimi ile çıkış gerilimi arasındaki karşılaştırmadır. Görev döngüsü değişikliklerini kontrol etmek ve ihtiyaç duyulan sabit çıkış gerilimini elde etmek için PWM tekniği kullanılarak anahtarlama cihazı için kontrol sinyali geliştirilir ve uygulanır. Hem çıkış gerilimi hem de endüktör akım geribesleme devresinde kullanılabilir. Bu yüzden iki tür geribesleme devresi mevcuttur: gerilim mod kontrolü ve akım mod kontrolü. Gerilim modu yalnızca çıkış gerilimini kullanırken, akım modu geribesleme için hem çıkış gerilimi ve endüktör akımı kullanılır.

Gerilim modu kontrolünde gerçek gerilim ile arzu edilen referans gerilimi karşılaştırmak için yalnızca bir dış döngü kullanılır. Daha sonra kompenzatöre PWM tekniği vasıtasıyla görev döngüsünü kontrol eden kontrol sinyalini gerçekleştirmek ve uygulamaya sokmak üzere hata sinyali verilir. PWM sinyali birçok farklı şekilde yapılabilir. Örneğin tahrik devresi ile mikrokontrolörden elde edilebileceği gibi, anahtarlama cihazının tahriki için gerekli olan sinyalleri üretmek için bir rampa sinyali ile kontrol sinyalini karşılaştıran karşılaştırma teknikleri kullanılarak da elde edilebilir.

Akım modu kontrolünde iki döngüye ihtiyaç duyulur. Temel dış döngüye bir iç döngü eklenir. Sistemin yanıtının hızlandırılması için iç döngü kullanılır. Bu mod Boost ve Boost-Buck Dönüştürücüler gibi karma evreli dizeler kullanıldığında çok etkilidir. Yukarıda gerilim mod kontrolünde bahsedilen dış döngü burada da iç döngüden daha yavaş bir yanıtla kullanılır. Dış döngüden uygulanan sinyal iç döngü için bir giriş akım referansı sinyalidir. Bu referans değeri gerçek endüktör akım değeriyle karşılaştırılır ve bu yaklaşım dış döngüden çok daha hızlı bir şekilde gerçekleştirilir. Bu yüzden dış döngünün amacı hata gerilim sinyaline göre iç döngüye referans değer sağlamaktır. Böylelikle sistemin yanıt performansı çok daha iyi ve daha hızlı olur. Bu gözetilmeksizin, bu yaklaşım kompensatör tasarımı boyunca alt harmonikler dolayısıyla yüksek frekans istikrarsızlığına neden olabilir.

Bu araştırma kapsamında DC-DC Boost Dönüştürücü gerilm mod kontrolü kapsamında ele alınmıştır. Boost Dönüştürücü (kademeli artırma dönüştürücüsü olarak da bilinir) giriş geriliminden daha büyük olan sabit çıkış gerilimi üreten anahtarlı mod DC-DC dönüştürücü türüdür. AA (alternatif akım) eşdeğeri devre modellemesi için devre ortalaması, akım enjeksiyonlu yaklaşım, ortalama anahtarlama modellemesi ve durum uzayı ortalama yöntemi gibi birçok yöntem mevcuttur. Durum uzayı ortalama modellemesi DC-DC Dönüştürücü'nün modellemesinde yaygın olarak kullanılır.

Küçük sinyal modeli gibi ortalama teknikleri DC-DC dönüştürücülerin modellerini türetmek için kapsamlı olarak kullanılmıştır. Bu devre modeli sistemi uyarmak ve uygun kontrolörü tasarlamak için kullanılır. Küçük sinyal modeli dinamik ve sabit durum çalışma noktasındaki değişiklikler hakkında bir fikir verir. Durum değişkenleri ve kontrol değişkenlerinin sabit durum çalışma noktasının çevresindeki aa değişkenlikler/parazitleri olduğu varsayılır. Fakat küçük sinyal modeli çalıştırma noktalarındaki değişikliklere ilişkili olarak değişir.

Araştırmacılar DC-DC dönüştürücü kontrolleri konusunda büyük çabalar göstererek farklı hususlar kapsamında birçok kontrolör önerilmiştir. Elde edilen araştırmadan durum geribesleme kontrolörler tekniklerinin kararlılık ölçütünü elde ettiği ve çalışma noktası koşulları kapsamında iyi bir dinamik performansa ulaştığı anlaşılmıştır. Daha önceki tasarımlarda çeşitli sorunlarla karşılaşılmıştır. Bunun iki ana nedeni vardır: ilk neden konvertörler için iyi modelleme ve etkili analiz gerekliliğinden gelmektedir. İkinci neden de anahtarlama konvertörlerinin devre topolojilerinin geniş bir aralığa sahip olması ve böylece geleneksel yaklaşımlar kullanan bu konvertörlerin kontrolünün karmaşık bir hal alması ve topolojinin bağımlı kalmasıdır. Bu yüzden sorun kontrolü DC-DC konvertörler karma evreli dizge olarak kabul edildiğinde yani Boost Dönüştürücü gibi sağ yarıdaki düzlem üzerinde kararsız bir sınıf olduğunda daha zor bir hal alır.

Genellikle ortalama modeller doğrusal bir kontrolör türetmek için belli bir kullanım noktasında doğrusal bir hale getirilebilir. Lâkin konvertör doğrusalsızlığı dikkate almayan bir tasarım, kötüleşen çıkış sinyaliyle ve büyük pertübasyonların varlığındaki kararsız davranışla sonuçlanabilir. Doğrusalsızlıkların ve parametre karasızlığının dikkate alınması için, konvertör modellerinin ve dayanıklı kontrol yöntemlerinin araştırılması hala aktif olarak devam etmektedir.. Küçük sinyal modelleri Boost Dönüstürücüler için ayrıntılı olarak elde edilmiştir. İki kontrol stratejisi önerilmiştir; Kök-yer eğrisi teknikleri ve durum geribeslemesi yaklaşımı. Görev döngüsü arzu edilen çıkış gerilimlerini elde etmek için kontrol edilir. Konvertörün doğrusallaştırılmış küçük sinyal modelini temel alan kontrol stratejileri çalışma noktaları çevresinde iyi bir performansa sahiptir. Durum uzayı modeli görev döngüsüne bağlıdır. Fakat Boost Dönüştürücü'nün küçük sinyal modeli çalışma noktası değişiklik gösterdikçe değişir. Kutuplar ve sağ yarı düzlem sıfırının yanında frekans yanıtının büyüklüklerinin hepsi görev döngüsüne bağlıdır. Bu vüzden kontrolör tesis dinamik özelliklerindeki değişikliklere uyum sağlayabilmelidir.

Genelde PID kontrolörü geleneksel bir doğrusal kontrol yöntemidir. Bu yüzden, bu çalışma noktasındaki değişikliklere iyi karşılık vermek için doğrusal PID kontrolörü gibi küçük sinyal doğrusallaştırma tekniklerini kullanan kontrolör için zordur.

Bu araştırmada kök-yer eğrisi tekniklerini kullanarak hem sürekli-zaman alanında hem de ayrık-zaman bir şekilde bir İntegral Kontrolör tasarlanmıştır. Ayrıca durum uzayı teknikleri kullanılarak kutup yerleşim ve LQR yöntemlerini temel alan Boost Dönüştürücüsü için bir durum geribeslemesi kontrolörü tasarlanmıştır.

Kök-yer eğrisi teknikleri veya frekans yanıt teknikleri gibi tasarımın frekans bölgesi yöntemleri bütün kapalı döngü kutuplarını yerleştirmek için yeterli parametreye sahip olmadığından daha yüksek düzen sistemlerinin bütün kapalı döngü kutuplarını tasarlayamaz ve belirleyemez. Durum geri beslemesi kontrolörü gibi durum uzayı yöntemleri bu sorunu sisteme diğer ayarlanabilir parametreler getirerek çözmektedir.

Telafi edilen Boost Dönüştürücü giriş geriliminde ve yükteki ani değişiklikler kapsamında kontrol edilmiştir. Dönüştürücü aynı zamanda referans geriliminin izlenmesi kapsamında da kontrol edilmiştir. Ayrıca performans parametresi ve sabit durum parametreleri gibi simülasyon sonuçları da tartışılmış ve çizelge haline getirilmiştir. Çıkış gerilimini yanıtının taslağı çizilmiş ve farklı kontrolör durumları için kıyaslama yapılmıştır.

Tasarlanan kontrolör türleri tasarım metodolojisi, uygulama problemleri ve performans açısından karşılaştırılmıştır. Tasarlanan kontrol yöntemlerinin birbirine yakın bir performansa sahip olduğu gözlemlenmiştir.

Simülasyon ve sonuçlar temel alınarak doğrusal Integral Kontrolör sistem yüksek yük değişikliklerine tabi tutulduğunda kötü performans sergilemiş ve çalışma noktalarındaki değişikliklere kötü yanıt vermiştir. Diğer yandan kutup yerleşimi ve LQR yöntemleri temel alınarak tasarlanan kontrolörler çalışma noktasındaki değişiklikler gözetilmeksizin gayet iyi çıkış voltaj regülasyonu ve mükemmel dinamik performanslar sergilemiştir.

Doğrusal optimal kuadratik regülatör (LQR) yöntemi, bu kontrolörler iyi bir çözüme sahip olduğundan ve mükemmel statik ve dinamik özellikler, kabul edilir bir dayanıklılık, çıkış regülasyonu, parazit reddi ve bütün çalışma noktalarında daha yüksek verim sağladığından bahsi geçen kontrolörlerin en iyi tekniği olarak sonuç vermiştir.

Bu yüzden LQR baskın kapalı döngü kutuplarının arzu edilen bölgelere yakın olarak atandığı ve kalan kutupların da baskın olmayacağı bir şekilde tasarımcının teknik özelliklerine ilişkin optimal yanıtı sağlamaktadır. Bu yöntem uygun performans endeksini seçerek tesis parametre değişikliklerine duyarsızlığı temin eder. Başka bir deyişle, kontrol sisteminin durumları veya çıktıları kontrol çabasının kabul edilebilir bir tüketimini kullanarak bir referans durumundan kabul edilebilir bir sapma içerisinde tutulur. Ayrıca sistem düzeninin bağımsızlığıyla uygulanabilir ve sistemin küçük sinyal modelinin matrislerinden kolaylıkla hesaplanabilir.

Bu çalışmada, yükseltici tip DC-DC dönüştürücüler için sürekli-hal ve dinamik karakteristik açısından uygun bir performansa sahip kontrolör tasarımı amaçlanmıştır.

Bu araştırma sekiz bölümden oluşmaktadır: ilk bölümde konuya bir giriş sunulmakta, araştırmanın amacı ve tez organizasyonu verilmektedir. Diğer bölümler de aşağıdaki şekilde düzenlenmiştir:

Bölüm 2'de güç kaynaklarının tanımları ve sınıflandırmaları hakkında kapsamlı bir girişe yer verilmiştir. Doğrusal Gerilim ve anahtarlama regülatörlerinin temel fonksiyonları tartışılmıştır. Anahtarlamalı güç kaynağı (SMPS) topolojilerinin temelleri. Bazı güç, enerji ve DC kazanç ilişkilerinden bahsedilmiştir.

3. Bölümde Boost Dönüştürücü devresinin çalışma ilkeleri anlatılmıştır. Boost Dönüştürücü devresinin sürekli iletim modu (CCM) üzerine analiz yapılmıştır. Boost Dönüştürücünün güç dönüştürme tekniği, gerilimleri, akımları ve güç denklemleri ayrıntılı olarak çıkarılmıştır. Boost Dönüştürücü'nün elektrik seçim mekanizmalarının unsurları anlatılmıştır.

4. Bölüm durum uzayı ortalama tekniği kullanılarak durum uzayıyla Boost Dönüştürücü'nün tasarım ve modellenmesini içerir. Burada büyük sinyal, sabit durum ve küçük sinyal durum uzayı modelleri elde edilir ve sürekli zaman alanı kapsamında gerçekleştirilir.

5. Bölüm'de kontrol sistemi kavramları hakkında genel bakışlar anlatılır. Bazı önemli ve temel terminolojiler hakkındaki tanımlar tartışılır. Açık döngüler ile kapalı döngü sistemleri kavramları ile bunların belli avantaj ve dezavantajları sunulmuştur. Kontrol sistem tasarımından, prosedürlerinden ve telafilerden bahsedilmiştir. Bilgisayarla kontrol edilen sistemler ile dijital kontolör tasarım kavramları da sunulmuştur. Bunlara ek olarak, ayrı kök yer eğrisi ve z alanındaki geçici zaman yanıtı verilmiştir.

6. Bölüm'de hem sürekli zaman alanı hem de ayrık zaman alanı kapsamında kök yer eğrisi teknikleri kullanılarak Boost Dönüştürücü'nün bir İntegral kontrolör ile tasarımı, uygulanması ve hesaplamaları ayrıntılı olarak anlatılmıştır. Simulink/MATLAB kullanılarak yapılan simülasyonlar gerçekleştirilmiştir. Performans parametreleri ve integral kontrolör kullanılarak elde edilen sonuçlar çizelgeler olarak verilmiştir.

7. Bölüm'de tam durum geri besleme kontrolü kavramları ayrıntılı olarak tartışılmıştır. Kutup yerleştirme tekniği ve Doğrusal optimal kuadratik regülatör yöntemleri kullanılarak ayrık-zaman alanı kapsamında (LQR) Boost Dönüştürücü'nün tasarımı, modelleme ve uygulanması gerçekleştirilir. Öncelikle kutup yerleşim yöntemi ile dijital kontrolör tasarımı ayrıntılı olarak tartışılır ve gerçekleştirilir. İkinci olarak LQR yöntemi kullanılan dijital kontrolör tasarımı tartışılır ve kontrolör elde edilir. Bu iki yöntem birbiriyle kıyaslanarak gösterilir. Simulink/MATLAB kullanılarak elde edilen simülasyon sonuçları gösterilir ve her bir kontrolör için aynı zamanda performans parametreleri de çizelgeler halinde verilir.

8. Bölüm'de Sonuçlar verilir ve ardından referanslar gelir.

### **CHAPTER 1. INTRODUCTION**

#### **1.1. Introduction**

Power electronics and control system concepts have a basic relation to each other since the beginning. Switch mode power supplies (SMPS) is a variable structure periodic systems which its mechanism is determined by logic signals. A lot of researches are obtained with the analysis of switching DC-DC converters. Generally, a mathematical representation is considered with the related control circuits [1], [2].

Power electronics can be defined as the technology that use means of power semiconductor devices (operate as switches) for the process control and conversion of electrical energy into a form suitable for utilization by electronic equipment, machines and other devices.

"With the advent of Silicon Controlled Rectifiers (SCRs) in 1950s, the application of Power Electronics spread to various fields of Engineering such as in solid state industrial drives, high frequency converters, inverters, uninterruptible power supplies, Electronic tap changers, lighting control, home appliances and in medical instrumentation. Gradually since 1970, various Power Electronic devices were developed and were available commercially. The typical classification of the devices based on the controllability characteristics are, Uncontrolled turn on and turn off devices (eg. Diode), Controlled turn-on and uncontrolled turn-off (eg. SCR) and Controlled turn on and off characteristics (eg. Power Bipolar Junction Transistor (PBJT)), Metal Oxide Semiconductor Field Effect Transistor (MOSFET), Gate Turn Off thyristors (GTOs), Static Induction Thyristors (SITH), Insulated-Gate Bipolar Transistors (IGBTs), Static Induction Thyristors (SITs) and MOS-Controlled Thyristors (MCTs) "[3]. In the power electronics circuits, some elements like diode can be controlled by power circuit without any control signals, and some elements like SCR needs a control signal to turn ON and can be turned OFF by the power circuit. Also, some elements like MOSFET need a control signal to be turn ON as well as to turn OFF. In addition, some improvements to the current and voltage ratings are continued with the evolution of those power electronics devices [3].

Then, related to the acceleration in the scientific production, the control signal and power devices can be included in the same semiconductor for the design of energy processing circuits. Thus, there is no any distance in the design methodology between the engineers of power electronics and digital integrated circuit designers. Therefore, wide digital solutions to the control problem for power electronic circuits are expected in the next years [1].

Power converters can be classified like: DC-DC Converters, AC-AC Converters, Phased controlled converters (AC-DC Converters), DC-AC converters (Inverters), and AC voltage controllers (regulators). Based on this classification, electric power is transformed from one form to another one in order to increase the efficiency and the production which are needed in several devices and industrial applications [4].

DC-DC converters are widely used in the industrial applications since they convert a DC voltage source to other different voltage levels which is very important in power electronics field. DC-DC converters are extensively used in distributed power supply systems and modern power electronics devices due to their high efficiency, high power density, high power levels, low cost, and small size [5]. They are also used extensively in Uninterruptible power supply, power factor improvement, harmonic elimination, fuel cells applications and in photovoltaic arrays. They are also used in other various applications like battery operated vehicles, trolley cars, traction motor control and DC motors control [3]–[8].

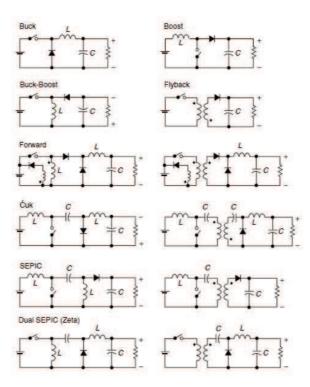

DC-DC Converters (also known as Choppers) can be step-up or step-down converters, and can have multiple output voltages. In case of step-down converters, output voltage is lower than the input voltage, while it is higher than the input

voltage in case of step-up converters. Some converters could set to be step-up and step-down converters. In addition DC-DC converters could have a single output or multiple outputs. Also, the output voltage can be fixed or adjustable. Therefore, a wide variety of topologies is employed by DC-DC converters technology [9]. Every case has its application in electrical and electronic circuits and systems.

DC-DC converters design can be obtained using one of the power electronics switching elements as MOSFETs, power BJTs or IGBTs. These switching elements can provide high efficiency, fast dynamic response, smooth control, small size, low cost and maintenance. The output voltage of the converter is controlled by On-Off interval tuning of these power switches. On other words, these main switching devices are driven with the desired duty cycle. Duty cycle is the ratio between the On-time to the total switching period. Two different control strategies can be used in the subject of duty cycle control; time ratio control and current limit control. Time ratio control can be performed using a constant frequency operation or variable frequency operation. In case of constant frequency which is also known as pulse width modulation (PWM) technique, the On-time varies and the switching frequency is kept constant. While in case of variable frequency which is also known as frequency modulation technique, the switching frequency varies and the On-time is kept constant. Frequency modulation has different disadvantages since it needs accurate control during the wide variations in switching frequency. Therefore, some problems could face the designers such as the needs of filter design, interference with signaling and discontinuous load current if the device's Off-time increased to high value. Current limit control is performed in the case of applications that use energy storage elements as loads. Then, the switch On-Off interval time is controlled related to the maximum and minimum desired values of load current [3], [10].

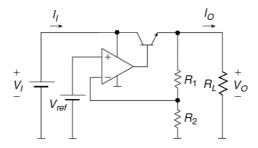

In order to control the duty cycle of these converters, feedback circuit is required. The famous feedback circuit which is widely used in this subject is the comparison between the output voltage with the reference voltage. Control signal is generated and performed to the switching device using PWM technique to control the duty cycle variations and to obtain the required fixed output voltage. Both of the output voltage and the inductor current can be used in the feedback circuit. Therefore, there are two modes of feedback circuits; voltage mode control and current mode control. The voltage mode control uses the output voltage only while the current mode uses both the output voltage and the inductor current for the feedback.

In voltage mode control, just one outer loop is used to compare the actual output voltage with reference desired voltage. Then, error signal is given to the compensator to be performed and execute the control signal which controls the duty cycle via PWM technique. PWM signal can be performed in much ways; for example, it can obtained directly from the microcontroller via a driver circuit or it can obtained using comparison techniques which compare the control signal with a ramp signal to produce the needed pulses to drive the switching device.

In current mode control, two loops are required. One inner loop is added to the basic outer loop. The inner loop is used to speed up the system's response. This mode is very effective in case of non-minimum phase systems like Boost and Boost-Buck Converters [3], [11]. The outer loop which is discussed above in the voltage mode control is used here but with much slower response than the inner loop. The signal which is executed from the outer loop is an input current reference signal for the inner loop. This reference value is compared with the actual inductor current value and this approach must be performed much faster than the outer loop. Therefore, the outer loop purpose is to provide the inner loop with the reference value according to the error voltage signal. And thus, the response performance of the system can be much better and faster. Regardless of this, this approach can face high frequency instability due to sub-harmonics during the compensator design [3].

In this research work, DC-DC Boost Converter under voltage mode control is considered. Boost Converter, (also known as a step-up converter) is a type of switched-mode DC-DC converter which produces a constant output voltage that is greater than input voltage. A number of methods are appeared for ac equivalent circuit modeling such as circuit averaging, current injected approach, averaged switch modeling and state space averaging method [5]. The state space averaged modeling is widely used in DC-DC Converter's modeling [12].

Averaging techniques such as small signal model has been widely used to derive model of DC-DC converters [2], [13], [14]. This circuit model is used to simulate the system and design the suitable controller. Small signal model gives an idea of the dynamics and variations about steady state operating point. It is considered that state variables and control variable have small ac variations/disturbances around the steady state operating point. But, the small signal model changes related to the variations in the operating points [12].

Researchers have delivered great efforts in the subject of DC-DC converters control and many controllers under various considerations were proposed. In the mid-1960, investigations of basic switching converters, modeling, and analysis are commenced. In the mid-1980's, advancement in the closed loop control of switching converters were combined with the regulation and dynamic response improvements [15]. In 1990's until this time, new approaches and control methods are addressed and discussed [3]. Tse et al (2002) have performed analysis of the non-linear phenomena in the power electronics systems. The chaotic behavior of the Boost Converter is discussed. The author paved the way to the power electronic converters to be used in several applications. Gonzalez et al (2005) used passivity based non-linear design to perform an observer controller for the Boost Converter. The obtained output shows undesirable overshoots and undershoots. A new switching cycle compensation algorithm have proposed by Feng et al (2006) to optimize the transient performance of the DC-DC converters under input voltage variations. The controller is implemented used FPGA and sensing resistors to measure the inductor current. The system has an improvement in the dynamic performance. But this type which based on the current measurement is not much effective due to the higher power loss. Bo-Cheng et al (2008) have designed a state feedback controller for the Boost Converter using sampled inductor current. It shows the control ability of chaotic behavior of the Boost Converter and stability criterion is achieved. But, the robustness of the control law was not checked. Chen et al (2008) have identified the stable operating point by making analysis to the Boost Converter. They suggested that the effects of fast and slow scale bifurcations that occur in voltage mode control and current mode control can be eliminated by increasing the feedback gain. Sreekumar and Agarwal (2008) have obtained output voltage regulation for the Boost Converter using new hybrid control algorithm. System was stable under operating conditions, but this control algorithm cannot be applied for higher switching frequency since it causes limitations on driver circuit, device speed, and power loss. On other hands, Carlos et al (2009) have designed a controller using Linear Quadratic Optimal Regulator method. Stability and performance of the converter are achieved. Authors built the controller taking into account more than one plant by using Linear Matrix Inequalities (LMI) approach. Liping Guo, John Y. Hung and R. M. Nelms (2009) have designed a fuzzy controller for the Boost Converter. Experimental results showed fast transient response with stable steady state and voltage regulation under circuit parameter variations. Also, Mariethoz et al (2010) have used state feedback control techniques for the Boost Converter with load estimation based on observer controller. Authors have taken into the account the time response and the capability of disturbance rejection. They used five different methodologies for the controller design. The system response shows performance improvements and disturbance rejection. Mohammed Alia et al (2011) and Mohammed Abuzalata (2012) have used LabVIEW software as a platform to make PID tuning and to generate PWM techniques respectively.

It is understood from the above survey that the state feedback controller techniques have obtained the stability criterion and have achieved a good dynamic performances under operating point conditions. The previous designs suffer from various problems. There are two main reasons: the first reason comes from the requirement of good modeling and effective analysis for the converters. While the second reason is that the circuit topologies of switching converter have a wide range, and thus the control of these converter using conventional approaches become complicated and topology dependent [16]. Therefore, the problem control will be more difficult when the DC-DC converter is considered as non-minimum phase system (has an unstable zero on the right-half-plane) such as the Boost Converter.

Usually, such averaged models are linearized at a certain operation point in order to derive a linear controller. Nevertheless, a design that disregards converter nonlinearities may result in deteriorated output signal or unstable behavior in presence of large perturbations [17]. In order to take into the account nonlinearities

and parameter uncertainty, the study of converter models and robust control methods is still an active area of investigation [18]–[22].

PID controller is a traditional linear control method used in many applications [23]. Linear PID controllers for DC-DC converters are usually designed by frequency domain methods applied to the small signal models of the converters. PID controller response could be poor against changed in the operating points [24]–[26].

Frequency domain methods of design such as root locus techniques or frequency response techniques can't design and specify all closed loop poles of the higher order system since those methods don't have sufficient parameters to place all of the closed loop poles. State space methods such as state feedback control solve this problem by introducing into the system other adjustable parameters [27].

State feedback control and the approach of Linear Quadratic Optimal Regulator (LQR) have a good control solution for the systems with good dynamic response, accepted robustness, output regulation, and disturbances rejection.

#### **1.2. Problem Statement**

Traditionally, small signal linearization techniques have largely been employed for controller design. Many control strategies have been proposed, and duty cycle is controlled to obtain the desired output voltage. Control strategies that are based on the linearized small signal model of the converter have good performance around the operating point as it will discussed in this research. However, a Boost Converter's small signal model changes when the operating point varies. The poles and a right-half-plane zero, as well as the magnitude of the frequency response, are all dependent on the duty cycle. Therefore, it is difficult for the controller which using small signal linearization techniques such as linear PID controller to respect well to changes in operating point, and they exhibit poor performance when the system is subjected of large load variations.

#### **1.3. Research Objectives**

In this research, various methods and control techniques will be applied to the Boost Converter system. It is aimed to check these controllers' effects to the system's performance. Also, it is aimed to select the best controller in which robust stability and performance despite model inaccuracies will be achieved. The designed controller is expected to provide excellent static and dynamic characteristics at all operating points. These objectives are organized as follows:

- 1. To investigate different topologies currently working for power systems.

- 2. To investigate different control techniques and their effects.

- 3. To protect the input source and the load.

- 4. To maintain a stable regulation of the output voltage.

- 5. To maximize the bandwidth of the closed-loop system in order to reject disturbances.

- 6. To satisfy desirable transient characteristics.

- 7. Development of control strategy with fast response in order to attain stable, quality and fault tolerant power system under static and dynamic conditions.

#### 1.4. Overview of the Research Work

This research consists of eight chapters; the first chapter presents an introduction, research objectives and thesis organization, while the other chapters are organized as follows:

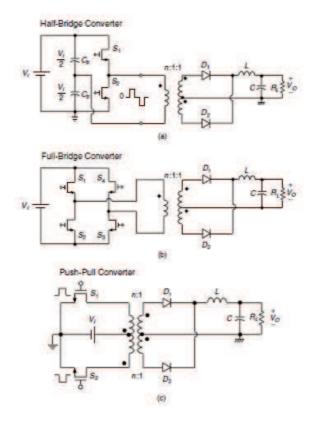

Chapter 2 presents extensive introduction about the definitions and classifications of power supplies. Linear Voltage and switching regulators basic functions have been discussed. The fundamental of switching-mode power supply (SMPS) topologies. Some power, energy and DC gains relations have been covered.

Chapter 3 presents the operating principles of the Boost Converter circuit. Analysis is applied to the Boost Converter's circuit in continuous conduction mode (CCM). Boost Converter's power conversion technique, voltages, currents and power equations are derived in details. The electrical selection mechanisms of Boost Converter's elements have been covered.

Chapter 4 presents the design and modeling of Boost Converter by state space method using state space averaging technique; large signal, steady state and small signal state space models are obtained and satisfied under continuous time domain.

Chapter 5 presents some overviews about control system concepts. Definitions about some important and basic terminologies have been discussed. The concept of the open loop versus closed loop systems, and the major advantages and disadvantages of them have been presented. Control system design; procedures and compensation have been covered. Computer controlled systems and digital controller design concepts are also presented. In addition, discrete root locus, stability and transient time response in z-domain have been covered.

Chapter 6 presents design, implementation and calculations in details of Boost Converter with an Integral controller using root locus techniques under both continuous time domain and discrete time domain. Simulation using Simulink/MATLAB has been carried out. Performance parameters and obtained results using integral controller are tabulated.

Chapter 7 discussed in details the concepts of full state feedback control. Design, modeling, and implementation of Boost Converter with state feedback controller using pole placement technique and Linear Quadratic Optimal Regulator (LQR) methods under discrete time domain are obtained. Firstly, digital controller design with pole placement method is discussed in details and carried out. Secondly, digital controller design with LQR method is discussed and controller has been obtained. The two methods are shown compared against each other. Simulation results using Simulink/MATLAB are shown and the performance parameters are also tabulated for each controller.

Chapter 8 Conclusion are given and references follow this chapter.

#### **CHAPTER 2. AN OVERVIEW OF POWER SUPPLIES**

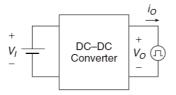

#### 2.1. Classification of Power Supplies

Power supply is a constant voltage source with a maximum current capability, this technology allows us to build and operate systems and electronic circuits. All electronic circuits, both analog and digital, require power supplies. In some cases, electronic systems need more than one dc supply voltage. In our daily life, power supplies are used widely, such as personal computers, communications, instrumentation equipment, medical, and defense electronics. Using a transformer, rectifier and filter, a dc supply voltage can be derived from battery or an ac utility line. This resultant dc supply voltage is not constant and could has ac ripples, *voltage regulator* usually used to attenuate the ac ripples and set the dc voltage more constant, so it will be enough suitable and safe for most applications [9].

Power supplies have two general classes: regulated and unregulated. Despite source line voltage, load and temperature variations, regulated power supplies have fixed output voltage with small change range, 1-2% of the nominal/desired value. Regulated dc power supplies also called *dc voltage regulators*. There are also *dc current regulators*, as battery chargers [9], [10].

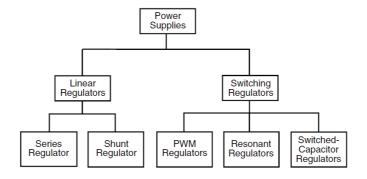

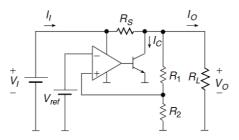

Figure 2.1. Classification of Power Supply Technologies [9]

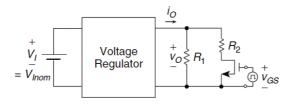

Voltage regulators or power supplies are classified into two popular categories, *linear regulators* and *switching-mode power supplies* as shown in Figure 2.1. Linear regulator has two basic topologies, series and shunt voltage regulator. On the other hand, switching-mode voltage regulators have three categories, pulse width modulator, resonant and switched-capacitor regulators.

Transistors in the linear regulator circuit work in the active region as dependent current sources, but they work as switches in the switching regulator circuit. In the first case, it is expected to have high voltage drops at high currents, waste large amount of power; which leads to have a low efficiency system. Furthermore, linear regulators are large and heavy, but offer low noise scale. On the contrary, switching regulators show less power dissipation, very low voltage drop at high currents and nearly zero current in the case of high voltage drop across them, resulting high efficiency (approximately 80-90%) related to the low conduction losses. Switching losses and switching frequency have proportional relation, so efficiency will be reduced in the high frequencies.

PWM and resonant regulators have small size, light weight and very good conversion efficiency, thus they are used at high power and voltage levels. Switched-Capacitor and linear regulators can be integrated fully and are used in low power and voltage applications.

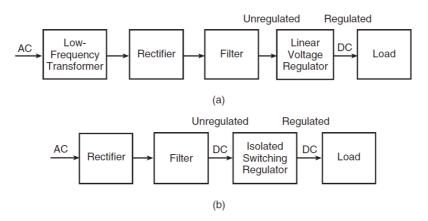

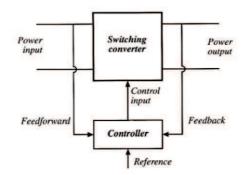

Figure 2.2. Block diagrams of AC-DC power supplies. (a) With a linear regulator. (b) With a switching mode voltage regulator [9]

Two AC-DC power supplies examples are shown in Figure 2.2. The power supply in the Figure 2.2(a) has a linear voltage regulator, while power supply in the Figure 2.2(b) has a switching-mode voltage regulator.

As shown in Figure 2.2(a), diagram contains step-down low-frequency transformer, rectifier, low pass filter, linear voltage regulator and a load. Since, the ac line has a very low frequency (50Hz, 60Hz in Europe and USA respectively), thus the line transformer will be heavy and huge. After filter stage, the output voltage is unregulated which can be varies related to the ac line changes, then a voltage regulator is needed to have a stable and constant dc voltage to the load.

Figure 2.2(b) contains rectifier, low pass filter, switched-mode voltage regulator and a load without using the step-down transformer, the ac voltage is directly rectified from the ac power line. The switching-mode voltage regulator works under high switching frequency, this frequency is much higher than one of ac line power sources, thus the transformer will be small in size and weight, and also the capacitor and inductor values are reduced.

"The switching frequency usually ranges from 25 to 500 kHz. To avoid audio noise, the switching frequency should be above 20 kHz. A PWM switching-mode voltage regulator generates a high-frequency rectangular voltage wave, which is rectified and filtered. The duty cycle (or the pulse width) of the rectangular wave is varied to control the dc output voltage. Therefore, these voltage regulators are called PWM DC–DC converters." [9]