# **Edith Cowan University**

## Research Online

ECU Publications Pre. 2011

2008

# **Double Boundary Trench Isolation Effects on a Stacked Gradient Homojunction Photodiode Array**

Paul V. Jansz Edith Cowan University, pjansz@our.ecu.edu.au

Steven Hinckley Edith Cowan University, s.hinckley@ecu.edu.au

Follow this and additional works at: https://ro.ecu.edu.au/ecuworks

Part of the Engineering Commons

#### 10.1109/COMMAD.2008.4802115

This is an Author's Accepted Manuscript of: Jansz, P. V., & Hinckley, S. (2008). Double Boundary Trench Isolation Effects on a Stacked Gradient Homojunction Photodiode Array. Proceedings of Conference on Optoelectronic and Microelectronic Materials and Devices, 2008. COMMAD 2008. (pp. 156-159). Hilton, Sydney NSW. IEEE Press.

© 2008 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This Conference Proceeding is posted at Research Online.

https://ro.ecu.edu.au/ecuworks/808

# Double Boundary Trench Isolation Effects on a Stacked Gradient Homojunction Photodiode Array

Paul V. Jansz and Steven Hinckley

Physics Research Group, School of Engineering.

Edith Cowan University, Joondalup, Western Australia 6027 Australia.

Email: p.jansz@ecu.edu.au & s.hinckley@ecu.edu.au

Abstract—The effect of the width of inter-pixel double boundary trench isolation on the response resolution of a two dimensional CMOS compatible stacked gradient homojunction photodiode array was simulated. Insulation and P-doped double boundary trench isolation were compared. Both geometries showed improved crosstalk suppression and enhanced sensitivity compared to photodiode geometries previously investigated, combined with a reduction in fabrication complexity for the insulation DBTI configuration.

Keywords- CMOS; crosstalk; double boundary trench isolation; inter-pixel nested ridges; quantum efficiency; SiO<sub>2</sub>; stacked gradient homojunction photodiode.

#### I. INTRODUCTION

To produce high-speed high-resolution CMOS imaging systems, photodiode array crosstalk and maximum Quantum Efficiency (QE) need to be optimized [1]-[3]. Backwall illumination allows the spectral response of individual photodiodes to be tailored to a specific wavelength band because the depth of carrier photogeneration is proportional to the wavelength due to the indirect nature of the silicon absorption coefficient [4].

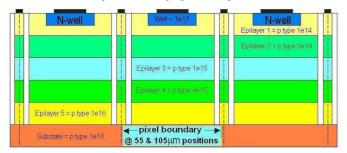

This investigation of the Stacked Gradient homojunction – Double Boundary Trench Isolation (StaG-DBTI) photodiode (PD) geometries add to previous work with the aim of achieving devices that balance the maximization of response resolution with the minimization of device fabrication complexity. This furthers previous research [10] showing that the StaG PD (Fig.1) showed superior QE and reduced crosstalk [11] compared to other photodiode structures [5]-[9].

Previous research with nested inter-pixel ridge StaG PD (StaG-R PD) [12] (Fig. 2) has shown enhanced pixel response resolution beyond that of the StaG PD (Fig. 1). However the complexity of fabricating this geometry (Fig. 2) led first to the single BTI StaG PD geometry [13] (Fig. 3) and then to the present doped Double BTI (DBTI) StaG PD (Fig. 4) and Insulation DBTI StaG PD geometries (Fig. 5).

This present research investigates the effect of the width of each BTI for the doped DBTI StaG PD, on the response resolution of a two dimensional CMOS compatible photodiode array. DBTI and single BTI StaG PD with insulation making up the BTI are also investigated for comparison with the

former geometry. The optical responsivity for both architectures was compared with the StaG PD, with and without inter-pixel nested ridges, and with single inter-pixel BTI. Results were also compared with the conventional single junction photodiode (SJPD), the guard ring electrode SJPD, Guard-BTI SJPD, twin BTI SJPD and the double junction Photodiode (DJPD). Due to the advantages of the backwall illumination [4], comparison was made to frontwall illumination for each photodiode geometry.

#### II. METHOD

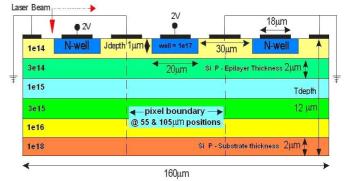

The crosstalk and maximum quantum efficiency of the central pixel of the three pixel array 160  $\mu$ m wide and 12  $\mu$ m deep with various geometries (Fig. 4 & 5) was simulated using SEMICAD DEVICE (v1.2), used to allow comparison with photodiode configurations previous simulated.

The simulated three-pixel array was scanned at 5  $\mu m$  intervals along the frontwall or backwall of the array using a simulated laser beam of 633nm wavelength, 5 $\mu m$  width and 0.1  $\mu W$  power for comparison to previous results [5]-[9], [11]-[13].

$\underline{\text{Crosstalk}}$  was compared using the Relative Crosstalk parameter: Relative Crosstalk is equal to the Normalized QE produced at the central Pixel for illumination just outside the central pixel at the 50 $\mu$ m position.

<u>Sensitivity</u> was defined as the maximum QE produced at the central pixel for illumination over the central pixel. For back illumination this is normally for illumination at the centre of the pixel. For front illumination the maximum QE usually occurs for illuminations outside the well due to negating hole current photo-generated in the well.

Figure 1. The primitive StaG Photodiode array [11].

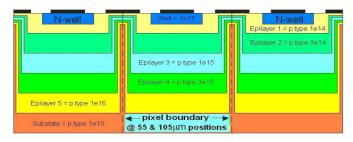

Figure 2. The StaG Photodiode array with inter-pixel nested ridges (StaG-R) extending to the frontwall [12].

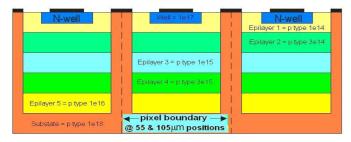

Figure 3. The StaG Photodiode array with inter-pixel Boundary Trench Isolation (BTI) extending to the frontwall [13].

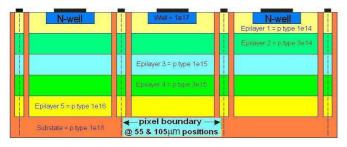

Figure 4. The StaG Photodiode array with inter-pixel Double Boundary Trench Isolation (DBTI) with p+ substrate doping, extending to the frontwall.

Figure 5. The StaG Photodiode array with inter-pixel Double Boundary Trench Isolation (DBTI) consisting of SiO<sub>2</sub>, extending to the frontwall.

Transparent ohmic contacts were used on the well and substrate surfaces on the front side of the array. Identical devices were simulated for both the BW and FW cases at  $5\mu m$  intervals along the backwall and frontwall, respectively.

#### III. THEORY

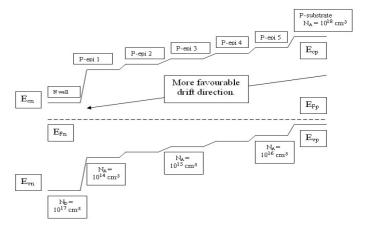

The principle of the StaG geometry is that it is energetically more favorable for carriers to migrate in the direction of decreasing doping, towards the depletion region, resulting in improved crosstalk and sensitivity for both modes of illumination (Fig. 6). The direction of decreasing doping

produces a potential gradient that drives the minority photocarriers towards the depletion region [11], [12]. The epilayers doped in this manner act together as a minority carrier mirror reflecting carriers vertically towards the depletion region.

Figure 6. Energy band diagram schematic of an unbiased five p - epilayer StaG PD indicating the more favourable direction of carrier drift - i.e. the potential gradient drives minority carriers towards the depletion region.

As this structure introduces directionality to carrier transport, adding a vertical 5-epilayer StaG structure will also reflect carriers generated from the sides of the pixel towards the depletion region (Fig. 2). This geometry would be very difficult to fabricate and thus the BTI geometry was introduced and investigated. The BTI structure (Fig. 3 & 4) represents a lateral stacked gradient homojunction, that is, a two layered structure, rather than the StaG-R five layered architecture photodiode (Fig. 2). Both the single BTI (Fig.3) and DBTI (Fig. 4) will act as minority carrier mirrors, increasing the pixel's carrier capture efficiency, suppressing crosstalk and increasing sensitivity. Additionally both DBTI structures (Fig. 4 & 5) will trap crosstalk carriers within their inter-pixel cavities, benefiting crosstalk suppression further: one acting as a minority carrier mirror (Fig. 4), and the other (Fig. 5) preventing crosstalk carriers passing through the adjacent BTI into the pixel.

The quantum efficiency  $(\eta, QE)$  for an incident wavelength  $(\lambda)$ , and radiant intensity  $(P_{opt})$  was calculated using

$$\eta(\lambda) = \frac{hcI_{\lambda}}{\lambda qP_{opt}} \tag{1}$$

where h is Planck's constant, c is the speed of light, and q is the electronic charge. The QE was calculated for the simulated electron, hole and total currents  $(I_{\lambda})$ .

#### IV. RESULTS AND DISCUSSION

### A. Relative Crosstalk and sensitivity comparison.

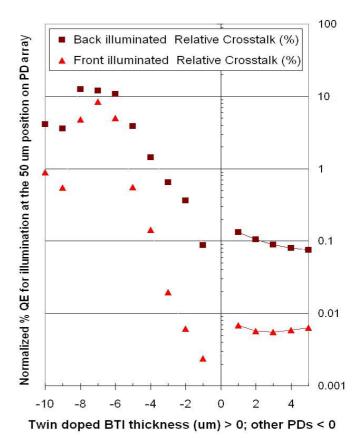

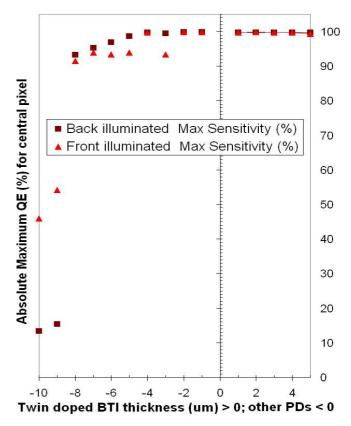

Fig. 7 and Fig. 8 compare the relative crosstalk and maximum QE (sensitivity) for specific photodiode geometries with that of the doped DBTI architecture. The negative values

on the horizontal axis refer to specific photodiode geometries while the positive values on the same axis refer to BTI width. This device geometry code is outlined in Table 1.

TABLE I. HORIZONTAL AXIS NUMBER GUIDE FOR FIG. 7 AND 8.

| Photodiode Configuration                                       | Horizontal<br>axis number<br>(Fig 7 & 8) |

|----------------------------------------------------------------|------------------------------------------|

| BTI width (μm) for StaG Twin BTI 6 μm apart (Fig. 5)           | 1 - 5                                    |

| StaG twin BTI SiO <sub>2</sub> 1 μm thick (Fig. 4)             | -1                                       |

| StaG single BTI SiO <sub>2</sub> 1 μm thick (similar to Fig.3) | -2                                       |

| StaG with fully nested ridges (Fig. 2)                         | -3                                       |

| StaG single doped BTI 1 μm thick (Fig. 3)                      | -4                                       |

| StaG flat without BTI (Fig. 1)                                 | -5                                       |

| Naked SJPD with twin BTI SiO <sub>2</sub> 1 μm thick [8],[9]   | -6                                       |

| Naked SJPD with single BTI SiO <sub>2</sub> 1 μm thick [8]     | -7                                       |

| Naked SJPD - just substate and wells [5],[9]                   | -8                                       |

| Guard ring with single BTI SJPD [8]                            | -9                                       |

| Guard ring electrode SJPD [7], [9]                             | -10                                      |

The  $SiO_2$  DBTI has superior crosstalk suppression to the doped DBTI geometry, which is superior to all other photodiode configurations except the Double Junction PhotoDiode (DJPD) [9]. The DJPD shows superior crosstalk suppression as its outer depletion region acts as a perfect crosstalk shield [9]. For the doped DBTI StaG photodiode geometry, crosstalk reduces (Fig. 7) with increasing BTI width from 1 to 5  $\mu$ m for back illumination but is a minimum at 3  $\mu$ m for front illumination.

Front illumination shows relative crosstalk an order of magnitude below that of back illumination across all the photodiode geometries simulated (Fig.7). This is because the former is immediate to the depletion region while the latter is immediate to the substrate, allowing lateral crosstalk diffusion [5]-[9], [11]-[13] and vertical channeling via the ridges (Fig. 2)[12], and single BTI (Fig. 3)[13].

The sensitivity of the DBTI photodiode geometry is superior as the other StaG PD geometries being at 99.8% for both illumination modes. For front illumination the central QE reduces to 87% due to the generation of a negating minority hole current inside the well. This is the same for the front illuminated single BTI StaG photodiode geometry, both doped and with SiO<sub>2</sub>. Sensitivity is above non-StaG geometries such as the DJPD [9]. DJPD sensitivity is reduced for the same reason as its crosstalk is reduced. This is especially true for back illumination, as the majority of carriers are generated outside the outer depletion region of the DJPD [9].

The use of 50  $\mu$ m pitch pixels is for comparison with previous photodiode geometries. Future work will investigate pixels with 10 to 5  $\mu$ m pitch using the best geometries.

Figure 7. Relative crosstalk comparison for both modes of illumination.

Figure 8. Maximum sensitivity comparison for both modes of illumination.

#### B. The Mechanism.

The physical mechanism driving the reduction in crosstalk is internal reflection of crosstalk photo-carriers generated between the DBTI. The doped BTI act as a bi-layer minority carrier mirror while the SiO<sub>2</sub> BTI block transport across their structure. The reflected carriers then recombine in the cavity.

#### V. CONCLUSION

The back illuminated and front illuminated StaG-twin doped BTI and StaG-twin SiO<sub>2</sub> BTI SJPD have shown improve crosstalk suppression and equivalent sensitivity compared to the StaG-, StaG-R- and StaG-BTI-photodiode geometries. Previously simulated non-StaG photodiode geometries also showed more crosstalk and less sensitivity than the StaG-DBTI photodiode geometries except the Double Junction PhotoDiode (DJPD) which showed orders of magnitude less crosstalk [9]. However the DJPD is disadvantaged in sensitivity especially for the back illumination mode [9]. The Twin doped BTI acts as a minority mirror while the later acts as an insulator, both capturing crosstalk carriers between their BTI structures and eliminating crosstalk.

This investigation of the StaG-twin BTI PD is along a path of device geometry evolution with the aim to achieve PD geometries that balance the maximization of response resolution with the minimization of device fabrication complexity. This is achieved through a process of stepwise refinement. The present results indicate the prospect of obtaining significant crosstalk suppression and sensitivity enhancement in CMOS imaging arrays through achievable modifications to the array structure with the view to producing high-speed high-resolution imaging systems.

#### ACKNOWLEDGMENT

The authors wish to thank Prof. Dr Albert Theuwissen of Delft Technical University for introducing the authors to the benefits of the Stacked Gradient homojunction photodiode architecture and subsequent useful encouragement, and Graham Wild of Edith Cowan University for useful discussions.

#### REFERENCES

- [1] M. Furumiya, H. Ohkubo, Y. Muramatsu, S. Kurosawa, F. Okamoto, Y. Fujimoto, & Y. Nakashiba, "High-sensitivity and no-crosstalk pixel technology for embedded CMOS image sensor", *IEEE Trans. El. Devices*, 48, 2001, pp. 2221-2226.

- [2] I. Brouk, Y. Nemirovsky, S. Lachowicz, E.A. Gluszak, S. Hinckley, & K. Eshraghian, "Characterization of crosstalk between CMOS photodiodes", *Solid State Electronics*, 46, 2003, pp. 53-56.

- [3] J.S. Lee, M.E. Jernigan & R.I. Hornsey, "Characterization and deblurring of lateral crosstalk in CMOS image sensors", *IEEE Trans. El. Devices*, **50**, 2003, pp. 2361-2368.

- [4] S. Hinckley, E.A. Gluszak & K. Eshraghian, "Modelling of device structure effects in backside illuminated CMOS compatible photodiodes", *Proc. COMMAD 2000*, Melbourne. IEEE Press, 2000, pp 399–402.

- [5] S. Hinckley, P.V. Jansz, E.A. Gluszak, & K. Eshraghian, "Modelling of device structure effects on electrical crosstalk in back illuminated CMOS compatible photodiodes", *Proc. COMMAD* 2002, Melbourne. IEEE Press, 2002, pp. 397–400.

- [6] S. Hinckley, P.V. Jansz, & K. Eshraghian, "Pixel structure effects on crosstalk in backwall illuminated CMOS compatible photodiode arrays", *Proc. of DELTA 2004*, Melbourne. IEEE Press, 2004, pp. 53– 56.

- [7] P.V. Jansz-Drávetzky & S. Hinckley, "Guard-ring electrode effects on crosstalk in simulated 2D CMOS compatible vertical photodiode pixel arrays", *Proc. COMMAD 2004*, Melbourne. IEEE Press, 2004, pp.299-302

- [8] P.V. Jansz & S. Hinckley, "Pixel boundary trench effects on a CMOS compatible single junction photodiode array with and without guard ring electrodes.", unpublished (2003).1

- [9] P.V. Jansz-Drávetzky, Device structural effects on electrical crosstalk in backwall illuminated CMOS compatible photodiode arrays. Honours Thesis. Edith Cowan University. Perth, WA, 2003.

- [10] B. Dierickx & J. Bogaerts, "NIR-enhanced image sensor using multiple epitaxial layers", Proc. Of SPIE – IS&T Electronic Imaging, 5301, 2004, pp. 205–212.

- [11] S. Hinckley & P.V. Jansz, "Stacked homojunction effects on crosstalk and response resolution in CMOS compatible photodiode arrays.", *Proc. Of IFIP WG 10.5 conference on VLSI-SoC 2005*, Perth, IFIP, 2005, pp. 383-388.

- [12] S. Hinckley & P.V. Jansz, "The effect of inter-pixel nested ridges incorporated in a stacked gradient homojunction photodiode architecture.", Proc. Of SPIE conference on Smart Structures, Devices and Systems III (AU102), Adelaide, SPIE, 2006.

- [13] P. V. Jansz & S. Hinckley, "Inter-pixel boundary trench isolation effects on a stacked gradient homojunction single junction photodiode pixel architecture.", *Proc. COMMAD 2006*, Melbourne. IEEE Press, 2006.