Edith Cowan University Research Online

**Theses : Honours**

Theses

1999

## A 2D DWT architecture suitable for the Embedded Zerotree Wavelet Algorithm

James Martinez Edith Cowan University

Follow this and additional works at: https://ro.ecu.edu.au/theses\_hons

Part of the Graphics and Human Computer Interfaces Commons, and the Theory and Algorithms Commons

#### **Recommended Citation**

Martinez, J. (1999). A 2D DWT architecture suitable for the Embedded Zerotree Wavelet Algorithm. https://ro.ecu.edu.au/theses\_hons/513

This Thesis is posted at Research Online. https://ro.ecu.edu.au/theses\_hons/513

# Edith Cowan University

## **Copyright Warning**

You may print or download ONE copy of this document for the purpose of your own research or study.

The University does not authorize you to copy, communicate or otherwise make available electronically to any other person any copyright material contained on this site.

You are reminded of the following:

- Copyright owners are entitled to take legal action against persons who infringe their copyright.

- A reproduction of material that is protected by copyright may be a copyright infringement. Where the reproduction of such material is done without attribution of authorship, with false attribution of authorship or the authorship is treated in a derogatory manner, this may be a breach of the author's moral rights contained in Part IX of the Copyright Act 1968 (Cth).

- Courts have the power to impose a wide range of civil and criminal sanctions for infringement of copyright, infringement of moral rights and other offences under the Copyright Act 1968 (Cth).

Higher penalties may apply, and higher damages may be awarded, for offences and infringements involving the conversion of material into digital or electronic form.

### A 2D DWT ARCHITECTURE SUITABLE FOR THE EMBEDDED ZEROTREE WAVELET ALGORITHM

A Thesis Submitted in partial fulfilment of the requirements for the award of Bachelor of Engineering

#### **James Martinez**

November 1999

Faculty of Health and Sciences

School of Engineering and Mathematics

Edith Cowan University

Western Australia

## USE OF THESIS

The Use of Thesis statement is not included in this version of the thesis.

#### ABSTRACT

Digital Imaging has had an enormous impact on industrial applications such as the Internet and video-phone systems. However, demand for industrial applications is growing enormously. In particular, internet application users are growing at a near exponential rate

The sharp increase in applications using digital images has caused much emphasis on the fields of image coding, storage, processing and communications. New techniques are continuously developed with the main aim of increasing efficiency. Image coding is in particular a field of great commercial interest. A digital image requires a large amount of data to be created. This large amount of data causes many problems when storing, transmitting or processing the image. Reducing the amount of data that can be used to represent an image is the main objective of image coding.

Since the main objective is to reduce the amount of data that represents an image, various techniques have been developed and are continuously developed to increase efficiency. The JPEG image coding standard has enjoyed widespread acceptance, and the industry continues to explore its various implementation issues. However, recent research indicates multiresolution based image coding is a far superior alternative.

A recent development in the field of image coding is the use of Embedded Zerotree Wavelet (EZW) as the technique to achieve image compression. One of The aims of this theses is to explain how this technique is superior to other current coding standards. It will be seen that an essential part of this method of image coding is the use of multiresolution analysis, a subband system whereby the subbands are logarithmically spaced in frequency and represent an octave band decomposition. The block structure that implements this function is termed the two dimensional Discrete Wavelet Transform (2D-DWT).

The 2D DWT is achieved by several architectures and these are analysed in order to choose the best suitable architecture for the EZW coder. Finally, this architecture is implemented and verified using the Synopsys Behavioural Compiler and recommendations are made based on experimental findings.

#### DECLARATION

I certify that the attached project is my own work and that any material drawn from other sources has been acknowledged.

#### ACKNOWLEDGEMENT

I would like to thank Dr Hon Nin Cheung and Ken Ang Li-Minn who assisted me in the completion of this project. Also I would like to thank Cole Bergensen for all help given with the Synopsys VHDL software.

11-7-99

## **TABLE OF CONTENTS**

| Abstract                        | 11  |

|---------------------------------|-----|

| Declaration and Acknowledgement | iii |

1

#### Introduction

#### CHAPTER 1 WAVELET AND IMAGE CODING

| 1.0 Basic Wavelet theory                       | 5  |

|------------------------------------------------|----|

| 1.1 Choice of wavelet basis                    | 7  |

| 1.2 Dilation                                   | 9  |

| 1.3 Image Compression                          | 01 |

| 1.4 Subband transforms                         | 11 |

| 1.5 Transform properties                       | 12 |

| 1.51 Scale and orientation                     | 13 |

| 1.52 Spatial localisation                      | 13 |

| 1.53 Orthogonality                             | 14 |

| 1.6 Some Transforms                            | 15 |

| 1.61 The Gabor Transform                       | 15 |

| 1.62 The DCT Transform                         | 16 |

| 1.63 The Laplacian pyramid                     | 17 |

| 1.64 Quadrature mirror filters                 | 18 |

| 1.65 Asymmetrical QMF filters                  | 19 |

| 1.66 Non-Separable QMF transforms              | 19 |

| 1.7 Multiresolution Analysis                   | 20 |

| 1.8 Wavelet transform Vs Subband decomposition | 22 |

| 1.9 Wavelet properties                         | 23 |

| 1.10 Entropy                                   | 26 |

|                                                |    |

#### CHAPTER 2 IMAGE CODERS

.

| 2.1 Basic image coders                   | 27 |

|------------------------------------------|----|

| 2.2 Entropy coding and arithmetic coding | 28 |

| 2.3 Transform coding                     | 28 |

| 2.4 Run length coding                    | 29 |

| 2.5 Zerotree coding                      | 29 |

| 2.6 Embedded zerotree wavelet transform  | 30 |

#### CHAPTER 3 SEARCH STRATEGIES AND EZW COMPONENTS

| 3.1 Tree search strategies                              | <u>34</u> |

|---------------------------------------------------------|-----------|

| 3.2 Depth first search and Breadth first search         | 35        |

| 3.3 EZW components                                      | 36        |

| 3.31 Discrete Wavelet transform                         | 37        |

| 3.32 Mallat's tree algorithm                            | 38        |

| 3.4 Two dimensional discrete wavelet transform (2D-DWT) | 39        |

| 3.5 Quantization zerotree                               | 40        |

| 3.6 Arithmetic coding                                   | 40        |

|                                                         |           |

#### CHAPTER 4 TWO DIMENSIONAL DWT ARCHITECTURES

| 4.1 Two dimensiona DWT architectures        | 41 |

|---------------------------------------------|----|

| 4.2 Comoputational complexity of the DWT    | 42 |

| 4.3 Data dependencies within DWT            | 43 |

| 4.4 Finite precision effect                 | 45 |

| 4.6 Image quality                           | 46 |

| 4.61 Subjective and objective image quality | 46 |

#### CHAPTER 5 / PROPERTIES OF DWT ARCHITECTURES

| 5.0 Architecture considerations        | 48 |

|----------------------------------------|----|

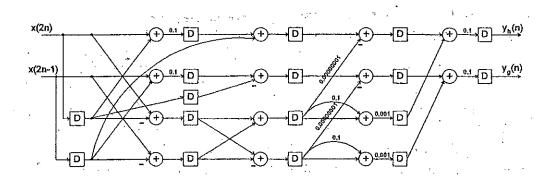

| 5.1 Systolic architecture              | 48 |

| 5.2 Lattice filter type architecture   | 50 |

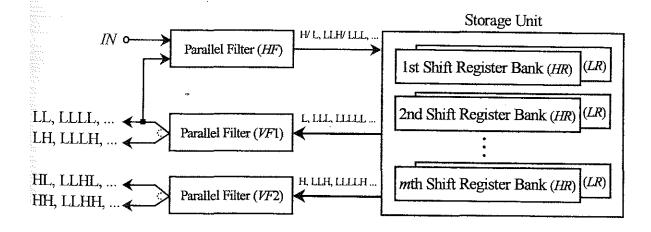

| 5.3 Pararell architecture              | 52 |

| 5.4 2D-DWT Processor type architecture | 54 |

| 5.5 Recursive type architecture        | 57 |

| 5.6 Recommended architecture           | 58 |

| 5.7 XILINK XC40000                     | 61 |

| 5.8 MAC implementation                 | 62 |

| 5.9 FIR filter implementation          | 63 |

| 5.10 Memory bank                       | 64 |

| 5.11 Control unit                      | 66 |

#### CHAPTER 6 VHDL IMPLEMENTATION

| 6.0 VHDL for hardware design         | 67 |

|--------------------------------------|----|

| 6.1 Hardware for implementation      | 69 |

| 6.2 Control                          | 70 |

| 6.3 VHDL architecture implementation | 77 |

| 6.4 Behavioural VHDL core            | 79 |

| 6.5 Filter variations                | 84 |

| 6.6 Structural architecture          | 85 |

| 6.7 Modularity                       | 86 |

| 6.7 Structural computational unit    | 86 |

| 6.71 Structural multiplier           | 87 |

| 6.72 Structural adder                | 88 |

| 6.73 Structural multiplexer          | 89 |

| 6.74 Structural delay unit           | 89 |

| 6.75 Strutural memory bank           | 89 |

| 6.76 Structural control              | 90 |

#### CHAPTER 7 RESULTS

| 7.0 Introduction                      | 91 |

|---------------------------------------|----|

| 7.1 Results and observations          | 92 |

| 7.2 Outcomes                          | 94 |

| 7.3 Throughput                        | 96 |

| 7.4 Latency                           | 97 |

| 7.5 Comparison to other architectures | 98 |

| 7.6 Input output considerations       | 99 |

#### CHAPTER 8 CONCLUSION

# 8.0 Conclusion

| 8.1 Further work         | 104 |

|--------------------------|-----|

| 8.2 Concluding statement | 104 |

| Bibliography             | 105 |

| Appendices               | 109 |

100

#### INTRODUCTION

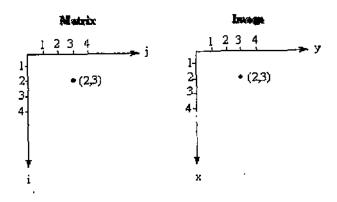

Digital images are used in many applications such as the internet and high definition TV (HDTV). An image can be considered as a positive function on a plane. The value of this function at each point specifies the luminance or brightness of the picture at that point. Digital images are sampled versions of such functions where the value of the function is specified only at discrete locations on the image plane, known as pixels. The standard representation of a digital image is then that of samples (pixels) residing on a rectangular lattice or matrix as shown in figure 1.0.

Fig. 1.0 Image representation as a matrix of luminance values

If an image is made of pixels of certain brightness placed in a rectangular matrix of size MxN, then there would be M xN pixels. Furthermore each pixel has a certain level of brightness which is represented to a pre-defined precision B (usually 8 bits), hence an image is composed of MxNxB bits. If an image is composed of 512 pixels and each pixel has a value of 0-255 for brightness which requires 8 bits, then the canonical representation of this image requires  $512^2 \times 8 = 2097152$  bits.

The huge amount of data required to represent an image is further aggravated when we consider that colour images requires even more data due to the representation of colour by a three dimensional vector function on a plane. Also most digital images have in excess of 512x512 pixels and hence require much larger storage space. Image coding consists of mapping images to strings of binary digits. The function of all image coders is to produce a binary string whose length is smaller the original canonical representation of the image by transforming the image.

In most cases, an image has a large amount of redundant data which is not required to represent the image accurately. In other words this redundant data can be removed without affecting the image quality significantly. Transform coding hence breaks the pixel array representing the image into a statistically uncorrelated data set. In plain language this means that the image is split into bands of different detail levels. When an image transformer is used effectively with a quantitiser, good compression can be achieved.

Quantizing a group of pixels together is known as vector quantization, or VQ. It has been shown [1] that in principle this method can achieve the highest compression that can be achieved by any coder. However it is also true that that the computational cost and delays experienced by these coders grow with dimensionally, limiting the practicality of VQ. For this reason and other difficulties, most practical coding algorithms have turned to transform coding instead of high dimensional VQ.

.

Transform coding consists of scalar quantization in conjunction with a linear transform to capture much the benefits of VQ without many of the problems experienced by VO. Transform coding is successful if the basis functions of the transform represent the features of the signal accurately. At present, one of the most successful representations is the wavelet transform which can be viewed as a special case of a subband transform.

The theory underlying wavelets brings to bear a fundamentally different perspective than the frequency-based subband framework. The temporal properties of the wavelet transform have proved particularly useful in motivating some of the most recent coders. The Development of Embedded Zerotree Wavelet coding [2] motivated a flurry of activity in the area of zerotree wavelet algorithms. The inherent simplicity of the zerotree data structure, its computational advantages, as well as the potential for generating an embedded bitstream are all desirable qualities of good image coders.

This technique uses a two dimensional wavelet transform to break the data into low frequencies containing most of the image details and high frequencies containing most of the redundant data. It will be seen in this theses that the EZW algorithm achieves very good rate distortion performance and have a successive refinement property meaning that it generates an embedded code.

The purpose of this thesis is focused on investigating the advantages of the EZW algorithm over other existing compression techniques. A model of the EZW coder will also be presented and this will be discussed in detail. An essential functional block of the EZW coder is the 2-D Discrete Wavelet Transform and the aim of this theses is to investigate current efficient architectures to implement this function. A suitable architecture will be selected and then implemented and verified in VHDL using the Synopsys Behavioural Compiler or Accolade PeakVHDL Tools.

The organisation of this thesis is as follows. Chapter 1 provides an overview of image compression fundamentals and wavelets and provides a solid background to many fundamental issues. Chapter 2 discusses the EZW coder and compares this to other existing coders. Chapter 3 looks at the current EZW model and elaborates on the building blocks of this model. Chapter 4 discusses current 2-D DWT architectures and outlines a recommended architecture. Chapter 5 discussess VHDL modelling of the proposed architecture. Chapter 6 investigates and evaluates results of the VHDL simulations. Finally, Chapter 7 gives conclusions and further work for the overall research.

#### CHAPTER 1

#### WAVELETS AND IMAGE CODING

#### 1.0 BASIC WAVELET THEORY

Wavelets are functions that can be used to filter other functions into low frequency components and multiple levels of high frequency components. The low frequency information is obtained from a scaling filter, and the high frequency information is obtained from detail, or wavelet, filters. The wavelet transform has an advantage over the Fourier transform in that it is able to deal with low frequency information over a large time and high frequency information over a short time. This makes wavelets desirable when dealing with functions containing a wide range of frequencies.

The Discrete Wavelet Transform (DWT) as shown in Eq.(1) is quite simple to compute once the basis functions have been chosen.

$$C_{i} = \sum \frac{N-1}{J=0} b_{ij} a_{j}$$

(1)

Where:

$C_i = i^{th}$  Transformed coefficient.  $b_{ij} = j^{th}$  value of  $i^{th}$  normalised basis functions.  $a_j =$  value of datum.

N = number of taps in the basis functions.

Similarly, the inverse transform is shown in Eq.(2).

$$\tilde{a}_{1} = \sum_{j=0}^{N-1} b_{ji} C_{j}$$

(2)

Where:

$C_{j} = j^{th} \text{ transformed coefficient.}$   $b_{ji} = i^{th} \text{ value of } j^{th} \text{ basis function.}$   $\tilde{a}_{i} = \text{reconstructed datum value.}$ N = number of taps in the basis functions.

The DWT is a one dimensional transform. Multi-dimensional data can be transformed by applying the transform to each dimension separately. Also, wavelets can be easily applied to different block sizes of the data. The basic wavelet function called the mother wavelet needs only to be translated and scaled to change the extend of the transform.

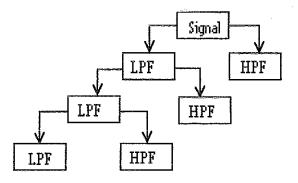

The Mallat algorithm for DWT [3] is a computationally efficient method of implementing the wavelet transform. The algorithm operates on a finite set of N input data, where N is a power of two. The data is passed through two convolution functions, each of which creates an output stream that is half the length of the original input. It will be seen later that the convolution functions are a low pass and a high pass FIR filters.

Furthermore the DWT is a convolution function. The property of convolution functions is that the low pass filter output contains most of the "information content" of the original input signal while the high pass filter output contains the difference between the true input and the value of the reconstructed input if it were to be reconstructed from only the information given in filter's output. In general, higher order wavelets tend to put more information in the low pass filter output and less in the high pass filter output.

The property of putting more information in the low pass filter output is very significant in image compression, if the average amplitude of the high pass filter is low enough, then the high pass filter output may be discarded without greatly affecting the quality of the reconstructed signal. An important objective of this thesis is to find wavelet functions which cause the high pass output to be nearly zero.

#### **1.1 CHOICE OF WAVELET BASIS**

Deciding on the optimal wavelet basis to use for image coding is a difficult problem. A number of design criteria, including smoothness, accuracy of approximation, size support, and filter selectivity are known to be important [4].

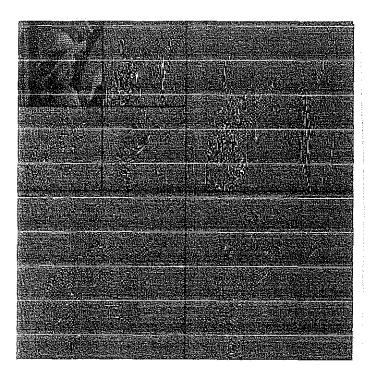

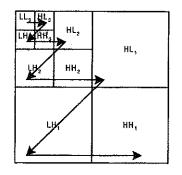

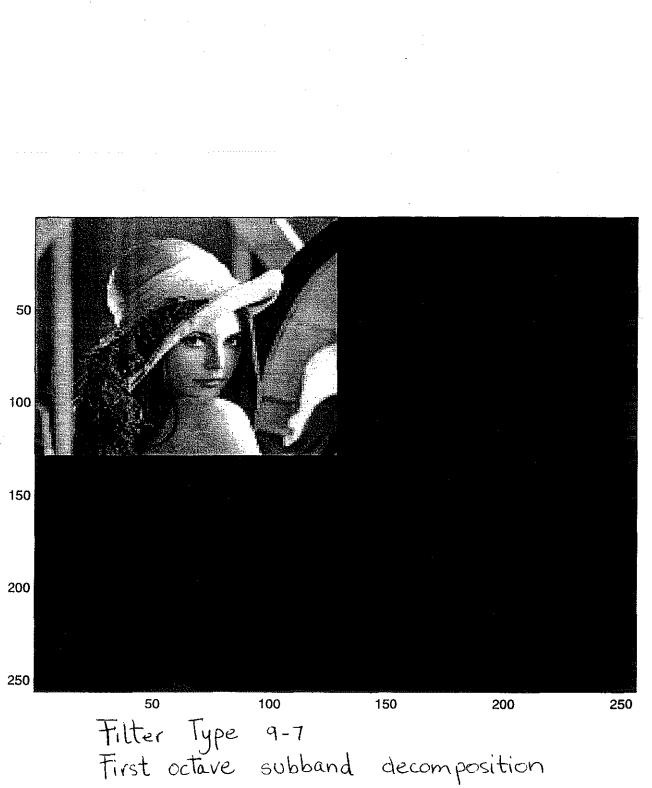

The simplest form of wavelet basis for images is a separable basis. This basis is formed from translations and dilations of products of one dimensional wavelets. Using separable transforms resolves the problem of designing efficient wavelets to a one dimensional problem, hence almost all current coders employ separable transforms. However recent work by Sweldens and Kovacevic [5] simplifies current difficulties with non-separable bases, and such bases may prove more efficient than separable transforms. The prototype basis functions for separable transforms are  $\phi(x)\phi(y)$ ,  $\phi(x)\psi(y)$ ,  $\psi(x)\phi(y)$ , and  $\psi(x)\psi(y)$ . Each step of the transform for such bases involves two frequency splits instead of one. Suppose that a N x N image is applied to the process. First each of the N rows in the image is split into a low pass half and a high pass half. The result is an N x  $\frac{N}{2}$  low pass sub image and an N x  $\frac{N}{2}$  high pass sub image. Next each column of the sub images is split into a low pass and a high pass half. The result is a four way partition of the image into horizontal low pass/vertical low pass, horizontal high pass/vertical low pass, horizontal low pass sub image is sub image is sub-image is sub-image is sub-image is sub-image is sub-image is used in the same manner in the next step. An N x N image exposed to this process is illustrated in figure 1.1. Also it will be seen that the Mallat algorithm for the discrete wavelet transform involves this procedure exactly.

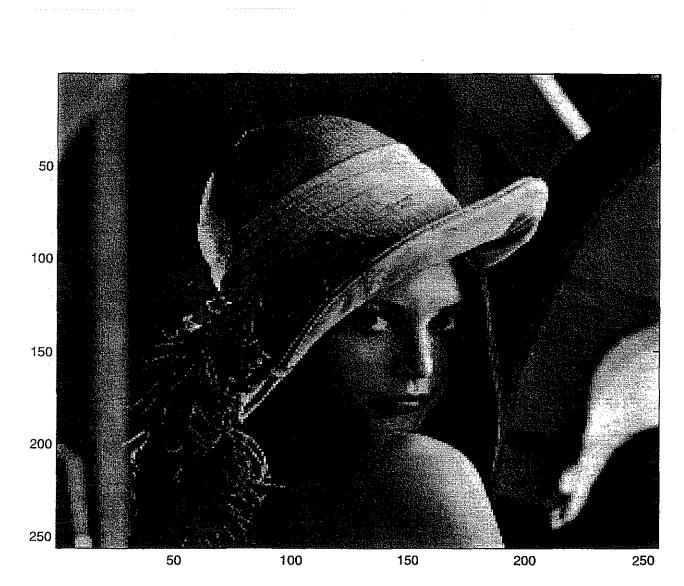

Fig. 1.1 Wavelet transform of the image "Lena"

#### **1.2 DILATION**

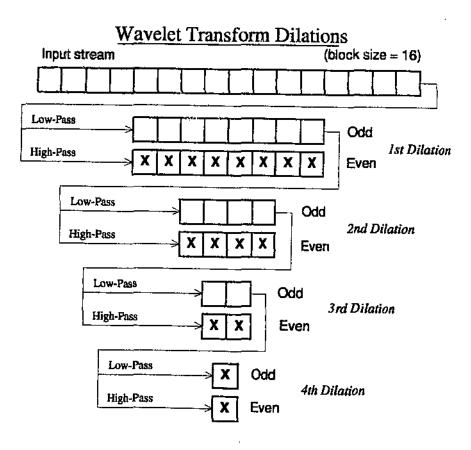

Since most of the information exits in the low pass filter output, then it is possible to transform this low pass filter output by filtering the output with another set of high pass and low pass filters. The new output of this filters is a set of data each one quarter the size of the original input. Again the low pass filter output of the 2nd dilation can be further transformed and so on.

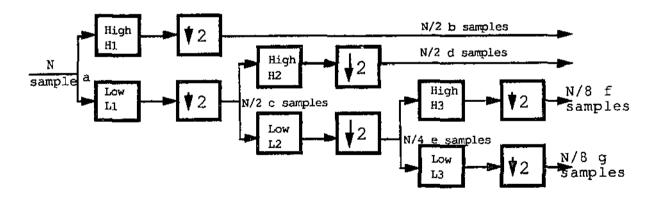

If the number of input samples is  $N = 2^{D}$  then a maximum of D dilations can be performed, the last dilation resulting in a single low pass value and high pass value as shown in figure 3.1. The decomposition is on a logarithmic frequency scale as opposed to the linear scale of the Fourier transform and the lowest possible frequency which can be represented by the decomposition is clearly limited by the number of samples in the block. This differs from the Fourier treatment in which the decomposition includes all frequencies down to zero due to its infinite support..

Fig. 1.2 Dilations of a sample block of data

#### 1.3 IMAGE COMPRESSION

Wavelet transformed images become sparse ideally. This means that a high proportion of the matrix has zero entries or close to zero. The low pass filter output contains most of the information and the high pass filter contains flavour or nuance information, which can be discarded without affecting greatly the quality of the image. Compression is achieved when the zero elements in the sparse matrix are discarded. Ideally if the sparse matrix contains many zero entries, then the size of the matrix can be reduced considerably after removal of the zero entries. Furthermore, a non negative threshold value  $\varepsilon$  can be defined for the compression system and any data whose magnitude is less than or equal to  $\varepsilon$  will be reset to zero.

Lossy compression is achieved when  $\varepsilon > 0$  since when the image is reconstructed it results in an approximation of the original image. The reconstructed image may be an approximation but the quality of the reconstructed image is visually acceptable. In some cases it is difficult to tell the difference visually between original and reconstructed. The second type of compression available is lossless compression,  $\varepsilon = 0$ . This type of compression has the property that the reconstructed image is an exact copy of the original image without any errors. Obviously since more data can be discarded when lossy compression is used, then higher compression rates can be expected for this method of compression. Compression ratios of up to 100:1 and even greater are possible, however, the increase in compression ratio is only at the expense of degraded image quality in the reconstructed image.

#### 1.4 SUBBAND TRANSFORMS

Linear transforms are the basis for many techniques used in image processing, image analysis, and image coding. Subband transforms are a subclass of linear transforms which offer useful properties for these applications. In this chapter a variety of subband decompositions will be examined and their use in image coding is illustrated.

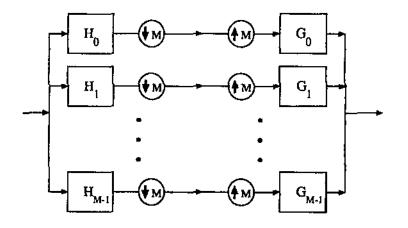

Traditionally, coders based on linear transforms are divided into two categories: Transform coders and subband coders. This distinction is due in part to the nature of the computational methods used for the two types of representation. A subband transformer is a multi-rate digital signal processing systems. There are three elements to multi-rate systems: Analysis filters (H<sub>n</sub>), interpolators  $\uparrow M$ , decimators  $\downarrow M$ , and Synthesis filters (G<sub>n</sub>). These elements are packed in a block termed the filter bank as seen in figure 4.1.

Fig.1.3 Filter bank

Transform coding techniques are usually based on orthogonal linear transforms. The Discrete Fourier Transform (DFT) is a typical transform which decomposes a signal into sinusoidal frequency components. Also, the Discrete Cosine Transform (DCT) and the Karhunen-Loeve Transform (KLT) are typical transform coding techniques. The transform is performed in most cases by taking the inner product of the finite-length signal with a set of basis functions. This produces a set of coefficients, which are then passed on to the quantization stage of the coder.

Subband transforms are generally computed by convoluting the input signal with a set of bandpass filters and decimating the results [6]. Each decimated subband signal encodes a particular portion of the frequency spectrum, corresponding to information occurring at a particular spatial scale. To reconstruct the signal, the subband are upsampled, filtered, and then combined additively.

#### 1.5 TRANSFORM PROPERTIES

The criteria used in choosing a linear transformation for coding purposes should be carefully developed. There is a set of properties which are relevant when considering the problem of image coding. The properties of interest are;

- Scale and orientation

- Spatial Location

- Orthogonality

#### **1.51 SCALE AND ORIENTATION**

Images contain objects and features of many different sizes which may be viewed over a large range of distances. Image transformation should analyse the image simultaneously and independently at different scales. Several authors [7,8] have argued that the correct partition in terms of scale is one in which the scales are related by a fixed constant of proportionality. In the frequency domain, this corresponds to a decomposition into localised subbands with equal widths on a logarithmic scale.

For two-dimensional signals, a localised region in the frequency plane corresponds spatially to a particular scale and orientation. Orientation specificity allows the transform to extract higher order oriented structures typically found in images, such as edges and lines. Thus, it is useful to reconstruct transformations which partition the input signal into localised patches in the frequency domain.

#### **1.52 SPATIAL LOCALISATION**

Spatial localisation is useful where information about the location of features in the image is critical. Spatial localisation should not occur abruptly since it leads to poor localisation in the frequency domain but in most image coding systems it is advantageous to have spatial localisation.

The concept of joint localisation in the spatial and spatial-frequency domains may be contrasted with the two most common representations used for the analysis of linear systems: the sampled or discrete signal, and its Fourier transform.

The standard basis for discrete signals consists of impulses located at each sample location. The basis functions are maximally localised in space, but convey no information about scale. On the other hand, the Fourier basis set is composed of even and odd phase sinusoidal sequences, whose usefulness is primarily due to the fact that they are the eigenfunctions of the class of linear shift-invariant systems. Although they are maximally localised in the frequency domain, each one covers the entire spatial extent of the signal.

#### **1.53 ORTHOGONALITY**

Decorrelation is the main reason for orthogonality as a property of an image coding system. Given a signal with prescribed second order statistics, there is an orthogonal transform which will decorrelate the signal. This means that the second order correlation of the transform coefficients will be zero. Orthogonality is usually not discussed in the context of subband transform, although many such transforms are orthogonal. Hence orthogonality is not strictly necessary but in most image coders it is advantageous to have the property of orthogonality.

#### 1.6 SOME TRANSFORMS

For a transform to be useful it should be well localised in the spatial and frequency domains. Furthermore, Criteria has been provided [10] for choosing a linear transformation for image coding purposes. An explicit representation of scale is widely accepted as being important for effective image representation [3]. In addition to localisation in frequency, it is advantageous for the basis function to be spatially localised. Finally, the basis should be orthogonal for proper decorrelation of the image.

In this section several transforms will be examined by considering the criteria of scale, localisation and orthogonallity. Each transform will be then evaluated for its advantageous and disadvantageous properties.

#### **1.61 THE GABOR TRANSFORM**

A solution to the problem of spatial localised subband decomposition is proposed by Dennis Gabor [9]. Gabor introduced a one dimensional transform in which the basis functions are sinusoids weighted by Gaussian windows. The Gabor transform can be considered to perform a localised frequency decomposition in a set of overlapping windows. The resulting basis functions are localised in both space and spatial frequency. In two dimensions, the Gabor basis functions are directional sinusoids weighted by gaussian windows. Daugman [11] has used two dimensional Gabor transforms for image compression successfully.

The problem with this transform is that the sampling functions are drastically different from the basis functions, hence the basis function is non orthogonal. In a coding application, errors introduced by quantization of the coefficients will be distributed throughout the spatial and frequency domains, even though the coefficient values are computed based on the information in localised spatial and frequency regions.

An interesting feature of the Gabor Transform is that localisation can be improved if an overcomplete Gabor basis set is used by spacing the Gaussian windows more closely than is required, or by dividing each window into more frequency bands. The use of overcomplete Gabor basis is an active area of research and several authors [12,13] have used this to compress image data.

#### **1.62 THE DCT TRANSFORM**

The DCT is the cornerstone of the JPEG image compression standard. In the baseline version of this standard, the image is divided into a number of 8 x 8 pixel blocks, and the block DCT is applied to each block. The resulting block DCT basis functions constitute a subband transform. The DCT has the property of packing signal energy into a small number of coefficients and is a desirable feature in most transform coders. Furthermore, the transform is orthogonal hence many of the problems of the Gabor transform are eliminated.

The problem with this transform is that although the resulting block DCT basis functions constitute a subband transforms, the subbands are not well localised. The subsampled subband images will contain severe amounts of aliasing. This aliasing is removed in the synthesis stage, however, if the transform coefficients are quantized or discarded then the aliasing is not removed and the errors appear as block edge artefacts in the reconstructed image. Jager [14], has proposed techniques for reducing the aliasing of the block DCT by using lapping techniques. However the amount of aliasing removed is limited to equal-sized subbands. Also it is advantageous to subdivide the spectrum into equal log-width subbands in order to reduce the amount of aliasing [14].

#### **1.63 THE LAPLACIAN PYRAMID**

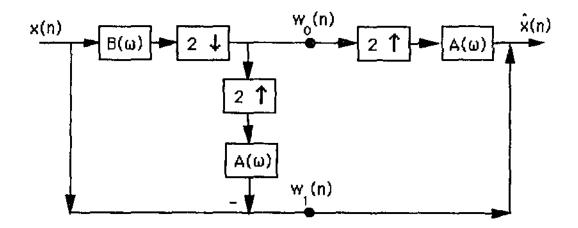

This is one of the first techniques used for octave subband decomposition as developed by Burt [17]. An octave subband transform may be constructed by cascading a two band analysis/synthesis (A/S) system in a non uniform manner as shown in figure 5.1. This system is suitable for data compression, since the multi-scale nature of the pyramid makes it particularly useful for the task of progressive transmission. In the case of a pyramid, this is easily accomplished by sending the transform coefficients in order from lowest to highest resolution.

The Laplacian pyramid suffers from similar problems to the Gabor Transform since this transform is also non orthogonal. The most serious problem with this transform is that quantization errors from highpass subbands do not remain in these subbands. Instead, they appear in the reconstructed image as broadband noise. Furthermore, the basis set is overcomplete, requiring an increase of the number of sample points over the original image. Finally, the two-dimensional basis functions are not oriented, and thus will not extract the oriented structural redundancy typically found in natural images.

Despite all the difficulties experienced by this transform, it is still considered very efficient in progressive image coding. The Laplacian pyramid has been effectively used for motion-compensated video coding, where its overcompleteness makes it robust in to motion-compensation errors [18].

Fig. 1.4 A one level of the Laplacian pyramid. B(W) is a low pass filter and A(W) is a high pass filter

#### 1.64 QUADRATURE MIRROR FILTERS

A useful two-band subband transform was developed by Croiser et. al. [19,20] and is commonly used for speech coding. This transform is based on banks of Quadrature Mirror Filters (QMF). The filters used by Croiser were a class of non-ideal FIR bandpass filters that could be used in an A/S system while still avoid aliasing in the overall system output. Aldelson et al. [21] and Mallat [3] found that these filters form an orthogonal subband transform. Mallat related QMF to the mathematical theory of wavelets and Vetterli [22] suggested the used of these filters for image coding of two dimensional images.

Transforms using QMF captures the advantages of previous mentioned transform coding techniques, while avoiding the disadvantages. It satisfies the properties of useful transform coding being: it is multi-scale and oriented, it is spatially localised, and is an orthogonal transform, and so constrains quantization errors to remain within subbands.

The QMF transform has an unfortunate aspect, the orientation decomposition is incomplete and hence the two diagonal orientations lump together in a single subband. This causes the reconstructed image to look 'blocky'. To address this problem authors like Adelson [21] have proposed using non-separable or non oriented filters [22].

#### **1.65 ASYMMETRICAL QMF FILTERS**

For a QMF transform, the computational complexity is directly proportional to the size of the filters employed. Separable QMF filters can sometimes ignore the issue of computational efficiency due to the steady increase in the speed of signal processing hardware. However, when considering the encoding and decoding of images using general purpose hardware, issues such as computational speed are very important.

In this situation, it is advantageous to develop asymmetric coding techniques in which simplicity is emphasised at one end at the expense of complexity most of the time. In QMF bank filters this requires designing the filters to be less orthogonal. In a A/S system the computational efficiency can be increased by using a very compact filter pair in the synthesis stage as demonstrated by Mallat and Adelson [3,21].

#### **1.66 NON-SEPARABLE QMF TRANSFORMS**

Most two dimensional work with QMFs employs separable or non oriented filters to achieve the transform. As discussed before, separable application of one dimensional QMFs produces a representation in which one of the subbands contains a mixture of two orientations and is a major drawback of separable QMFs. Splitting the frequencies at this subband requires very large filters. In general, the high-frequency diagonal regions of the spectra of the natural images are relatively insignificant. But if the filter bank is cascaded to form a pyramid, then the lower frequency diagonals ( where there is significant power) will also be mixed. The non-separable QMF transform has been investigated by Adelson [21] and uses hexagonal symmetric filters to achieve non separable QMF transforms. However although improving the situation of mixed orientations, the nature of the function is blocked like the DCT, hence unlikely to offer efficient image compression.

#### **1.7 MULTIRESOLUTION ANALYSES**

Most linear transforms have been motivated by probabilistic considerations and assume that the image can be reasonably well-approximated by Gaussian random vectors with a particular covariance structure. The use of the wavelet transform in image coding is motivated by a rather different perspective, that of approximation theory. Wavelet transforms assume that images are locally smooth functions and can be well-modelled as piecewise polynomials. This new perspective provides some valuable insights into the coding process and has motivated some significant advances.

To illustrate the usefulness of multiresoltuion analyses and how wavelets are motivated by this perspective consider a continuous-valued square-intergrable function f(x) using a discrete set of values. A natural set of values to approximate f(x) is a set of regularly spaced, weighted local averages of f(x) such as might be obtained from the sensors in a digital camera. A simple approximation of f(x) based on local averages is a step function approximation it has the form

$$Af(x) = \sum_{n} f_n \phi(x-n)$$

where  $f_n$  is the height of the step in [n,n+1] and  $\phi(x) = 1$  for  $x \in [0,1)$  and 0 elsewhere.

A more generalised approximation will have the form

$$Af(x) = \sum_{n} (\delta(x-n), f(x)) \phi(x-n)$$

Where  $\delta(x)$  is a weight function and  $\phi(x)$  is an interpolating function. The restriction on  $\phi(x)$  ensures that the approximation is exact when f(x) is a linear combination of the functions  $\phi(x-n)$ .

The resolution of the approximation of f(x) can be varied by dilating and contracting the functions  $\phi(x)$  and  $\delta(x)$ . The approximation of Af(x) can then be formed by projecting f(x) onto the span of the functions  $(\phi^{j} (x-2^{-j}k))_{k \in \mathbb{Z}}$ . If V<sub>j</sub> is the space spanned by this functions then the resolution j approximation A<sup>j</sup> f is simply a projection (not necessary an orthogonal one) of f(x) onto the span of the functions  $\phi^{j}(x-2^{-j}k)$ .

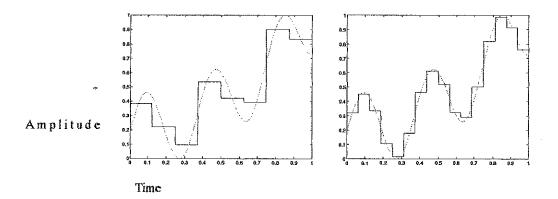

The approximation  $A^{j}$  f(x) corresponds to an orthogonal projection of f(x) onto the space of step functions with step width  $2^{-j}$ . Figure 6.1 shows the difference between the coarse approximation  $A^{0}$  f(x) on the left and the higher resolution approximation  $A^{1}$  f(x) on the right.

Fig. 1.5 A continuos function f(x) (plotted as a dotted line) and the  $A^0 f(x)$  approximation. Right diagram is  $A^1 f(x)$ , a higher resolution approximation of f(x).

#### **1.8 WAVELET TRANSFORMS VS SUBBAND DECOMPOSITION**

The wavelet transform is a special case of a subband transform, as the derivation of the fast wavelet transform reveals. Wavelets involve the analysis of continuous functions whereas analysis of subband decompositions is more focused on discrete time signals. Hence, the main contribution of wavelets transform is one of perspective. The theory of wavelets has a strong spatial component whereas subbands are more focused in the frequency domain.

The subband and wavelet perspectives represent two extreme points in the analysis of the iterated filtering and down sampling process. The filters used in subband decompositions are typically designed to optimise the frequency domain behaviour of a single filtering and subsampling. Theoretically, the wavelet basis functions can be obtained by iterating the filtering and performing a down sampling procedure an infinite number of times. However in typical applications, the number of iterations is limited to the sample size. Examination of the properties of the basis functions provide considerable insight into the effects of iterated filtering.

The wavelet framework explicitly specifies an underlying continuous-valued function from which the original coefficients are derived. The use of continous-valued functions allows the use of powerful analytical tools, and it leads to a number of insights that can be used to guide the filter design process. Within the continuous-valued framework the types of functions that can be represented exactly with a limited number of wavelet coefficients are characterised. Examination of these issues have led to important new design criteria for both wavelet filters [4] and subband decompositions. The second important difference is that wavelets involves spatial as well as frequency considerations whereas subband transform is typically more focused on the frequency domain. Also Coefficients in the wavelet transform correspond to features in the underlying function in specific, well-defined locations. The explicit use of spatial information has proven quite valuable in motivating some of the most effective wavelet coders.

#### **1.9 WAVELET PROPERTIES**

Whereas in subband transform the properties of scale, orthogonality and localisation are of significance, in wavelets the properties of particular interest for image coding are accuracy of approximation, the smoothness, and the support of the wavelet bases [23]. When coding natural images which tend to contain locally smooth regions, it is important that the building blocks be reasonably smooth. If the wavelets possess discontinuities or strong singularities, coefficient quantization errors will cause these discontinuities and singularities to appear in decoded images. Such artefacts are highly visually objectionable, particularly in smooth regions of images.

Procedures for estimating the smoothness of wavelet bases has been developed by Rioul [24] who has pointed that in certain conditions the smoothness of scaling functions is more important criterion than standard frequency selectivity criterion used in subband coding.

Accuracy of approximation is another important property to consider in wavelet based coders. Wavelets can construct smooth, compactly supported bases that can exactly reproduce any polynomial up to a given degree. If a continuous valued function f(x) is locally equal to a polynomial, then the portion of f(x) which is equal can be reproduced with just a few wavelet coefficients.

The degree of the polynomials that can be reproduced exactly is determined by the number of vanishing moments of the dual wavelet  $\psi(x)$ . This wavelet has N vanishing moments provided that  $\int x^k \psi(x) dx = 0$  for k = 0, ..., N. Compactly supported bases for  $L^2$  for which  $\psi(x)$  has N vanishing moments can locally reproduce polynomials of degree N-1.

The number of vanishing moments also determines the rate of convergence of the approximations  $A^{f}$  to the original function f as the resolution goes to infinity. It has been shown [23] that  $||f - A^{f}|| \le C2^{-fN} ||f^{(N)}||$  where N is the number of vanishing moments of  $\psi(x)$  and  $f^{N}$  is the N<sub>th</sub> derivative of f.

The size of support of the wavelet basis is another important wavelet property. Suppose that the function f(x) is equal to a polynomial of degree N-1. If  $\psi$  has N vanishing moments, then any basis function for which the corresponding dual function lies entirely in the region in which f(x) is a polynomial will have a zero coefficient. The smaller the support of  $\psi$  is, the more zero coefficients that can be achieved. More importantly, edges produce large wavelet coefficients. The larger  $\psi$  is, the more likely it is to overlap an edge hence it is important that wavelets have reasonably small support.

There is a problem with limited support in wavelets as specified by Simoncelli [21]. Wavelets with short support have strong constraints on their regularity and accuracy of approximation, but as the support is increased they can be made to have arbitrary degrees of smoothness and number of vanishing moments. This limitation on support is equivalent to keeping the analysis filters short.

Limiting filter length is also an important consideration in the subband coding literature, because long filters lead to ringing artefacts around the edges of the image. Unser [26] shows that spline wavelets are attractive for coding applications based on approximation theoretic considerations. Experiments by Rioul [24] for orthogonal bases indicate that smoothness is an important consideration for compression. Antonini at al [25] find that both vanishing moments and smoothness are important, and for the filters tested they found that smoothness appeared to be slightly more important than the number of vanishing moments.

Nonetheless, Vetterly and Herley [38] state that "the importance of regularity for signal processing applications is still an open question". The bases most commonly used in practice have between one and two continuous derivatives. Additional smoothness does not appear to yield significant improvements in coding results.

Villasenor et al [4] have systematically examined all minimum order biorthogonal filter banks with lengths  $\leq$  36 as well as the additional mentioned criteria, the oscillatory behaviour and sensitivity of the coarse-scale approximations  $A^{j}f(x)$  to translations of the function f(x) have been examined by experiments. The best filter found in these experiments was a 7/9 tap spline variant with less dissimilar lengths from [25]. This filter is one of the most common wavelet coding filters currently used..

For biorthogonal transforms, the squared error in the transform domain is not the same as the square error in the original image. As a result, the problem of minimising image error is considerably more difficult than in the orthogonal case. A number of other filters yield performance comparable to that of the 7/9 filter of [25] provided that bit allocation with a weighted error measure is performed. One such basis is the Daslauriers-Dubuc interpolating wavelet of order 4 [27], which has the advantage of having filter taps that are dyadic rationals.

A new set of filters have been developed by Balasingham and Ramstad [28]. Their design combines classical filter design techniques from ideas from wavelet constructions. This filters yields performance significantly better than the popular 7/9 filter set from [25].

#### 1.10 ENTROPY

The entropy of the signal plays an important part in image coding and compression with respect to the possible effectiveness in the storage and transfer of the signal [16]. In many cases a transformation of the signal leads to a representation of the signal which lowers entropy of the signal. Now, the influence of the used wavelet filter to the entropy of the wavelet coefficients depends on the specific distribution and is defined as follows.

$$H=-E[Ln P_{y}(y)]$$

(3)

With respect to the estimation of the distribution function one has to differ between the approximation and the set of the detail signals. The approximation has a strong correlation, while the coefficients of the detail signals are decorrelated extensively. For the set of detail signals one can assume a Laplace distribution of the coefficients with respect to experimental investigations [17]. In analogy to the detail signals one can fit them to the same distribution of the approximation coefficients with a predictive coding. After the predictive coding, the entropy is calculated as;

$$H_{\lambda} = \frac{-\lambda}{2} \int e^{-\lambda |x-x|} (\ln \frac{\lambda}{2} - \lambda |x-x|) dx$$

(4)

#### **CHAPTER 2**

#### **IMAGE CODERS**

### **2.1 BASIC IMAGE CODERS**

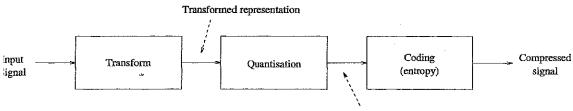

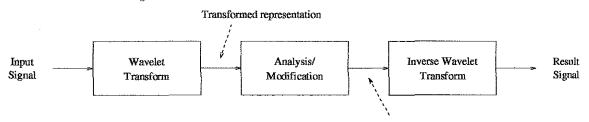

Most wavelet based coders are derived from the transform coder paradigm. There are three basic components that underlay current wavelet coders: a decorrelating transform, a quantization procedure, and an entropy coding procedure as seen in figure 2.1. Considerable research is being performed on all three of these component and the function that each component has in the image coder.

Quantised transformed representation

Fig. 2.1 A basic image coder

27

٠.

#### 2.2 ENTROPY CODING AND ARITHMETIC CODING

Arithmetic Coding provides a near-optimal entropy coding for the quantized coefficient values. The coder requires an estimate of the distribution of quantized coefficients, this estimate can be approximately specified by providing parameters for a generalised Gaussian or a Laplacian density. Alternatively, the probabilities can be estimated on-line. On-line adaptive estimation has the advantage of allowing coders to exploit local changes in image statistics. Efficient adaptive estimation procedures are discussed in [29].

Because images are not jointly Gaussian random processes, the transform coefficients, although decorrelated, still contain considerable structure. The entropy coder can take advantage of some of this structure by conditioning the encodings on previously encoded values. Chen [29] presents a coder which obtains modest performance improvements using such a technique.

### 2.3 TRANSFORM CODING

Chapter 1 indicated that there are generally two types of transform coders, subband based coders, and transform based coders. Moreover subband coding has been discussed in detail in this chapter. Transform coding is used in image coders to reduce spectral redundancy by condensing the energy of an image into a small area.

Typically coders split the image into smaller blocks and a unitary transform is applied to each of the blocks resulting in the formation of a block of transform coefficients which represent the image. The transform coefficients produced by the application of a unitary transform is simply the significance of the frequency information in the image. Therefore low-frequency information will correspond to transform coefficients that are large in value, and high frequency information will correspond to coefficients that are small in value.

# 2.4 RUN LENGTH CODING

This coding method uses the statistical properties of an image to reduce redundancy but instead of generating variable length codewords, the codewords generated are of a fixed length.

# 2.5 ZEROTREE CODING

The knowledge that images of interest are formed mainly from flat area, textures, and edges allows to make advantage of the resulting cross-band structure. Zerotree coders combine the idea of cross-band correlation with the notion of coding zeros jointly to generate very powerful compression algorithms.

The first instance of the implementation of zerotrees is due to Lewis and Knowles [30]. In their algorithm, the image is represented by a tree structured data. This data structure is implied by a dyadic discrete wavelet transform in two dimensions. The zerotree quantization model used by Lewis and Knowles was arrived at by observing that often when a wavelet coefficients are small, its children on the wavelet tree are also small. This phenomenon happens because significant coefficients arise from edges and textures, which are local. It is not difficult to see that this is a form of conditioning. Lewis and Knowles took this conditioning to the limit, and assumed that insignificant parent nodes always imply insignificant child nodes. A tree or sub-tree that contains only significant coefficients is known as zerotree.

The most significant contribution of the work by Lewis and Knowles was to realise that wavelet domain data provide an excellent context for run-length coding: not only are a large run lengths of zeros generated, but also there is no need to transmit the length of zero runs, because they are assumed to automatically terminate at the leaf nodes of the tree. Much the same as in JPEG, this is a form of joint vector/scalar quantization. Each individual coefficient is quantized separately, but the symbols corresponding to small coefficients in fact are representing a vector consisting of that element and the zero run that follows it to the bottom of the tree.

Lewis and Knowles assumed that small parents always have small descendants. However, this assumption causes large distortions in image reconstruction if the small parents don't have small children. This has led many authors like Shapiro[2] to develop a much more powerful algorithm called, Embedded Zerotree Wavelet Algorithm, which overcomes many of the difficulties of the Lewis and Knowles coder.

### 2.6 THE EMBEDDED ZEROTREE WAVELET ALGORITHM

The Lewis and Knowles algorithm, while capturing the basic ideas inherent in many of the later coders, was incomplete. It had all the intuition that lies at the heart of more advanced zerotree coders, but did not efficiently specify significance maps, which is crucial to the performance of wavelet coders. The first algorithm to employ both the non zero data and significance map was produced by Shapiro [2] and was to revolutionise the way more advanced coders operate. The bits needed to specify a significance map can easily dominate the coder output, especially at lower bitrates. However, there is a great deal of redundancy in a general significance map for visual data. Therefore the bitrates for its representation can be kept in check by conditioning the map values at each node of the tree on the corresponding value at the parent node. Whenever an insignificant parent is observed, it is highly likely that the descendants are also insignificant. Therefore, most of the time a "zerotree significance" map symbol is generated. But because p, the probability of this event, is close to 1, its information content, -p log p, is very small. So most of the time, a very small amount of information is transmuted and this keeps the average bitrate needed for the significance map relatively small.

Once in a while, one or more of the children of an insignificant node will be significant. In that case, a symbol for "isolated zero" is transmitted. The likelihood of this event is lower, and thus the bitrate for conveying this information is higher. But it is essential to pay this price to avoid losing significant information down the tree and therefore generating large distortions.

In summary, Shapiro's algorithm uses three symbols for significance maps: zerotree, isolated zero, or significant value. By using this structure, and by conditionally entropy coding these symbols, the coder achieves very good rate distortion performance. In addition, Shapiro's coder also generates an embedded code. Coders that generate embedded codes are said to have the progressive transmission or successive refinement property. Successive refinement consists of first approximating the image with a few bits of data, and then improving the approximation as more and more information is supplied. An embedded code has the property that for two given rates R1>R2, the rate R2 code is a prefix to the rate R1 code.

31

The EZW encoder can easily achieve a precise bitrate because it continues to output bits when it reaches the desire rate. Furthermore, it can cease decoding at any point, generating an image that is the best representation possible with the decoded number of bits. This is of practical interest for broadcast applications where multiple decoders with varying computational, display and bandwidth capabilities attempt to receive the same bitstream. With an embedded code, each receiver can decode the passing bitstream according to its particular needs and capabilities. Also the EZW coding system is useful in indexing and browsing applications, where only a rough approximation is sufficient for deciding whether the image needs to be decoded or received in full.

Shapiro generated an embedded code by using a bit-slice approach. In the bit-slice approach wavelet coefficients are indexed into a one dimensional array and ordered according to their significance. This places the lower frequency contents of the image before the high frequency bands. When wavelet coefficients are encoded using their order of importance, it is sometimes referred to as a raster scan order.

The bit-slice code is generated by scanning the one dimensional array and comparing each coefficient to a threshold T. This initial scan provides the decoder with sufficient information to recover the most significant bit slice. In the next pass, information about each coefficient is refined to a resolution of T/2, and the pass generates another bit slice of information. This process is repeated until there are no more slices to code..

The upper bit slice contains a great number of zeros because coefficients at this level are either zero or bellow the threshold level T. The role of zerotree coding is to avoid transmitting all these zeros. Once a zerotree symbol is transmitted, it is known that all the descendants will also be zero coefficients, so no information is transmitted for them. In effect, zerotrees are a clever form of run-length coding, where the coefficients are ordered in a way to generate longer run lengths as well as making the runs self terminating so the length of the runs need not be transmitted.

32

The zerotree symbols with high probability and small code length can be transmitted again and again for a given coefficient until it rises above the sinking threshold, at which point it will be tagged as a significant coefficient. After this point, no more zerotree information will be transmitted for this coefficient.

Shapiro used a clever method of encoding the sign of the wavelet coefficient with the significance information. Further details of the priority of wavelet coefficients, the bit-slice coding, and adaptive arithmetic coding of quantized values, i.e. entropy coding can be read in Harder's thesis [21]

### **CHAPTER 3**

#### SEARCH STRATEGIES AND EZW COMPONENTS

#### **3.1 TREE SEARCH STRATEGIES**

٠.

The EZW algorithm establishes an ancestor-decendant relationship between the wavelet coefficients in the image subbands. Figure 4.1 shows the image subbands obtained after the 2D-DWT and an ancestor-decendant tree hierarchy between the wavelet coefficients in the image subbands has been applied to an image. The scanning of the coefficients is done in a particular manner so that no child node is scanned before its parent is scanned. In essence, all the coefficients in a subband are encoded before encoding the coefficients in another subband. The order of encoding begins from the lowest frequency subband and ends at the highest frequency subband as indicated.

Fig. 3.1 Raster Scanning of coefficients

34

#### 3.2 DEPTH FIRST SEARCH AND BREADTH FIRST SEARCH

The original EZW algorithm uses a raster scan to encode the wavelet coefficients as seen in figure 4.1. Two other tree searching strategies to encode the wavelet coefficients are possible: the Depth First Search (DFS), and the Breadth First Search (BFS). These strategies provide alternative ways to encode the wavelet coefficients.

The BFS coding strategy operates very similar to the raster scan strategy. Coefficients are also scanned at the same level from all tree hierarchies before the coefficients from another level are encoded. The main difference is the way or the order in which the coefficients are scanned in the same level of the tree hierarchy.

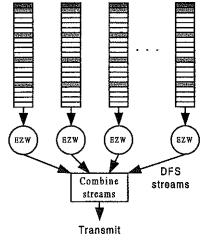

The DFS coding strategy encodes all the coefficients in a tree hierarchy before encoding another tree hierarchy. This simplifies and diversifies the implementation of the EZW algorithm [32]. However, this simplification comes at the cost of a decrease in coding efficiency but provides a dataflow oriented approach which is highly suitable for parallel architectures. The main reason for the parallel suitability is that the DFS performs a natural partitioning of the tree hierarchies into independent tree hierarchies which can then be processed in parallel by individual EZW processors as seen in figure 3.2.

Fig. 3.2

#### Parallel Bitstream Processing by individual EZW Processors

35

£.,

## **3.3 EZW COMPONENTS**

The EZW algorithm is a powerful image coding technique. It has been shown [2] that the algorithm consists of four fundamental operations;

- 1. A discrete Wavelet Transform or hierarchical subband decomposition.

- 2. Prediction of the absence of significant information across scales by exploiting the self-similarity inherent in images.

3. Entropy-coded successive approximation quantization.

4. Adaptive arithmetic coding.

Furthermore, prediction of significant information and entropy coding are commonly combined in a single structure termed Quantization zerotree as seen in figure 3.3.

Modified transformed representation

# Fig. 3.3

#### EZW coding system block structures

36

٢.

## 3.31 DISCRETE WAVELET TRANSFORM

The Discrete Wavelet Transform (DWT) is one of the most useful and efficient tools used to analyse digital signals in various signal processing areas. One major concern, in signal and image processing as well as the communication communities is the effective implementation of the wavelet transform and advanced tools for designing wavelet systems. When there are limitations in processing time and/or system size, implementation of the DWT becomes an engineering issue. The purpose of this thesis is hence to provide an engineering solution to the implementation of the discrete wavelet transform. Furthermore, it will be seen how the proposed solution fits well in the proposed DFS EZW coding system seen in figure 3.3.

The Discrete Wavelet transfer represents an arbitrary square integral function as superposition of a family of basis functions called wavelets. A family of wavelet basis functions can be generated by translating and dilating the mother wavelet corresponding to the family. The DWT coefficients can be obtained by taking the inner product between the input signal and the wavelet functions. Since the basis functions are translated and dilated versions of each other, a simpler algorithm, known as Mallat's tree algorithm or pyramid algorithm, has been proposed [3].

#### 3.32 MALLAT'S TREE ALGORITHM

In this algorithm, the DWT coefficients of one stage can be calculated from the DWT coefficients of the previous stage, which can be expressed as follows:

$$W_{1}(n,j) = \sum_{m} W_{1}(m,j-1)h(m-2n)$$

(5a)

$$W_{h}(n,j) = \sum_{m} W_{h}(m,j-1)g(m-2n)$$

(5b)

Where:

$W_{i}(n_{j})$  and  $W_{b}(j)$  are the n-th scaling coefficient at the j-th stage.

. h(n) are the Low Pass Filter (LPF) dilating coefficients.

. g(n) are the High Pass Filter (HPF) dilating coefficients.

For computing the DWT coefficients of the discrete-time data, it is assumed that the input represents the DWT coefficients of a high resolution stage. Equation 5 can then be used for obtaining DWT coefficients of subsequent stages. In practice, this decomposition is performed only for a few stages. Hence, DWT extracts information from the signal at different scales. The first level of the wavelet decomposition extracts the details of the signal ( high frequency components) while the second and all subsequent decompositions extract progressively coarser information, lower frequency components, as shown in figure 3.4

Figure 3.4 Mallat Algorithm For DWT

38

## 3.4 TWO DIMENSIONAL DISCRETE WAVELET TRANSFORM (2D-DWT)

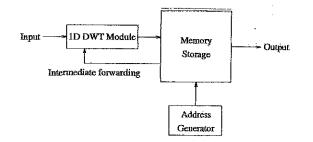

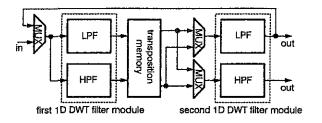

The 2D-DWT can be calculated by several different methods. Most commonly, it is calculated by using a separable approach [3]. First, the One Dimensional Discrete Wavelet Transform (1D-DWT) is performed on each row of the image proceeded by a matrix transposition operation [33]. The transposition memory works on rows of the image to invert the image, hence rows become columns and vice versa. Finally, a one dimensional DWT is performed on the transposed data to achieve two dimensional data. Hence, a 2D-DWT can be implemented by inserting a matrix transposer between two 1D-DWT modules.

In order to reconstruct the original data, the DWT coefficients are upsampled and passed through another set of lowpass and highpass filters which is expressed as:

$$W_{l}(n,j) = \sum_{k} W_{l}(k,j+1)h_{0}(n-2k) + \sum_{l} W_{h}(l,j+1)g_{0}(n-2l)$$

(6)

where  $h_0(n)$  and  $g_0(n)$  are the lowpass and highpass synthesis filter corresponding to the mother wavelet. It is observed in equation 6 that the j-th level DWT coefficients can be obtained from the (j+1)-th level coefficients.

## **3.5 QUANTIZATION ZEROTREE**

The quantization step in the EZW algorithm involves transforming the coefficients array into a quantization zerotree structure. From this zerotree representation, a compressed data stream called a significance map representing the image is obtained using Successive-Approximation entropy-coded Quantisation (SAQ). The output of this block consists of significance maps (MAP) and Successively Approximated values of significant coefficients SAQ. SAQ applies a sequence of threshold successively to determine the significance of the coefficients to obtain a MAP.

## 3.6 ARITHMETIC CODING

The underlying reason for the choice of successive approximation to encode the significance maps for the EZW algorithm is considered directly from the goal of producing an embedded code comparable to the binary-representation of approximating a real number [2]. In achieving a reasonable coding efficiency with Huffman coding, the sequence that is generated by the source is generally divided up into blocks. Each of the blocks then get assigned a variable-length codeword. When decoded, the received codeword is parsed into variable-length blocks which correspond to the individual codewords. This causes a one-to-one correspondence between the codeword blocks and the source sequence blocks. Arithmetic coding on the other hand generates non-block codes. The entire sequence of source symbols is assigned a single arithmetic codeword.

An interval of real numbers between the values of 0 to 1 is defined by the codeword itself. As the number of symbols increases, the interval used to represent it becomes smaller and the number of bits required to represent the interval becomes larger. Each symbol of the message reduces the size of the interval in accordance with its probability of occurrence.

# **CHAPTER 4**

# 4.1 TWO DIMENSIONAL DWT ARCHITECTURES

Multiresolution analysis is an essential part of the EZW coding system. The output of this block consists of coefficients which are mapped in some way by the EZW quantizer. In developing a suitable 2D-DWT architecture, it is important to consider how this architecture fits with the EZW coding system. Moreover, it has been shown that the DFS searching strategy for the coefficients provides a dataflow oriented property which is highly suitable for parallel EZW processors [32].

The purpose of this thesis is to provide an efficient design for implementing the wavelet transform. Furthermore, to fit with the DFS EZW system the proposed architecture operates in a parallel manner which increases the speed of the architecture. Ideally, the factor of speed up achieved by parallelism should not cost more than a similar factor in area. In order to achieve an optimum design several current architectures are discussed in detail before the proposed architecture is considered.

The design employed in this thesis is aimed at special purpose custom single chip design. Hence, the issue of chip area and processing time is very important. Many other important design issues will also be considered.

## 4.2 COMPUTATIONAL COMPLEXITY OF THE DWT

As observed in equation 5, the complexity of each stage of wavelet decomposition is linear in the number of input samples where the constant factor depends on the length of the filter. For a dyadic wavelet decomposition, the number of input samples decreases by 50 % at subsequent stages of decomposition [35]. For a wavelet of order L, with number of decomposition stages j, the computational complexity for an one dimensional N elements sequence is.

$$C_{\text{dyadic}} = (N + \frac{N}{2} + \frac{N}{4} + \dots + \frac{N}{2^{J-1}}) \times 2L \text{ FLOPS}$$

= 4(1-2<sup>-J</sup>)NL FLOP (7)

Where FLOP corresponds floating point operations and usually refers to multiplications and additions. It can be pointed out that the complexity can be further be reduced using sophisticated algorithms, such as First Running FIR Filtering (FFT) [34]. However, these algorithms need complex control circuitry for hardware implementation.

In many applications, a regular tree, instead of a dyadic tree might be more appropriate. The computational complexity at each stage of a regular tree is 2NL FLOP. Hence, the total complexity for a j level decomposition is:

$$C_{\text{regular}} = 2 \text{ JNL FLOP}$$

(8)

The complexity of an irregular tree, or a wavelet packet algorithm is upper bounded by Cregular.

#### 4.3 DATA DEPENDENCIES WITHIN DWT

The Mallat tree decomposition is one of the most common methods used to implement the DWT since it is computationally efficient and can be implemented easily. The wavelet decomposition of a 1D signal for three stages as shown in figure 4.1 hints that there is a dependency of data as data flows from lower levels to higher levels. In order to implement a design, it is important to consider the data dependencies involved in the tree decomposition ...

The low pass, H(Z), and high pass, L(Z), transfer functions for an n-th order filter can be expressed according to:

$$H(Z) = g(0) + g(1)z^{-1} + g(2)z^{-2} + \dots g(n)z^{-n}$$

$$L(Z) = g(0) + g(1)z^{-1} + g(2)z^{-2} + \dots g(n)z^{-n}$$

(10)

$$(Z) = g(0) + g(1)z^{-1} + g(2)z^{-2} + \dots g(n)z^{-n}$$

(10)

It is not hard to define the data dependencies by considering equations 9 and 10. Letting a, b, c, d, e, f, g represent the intermediate and final DWT coefficients (assuming a six tap filter) as seen in figure 4.11 below we have:

Figure 1 Data dependencies in filter bank

$$b(0) = g(0)a(0) + g(1)a(-1) + g(2)a(-2) + \dots g(5)a(-5)$$

(11a)

$$b(2) = g(0)a(2) + g(1)a(1) + g(2)a(0) + \dots g(5)a(-3)$$

(11b)

$$b(4) = g(0)a(4) + g(1)a(3) + g(2)a(2) + \dots + g(5)a(-1)$$

(11c)

$$b(6) = g(0)a(6) + g(1)a(5) + g(2)a(4) + \dots g(5)a(1)$$

(11d)

$$c(0) = h(0)a(0) + h(1)a(-1) + h(2)a(-2) + \dots + h(5)a(-5)$$

(11e)

$$c(2) = h(0)a(2) + h(1)a(1) + h(2)a(0) + \dots + h(5)a(-3)$$

(11f)

$$c(4) = h(0)a(4) + h(1)a(3) + h(2)a(2) + \dots + h(5)a(-1)$$

(11g)

$$c(6) = h(0)a(6) + h(1)a(5) + h(2)a(4) + \dots h(5)a(1)$$

(11h)

# 2nd OCTAVE

$$d(0) = g(0)c(0) + g(1)c(-2) + g(2)c(-4) + \dots g(5)c(-10)$$

(11e)

$$d(4) = g(0)c(4) + g(1)c(2) + g(2)c(0) + \dots g(5)c(-6)$$

(11f)

$$e(0) = h(0)c(0) + h(1)c(-2) + h(2)c(-4) + \dots + h(5)c(-10)$$

(11g)

$$e(4) = h(0)c(4) + h(1)c(2) + h(2)c(0) + \dots + h(5)c(-6)$$

(11h)

# 3rd OCTAVE

$$f(0) = g(0)e(0) + g(1)e(-4) + g(2)e(-8) + \dots g(5)e(-20)$$

(11i)

$$g(0) = h(0)e(0) + h(1)e(-4) + h(2)e(-8) + \dots h(5)e(-20)$$

(11j)

As seen in the above equations, several intermediate results (c,e) are first computed, and then these are used to calculate multiple output samples. The intermediate results must be available for further processing at a specific time instant, implying a memory requirement in the proposed architecture design.

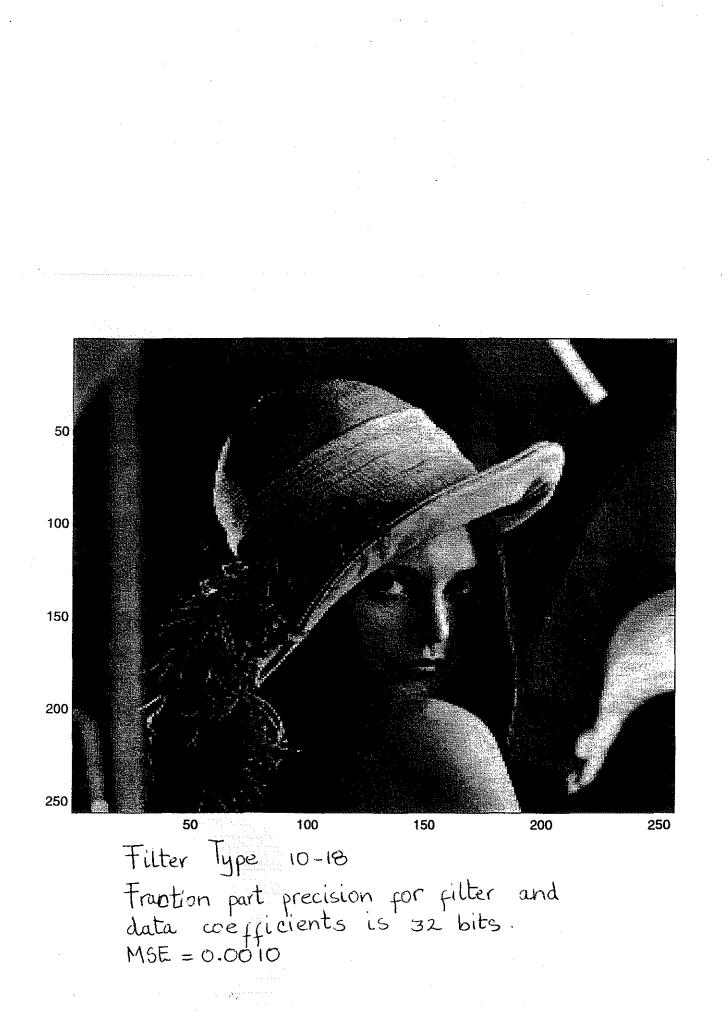

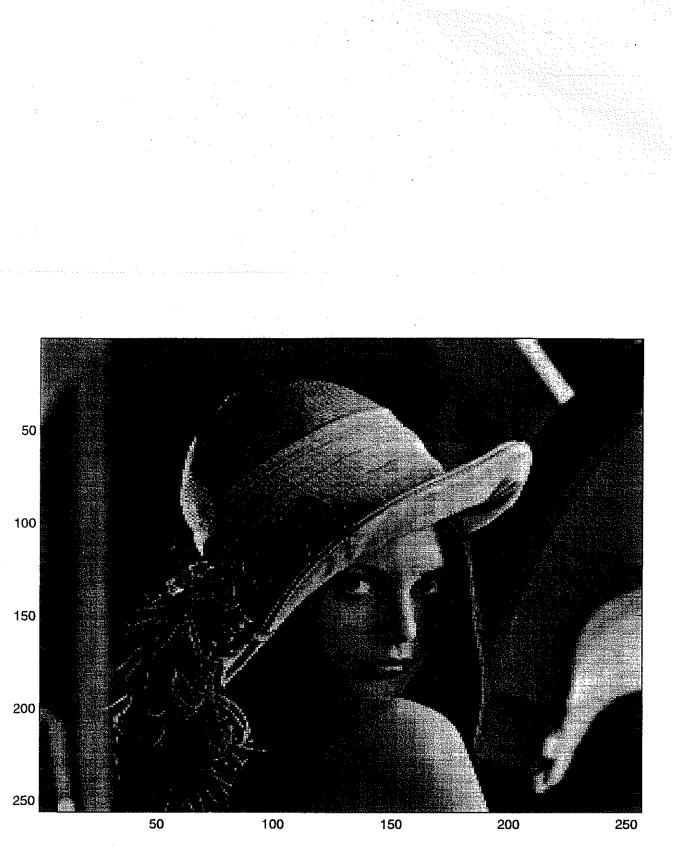

## 4.4 FINITE PRECISION EFFECT

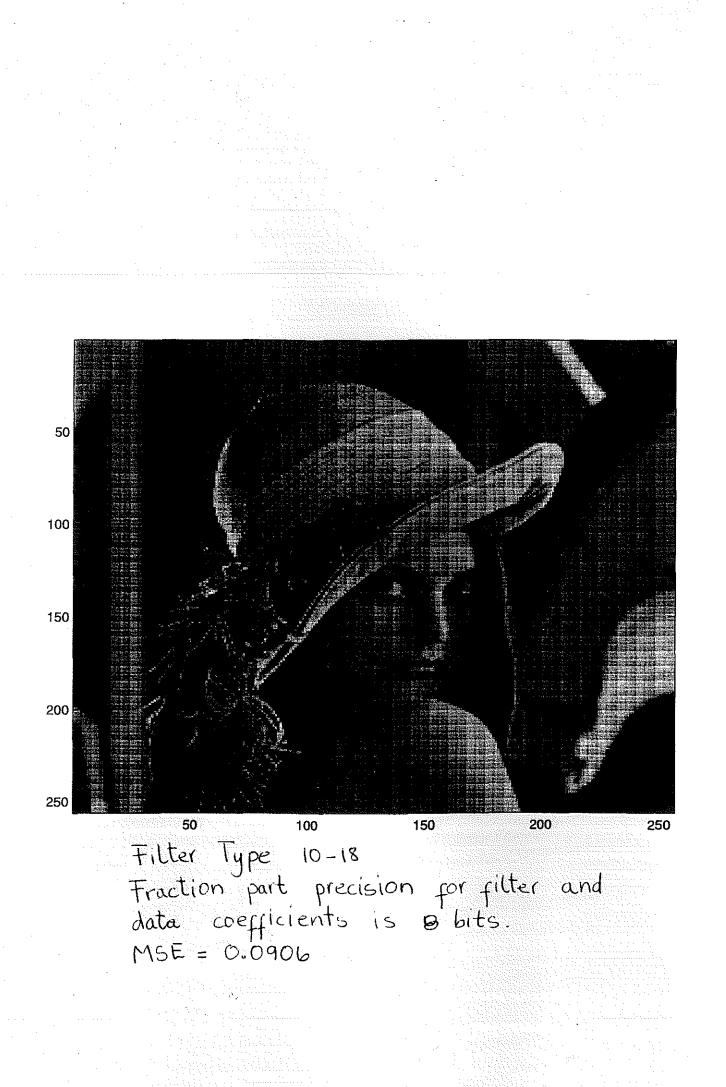

The accuracy of the DWT coefficients is determined by both the precision of the input data, and the wavelet filter coefficients. Reconstructed Image quality measurements results depend proportionally on finite precision effects. Moreover data and coefficient precision are important parameters in the design of DWT architectures. High accuracy is required to achieve suitable image quality, but hardware constraints only permit a certain level of accuracy and thesis paper intends to investigate how accuracy of filter and data coefficients affect image quality in order to produce an optimal design.

In terms of hardware requirements, the DWT coefficients are recursively calculated using equation 5, where W represents wavelet coefficients of a certain stage and h, g represent the corresponding filter coefficients. If The precision of W and h are assumed to be j and m bits respectively, then to execute equation 5, a j x m bits multiplier and accumulator is required.

A useful measure of accuracy of DWT coefficients is the Signal to Noise Ratio (SNR). Here, the signal is the floating point DWT coefficient and noise is the difference between the floating point and finite precision coefficients. In a particular design the performance variation for 1D signal with respect to the precision of filter coefficients with fixed 12 bits DWT coefficients and data was observed to be 50-70 dB SNR [15]. Furthermore, it was also observed that when 2D data was involved a decrease in the SNR results.

## 4.6 IMAGE QUALITY

Signal To Noise Ration (SNR) was briefly described as a useful measure of the accuracy of DWT coefficients. In practice this is not the only available method to measure image quality. Other image quality measurements are available to access quality of reconstructed image. These measurements provide powerful tools for accessing performance of DWT architectures.

# 4.61 SUBJECTIVE AND OBJECTIVE IMAGE QUALITY

Objective measuring employs formulas that represent certain information about the image so that a comparison can be made. In other words these formulas relate the original image to the reconstructed image in some way. In particular, the Root-Mean-Square-Error (RMSE), and the Peak Signal-to-Noise Ratio (PSNR) are very common formula applied to reconstructed images. Given an image represented by f and the reconstructed image represented by g, the RMSE is given by:

RMSE =

$$\sqrt{\frac{\sum_{i=1}^{n} \sum_{j=1}^{n} [f(i,j) - g(i,j)]^2}{N^2}}$$

(12)

This value is measured in dB and is the standard deviation of the error of the reconstructed image from the original image. Also, PSNR is a parameter derived from the RMSE as follows:

$$PSNR = 20 \log_{10} \left( \frac{I}{RMSE} \right)$$

(13)

Where I is the maximum image intensity, i.e. for a 8 bit pixel it would be  $2^{8}$ -1 = 255. Also a further parameter is termed Mean Square Error (MSE) and is simply found by squaring the RMSE value. Typical PSNR values have been found [31] for different compression techniques. These values are typical of good performing architectures. It is desirable that the proposed architecture produces similar results to the ones seen in table 4.1 bellow.

| Building Block      | Compression<br>Technique                 | Bit Rate<br>Bits/Pixel | PSNR(dB) |

|---------------------|------------------------------------------|------------------------|----------|

| Predictive coding   | 2D Differential                          | 1                      | 27.74    |

| Vector Quantization | Level 0 mean residual tree structured VQ | 0.5                    | 26.9     |

| Transform Coding    | JPEG<br>DCT                              | 0.5                    | 34.69    |

| Subband Coding      | Subband Coding with<br>VQ                | 0.56                   | 32.71    |

| Subband Coding      | Subband Coding with<br>EZW               | 0.50                   | 36.28    |

Table 4.1

PSNR for different compression techniques

Generally, the higher the PSNR the better the results obtained. Table 4.1 suggests that the EZW coding technique is one of the best techniques to achieve a high PSNR. A PSNR of 30 dB or higher is considered sufficient for most good quality image coding systems.

Subjective image quality measurements use the most crucial test, the human eye. The eye is very sensitive to poorly reconstructed images, many artefacts can be distinguished very quickly, hence it can be a valid tool to measure image quality.

# CHAPTER 5 DWT ARCHITECTURES

# 5.0 ARCHITECTURE CONSIDERATIONS

The aim of this thesis is the implementation of discrete wavelet transforms through an efficient architecture. Several designs are researched, these share a common criteria or have the same objectives; increasing throughput, decreasing area and attempt to make better use of computational components within the system.

Five important arquitectures will be discussed before a proposed architecture is presented. The existing architectures have unique features which makes them suitable for research. It is hoped to extract these beneficial features from the existing architectures in order to produce the recommended model.

# 5.1 SYSTOLIC ARCHITECTURE

Kung defines a systolic system as a network of processors which rhythmically compute and pass data through the system [35]. In other words, the data within the system is 'pumped' through the processors, which perform simple, local computations on the data. Furthermore, although the operations being performed may not be equal in all processors for a particular time-step, the data-movement and computations throughout the complete system are in synchronisation. The connections in the network are simple and local, and there is at least a single time-step required to move data from one processor to the next. The major benefits of this architecture as reported in [35] are:

- . Simple and regular connectivity

- . Concurrency.

- . Local communication operations

- . Balanced I/O and computation

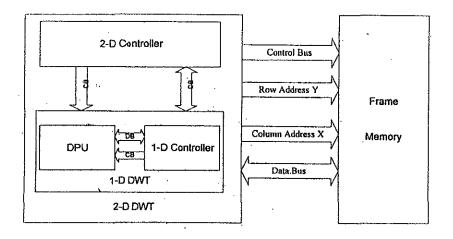

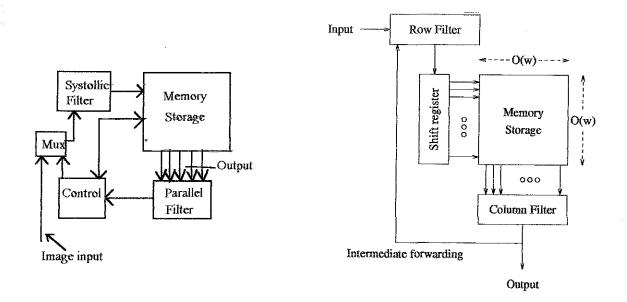

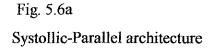

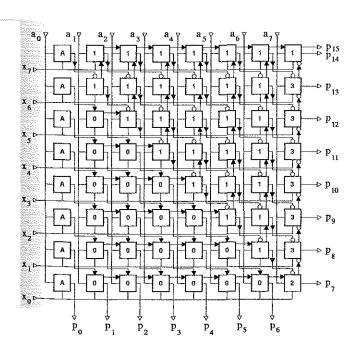

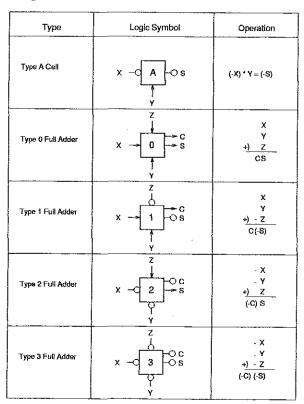

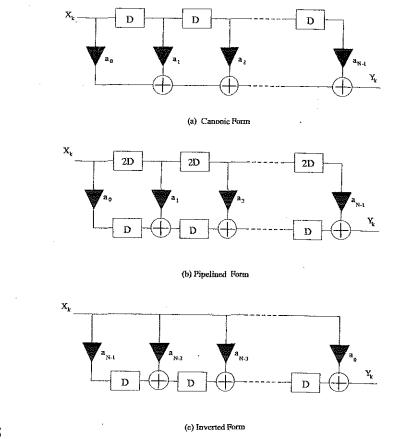

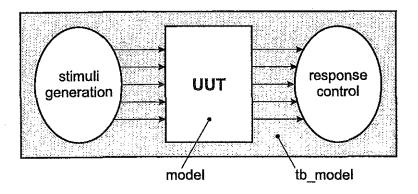

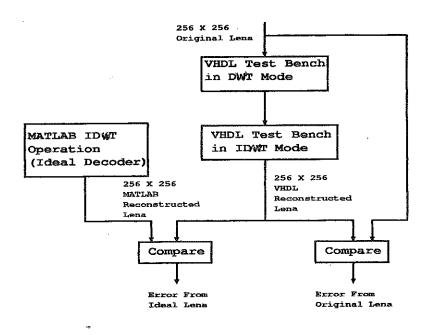

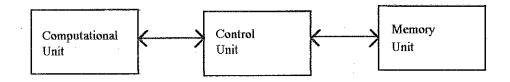

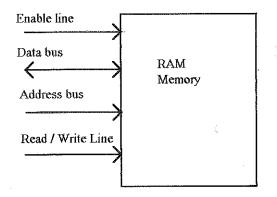

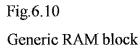

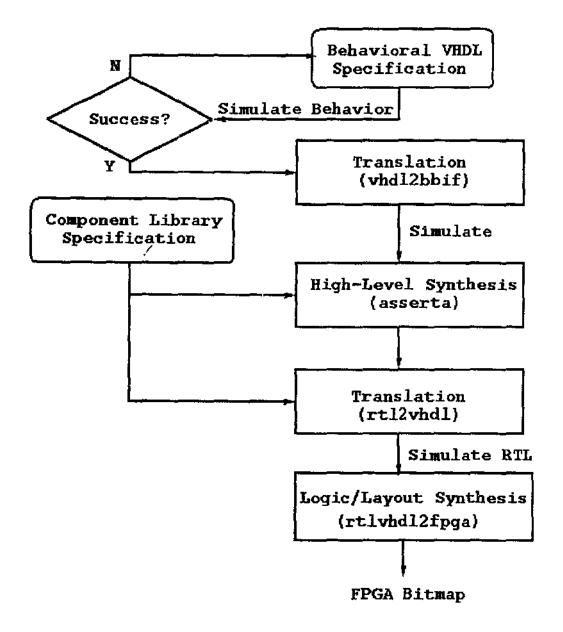

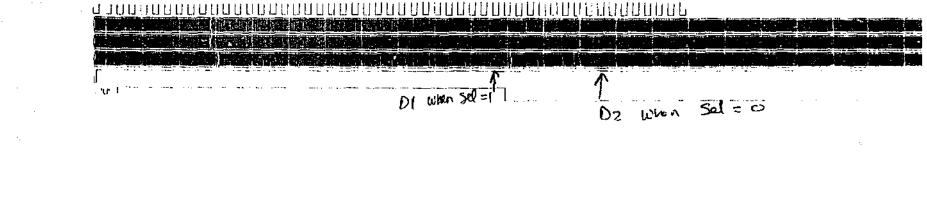

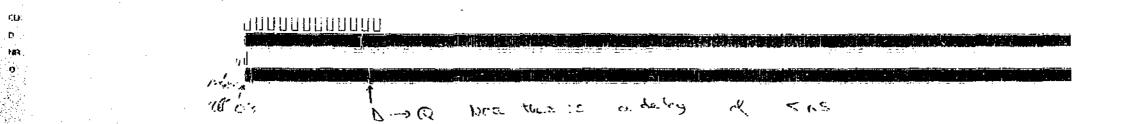

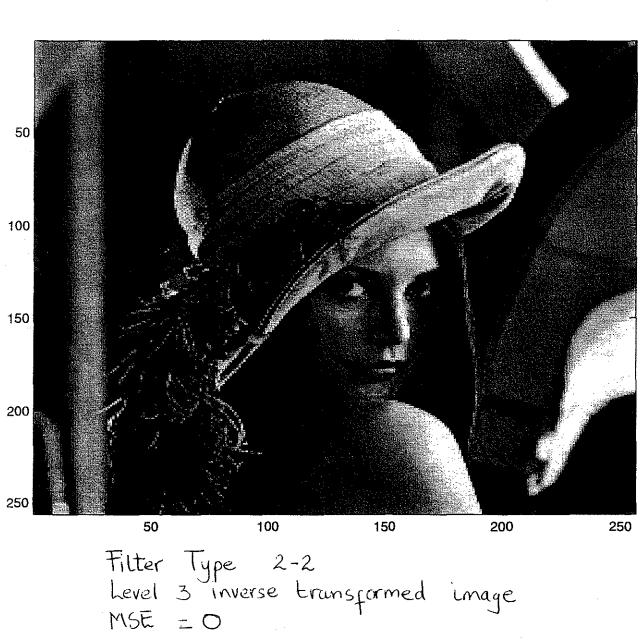

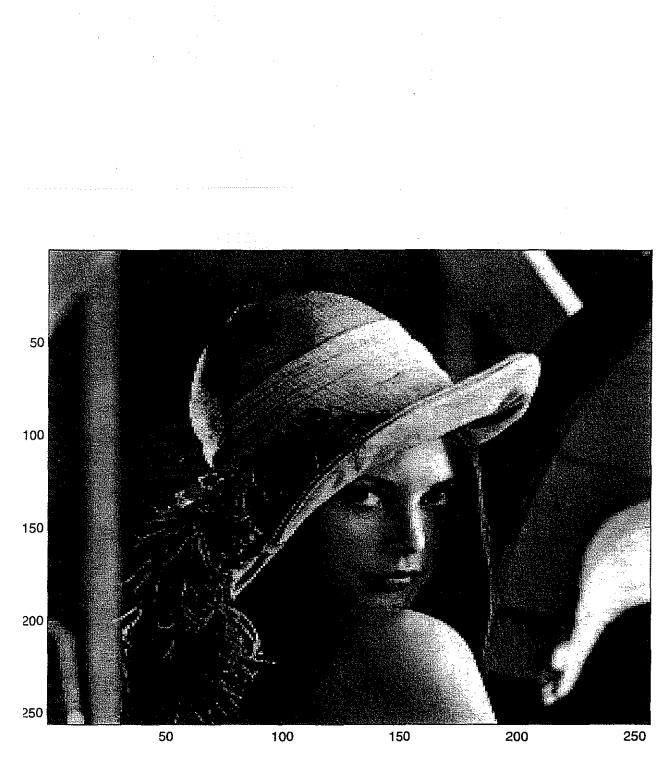

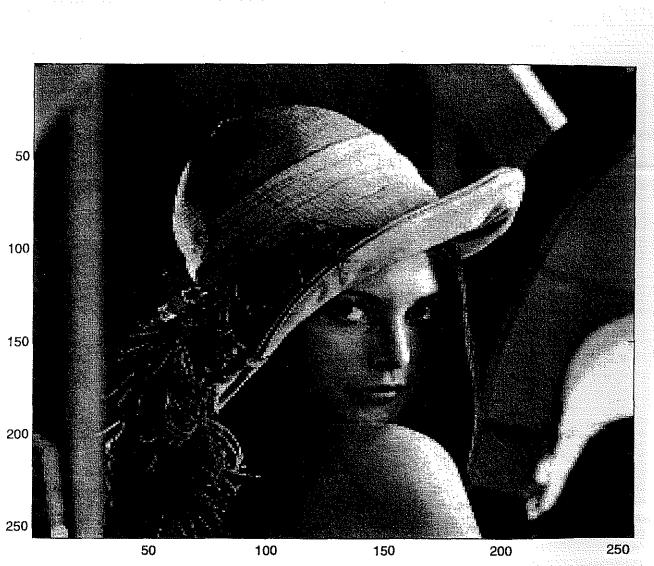

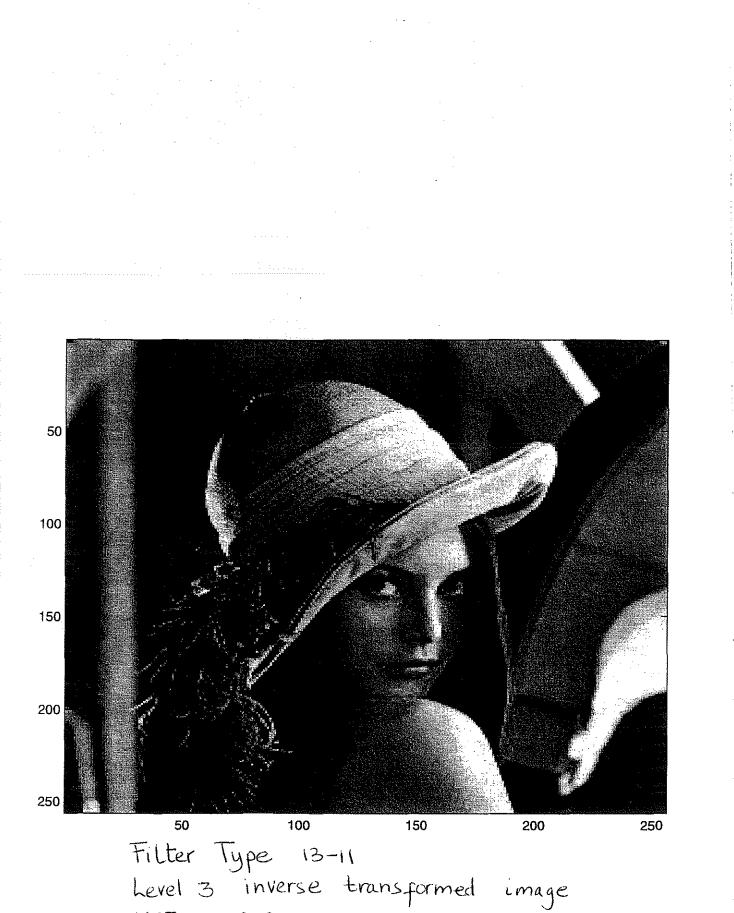

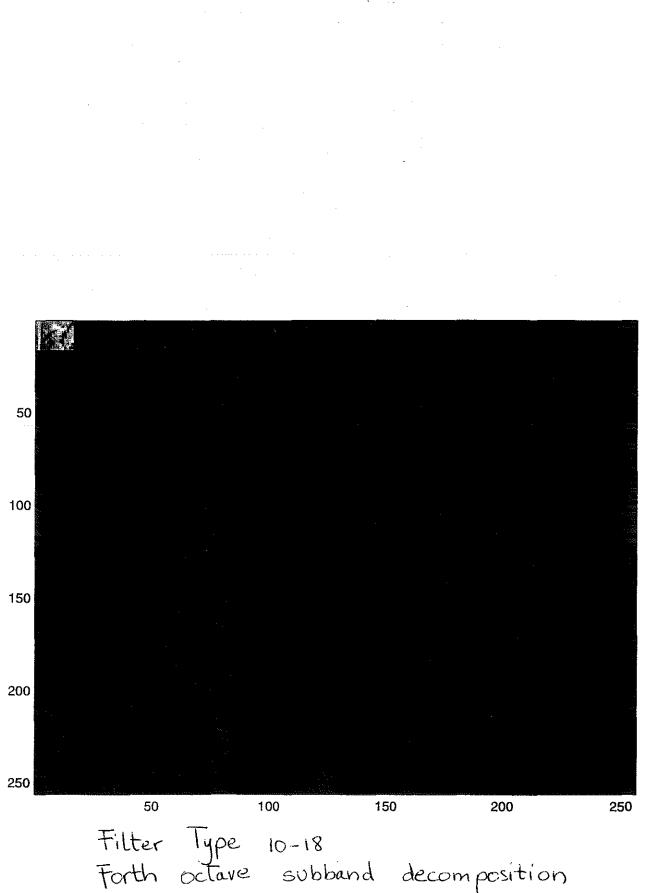

Furthermore, Systolic designs are typically highly pipelined, providing a high throughput for image coding applications. The architecture shown in figure 5.1 implements the 1D DWT and requires a transposition memory to fully implement the 2D DWT. In other words, to implement the 2D DWT transform, two modules (one for row transform and another for column transform) are used along a transposition memory [33]. Much scheduling is required if the 2D DWT is to be achieved by this architecture, hence most systolic designs are employed in one dimensional architectures.