Edith Cowan University Research Online

ECU Publications Pre. 2011

2005

# A Robust QR based detector for V Blast and its efficient hardware implementation

Fariborz Sobhanmanesh University of New South Wales, Sydney

Saeid Nooshabadi University of New South Wales, Sydney

Daryoush Habibi Edith Cowan University

Follow this and additional works at: https://ro.ecu.edu.au/ecuworks

Part of the Engineering Commons

# 10.1109/APCC.2005.1554093

This is an Author's Accepted Manuscript of: Sobhanmanesh, F., Nooshabadi, S., & Habibi, D. (2005). A Robust QR based detector for V Blast and its efficient hardware implementation. Proceedings of Asia Pacific Conference on Communications. (pp. 421-424). Perth. IEEE. Available here

© 2005IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This Conference Proceeding is posted at Research Online.

https://ro.ecu.edu.au/ecuworks/3000

# A Robust QR-based Detector for V-BLAST and its Efficient Hardware Implementation

Fariborz Sobhanmanesh<sup>\*</sup>, Saeid Nooshabadi<sup>\*</sup>, Daryoush Habibi<sup>+</sup>

\*School of Electrical Engineering and Telecommunication University of New South Wales, Sydney, Australia Email: <u>f.sobhanmanesh@student.unsw.edu.au</u>, saeid@unsw.edu.au

+School of Engineering & Mathematics, Edith Cowan University, WA Australia d.habibi@ecu.edu.au

Abstract: The use of multiple antennas at both transmitting and receiving sides of communication channel has increased the spectral efficiency to near the Shannon bound. However algorithmic complexity in the realization of the receiver is a major problem for its hardware implementation. In this paper we investigate a near optimal algorithm for V-BLAST detection in MIMO wireless communication systems based on QR factorization, offering remarkable reduction in the hardware complexity. Specifically, we analyze some hardware implementation aspects of the selected algorithm through MATLAB simulations and demonstrate its robustness. This technique can be used in an efficient fixed point VLSI implementation of the algorithm.

#### 1. INTRODUCTION

In recent years several new techniques have been developed to increase the data transmission rate in wireless data communication. To achieve higher data rates, efficient use of the available radio spectrum is essential. The V-BLAST detection algorithm technique for Multiple Input Multiple Output (MIMO) wireless communication systems [1] increases spectral efficiency to near the theoretical Shannon bound. However its complex receiver makes it unsuitable for low-power VLSI implementation. Several alternative algorithms and architectures for V-BLAST detection are proposed to reduce its complexity [2, 3]. For a suitable V-BLAST detection implementation, its algorithmic, arithmetic and architectural aspects require careful consideration. At the algorithmic level the numerical stability and robustness should be considered. At the arithmetic level signal At the architectural level quantization is important. parallelism and pipelining require attention.

In this paper we investigate the use of 1-pass QR factorization of the channel transfer matrix for VLSI hardware implementation. By suitable modification in the QR factorization technique we attempt to resolve the problem of numerical instability associated with the division based back substitution [4], while maintaining acceptable performance. We have selected the CORDIC method for

implementing the QR factorizer in an upper triangular systolic array. Our MATLAB simulations of fixed-point implementation of algorithm point to a possible efficient VLSI hardware implementation.

This paper is organized as follows. The brief system model of the V-BLAST MIMO systems is presented in Section 2. In Section 3 we present the 1-pass QR factorization method and compare it with the 2-pass QR algorithm [3] using simulation. In Section 4 we analyze some parameters of the proposed architecture based on CORDIC engine for the selected 1-pass QR factorization algorithm. We investigate the effects of these parameters on the final BER through MATLAB simulations. Section 5 provides the conclusions of this paper.

# 2. V-BLAST SYSTEM OVERVIEW

At the transmitter side of a MIMO system a single data stream is demultiplexed into M sub streams and each sub stream is encoded independently into the symbols from the same constellation set ( $\Omega$ ) and then fed to its dedicated transmit antenna. At each symbol time a vector  $S = (s_1, s_2, ..., s_M)^T$ , with each symbol  $s_i$  belongs to the QPSK constellation, is sent to the receiver through a rich scattering quasi-static flat fading wireless channel. The received signal  $r_i$  at the *i*<sup>th</sup> receiving antenna for that symbol time is a noisy superimposition of the M transmitted signals contaminated by AWGN, given by:

$$r_{i} = \sum_{j=1}^{M} h_{ij} s_{j} + n_{i} \quad i = 1, 2, ..., N \quad (1)$$

where  $h_{ij}$  is the channel fading between transmitter *j* and receiver *i*, which is a complex Gaussian random variable with zero mean and variance of 0.5 for the real and imaginary components, and  $n_i$  is the complex Gaussian white noise with zero mean and variance  $\sigma^2$ .

Because of the quasi-static flat fading nature of the channel we can assume that the channel transfer matrix is constant over a block time of L symbol duration and changes randomly after each block time. The rich scattering condition of the channel is well satisfied in indoor environments [5] with a number of scattering sources around the transmitter or receiver. The system in Eq. (1) can be expressed in matrix form as:

$$\mathbf{r}_{N^{*1}} = H_{N^{*M}} S_{M^{*1}} + \mathbf{n}_{N^{*1}}$$

(2)

Among the MIMO algorithms, Maximum Likelihood (ML) detector algorithm is considered to the best performing and computationally the most complex one. V-BLAST OPT [6] however is generally recognized as the optimum detector for MIMO. The original V-BLAST algorithm uses 4 operation steps, ordering, nulling, slicing and cancellation, to detect the transmitted signals [6].

#### 3. QR FACTORIZATION BASED METHOD

The repeated pseudo inverse matrix computation in the ordering step of the original V-BLAST is the main computational bottleneck of the algorithm [2]. To overcome this problem other alternative methods, with acceptable performance and minimal degradation, have been proposed [2, 3]. Algorithm based on the 2-pass QR detection is claimed to be 4 times less complex than the V-BLAST OPT algorithm while achieving comparable performance [3]. In this technique the channel matrix H is first arranged in decreasing column norm order. Such arrangement of columns ensures that signals are detected in the increasing and decreasing orders of their signal to noise ratios for subsequent pass one and pass two of QR factorization algorithm, respectively. Next, the 2-pass QR algorithm employs QR factorization twice with upper and lower triangularized channel matrices. Subsequently, Symbol Interference Cancellation (SIC) detection method is used to detect the transmitted symbols in the increasing and decreasing orders of their signal to noise ratios, by the backward and forward substitutions in upper and lower triangular channel matrices, respectively. It then averages the soft values of the detected symbols from the two passes to estimate symbols. For QAM constellation with q >4, we only require to employ 1-pass QR factorization, with backward substitution to detect the transmitted symbols in the decreasing order of their signal to noise ratios, to achieve satisfactory performance [3].

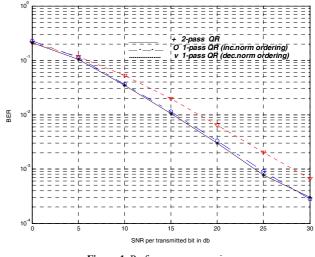

In our analysis we apply the 1-pass QR factorization detection algorithm to a  $4 \times 4$  channel matrix. The channel matrix is sorted with respect to its column norms in the increasing order. The transmitted signals come from the uncoded QPSK constellation set. Subsequently, we apply the backward substitution SIC with hard decision to upper triangular channel matrix. The hard decision technique further simplifies the hardware design. Our simulation results in Fig 1 indicate that the BER performance of the 1-pass QR

factorization with optimum ordering (increasing column norms) is very close to the 2-pass QR factorization in [3] with half the computational complexity.

Fig. 1 also shows the degraded BER performance for the worst case ordering (decreasing column norms). We can therefore conclude that the 1-pass QR factorization with increasing column norms order with hard decision provides a satisfactory performance with a complexity 8 times less than the V-BLAST OPT algorithm [3]. This makes the QR factorization an attractive technique for VLSI hardware implementation.

Figure 1. Performance comparison

#### 4. VLSI HARDWARE IMPLEMENTATION

Towards the goal of VLSI hardware implementation of the above algorithm, we have carried out the architecture design of the 1-pass QR factorization detection technique. In addition we analyzed some of the parameters influencing its hardware implementation through a set of MATLAB simulations.

# 4.1. Architecture

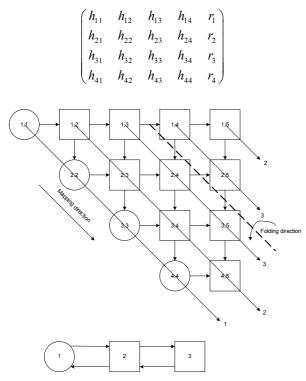

Our architecture for QR factorization is based on the triangular systolic array of Fig. 2 [7]. These array processors are CORDIC-based engines. Since not all of these processors are operating simultaneously, we can increase the efficiency of hardware utilization by mapping these 14 processors to 3 processors by time multiplexing and scheduling. This is achieved through a mapping and folding procedure indicated in Fig. 2 [8].

The first processor generates the given rotations for 4 boundary processors and the second and third processors do the given rotations on the channel transfer matrix and the received vector to make the upper triangular matrix. The input to this triangular systolic array is the channel matrix augmented by the received vector column as shown below.

Figure 2. Triangular systolic array

The processors are made of 2-stage CORDIC engines [10] for annihilating the sub diagonal entries of the channel matrix. The first stage CORDIC (*θ*-CORDIC) in processor 1 vectorizes the channel matrix entries (e.g.  $h_{41}$  and  $h_{31}$ ) by rotation in the complex plane to real numbers. It also keeps the record of the rotation angle  $\theta$  for each vectorization. In doing so it only keeps a record of the signs of the microrotations. This removes the need for large ROM for angle storage and simplifies the hardware complexity to a shift register buffer. The second stage CORDIC (*\varphi*-CORDIC) engine in processor 1 accepts two real numbers (e.g.  $h_{41}$  and  $h_{31}$ ) and annihilates one of them ( $h_{41}$  for upper triangular matrix) through vectorization while saving the other one  $(h_{31})$ for the next annihilation with vectorized  $h_{21}$ . The required rotation angle for annihilation is also calculated in the same manner as in the first stage CORDIC engine. These simple formatted angle information are passed horizontally to the second and the third processors to perform the same rotations on the corresponding row entries (e.g.  $h_{42}$ ,  $h_{43}$ ,  $h_{44}$ ,  $r_4$  for  $h_{41}$ ).

We have optimized the CORDIC engines for our specific application with respect to compensation gain, number of CORDIC iterations and also size of word-length for the variables.

#### 4.2. CORDIC compensation gain

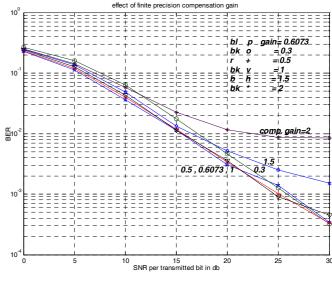

The CORDIC engine used for the rotation of vectors has a gain of k = 1.6473 [9]. To compensate for this gain, the rotated vector coming out of each CORDIC rotator should be

multiplied by the compensating scale factor of  $k^{-1} = 0.6073$ . The hardware multiplier required for this scaling factor is a major concern for the VLSI implementation design. We have simulated our V-BLAST architecture in MATLAB with different values of the compensating scale factor. The simulation results are shown in Fig. 3. The results show that this architecture is very robust with respect to variations in the scaling factor  $k^{-1}$ . For values of  $k^{-1}$  in the range of 0.5 to 1.0, the BER curves nearly match each other. However, for values outside this range, e.g. 0.3, 1.5 or 2.0, the performance is degraded severely. The compensating scale factor of 0.5 is selected for hardware implementation. This simplifies to 1-bit right shift through hardwiring. This choice of  $k^{-1}$  simplifies our hardware greatly.

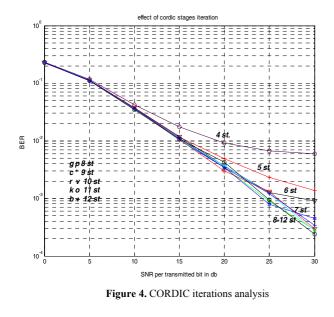

#### 4.3. Number of CORDIC iterations

Another parameter which we analyze for hardware optimization is the number of CORDIC iterations in each CORDIC engine and its influence on BER. The simulation results are present in Fig. 4. As shown in that Figure, CORDIC iterations of 4 to 6 do not offer good performance. However CORDIC iterations in excess of 7 will provide the same level of performance. To simplify the controller hardware for CORDIC rotator, we have chosen an iteration value of 8 for the CORDIC engines.

Figure 3. Compensation gain analysis

# 4.4. Word length analysis

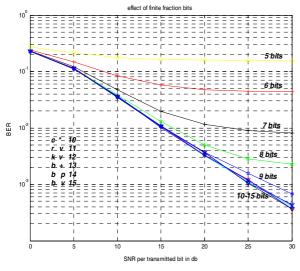

The third parameter that influences the VLSI hardware implementation cost and performance is the number of fractional bits that is required for signal representation. We have analyzed several values for the number of fractional bits for the representation of the channel transfer matrix entries, received vector components and intermediate results of CORDIC iterations. The results for values ranging from 8 to 15 bits are shown in Fig. 5.

As shown in Fig. 5, 10 to 15 fractional bits offer almost identical performances, while the performance with less than 10 fractional bits is degraded considerably. A value of 10 fractional bits can be considered to be optimum for the fixed-point representation of our system variables.

# 4.5. Back substitution SIC

After QR factorization of the channel matrix the back substitution SIC is used to estimate the transmitted signals. Numerical instability of division based back substitution

Figure 5 - Finite word length analysis

technique is a major problem associated with SIC technique [4]. To overcome the instability problem of division based

back substitution, we bypass the division operation by doing a pre-rotation on the incoming channel transfer matrix and using hard decision function. The pre-rotation makes all the diagonal entries of the upper triangular matrix R positive numbers, hence by using hard decision function we do not need any division. We can estimate the transmitted signal by simply considering the sign of the accumulated sum in the backward substitution SIC step. This method reduces the hardware complexity substantially, while maintaining an acceptable level of performance.

#### 5. CONCLUSION

In this paper we have studies the QR factorization method for V-BLAST detector from the hardware implementation point of view for a 4 transmitting, 4 receiving antenna MIMO wireless system. We have investigated and optimized some important parameters that influence the systolic array implementation of this system. They include optimization of the compensation gain factor, number of CORDIC iterations, and word-length. These optimizations provide robustness and acceptable BER, while offering simple VLSI hardware implementation.

#### REFERENCES

[1] G. J. Foschini: "Layered space-time architecture for wireless communication in fading environments when using multiple antennas", Bell Labs. Tech. J., vol. 2, Autumn 1996.

[2] Babak Hassibi: "An efficient square-root algorithm for blast", Conference Record of the Thirty-Fourth Asilomar Conference on Signals, Systems and Computers, 2000, Pacific grove, CA, U.S.A., pp. 1255-1259

[3] M. O. Damen, K. Abed-Meraim, and S. Burykh: "Iterative QR detection for blast", Journal of Wireless Personal Communications, vol. 19, issue 3 pp. 179 - 191, 2001.

[4] Zhan Guo and Peter Nilsson: "A Low-Complexity VLSI Architecture For Square Root MIMO Detection", in proceedings of IASTED CSS'03, Cancun, Mexico, May, 2003.

[5] G. J. Foschini and R. A. Valenzuela: "Initial estimation of communications efficiency of indoor wireless channels," Wireless Networks, vol. 3, no. 2, pp. 141–154, 1997.

[6] G. D. Golden, G. J. Foschini, R. A.Valenzuela, and P. W. Wolniansky: "Detection algorithm and initial laboratory results using V-BLAST space time communication architecture", IEE Elect. Letters, vol 35, no. 1, Jan. 1999.

[7] Y. Kung:" VLSI Array Processors", Englewood Cliffs, New Jersey: Prentice Hall, 1988.

[8] Ning Zhang, Bruno Haller, Bob Brodersen: "Systematic architecture exploration for implementing interference suppression techniques in wireless receivers", IEEE Workshop on Signal Processing Systems, SiPS 2000, Oct. 2000, pp. 218 – 227.

[9] R. Andraka: "A survey of CORDIC algorithms for FPGA based computers", FPGA 98, proceedings of the 1998 ACM/SIGDA sixth international symposium on Field Programmable Gate Arrays, Feb. 1998, Monterey, CA, pp. 191-200.

[10] C. M. Rader: "VLSI systolic arrays for adaptive nulling", IEEE Signal Processing Magazine, Vol 13,No 4, 1996, pp. 29-49