# Edith Cowan University Research Online

ECU Publications Pre. 2011

2002

# Image capture using integrated 3D SoftChip technology

Stefan Lachowicz Edith Cowan University

Alexander Rassau Edith Cowan University

Geoffrey Alagoda Edith Cowan University

Kamran Eshraghian Edith Cowan University

Myung-ok Lee Dongshin University, Korea

See next page for additional authors

Follow this and additional works at: https://ro.ecu.edu.au/ecuworks

Part of the Engineering Commons

## 10.1109/HSNMC.2002.1032389

This is an Author's Accepted Manuscript of: Lachowicz, S. W., Rassau, A. M., Alagoda, G. N., Eshraghian, K., Lee, M., & Lee, S. (2002). Image capture using integrated 3D SoftChip technology. Proceedings of 5th IEEE International Conference on High Speed Networks and Multimedia Communications. (pp. 19-23). Korea. IEEE. Available here © 2002 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

This Conference Proceeding is posted at Research Online.

https://ro.ecu.edu.au/ecuworks/4202

# Authors

Stefan Lachowicz, Alexander Rassau, Geoffrey Alagoda, Kamran Eshraghian, Myung-ok Lee, and Seung-Min Lee

# Image Capture Using Integrated 3D SoftChip Technology

Stefan Lachowicz\*, Alexander Rassau\*, Geoffrey Alagoda\*, Kamran Eshraghian\* Mike Myung-Ok Lee\*\*, Seung-Min Lee\*\*

> \* : Centre for Very High Speed Microelectronic Systems Edith Cowan University, JoondalupWA 6027, Australia Tel: +61 8 9400 5580, E-mail: s.Lachowicz@ecu.edu.au

\*\* : School of EE, Information and Communication Eng., Dongshin University

252 Daeho-Dong, Naju, Chonnam 520-714, Korea

Tel: +82-61-330-3195, E-mail: mikelee@white.dongshinu.ac.kr

#### Abstract

Mobile multimedia communication has rapidly become a significant area of research and development constantly challenging boundaries on a variety of technological fronts. The processing requirements for the capture, conversion, compression, decompression, enhancement, display, etc. of increasingly higher quality multimedia content places heavy demands even on current ULSI (ultra large scale integration) systems, particularly for mobile applications where area and power are primary considerations. The system presented in this paper is designed as a vertically integrated (3D) system comprising two distinct layers bonded together using Indium bump technology. The top layer is a CMOS imaging array containing analog-to-digital converters, and a buffer memory. The bottom layer takes the form of a configurable array processor (CAP), a highly parallel array of soft programmable processors capable of carrying out complex processing tasks directly on data stored in the top plane. Until recently, the dominant format of data in imaging devices has been analog. The analog photocurrent or sampled voltage is transferred to the ADC via a column or a column/row bus. In the proposed system, an array of analog-to-digital converters is distributed, so that a one-bit cell is associated with one sensor. The analog-to-digital converters are algorithmic current-mode converters. Eight such cells are cascaded to form an 8-bit converter. Additionally, each photosensor is equipped with a current memory cell, and multiple conversions are performed with scaled values of the photocurrent for colour processing.

## **1** Introduction

In the span of a few years, mobile multimedia communication has rapidly become a significant area of research and development constantly challenging boundaries on a variety of technological fronts. The pending roll-out of the 3G (3rd generation) and 4G (4th generation) wireless communications networks is further driving this development with the expectation for ever increasing levels of media rich content. The processing requirements for the capture, conversion, compression, enhancement. decompression. display. etc. of increasingly higher quality multimedia content places heavy demands even on current ULSI (ultra large scale integration) systems, particularly for mobile applications where area and power are primary considerations. In order to fully realise the capabilities promised by the 3G and 4G networks new enabling technologies are needed to facilitate the next generation of personal communications devices [1, 2]. In addition to the requirements for very low power, compact size and realtime processing, the rapidly evolving nature of telecommunications networks means that flexible soft programmable systems capable of adaptation to support a number of different standards and/or roles in the overall mobile communication system become highly desirable. Although fully software driven solutions for these problems could be developed, it is unlikely within current technological limitations that such solutions would be able to meet the requirements for very low power realtime processing.

The proposed system is designed as a vertically integrated (3D) system [3] comprising two distinct layers. The top layer takes the form of a transducer array, in this case a CMOS imaging array. Additionally this array will include a massively parallel, interconnected frame/state buffer memory allowing for very high speed data manipulation within the plane. Current active pixel sensors (APS) are focused on front-illuminated architectures, where the sensors and the signal processing circuitry are integrated in the same plane. The main feature of the APS concept is that each pixel includes a photosensor and a read-out circuit, which processes the photocurrent or photovoltage. To increase the fill-factor and thus the spatial resolution the die area used for a sensor should be maximized leaving a very limited space for the circuitry. Up till now the dominant format of data in imaging devices is still analog. The analog photocurrent or sampled voltage is transferred to the ADC via a column or a column/row bus. The first fully digital pixels have been reported in [4,5,6,7]. The pixels from [4,6,7] are characterized by very low fill factor and

0-7803-7600-5/02/\$17.00©2002 IEEE

relatively high pitch as the amount of circuitry required is significantly larger than in the case of the APS. However, the pixel level A/D conversion potentially offers higher SNR than chip or column level A/D conversion, and a dramatic reduction of power dissipation, brought about as a result of parallelizing the processing and reducing the clock speed [5]. In the proposed system, an array of analog-to-digital converters is distributed, such that a one-bit cell is associated with each sensor. The analog-todigital converters are algorithmic current-mode converters. Eight such cells are cascaded to form a full 8bit converter. Additionally, each photosensor is equipped with a current memory cell, and multiple conversions are performed with scaled values of the stored photocurrent for colour processing.

The bottom layer will take the form of a configurable array processor (CAP), a highly parallel array of soft programmable processors capable of carrying out complex processing tasks directly on data stored in the top plane via Indium bump interconnects [8,9]. Each of these processors includes its own embedded memory, along with a high precision ALU and instruction decoder. Software programmed instructions are sent globally to all processors from separate on-chip RAM. Transforms and other processing (e.g. modified discrete cosine transform, motion estimation, edge detection, etc.) are then carried out according to these software instructions on the highly parallel array allowing for very high speed data manipulation and throughput at low clock speed. A high efficiency bus architecture is implemented to interconnect the parallel array processors for rapid extraction or insertion of data. The resulting system is very flexible due to the programmable nature of the CAP and very efficient due to the vertical interconnects and parallelization and thus theoretically very low power, yet capable of highly complex real-time processing tasks. These features make the system ideal for mobile multimedia type applications and, as all components are based on standard CMOS technologies, it should also be suitable for low cost consumer products.

This paper details the architecture of the top level sensor array concentrating on the design and performance of the analog-to-digital converter array.

## 2 Indium bump technology

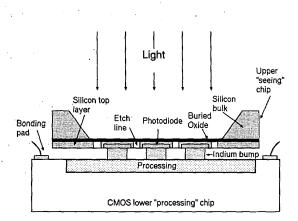

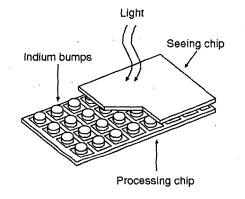

The Indium bump technology allows the realization of a system comprising two CMOS chips, as shown in Figure 1. The upper layer – the "seeing" chip, contains an array of photodetectors and AD converters, the lower one – the "processing" chip, includes the low power configurable array processor, as shown in Figure 2.

As the chips are bonded face-to-face, it is not possible to conventionally illuminate the "seeing" chip from the front side, but only from the backside of the chip. To achieve this it is thinned by silicon bulk micromachinning to approximately  $150 - 300 \,\mu\text{m}$ . Using anisotropic etching the wafer is further thinned to the final thickness of several microns.

Figure 1 Two chips bonded by means of Indium bumps

The pixel pitch, determined by the current capabilities of Indium bump technology, is approximately 20  $\mu$ m. However, the actual pixel size in the proposed system is larger than the minimum – approximately 50  $\mu$ m × 50  $\mu$ m, so that the sensor and the additional circuitry in the top layer can be accommodated in 0.18  $\mu$ m technology.

Figure 2 Physical construction of the array

### **3** The seeing chip architecture

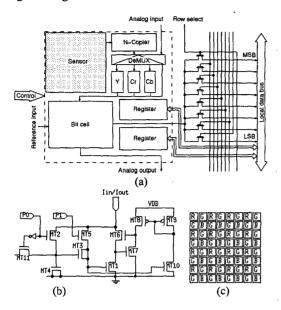

The top level chip is a sensor array containing the sensor itself, analog-to-digital converters, and a buffer memory as presented in Figure 3.

The high-accuracy current memory cell used can be found in [13] and is depicted in Figure 3(b).

A standard RGGB Bayer pattern filter is applied over the photodiode array for full colour capture. For conversion to YCrCb colour-space the captured R, G or B values in each pixel must be appropriately weighted and interpolated. The scaling is realized using current mirror scaling circuits prior to A/D conversion. The appropriately scaled values from R, G and B pixels can then be interpolated to their Y, Cr or Cb equivalents using a simple digital manipulation. The analog current copier storage cell allows the interpolation/conversion for each of these colour components to be carried out sequentially without any requirement for additional digital storage.

Figure 3 Image capture layer architecture: (a) The pixel structure (b) Current memory cell (c) RGGB Bayer pattern

#### 4 Distributed algorithmic currentmode analog-to-digital converter

#### 4.1 General structure

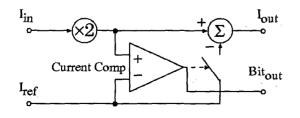

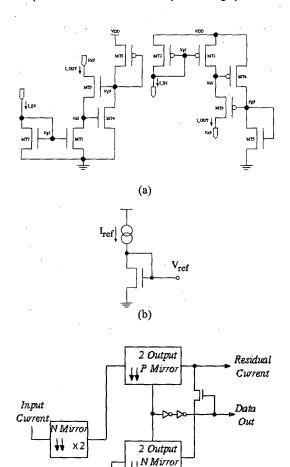

Current-mode algorithmic analog-to-digital converters are characterized by a very small amount of silicon area required and relatively simple hardware. A block diagram of the 1-bit converter is shown in Figure 4. The circuit operates as follows. The input current  $I_{in}$  is first multiplied by 2 and then compared with the reference current  $I_{ref}$ . If the signal  $2I_{in}$  is less than  $I_{ref}$  the digital output goes low and an output current  $2I_{in}$  is produced. However, if  $2I_{in}$  exceeds  $I_{ref}$  the digital output goes high, the switch will be closed and an output current of  $2I_{in} - I_{ref}$ is produced. An N-bit converter is obtained by cascading N 1-bit cells connecting the analog output with the analog input of the following cell.

# Figure 4 A bit cell for one bit A/D algorithmic conversion

An implementation of the above scheme using simple current mirrors, cascoded mirrors as well as active mirrors has been presented by Nairn et al. in [10,11]. It has been demonstrated that in the simple implementation, the accuracy of the subtracting block is the primary source of error, especially if the input current  $I_{in}$  is very close to the  $I_{ref}$ . The cascoded mirror implementation solves this problem, but the consequent reduction of the dynamic range of the  $\times 2$  block is detrimental, and to achieve the same 8-bit accuracy the supply voltage needs to be increased.

One highly advantageous property of this type of converter is the absence of control signals. No external lines are required except for the input current and reference voltage, output digital bit lines and the power supply.

#### 4.2 Regulated cascode mirror implementation

An implementation of the algorithmic 1-bit converter from Figure 3, using regulated cascode current mirrors is shown in Figure 5(a). Figure 5(b) presents the generation of the reference signal to be distributed for all one-bit cells.

The negative feedback in the regulated cascode mirrors provides an extremely high output resistance and also a small minimum output voltage (for the n-type mirror), which is equal approximately to a single saturation voltage of the transistor. This allows the use of such mirrors effectively in submicron technologies where the transistor output resistance in saturation and the power supply voltage are relatively low. Moreover, the transistors do not need to be very long, as opposed to the case of the simple mirror implementation where the transistor length is used to achieve high output resistance. However, the gate area must still be kept relatively large for sufficient  $V_T$  matching.

The current comparator in the converter is implemented as a cascade of two inverters where the first inverter operates as an integrating current-to-voltage converter providing filtering of the power supply noise.

The converter combines the advantage of precision subtraction of cascode mirrors with the high dynamic range of simple mirrors. It is also worth noting that the converter does not use any capacitors, linear or MOS, and the components used are fully compatible with a standard digital process.

#### 4.3 Distributed converter architecture

Eight active bit-cells form a distributed A/D converter and each bit cell in the array can remain in one' of the three states: selected cell, subordinate cell or inactive cell. In addition to the single-bit cell from Figure 4, the pixel requires configuration circuitry to enable the formation of the 8-bit cascade, sliding down the array according to the row select signal. In the selected cell the input current is the scaled copy of the photocurrent captured from the sensor associated with the bit-cell. In the subsequent 7 subordinate cells the input current is the output residue current from the previous cell. In the inactive cell, the input current is zero, and subsequently the power dissipated in an inactive cell is only the leakage power.

(c) **Figure 5** (a) Cascoded n-, and p-type mirrors, (b) the reference signal generation, (c)block diagram of the bit cell.

Reference

Referring to Figure 3, in the first step, the photocurrent is stored in the current memory cell. Subsequently, during A/D conversion, when the cell is selected, the current memory cell is connected to the input of the bit cell through a mirror scaling the current value for a particular colour component, and the digital output is connected to MSB of the local data bus. When the cell is subordinate, the bit cell is connected to the analog input, hence connecting the bit cell input to the output current of the cell immediately above and the digital output to one of the other bit lines in the data bus. When the cell is inactive the analog input of the bit cell and the digital output are disconnected. The interconnect in the eight pixels at the bottom of each column is slightly different in order to account for the "wrap-around".

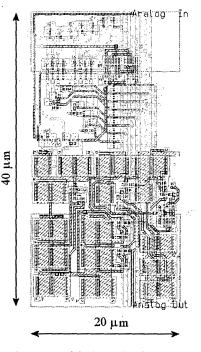

Figure 6 Layout of the bit cell and part of control circuitry

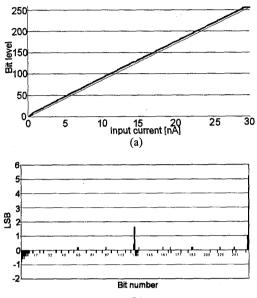

The layout of the bit cell together with a part of control circuitry is presented in Figure 6. The operation of the converter has been simulated using the models of the UMC 0.18 µm technology and the circuit performs as expected, as shown in Figure 7. The power dissipated by a cluster of 8 bit cells depends on a particular input current value, but does not exceed 15 µW (~2 µW per bit cell). Therefore, the power dissipation of a sensor array implementing CIF format (352 × 288) will be approximately 5.3 mW, excluding the power dissipated by the registers. The converter is also characterized by an absence of switching activity during the conversion process, as opposed to other reported pixel-level A/D converters [4,6] based on counting and/or oversampling. This property should significantly reduce the level of noise in the converted signal. In the worst case, the conversion time of the converter does not exceed 5 µs, which for the CIF format yields the maximum frame capture time of 5 ms consisting of three conversions of the scaled photocurrent for colour processing.

#### **5** Conclusions

A novel image capture system using 3D Soft-Chip CMOS technology has been described. It is characterized by a moderate fill factor of the order of 20%. The implemented architecture of the algorithmic analog-todigital converter provides for pixel-level digital readout. The conversion is performed in parallel in all columns of the sensor allowing for a significant reduction of the speed required for the scanning process. Moreover, there is very little switching, compared with the existing pixellevel AD converters employing counting and/or oversampling, yielding very low power dissipation for the sensor array. Further work will include the noise analysis of the proposed converter architecture and verification of the results obtained from simulation against the data obtained from the experimental chip planned for fabrication in mid-2002.

Figure 7 Operation of the converter simulated in UMC018 technology.

- (a) transfer characteristic

- (b) differential nonlinearity

#### Acknowledgment

The support of Australian Research Council, and Centre for Very High Speed Microelectronic Systems at Edith Cowan University is gratefully acknowledged.

## References

A.M.Rassau, G.Alagoda and K.Eshraghian, "Massively parallel wavelet based video codec for an intelligent pixel mobile multimedia communicator", Proc. of the 5th Int. Sym. On Signal Processing and its Applications, Brisbane, Australia, August 1999.

- [2] A.M.Rassau, G.Alagoda, D.Lucas, J.Austin-Crowe and K.Eshraghian, "Massively parallel intelligent pixel implementation of a zerotree entropy video codec for multimedia communications", Proc. of the IFIP International Conference on VLSI, Lisbon, Portugal, December 1999.

- [3] S. F. Al-Sarawi, D. Abbott and P.D. Franzon, "A review of 3-D packaging technology," IEEE Transactions on Computers, Packaging, and Manufacturing Technology – Part B, Vol. 21, No. 1, pp. 2-14, Feb. 1998.

- [4] B. Fowler, "CMOS area image sensors with pixel level A/D conversion", PhD dissertation, Stanford University, 1995.

- [5] A. El Gamal, D. Yang, and B. Fowler, "Pixel Level Processing -- Why, What and How?", Proceedings of the SPIE Electronic Imaging '99 conference, Vol. 3650, January 1999.

- [6] F. Andoh, H. Shimamoto and Y. Fujita, "A Digital Pixel Image Sensor for Real-Time Readout", IEEE Transactions on Electron Devices, Vol. 47, 2000, pp. 2123-2127.

- [7] K. Eshraghian, S. Lachowicz, G. Alagoda, K. Ang, "Architectural Mappings for Multimedia Smart-Pixel Arrays", Proceedings, IEEE International Workshop on Design, Test and Applications, Dubrovnik, Croatia, June 10-12, 1998, pp. 33-35.

- [8] D. H. Pommerening, D. D. Enders and T.E. Meinhardt, "Hybrid silicon focal plane array development: an update", Proc. SPIE, Vol. 267, pp. 23-30, 1981.

- [9] J. T. Longo, D.T. Cheung, A.M. Andrews, C.C. Wang and J.M. Tracy, "Infrared focal planes in intrinsic semiconductors", IEEE Trans. On Electronic Devices, Vol. 25, pp. 213-232, 1978.

- [10] D.G. Nairn and C.A.T. Salama, "An algorithmic analog-to-digital converter based on current mirrors", Electronics Letters, Vol. 8, 1988, pp.471-472.

- [11] D.G. Naim and C.A.T. Salama, "Current-Mode Algorithmic Analog-to-Digital Converters", IEEE Journal of Solid State Circuits, Vol. 25, 1990, pp. 997-1004.

- [12] D. Macq and P.G.A. Jespers, "A 10-Bit Pipelined Switched-Current A/D Converter", IEEE Journal of Solid State Circuits, Vol. 29, 1994, pp. 967-971.

- [13] C.Wang, M.O.Ahmad and M.N.S. Swamy, "Design and Implementation of a Switched-Current Memory Cell for Low-Power and Weak-Current Operations", IEEE Journal of Solid State Circuits, Vol. 36, 2001, pp. 304-307.