第 20 卷 第 4 期 2010 年 4 月

#### 计算机技术与发展 COMPUTER TECHNOLOGY AND DEVELOPMENT

Vol. 20 No. 4 Apr. 2010

# 基于 FPGA 的 PCI 接口 DMA 传输的设计与实现

# 单天昌.陆 达

(厦门大学 信息科学与技术学院,福建 厦门 361005)

摘 要:PCI 总线是高速同步总线,支持单字段传输和突发传输,突发传输中,写一次地址,传输多个数据段。DMA 技术是一种由 DMA 控制器控制的存储器与外部设备或存储器之间大数据量传输的方法,具有传输速度高,CPU 额外开销小的优点。介绍了一种使用 FPGA 在 32 位 PCI 接口内实现 DMA 块模式传输的设计方法,硬件部分基于 Xilinx Virtex - II Pro™芯片,通过一个 OPB - PCI 总线桥实现了 PowerPC 与主机间的 PCI 接口通信,不仅实现了 PCI 的突发式传输,发挥了 PCI 总线的高性能,而且将 CPU 从繁杂的 I/O 事务中解放出来,解决了原有通信系统中采用中断方式传输的瓶颈,使得 PCI 接口卡与主机间传输效率得到明显改善。

关键词:FPGA;DMA;PCI 总线;FIFO;突发式传输;OPB-PCI 桥

中图分类号: TP39 文献标识码:A 文章编号: 1673 - 629X(2010) 04 - 0215 - 05

# Design and Realization of DMA Transfers in PCI Interface Based on FPGA

SHAN Tian-chang ,LU Da

(School of Info. Sci. & Tech., Xiamen University, Xiamen 361005, China)

Abstract :PCI Bus is a kind of synchronous and high performance bus, supporting burst or single - cycle mode. A burst transfer is one consisting of a single address phase followed by two or more data phases. Direct memory access (DMA) is a means of having a peripheral device control a processor 's memory bus directly. DMA permits the peripheral to transfer data directly to or from memory without having each byte (or word) handled by the processor. Thus DMA enables more efficient use of interrupts, increases data throughput, and potentially reduces hardware costs by eliminating the need for peripheral - specific FIFO buffers. Introduces a design method of realizing block DMA transmission in 32 - bit PCI interface based on FPGA, with the choice of Xilinx Virtex - II Pro TM, realizes data communication between the PowerPC and host by means of a OPB - PCI Bus bridge, not only realizes the burst - mode transmission and embodies the superiority of the PCI bus, but also releases the CPU from the miscellaneous work of I/O, solves the bottleneck of the original communication system, significantly improves the transmission efficiency between PCI interface card and host computer.

Key words: FPGA; DMA; PCI bus; FIFO; burst transfer; OPB - PCI bridge

#### 0 引 言

PCI 总线<sup>[1]</sup> 是高速同步总线,具有 32 位(或 64 位) 总线宽度,工作频率 33MHz(或 66MHz),最大传输速率 132MB/s(或 528MB/s),其独立于处理器的独特设计和高性能、开放性等优势,使其得到迅速普及和发展。PCI 传输分单字段传输和突发传输,突发传输中,写一次地址,传输多个数据段<sup>[2]</sup>。

DMA 技术[3] 是一种由 DMA 控制器完成的存储

收稿日期:2009 - 07 - 13;修回日期:2009 - 10 - 21

基金项目:国家 863 项目(2003AA755024)

作者简介:单天昌(1983 - ),男,山东德州人,硕士研究生,研究方向为基于 FPGA 的飞行通信控制卡中数据的高速通信;陆 达,教授,硕士生导师,研究方向为嵌入式技术,电力系统质量检测。

器与外部设备或存储器之间大数据量传输的方法。在DMA 传输中,硬件设备代替 CPU 接管总线并负责数据传输,省去了由 CPU 负责传输时所必须的寻址指令。DMA 有两种类型:系统 DMA 和总线主控 DMA。总线主控 DMA 通常用在 PCI 设备中。

目前实现 PCI 接口 DMA 传输的有效方案<sup>[2]</sup>分两种: 采用专用的 PCI 接口芯片,如 PCI 9054 等均集成了 DMA 控制模块,只需配置相关参数即可,实现简单,但成本较高。 使用 IP 软核通过可编程逻辑器件 FPGA 实现。这种方案的优点:用户可以根据需要灵活设计 PCI 接口,不会浪费资源;而且用户逻辑和接口部分可以做在同一个器件内,PCI 接口和用户逻辑会结合得更紧密。该设计中采用了第二种方法,使用Xilinx 公司的 Virtex - II 系列 FPGA 来设计 32 位 PCI

接口,同时采用 OPB - PCI IP 核<sup>[4]</sup>实现了 DMA 块模式传输,既发挥出了 PCI 总线的高速传输性能,同时又大量减少了 CPU 处理时间,从两方面保证了接口卡与主机间的高速通信。

# 1 PCI接口整体逻辑结构

#### 1.1 PCI 接□整体逻辑

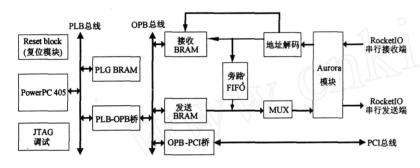

根据 PCI 接口所要实现的功能,将 FPGA 片內逻辑分为两部分: Power PC 405<sup>[5]</sup>处理器嵌入式系统和串行通信接口<sup>[6]</sup>。 PCI 接口总体逻辑如图 1 所示。 Power PC 405 处理器嵌入式系统包含 PLB 总线及 PLB 总线上的设备、OPB 总线以及 OPB - PCI 桥<sup>[4]</sup>;串行通信接口包含接收和发送 BRAM、旁路 FIFO、状态管理寄存器、地址解码器和多路复用即 MUX、以及 Aurora 模块。

图 1 PCI 接口的整体逻辑架构图

该设计中,在 Virtex - II Pro 器件内部构建了一个以 PowerPC 405 处理器硬核为中心的嵌入式计算机应用系统,各功能部件在 FP GA 内部都以 IP 核的形式来构建并连接。其中 Reset block 控制 FP GA 内各模块的 reset 信号的输入输出;J TA G 调试接口用于 J TA G 在线实时逻辑分析,从而验证设计的正确性。 Power PC处理器通过 PLB 总线和 OPB 总线与各外设 IP 核相连,PLB 总线和 OPB 总线之间通过 PLB - OPB 桥相连,PLB 总线和 OPB 总线之间通过 PLB - OPB 桥相连;OPB - PCI 桥实现了 OPB 总线和 PCI 总线之间的通信;为了存储应用程序,系统使用了 16k 字节 PLB总线块 RAM;此外还有二个 8k 字节的 OPB 总线块BRAM 用于存储通信数据,其中,接收存储器用于存储Aurora 核接收到的数据,而发送存储器则用于存储待发送的数据;Aurora 模块实现了设备双方通过 Aurora 链路层协议进行通信。

#### 1.2 传输过程中存在问题及解决方案的提出

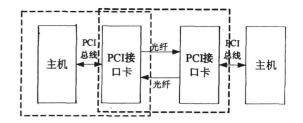

在实际应用中,多台主机通过 PCI 接口卡组成环 状拓扑结构,接口卡之间(中间虚线框部分)通过光纤 进行通信,接口卡之间通信主要是由 Aurora 模块来实 现的<sup>[6]</sup>。图 2 是主机通过接口卡通信。

图 2 主机通过接口卡通信

设计中接口卡间采用光纤进行通信,光纤的传输速率为 1.25 Gbps,由于 Rocket IO<sup>[5]</sup>采用 8B/10B 进行编码,因而实际上传输数据的最高速率应为 125 MB/s。但实际传输过程中,传输速率仅为 3.4 MB/s,要远远小于数据传输的最高速率。分析可知,接口卡之间通过光纤连接,可以在 Aurora 协议的基础上,通过 RocketIO 多吉比特收发器实现高速通信,但接口卡与主机之间(左侧虚线框部分)数据传输速率较低,成为制约

传输性能的瓶颈。经分析,影响数据传输速率的主要因素是 PCI 总线的工作方式。原系统设计中,PCI 总线采用的是单字段传输方式,没有使用突发式传输。

在 x86 结构 CPU 的个人计算机里,由计算机 CPU 发起读操作访问 PCI 目标设备时,计算机并不支持对 PCI 设备的进行突发读操

作,这是由于计算机的 BIOS 将 PCI 设备映射到非 Cache 存储器中,会出现读操作阻塞。对于突发写操作,也存在同样的问题。也就是说在 PC 环境下开发基于 PCI 的产品,PC 机不支持突发传输。为了实现高速的数据传输,就必须在 DMA 模式下操作。文中设计主要针对左侧虚线框部分进行设计,实现接口卡与主机间数据的 DMA 传输。

# 2 DMA 控制模块的设计与实现

要实现 DMA 传输,需要专门 DMA 控制硬件电路模块来支持,该设计中采用了 Xilinx 公司提供的 OPB - PCI 桥 IP 核中的 DMA 控制模块<sup>[4,7]</sup>。

#### 2.1 OPB-PCI桥

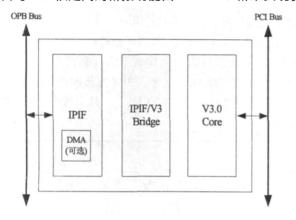

在设计中,基于 POWERPC 的嵌入式系统内系统总线为 CoreConnect 中的 OPB 总线,为了实现 OPB 总线与 PCI 总线之间的数据交换,选用了 Xilinx 公司提供的 OPB - PCI 桥,在 32 位 OPB 总线与 32 位 PCI 总线之间提供完全的桥接功。OPB - PCI 桥结构如图 3 所示。

\* OPB - PCI 桥结构。

OPB - PCI 桥结构[4]主要由三个相对独立的单元

组成: IPIF 接口、IPIF - PCI 桥、PCI 接口。IPIF 接口处理 OPB 总线端的事务,把 OPB 总线事务转化成一种更易于设计、更为简单的接口; PCI 接口逻辑使用了PCI 核(Xilinx LogiCore PCI 32/33 v3.0)来实现高性能、完全符合 PCI 总线规范的 PCI 接口,负责处理 PCI 总线的事务。OPB - PCI 桥使用 PCI 核实现一个简单的 32 位、33 MHz 的 PCI 主设备或目标设备。IPIF 接口与 PCI 核之间的桥接功能由 IPIF - V3 桥来实现。

图 3 OPB - PCI 桥结构

\* OPB - PCI 桥的主要 功能。

由于 OPB - PCI 桥主要 是在 OPB 总线和 PCI 总线 之间进行桥接,因此,它有 如下二个主要功能<sup>[4,8]</sup>:

协议转换功能。对于一个 OPB 主设备访问 PCI 从设备的事务,OPB - PCI 桥能接受来自 OPB 主设备、满足 OPB 总线协议的地址和事务控制信号,并经

协议转换后在 PCI 总线上启动一个符合 PCI 总线协议 的、访问 PCI 从设备的事务。对于 PCI 主设备亦同。

对来自总线设备的数据进行缓存。OPB 总线和 PCI 总线是频率不同的总线,在 OPB - PCI 桥中加入了先进先出缓冲器(FIFO)对数据进行缓存。

\* OPB - PCI 桥的工作模式。

OPB - PCI 桥有两种工作方式<sup>[8]</sup>:主桥方式和从桥方式。作为从桥时,主机系统将扫描 PCI 总线上连接的 PCI 总线设备,然后配置 OPB - PCI 桥的配置寄存器,来完成初始化配置过程。当作为主桥时,PCI 桥完全控制 PCI 总线。在设计中,DMA 模块控制数据传输,OPB - PCI 桥是 PCI 总线上主设备,工作方式为主桥。

包含 DMA 模块的 OPB - PCI 桥主要配置参数如表 1 所示。

表 1 OPB - PCI 桥主要配置参数

| 参数名称                     | 参数值                     |

|--------------------------|-------------------------|

| C_INCLUDE_PCI_CONFIG     | 1:工作方式为主桥               |

| C_ PCIBAR_ NUM           | 2:二个存储器空间               |

| C_PCIBAR2IPIFBAR_0       | 0X81000000:接收存储器的起始地址   |

| C_PCIBAR_LEN_0           | 20:PCI端访问的空间为 1M        |

| C_PCIBAR2IPIFBAR_1       | 0X81100000:发送存储器的起始地址   |

| C_PCIBAR_LEN_1           | 20:PCI端访问的空间为 1M        |

| C - DMA - CHAN - TYPE    | 0:包含 DMA 模块             |

| C. INCLUDE. INTR. MODULE | 1:如果包含 DMA,则必须包含完整的中断模块 |

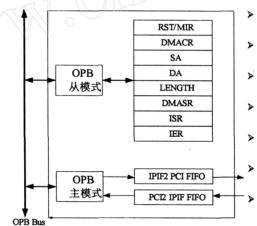

#### 2.2 OPB-PCI 桥中的 DMA 模块结构

DMA 控制模块负责接收计算机的 DMA 请求,接管总线控制权,发送操作时,以 DMA 方式将计算机存储器的数据以块方式读出并写到连接在本地总线的发送存储器,DMA 结束后发出中断通知计算机,然后释放对总线的控制权。在 OPB - PCI 桥中,DMA 控制模块位于 IPIF 接口部分,DMA 分为 Block DMA 模式和S/ G DMA 模式,OPB - PCI 仅支持 Block DMA 模式,DMA 控制模块结构[4]如图 4 所示。

- ▶ DMA 控制寄存器 (DMACR):接受命令, 控制其他功能模块的工作。

- ▶ 源地址寄存器 (SA): 存放交易中的源 地址。

- ➤ 目标地址寄存器 (DA): 存放交易中的 目的地址。

- ▶ 字节数寄存器 (LENGTH): 指定待传输 数据的字节数,采用的是减1操作。

- DMA状态寄存器 (DMASR): 反映DMA操作 状态。

- ▶ 中断状态寄存器(ISR): 为主机提供PCI 设备的中断状态。

- → 中断使能寄存器(IER): 可以屏蔽PCI 设备的中断请求。

#### 图 4 DMA 模块结构图

#### 2.3 DMA 功能实现

#### 2.3.1 DMA 功能

首先 DMA 控制模块处于等待状态,检测 DMA 传输请求,当计算机要求传输数据时就以 DMA START 中断请求,并设置好源地址寄存器、目的地址寄存器、字节数寄存器,然后 DMA 控制模块接受请求,发总线控制申请,当获取 PCI 总线和本地总线双方的控制权后,开始传输数据。一方面它输出源地址给计算机,读出计算机存储器的 N 个字节的数据块,装载到 FIFO中;另一方面,输出目的地址给本地总线上的存储设备,把 N 个字节的数据块从 FIFO 中卸载,写到本地总线。传输结束,DMA 控制模块中断通知计算机,同时释放双方总线控制权[4]。

#### 2.3.2 DMA 传输讨程

以主机通过接收存储器接收数据为例来说明 DMA 操作具体过程,完整的 DMA 操作过程可分为 PCI 总线操作和 OPB 总线操作。在此操作中, DMA 模块首先通过 OPB 总线将数据从接收存储器传到 OPB - PCI 桥内部的 IPIF2 PCI FIFO .然后再通过 PCI 总线操作将数据写人系统 Memory。DMA 控制器在 2 种总线上均为 Master 模式 .OPB - PCI 桥内部的 FIFO 起二总线速率匹配作用。数据在二总线上的操作并没 有直接的关系,仅通过OPB - PCI 桥内部 FIFO 状态实 现控制。

# \* DMA 初始化。

主机要进行 DMA 传输时,先初始化 DMA 控制模 块的寄存器,写源地址寄存器(接收存储器地址),目标

地址寄存器(主机 Memory 地址),字节计 数器(传输数据长度),发DMA START 请求。

#### \* OPB Bus 总线操作。

DMA 控制模块申请并获得 OPB 总线 控制权后,读取接收存储器数据到 OPB -PCI 桥内部的 IPIF2PCI. FIFO。此时 OPB - PCI 桥是 OPB 总线上的主设备。

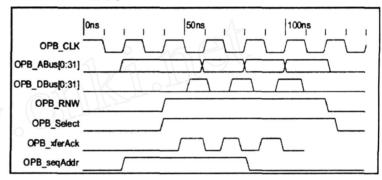

图 5 是 OPB 连续读的 OPB 信号图, 在传输过程中,OPB. seqAddr 输出为高

电平表示接收存储器地址连 续, 多个地址和多个数据分 别出现在 OPB. ABus 和 OPB DBus 上。OPB 总线不 直接支持突发模式,连续的 地址允许 OPB 从设备完成类 似突发模式的传输。下一次 交易的地址就是相同方向的 下一个连续的地址。在连续 交易过程中,OPB 主设备必 须锁定总线,即 M-busLock 信 号有效。

#### \* PCI 总线操作。

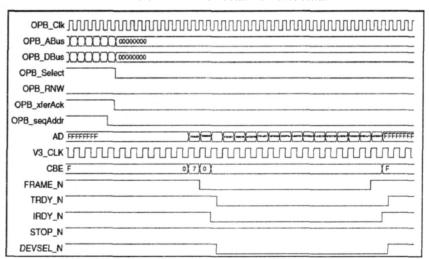

DMA 控制器申请并获得 PCI 总线控制权后,从 OPB - PCI 内部的 IPIF2PCI. FIFO 卸载数据并以 PCI 突发模式将数据写到主机的 Memory。此时 OPB -PCI 桥是 PCI 总线上的主设备。

图 6表示 OPB 向 PCI 突发写时 OPB 和 PCI 总线 的信号。OPB - PCI 桥作为起动方申请并且获得空闲 PCI 总线的访问权。在第一个时钟周期,起动方有效 FRAME. N,并且分别在 AD[31:0]和 CBE[3:0]提供

有效地址和操作命令。在第二个时钟周期,起动方有 效 IRDY. N,将数据写到 AD[31:0] 并且将字节使能 命令写到 CBE[3:0]。当 FRAME. N 有效时,目标设 备解析地址和命令,被选中的目标设备有效 DE-VSEL. N 和 TRDY. N。在第三个时钟周期,起动方和 目标设备采样到有效的 IRDY, N 和 TRDY, N, 写操 作的第一个数据传输开始。FRAME, N 一直保持低 电平有效,表明正在进行多个数据段的突发传送。起 动方在突发传送模式下只写第一个地址。每个目标设 备都包含一个地址计数器, 当开始地址出现在AD[31: 0]上以后,每次传输一个 DWORD,计数器加 4。起动 方通过无效 FRAME. N 来表明突发传输中的最后一 个数据。当 IRDY. N 与 TRDY. N 都无效时,突发传 送结束。

图 5 DMA 控制器读接收存储器

#### 图 6 DMA 控制器写 PCI 目标设备

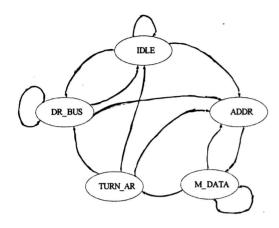

当DMA 控制器作为 PCI 上的主设备,向 PCI 写 数据时,主状态机如图7所示。

IDLE:表示起动方处于空闲状态。

ADDR:表示起动方处于地址阶段,此时有效的地 址出现在 ADIO,有效的命令出现在 M. CBE。

M. DATA: 表示起动方处于数据传输阶段。

DR. BUS: 表示 PCI 总线被锁定在 OPB - PCI 桥

上,此时,起动方负责驱动 ADIO[31:0]以及 CBE, IO [3:0]以及 PAR IO 来避免上述三态总线信号浮空。

TURN. AR:是总线从当前传输恢复到空闲前的 一个转换周期。

图 7 PCI 总线操作主状态机

#### \* FIFO.

在DMA 传输过程中,OPB 总线操作与 PCI 总线 操作,通过 OPB - PCI 桥内的 IPIF2PCI. FIFO<sup>[4]</sup>联系 起来, IPIF2PCI\_FIFO 有一个重要的参数为 C. TRIG. PCI. DATA. XFER. OCC. LEVEL,含义为:启 动向 PCI 目标设备突发模式传输操作的临界值,在 DMA 传输过程中,此参数应设为 16。当 FIFO 达到定 义的临界值时,OPB - PCI 桥发 PCI 总线访问请求。 进入数据段后,只要 PCI 目标设备可以接收,则 OPB - PCI 桥不断向 PCI 总线提供数据,直到 FIFO 为空。

传输过程中如果因为 OPB 侧写 IPIF2PCI\_FIFO 速度慢于 PCI 侧读 FIFO 而导致 FIFO 空 .则 OPB . PC 桥结束 PCI 传输交易。此后,当 IPIF2PCI. FIFO 的 C. TRIG. PCI. DATA. XFER. OCC. LEVEL 参数达 到定义的容量时,OPB - PCI 桥开始新的 PCI 交易,字 节计数器数值减为 0 时,DMA 传输结束。

#### 2.4 性能分析

在文中设计的 DMA 传输中,传输速率约为

$30MB/s_0$

在理想状态下,PCI 总线采用突发模式最快速率 能达到132MB/s,但在实际系统中,很多原因会导致速 率下降,主要包括总线仲裁时间、从设备响应时间、传 输中的意外终止与重试时间。在 DMA 传输过程中, OPB - PCI 桥中的 DMA 控制器要分别申请 OPB 总线 与 PCI 总线的使用权,这大大降低了传输性能,FIFO 控制操作也占用了大量时间,导致实际传输速度仅为  $30MB/s_a$

# 3 结束语

该设计采用 OPB - PCI 桥 IPcore 实现 32 位 PCI 总线与 32 位 OPB 总线间协议的转换,通过桥中的 DMA 控制模块实现了 OPB 存储设备与主机 Memory 之间的 DMA 数据传输,节省了成本,充分利用了资 源,紧凑而高效地实现了系统设计,采用 DMA 方式满 足了数据传输的高速要求,解决了接口卡与主机间传 输过程中的瓶颈问题,使得主机间通信速度得到了大 幅提升。

#### 参考文献:

- [1] Shanley T, Anderson D. PCI 系统结构[M]. 第4版. 刘 晖, 冀然然,夏意军,译,北京:电子工业出版社,2000.

- [2] 李贵山,陈金鹏. PCI 局部总线及其应用[M]. 西安:西安 电子科技大学出版社,2003.

- [3] 曲 红,林争辉,焦孟草,等.基于 PCI 总线的通用 DMA 设 计[J]. 国外电子测量技术,2004(4):17-19.

- [4] OPB PCI v1.02a User Guide Revision v1.02a[S].2006.

- [5] Virtex II Pro TM. Platform FPGA User Guide [M]. [s.1.]: Xilinx ,2004.

- [6] 闵小平,陆 达,洪鸿榕.基于现场可编程门阵列的高速 光纤通信的实现[J]. 厦门大学学报,2007(4):492 - 495.

- [7] PCI Local Bus Specification Revision 2.2[S].1998.

- [8] 吴德铭,陆 达. 高速通信中基于 FPGA 的 PCI 总线接口 研究与设计[J]. 计算机应用,2005(11):2717 - 2719.

(上接第 214 页)

# 参考文献:

- [1] 史 峰,邓连波. 旅客换乘网络优化设计[J]. 铁道科学与 工程学报, 2004,1(1):78-82.

- [2] 萨师煊, 王 珊. 数据库系统原理[M]. 第3版.北京:高 等教育出版社,2000.

- [3] 江 南,史 峰,卢红岩,等. 铁路旅客乘车方案优化决策 模型研究[J]. 铁道学报, 2007, 29(3):13-18.

- [4] 史 峰,马均培,向联慧,等.客运中转径路的换乘模型及

算法[J]. 铁道学报,1999,21(5):1-4.

- [5] 陈 深. 城市公共交通换乘系统研究[D]. 南京:东南大学, 2004.

- [6] 张 彦. 铁路客票中转换乘多径路选择问题的研究[J]. 铁道运输与经济,1997,19(8):11-13.

- [7] 石 雨,杨 浩. 铁路客运专线运营调度系统体系结构 [J]. 中国铁道科学, 2007, 28(1):106 - 112.

- [8] Yen J Y. Finding the K Shortest Loopless Paths in a Network [J]. Mgt. Sci,1971(17):712 - 716.