# 数字直放站中 CPRI 协议的 FPGA 实现

陈岳林1,石江宏2

(1. 厦门大学 福建 厦门 361005;2. 厦门大学 无线通信实验室 福建 厦门 361005)

摘 要:为了开发数字直放站连接系统,介绍 CPRI 协议规范和帧结构,讨论其硬件上的实现方案,给出基于 SCAN25100 的 FPGA 电路模块设计,采用 Verilog 语言设计开发功能模块。该方案具有便于功能扩展、成本低、使用灵活等特点,通过实际测试表明,此方案可进行可靠的数据传输,性能稳定,从而实现了数字直放站和基站之间更有效的互通,扩大了基站的覆盖范围。

关键词:直放站;CPRI;现场可编程逻辑阵列;SCAN25100

中图分类号:TN913 文献标识码:B 文章编号:1004-373X(2009)04-031-04

## Implementation of CPRI Protocol in Digital Repeater on FPGA

CHEN Yuelin<sup>1</sup>, SHI Jianghong<sup>2</sup>

(1. Xiamen University ,Xiamen ,361005 ,China ;2. Wireless Communication Lab ,Xiamen University ,Xiamen ,361005 ,China)

Abstract: To develop the connection of digital repeaters, CPRI protocol specification and frame structure are introduced. Its implementation on hardware is discussed. The detail module design of FPGA circuit and program based on SCAN25100 are elaborated. The design is easy to expand and low cost. The experimental analysis shows that the solution could accomplish the data transmission, and the interconnection between base station and digital repeater are implemented, the network s coverage is enhanced.

Keywords:repeater;CPRI;FPGA;SCAN25100

## 0 引言

随着移动通信的发展,通信网络覆盖范围已经成为衡量通信网络运行的重要标准,直接影响着运营商的经济效益。而直放站的发展应用,已成为提高运营商网络质量,解决网络盲区或弱区问题,增强网络覆盖的主要手段之一。一个基站可以与几个直放站相连,可以组成链状、星型、树型等灵活的拓扑结构,使基站的覆盖范围大大增加。同时,既节省空间,又降低成本,提高了组网的效率。

但由于传统模拟直放站设备间没有统一的协议规范,无法满足系统厂商与直放站厂商的兼容,无法实现基站和直放站之间更有效的互通,从而限制了两者之间控制和数据的可靠传输。2003年6年,由包括爱立信、华为、NEC、北电网络及西门子5大集团合力制定了CPRI(Common Public Radio Interface)接口。该组织成立的主要目的是制定这个接口的标准协议,从而使该接口成为一个公共的可用的指标。开放的CPRI接口为3G基站产品和2G数字直放站在增加效益,提高灵活性方面提供了便利。

收稿日期:2008-08-21

基金项目:福建省重大专项基金资助项目(2007 HZ003)

# 1 CPRI协议概述

CPRI 规范<sup>[1]</sup>定义了物理层和链路层两层协议,能实现数字基带 IQ 信号传输时分复用,其协议结构图如图 1 所示<sup>[2]</sup>。物理层用千兆以太网的标准,传输的数据采用 8 B/10 B 编解码,通过光模块串行发送,为达到所要求的灵活度和成本效益,线路比特速率有614.4 Mb/s,1 228.8 Mb/s和2457.6 Mb/s三种。链路层定义了一个同步的帧结构。帧结构包括基本帧和超帧,每个基本帧的帧频为 3.84 MHz,包括 16 个时隙,根据线路比特率的不同,每个时隙的大小分别为1 B,2 B,4 B。其中第一个时隙为控制时隙,其余 15 个时隙为 I/O 数据时隙,用来传送 I/O 数据流。超帧则由 256 个基本帧构成,256 个基本帧的控制时隙共同构成超帧的控制结构(如图 2 所示),同时,定义了快速 C/M 通道(以太网)和慢速 C/M 通道(HDLC),用于传送控制类和管理类的数据,可以对直放站进行维护<sup>[3,4]</sup>。

# 2 硬件实现方案

# 2.1 方案对比

对于 CPRI 硬件实现方案,有以下几种方案可以选择:

- (1) PMC 方案。采用 PMC7830 或 PMC7832 芯片,这一类芯片把 CPRI 协议全部集成在芯片内部,只留出接口,使用简单方便,可完全支持用于无线基站连接的公共射频接口(CPRI)规范。

- (2) 用带 ROCKET IO 的 FPGA 实现 CPRI协议,此方法灵活性高,但开发时间周期会比较长,影响产品开发。

- (3) FPGA 与 SCAN25100 相结合。由 FPGA 实现 CPRI 的成解帧及相关接口设计, SCAN25100 负责完成 8 B/10 B 编解码和高速串并转换。链路层的帧协议修改方便,而物理层则由芯片完成,使用简单,性能稳定。开发成本较低,且扩展性好。

- (4) FPGA 与 TL K4015 相结合。TL K4015 是4 通 道、0.6~1.5 Gb/s 通道收发器,当系统需要多的通道数时,使用该方案可以减少电路板尺寸。

|             | 用户平        | 面   | 控制和管理平面 |  |            |     | 同步         |  |  |

|-------------|------------|-----|---------|--|------------|-----|------------|--|--|

| 链路层         | 路层 IQ数据 卡用 |     |         |  | HDLC<br>接口 |     | L1带内<br>协议 |  |  |

| Alexand Feb | 时分复用       |     |         |  |            |     |            |  |  |

| 物理层         | ŧ          | 气传输 |         |  | 光纤         | 光纤传 | 俞          |  |  |

图 1 CPRI协议结构

| 子通道0   | 同步字节  | 超帧号    | 基站帧号低位 | 基站帧号高位 |

|--------|-------|--------|--------|--------|

| 子通道1   | 慢速C&M | 慢速C&M  | 慢速C&M  | 慢速C&M  |

| 子通道2   | 版本    | HDLC速率 | 线路告警   | 以太网指针P |

| 子通道3   | 保留    | 保留     | 保留     | 保留     |

|        |       |        |        |        |

| 子通道16  | 厂商特定字 | 厂商特定字  | 厂商特定字  | 厂商特定字  |

|        |       |        |        |        |

| 子通道P-1 | 厂商特定字 | 厂商特定字  | 厂商特定字  | 厂商特定字  |

| 子通道P   | 快速C&M | 快速C&M  | 快速C&M  | 快速C&M  |

|        | •••   |        | •••    | •••    |

| 子通道63  | 快速C&M | 快速C&M  | 快速C&M  | 快速C&M  |

图 2 CPRI 超帧控制字结构

#### 2.2 硬件详细设计

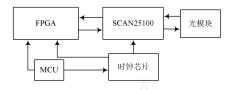

该设计采用第3种的硬件实现方案,整个硬件实现由5个部分组成,如图3所示,分别为CPRI链路层协议实现模块,CPRI物理层协议实现模块、光传输模块、时钟管理模块和系统配置与监控模块。

#### 2.2.1 CPRI 链路层协议实现模块

CPRI链路层只是定义了一个同步的帧结构,而里面的 IQ 数据和控制管理数据都是由用户按需求自由处理的,采用 FPGA 实现 CPRI 的成帧、解帧及相关的控制,处理灵活,方便以后服务增加进行升级。在下面的软件部分做详细介绍。

# 2.2.2 CPRI 物理层协议实现模块[5,6]

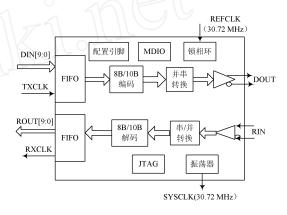

采用国半的 CPRI 串行/解串器 SCAN25100, SCAN25100 是专门为 CPRI 协议设计的高速串并转换芯片,除了串并转换之外,还有 8 B/10 B 编解码功能, 其内部结构框图如图 4 所示。

图 3 硬件实现框图

图 4 SCAN25100 结构框图

图 4 中的 TXCL K 和 RXCL K 都是双边沿采集数据,降低了频率要求,光纤接口(DOUT 和 RIN)的速率由 TXCL K 决定,当 TXL C K 为 61.44 M Hz 时,经 8 B/10 B 编码,再并串转换后,DOUT 的速率就是1 228.8 Mb/s。对于 RXCL K 也就是接收过程的时钟,可以采用芯片内部自动恢复模式。当作为 RE 端时,内部振荡器产生的 30.72 M Hz 时钟 S YSCL K 可以直接作为参考时钟REFCL K,省去一个精准的外部时钟,而且可以利用芯片上的两个锁相环路自动将远程射频单元同步到负责基带处理工作的基站。当作为 REC 端时,需要由时钟芯片产生 30.72 M Hz 的时钟给SCAN25100 当参考时钟。具体应用时,可以使用芯片的配置引脚进行芯片工作模式配置,也可以用 MDIO接口对芯片内部寄存器进行编程,达到配置芯片的目的。

此外,该芯片还提供了延迟校准测量功能,通过读内部相应的寄存器值,再进行简单的换算后,就可以得到数据的传输延迟,其准确度达到 ±800 ps。SCAN25100很好地满足 CPRI 物理层的功能,性能稳定,省去了8 B/10 B 编解码和接收端的时钟恢复,减轻FPGA 开发压力。

#### 2.2.3 光纤传输模块

由于 CPRI 光口的传输速率 有 614.4 Mb/s,

1 228.8 Mb/ s和 2 457.6 Mb/ s 三种,所以光纤模块应该选用多模光纤模块,可以满足 3 种速率的不同选择<sup>[7]</sup>。实现多块单板之间的通信,形成链状和星型混全组网,提高整个数字直放站系统的覆盖范围。

## 2.2.4 时钟管理模块

对于数字直放站系统,需要用到好几个低抖动、低相位噪声时钟,如 SCAN25100,FPGA 等,而且电平有LVDS,LVPECL,CMOS等。时钟是整个系统的核心,其性能直接影响整个系统的工作。

AD9516 是一款将低相位噪声时钟发生和小于1 ps 低抖动 14 通道时钟分配功能集成在一起的时钟集成电路。内部集成了 1 个整数 n 分频的频率合成器、2 个参考输入端、1 个压控振荡器(VCO)、可编程驱动器、可调延迟线和 14 个时钟驱动器,包括 LVPECL,LVDS 和 CMOS 三种电平模式输出<sup>[8]</sup>。由于片内集成了 VCO,省去了外部振荡器,同时也提高了系统设计的稳定性。3 种电平模式时钟输出,丰富了接口方式,给系统设计提供了便利,因此,该系统中采用 ADI 的时钟芯片 AD9516。

## 2.2.5 系统配置及监控

利用单片机对时钟芯片等进行初始化配置,与 FPGA进行通信,实现相应的系统监控功能。

#### 2.3 电路接口设计和 PCB 布板问题

#### 2.3.1 接口电平

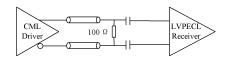

SCAN25100 的串口输出是 CML 差分电平模式,而光纤模块的接口电平是 LVPECL 差分电平模式,为了实现稳定可靠工作,需要进行接口电平转换,其接口转换如图 5 所示 $^{[5]}$ 。

图 5 CML与LVPECL 电平转换

在该系统中,当 CML 差分输出时,芯片已经在差分输出加了电阻,而光纤模块的 LVPECL 电平中已经有隔直电容,所以在处理两者之间的接口电平时显得十分简单,可以把两者直接相连就可以解决接口电平匹配问题。

# 2.3.2 PCB 布板

由于是 GHz 级的设计,对 PCB 设计的要求较高,对高速差分布线,特别是光模块和 SCAN25100 接口走线(图 4 中的 DOUT 和 RIN),应该尽量短且不同层布线,减少收发之间的串扰,增加回流过孔减少其他信号耦合,设计好高速差分走线的阻抗匹配,保证高速串行

信号的完整性。

### 3 软件实现

# 3.1 单片机[9]

实现 SPI 通信协议 ,完成对时钟芯片 、A/D与D/A的初始化配置 ,使得时钟芯片提供多路时钟分别给FPGA ,SCAN25100 , A/D与D/A。实现 LC 通信协议 ,完成单片机与 FPGA 之间的通信 ,从而对数字中频进行设置及监控。实现 485 总线对整个系统进行监控。3.2 FPGA

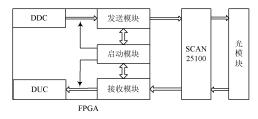

主要是完成 CPRI 的链路层协议。主要分为 3 个模块,发送、接收、CPRI 启动过程模块。其结构如图 6 所示,FPGA 内部实现 CPRI 的成解帧和数字上下变频 (DDC 及 DUC,这里不在讨论),发送模块负责把数字下变频数据通过 CPRI 帧发送给 SCAN25100,接收模块则把接收的 CPRI 帧提取出数字上变频需要的数据。只有当启动模块完成后,输出 1 个控制信号,数字中频和 CPRI 之间才能互相传递数据。

图 6 FPGA 内部功能模块结构

# 3.2.1 发送模块

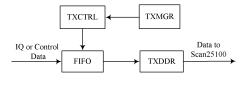

按照 CPRI 基本帧和超帧结构 ,把 DDC (数字下变频) 的 IQ 数据信号与相应的控制信号成帧后发送给 SCAN25100 ,SCAN25100 再进行 8 B/10 B 编码 ,从光模块发送出去。如图 7 所示 ,TXM GR 模块产生 IQ 数据和控制数据的使能信号 ;TXCTRL 模块则对 CPRI 超帧的控制时隙进行状态转换 ,产生不同的控制信号 ,从而从 FIFO 中选择读出不同的控制信号 ;TXDDR 模块则是把数据通过时钟双边沿进行发送。

图 7 发送模块

#### 3.2.2 接收模块

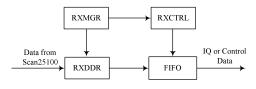

将从 SCAN25100 接收到的数据进行同步头 (K28.5)检测,进行 CPRI 解帧工作,把控制信号和 IQ 数据信号分解出来,IQ 数据信号送到 DUC(数字上变频)。如图 8 所示,RXDDR 模块则是通过时钟双边沿

接收数据;RXMGR模块通过检测帧头产生 IQ 数据和控制数据的使能信号;RXCTRL模块则对 CPRI 超帧的控制时隙进行状态转换,产生不同的控制信号,从而把接收到不同的控制信号写入 FIFO,提供给其他模块。

图 8 接收模块

# 3.2.3 CPRI 启动过程模块

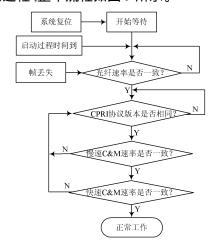

CPRI 规范中的启动过程,此过程是相当重要的,需要软件和硬件共同完成。协商确定物理层的协议、慢速通道(HDLC)和快速通道(以太网)的传输速率,完成REC和 RE 之间的链路建立,从而进行正常的通信过程。在设计过程中,理清各个状态的作用,利用状态机实现启动过程,整个流程如图 9 所示。

图 9 CPRI 启动过程

# 4 实际测试结果

#### 4.1 自环测试

在实验室常温环境下进行实际测试,采用 Chips-cope 抓取发送和接收的数据进行比较的方法。也就是说,产生一段测试数据,按 CPRI 帧格式发送给 SCAN25100,通过光模块自环回来,如图 3 所示,然后用 Chipscope 抓取接收回来的数据,与发送的数据进行对比,确认链路是正常通信。

经过反复测试,该系统已经能正常稳定通信,如图 10 所示。发送数据(Txdata)帧头为 0xBC50,发送时刻为 2172,随后的发送数据的高 8 位和低 8 位分别以 2 累加。接收数据(RxData)在 2193 时刻接收到帧头 0xBC50,随后接收到的数据也是高 8 位和低 8 位分别以 2 累加,而且跟发送的数据是一样的。

#### 4.2 联合测试

CPRI 模块的成解帧都是在 FPGA 内部完成的,而数字中频模块(DDC,DUC)也全部在 FPGA 里面完成设计,如图 6 所示。两部分的接口显得非常简单,只需要把两部分代码整合成一个工程就行。同样,在实验室常温环境下进行测试,整个系统能正常稳定的工作。

#### 5 结 语

CPRI 是规范基站内部 REC 和 RE 之间的接口标准协议。该设计把 CPRI 的两层协议分开设计实现 ,FPGA 实现 CPRI 链路层 ,设计灵活。芯片 SCAN25100 实现物理层 ,由于芯片具备自动同步及准确校准时延等功能 ,方便后续设计分布式远程射频基站系统。通过对电路板的实际测试 ,调整电路设计及 PCB 部分布线设计 ,不断地

| Bus signal | 2172 | 2173 | 2174 | 2175   | 2176 | 2177 | 2178 | 2179 | 2180 | 2181 | 2182 | 2183 | 2184 | 2185 |

|------------|------|------|------|--------|------|------|------|------|------|------|------|------|------|------|

| RxData     | CBCA | CDCC | CFCE | D1D0   | D3D2 | D5D4 | D7D6 | D9D8 | DBDA | DDDC | DFDE | E1E0 | E3E2 | E5E4 |

| TxData     | BC50 | F3F2 | F5F4 | F7F6   | F9F8 | FBFA | FDFC | FFFE | 0100 | 0302 | 0504 | 0706 | 0908 | 0B0A |

|            | 2183 | 2184 | 2185 | 2186   | 2187 | 2188 | 2189 | 2190 | 2191 | 2192 | 2193 | 2194 | 2195 | 2196 |

| RxData     | DFDE | E1E0 | E3E2 | E5E4   | E7E6 | E9E8 | EBEA | EDEC | EFEE | F1F0 | BQ50 | F3F2 | F5F4 | F7F6 |

| TxData     | 0706 | 0908 | OB0A | (ODOC) | OF0E | C1C2 | 1110 | 1312 | 1514 | 1716 | 1918 | IDIC | 1F1E | 2120 |

图 10 测试结果

调整优化设计,CPRI模块正常稳定工作,该模块已经和其他模块(DDC,DUC等)通过了联合测试。

#### 参 考 文 献

- [1] Anon. CPRI Specification V2.0[EB/OL]. http://www.cpri.info/.2007.

- [2] 钟显成,王宏伟. CPRI 协议分析仪的硬件开发与实现[J]. 世界电子元器件,2007(6):56-57,60.

- [3] 任姝婕,吴泽民.3G数字直放站传输接口标准的分析[J]. 现代电子技术,2005,28(23):7-9,13.

- [4] 王彦,倪琰,蒋伟,等.3G数字基站射频拉远 CPRI 规范的实现[J]. 移动通信,2007,31(2):105-109.

- [5] Anon. NSC\_CPRI\_Framer\_Design\_Doc\_v1.0[EB/OL]. http://www.national.com,2007.

- [6] Anon. SCAN25100 Datasheet [EB/OL]. http://www.national.com,2007. (下转第 38 页)

# 2.2 单片机数据处理

单片机数据处理环节的硬件部分包括 A/D 转换和 数据处理两个部分。对于这里所使用的 MSP43014X 系列的单片机,虽然其内部集成了 12 位 A/D 转换器, 但是由于需要多个通道同时转换三相电压、电流信号, 因此要另外选取单独的 A/D 转换芯片,在这里选择 MAX125 芯片,该芯片是一个具有 2 x4 通道同时采 样、14 位数据采集系统。在 A/D 转换过程中,首先采 集 A 相电压、电流 .B 相电压、电流这 4 路信号:转换结 束后,单片机读取4路采样值然后再选择C相电压、电 流进行采样。其核心部分单片机采用德州仪器公司 (TI)的 MSP430 系列超低功耗微控制器。该芯片具有 1个16位CPU、16位的寄存器以及常数发生器,能够 最大限度地提高代码效率。为了使整个检测装置能够 快速实时达到检测性能,单片机外接2块通过译码器扩 展的 64 KB 的数据存储器和 1 块 32 KB 的 EPROM 片 外程序存储器。为了使该检测仪能够同时检测三相电 路的谐波信号,在硬件部分 A/D 转换部分要设置 1 个 三选一的开关,利用软件系统控制每次采集并转换的某 一相位。外设与显示设备的设计这里不再详述。

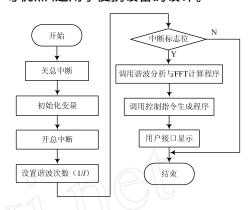

#### 3 系统软件总体介绍

软件设计主要采用 C 语言编程。在程序编程中,由于 MSP430 无法直接进行复数运算,必须把复数分解成实部与虚部的和,然后分别进行计算,因此需要先将正弦表在程序中计算形成,以便程序在采样之后读取进行运算。另外在程序运行后,需通过外设输入相应谐波次数。系统总体软件结构流程图如图 4 所示。

# 4 结 语

这里所提出的谐波检测系统,利用 MSP430 系列单片机组成的相关采集与运算电路,对电弧炉负载的电网电流谐波进行实时的检测并显示,有助于对电弧炉系统进行分析与控制和开展电力系统谐波抑制的研究。

相比于 DSP 芯片, MSP430 系列单片机更具有低功耗, 低成本等优点,适用于便携设备的设计。

图 4 系统软件流程

#### 参考文献

- [1] 林海雪. 电能质量国家标准讲座(3):公用电网谐波标准 [J]. 大众用电,2005(2):12-22.

- [2] 胡广书. 数字信号处理[M]. 北京:清华大学出版社,2003.

- [3] 郭文彬. 嵌入式电网参数监测系统的研制[D]. 镇江:江苏大学,2006.

- [4] 周国伟,石新春,工良清.基于单片机的滤波检测触发电路设计[J].电气传动自动化,2006,28(4):39-41.

- [5] 毕莹,刘小河.基于单片机的谐波检测仪的设计[J].现代电子技术,2008,31(6):161-164.

- [6] 沈建华,杨艳琴. MSP430系列16位超低功耗单片机原理与实践[M]. 北京:北京航空航天大学出版社,2008.

- [7] 杨润贤,郑恩让.基于嵌入式和 DSP 的电力谐波分析仪的设计[J].计算机测量与控制,2006,14(10):1 380-1 383.

- [8] 郝坷. 电力系统谐波检测与治理[J]. 中国测试技术,2005, 31(6):64-67.

- [9] 黄方能,吴玉燕. FFT 谐波检测存在的问题[J]. 广西电力, 2005,28(4):39-41.

- [10] 薛蕙,杨仁刚.基于 FFT 的高精度谐波检测算法[J].中国电机工程学报,2002,22(12):106-108.

- [11] 李红,杨善水.傅里叶电力系统谐波检测方法综述[J].现代电力,2004,21(4):39-44.

作者简介 胡 潇 1983 年出生,硕士研究生。研究方向为电弧炉系统谐波检测。 刘小河 教授,博士生导师。研究方向为供电系统的非线性问题、非线性系统分析与控制、自适应控制等。

(上接第34页)

- [7] 董诗波. WCDMA 光纤直放站射频光收发模块的研究与设计[D]. 武汉:武汉理工大学,2005.

- [8] Anon. AD9516 datasheet [EB/OL]. http://www.analog.com/static/imported-files/data\_sheets/AD9516\_2.pdf,2007.

- [9] Anon. ATmega16L Datasheet [EB/OL] http://down.ic-cavr.com/uploadsoft/ic/ATmega16\_cn.pdf,2007.

- [10] Anon. Introduction to LVDS , PECL and CML [EB/OL]. http://www.maxinric.com.cn/appnotes10.cfm/ac\_pk/ 11 ,2007.

作者简介 陈岳林 男,1983年出生,厦门大学硕士研究生。主要研究方向为无线通信技术。 石江宏 男,1968年出生,厦门大学副教授。主要研究方向为无线通信技术。