DOI: 10. 13290/j. cnki. bdtjs. 2014. 02. 006

# Ge/SiGe 异质结构肖特基源漏 MOSFET

张茂添,刘冠洲,李成,王尘,黄巍,赖虹凯,陈松岩(厦门大学物理系半导体光子学研究中心,厦门361005)

摘要:制备了氧化铪( $HfO_2$ )高 k 介质栅 Si 基 Ge/SiGe 异质结构肖特基源漏场效应晶体管 (SB-MOSFET) 器件,研究了 n 型掺杂  $Si_{0.16}Ge_{0.84}$ 层对器件特性的影响,分析了 n 型掺杂 SiGe 层降低器件关态电流的机理。使用 UHV CVD 沉积系统,采用低温 Ge 缓冲层技术进行了材料生长,首先在 Si 衬底上外延 Ge 缓冲层,随后生长32 nm  $Si_{0.16}Ge_{0.84}$ 和12 nm Ge,并生长1 nm Sife 为钝化层。使用原子力显微镜和 X 射线衍射对材料形貌和晶体质量进行表征,在源漏区沉积 Ni 薄膜并退火形成 NiGe/Ge 肖特基结,制备的 P 型沟道肖特基源漏 MOSFET,其未掺杂 Ge/SiGe 异质结构 MOSFET 器件的空穴有效迁移率比相同工艺条件制备的硅器件的高 1.5 倍,比传统硅器件空穴有效迁移率提高了 80%,掺杂器件的空穴有效迁移率与传统硅器件的相当。

关键词: Ge/SiGe 异质结构; 肖特基势垒; 关态电流; 迁移率; 掺杂 中图分类号: TN386 文献标识码: A 文章编号: 1003-353X (2014) 02-0108-06

## Schottky Barrier S/D Metal Oxide Semiconductor Field Effect Transistors with Ge/SiGe Heterostructure

Zhang Maotian , Liu Guanzhou , Li Cheng , Wang Chen , Huang Wei , Lai Hongkai , Chen Songyan

( Department of Physics , Semiconductor Photonics Research Center , Xiamen University , Xiamen 361005 , China)

Abstract: Si-based Ge/SiGe heterostructure Schottky barrier source and drain metal oxide semiconductor field effect transistors (SB-MOSFETs) with hafnium dioxide high-*k* gate were fabricated. The effect of the n-type doped Si<sub>0.16</sub>Ge<sub>0.84</sub> layer on the device performance was investigated, and the mechanism of the device off-state current reduction caused by the n type doping SiGe layer was analyzed. Firstly, Ge buffer was fabricated with low-temperature Ge buffer technique. Then a 32 nm Si<sub>0.16</sub>Ge<sub>0.84</sub> layer and a 12 nm Ge layer were grown on the Ge buffer in the same UHVCVD system. For comparative study, the 32 nm Si<sub>0.16</sub>Ge<sub>0.84</sub> layer was controlled undoped or n-type doped by P. For all samples, 1 nm Si layer was grown to passivate the Ge surface. Atomic force microscopy and X-ray diffraction were used to characterize the surface morphology and crystal quality of the materials. NiGe/Ge Schottky junctions in source and drain were formed by nickel layer deposition and anneal. The fabricated Ge/SiGe heterosturctual MOSFET device without n-type doping shows 150% enhancement of the hole effective mobility over that of the control Si device and about 80% enhancement over the universal Si device. And the device with n-type doping shows a comparable hole effective mobility with the universal Si MOSFET device.

**Key words**: Ge/SiGe heterosturcture; Schottky barrier; off-state current; mobility; doping **EEACC**: 2560R

基金项目: 国家自然科学基金资助项目 (61036003,61176092); 国家重点基础研究发展计划 (973 计划) 资助项目 (2012CB933503,2013CB632103); 中央高校基本科研业务费资助项目 (2010121056)

通信作者: 李成, E-mail: lich@xmu.edu.cn

108 半导体技术第 39 卷第 2 期

2014年2月

### 0 引言

随着集成电路特征尺寸进入纳米量级,器件性能的进一步提高面临多方面因素的制约和挑战。高迁移率半导体材料如 III-V 族和 Ge 应用于 MOSFET 器件受到广泛的关注。Ge 与 Si 具有相同的晶体结构和相似的材料性质,其电子和空穴迁移率分别是 Si 的 2 倍和 4 倍,且与 Si 标准工艺具有良好的兼容性,是下一代集成电路的重要候选材料之一。然而,与 Si 相比,Ge 器件的制备仍面临着很大的挑战,如锗固有的表面态密度高,缺乏稳定的氧化层,杂质尤其是 n 型杂质在 Ge 中扩散快、浅结制造困难、本征载流子浓度高和窄禁带宽度导致的大漏电流等都需要深入研究解决。

近年来,随着高k介质材料广泛用作MOSFET的栅介质, Ge 沟道 MOSFET 器件的研究取得了很 大进展。研究工作的重点集中于解决高 ½ 栅介质与 Ge 界面态问题。如 2002 年, H. Shang 等人[1] 报道 了采用 GeON 栅介质制备的 Ge MOSFET, 其空穴 有效迁移率比传统 Si 器件有显著提高。此后,研 究人员通过 Ge 表面钝化技术,如采用超薄 Si 薄 膜<sup>[2]</sup>、GeO<sub>2</sub>薄膜<sup>[3-4]</sup>、(NH<sub>4</sub>)<sub>2</sub>S<sup>[5]</sup>和H<sub>2</sub>S<sup>[6]</sup>等钝化 Ge 表面而改善高 k 介质与 Ge 界面,获得了高性能 的 Ge MOSFET 器件。此外, Ge 异质结和量子阱结 构等也被应用于 Ge 器件中,以进一步提高 Ge MOSFET 器件性能。2010 年 R. Pillarisetty 等人<sup>[7]</sup> 采 用应变 Ge 量子阱制备的 MOSFET 器件获得了 770 cm<sup>2</sup> · (V<sup>-1</sup> • s<sup>-1</sup>) 的峰值空穴迁移率。2012 年 P. Hashemi等人[8] 制备的 Ge 量子阱 MOSFET 获得 了940  $\text{cm}^2 \cdot (V^{-1} \cdot \text{s}^{-1})$  的空穴有效迁移率。然而, 虽然目前在高k介质与Ge界面钝化技术方面取得 显著进展,但是浅结的制备和关态电流的改善等仍 需进一步探索。使用肖特基源漏结可避免注入掺杂 扩散引起的的源漏结深问题,因而重新受到人们的 关注。2007年, T. Yamamoto 等人<sup>[9]</sup>报道了SiO,为 栅介质的 NiGe/Ge 肖特基源漏 Ge MOSFET, 获得 了250 cm<sup>2</sup>/(V•s)的空穴有效迁移率。2012年, B. Liu 等人[10] 采用肖特基源漏制备的多栅 Ge MOSFET器件的开关比达到 10<sup>2</sup>,并且获得了约 740 μS/μm的饱和跨导。

本文以高 k 介质/金属叠层为栅 , Si 基外延 Ge/SiGe 异质结构作为沟道层 , 并以 NiGe/Ge 肖特 基结为源漏制备了 p 型沟道肖特基源漏 Ge MOS-

FET,获得的空穴有效迁移率比传统的硅器件提高了 80%,并对 n 型掺杂 SiGe 层降低器件关态电流的机理进行了讨论。

### 1 材料生长与器件制备

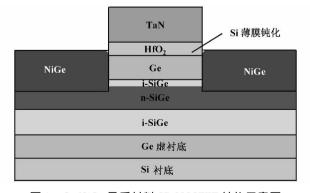

在超高真空化学气相沉积系统 (UHVCVD) 中采用低温 Ge 缓冲层技术在 Si 衬底上外延生长 440 nm Ge、32 nmSiGe、12 nm Ge 和约1 nm Si 钝 化层。具体生长过程为: 将4英寸(1英寸= 2.54 cm) n型Si (100) 圆片(电阻率为0.1~  $1.2 \Omega \cdot cm$ ) 经过 RCA 标准清洗后传入预处理室, 在 200 ℃下恒温1 h去除水汽后传入生长室。在高 真空条件下(10<sup>-8</sup>Pa) 缓慢加热衬底到900 ℃,恒 温30 min, 去除衬底表面形成的自然氧化层, 从而 获得清洁的生长表面。然后降温到750 ℃ 生长 300 nm Si缓冲层,随后在330 ℃生长90 nm低温 Ge 缓冲层和在600 ℃下生长350 nm高温 Ge 作为虚衬 底,生长细节可参见文献[11]。随后进行Ge/SiGe 异质结构的生长。先生长20 nm SiGe,随后生长 10 nm掺 P 的 SiGe 层 (或者不掺杂,不掺杂样品称 为样品 A,掺 P样品称为样品 B) 和2 nm SiGe 作 为隔离层,再在600 ℃下生长 12 nm Ge 沟道层, 最后在380 ℃下生长1 nm Si钝化层,其中掺 P 的 SiGe 层的掺杂浓度约为  $5 \times 10^{17}$  cm<sup>-3</sup>。

在材料生长完成后,进行了 SB-MOSFET 器件的工艺制备。首先分别用电子束蒸发设备和磁控溅射台制备20 nm  $HfO_2$ 和20 nm氮化钽(TaN),并进行光刻、刻蚀等工艺,形成  $HfO_2$ /TaN 高 k/金属叠栅;最后溅射10 nm Ni,并在400  $^{\circ}$ C 下退火60 s,形成 NiGe/Ge 肖特基源漏结,将未反应的 Ni 用酸腐蚀去除。所制备的器件为环形栅结构,其内外边长分别为 200 和240  $\mu$ m,器件结构如图 1 所示。

图 1 Ge/SiGe 异质材料 SB-MOSFET 结构示意图 . 1 Structure schematic of the SB-MOSFET with Ge/SiG

Fig. 1 Structure schematic of the SB-MOSFET with Ge/SiGe heterostructure

February 2014

Semiconductor Technology Vol. 39 No. 2 109

### 2 结果与讨论

#### 2.1 材料表征

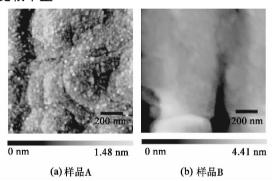

本文对在 Si 衬底上生长的外延材料表面形貌、晶体质量等进行了表征。图 2 为用原子力显微镜测试样品的表面形貌。样品 A 的表面粗糙度为0.4 nm,样品 B 的表面粗糙度约为0.7 nm。由于外延过程中掺杂对晶体质量有所影响,样品的表面粗糙度略有增大。但是总体而言,两个样品的表面均比较平整。

图 2 原子力显微镜测试的样品形貌图 Fig. 2 AFM images of samples morphology

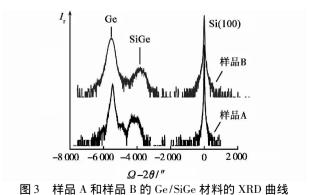

图 3 给出两个样品 X 射线衍射 (XRD) 曲线。曲线上从右到左三个峰分别对应于 Si 峰、SiGe 峰和 Ge 峰。两个样品的 Ge 峰和 SiGe 峰的峰形对称,表明样品具有较好的结晶质量。界面互扩散比较小。样品 A 的 Ge 峰半高宽为 630 ", 30 nmSiGe 层的半高宽为 820 "。样品 B 的 Ge 峰、SiGe 峰半高宽略有增加,分别为 750 "和 1 000 ",表明掺杂后样品的结晶质量略有恶化。基于 XRD 动力学理论,模拟了 XRD 曲线,从中提取出样品 A 和 B 中 SiGe 层中的 Ge 组分和 Ge 层的应变。样品 A 中 SiGe 层

Fig. 3 XRD curves of Ge/SiGe heterostructure materials of sample A and sample B

110 半导体技术第 39 卷第 2 期

的 Ge 组分为 0.84。样品 B 中 SiGe 层的 Ge 组分为 0.87。根据 Ge 峰的位置,计算得到样品 A 和样品 B 中 Ge 层所受的张应变分别为 0.19% 和 0.12%。

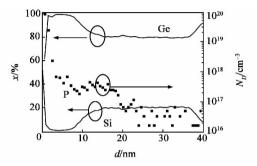

对样品 B 中 P 杂质分布进行二次离子质谱 (secondary ion mass spectroscopy , SIMS) 测试 , 如图 4 所示。图 4 中 d 为样品剖面的纵向深度 , x 为 SiGe 层中 Si 和 Ge 的组分 ,  $N_{\rm D}$  为 SiGe 层的掺杂浓度。

图 4 样品 B 中 P 杂质分布二次离子质谱法 (SIMS) 曲线 Fig. 4 Secondary ion mass spectroscopy (SIMS) profiles of phosphorus in sample B

图 4 中显示出的 Ge , Si 和 P 在表面附近的突变分布是由测试误差引起的。SiGe 层的掺杂浓度  $N_D$ 约为  $5 \times 10^{17} \, \mathrm{cm}^{-3}$  , 在生长过程中 P 原子向两边发生了较严重的扩散现象。此外,由于 SiGe 层掺杂完后 P 有严重的寄生效应,在随后生长 Ge 层的过程中,真空腔内的 P 杂质原子仍起到掺杂的作用。使 Ge 沟道层中 P 掺杂浓度与 SiGe 层中相近。SIMS 测试的 SiGe 层的组分与由 XRD 峰位计算结果基本相符。

#### 2.2 器件电学特性与分析

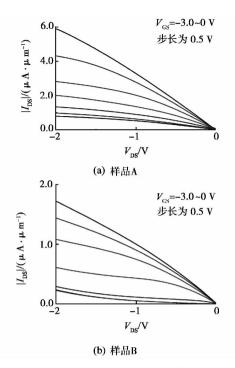

测试了样品 A 和 B 的输出特性,测试条件为,栅电压从 0 V 到 -3 V,步长为 -0.5 V。图 5 给出了样品 A 和 B 的输出特性( $I_{DS}$   $-V_{DS}$ )(其中  $I_{DS}$  为单位栅宽的漏端电流, $V_{DS}$  为漏端电压, $V_{CS}$  为栅电压)。样品 A 在栅电压为0 V时就已开启,而样品 B 在栅电压为 -1 V时开启。

由于未故意掺杂样品 A 中外延生长的 Ge 层显弱 p 型,NiGe 与 p-Ge 接触的势垒高度很小,因此在零电压下即形成空穴导电通道产生电流。而样品 B 进行了 n 型掺杂,需要比样品 A 更大的栅电压才能形成空穴导电通道,并且在相同的栅和漏电压下,样品 A 的漏端电流更大。

2014年2月

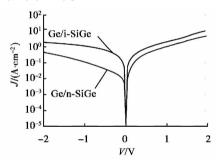

为了进一步了解掺杂对器件 I—V 特性的影响,对 NiGe/Ge 肖特基源漏接触特性进行测试,其 J—V 特性曲线如图 6 所示。

图 6 样品 A 和样品 B 的肖特基源漏结 J-V 特性曲线 Fig. 6 J-V characteristic curves of the Schottky source/ drain junctions of sample A and B

样品 A 的 I-V 特性接近欧姆接触,表明 NiGe 与弱 p-Ge 接触的空穴势垒很低,导致空穴很容易越过势垒到达沟道区,形成电流;对于样品 B,由于在 SiGe 掺杂过程中,Ge 沟道也被掺入 P 杂质,表现出 n-Ge 的性质,NiGe/Ge 接触表现为肖特基接触特性。基于热发射模型 $^{[12]}$ ,提取出 NiGe/Ge 接触的势垒高度。热发射电流可表达为

$$J_{n} = J_{s \to m} + J_{m \to s} = \left[ A^{*} T^{2} \exp\left( -\frac{q\phi_{\text{Bn}}}{kT} \right) \right] \left[ \exp\left( \frac{qV}{kT} \right) - 1 \right] =$$

February 2014

$$J_{TE}\left[\exp\left(\frac{qV}{kT}\right) - 1\right] \tag{1}$$

式中:  $J_{\text{TE}} = A^* T^2 \exp\left(-\frac{q\phi_{\text{Bn}}}{kT}\right)$  为饱和电流度;  $A^*$

为理查德森常数; k 为玻耳兹曼常数; T 为测试温度;  $\phi_{Bn}$  为电子的肖特基势垒高度;  $J_{s \to m}$  和  $J_{m \to s}$  分别为半导体到金属的电流密度和金属到半导体的电流密度。通过对 I - V 特性曲线的拟合,提取得到样品B 的 NiGe/Ge 接触的电子势垒高度为0. 63 eV。由此看出,样品B 的 NiGe/Ge 接触具有较高电子势垒,在零栅电压下电子难以越过势垒形成电流。但当栅电压达到 -1 V时,Ge 表面开始形成空穴反型层,源漏开始导通。

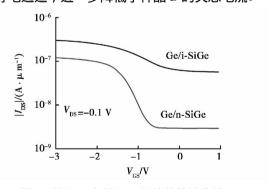

图 7 给出样品 A 和 B 的转移特性( $I_{DS}$   $\stackrel{1}{\sim}_{CS}$ ),测试时栅电压由 I V 到 -3 V,漏电压设定为 -0.1 V。样品 A 的开关比远小于样品 B,样品 A 的开态电流比样品 B 略大。由于样品 B 中沟道层被掺入了 P 原子,导致载流子在沟道中发生杂质散射,使得迁移率下降、开态电流减小。而样品 B 获得了比样品 A 小得多的关态电流,这主要有以下两个原因:第一,由于样品 A 的 Ge 沟道层为弱 p 型,源漏 NiGe/Ge 接触呈现出欧姆特性,结反向电流大,引起较大的关态电流。而样品 B 源漏 NiGe/Ge 结为肖特基接触,有较高的电子势垒,具有较小的关态电流。第二,由于样品 B 存在 n 型掺杂的 SiGe 隔离层,阻止空穴在沟道层以下的本征区形成导电通道,进一步降低了样品 B 的关态电流。

图7 样品 A 和样品 B 的转移特性曲线

Fig. 7  $~I_{\rm DS}\text{--}V_{\rm GS}$  characteristic curves of samples A and sample B

为了对比两个样品的亚阈特性并提取器件有效迁移率,采用线性外推法,提取器件的阈值电压并采用漏电导法提取了器件有效迁移率。线性外推法提取器件的阈值电压原理 $^{[13]}$ 177 -179 如下: 当 $V_{\rm DS}$ 较小(50 ~ 100 mV)时,器件工作在线性区,漏电流  $I_{\rm DS}$  可表示为

Semiconductor Technology Vol. 39 No. 2 111

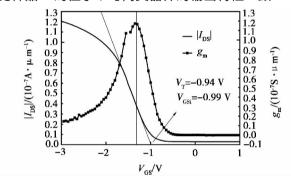

$I_{\rm DS} = k(V_{\rm GS} - V_{\rm T} - 0.5V_{\rm DS})(V_{\rm DS} - I_{\rm DS}R_{\rm SD})$ (2)式中:  $R_{\rm SD}$  是串联电阻。当  $I_{\rm DS} = 0$  时, $V_{\rm CS} - V_{\rm T} - 0.5V_{\rm DS} = 0$ 。即由  $I_{\rm DS} = 0$  时截距电压  $V_{\rm CS} = V_{\rm GS}$  可确定阈值电压  $V_{\rm T} = V_{\rm CSi} - 0.5V_{\rm DS}$ 。由于在栅电压低于  $V_{\rm T}$  时,由于亚阈值电流的影响, $I_{\rm DS} - V_{\rm GS}$  曲线偏离线性关系。栅电压高于  $V_{\rm T}$  时,由于串联电阻和迁移率的退化效应, $I_{\rm DS} - V_{\rm GS}$  曲线也偏离线性关系。因此,在应用线性外推法时,要找出  $I_{\rm DS} - V_{\rm GS}$  曲线斜率最大值,即跨导最大值  $g_{\rm m} = \partial I_{\rm DS}/\partial V_{\rm GS}$ ,并在此点对  $I_{\rm DS} - V_{\rm GS}$  作线性拟合,外推到  $I_{\rm DS} = 0$ ,即可得到阈值电压。

图 8 显示出样品 B 的转移特性和应用线性外推 法求阈值电压的过程,提取出的阈值电压为  $V_{\rm T}=-0.94~V$ 。同理求得样品 A 的阈值电压为 -0.2~V,比样品 B 的值小,与两类器件的输出特性一致。

图 8 线性外推法提取阈值电压示意图

Fig. 8 Schematic diagram of the method for measuring the linear threshold voltage

漏电导法提取器件有空迁移率原理<sup>[13]</sup>397 - 401 如下:

当  $V_{

m DS}$  较小(50 ~ 100 mV)时,有效迁移率  $\mu_{

m eff}$  和 pMOSFET 有效电场强度  $E_{

m eff}$  可分别表示为

$$\mu_{\rm eff} = \frac{g_{\rm d}L}{Q_{\rm e}W} \tag{3}$$

$$E_{\rm eff} = \frac{Q_{\rm b} + Q_{\rm n}/3}{\varepsilon_{\rm s}\varepsilon_{\rm 0}} \tag{4}$$

式中:漏电导  $g_{\rm d}=\frac{\partial I_{\rm DS}}{\partial V_{\rm DS}}\bigg|_{V_{\rm CS}=const}$ ; 反型层电荷面密度  $Q_{\rm n}=C_{\rm ox}(V_{\rm GS}-V_{\rm T})$  ,空间电荷区电荷面密度  $Q_{\rm b}=\sqrt{4\kappa_{\rm s}\varepsilon_0kTN_{\rm d}\ln\Bigl(\frac{N_{\rm A}}{n_{\rm i}}\Bigr)}$  ;  $\varepsilon_{\rm s}$  是栅氧相对介电常数;  $\varepsilon_0$  是真空介电常数; L/W 为器件长宽比。

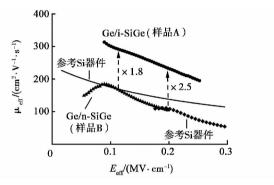

联立式(3)和(4)求解得到器件有效空穴 迁移率与有效电场的关系,如图9所示。制备的Si

112 半导体技术第 39 卷第 2 期

SB-MOSFET 器件的有效空穴迁移率达到了传统 Si器件的约 90%。样品 A 的有效空穴迁移率相比传统 Si 器件提高了约 80%,在  $E_{eff}=0.1$  MV  $\cdot$  cm  $^{-1}$  处达到了313 cm  $^2$  · (  $V^{-1}$  · s  $^{-1}$ ) ,比参考 Si 器件提高了约 150%。而样品 B 由于其沟道层有 P 原子掺杂,严重的杂质散射导致样品 B 在低场区表现出迁移率衰退,其有效空穴迁移率比样品 A 低,但仍与传统 Si 器件相近。

图 9 样品 A 和样品 B 的有效空穴迁移率随有效电场强度的关系

Fig. 9 Dependence of the effective hole mobility on the effective field of sample A and sample B

### 3 结 论

本文介绍了肖特基源漏 Ge/SiGe 异质结构 MOSFET 器件的研制过程和结果,其最大有效空穴迁移率达到313 cm²/(V•s),比传统 Si 器件提高了约80%,比参考 Si 器件提高了约150%。对 n型掺杂 SiGe 层对 NiGe/Ge 接触及器件特性的影响进行研究,发现通过掺杂调控源漏肖特基结势垒高度,可有效降低 Ge pMOSFET 的关态电流。但是,沟道层中 P 原子的掺杂会导致沟道中较严重的杂质散射,使器件的有效迁移率降低。因此为获得更高性能的 MOSFET 器件,需进一步优化肖特基源漏以及 Ge/SiGe 异质结构调制掺杂技术。

#### 参考文献:

- [1] SHANG H, OKOM-SCHMIDT H, CHAN K K, et al. High mobility p-channel germanium MOSFETs with a thin Ge oxynitride gate dielectric [C] // Proceedings of IEEE International Electron Devices Meeting. San Francisco, USA, 2002: 441 – 444.

- [2] MITARD J , VICENT B , JAEGER B D , et al. Electrical characterization of Ge-pFETs with HfO<sub>2</sub>/TiN metal gate: review of possible defects impacting the hole

2014年2月

- mobility [J]. ECS Trans, 2010, 28 (2): 157-169.

- [3] DELABIE A, BELLENGER F, HOUSSA M, et al. Effective electrical passivation of Ge (100) for high-k gate dielectric layers using germanium oxide [J]. Applied Physics Letters, 2007, 91 (8): 082904-1 - 082904-3.

- [4] TORIUMI A, TABATA T, LEE C H, et al. Opportunities and challenges for Ge CMOS—Control of interfacing field on Ge is a key [J]. Microelectronic Engineering, 2009, 86 (7/8/9): 1571 1576.

- [5] SIONCKE S , LIN H C , BRAMMERTZ G , et al. Atomic layer deposition of high-k dielectrics on sulphur passivated germanium [J]. Electrochemic Soc , 2011 , 158 (7): 687 – 692.

- [6] MERCKLING C , CHANG Y C , LU C Y , et al. H<sub>2</sub> S molecular beam passivation of Ge (001) [J]. Microelectron Eng , 2011 , 88: 399 402.

- [7] PILLARISETTY R , CHU-KUNG B , CORCORAN S , et al. High mobility strained germanium quantum well field effect transistor as the p-channel device option for low power ( $V_{\rm cc}=0.5$  V) III-V CMOS architecture [C] // Proceedings of 2010 IEEE International Electron Devices Meeting. San Francisco , USA , 2010: 150 153.

- [8] HASHEMI P , HOYT J L. High hole-mobility strained— Ge/Si<sub>0.6</sub>Ge<sub>0.4</sub> p-MOSFETs with high-k/metal gate: role of strained-Si cap thickness [J]. IEEE Electron Device Lett , 2012 , 33 (2): 173 – 175.

- [9] YAMAMOTO T, YAMASHITA Y, HARADA M, et al. High performance 60 nm gate length germanium p-MOSFETs with Ni germanide metal source/drain [C] // Proceedings of IEEE International Electron Devices Meeting. Washington, DC, USA, 2007: 1041 – 1043.

- [10] LIU B, GONG X, HAN G Q, et al. High-performance germanium Ω-gate MuGFET with Schottky-barrier nickel germanide source/drain and low-temperature disilane-passivated gate stack [J]. IEEE Electron Device Lett, 2012, 33 (10): 1336-1338.

- [11] 陈城钊,郑元宇,黄诗浩,等. 硅基低位错密度厚锗外延层的 UHV/CVD 法生长 [J]. 物理学报, 2012,61(7):078104.

- [12] 施敏,伍国珏. 半导体器件物理 [M]. 西安: 西安 交通大学出版社,2008: 118-120.

- [13] 施罗德. 半导体材料与器件表征技术 [M]. 大连理工大学半导体研究室,译. 大连: 大连理工大学出版社,2008.

(收稿日期: 2013-10-30)

#### 作者简介:

张茂添(1989─),男,浙江平阳人,硕士研究生,研究方向为锗材料生长与器件工艺:

李成(1970一),男,河北张家口人,博士,教授,研究方向 为半导体光电子材料及 Si 基集成光电子学。

# 飞兆半导体推出 650 V 绿色模式降压开关

2014 年 1 月 9 日,家用电器、工业电机和智能电表应用需要能提供低待机功耗的解决方案,以便为最终用户实现能效。同时,设计人员需要能提高器件额定功率的功率可扩展性,以便在简化设计的同时实现额外的系统功能。为应对此挑战,飞兆半导体开发了 FSL306 和 FSL336 650 V 绿色模式 AC 降压开关。这些器件可在低可用工作电流(250  $\mu$ A)下实现间歇模式运行,有助于降低待机模式功耗,提高能效。 FSL306 器件可通过调节限流引脚实现 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5

FSL306 和 FSL336 器件借助安全自动重启模式等保护功能提供更高的可靠性。出现故障后,开关在等待 650 ms 后重启。该功能可提高系统可靠性。这些器件在单个封装中组合了一个 PWM 控制器和一个分立式 MOSFET。高压稳压器无需辅助偏压绕组就可工作。FSL306 和 FSL336 利用内置误差放大器便可提供直接反馈,无需并联稳压器,有助于降低总体物料成本,节省电路板空间。

Semiconductor Technology Vol. 39 No. 2 113