| 学校编码:10384 | 分类号 | 密级 |

|------------|-----|----|

|            | ·   | •  |

学号: 200130008 UDC\_\_\_\_\_

# 学位论文 PIC 兼容单片机的电路分析与设计

PIC Compatible MCU's Circuit Analysis and Design 袁江南

指导教师姓名:邢建力 教授级高级工程师

申请学位级别:硕士

专业名称:无线电物理

论文提交日期:2004年5月 日

论文答辩日期: 2004年 月 日

学位授予单位:厦门大学

学位授予日期:2004年 月 日

| 答辩委员会主席: |  |

|----------|--|

|          |  |

评 阅 人:

2004年5月

## 厦门大学学位论文原创性声明

兹呈交的学位论文,是本人在导师指导下独立完成的研究成果。本人在论文写作中参考的其他个人或集体的研究成果,均在文中以明确方式标明。本人依法享有和承担由此论文而产生的权利和责任。

声明人(签名):

年 月 日

## 学 位 论 文

# PIC 兼容单片机的电路分析与设计

PIC Compatible MCU's Circuit Analysis and Design

袁江南

厦门大学电子工程系2004年5月

## 摘要

随着微电子技术的飞速发展,作为电子系统核心的集成电路。一直遵照着摩尔定律在发展,集成度方面,已经能在单芯片上集成几百万、上千万晶体管。同时,芯片的功耗越来越低,工作速度越来越高。如今在单芯片上集成一个系统,即所谓的系统芯片(SOC)已成为可能。集成电路业进入系统芯片时代后,在芯片设计中采用 IP 核(知识产权)是设计发展一个必然选择,基于 IP 核复用的自顶向下的设计可提高设计效率,节省人力和满足面市时间的要求。

基于 IP 的设计的关键显然是各种性能优异、方便重用的 IP 核。IP 核可分为硬核、固核 和软核。其中的硬核依赖特定的工艺库,目前主要来源是外国的 IP 专业供应商,设计服务公司和代工厂。而软核是一个仅仅以软件形式存在的可综合的硬件描述语言(HDL)描述。由于其与制造工艺库完全没有关系,所以可作为追赶国际先进水平的突破口。

Mi crochi p 公司生产的 PI C 系列微控制器是当今世界上采用 RI SC 结构的主流机种之一。具有速度快、成本低、稳定可靠的优点,在我国有广泛的应用群体。本论文是在深入分析 PI C 微处理器的电路结构和工作原理的基础上,用自顶向下的方法设计出可供重用的 IP 软核。包括微控制器核及其周边的常用接口如串行口,SPI 接口,I 2C 接口及目前流行的 USB1.1 接口。

论文的第一章简要介绍了 EDA 工程的发展及自顶向下的设计方法。第二章剖析了 PIC16C54 微控制器的工作原理。第三章是论文的中心,即采用自顶向下的设计方法设计了可重用的 PIC16C5X 及 PIC16C55X IP 软核,并且在 FPGA 上得到了验证。第四章设计了常用的外围接口如串行口,SPI 接口,I2C 接口。第五章对当今流行的 USB1.1 接口电路进行了分析与设计。第六章对论文的工作进行了总结。

本论文在设计 IP 软核时并没有拘泥于现有的电路,而是充分考虑到了设计的可综合性和可重用性原则,对系统结构进行了充分的讨论和规划。最终完成的各 IP 核都是可综合、可实现、 方便重用的。在构建更大规模的芯片时具有一定应用价值。

关键词:PIC 微控制器;IP 核;接口电路

#### **Abstract**

With the development of microelectronics technology, the core of electronics system, Integrated Circuits, have made great progress to integrate millions of transistors in a single chip with lower power consumption. It's possible to build a system in a single chip to construct so call System On Chip (SOC) today. In order to improve the efficiency and shorten the time for new products to enter into market, IP(Intellectual Property) reusing and Top-down design method become the inevitable way to the age of SOC.

The key element of IP based design lies in all kinds of good performance and easy-to-reuse IP cores. IP cores include hard cores and soft cores. Built on special technique library, hard cores mainly come from foreign IP providers, designing corporations and foundries. Softcore exists in the form of software of synthesizable HDL code. The synthesizable IP softcore, having nothing to do with technique library, can be looked as the breakthrough of IC technology.

Microchip's PIC series microcontrollers are world-wide used RISC MCU. They are widely used in China because of high-speed, low-cost and reliability. After a deep and thorough analysis of circuit construction and working process of PIC16C54 MCU, softcores of PIC16C5X and PIC16C55X is presented in this thesis, including UART, SPI, I2C and USB1.1 interface.

The thesis is organized as following:

Chapter 1 briefly introduces the development of EDA technology and Top-down design. Chapter 2 analyzes PIC16C54 MCU's circuit construction and working principle. Chapter 3 is probably the most important chapter of the thesis and presents PIC16C5X and PIC16C55X compatible softcore and implements them in Xilinx FPGA as well. In Chapter 4, UART, SPI and I2C interface circuit are designed and verified in FPGA. Chapter 5 analyzes and designs USB1.1 interface circuit, which becomes more popular in computer system. Chapter 6 gives a brief summary of this thesis.

Synthesizable and reusable principle of IP softcore is fully followed in this paper. So it's useful in building a large scale SOC.

Key Words: PIC MCU; IP Core; Interface Circuits.

## 目 录

| 中文摘要                    | i  |

|-------------------------|----|

| Abstract                | ii |

| 第一章 引言                  | 1  |

| 1.1 数字系统设计方法的变革         | 1  |

| 1.2 基于 IP 核的设计          |    |

| 1.3 本论文的主要内容            | 6  |

| 第二章 PIC16C54 微控制器电路分析   | 7  |

| 2.1 时钟产生与控制模块           | 7  |

| 2.2 程序计数器 PC            | 9  |

| 2.3 程序存贮器 ROM 地址译码器     | 13 |

| 2.4 程序存贮器 ROM           |    |

| 2.5 指令寄存器与文件选择寄存器 FSR   | 14 |

| 2.6 指令译码器               | 17 |

| 2.7 算术逻辑单元 ALU 与 W 寄存器  | 18 |

| 2.8 端口寄存器与 TRIS 寄存器     | 23 |

| 2.9 端口计数器/定时器           | 24 |

| 2.10 预分频器与看门狗定时器        |    |

| 2.11 状态寄存器与 OPTI ON 寄存器 | 28 |

| 2.12 通用寄存器 RAM          | 29 |

| 第三章 PIC 兼容微控制器软核的设计     | 32 |

| 3.1 软核结构的确定             | 32 |

| 3.2 软核各模块的设计            | 49 |

| 3.3 软核的功能仿真             | 59 |

| 3.4 软核的综合                 | 64  |

|---------------------------|-----|

| 3.5 软核的布局布线,后仿真与实现        | 66  |

| 3.6 中断系统的设计实现以及软核的扩展和使用说明 | 72  |

| 第四章 常用外围通信接口模块的设计         |     |

| 4.1 串行通信接口模块的设计与实现        | 77  |

| 4.2 SPI 通信接口模块的设计与实现      | 84  |

| 4.3 I2C 通信接口模块的设计与实现      | 86  |

| 第五章 USB1.1 通信接口模块的设计      | 93  |

| 5.1 USB1.1 体系结构           | 93  |

| 5.2 USB1.1 通信协议           | 94  |

| 5.3 USB1.1 接口模块的各子模块划分    | 98  |

| 5.4 USB1.1 通信接口模块各子模块设计   | 100 |

| 5.5 USB1.1 模块与微控制器的接口     | 112 |

| 5.6 USB1.1 模块的仿真、综合与布局布线  | 114 |

| 第六章 总结                    | 118 |

| 参考文献                      | 120 |

| <b>死油</b>                 | 122 |

## INDEX

| Chinese Abstracti                                        |     |

|----------------------------------------------------------|-----|

| Abstractii                                               |     |

| Chapter1 Introduction                                    | .1  |

| 1.1 The evolution of digital system design               | .1  |

| 1.2 IP based design                                      | 4   |

| 1.3 About this thesis                                    | 6   |

| Chapter2 PIC16C54 MCU circuit analysis                   |     |

| 2.1 Clock generation module                              | . 7 |

| 2.2 Program counter                                      |     |

| 2. 3 Program ROM address decoder                         | 13  |

| 2. 4 Program ROM                                         | 14  |

| 2.5 Instruction register and file selection register FSR | 14  |

| 2.6 Instruction decoder                                  | 17  |

| 2.7 ALU and W register                                   | 18  |

| 2.8 I/O register and TRIS register                       | 23  |

| 2.9 Counter/Timer                                        | 24  |

| 2.10 Divider and watch dog timer WDT2                    | 6   |

| 2.11 Status register and option register                 | 28  |

| 2.12 General register RAM                                | 29  |

| Chapter3 PIC compatible MCU softcore design              | 32  |

| 3.1 Construction of the softcore                         | 32  |

| 3. 2 Modules design of the softcore                      | 49  |

| 3.3 Function simulation of the softcore                  | 59  |

| 3.4 Synthesis of the softcore64                                |

|----------------------------------------------------------------|

| 3.5 Layout, timing simulation and implementation66             |

| 3.6 Interrupt system design and using method of the softcore72 |

| Chapter4 Peripheral interface circuits design77                |

| 4.1 Series interface circuit design and implementation77       |

| 4.2 SPI interface circuit design and implementation84          |

| 4.3 I2C interface circuit design and implementation86          |

| Chapter5 USB1.1 interface circuit design93                     |

| 5.1 USB1.1 topology93                                          |

| 5. 2 USB1. 1 protocol94                                        |

| 5.3 Modules dividing of USB1.1 interface circuit98             |

| 5. 4 Modul es design of USB1. 1 interface circuit100           |

| 5.5 Interface between USB1.1 and MCU112                        |

| 5.6 Simulation, synthesis and layout114                        |

| Chapter6 Summary118                                            |

| References                                                     |

| Grati tude 122                                                 |

## 第一章 引言

### 1.1 数字系统设计方法的变革

#### 1.1.1 EDA 工程发展历程

EDA (Electronic Design Automation)就是以计算机为工作平台,以 EDA 软件工具为开发环境,以硬件描述语言为设计语言,以可编程器件为实验载体,以 ASIC、SOC 芯片为目标器件,以电子系统设计为应用方向的电子产品自动化设计过程。一般认为,EDA 技术经历了下面3个发展阶段[参见文献1、2]:

#### 1. CAD 阶段

电子 CAD 阶段是 EDA 技术发展的早期阶段。20 世纪 70 年代,随着中小规模集成电路的开发应用,传统的手工制图设计印刷电路板和集成电路的方法已无法满足设计精度和效率的要求。因此工程师们开始进行二维平面图形的计算机辅助设计(Computer Aided Design—CAD),以便解脱繁杂、机械的版图设计工作,这就产生了第一代 EDA 工具。这个阶段的特征是计算机采用小型计算机,软件功能为交互式图形编辑,设计规则检查,以及用于集成电路的版图设计。

## 2. CAE 阶段

到了 80 年代,随着集成电路规模的扩大,电子系统设计的逐步复杂,为了适应电子产品在规模和制作上的需要,电子 CAD 的工具逐步完善和发展,尤其是人们在设计方法学、设计工具集成化方面取得了长足的进步,开始进入计算机辅助工程(Computer Aided Engineering—CAE)阶段。在这个阶段,各种单点设计工具和各种设计单元库逐渐完备,出现了以计算机仿真和自动布线为核心技术的第二代 EDA 工具。并且开始将许多单点工具集成在一起使用,大大提高了工作效率。

#### 3. EDA 阶段

20世纪90来,微电子工艺有了惊人的发展,工艺水平已以达到了深亚微米级,一个完整的数字电子系统集成于一块芯片上(System On a Chip—SOC)已成为可能。这样就对电子设计的工具提出了更高的要求,同时也促进了设计工具的发展。90年代后期,出现了以高级语言描述、系统级仿真和综合技术为特征的第三代 EDA 工具。电子设计由辅助手段变为主要特征是自动化程度的提高,人工干预的减少。未来 EDA 的发展趋势是高度自动化,设计者从事概念设计或者是电子系统的"行为设计",而大部分工程中的技术问题,由 EDA 工具解决。EDA 工具的出现,极大地提高了系统设计的效率,使广大的电子设计师开始实现"概念驱动工程"的梦想。设计师们摆脱了大量的具体设计工作,而把精力集中于创造性的方案与概念构思上,从而极大地提高了设计效率,缩短了产品的研制周期。

从发展的过程看,EDA 技术一直滞后于制造工艺的发展,它是在制造技术的驱动下不断地向前进步的;从长远看,EDA 技术将随着微电子技术、计算机技术的不断发展而发展。

### 1.1.2 数字系统自顶向下的设计方法与流程

近 10 年来,电子系统的设计方法发生了很大的变化。半导体集成电路已由早期的单元集成、部件电路集成发展到整机电路集成和系统电路集成。电子系统的设计方法也由过去的那种集成电路厂家提供通用芯片,整机系统用户采用这些芯片组成电子系统的"Bottom-up"(自底向上)设计方法改变为一种新的"Top-down"(自顶向下)设计方法。在这种新的设计方法中,由整机系统用户对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路 ASIC 来实现,且这些专用集成电路是由系统和电路设计师亲自参与设计的,直至完成电路到芯片版图的设计,再交由 IC 工厂投片加工,或者是用可编程逻辑(例如 CPLD 和 FPGA)现场编程实现。

"自顶向下"(Top-Down)的全新设计方法首先从系统设计入手,在顶层

进行功能方框图的划分和结构设计。在方框图一级进行仿真、纠错,并用硬件描述语言对高层次的系统行为进行描述,在系统一级进行验证。然后用综合优化工具生成具体门电路的网表,其对应的物理实现是印刷电路板或专用集成电路。由于设计的主要仿真和调试过程是在高层次上完成的,这不仅有利于早期发现结构设计上的错误,避免设计工作的浪费,而且也减少了逻辑功能仿真的工作量,提高了设计的一次成功率。

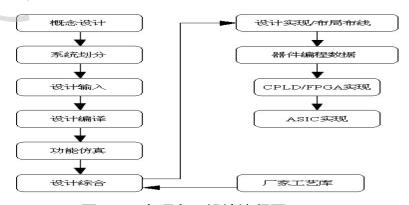

高层次设计是一种"概念驱动式"设计,设计人员无需通过门级原理图描述电路,而是针对设计目标进行功能描述,由于摆脱了电路细节的束缚,设计人员可以把精力集中于创造性的概念构思与方案上,一旦这些概念构思以高层次描述的形式输入计算机后,EDA 工具就能以规则驱动的方式自动完成整个设计。这样,新的概念得以迅速有效地变成为产品,大大缩短了产品的研制周期。不仅如此,高层次设计只是定义系统的行为特性,而不涉及实现工艺,在厂家综合库的支持下,利用综合优化工具可以将高层次描述转换成针对某种工艺优化的网表,工艺转化变得轻松容易。高层次设计的设计流程如图 1.1 所示。(注:设计 ASIC 是并不一定要经过 FPGA 验证这一步,同时 ASIC 的设计还涉及到版图设计、提取、仿真、一致性验证等。)

图 1.1 自顶向下设计流程图

### 1.2 基于 IP 核的设计

#### 1.2.1 IP 复用技术

IP(Intellectual Property)原来的含义是指知识产权,在IC设计领域则可以理解为实现某种功能的设计。IP核(IP模块)则是指完成某种功能的虚电路模块。在电子系统的设计往系统级发展的今天,IP复用(IPReuse)技术已经引起世界范围的关注。越来越多的人开始认识到它的优越性,并努力推动基于IP复用的设计技术的发展。

一般将 IP 核分为硬核、固核和软核三种类型。软核指的是在寄存器级或门级对电路功能用 HDL 进行描述,表现为 VHDL 或 Veri I og HDL 代码。硬核指的是以版图形式描述的设计模块,它基于一定的设计工艺,而且用户不能改动。固核介于硬核和软核之间,允许用户重新定义关键的性能参数,内部连线也可以重新优化。

可综合的寄存器传输级(RTL)模型是 IP 模块的一种重要表达形式,它的最重要的特点是灵活,这些模型可以方便地从一种工艺技术转换到另一种工艺技术,也很容易从一种应用转换到另一种应用。当然,软核的开发成本相对较低,使用灵活,但其可预测性差,延时不一定能达到要求。一般,硬核的使用采用移植的方法。知识产权的要求和内部时序的要求不允许使用者更改其内部设计。硬核的开发成本相对较高,但它的可预测性强,可靠性高,能够很快地投入使用。为了对设计进行仿真,硬核必须附带有精确的时延模型。一旦工艺条件改变,则硬核必须相应改变设计。

## 1.2.2 系统芯片(SOC)设计与 IP 复用

系统芯片(SOC)也称为芯片系统,是指把一个完整的系统集成在一个芯片上,或是用一个芯片实现一个功能完整的系统。

电子工业正向系统级芯片(SOC)设计转移,如果只是简单地对当前的 IC设计方法进行改变,这种设计转移就会失败。要使SOC设计成功,就要更 多地采用知识产权 IP 模块复用。目前的设计复用方法很大程度上集中于创建"软"的、RTL 级可配置的 IP 模块,以及如何将 RTL 级设计综合成标准单元库,以及标准单元布局布线工具,最终实现硅片所需的"硬"格式。在应用 IP 模块复用方法进行设计的过程中,逐渐产生的一个问题是:在开发完一个产品后,怎么能尽快开发出其系列产品。这样就产生了新的概念—PBD,即基于平台的设计方法(Platform Based Design)。

PBD 是设计技术发展的下一阶段,它是一种基于 IP、面向特定应用领域的 SOC 设计环境,包括硬件系统,配套软件开发系统。利用基于平台的设计方法可以在更短的时间内设计出满足需要的电路。特别适合于 ASIC(专用集成电路)的应用需求,具有很大的灵活性。

目前,在32位微处理器平台方面当以ARM核为典型代表。在8位微处理器方面,目前仍以8051系列最多。如Triscend公司提供的内嵌8051核的E5系列可编程芯片。Actel公司也于2003年10月推出了采用8051内核的嵌入式系统平台Platform8051。这恐怕与Intel公司一开始将8051技术开放这一做法不无相关。应该讲,最初的8051和现今适合于用做构建SOC核心的8051核有极大的不同。例如,Cygnal公司推出的C8051F在设计上就做了很大改变,采用了一些RISC处理器的特点,废除了机器周期的概念,指令以时钟周期为运行单位。平均每个时钟可以执行完1条单周期指令,从而大大提高了指令运行速度[参见文献3]。

这也给我们一个启示,即为了设计一个适合于构建 SOC 的微控制器内核,不必拘泥于它最初的结构设计,而是在保留其基本架构和指令系统的基础上,按照 IP 核可复用的设计原则进行设计。

Mi crochi p 公司生产的 PIC 系列微控制器是当今采用 RISC 结构的主流机种之一。它具有结构简单,运行速度快,成本低廉的特点。本论文的主要任务就是分析 PIC 微控制器的工作原理,在此基础上结合可重用设计的一些

原则,构建出适合作为处理器核心的 IP 软核。

## 1.3 本论文的主要内容

本论文第二章首先用逆向设计的方法分析了 PI C16C54 微控制器,目的是了解它的工作过程和基本结构。当然,最后得到的版图和逻辑图及仿真结果本身也是一个设计成果。

第三章是论文的重点,即按照设计可重用和软 IP 核设计要求,结合第二章的结果,确定了 PIC 微控制器软核的基本架构。随后用 Veri I og 语言描述的自顶向下正向设计方法进行了设计。并最终在 FPGA 上验证了设计。

在设计过程中,我们没有拘泥于原 PIC 电路的结构,而是充分考虑了设计可重用 IP 核的一般原则,重新规划了电路的基本结构。设计过程中充分体现了软核灵活的特点,如为了方便使用,我们加入了中断系统,最后得到了 PIC16C5X 与 PIC16C55X 相当的软核。

第四章采用自顶向下的方法设计了 UART, SPI, I2C 接口。一方面,探讨了外围模块与微控制器软核的结合方法,另一方面,这些设计都是可综合的,并且在 FPGA 上得到验证,本身也是可用的 IP 软核。

第五章中按实际需要对当今流行的 USB 接口模块中的 USB1.1 接口协议进行了分析与设计。同时探讨了该模块与 PIC 微控器软核的结合方法。

第六章对论文的工作进行总结。

## 第二章 PIC16C54 电路分析

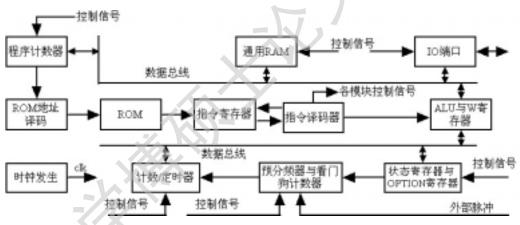

本章中我们用逆向设计的方法分析了 PIC16C54 的结构与工作过程。通过逆向电路分析,可以迅速地学习到先进的电路结构与设计方法。从而为将来的设计打下坚实的基础。分析工作从版图提取开始,随后将获得的电路输入到 Cadence 公司的 EDA 软件包中的 Composer 软件中。然后对电路逐步进行整理并用 Veri log-XL 软件进行仿真分析。PIC16C54 电路非常紧凑,估计门数在 4000 门左右。最后得到的整体框图如图 2.1 所示。本章中我们将对各模块内部结构进行分析。

图 2.1 PIC16C54 整体结构框图

## 2.1 时钟产生与控制模块

PIC 系列微处理器是精简指令集(RISC)的架构。它采用两级流水结构,除了程序执行地址变更的指令外,所有指令在一个机器周期内取指、执行完毕。一个机器周期包含四个时钟周期。芯片采用了四相不重叠时钟的方案,把一个机器周期分成四个小时序节拍 01,02,03,04。在每一个节拍内完成一个小动作,合起来组成一个机器周期。这是流水线结构的处理器常采用的指令执行方式。芯片内部的一些电路,特别是译码电路广泛采用了 CMOS 动态

Degree papers are in the "Xiamen University Electronic Theses and Dissertations Database". Full texts are available in the following ways:

- 1. If your library is a CALIS member libraries, please log on <a href="http://etd.calis.edu.cn/">http://etd.calis.edu.cn/</a> and submit requests online, or consult the interlibrary loan department in your library.

- 2. For users of non-CALIS member libraries, please mail to etd@xmu.edu.cn for delivery details.