学校编码: 10384

学号: 19820071152283

密级

## 度の大了

硕 士 学 位 论 文

# 基于数字 ASIC 设计流程的 QPSK 调制器 的设计与实现

Design and Implementation of QPSK Modulator Based on Digital ASIC Design Flow

陈冀明

李开航副教授

指导教师姓名:

肖芬教授

专业名称:

微电子学与固体电子学

论文提交日期:

2010年5月

论文答辩日期:

2010年6月

#### 厦门大学学位论文原创性声明

本人呈交的学位论文是本人在导师指导下,独立完成的研究成果。本人在论文写作中参考其他个人或集体已经发表的研究成果,均在文中以适当方式明确标明,并符合法律规范和《厦门大学研究生学术活动规范(试行)》。

另外,该学位论文为( )课题(组) 的研究成果,获得( )课题(组)经费或实验室的 资助,在( )实验室完成。(请在以上括号内填写 课题或课题组负责人或实验室名称,未有此项声明内容的,可以不作 特别声明。)

> 声明人(签名): 陈冀明 2010年 6 月 7 日

#### 厦门大学学位论文著作权使用声明

本人同意厦门大学根据《中华人民共和国学位条例暂行实施办法》等规定保留和使用此学位论文,并向主管部门或其指定机构送交学位论文(包括纸质版和电子版),允许学位论文进入厦门大学图书馆及其数据库被查阅、借阅。本人同意厦门大学将学位论文加入全国博士、硕士学位论文共建单位数据库进行检索,将学位论文的标题和摘要汇编出版,采用影印、缩印或者其它方式合理复制学位论文。

本学位论文属于:

( )1. 经厦门大学保密委员会审查核定的保密学位论文,

于 年 月 日解密,解密后适用上述授权。

( ) 2. 不保密,适用上述授权。

(请在以上相应括号内打"√"或填上相应内容。保密学位论文 应是已经厦门大学保密委员会审定过的学位论文,未经厦门大学保密 委员会审定的学位论文均为公开学位论文。此声明栏不填写的,默认 为公开学位论文,均适用上述授权。)

声明人(签名): 陈冀明

2010年 6月7 日

#### 摘要

QPSK 调制技术被广泛应用于现代通信系统中,具有频谱利用率高、频谱特性好、抗干扰性强、实现电路简单等特点。近年来移动通信和卫星通信的快速发展为其提供了更加广阔的发展空间。由于使用数字 ASIC 设计的方法实现 QPSK 调制器具有电路性能好、功耗低、体积小等优点,本文基于数字 ASIC 设计方法,设计并实现了一款基带数据频率 1Mb/s,载波频率 20MHz 的 QPSK 调制器。

本文首先介绍了 QPSK 调制系统的基本原理,并且详细分析了 QPSK 调制器各个主要功能模块的原理,包括数控振荡器、脉冲成形滤波器和插值滤波器三个部分;还将数字 ASIC 设计流程划分为前端设计和后端设计,详细介绍了流程中各个步骤完成的任务及其操作过程。其次采用自顶向下设计思想,在模块划分的基础上,先对 QPSK 调制器的各个模块进行参数及算法设计,接着用 Matlab 仿真软件进行仿真设计,最后采用 Verilog HDL 实现电路的功能和 RTL 代码,同时使用 Modelsim 对各个代码进行功能验证。在设计过程中,采用流水线、ROM 压缩等有效技术来优化电路的结构和减小电路的面积。最后本文采用 SMIC0.18 μm 工艺库,使用 Design Compiler、Primetime、Formality 和 Astro 等工程上最常用的数字 ASIC 设计软件工具,实现了逻辑综合、静态时序分析、形式验证和自动布局布线等步骤,最终完成了 OPSK 调制器的数字 ASIC 设计。

通过数字ASIC仿真测试软件验证表明,本文设计的QPSK调制器能够实现正确的功能,并且体现出较好的时序、面积、功耗等性能,在工程应用上具有一定的参考及实用价值。

关键词: QPSK 调制 数字滤波器 ASIC Verilog

#### **Abstract**

QPSK modulation techniques are widely used in modern communication systems, which are characterized with high spectrum efficiency, better spectrum specification, strong anti-interference performance, and ease of implementation. In recent years, the rapid development of mobile communications and satellite communications provide QPSK modulation techniques a wider space for future development. Using digital ASIC design to implement QPSK modulator has many advantages such as good circuit performance, low power consumption, small size, etc. In this graduation thesis, a QPSK modulator is designed and implemented based on digital ASIC design flow, with the baseband data frequency of 1Mb/s and carrier frequency of 20MHz.

Firstly, the basic principles of QPSK modulation system is introduced, the principles of all major functional modules of a QPSK modulator, including numerical control oscillator, pulse shaping filter and interpolation filter, are analyzed in detail. In this thesis, the digital ASIC design flow is divided into front-end design and back-end design, and the task and operations of each step of the process are introduced. Secondly, followed by top-down design flow and base on the module division, algorithm and parameters of the QPSK modulator's blocks are designed and then simulated using Matlab software. The circuit function and RTL code are realized using Verilog HDL while the functional verification of each code is executed using the Modelsim. In the design process, the pipeline and ROM compression method are used to optimize the structure of the circuit and to reduce the circuit area. Finally, using SMIC0.18 technology library, the digital ASIC design of the QPSK modulator is achieved, in which the logic synthesis, static timing analysis, formal verification and automatic placement and routing steps are completed using the most commonly tools for digital ASIC design flow such as the Design Compiler, Primetime, Formality and Astro software, etc.

The simulation result of the digital ASIC and test software confirm that the QPSK modulator circuits designed in this thesis realized the function of a QPSK modulator

with good sequence, small sizes, and low power consumption performance, which is of certain value both in study and in practical engineering applications.

Keywords: QPSK modulation; digital filter; ASIC; Verilog

### 目 录

| 英文摘要       II         第一章 绪论       1         1.1 课题背景       1         1.2 论文的主要工作及结构       2         第二章 QPSK 调制系统的设计原理       4         2.1 QPSK 调制原理介绍       4         2.1.1 二进制相移键控       4         2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程       16         3.2.1.2 附近的下设计       16         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2. 后端设计基本流程       21         3.2.2. 后端设计基本流程       22         3.2.2. 后端设计基本流程       22         3.2.2. 后端设计基本流程       22         3.2.2. 后端设计基本流程       22         3.2.2. 月 自动中局布线       22         3.2.2. 月 PRI 和用 <th>中文</th> <th>摘要</th> <th>•••••</th> <th>••••••</th> <th>••••••</th> <th>••••••</th> <th>•••••••</th> <th>I</th> | 中文         | 摘要      | •••••    | ••••••                                 | •••••• | ••••••     | •••••••             | I  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|----------|----------------------------------------|--------|------------|---------------------|----|

| 1.1 课题背景 1.2 论文的主要工作及结构 2.2 第二章 QPSK 调制系统的设计原理 4 2.1 QPSK 调制原理介绍 4 2.1.1 二进制相移键控 4 2.1.2 四进制相移键控 5 2.2.1 数控振荡器的原理 6 2.2.2 成形滤波器的原理 9 2.2.3 插值滤波器的原理 12 2.3 本章小结 13 第三章 数字 ASIC 设计流程 14 3.1 数字集成电路设计方法 14 3.1.1 自底向上设计 14 3.1.2 自顶向下设计 15 3.2 数字 ASIC 设计流程 16 3.2.1 前端设计基本流程 16 3.2.1 模块划分和 RTL 代码偏写 16 3.2.1.1 模块划分和 RTL 代码编写 16 3.2.1.2 RTL 代码仿真 17 3.2.1.3 逻辑综合和优化 18 3.2.1.4 形式验证与静态时序分析 19 3.2.2 后端设计基本流程 21 3.2.2 形式验证与静态时序分析 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 英文         | 摘要      | •••••    |                                        | •••••• | •••••      | ••••••              | II |

| 第二章 QPSK 调制系统的设计原理 4  2.1 QPSK 调制原理介绍 4 2.1.1 二进制相移键控. 4 2.1.2 四进制相移键控. 4 2.1.2 四进制相移键控. 5 2.2.1 数控振荡器的原理 66 2.2.2 成形滤波器的原理 9 2.2.3 插值滤波器的原理 12 2.3 本章小结 13  第三章 数字 ASIC 设计流程 14 3.1 1 自底向上设计 14 3.1.1 自底向上设计 14 3.1.2 自页向下设计 15  3.2 数字 ASIC 设计流程 16 3.2.1 前端设计基本流程 16 3.2.1 前端设计基本流程 16 3.2.1.1 模块划分和 RTL 代码编写 16 3.2.1.2 RTL 代码仿真. 17 3.2.1.3 逻辑综合和优化 18 3.2.1.4 形式验证与静态时序分析 19 3.2.2 后端设计基本流程 21 3.2.2.1 自动布局布线 22 3.2.2.1 自动布局布线 22 3.2.2.1 自动布局布线 22 3.2.2.1 形式验证与静态时序分析 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 第一         | 章 绪说    | <b>ት</b> |                                        | •••••  | •••••      |                     | 1  |

| 第二章 QPSK 调制系统的设计原理 4  2.1 QPSK 调制原理介绍 4 2.1.1 二进制相移键控. 4 2.1.2 四进制相移键控. 4 2.1.2 四进制相移键控. 5 2.2.1 数控振荡器的原理 66 2.2.2 成形滤波器的原理 9 2.2.3 插值滤波器的原理 12 2.3 本章小结 13  第三章 数字 ASIC 设计流程 14 3.1 1 自底向上设计 14 3.1.1 自底向上设计 14 3.1.2 自页向下设计 15  3.2 数字 ASIC 设计流程 16 3.2.1 前端设计基本流程 16 3.2.1 前端设计基本流程 16 3.2.1.1 模块划分和 RTL 代码编写 16 3.2.1.2 RTL 代码仿真. 17 3.2.1.3 逻辑综合和优化 18 3.2.1.4 形式验证与静态时序分析 19 3.2.2 后端设计基本流程 21 3.2.2.1 自动布局布线 22 3.2.2.1 自动布局布线 22 3.2.2.1 自动布局布线 22 3.2.2.1 形式验证与静态时序分析 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1          | 1 油品    | ᄕ모       |                                        |        |            |                     |    |

| 第二章 QPSK 调制系统的设计原理       4         2.1 QPSK 调制原理介绍       4         2.1.1 二进制相移键控       4         2.1.2 四进制相移键控       4         2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1.1 自底向上设计       14         3.2.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 1 床巡り   | 月京       | ······································ | •••••  | ••••••     |                     | 1  |

| 2.1 QPSK 调制原理介绍       4         2.1.1 二进制相移键控       4         2.1.2 四进制相移键控       4         2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真       16         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |         |          |                                        |        |            |                     |    |

| 2.1 QPSK 调制原理介绍       4         2.1.1 二进制相移键控       4         2.1.2 四进制相移键控       4         2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真       16         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 第二         | 章 QPS   | SK 调制    | <b>制系统的设</b>                           | 计原理…   |            |                     | 4  |

| 2.1.1 二进制相移键控. 4 2.1.2 四进制相移键控. 4 2.2 QPSK 调制关键模块原理分析 5 2.2.1 数控振荡器的原理. 6 2.2.2 成形滤波器的原理. 9 2.2.3 插值滤波器的原理. 12 2.3 本章小结 13 第三章 数字 ASIC 设计流程 14 3.1 数字集成电路设计方法 14 3.1.1 自底向上设计. 14 3.1.2 自顶向下设计. 15 3.2 数字 ASIC 设计流程 16 3.2.1 前端设计基本流程 16 3.2.1.1 模块划分和 RTL 代码编写 16 3.2.1.2 RTL 代码仿真. 17 3.2.1.3 逻辑综合和优化 18 3.2.1.4 形式验证与静态时序分析 19 3.2.2 后端设计基本流程 21 3.2.2.1 自动布局布线 22 3.2.2.2 形式验证与静态时序分析 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |         |          |                                        |        |            |                     |    |

| 2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1 数字集成电路设计方法       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程       16         3.2.1.2 RTL 代码仿真       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ۷.         |         |          |                                        |        |            |                     |    |

| 2.2 QPSK 调制关键模块原理分析       5         2.2.1 数控振荡器的原理       6         2.2.2 成形滤波器的原理       9         2.2.3 插值滤波器的原理       12         2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1 数字集成电路设计方法       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程       16         3.2.1.2 RTL 代码仿真       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | 2.1.1   | 一、江市     |                                        |        | <b>X</b> 5 | • • • • • • • • • • | 4  |

| 2. 2. 1 数控振荡器的原理                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2          |         |          |                                        |        |            |                     |    |

| 2. 2. 2 成形滤波器的原理                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.         |         |          |                                        |        |            |                     |    |

| 2. 2. 3 插值滤波器的原理                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |         |          |                                        |        |            |                     |    |

| 2.3 本章小结       13         第三章 数字 ASIC 设计流程       14         3.1 数字集成电路设计方法       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |         |          |                                        |        |            |                     |    |

| 第三章 数字 ASIC 设计流程143.1 数字集成电路设计方法143.1.1 自底向上设计153.2 数字 ASIC 设计流程163.2.1 前端设计基本流程163.2.1.1 模块划分和 RTL 代码编写163.2.1.2 RTL 代码仿真173.2.1.3 逻辑综合和优化183.2.1.4 形式验证与静态时序分析193.2.2 后端设计基本流程213.2.2.1 自动布局布线223.2.2.2 形式验证与静态时序分析23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |         |          |                                        |        |            |                     |    |

| 3.1 数字集成电路设计方法       14         3.1.1 自底向上设计       14         3.1.2 自顶向下设计       15         3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程       21         3.2.2.1 自动布局布线       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          | 3 本章小   | 卜结       |                                        | •••••  | •••••      | •••••               | 13 |

| 3. 1. 1 自底向上设计                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 第三         | 章 数字    | Z ASIO   | 设计流程                                   |        | ••••••     | •••••••             | 14 |

| 3. 1. 2 自顶向下设计                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.         | 1 数字组   | [成电路     | 路设计方法                                  | •••••  | •••••      |                     | 14 |

| 3.2 数字 ASIC 设计流程       16         3.2.1 前端设计基本流程.       16         3.2.1.1 模块划分和 RTL 代码编写       16         3.2.1.2 RTL 代码仿真.       17         3.2.1.3 逻辑综合和优化       18         3.2.1.4 形式验证与静态时序分析       19         3.2.2 后端设计基本流程.       21         3.2.2.1 自动布局布线.       22         3.2.2.2 形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | 3. 1. 1 | 自底向      | ]上设计                                   |        |            |                     | 14 |

| 3. 2. 1 前端设计基本流程.       16         3. 2. 1. 1 模块划分和 RTL 代码编写.       16         3. 2. 1. 2 RTL 代码仿真.       17         3. 2. 1. 3 逻辑综合和优化.       18         3. 2. 1. 4 形式验证与静态时序分析.       19         3. 2. 2 后端设计基本流程.       21         3. 2. 2. 1 自动布局布线.       22         3. 2. 2. 2 形式验证与静态时序分析.       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>///</b> | 3. 1. 2 | 自顶向      | ]下设计                                   |        |            |                     | 15 |

| 3. 2. 1 前端设计基本流程.       16         3. 2. 1. 1 模块划分和 RTL 代码编写.       16         3. 2. 1. 2 RTL 代码仿真.       17         3. 2. 1. 3 逻辑综合和优化.       18         3. 2. 1. 4 形式验证与静态时序分析.       19         3. 2. 2 后端设计基本流程.       21         3. 2. 2. 1 自动布局布线.       22         3. 2. 2. 2 形式验证与静态时序分析.       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.         | 2 数字 A  | ASIC 设   | 计流程                                    |        |            | ••••                | 16 |

| 3. 2. 1. 2       RTL 代码仿真.       17         3. 2. 1. 3       逻辑综合和优化.       18         3. 2. 1. 4       形式验证与静态时序分析.       19         3. 2. 2       后端设计基本流程.       21         3. 2. 2. 1       自动布局布线.       22         3. 2. 2. 2       形式验证与静态时序分析.       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |         | 前端设      | 计基本流程                                  |        |            |                     | 16 |

| 3. 2. 1. 3       逻辑综合和优化       18         3. 2. 1. 4       形式验证与静态时序分析       19         3. 2. 2       后端设计基本流程       21         3. 2. 2. 1       自动布局布线       22         3. 2. 2. 2       形式验证与静态时序分析       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |         |          |                                        |        | -          |                     |    |

| 3. 2. 1. 4       形式验证与静态时序分析                                                                                                             <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |         |          |                                        | -      |            |                     |    |

| 3. 2. 2. 1 自动布局布线                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |         |          |                                        |        |            |                     |    |

| 3. 2. 2. 2 形式验证与静态时序分析                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 3. 2. 2 | 后端设      | 计基本流程                                  |        |            |                     | 21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |         |          |                                        | •      |            |                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |         |          |                                        |        |            |                     |    |

| 3.3 本章小结 24                   |

|-------------------------------|

| 第四章 QPSK 调制系统 Verilog 设计与仿真25 |

| 4.1 可综合的 Verilog 代码25         |

| 4.2 数控振荡器的设计与仿真26             |

| 4.2.1 相位累加器设计仿真27             |

| 4.2.2 相幅转换器设计仿真30             |

| 4.2.3 相位偏移控制器设计仿真34           |

| 4.3 脉冲成形滤波器设计仿真35             |

| 4.4 插值滤波器设计仿真42               |

| 4.5 串并转换与星座映射模块设计仿真45         |

| 4.6 本章小结 46                   |

| 第五章 QPSK 调制系统数字 ASIC 实现47     |

| 5.1 QPSK 调制系统的逻辑综合优化47        |

| 5.1.1 逻辑综合优化过程简介48            |

| 5.1.2 DDS 的综合优化50             |

| 5.1.3 QPSK 调制系统的综合优化57        |

| 5.2 QPSK 调制系统的静态时序分析和形式验证59   |

| 5.3 QPSK 调制系统的自动布局布线61        |

| 5.4 本章小结65                    |

| 第六章 总结与展望66                   |

| 6.1 工作总结 66                   |

| 6.2 设计展望 66                   |

| 参 考 文 献68                     |

| 致 谢71                         |

| 攻读硕士学位期间发表的论文72               |

#### **Table of contents**

| Abstract in Chinese                                    | I  |

|--------------------------------------------------------|----|

| Abstract in English                                    | II |

| Chapter 1 Introduction                                 | 1  |

| 1.1 Subject background                                 | 1  |

| 1.2 Work and structure of thesis                       | 2  |

| Chapter 2 Design principles of QPSK modulation systems |    |

| 2.1 Introduce the principles of QPSK modulation        | 4  |

| 2.1.1 Binary Phase Shift Keying                        | 4  |

| 2.1.2 Quaternary phase shift keying                    | 4  |

| 2.2 Principle of key modules in QPSK modulation        | 5  |

| 2.2.1 Principles of numerical control oscillator       | 6  |

| 2.2.2 Principle of pulse shaping filter                | 9  |

| 2.2.3 Principle of interpolation filter                |    |

| 2.3 Summary                                            | 13 |

| Chapter 3 Design flow of digital ASIC                  | 14 |

| 3.1 Design method of digital                           | 14 |

| 3.1.1 Bottom-up design                                 | 14 |

| 3.1.2 Top-down design                                  | 15 |

| 3.2 Design flow of digital ASIC                        | 16 |

| 3.2.1 the basic process of Front-end design            |    |

| 3.2.1.1 Module division and RTL coding                 |    |

| 3.2.1.3 logic synthesis and optimization               |    |

| 3.2.1.4 Formal verification and static timing analysis |    |

| 3.2.2 The basic process of Back-end design             |    |

| 3.2.2.1 Automatic placement and routing                |    |

| 3.2.2.3 DRC and LVS verification                       | 23 |

| 3.3 summary                                                                      | 24     |

|----------------------------------------------------------------------------------|--------|

| Chapter 4 Design and Simulation of the QPSK modulation s                         | system |

| using Verilog                                                                    | 25     |

| 4.1 Verilog code can be integrated                                               | 25     |

| 4.2 Design and Simulation of Numerically Controlled Oscillator                   | 26     |

| 4.2.1 Design and Simulation of the phase accumulator                             | 27     |

| 4.2.2 Design and simulation phase and amplitude converter                        | 30     |

| 4.2.3 Design and simulation of phase shift controller                            |        |

| 4.3 Design and simulation of pulse shaping filter                                | 35     |

| 4.4 Design and simulation of interpolation Filter                                | 42     |

| 4.5 Design and simulation of serial parallel conversion and const mapping blocks |        |

| 4.6 summary                                                                      | 46     |

| Chapter 5 Digital ASIC implementation of QPSK modulation s                       |        |

| 5.1 logic synthesis and optimization of QPSK modulation system                   | 47     |

| 5.1.1 Description logic synthesis optimization process                           |        |

| 5.1.2 Logic synthesis and optimization of DDS                                    | 50     |

| 5.1.3 logic synthesis and optimization of QPSK modulation system                 | 57     |

| 5.2 Formal verification and static timing analysis of QPSK mod system            |        |

| 5.3 Automatic placement and routing of QPSK modulation system                    | 61     |

| 5.4 Summary                                                                      | 65     |

| Chapter 6 Summary and Outlook                                                    | 66     |

| 6.1 Work Summary                                                                 | 66     |

| 6.2 Design Forecast                                                              | 66     |

| References                                                                       | 68     |

| Acknowledgement                                                                  | 71     |

#### 第一章 绪论

#### 1.1 课题背景

通信是人类生活中不可或缺的部分,如何更加方便及有效地传输信息一直是 通信中的重点。自从19世纪人们使用电信号传输信号后,信号调制已成为通信学 中很重要的一部分。信号调制是指使用信号 f(t) 来控制载波的某一个或者几个 参数,使载波按照信号 f(t) 的规律变化的技术。调制实现了频率搬移,其目的 主要有:(1)、改变信号频率便于信道传输。在无线通信中,为了充分发挥天线 的功能,一般规定天线尺寸大于信号波长的十分之一。而基带信号一般包含直流 分量和低频分量,如果直接发射基带信号,天线尺寸可能达到几十公里,这是不 可能进行应用的。通过对基带信号的调制,可以将信号频谱搬移到任意合适的频 率范围,从而便于发射传输。(2)、改变信号的频率分量构成,实现与信道特性 的匹配。通信的信号需要在各种不同的信道中传输,如果信号的频率特性与信道 特性不匹配,就可能引入太多的干扰,从而影响通信质量。例如部分信号所占的 频谱范围比较大, 在信道传输过程中可能会引起传输特性的改变。此时就可以通 过调制将信号的带宽限制在较小的范围内,使传输特性的变化减小。(3)、实现 信道复用。通常一个信道的信息容量可以传输多个信号,但是如果直接传输基带 信号,就会在各个信号之间引入干扰。通过各种不同的调制,就可以实现在一个 信道中同时传输许多信号的目的。例如通过频域调制,将各个信号的频谱限制在 互不重叠的频率范围,可以实现频分复用;通过时域调制,使信号在不同时间交 错传输,可以实现时分复用等[1]。

随着通信技术的发展,信号调制技术也得到了长足的进步。按照对载波不同的参数进行调整分类,可以将调制方式划分为调幅调制、调频调制和调相调制。如果是使用数字信号对载波进行调制,相对应的可以将调制方式划分为振幅键控、频移键控和相移键控。相对其他的数字信号调制方式,QPSK调制具有更高的频率利用率,更强的抗干扰能力以及更简单的电路实现。QPSK调制的另外一个特点是可以使用全数字方法实现,可以减小调制电路面积,降低成本。因此OPSK调制广泛地应用于数字微波通信和卫星通信等领域<sup>[2]</sup>。

数字信号理论和微电子技术的快速发展使得采用数字集成电路来设计QPSK调制系统成为可能。使用HDL语言可以方便地对QPSK调制电路的功能及其结构进行设计及仿真,根据功能要求随时调整电路设计,提高了设计的灵活性,缩短了设计周期。相对于数字信号处理器 (DSP) 和现场可编程逻辑门阵列 (FPGA),专用集成电路 (ASIC) 在电路成本、性能、面积及功耗上具有明显的优势,因此数字ASIC设计方法在通信领域得到了广泛的应用<sup>[3]</sup>。

目前国外已出现的许多全数字QPSK调制解调器方面的研究成果和芯片。例如STEL公司的STEL-1109; 意法半导体公司(ST)的ST5518、STV6110A; 比利时纽泰克(Newtec)公司的NTC-2280等。

国内的QPSK调制解调器方面的成果和芯片也十分丰富。例如凌讯公司的LGS-8934-A1,它支持中国数字电视地面广播传输标准,主要用于移动接收,支持高清及标清电视和其它多媒体服务的广播传输,适用于各种低功耗、小体积的电视接收终端产品。富士通的MB86A15,它主要用于数字卫星广播,包括调谐器、QPSK解调器和前向错误纠正器(FEC)。泰合志恒的TP3021主要应用于中国移动多媒体广播,在同一封装里集成了解调器和调谐器,接收性能在QPSK调制方式下为99.6dBm。

但是这些芯片主要是针对无线通信和卫星通信,大部分偏向于QPSK解调方面的性能,由于它们的针对性很强,电路的灵活性也很差。同时国内还存在着许多以FPGA和DSP为核心的QPSK调制解调器,这些芯片处理速度慢,芯片成本高。因此设计实现一款基于数字ASIC的QPSK调制电路具有实际的工程意义。

#### 1.2 论文的主要工作及结构

本文基于数字ASIC设计方法设计并实现了QPSK调制电路,主要工作包括以下几个方面:分析了QPSK调制原理和主要模块的工作原理;介绍了数字ASIC设计基本流程;基于数字ASIC设计流程,完成了数字ASIC的前端和后端设计,实现了QPSK调制电路的功能和版图。

本文共分为六章,各章主要内容如下:

第一章为绪论,首先介绍了课题的研究背景,并且简要介绍了国内外QPSK的发展现状,最后概括了本文的主要工作及其结构。

第二章为QPSK调制的主要原理,包括QPSK调制的基本原理,各个主要功能模块的工作及设计原理,并且给出QPSK调制系统的基本框图。

第三章为数字ASIC的设计流程,在分析了目前常用的设计方法后,将数字 ASIC设计流程分为前端设计和后端设计,对每个步骤的操作和原理进行介绍。

第四章为QPSK调制系统的Verilog设计仿真,在这章中根据QPSK调整系统各个模块的基本原理,对每个模块进行详细的设计,并且进行功能仿真,得到正确的Verilog代码。

第五章为QPSK调制系统的数字ASIC设计流程,在这章中实现了从综合优化 到自动布局布线的各个步骤,并且对每个步骤的操作过程和结果进行分析,最后 得到QPSK调整系统的版图。

第六章为总结和展望,对论文的工作进行总结,并对未来的工作方向进行展望。

#### 第二章 QPSK 调制系统的设计原理

#### 2.1 QPSK 调制原理介绍

#### 2.1.1 二进制相移键控

相移键控是目前扩频通信中使用较多的一种调制方式,相移键控是利用载波的相位或者其变化来传输数字信号的,其中最基本的是二进制相移键控(BPSK)。

在二进制相移键控(BPSK)中,载波的幅度和频率不变,而其相位0和 $\pi$ 分别对应于码元0和1。对载波调制的已调信号可以表示为:

$$S_{(bpsk)} = A(t)\cos[\omega_0 t + \theta(t)]$$

(2.1)

其中 $\omega_0$ 是载波的角频率, $\theta(t)$ 是调制的载波相位取值。由于BPSK是对数字信号进行调制,因而A(t)可以用 $\sum_n g(t-nT)$ 代替。其中g(t)为数字信号波形,T为数字信号的周期,在一个周期内 $\theta(t)$ 保持不变。于是,BPSK信号就可以表示为[4]:

$$S_{(bpsk)} = \begin{cases} +\sum_{n} g(t - nT)\cos\omega_{0}t & "0" \\ -\sum_{n} g(t - nT)\cos\omega_{0}t & "1" \end{cases}$$

(2.2)

#### 2.1.2 四进制相移键控

如果用载波的多个不同相位来表示多进制数字信号,该调制方式就是多进制相移键控(MPSK)。如果载波有 2<sup>n</sup> 个相位,它就可以代表n位二进制码元的不同组合的信息。MPSK中常用的一种调制就是四进制相移键控,它也称为正交相移键控(Quadrature Phase Shift Keying, QPSK),是利用载波的四个不同的相位来代表数字信息的调制信号。

QPSK已调信号可表示为:

$$S_{(qpsk)} = \sum_{n} g(t - nT)\cos[\omega_0 t + \theta(t)]$$

(2.3)

其中各个参数与二进制相移键控的含义一样。在一个信号周期内, $\theta(t)$  保持不变,设为 $\phi_t$ 。将上式展开,可以得到:

$$S_{(qpsk)} = \left[\sum_{n} g(t - nT)\cos\varphi_{k}\right]\cos\omega_{0}t + \left[\sum_{n} g(t - nT)\sin\varphi_{k}\right]\sin\omega_{0}t$$

$$= I_{k}\cos\omega_{0}t + Q_{k}\sin\omega_{0}t \qquad kT \le t \le kT + 1 \qquad (2.4)$$

其中令  $I_k = [\sum_n g(t-nT)\cos\varphi_k]$  ,  $Q_k = [\sum_n g(t-nT)\sin\varphi_k]$  。则QPSK调制可用两路分量来传递信息,  $I_k$  为第k个符号的同相分量,  $Q_k$  为第k个符号的正交分量。

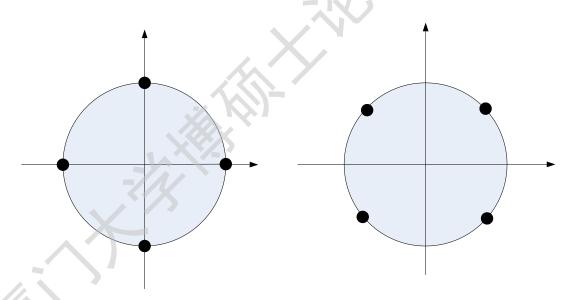

在QPSK调制中,四个相位对应于两位二进制数的不同组合,这种对应关系又存在 $\frac{\pi}{2}$ 体系和 $\frac{\pi}{4}$ 体系两种。在 $\frac{\pi}{2}$ 体系中,相位选择0, $\frac{\pi}{2}$ , $\pi$ , $\frac{3}{2}$  $\pi$ 四个离散值;在 $\frac{\pi}{4}$ 体系中,相位选择 $\frac{\pi}{4}$ , $\frac{3}{4}$  $\pi$ , $\frac{5}{4}$  $\pi$ , $\frac{7}{4}$  $\pi$ 四个离散值。由 $I_k$ 和 $Q_k$ 的公式,可以得知两个分量合成的矢量点会落在同一圆周上。在坐标轴上将二进制数与相位的对应关系表示出来,这种图称为QPSK的相位星图。

**图 2.1** QPSK 调制  $\frac{\pi}{2}$  体系与  $\frac{\pi}{4}$  体系相位星图

#### 2.2 QPSK 调制关键模块原理分析

根据上一节的理论,本文采用的QPSK调制原理框图如图2-2所示<sup>[5]</sup>。本节将对原理框图中关键的功能模块的原理进行简要的分析。

Q

Degree papers are in the "Xiamen University Electronic Theses and Dissertations Database". Full texts are available in the following ways:

- 1. If your library is a CALIS member libraries, please log on <a href="http://etd.calis.edu.cn/">http://etd.calis.edu.cn/</a> and submit requests online, or consult the interlibrary loan department in your library.

- 2. For users of non-CALIS member libraries, please mail to etd@xmu.edu.cn for delivery details.