# The Development of a High Performance Digital RF Transmitter for NMR

By

Shaw Wei Cheoo

A thesis submitted to the Victoria University of Wellington in fulfilment of the requirements for the degree of Master of Engineering in Electronic Engineering.

Victoria University of Wellington 2012

#### **Abstract**

This Master's thesis consists of the development of a Nuclear Magnetic Resonance (NMR) Radio Frequency (RF) transmitter, which is a core electronic subsystem of an NMR system. The main purpose of this research is to contribute to the application of NMR, which is a new sensing technology that has yet to be fully implemented into the everyday world. One of the barriers to adopting this technology is its complexity. However, the invention of high speed digital FPGAs (Field Programmable Gate Array) such as the Spartan series has made it easier to develop high performance NMR systems over recent years. The major contribution to this research is the development of faster digital signal processing hardware, and methodologies that have been implemented on a single chip. This has reduced the size and the cost of the electronic subsystem and contributed towards the evolution of NMR as a general tool. This thesis introduces the concept of implementing a high-speed NMR RF multi-frequency transmitter by using multiple Direct Digital Synthesis (DDS) cores to generate sine-waves, which range from 100 kHz to 750 MHz. The research required three stages to be achieved, beginning with conceptual design of a high-speed transmitter using MATLAB-Simulink, RTL-level (Register-Transfer Level) simulation and hardware implementation, which included hardware testing on a prototype board. This Master's research is to seek a solution to building a multi-core DDS module in an FPGA device. In other words, the research work focuses on finding an alternative solution to constructing a DDS system. The project involves building up the VHSIC Hardware Description Language (VHDL) program to work beyond the hardware limitation of an FPGA device. Hence, the final solution does not consider any noise impact due to the structure of the developed system.

## **Acknowledgements**

I wish to express my sincere thanks to my supervisor and co-supervisor, Dr. Robin Dykstra and Dr. Paul Teal for providing me with all the necessary suggestions toward my research.

I place on record my sincerest gratitude to the committee members Prof Dale Carnegie, Dr. Christopher Hollitt and Dr. Alex Potanin in helping me in the conversion to Master's level and for their extreme patience in the face of numerous obstacles.

I also want to thank my fellow PhD students for their constant encouragement, support, feedback and friendship. I am extremely grateful and indebted to them for their expert, sincere and valuable guidance extended to me.

I take this opportunity to record my sincere thanks to my family in Malaysia for their unceasing encouragement and support.

Finally yet importantly, I would like to thank everyone who, directly or indirectly, has lent me their hand while I encountered problems in New Zealand.

# **Table of Contents**

| Abst | ract     |                                                          | i    |

|------|----------|----------------------------------------------------------|------|

| Ackn | owledg   | ement                                                    | ii   |

| List | of Table | es s                                                     | viii |

| List | of Figur | es                                                       | ix   |

| Tabl | e of Abl | previations                                              | xiv  |

| Chap | oter 1   | Introduction                                             | 1    |

| 1.1  | Probl    | em Statement                                             | 1    |

| 1.2  | Over     | view of proposed NMR RF transmitter                      | 3    |

| 1.3  | Intro    | duction of NMR RF transmitter in NMR spectroscopy        | 4    |

|      | 1.3.1    | Phase Coherent                                           | 5    |

| 1.4  | Thesi    | s Motivation                                             | 6    |

|      | 1.4.1    | Challenges of an NMR RF Transmitter for NMR Applications | 6    |

|      | 1.4.2    | Limitations of Current of RF Transmitter                 | 8    |

|      |          | 1.4.2.1 Deficiency of NMR RF Transmitter                 | 8    |

|      |          | 1.4.2.2 NMR RF Transmitter with External DDS             | 9    |

|      |          | 1.4.2.3 FPGA-based NMR RF Transmitter                    | 10   |

| 1.5  | Resea    | orch Goals                                               | 11   |

| 1.6  | Orga     | nisation of Thesis                                       | 14   |

| Chap | oter 2   | Background                                               | 15   |

| 2.1  | NMR      | Transceiver                                              | 15   |

| 2.2  | Fund     | amentals of the Sinusoidal Oscillator                    | 17   |

|      | 2.2.1    | Recursive Oscillators                                    | 17   |

| 2.3  | Direc    | t Digital Synthesis                                      | 18   |

|      | 2.3.1    | Phase Accumulator                                        | 19   |

|      | 2.3.2    | Phase-to-Amplitude Converter                             | 21   |

|      | 2.3.3    | Phase Truncation                                         | 22   |

|      | 2.3.4    | CORDIC                                                   | 28   |

|      |          | 2.3.4.1 Rotation Mode                                    | 29   |

|      |        | 2.3.4.2 Vectoring Mode                              | 31 |

|------|--------|-----------------------------------------------------|----|

|      |        | 2.3.4.3 Sine and Cosine Function                    | 33 |

|      | 2.3.5  | DAC                                                 | 34 |

| 2.4  | Comp   | arisons between LUT-based DDS and CORDIC Algorithm  | 35 |

| 2.5  | FPGA   |                                                     | 37 |

| 2.6  | Sparta | an-6 (XC6SL45T)                                     | 40 |

|      | 2.6.1  | Basic Architecture of Spartan-6                     | 42 |

|      | 2.6.2  | CLB                                                 | 46 |

|      | 2.6.3  | LUT                                                 | 48 |

|      | 2.6.4  | Storage Elements                                    | 49 |

|      | 2.6.5  | Multiplexers                                        | 49 |

|      | 2.6.6  | Carry Logic                                         | 49 |

|      | 2.6.7  | Distributed RAM                                     | 49 |

|      | 2.6.8  | Shift Registers                                     | 49 |

|      | 2.6.9  | I/O Architecture of Spartan-6                       | 51 |

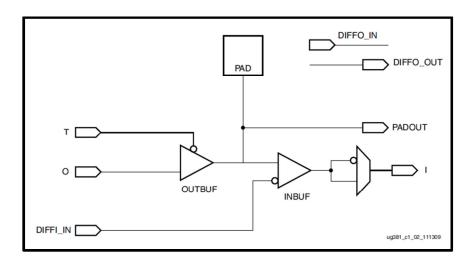

|      |        | 2.6.9.1 IOB                                         | 52 |

|      |        | 2.6.9.2 Input/Output Logic Resources                | 52 |

|      | 2.6.10 | Input/ Output Serialisation and Deserialisation     | 54 |

|      |        | (ISERDES and OSERDES)                               |    |

|      | 2.6.11 | Clock Resources                                     | 55 |

|      | 2.6.12 | Other Resources of Spartan-6                        | 57 |

| 2.7  | Develo | opment Tools                                        | 58 |

| 2.8  | Summ   | nary                                                | 59 |

| Chap | oter 3 | Design and Development                              | 60 |

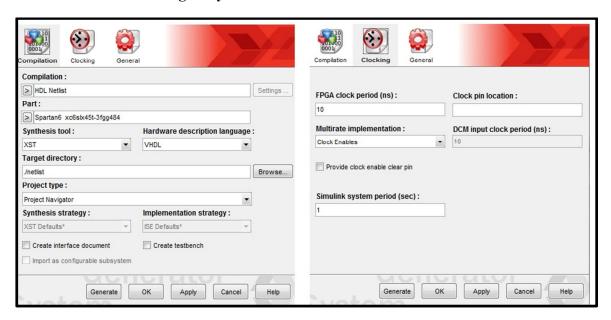

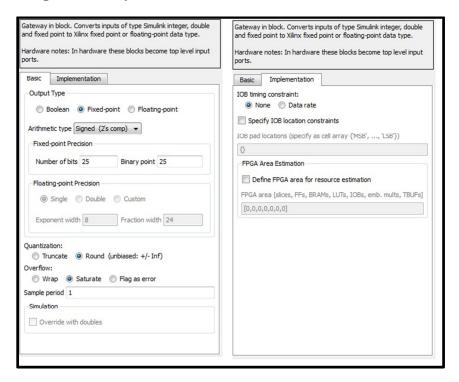

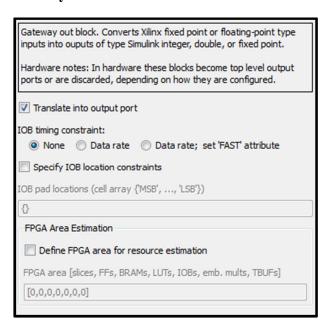

| 3.1  | High-l | level Simulation of a DDS core with MATLAB-Simulink | 60 |

|      | 3.1.1  | Design Requirements                                 | 62 |

|      | 3.1.2  | Matlab-Simulink of a Basic DDS System               | 64 |

| 3.2  | Conce  | ptual Design of an 8-Core DDS System                | 66 |

|      | 3.2.1  | Design Requirements                                 | 66 |

|      | 3.2.2  | Simulink of an 8-Core DDS Module                    | 67 |

|      | 3.2.3  | Phase Register and Minimum Phase Offset Calculation | 69 |

|      |        | 3.2.3.1 Phase Register                              | 69 |

|      |        | 3.2.3.2 Eight Phase Offsets and Step Size           | 71 |

|     | 3.2.4 | 2 GHz I   | DDS System                                              | 74  |

|-----|-------|-----------|---------------------------------------------------------|-----|

|     |       | 3.2.4.1   | 2 GHz Phase Accumulator                                 | 74  |

|     |       | 3.2.4.2   | Sine LUT Module                                         | 76  |

|     | 3.2.5 | 2 GHz I   | DAC Module (Mock)                                       | 78  |

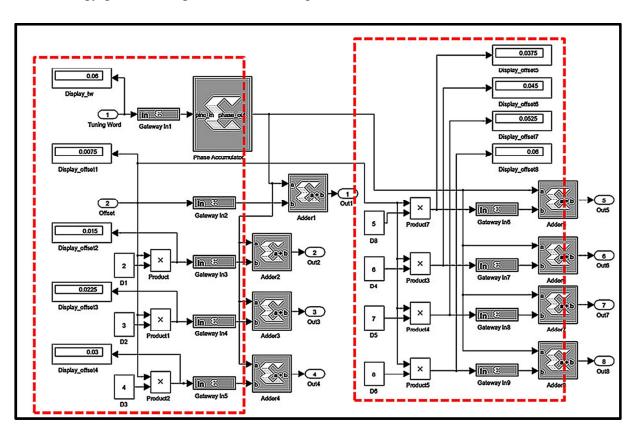

| 3.3 | Conce | eptual De | sign of a Multi-Frequency RF Generator                  | 80  |

|     | 3.3.1 | Design 1  | Requirements                                            | 80  |

|     | 3.3.2 | Simulin   | k of Multi-Frequency RF Generator                       | 81  |

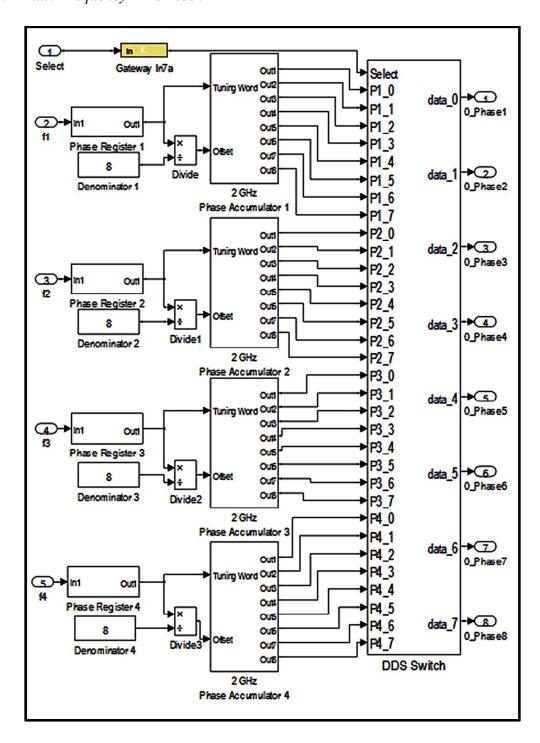

|     |       | 3.3.2.1   | Multi-Frequency DDS block                               | 83  |

| 3.4 | MAT   | LAB-Sim   | ulink Simulation Results                                | 87  |

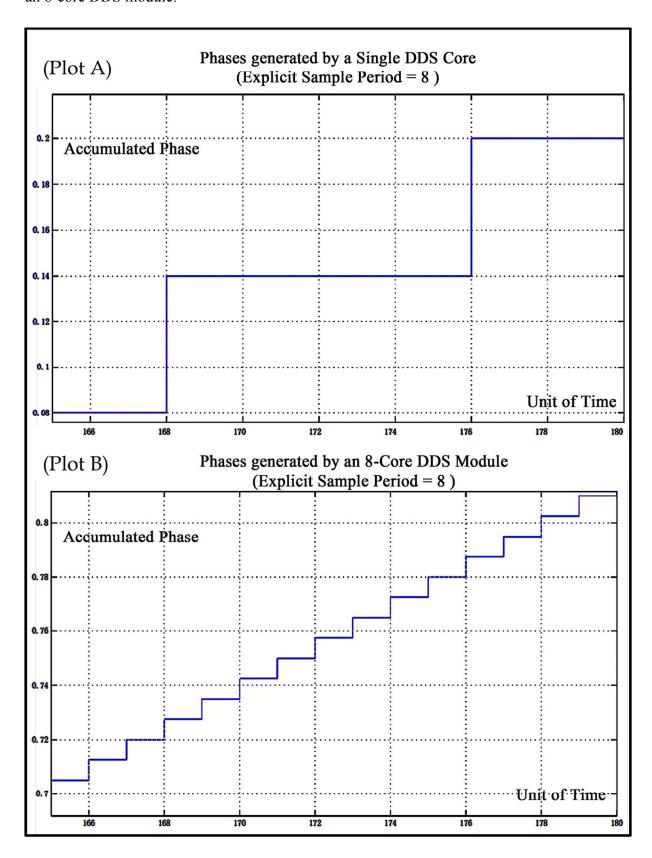

|     | 3.4.1 | Simulat   | ion Results of a Single DDS Core                        | 87  |

|     | 3.4.2 | Simulat   | ion of an 8-Core DDS Module                             | 91  |

|     |       | 3.4.2.1   | Simulation Results of Phase Offset                      | 92  |

|     |       | 3.4.2.2   | Simulation Results of an 8-Core DDS Module              | 94  |

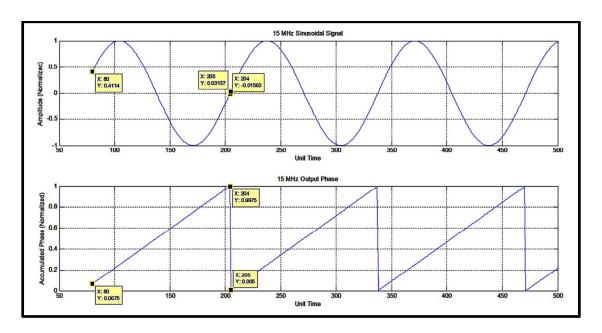

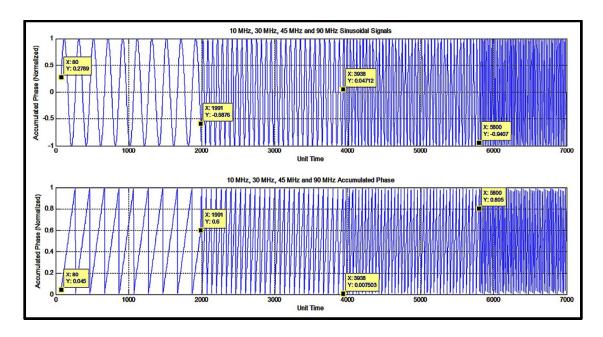

|     | 3.4.3 | Simulatio | n Results of a Multi-Frequency RF Generator             | 99  |

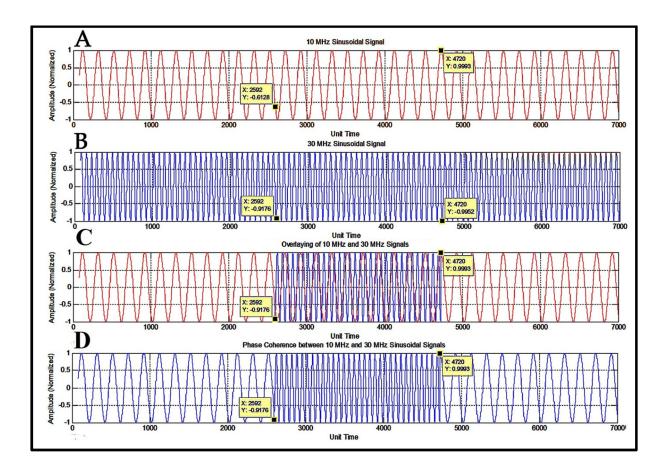

|     |       | 3.4.3.1   | Simulation results of Phase Coherence for               | 101 |

|     |       |           | Multi-Frequency RF Generator                            |     |

| 3.5 | RTL-  | Level Sin | nulation of DDS using FPGA                              | 103 |

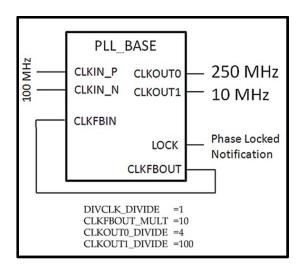

|     | 3.5.1 | Architec  | cture of PLL                                            | 103 |

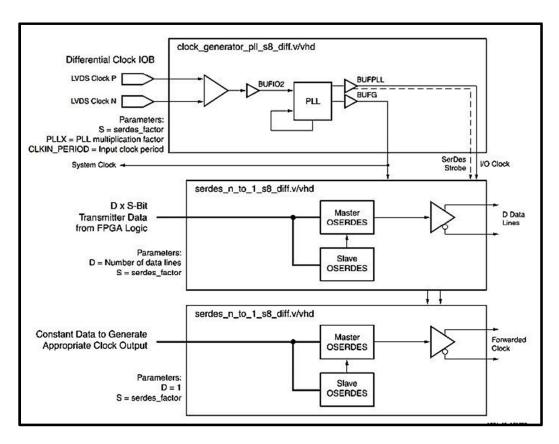

|     | 3.5.2 | OSERD     | ES Module                                               | 107 |

|     | 3.5.3 | Develop   | oment of a Test-bench file                              | 109 |

|     | 3.5.4 | RTL-Le    | evel of a Single DDS Core                               | 111 |

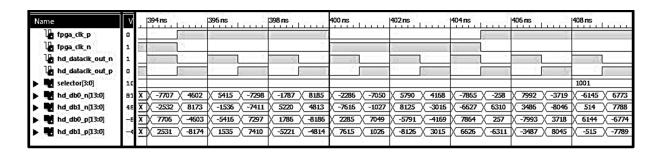

|     |       | 3.5.4.1   | Simulation Results of a Single DDS Core Module          | 113 |

|     | 3.5.5 | Develop   | oment of an 8-Core DDS System                           | 117 |

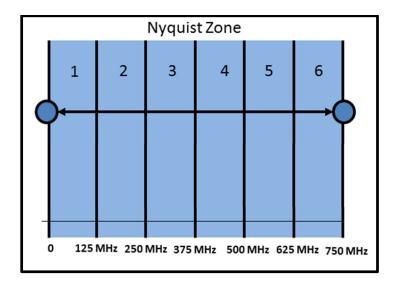

|     |       | 3.5.5.1   | Overview of Nyquist Zones of an 8-Core DDS System       | 118 |

|     |       | 3.5.5.2   | Block Diagram of an 8-Core DDS Module                   | 123 |

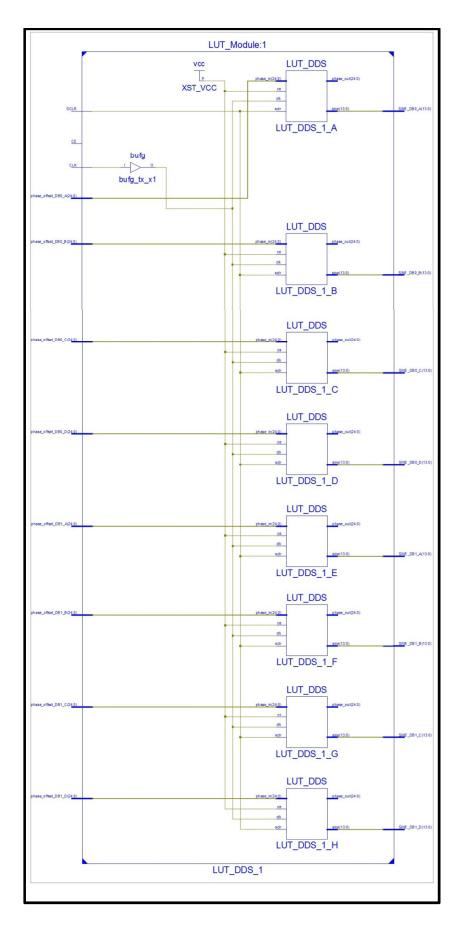

|     |       | 3.5.5.3   | RTL schematics of an 8-Core DDS Module                  | 125 |

|     |       | 3.5.5.4   | VHDL Development of an 8-core DDS Module                | 129 |

|     |       |           | with Over-sampling Concept                              |     |

|     |       | 3.5.5.5   | Simulation Results of an 8-Core DDS System              | 132 |

|     |       |           | with Over-sampling Concept                              |     |

|     |       | 3.5.5.6   | Development of an 8-Core DDS System with Under-sampling | 140 |

|     |       | 3.5.5.7   | VHDL Implementation of an 8-Core DDS System             | 140 |

|     |       |           | with Under-sampling                                     |     |

|      |        | 3.5.5.8 Simulation Results                                     | 149 |

|------|--------|----------------------------------------------------------------|-----|

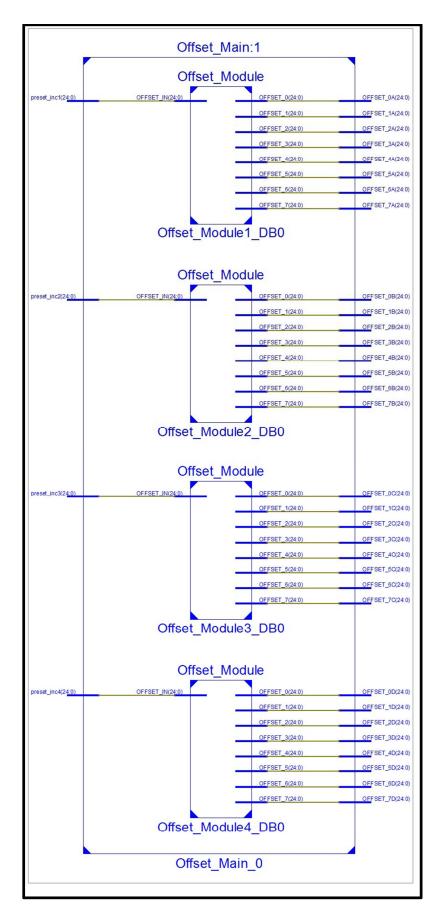

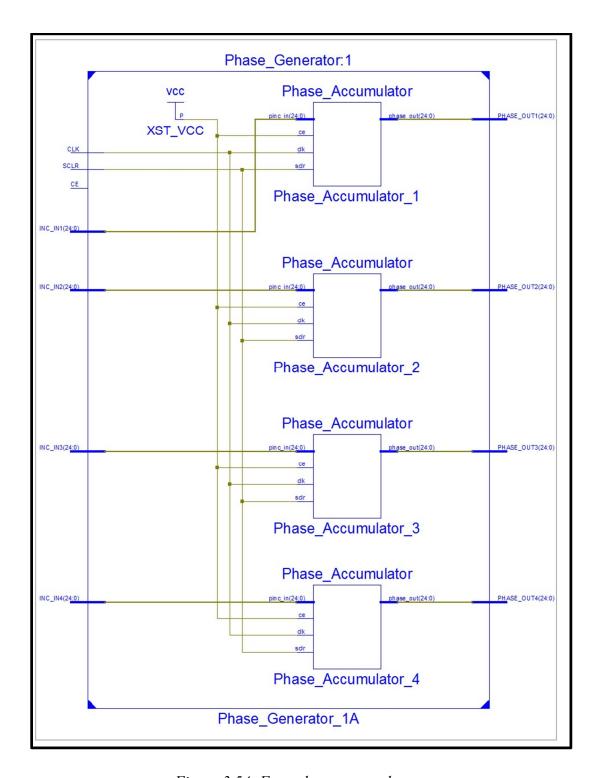

|      | 3.5.6  | Development of Multi-Frequency RF Generator                    | 157 |

|      |        | 3.5.6.1 RTL schematics of a Multi-Frequency RF Generator       | 157 |

|      |        | 3.5.6.2 Implementation of Multi-Frequency RF Generator in VHDL | 160 |

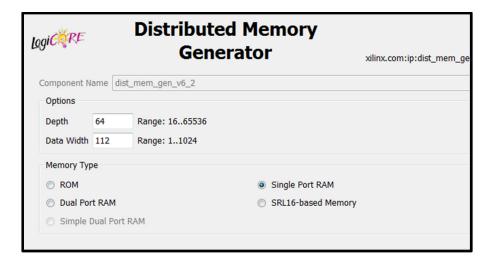

|      | 3.5.7  | Development of a Custom Data Distributor by Using              | 164 |

|      |        | Distributed Memory Block                                       |     |

|      |        | 3.5.7.1 Implementation of Addressable Distributed Memory Block | 165 |

|      |        | in VHDL                                                        |     |

|      |        | 3.5.7.2 Simulation Results                                     | 169 |

| Chap | oter 4 | Hardware Implementation, Testing and Results                   | 172 |

| 4.1  | Overv  | view of T-Rex v4.0                                             | 173 |

| 4.2  | Serial | l Programming on DAC and Clock Chips                           | 176 |

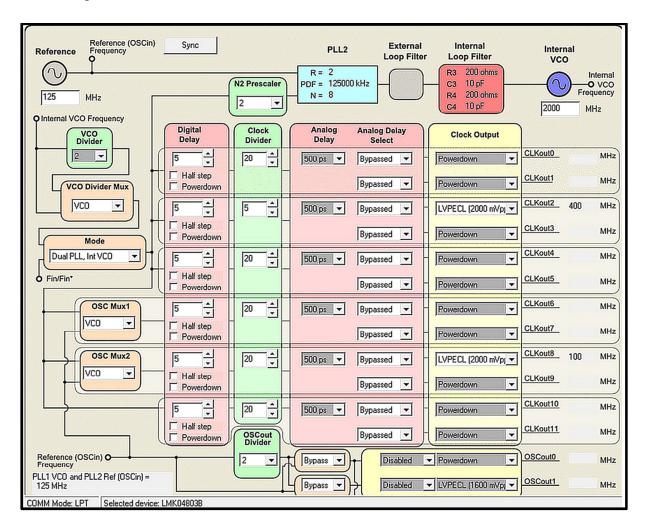

|      | 4.2.1  | Clock Chip Configuration: LMK04803B                            | 177 |

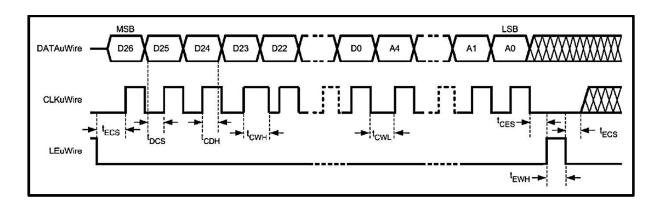

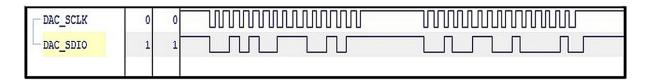

|      |        | 4.2.1.1 Development of MICROWIRE for an LMK04803B              | 179 |

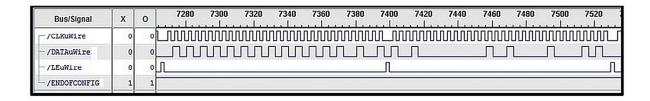

|      |        | 4.2.1.2 Implementation of Serial Programming for an LMK04803B  | 183 |

|      |        | 4.2.1.3 Tests and Results                                      | 186 |

|      | 4.2.2  | SPI Configuration for DAC Chip: AD9739                         | 190 |

|      |        | 4.2.2.1 Development of SPI Configuration for an AD9739         | 191 |

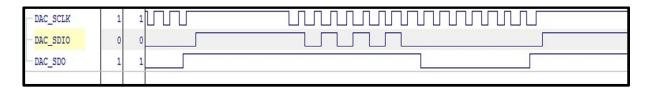

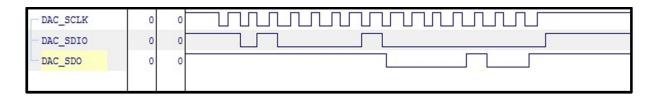

|      |        | 4.2.2.2 Implementation of SPI Configuration for an AD9739      | 193 |

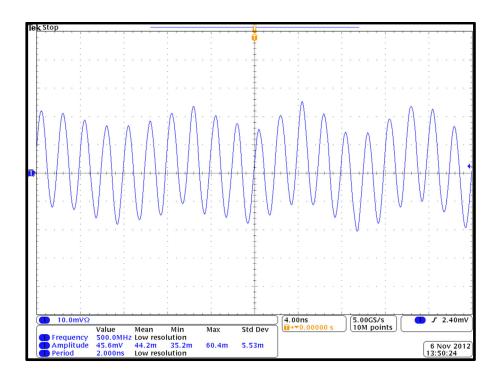

|      |        | 4.2.2.3 Tests and Results                                      | 199 |

| 4.3  | Hard   | ware implementation of High Speed RF transmitter               | 206 |

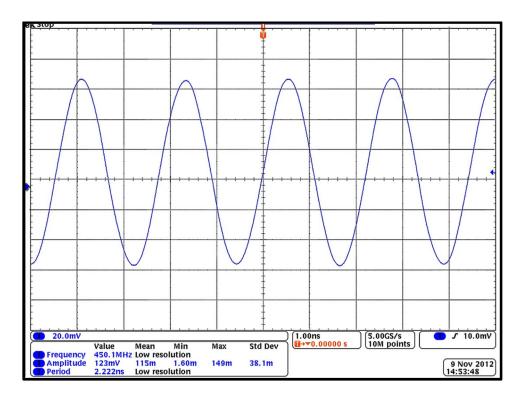

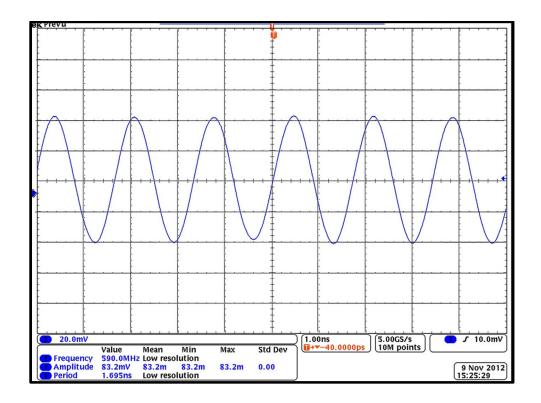

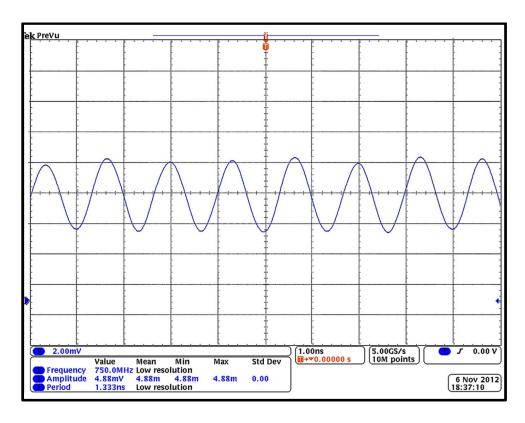

|      | 4.3.1  | Experimental Results of 8-Core DDS System                      | 208 |

|      |        | 4.3.1.1 Discussion                                             | 213 |

|      | 4.3.2  | Experimental Results of Phase Coherence                        | 215 |

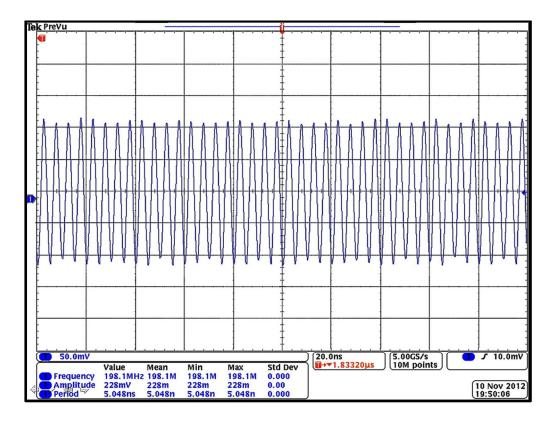

| 4.4  | Hard   | ware Implementation of Distributed Memory Block                | 219 |

|      | 4.4.1  | Test Results of Distributed Memory Block                       | 220 |

|      | 4.4.2  | FPGA Device Utilisation Summary                                | 223 |

| Chap | oter 5 | Conclusion and Future Work                                     | 225 |

| 5.1  | Concl  | lusion                                                         | 225 |

| 5.2  | Futur  | re Work                                                        | 228 |

| Appendix A: Parameter settings of Matlab-Simulink Blocks | 229 |

|----------------------------------------------------------|-----|

| Appendix B: Parameter settings of Xilinx IP Cores        | 235 |

| References                                               | 238 |

# **List of Tables**

| Table 2.0: Features of Spartan-6 [56].                                                  | 44  |

|-----------------------------------------------------------------------------------------|-----|

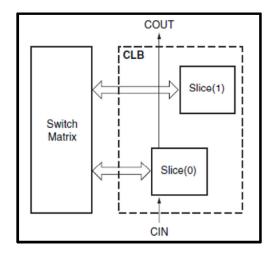

| Table 2.1: Slice features [56].                                                         | 47  |

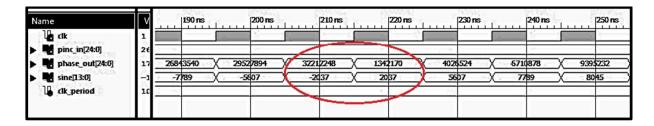

| Table 2.2: Logic resources of a CLB [56].                                               | 47  |

| Table 3.0: Calculation of Phase Offset for 1st to 8th sequential phases.                | 73  |

| Table 3.1: Sample period of Simulink block.                                             | 79  |

| Table 3.2: Selection of output signal via Switch-A and Switch-B.                        | 86  |

| Table 3.3: Comparison between Simulink and mathematical calculation results.            | 93  |

| Table 3.4: Default connection of switches.                                              | 100 |

| Table 3.5: Attributes of PLL module.                                                    | 104 |

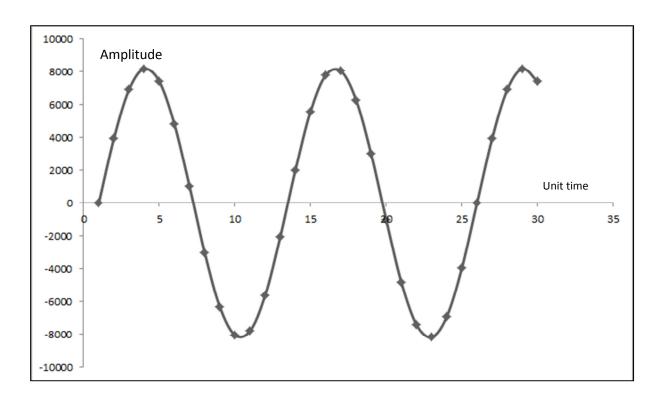

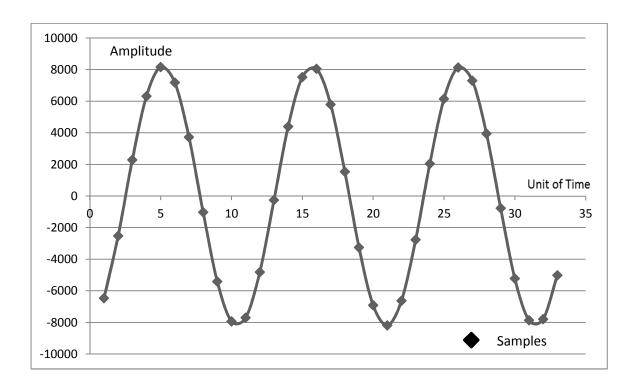

| Table 3.6: First 30 samples of 20 MHz sine-wave.                                        | 114 |

| Table 3.7: Results of 8-core DDS system.                                                | 133 |

| Table 3.8: 3-bit 'nyquist_zone1' vs. Nyquist zone.                                      | 142 |

| Table 3.9: Sequences to transfer digital amplitudes to DAC.                             | 148 |

| Table 3.10: First 33 data points of a 190 MHz sine-wave.                                | 150 |

| Table 3.11: First 33 data points of a 290 MHz Sine-Wave (3 <sup>rd</sup> Nyquist Zone). | 153 |

| Table 3.12: Logic status of SWITCH.                                                     | 162 |

| Table 3.13: First 136 data points captured by the test-bench.                           | 170 |

| Table 4.0: MICROWIRE timing diagram [42].                                               | 178 |

| Table 4.1: Register values of 400 MHz and 100 MHz clock signals [42].                   | 182 |

| Table 4.2: Modes in SPI configuration.                                                  | 196 |

| Table 4.3: SPI initialisation with SYNC controller disabled [8].                        | 199 |

| Table 4.4: Eight Phase offsets of six signals.                                          | 209 |

# **List of Figures**

| Figure 1.0: Overview of proposed RF transceiver.                              | 3  |

|-------------------------------------------------------------------------------|----|

| Figure 1.1: An FID signal.                                                    | 4  |

| Figure 1.2: Magnetisation vector M spiralling down into the x-y plane         | 5  |

| due to an applied RF pulse.                                                   |    |

| Figure 2.0: Block diagram of an NMR system [5].                               | 15 |

| Figure 2.1: Basic DDS structure [8].                                          | 18 |

| Figure 2.2: Digital phase wheel [5].                                          | 19 |

| Figure 2.3: Phase truncation error [5].                                       | 23 |

| Figure 2.4: Taylor series approximation for quarter sine converter [48].      | 26 |

| Figure 2.5: Relative bit position of data word implemented in Figure 2.4[48]. | 26 |

| Figure 2.6: Diagram of vector rotation [58, 60].                              | 29 |

| Figure 2.7: Diagram of vector translation [58, 60].                           | 31 |

| Figure 2.8: Key differences between different Xilinx FPGA families.           | 39 |

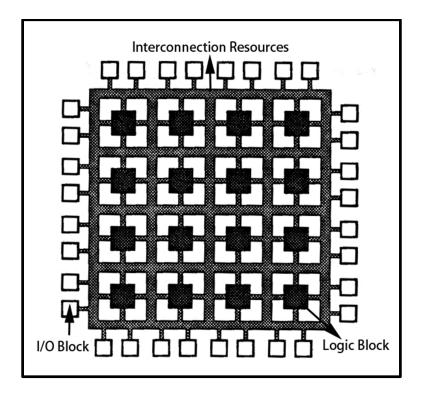

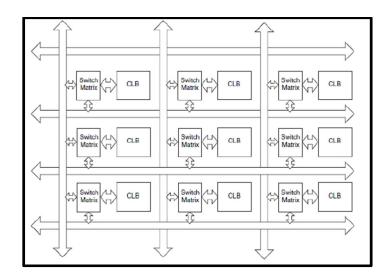

| Figure 2.9: FPGA architecture [64].                                           | 42 |

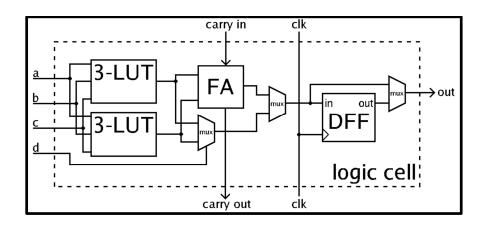

| Figure 2.10: Simplified block of a logic cell [21].                           | 44 |

| Figure 2.11: CLB and interconnect channels [55].                              | 46 |

| Figure 2.12: Slices in a CLB [55].                                            | 46 |

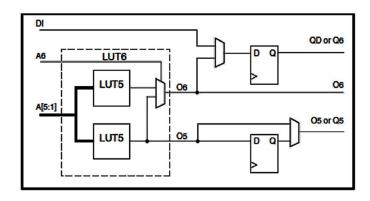

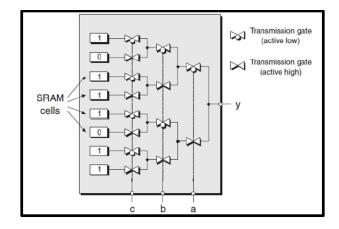

| Figure 2.13: LUT of Spartan-6 [55].                                           | 48 |

| Figure 2.14: A transmission gate-based LUT [28].                              | 48 |

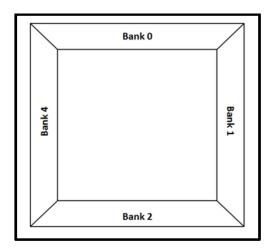

| Figure 2.15: Spartan-6 XC6SL45T I/O banks [54].                               | 51 |

| Figure 2.16: I/O tile of Spartan-6 [54].                                      | 51 |

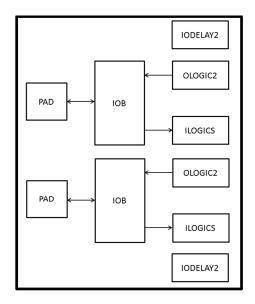

| Figure 2.17: Basic IOB diagram [54].                                          | 52 |

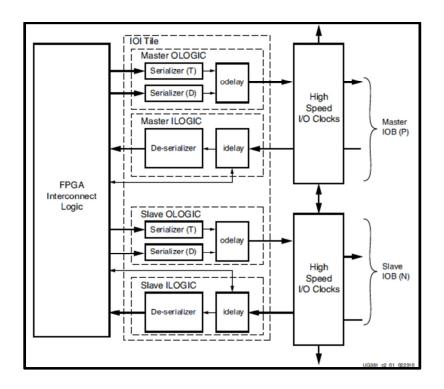

| Figure 2.18: Resources of master and slave IOLOGICs [54].                     | 53 |

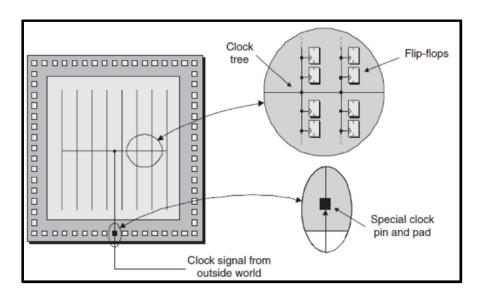

| Figure 2.19: A simple clock tree [28].                                        | 55 |

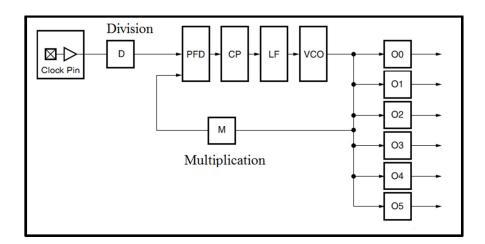

| Figure 2.20: Overview of a PLL in Spartan-6 [61].                             | 56 |

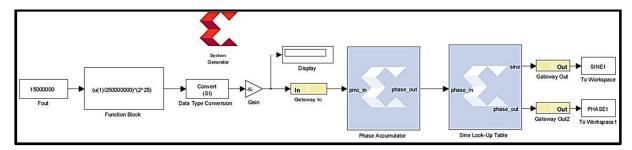

| Figure 3.0: Matlab-Simulink of a single DDS.                                  | 64 |

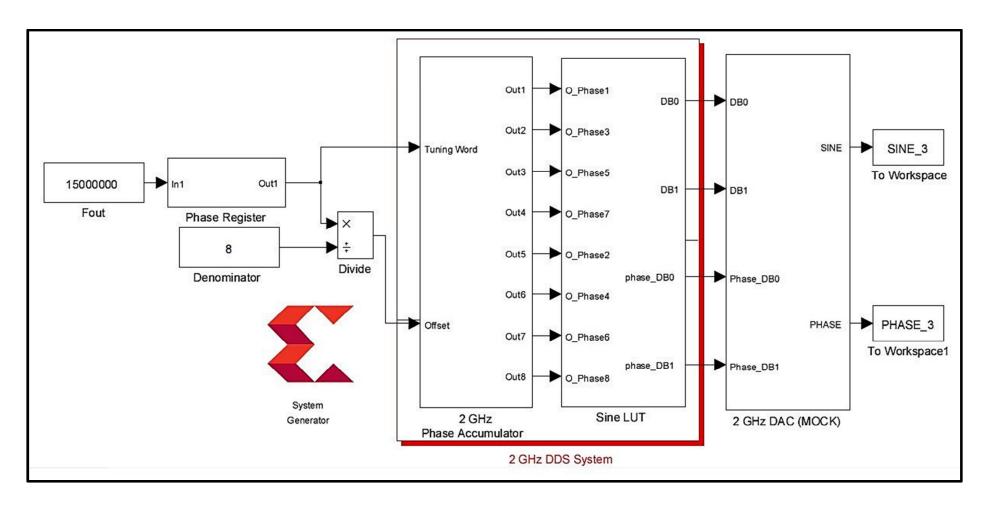

| Figure 3.1: Conceptual design of a 2GHz sampling transmitter.                        | 68  |

|--------------------------------------------------------------------------------------|-----|

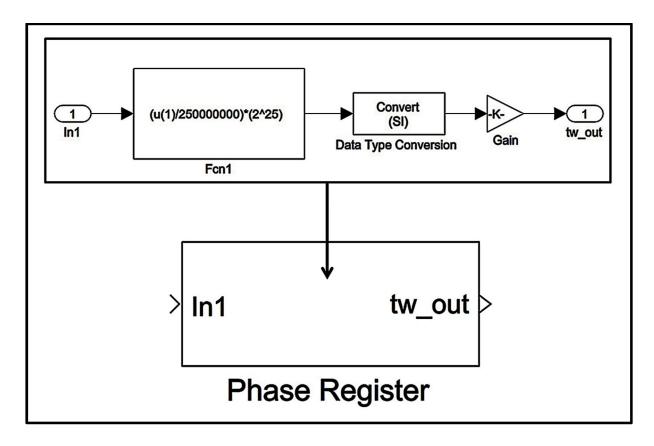

| Figure 3.2: Phase register Simulink block.                                           | 70  |

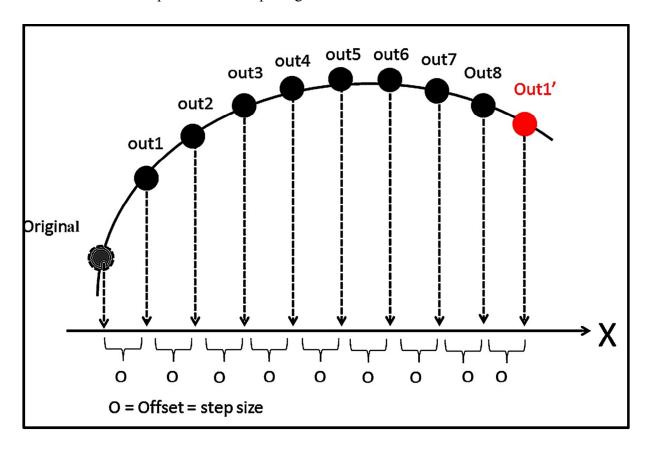

| Figure 3.3: Phase offsets.                                                           | 71  |

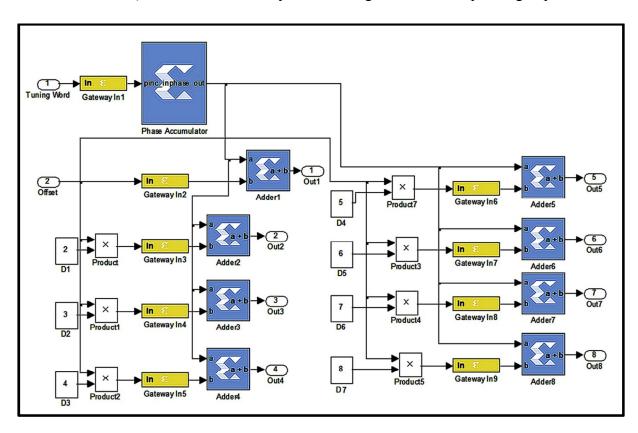

| Figure 3.4: Internal structure of a 2 GHz phase accumulator block.                   | 74  |

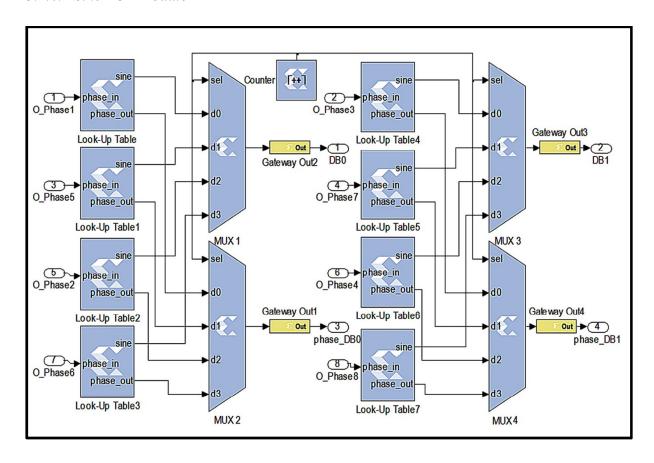

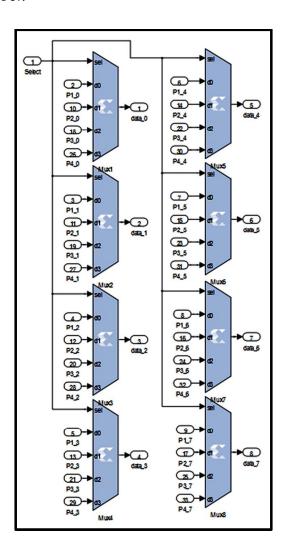

| Figure 3.5: Internal structure of a sine LUT module.                                 | 76  |

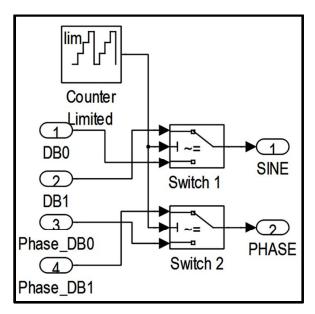

| Figure 3.6: DAC module (Mock).                                                       | 78  |

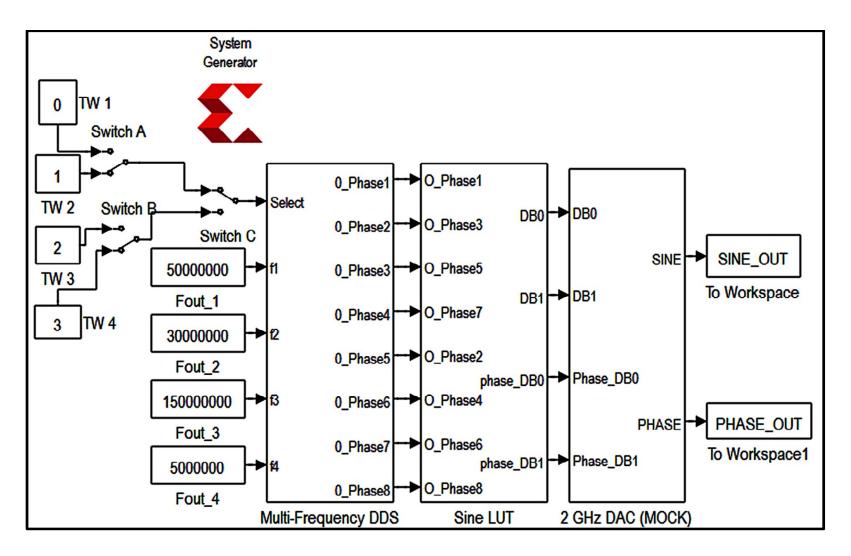

| Figure 3.7: Simulink model of Multi-Frequency DDS module.                            | 82  |

| Figure 3.8: Internal structure of a multi-frequency DDS function block.              | 83  |

| Figure 3.9: Internal structure of the DDS switch block.                              | 85  |

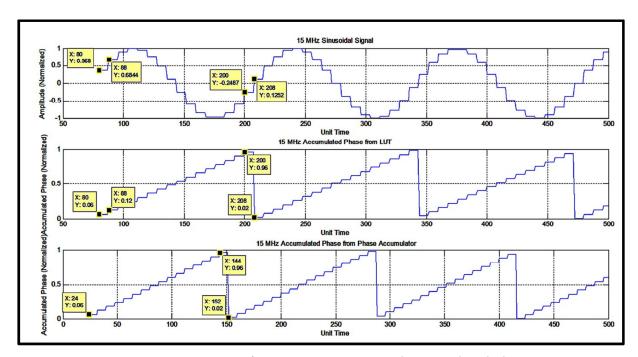

| Figure 3.10: Outputs of 15 MHz sine-wave and accumulated phases.                     | 88  |

| Figure 3.11: Matlab-Simulink model for phase offset simulation.                      | 92  |

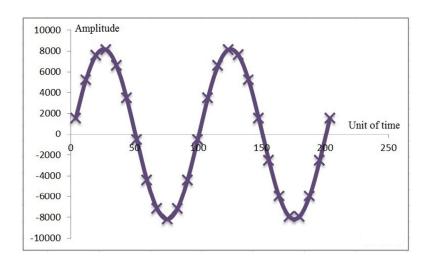

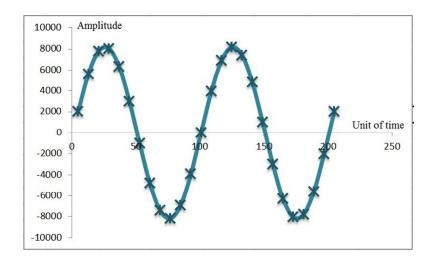

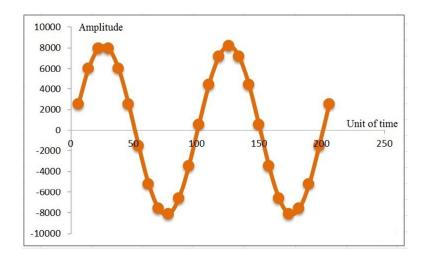

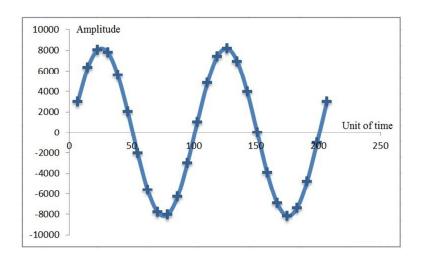

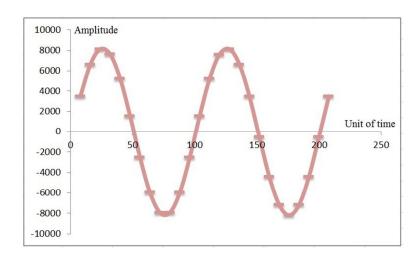

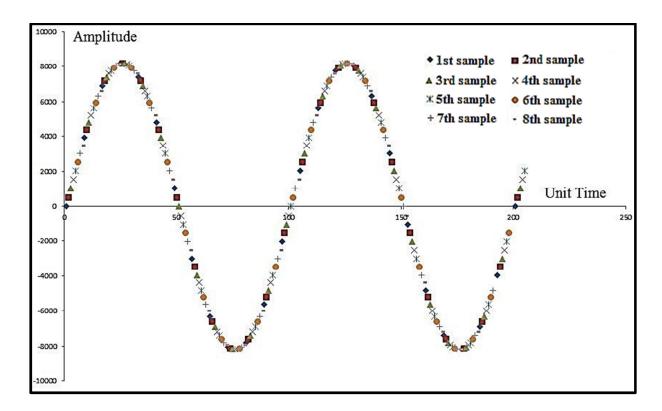

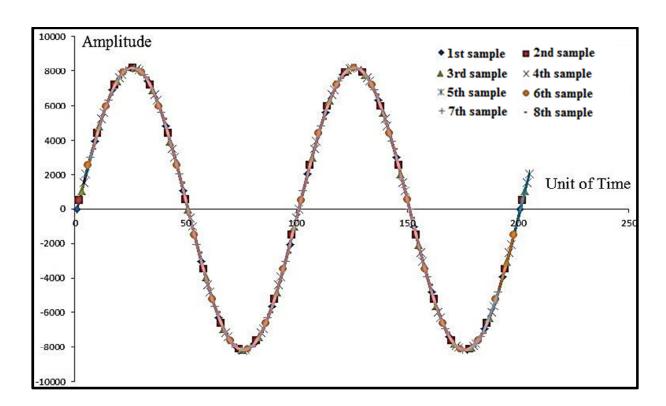

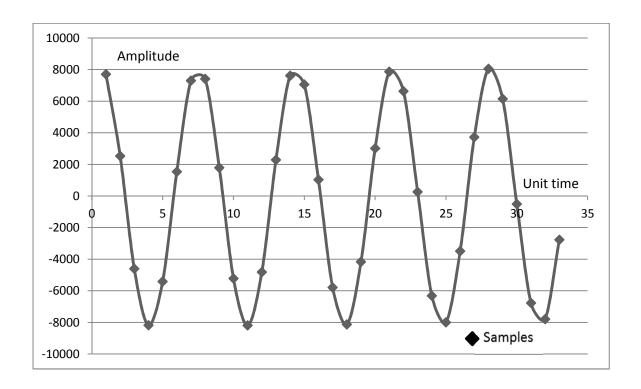

| Figure 3.12: Simulation results of an 8-core DDS module captured at sine LUT module. | 94  |

| Figure 3.13: Phase steps of a single DDS core and an 8-core DDS module (15 MHz).     | 97  |

| Figure 3.14: Four signals generated by a multi-frequency RF generator.               | 100 |

| Figure 3.15: Phase coherence between 10 MHz and 30 MHz signals.                      | 101 |

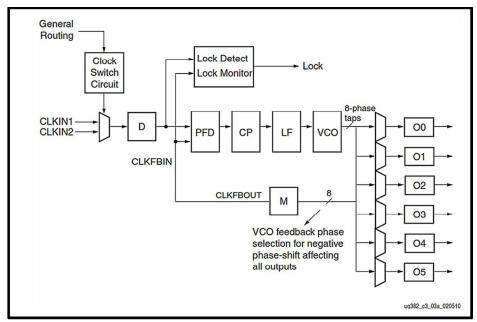

| Figure 3.16: PLL module [61].                                                        | 103 |

| Figure 3.17: PLL block diagram: CLK_FEEDBACK = CLKFBOUT.                             | 105 |

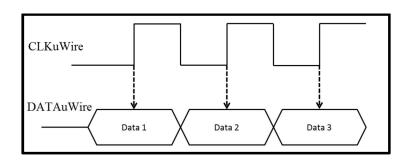

| Figure 3.18: Data transmission with one SDR forwarded clock [36].                    | 107 |

| Figure 3.19: Test-bench code to capture output data.                                 | 109 |

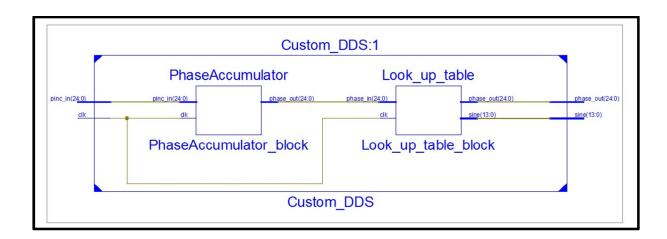

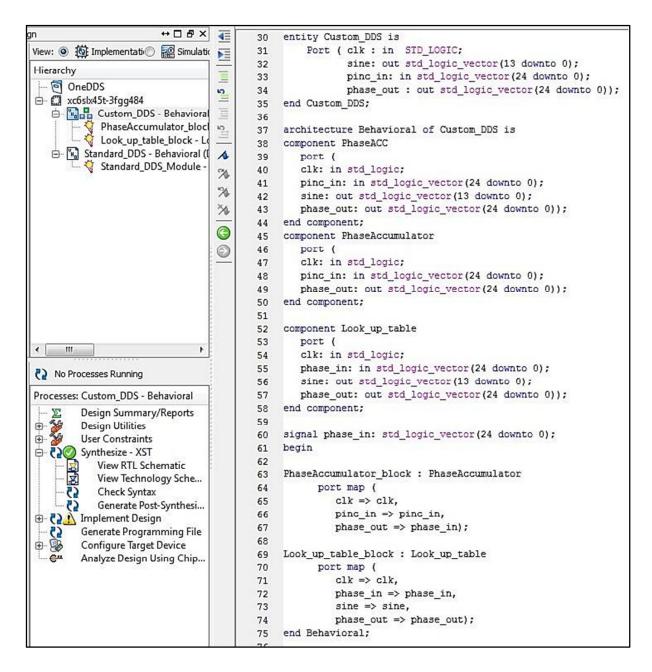

| Figure 3.20: RTL schematic of a custom DDS module.                                   | 111 |

| Figure 3.21: VHDL code for a standard DDS module.                                    | 112 |

| Figure 3.22: Simulation results of a DDS Core.                                       | 113 |

| Figure 3.23: Sine-wave with frequency = 20 MHz.                                      | 115 |

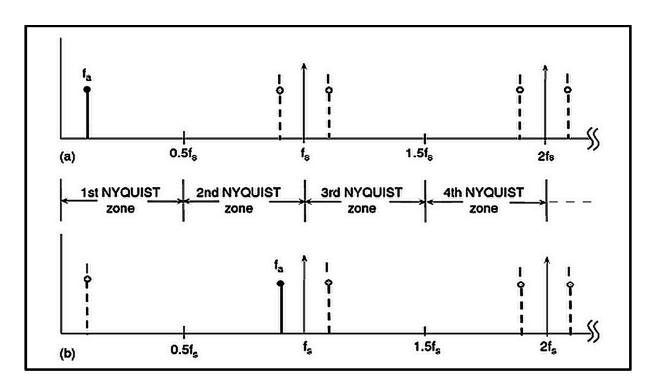

| Figure 3.24: Diagram of output signal (fa) sampled at fs [51].                       | 119 |

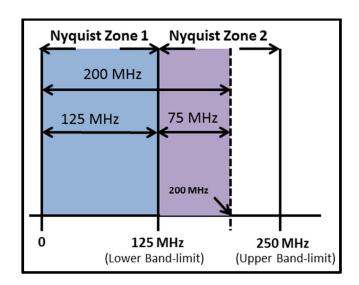

| Figure 3.25: Nyquist zone.                                                           | 120 |

| Figure 3.26: Diagram of under-sampling to obtain 200 MHz output.                     | 120 |

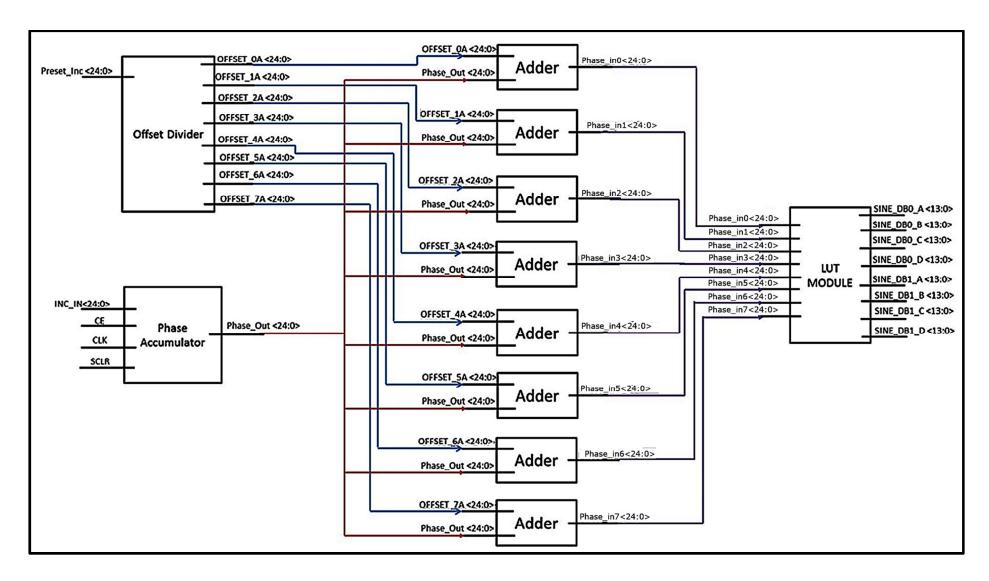

| Figure 3.27: Block diagram of custom DDS with eight DDS cores.                       | 124 |

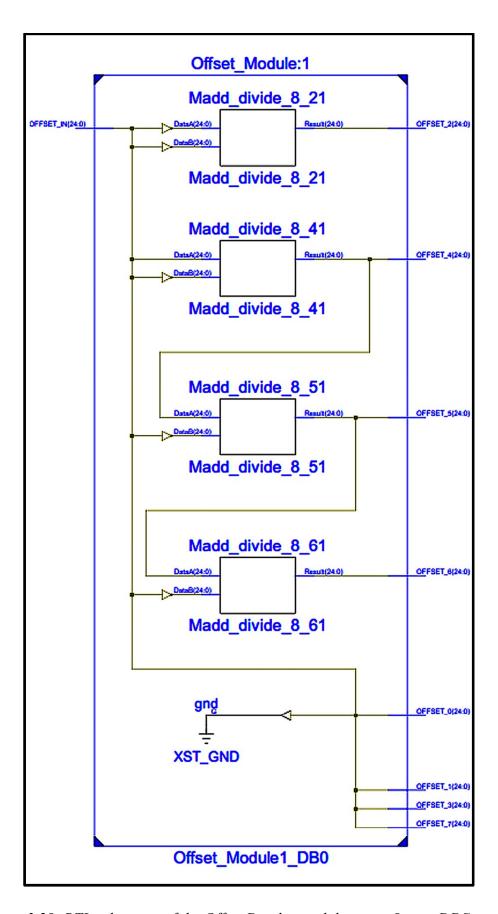

| Figure 3.28: RTL schematic of the Offset Divider modules in an 8-core DDS system. | 126 |

|-----------------------------------------------------------------------------------|-----|

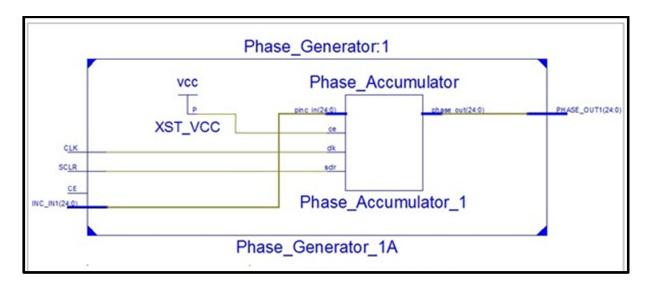

| Figure 3.29: RTL schematic of a Phase Accumulators in an 8-core DDS System.       | 127 |

| Figure 3.30: RTL Schematic of eight LUTs.                                         | 128 |

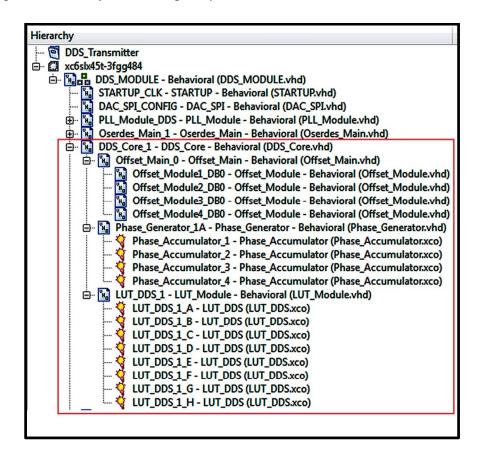

| Figure 3.31: Project hierarchy of an 8-core DDS module.                           | 129 |

| Figure 3.32: VHDL code for offset divider.                                        | 129 |

| Figure 3.33: Entity declaration of DDS_Core.                                      | 131 |

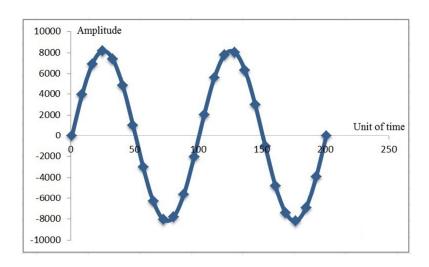

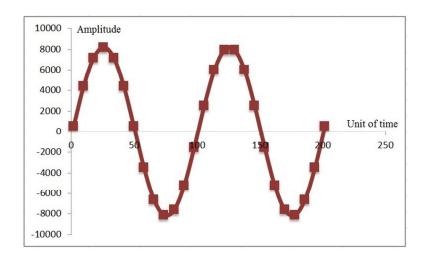

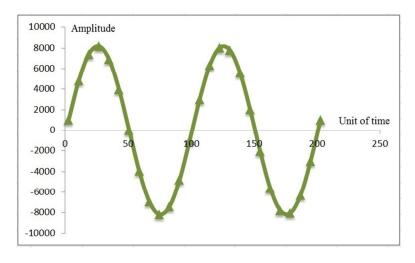

| Figure 3.34: Plot of 1 <sup>st</sup> sample phase.                                | 135 |

| Figure 3.35: Plot of 2 <sup>nd</sup> sample phase.                                | 135 |

| Figure 3.36: Plot of 3 <sup>rd</sup> sample phase.                                | 135 |

| Figure 3.37: Plot of 4 <sup>th</sup> sample phase.                                | 136 |

| Figure 3.38: Plot of 5 <sup>th</sup> sample phase.                                | 136 |

| Figure 3.39: Plot of 6 <sup>th</sup> sample phase.                                | 136 |

| Figure 3.40: Plot of 7 <sup>th</sup> sample phase.                                | 137 |

| Figure 3.41: Plot of 8 <sup>th</sup> sample phase.                                | 137 |

| Figure 3.42: Final output after overlaying Figure 3.34 to Figure 3.41.            | 138 |

| Figure 3.43: Visualisation of complete sine-wave.                                 | 139 |

| Figure 3.44: VHDL program to search for image frequency.                          | 141 |

| Figure 3.45: Bit inversion for the output phases.                                 | 143 |

| Figure 3.46: VHDL code to transfer the phases from the even Nyquist zone to LUTs. | 145 |

| Figure 3.47: Declaration of LUT module.                                           | 146 |

| Figure 3.48: VHDL function to transfer phase values to a LUT module.              | 147 |

| Figure 3.49: Simulation results of a 190 MHz signal using Isim.                   | 150 |

| Figure 3.50: 190MHz sine-wave.                                                    | 151 |

| Figure 3.51: Simulation results of a 290 MHz signal using ISim.                   | 153 |

| Figure 3.52: 290MHz sine-wave.                                                    | 154 |

| Figure 3.53: Four offset module.                                                  | 158 |

| Figure 3.54: Four phase accumulators.                                             | 159 |

| Figure 3.55: Project hierarchy of multi-frequency DDS system.                  | 160 |

|--------------------------------------------------------------------------------|-----|

| Figure 3.56: VHDL coding of signal switching routine.                          | 161 |

| Figure 3.57: Predefined tuning word.                                           | 163 |

| Figure 3.58: Switching between an 8-core DDS module                            | 165 |

| and a distributed memory block.                                                |     |

| Figure 3.59: Component declaration of distributed memory block.                | 166 |

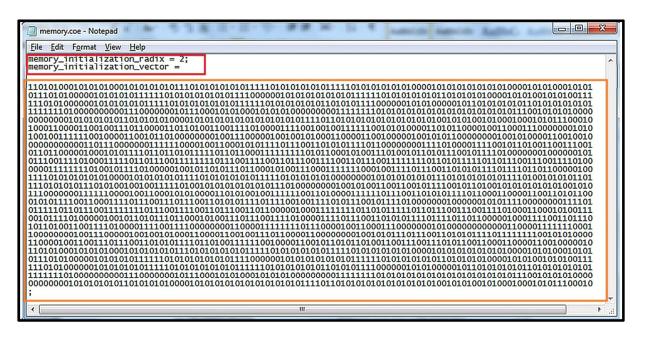

| Figure 3.60: Coefficient file.                                                 | 166 |

| Figure 3.61: VHDL coding to retrieve the content of a coefficient file.        | 168 |

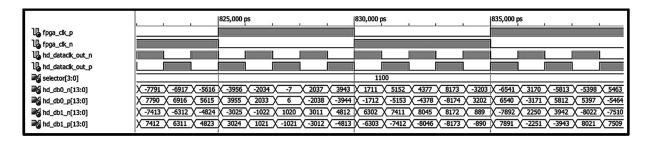

| Figure 3.62: Simulation results of distributed memory block using Isim.        | 169 |

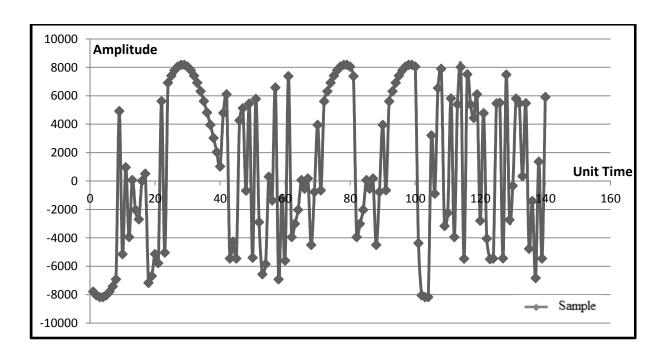

| Figure 3.63: Simulated results of a random signal.                             | 171 |

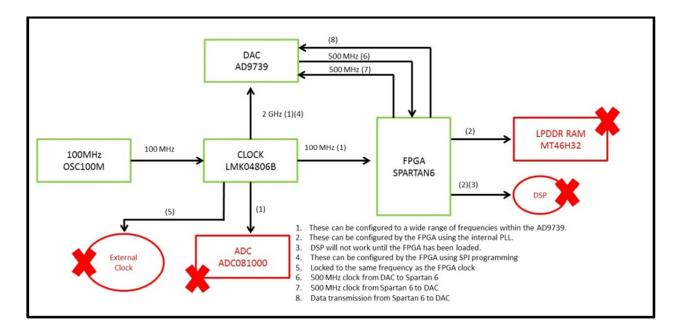

| Figure 4.0: Block diagram of T-Rex v4.0 [46].                                  | 173 |

| Figure 4.1: Top view of T-Rex v4.0.                                            | 174 |

| Figure 4.2: MICROWIRE timing diagram [42].                                     | 178 |

| Figure 4.3: Interface of CodeLoader4.                                          | 179 |

| Figure 4.4: Binary numbers of R0 to R31 generated by CodeLoader4.              | 180 |

| Figure 4.5: Initialisation of a Spartan 6 start-up clock.                      | 183 |

| Figure 4.6: VHDL coding of serial programming of LMK04803B.                    | 184 |

| Figure 4.7: Real-time simulation results.                                      | 187 |

| Figure 4.8: Simplified diagram of clock transition on data valid window.       | 187 |

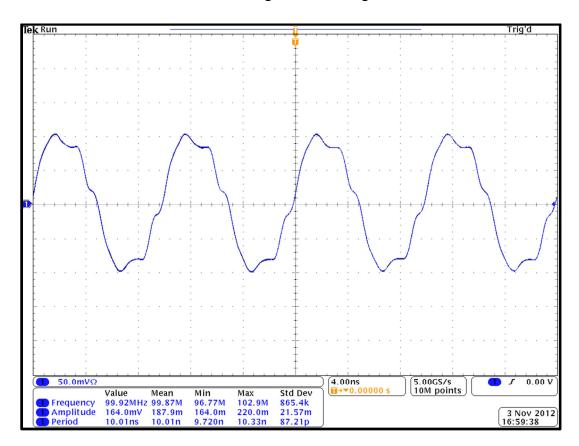

| Figure 4.9: 100 MHz clock signal at CLKout8.                                   | 188 |

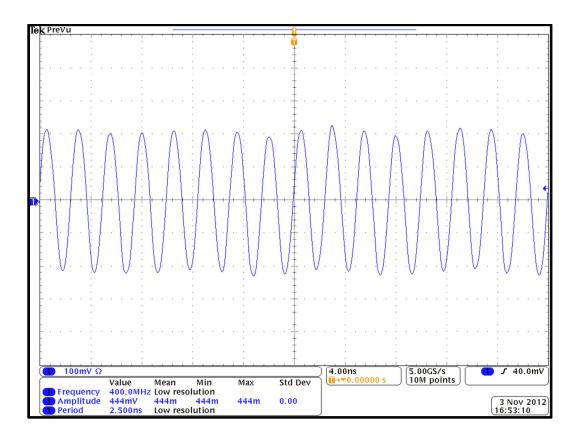

| Figure 4.10: 400 MHz clock signal at CLKout2.                                  | 189 |

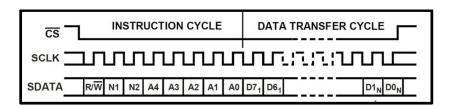

| Figure 4.11: SPI timing diagram of AD9739 [8].                                 | 191 |

| Figure 4.12(A): Write routine of SPI configuration (Not a full VHDL program).  | 193 |

| Figure 4.12 (B): Write routine of SPI configuration (Not a full VHDL program). | 194 |

| Figure 4.13: Read process of SPI configuration.                                | 197 |

| Figure 4.14: Write routine to SPI interface.                                   | 201 |

| Figure 4.15: Read routine to SPI interface at Register 0x2A.                   | 202 |

| Figure 4.16: Read routine to SPI interface at Register 0x21.         | 203 |

|----------------------------------------------------------------------|-----|

| Figure 4.17: 500 MHz clock generated by AD9739 DCO pin to Spartan-6. | 204 |

| Figure 4.18: Analog output without offset binary conversion.         | 207 |

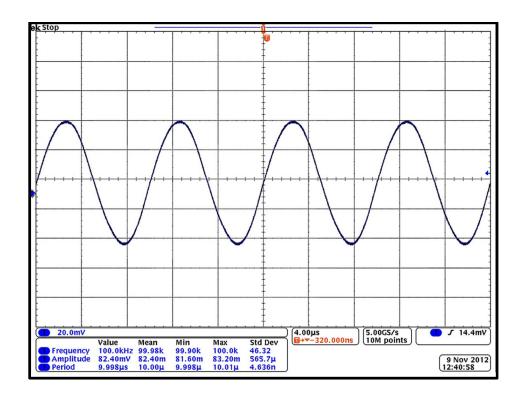

| Figure 4.19: 100 kHz sine-wave.                                      | 210 |

| Figure 4.20: 500 kHz sine-wave.                                      | 210 |

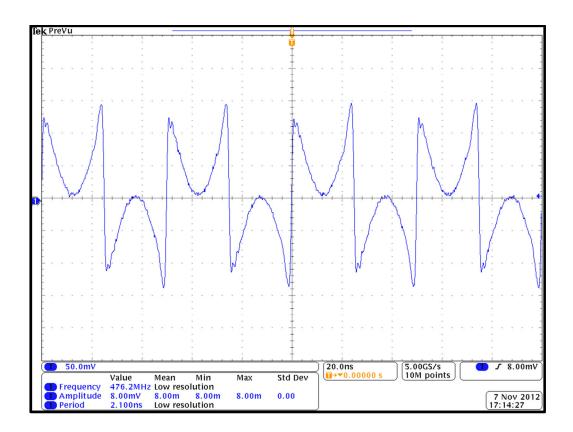

| Figure 4.21: 210 MHz sine-wave.                                      | 211 |

| Figure 4.22: 450 MHz sine-wave.                                      | 211 |

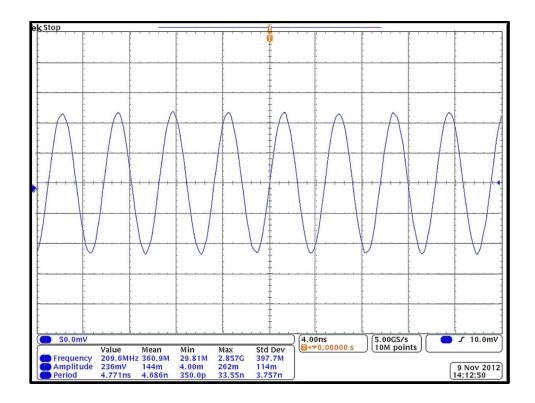

| Figure 4.23: 590 MHz sine-wave.                                      | 212 |

| Figure 4.24: 750 MHz sine-wave.                                      | 212 |

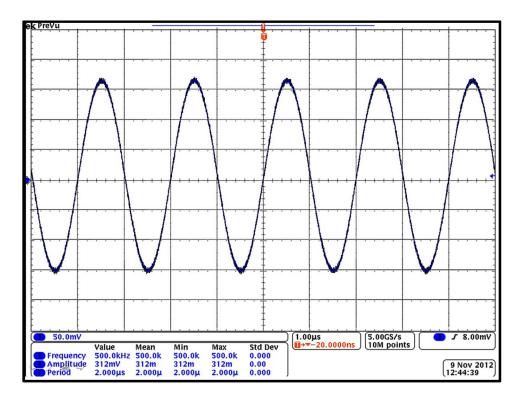

| Figure 4.25: 200 MHz sine-wave.                                      | 215 |

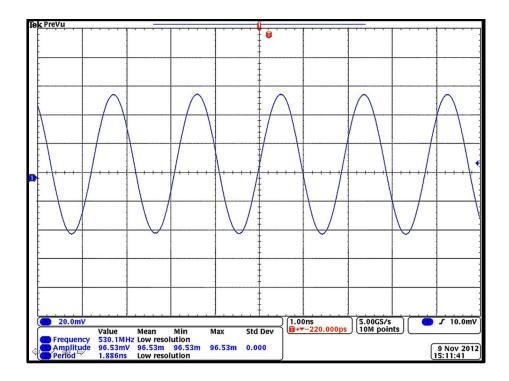

| Figure 4.26: 530 MHz sine-wave.                                      | 216 |

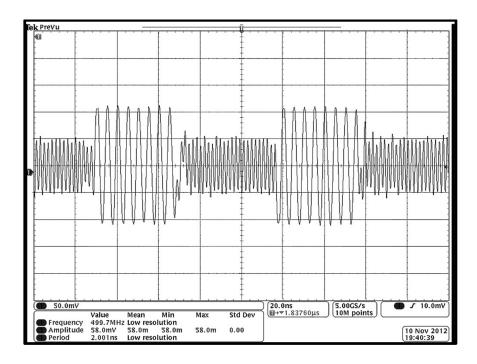

| Figure 4.27: Switching between 200 MHz and 530 MHz.                  | 217 |

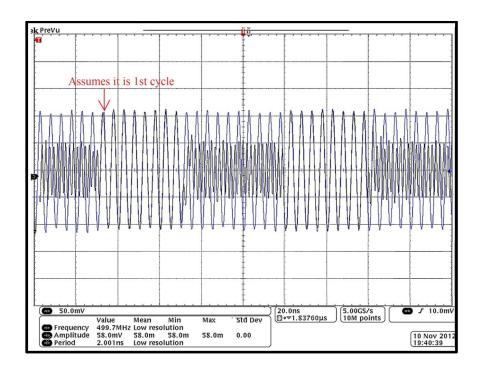

| Figure 4.28: Phase coherence of 200 MHz sine-wave.                   | 218 |

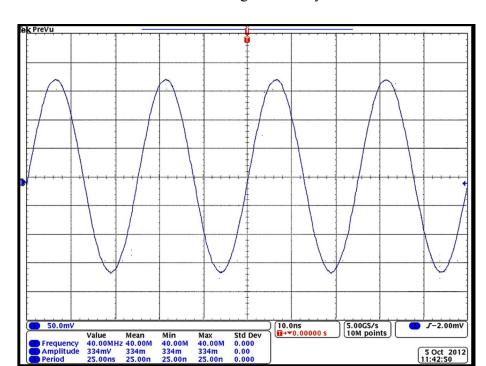

| Figure 4.29: 40 MHz signal generated by 8-core DDS module.           | 220 |

| Figure 4.30: Custom data for 40 MHz sine-wave.                       | 221 |

| Figure 4.31: 40 MHz signal generated by distributed memory block.    | 221 |

| Figure 4.32: Device utilisation summary.                             | 223 |

| Figure 4.33: Performance summary.                                    | 224 |

### **Table of Abbreviations**

ASIC Application-Specific Integrated Circuits

BUFG Global Clock Buffers

BUFPLL High Speed I/O Clock Buffer

CE Chip Enable

CIC Cascaded Integrator-comb

CLB Configurable Logic Blocks

CLKOUT Clock Output

CMT Clock management tiles

CS Chip Select

CORDIC Coordination Rotation Digital Computer

CP Charge Pump

DAC Digital-to-analog converter

DACCLK DAC Master Clock

DCI Input clock pin

DCM Digital Clock Manager

DCO Output clock pin

DDR Double data rate

DDS Direct Digital Synthesis

DLL Delay Lock Loop

DSP Digital signal processing

EMF Electromotive Force

EMI Electromagnetic Interference

FA Full adder

FFT Fast Fourier Transform

FID Free Induction Decay

FIR Finite Impulse Response

FPGA Field programmable gate array

GTP Gunning Transceiver

IBUFG Single-ended Input Global Clock Buffer

ILOGIC Input Logic

IOB Input/output Block

IOI I/O interface

IP Intellectual Property

ISE Integrated Software Environment

LAB Logic Array Blocks

LF Loop Filter

LSB Least Significant bit

LUT Look-up tables

LVDS Low-voltage differential signal

MADD Multiply-Add

MCU Microcontroller unit

MSB Most significant bits

MUX Multiplexer

NAND Negated ANDs

NMR Nuclear Magnetic Resonance

OLOGIC Output Logic

OSERDES Output Serialisation or Deserialisation

PFD Phase-Frequency Detector

PIC Peripheral interface controller

PLD Programmable Logic Device

PLL Phase locked loop

PROM Programmable Read-Only Memory

RF Radio Frequency

ROM Read-only memory

RTL Register-transfer level

SCLK Serial Clock

SCLR Synchronise Clear

SDIO Serial Data Input Output

SDO Serial Data Output

SDR Single data rate

SERDES Serialisation or de-serialisation

SFDR Spurious free dynamic range

SNR Signal-to-noise ratio

SOPC System on Programmable Chip

SPI Serial Peripheral Interface

SRAM Static Random-Access Memory

TTL Transistor logic

VCO Voltage Controlled Oscillator

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# **Chapter 1**

#### Introduction

This chapter introduces the problem statement, an overview of the proposed NMR RF transmitter, the motivation, research goals, and organisation of this thesis.

#### 1.1 Problem Statement

In the communication field, an RF transmitter of a device has been associated with the frequency and modulation of a carrier signal. These techniques are transferable to NMR where an amplitude-modulated stimulus is applied to a probe.

In the past few decades, the implementation of a traditional NMR RF transmitter has been achieved using analog construction. Although it has many advantages such as high precision, there are several drawbacks are still associated it such as cost, size, complexity and portability [6]. After 40 years of research, developments of microelectronics brought a technological revolution to the transceiver system. The availability of commercial products in recent years has resulted in a dramatic switch from classical architecture towards a digital domain [11].

The momentous changes in the architectural conception of an NMR RF transmitter, which used to be exclusively granted by the technological possibilities of hardware integration, can now be realised by modern microelectronic devices. Most of the current NMR RF transmitters try to merge the analog and digital approach in order to get the best performance from both worlds.

Assorted RF transceivers are developed for different applications such as wireless communications, digital radiation spectrometers and so on. Despite the fact that not all the RF transmitters are fitted to the NMR system, but these RF transmitters can be altered to suit different applications in NMR spectroscopy. Modifications of the RF transmitter enable the NMR system to meet the objectives of this thesis research.

Several NMR RF transmitters have been proposed in recent years resulting in innumerable solutions that generally tend to sacrifice some features like overall system throughput or real-time capability in favour of an increase in system versatility [25, 26, 41, 63]. This thesis proposes the implementation of an NMR RF transmitter on a single FPGA chip. The proposed solution contains internal DDS modules, which could run in parallel to

generate high-speed samples. In addition, this can help overcome the frequency limitation of a standard NMR RF transmitter generating analog sine-wave signals ranges from 100 kHz to 750 MHz at 2 GHz sampling rate. Moreover, the proposed system could support an output signal of up to four distinct frequencies. This overcomes the phase coherence problem.

#### 1.2 Overview of Proposed NMR RF Transmitter

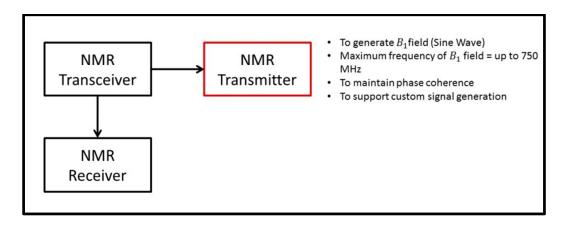

Figure 1.0: Overview of proposed RF transceiver.

The NMR RF transmitter proposed in this thesis is part of the NMR transceiver as shown in Figure 1.0. This NMR transmitter can generate a variable sine-wave (B<sub>1</sub>) from 100 kHz to 750MHz. 100 kHz is the minimum frequency we aim for the system to generate. 750 MHz is selected, as the upper limit output frequency after considering that sample of high frequency signal might be insufficient to maintain the signal shape as sinusoidal.

Usually, the signal generated by the transmitter can be represented by the formula below:

$$x(t) = A_{Gain} \sin \left[ 2\pi f_c t \right] \tag{1.0}$$

$A_{Gain}$  is a unity gain, which is used to determine the amplitude of the signal. In this thesis, it will be treated as '1'.  $f_c$  is the signal frequency while 't' is the sampling time.

The purpose of an NMR RF transmitter focuses on preserving the phase coherence of a signal. The phase coherence lost is a limitation of most of the NMR transmitters available within the NMR field. Most of the systems lose the original signal phase after switching to another frequency.

#### 1.3 Introduction of NMR RF Transmitter in NMR Spectroscopy

NMR spectroscopy is a technique used to study the physical, chemical, and biological properties of materials by probing the nuclear dipole moments in the material [23]. It was found and measured using molecular beams by Isidor Rabi in 1938 [32]. He received the Noble Prize in Physics in 1944 for his work [1]. Two years later, Felix Bloch and Edward Mills Purcell expanded the technique to liquids and solids. They used it as an analytical tool in chemistry and physics in 1946. They too were awarded the Nobel Prize in Physics in 1952 [2, 17].

NMR is a phenomenon that occurs when the nuclei of certain atoms are immersed in a static  $B_0$  field and exposed to an oscillating  $B_1$  field [16, 23]. In a sample unit, the nuclei are in equilibrium with the stationary field when they are completely aligned. When a  $B_1$  field is applied, they will be disturbed from equilibrium. After the RF transmitter is turned off, they will begin to return to equilibrium by transferring energy to the surrounding molecular environment. This process is called 'relaxation' [18].

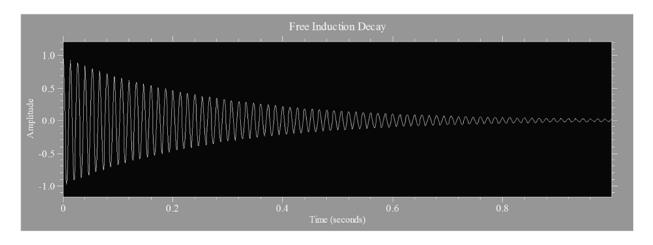

The  $B_1$  field is a sine-wave signal generated by an RF transmitter (RF pulse). It is applied to stimulate the spins, which would generate a decaying resonance signal known as a Free Induction Decay (FID). Figure 1.1 is the example of a FID [23].

Figure 1.1: An FID signal.

#### 1.3.1 Phase Coherence

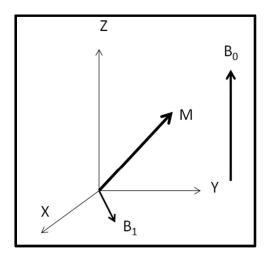

Before the RF pulse is applied to the system, nuclei are in its characteristic frequency, but are out of phase. At a certain time when the RF pulse is transmitted to the system, all the nuclear magnetic moments become coherent. This forces the magnetisation vector M to spiral down around the z-axis as shown in Figure 1.2.

Figure 1.2: Magnetisation vector M spiralling down into the x-y plane due to an applied RF pulse.

The magnetisation vector now precesses in the x-y plane at the Larmor frequency. When it reaches the x-y plane, the RF field is removed, and the precessing magnetisation can then be observed as an induced Electromotive Force (EMF) in a coil surrounding the sample. At that moment, the phase coherence of the nuclear spins is lost. The nuclear magnetic moments return to random arrangement around the z-axis. In other words, there is no net x-y magnetisation. This process is known as the 'relaxation process' and is recorded by the NMR spectroscopy.

In summary, the NMR RF transmitter makes the excitation of nuclei at different times as possible while the phase coherence is maintained. Therefore, the RF pulse transmitted to the magnet system must be able to maintain coherence before and after switching to other frequencies.

#### 1.4 Thesis Motivation

Zhang and Dong constructed a multi-channel adjustable frequency system in their research [66]. They used a NOIS II processor from Altera Corporation. In their paper, they proposed a custom DDS module, which contains three output channels. Nios II is powerful but the application of Nios II in their proposed system has many redundancies in the chip because plenty of features remain unused. A similar solution can be implemented by using low-level FPGA devices such as the Cyclone series from Altera or Spartan series from Xilinx to optimise the utilisation of the processing unit. Furthermore, their proposed DDS system operates at 210 MSPS, and the DDS system is classified as a low speed system. The limitations of their system lie behind the motivations of the research work presented in this thesis.

#### 1.4.1 Challenges of an NMR RF Transmitter for NMR Applications

The design of an NMR RF transmitter based on an 'All in One' modular concept is difficult to implement by fitting multi-DDS cores into a single chip. The challenges to the research are because of:

- 1. Many NMR RF transmitters are formed by different combinations of electronic components such as DDS chips, memory chips and so on. The present NMR RF transmitter uses too many external components, which can be substituted by an FPGA device. This traditional design of a standard NMR RF transmitter limits the improvement and enhancement of the existing system in the future [33, 41, 47, 63].

- 2. Various commercial products and research works on NMR RF transmitters are carried out by utilising external DDS chips. The advantage of utilising the additional DDS chips is that it could make the design process of the system easier. Unfortunately, the system encounters phase coherence lost after the switching of an output signal from one frequency to another [38, 39].

- 3. Many present commercial products and academic researchers emphasise a 1 GHz sampling rate or lower for the RF transmitter. The achievable throughput is still far away from the possibility of a high-resolution digital RF transceiver. The hardware components, which are used in the system, have restricted the maximum signal frequency to a 1 GHz sampling rate. Recently, advances in electronics and computing

make it much easier to design a more compact system. The activities within this area have increased to make the 2 GHz signal sampling feasible [7, 8, 25, 40, 41, 45, 46, 47, 63].

#### 1.4.2 Limitations of Current of RF Transmitter

#### 1.4.2.1 Deficiency of NMR RF Transmitter

Most of the NMR RF transmitters use discrete components to build up an entire RF system. The implementation is deficient because the circuitry often takes up a lot of board space. It is also prone to signal drift, interference, distortion and so on. Moreover, these NMR RF transmitters are bulky, semi-portable, and more costly. Discrete components cause the system board to have a complicated circuit design, and the whole RF system lacks visibility to control signals flexibly. These factors are the motivation to look for alternative solutions.

From commercial and industrial points of view, it is necessary to have a flexible design that can be adapted easily to suit different requirements. However, this is hard to achieve because the performance of a DDS system relies on the hardware components on the circuit board. If further improvements are needed, a system upgrade might not be achievable if the forthcoming works are beyond the ability, which the components could support. Furthermore, the system board may not be able to extend its life cycle if damaged or missing parts on the board become no longer available. At that moment, the whole system needs to be re-designed to meet the new requirements [33].

Many researchers have integrated an FPGA into the RF system. However, not all the modules within the RF system are implemented on a single FPGA chip. In this case, the FPGA chip is only used for minor processing purposes such as signal latching, digital switching, clock synthesis and so on. External DDS chips are still applied in the RF system to generate high-speed sine-waves. A similar methodology has been proposed and in work by Takeda. In his paper, he utilised an FPGA chip together with an external DDS chip, AD9740, to generate a sine-wave signal [41].

#### 1.4.2.2 NMR RF Transmitter with External DDS

Another publication of Takeda describes, "A highly integrated FPGA-based NMR spectrometer". His concepts can be achieved by using an FPGA device to incorporate a pulse programmer and a receiver. A DDS interface, which is connected to an external DDS chip, could support the high frequency generation of up to 400 MHz. His original pulse programmer used several tens of integrated circuits on a few circuit boards and there are numerous wire connections among them [41].

In the latest NMR products, FPGAs have been added to the products of several companies. These companies used the FPGA devices as digital signal processing units. A general-purpose pattern generator system known as the "Programmable transistor-to-transistor logic (TTL) and DDS RF Pulse Generator" has been designed and manufactured by SpinCore Technologies Inc. The PulseBlasterTM processor provides all the timing for pulse synchronisation. However, a DDS chip is used to provide the RF excitation from DC to 300MHz [39].

Another FPGA-NMR product by SpinCore Technologies Inc. is a radio processor called the "Complete RF Acquisition and excitation system with Digital Detection, Real-Time signal Processing and Signal Averaging". It is a general-purpose, broadband, RF data acquisition and excitation system. It is a complete NMR subsystem with a frequency range from 0 to 100 MHz. A DDS chip is used to generate an RF output with 14-bit resolution and up to 300 MSPS clock rate [38].

The Magritek Kea2 is another FPGA-based NMR spectrometer system. It could be found on a T-Rex v2.0 board, which was developed at Victoria University of Wellington. This board utilises an AD9910 1 GHz sample rate DDS chip to generate a sine-wave from DC to 400 MHz [27, 47].

The disadvantage of using multiple DDS chips is the loss in phase coherence especially after the sine-wave frequency is varied. Usually, an external DDS chip comes with a built-in digital-to-analog converter (DAC). Numerous commercial products operate at sampling frequencies of up to 1 GHz because it is the maximum clock speed of the built-in DAC available on the market. The sampling frequency can be improved to 2 GHz if a dual data port DAC chip is used together with an FPGA chip. This DDS system is currently on the T-Rex v4.0 board. It is fast enough to carry out a 2 GHz DDS operation [46].

#### 1.4.2.3 FPGA-based NMR RF Transmitter

Some companies like SpinCore Technologies, Agilent Technologies, and Magritek have introduced RF transceivers with an on-board external DDS chip. This structure can support a few hundred MHz to 1 GHz sampling frequency [3, 27, 38, 39]. Huang, Ren, and Mao from Beijing Institute of Technology proposed a method in DDS design by using discrete components (not the FPGA device). Their DDS system is merged with phase lock loop (PLL) outputs to produce a signal generator. Their signal generator can operate at 2728 MHz sampling rate and is capable of generating a signal of up to ~341MHz [66]. However, the entire system is bulky. The size of the system can be reduced by using an FPGA device to replace most hardware components.

The invention of a pulse generator should not simply rely on a faster DDS chip. The design should consider using a customised DDS module in an FPGA chip to achieve better productivity than a system built with many external DDS chips. A DDS module is dependent on the frequency of a DAC chip. All the data generated by the DDS module must synchronise with the conversion process of the DAC chip. Thus, the research must focus on the methodologies to attain such a high clock rate. The system should benefit from the maximum potential across the device.

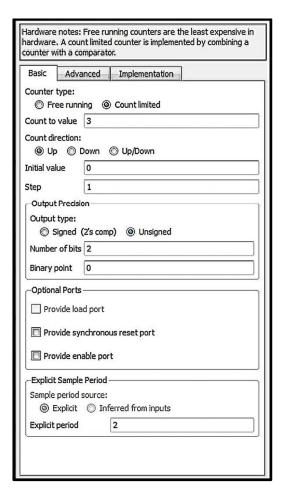

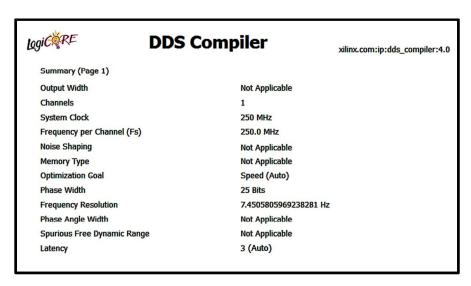

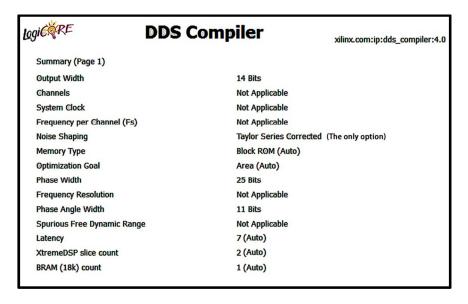

Recently, many researchers have exploited an FPGA chip to develop an NMR transceiver. Nevertheless, the FPGA chip is not fully utilised to make a transceiver. External DDS chips are not replaced by the FPGA chip due to the DDS core being generated by an FPGA chip such as Xilinx FPGA, which could only support up to 250 MHz. It could not meet the trend of the DDS system to operate at 1 GHz.

#### 1.5 Research Goals

An overall goal of the research is to investigate a new approach to the NMR RF transmitter. The detail research objectives are as below:

- 1. Design a high-speed NMR RF transmitter. The goal is to explore the potential of a built-in DDS core of an FPGA chip to generate a dual-channel output at a 1 GHz sampling frequency of each. This output will be processed by a dual-input DAC chip for a total of 2 GHz sampling rate. The entire system should be able to generate the output signal ranging from 100 kHz to 750MHz. To accomplish this goal, it is necessary to study and to investigate the structures of these features to see how they could be utilised as a main core in a pulse generator. However, due to the limitations of FPGA to go beyond an allowable clock speed in DDS, the challenges of this problem lead to four objectives as below:

- a. Design a new topology for an NMR RF transmitter by using Matlab-Simulink.

- The Simulink is used to design the structures of a high-speed RF transmitter. The structures are verified through the Matlab-Simulink simulation.

- b. Simulate the designs in 1(a) above in the register-transfer level (RTL-level) simulation by using the Xilinx VHDL compiler.

- The simulations in Matlab do not consider the timing constraints within the DDS system. Matlab simulations are used to verify the functionality of the design and to analyse the flow from input to output. Therefore, it is necessary to simulate the design in RTL-level to ensure the behavioural structures meet the timing constraints.

- c. Design a new methodology to run a dual-output DDS module at 1 GHz each. The 1GHz frequency is beyond the clock limitation of an internal DDS core in an FPGA chip [29, 44].

- According to the datasheet provided by Xilinx, a DDS core has a single sine or/and cosine output signal. The DDS core can operate at a maximum clock of 250 MHz. A 250 MHz clock speed is insufficient to generate outputs at 1 GHz sampling frequency. Consequently, the proposed custom DDS system is expected

to quadruple the clock speed of the system by implementing multiple DDS core modules within the system.

d. Analyse and investigate the relationship between Nyquist zones and output frequencies.

If a desired signal is beyond 125 MHz, an alternative solution should be investigated. The new solution should be able to generate the samples of high-speed signal (outside of the 1<sup>st</sup> Nyquist zone) by using its folded frequency.

e. Develop a custom signal generator by using a distributed memory block.

A signal in any form can be generated by using this method because it is DDS free and fully customised by users.

f. Develop an innovative methodology to implement an RF generator.

The RF generator should support switching of four frequencies to a single output.

This solution can maintain phase coherence of a signal when the signal is switching from one frequency to another.

- 2. After the simulations, the next task is to transfer the simulated solutions to a prototype board. This section leads to four objectives as below:

- a. To configure the on-board DAC and clock chip.

The evaluation board could not function properly without the configuration of DAC and clock chip. The DAC chip should be programmed to enable a 2 GHz processing rate. It must be able to convert dual-input digital data from DDS to a single analog output at a 2 GHz sampling rate. The clock chip should be programmed to generate a 100 MHz clock to an FPGA chip and a 2 GHz to a DAC chip.

b. To transfer the VHDL coding of an 8-core DDS module to a prototype board.

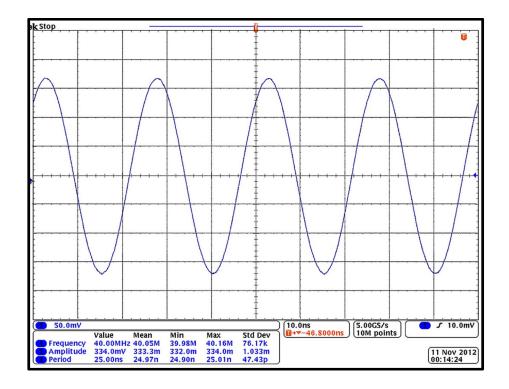

DDS modules will be modified to support multi-frequency generation. The analog signal obtained from the evaluation board will be measured by using a Tektronix MSO 4204 Mixed Signal Oscilloscope.

c. To insert a distributed memory block into the system.

A coefficient file with custom data can be loaded into a distributed memory block. The data will be retrieved and sent to a DAC chip. The output is measured by using a Tektronix MSO 4204 Mixed Signal Oscilloscope.

d. To examine and to observe the phase coherence of the system.

Once the system manages to generate an output signal, the phase coherence of the signal is tested. The results are observed and recorded in Chapter 4.

#### Notes:

Theoretically, the Nyquist frequency of an 8-core DDS system is 1 GHz because the output signal is at a 2 GHz sampling rate. However, it is impossible to generate an output with 1 GHz because an ideal low-pass filter does not exist in real life.

#### 1.6 Organisation of Thesis

#### Chapter 2: Background

Chapter 2 contains the essential background of an NMR RF transmitter and an FPGA device. The review covers the preliminary concepts of a standard RF transmitter, and the basic components used to form a DDS oscillator. The background of an FPGA device includes the fundamental concepts and the architecture of the device is stated in this section.

#### Chapter 3: Design and Development

Chapter 3 emphasises the design and development of an 8-core DDS system. The research begins by using Matlab-Simulink to simulate a single DDS system. From the single DDS system, more modules are added to create an 8-core DDS module. After that, the 8-core DDS module is modified to form a multi-frequency generator, which could support the switching of an output signal between four frequencies. After the Matlab simulation, Simulink designs are transferred to the RTL-level simulation. The simulation is done by utilising Xilinx ISim simulator. A distributed memory block was inserted into the system to generate a random signal.

#### Chapter 4: Hardware Implementation, Testing and Results

Hardware testing of an 8-core DDS system is implemented on an evaluation board. The on-board DAC and clock chip are configured so that the entire system can generate an analog signal at 2 GHz sampling rate. After the configuration, several random frequencies are chosen to test the developed system on the evaluation board. Then, the phase coherence of the output signal is tested and observed. The last part of the hardware testing is to generate a signal by using a distributed memory block. All the results are recorded and presented in this chapter.

#### Chapter 5: Conclusion and Future Work

Chapter 5 is the final chapter of the thesis. A conclusion is presented to wrap up the entire thesis. The concluding part concerns the future work, which can be carried out to enhance and improve the NMR RF transmitter developed in this thesis.

# **Chapter 2**

# **Background**

This chapter reviews the background of an NMR RF transmitter, which is used as a pulse generator in the NMR transceiver. The background covers the existing techniques, essential background, and basic concepts of an NMR RF transmitter. Lastly, it discusses the background and basic architecture of an FPGA device.

#### 2.1 NMR Transceiver

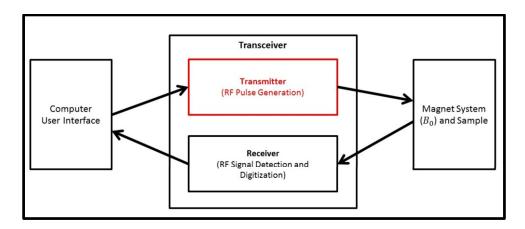

An NMR spectrometer requires a magnet, a coil, and some electronic instrumentation such as a transceiver and a computer. These instruments provide the stimulus and to be subsequent detect the FID signal [37]. Figure 2.0 depicts a simplified NMR system.

Figure 2.0: Block diagram of an NMR system [5].

Typically, the most expensive and difficult part of the system is the magnet system. The cost of the system is proportional to the magnetic strength. The better the sensitivity and spectral resolution of the system, and hence more expensive is the magnet.

The first block to the left in Figure 2.0 refers to the digital part of the system. This usually involves a computer to control all the sequencing of events, processing and storing of data. It serves as the medium of communication between the user and the spectrometer. The transceiver is responsible for the generation and detection of analog RF signals. There are two modules in the transceiver, a transmitter, and a receiver. The transmitter performs the tasks of generating real-time RF pulses to stimulate the B<sub>1</sub> coil in the magnet system. This part is the main research core of this thesis. The receiver acts as a detector to detect the

returning FID. Firstly, the receiver amplifies the small RF FID signal and then digitises the signal. The digital data is processed to capture the NMR information. However, this thesis focuses only on the NMR RF transmitter, which is highlighted in red. The computer interface, magnet system and receiver module in the transceiver are not discussed in this thesis.

#### 2.2 Fundamentals of the Sinusoidal Oscillator

A sinusoidal oscillator is also known as a sine-wave generator and is used to generate a sine waveform. The synthesis process is known as digital sine oscillation. The summary below shows examples of sinusoidal oscillators presented over the past few years.

#### 2.2.1 Recursive Oscillators

Recursive oscillators use the traditional methods to produce cosine or sine signals. In the early 1900s, the German physicist Heinrich Barkhausen modelled an oscillator as an amplifier. His model has the output feedback to input via a phase shifting network. The Barkhausen criteria for the oscillator require the function gain to be equal to one, and the total loop phase shift needs to be a multiple of  $2\pi$  radians [43].

As a result, several oscillators have been designed with this approach such as [43]:

- Direct Form oscillator

- Coupled Form Oscillator

- Digital Waveguide Oscillator and many more

This thesis concentrates on the development of a sinusoidal oscillator using the builtin modules of an FPGA device. The sinusoidal oscillator can be implemented by either using Coordination Rotation Digital Computer (CORDIC) or DDS modules in the FPGA devices.

#### 2.3 Direct Digital Synthesis

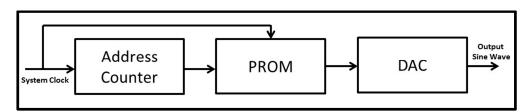

DDS usually refers to look-up table (LUT) based sinusoid generators. A DDS is a technique to generate frequency- and phase-tunable output signals. It uses digital data processing blocks with a fixed-frequency precision clock to generate a sinusoidal signal [5]. In Figure 2.1, a simple DDS can be created with a precision reference clock, an address counter, a Programmable Read-Only Memory (PROM) LUT and a DAC chip. In this basic system, PROM stores the amplitudes of a complete sine-wave. The address counter is used to generate memory addresses to access the PROM. A memory address is an identifier for a memory location in the PROM. The memory address will retrieve the digital amplitude from the PROM to the DAC chip.

Figure 2.1: Basic DDS structure [8].

There are two factors to determine the output frequency generated by a DDS block:

- Frequency of the DDS system clock

- Sine-wave step size

The advantage of using the DDS based system is that the simplistic architecture of the DDS system is less susceptible to the tuning flexibility. The reason is the output frequency can only be changed by modifying the system clock speed or by re-programming the step size in the PROM.

#### 2.3.1 Phase Accumulator

The main part of the DDS system is the phase accumulator whose contents are updated once on each clock cycle. Each time the phase accumulator is triggered, the tuning word or phase increment, M is added to the contents of the phase accumulator. Let us assume that the initial content of the phase accumulator is 00...00 and M=00...01. The phase accumulator is updated by 00...01 on each clock cycle.

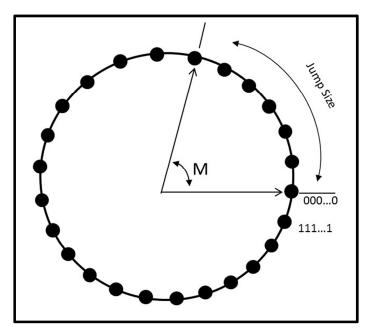

A phase accumulator replaces the address counter in Figure 2.1 to introduce a function known as a 'phase wheel'. This 'phase wheel' can be visualised as a vector rotating around the phase circle as illustrated in Figure 2.2.

Figure 2.2: Digital phase wheel [5].

In Figure 2.2, every point of the phase wheel corresponds to the sample phases of a full sine-wave. When the vector rotates around the wheel, a phase accumulator is visualised to generate equivalent phases of a sine-wave signal. One revolution of vector rotation of the phase wheel at a constant speed produces a finished cycle of an output sine-wave. The revolution of the phase wheel represents an overflow in the phase accumulator. Nevertheless, this complete output sine-wave is linear and is unsuitable to be applied directly to generate a sine-wave signal. Hence, a sine LUT is used to convert the output phases to sine-wave digital amplitudes. A DAC chip is then used to convert these amplitudes to an analog signal [5].

Each time the phase accumulator receives a clock pulse, the phase accumulator increases the stored number in the phase register by adding a tuning word to that register. The

magnitude of phase increment is based on the frequency tuning word. This frequency tuning word forms a 'hopping' process to skip the N-bit phase points of the phase wheel. These N-bit phase points are known as phase step size or phase jump size. The control over the jump size constitutes the frequency tuning resolution of the DDS system. The larger the jump size, the faster the phase accumulator overflows to complete the generation of a sine-wave cycle [5].

Any changes in the frequency tuning word result in immediate changes in the output frequency. The output frequency is inversely proportional to the number of samples per cycle. When the output frequency increases, the total samples per unit cycle decrease. However, the Nyquist sampling theory dictates a complete sine-wave must have at least two samples per cycle to construct the output waveform. Thus, the maximum frequency of an output sine-wave is half of the DDS system clock.

In summary, the frequency of a sine-wave signal can be expressed by the equation (2.0) below:

$$f_{out} = \frac{M}{2^N} f_{system}$$

$$So, M = \frac{f_{out} \times 2^N}{f_{system}} \tag{2.0}$$

$f_{out} = the \ frequency \ of \ an \ output \ sine - wave \ signal$

M = frequency tuning word

N = N - bit of a phase accumulator

$f_{system} = system frequency$

'M' is also known as a digital number for phase hopping in an accumulation. 'N' is the total bits of a phase accumulator, so  $2^N$  is the amount of steps available in the accumulator. The division of  $f_{\text{system}}$  by  $2^N$  represents the frequency resolution of the system.

# 2.3.2 Phase-to-Amplitude Converter

In this thesis, the phase-to-amplitude converter or LUT is configured as a sine LUT. If B represents the width of a truncated phase, a sine LUT can be simply a read-only memory containing 2<sup>B</sup> samples that create the sample-domain waveform from the truncated phase received from the phase accumulator. In other words, it converts phases from a phase accumulator to amplitudes. These digital phases are also the memory addresses used to retrieve the corresponded amplitudes from the sine LUT.

A PROM can be used to implement a sine LUT. A PROM based LUT is easily implemented due to the simplicity of the PROM circuit. A LUT contains one complete cycle of the waveform to be generated. The LUT translates the truncated phases into the sample amplitudes which are then converted to an analog signal by DAC.

If a high precision signal is required, the LUT needs a very large capacity as more bits are required to store the amplitudes. This increases the hardware cost and the implementation is limited by the capacity of the PROM. Practically, only the 'high bits' of an accumulated phase are used as a memory address to access the LUT. Generally, these high bits are known as the truncated phase. The size of a LUT is  $2^B$  words, therefore B <N; N is the width of accumulated phases.

#### 2.3.3 Phase Truncation

The N-bit of a phase accumulator determines the frequency resolution of a DDS system. The greater the value of N means the better the resolution of the system. However, the high frequency resolution of the DDS system can increase the capacity of the LUT block. Considering that each entry of the LUT block has an N - bit of precision data, it then requires a huge capacity of LUT. For example, for the LUT block of Xilinx FPGA devices, the phase truncation is done in the LUT block before converting the phase to amplitude. Generally, the width of a phase accumulator block of Xilinx devices can be up to 48 bits. If all the 48 bits are used, then the LUT block requires 281.147 X 10<sup>12</sup> bits of memory.

In a practical DDS system, all the bits of the phase accumulator are not passed on to the LUT. These bits are truncated, leaving only some of most significant bits (MSB) for amplitude conversion. This method reduces the size of the LUT and does not affect the frequency resolution.

A phase truncation technique uses a fraction of the MSB of the accumulator output to provide phase information. If a phase accumulator has data length = N-bit and no phase truncation has applied to the accumulated phases, then the LUT needs  $2^N$  depth to store the amplitudes. If the phase truncation is applied, the lower N'-bit of the accumulated phase is ignored. Then, the accumulated phase remains the upper N-N'-bit. This N-N'-bit is the data width of a truncated phase which means N-N' = B. Therefore, the sine LUT needs only  $2^{(N-N')}$  or  $2^B$  bits to store the data.

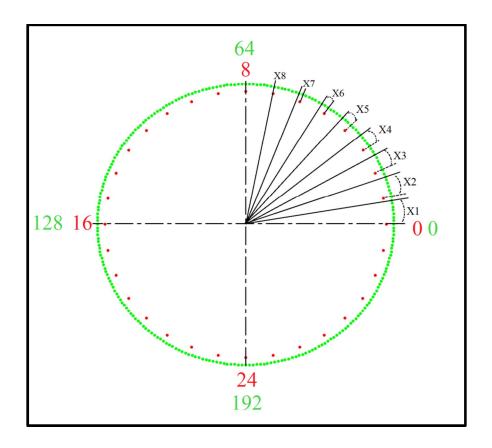

The implication of phase truncation can be depicted by the concept of the 'digital phase wheel'. In order to give a clear explanation of the digital phase wheel, assume a simple 8-bit phase accumulator of which only the upper 5 bits are used as input to sine LUT. The result is the phase resolution represented by the outer circle tic marks. After the truncation, the resolution is identified by the inner circle of tic marks [5]. The phase resolution of an 8-bit phase accumulator is  $360^{\circ}/2^{\circ} = 1.406^{\circ}$ .

Figure 2.3: Phase truncation error [5].

If a tuning word of 7 is selected, the accumulator would have increments of 7. In Figure 2.3, the first eight phase angles correspond to the count steps of the phase accumulator. After the first count on the outer circle (increment by 7), the phase step falls short of the first inner tick mark. It causes a discrepancy between the phases of the outer circle (8-bit resolution) and inner circle (5-bit resolution). The phase error due to this discrepancy is  $7 \times 1.406^{\circ} = 9.842^{\circ}$  as noted by X1 in Figure 2.3.

After the  $2^{nd}$  phase step, 7 more counts on the outer circle. The accumulated phases fall between the  $1^{st}$  and the  $2^{nd}$  tick marks on the inner circle. Again, there is a discrepancy between the phases of the outer circle (8-bit resolution) and inner circle (5-bit resolution). The phase error is  $6 \times 1.406^{\circ} = 8.436^{\circ}$  as noted by X2 in Figure 2.3.

The phase errors due to the discrepancy between the inner and outer circles on every clock cycle are listed below:

On the  $3^{rd}$  phase step (X3), phase error is 5 X 1.406° = 7.03°

On the 4<sup>th</sup> phase step (X4), phase error is  $4 \times 1.406^{\circ} = 5.624^{\circ}$

On the 5<sup>th</sup> phase step (X5), phase error is 3 X  $1.406^{\circ} = 4.218^{\circ}$

On the  $6^{th}$  phase step (X6), phase error is 2 X 1.406° = 2.812°

On the  $7^{th}$  phase step (X7), phase error is 1 X 1.406° = 1.406°

On the  $8^{th}$  phase step, phase error is  $0 \times 1.406^{\circ} = 0^{\circ}$ . The reason is that the accumulator phase (outer circle) and the 5-bit resolution phase (inner circle) coincide. As a consequence, there is no discrepancy between these two circles and so no phase error. This pattern continues as the accumulator increments by 7 (each time) which are represented by the outer circle.

Hence, the phase errors due to the truncation will result in errors in amplitude during the phase-to-amplitude conversion. Fortunately, the phase errors are periodic. In other words, the accumulator phase and truncated phase will coincide after some revolutions of the phase wheel regardless of the tuning word.

Although the phase truncation leads to the truncation error, it can be reduced by applying a noise shaping technique. The noise shaping technique used in this Master research is the Taylor Series Corrected DDS.

# • Taylor Series Corrected DDS

In the Taylor series corrected DDS; the previously discarded fractional bits have been used to calculate corrections to the phases. The corrections are added to the look-up table values to produce outputs with very high spurious free dynamic range (SFDR). This noise shaping technique can maintain the LUT to a reasonable size. The Taylor series corrected approximation is the expansion of a function of:

$$f(x) = f(a) + f'(a) \frac{(x-a)}{1!} + f''(a) \frac{(x-a)^2}{2!} + \cdots$$

(2.1)

Hence, the Taylor expansion of  $\sin\left(\frac{\pi}{2}q\right)$  (quarter-wave storage in LUT) is as below:

$$\sin\left(\frac{\pi}{2}q\right) = \sin\left(\frac{\pi}{2}r\right) + k_1(q-r)\cos\left(\frac{\pi}{2}r\right) - \frac{k_2(q-r)^2\sin\left(\frac{\pi}{2}r\right)}{2} + \cdots \tag{2.2}$$

The total q-bit phase is divided into the upper phase 'r' and the lower phase 'q-r' [48]. After the phase truncation, only the upper phase 'r' is used for the phase information, so the Taylor series is performed around 'r'.

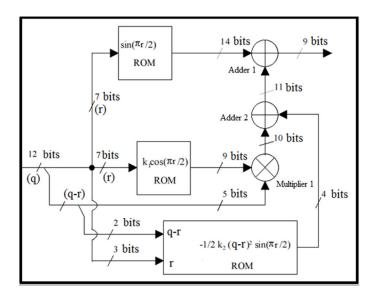

The phase values have angular units so the constant  $k_n$  (n=1,2,3...) is used to adjust the units of each series term.  $k_n$  includes a multiple of  $\pi/2$  to compensate for the phase units. It is also used to make sure the expression is always positive [15]. From equation (2.2),  $k_1$  is  $\pi/2=1.57$  and  $k_2$  is  $-(\pi/2)^2=-2.47$ . The Taylor series approximation takes up to three terms. In fact, additional terms can be employed but the contribution to the accuracy is very small [48]. This architecture needs two read-only memory (ROM) blocks to store  $\sin\left(\frac{\pi}{2}r\right)$  and  $\cos\left(\frac{\pi}{2}r\right)$ . The unit conversion factor  $k_n$  is included in the values stored in the sine and cosine ROMs.

Figure 2.4: Taylor series approximation for quarter sine converter [48].

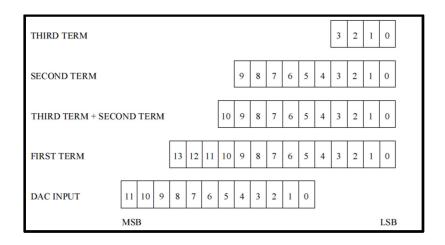

Figure 2.5: Relative bit position of data word implemented in Figure 2.4[48].

For example, an input phase (q) has 12 bits (Figure 2.4). The upper 7 bits of 'q' are used as the upper phase increment 'r'. This 'r' is transferred to both sine ROM and cosine ROM at the same time. The upper 7 bits are the address signals and hence determine the number of entries in the ROMs. More bits in the upper phase address result in a larger LUT with decreased speed and greater cost. The  $\sin (\pi r/2)$  ROM is the first term of the Taylor series expansion. The output from the sine ROM will then sum the other terms from the expansion to re-construct the final phase (Adder 1).

The output of the  $\cos{(\pi r/2)}$  is configured to incorporate the predetermined unit conversion value  $k_1$ . The cosine ROM is less significant than the amplitude term. Thus, the output can be at lower accuracy and so 9-bit output number is used. The lower 5 bits (q-r) are used to compute the other two terms used in the Taylor series expansion. The 'q-r' is

multiplied with the output from cosine ROM to generate the second term (Multiplier 1). The second term has 10-bit output number.

The MSB of output from the 'multiplier 1' has a bit alignment with the DAC input Least Significant bit (LSB). Because of the alignment, the output number ranges from 1 LSB to 1/1024 LSB of the final 10-bit DAC input used. Not all the bits after the 'multiplier 1' are needed to maintain the accuracy of the system. Therefore, the system truncates the multiplication product to 10 bits. In any case, truncation to 10 bits after 'multiplier 1' was used in the example in Figure 2.4. Any bit widths can be used as desired as long as the principles of the design are met.

The third expansion term is computed in a ROM by combining the derivative of sin  $(\pi r/2)$  and  $(q-r)^2$ . This is done by selecting the upper 2 bits of 'q-r' and the lower 3 bits of 'r' as a portion of the address for the ROM. This is possible because the last expansion term only contributes roughly 1/4 LSB to the DAC input (see Figure 2.5). In Figure 2.4, only the 'r' is needed for this degree of accuracy. Finally, the third term ROM output will combine with the 'multiplier 1' output in 'Adder 2'. Subsequently, the result will combine with the first term ROM output in the 'Adder 1'.

#### **2.3.4 CORDIC**

CORDIC is an algorithm used for computing the hyperbolic and trigonometric functions, where the initial vector is rotated by a predetermined sequence of sub-angles. The summation of the rotations approaches the given angle by using minimal hardware such as shift, add, subtract and compare [14, 50]. When comparing CORDIC with the ROM-based DDS, CORDIC does not incur an exponential growth of the hardware as the output word size increases. However, it is difficult to achieve high throughput because of the sequential nature of the algorithm [14].

Two architectural configurations are available for the CORDIC core:

- 1. A fully parallel configuration with single-cycle data throughput at the expense of the silicon area

- 2. A word serial implementation with multiple-cycle throughput but occupying a small silicon area

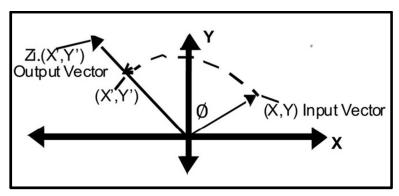

According to Volder, an algorithm is derived from the general rotation. A transform rotates a vector (X, Y) through an angle  $(\emptyset)$ . This rotation yields a new vector (X', Y') in a Cartesian plane. The equations below represent the condition of the rotation [50]:

$$X' = X\cos\phi - Y\sin\phi \tag{2.3}$$

$$Y' = Y\cos\phi - X\sin\phi \tag{2.4}$$

$\emptyset' = 0$

A CORDIC can operate in two major modes. The first is rotation mode and the second is vectoring mode. The CORDIC algorithm introduces a constant scale factor,  $Z_n$ , which is only dependent on the number of iterations (n) and can be compensated by multiplying a  $1/Z_n$  [10].

#### 2.3.4.1 Rotation Mode

CORDIC rotates a vector by a specified angle, also known as micro-rotations. These micro-rotations are the sequence of successively smaller rotations, each of the atan  $(2^{-i})$ . The entire process can be expressed as a simple shift and add/ subtraction operations. Equation (2.5) to (2.7) shows the expression for an  $i^{th}$  iteration, where i is the iteration index from 0 to n.

$$x_{i+1} = x_i - \alpha_i \cdot y_i \cdot 2^{-1} \tag{2.5}$$

$$y_{i+1} = y_i - \alpha_i \cdot x_i \cdot 2^{-1} \tag{2.6}$$

$$\emptyset_{i+1} = \emptyset_i + \alpha_i \cdot \text{atan}(2^{-i}), \tag{2.7}$$

$\alpha_i = \pm 1$  indicates the direction of rotation

If the series of 'n' micro-rotations are performed by the CORDIC algorithm, the expression in the  $n^{th}$  iteration can be summarised using equation (2.8) to (2.10) below:

$$X' = \prod_{i=1}^{n} \cos \left( \tan(2^{-i}) \right) (X_i - \alpha_i Y_i 2^{-i})$$

(2.8)

$$Y' = \prod_{i=1}^{n} \cos \left( \arctan(2^{-i}) \right) (Y_i - \alpha_i X_i 2^{-i})$$

(2.9)

$$\emptyset' = \sum_{i=1}^{n} \emptyset - (\alpha_i \cdot \operatorname{atan}(2^i))$$

(2.10)

The explanation above can be simplified by the diagram of vector rotation in Figure 2.6 below.

Figure 2.6: Diagram of vector rotation [58, 60].

In Figure 2.6, the vector (X, Y) is rotated through the angle  $(\emptyset)$  to a new vector (X', Y'). The vector rotation is dependent on the value  $\alpha_i$ . The direction of the rotation  $\alpha_i$  should

be selected so that  $\emptyset'$  converges towards zero. For example, if  $\emptyset_{i+1} \ge 0$ ,  $\alpha_i = -1$  and if  $\emptyset_{i+1} < 0$ ,  $\alpha_i = +1$ . The coordinate components of the output vector are computed after the given coordinates component of an input vector are rotated to the desired angle  $(\emptyset)$ . The equations (2.11) to (2.13) show the expression of these coordinates. [50]:

$$X' = Z_n \cdot X \cos \emptyset - Y \sin \emptyset \tag{2.11}$$

$$Y' = Z_n.Y\cos\phi + X\sin\phi \tag{2.12}$$

$\emptyset' = 0$

CORDIC Scale Factor,

$$Z_n = \prod_{i=0}^n \sqrt{1 + 2^{-2i}}$$

(2.13)

The vector rotation mode is used for the conversion of polar coordinates to the rectangular coordinates. However, it is also used to calculate the sine and cosine functions.

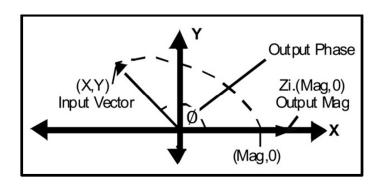

# 2.3.4.2 Vectoring Mode

The vector translation is the modification of the vector rotation algorithm. In vector translation, CORDIC rotates the input vector towards the x-axis while accumulating an angle. The attribute of the vector translation can calculate the magnitude and phase of the input vector. Thus, it is used to convert the rectangular coordinates to be polar coordinates. Figure 2.7 below shows the basic operation of the vector translation.

Figure 2.7: Diagram of vector translation [58, 60].

In Figure 2.7, the vector translation rotates the input vector (X, Y) around the circle until the angle aligns the result vector with the X-axis (Y=0) [49]. This is the point where the magnitude X' and angular argument  $\emptyset$ ' of (X, Y) are computed. The direction of the rotation  $\alpha_i$  should be selected so that Y' converges towards zero. For example, if  $\emptyset_{i+1} \ge 0$ , then  $\alpha_i = -1$  and if  $\emptyset_{i+1} < 0$ , then  $\alpha_i = +1$ . The CORDIC equations for the vector translation are [50]:

$$X' = Z_n \sqrt{X^2 + Y^2} \tag{2.14}$$

Y'=0

$$\emptyset' = \operatorname{atan}\left(\frac{X}{Y}\right) \tag{2.15}$$

CORDIC Scale Factor,

$$Z_n = \prod_{i=0}^n \sqrt{1 + 2^{-2i}}$$

(2.16)

Both vector rotation and vector translation are limited to the rotation angles between  $\pm 90^{\circ}$ . This restriction is due to the use of  $2^{\circ}$  for tangent in the 1<sup>st</sup>-iteration. A complete sinewave is symmetric from quadrant to quadrant. Every sine value from 0 to  $2\pi$  can be represented by reflecting or inverting the first-quadrant. If any rotation angles are greater than  $90^{\circ}$ , coarse rotation and inverse coarse rotation are needed. The coarse rotation is used to shift

the input samples from the full circle into the first-quadrant. The inverse coarse rotation is used to shift the output samples to the correct quadrant [10, 58, 60].

Several functions can be operated by the CORDIC such as:

- Sine and cosine function

- Polar-to-rectangular transformation

- Arctangent function

- Vector magnitude function

- Cartesian to polar transformation

- Inverse CORDIC function and so on

Usually, only sine and cosine functions are used for sinusoidal oscillation [44].

# 2.3.4.3 Sine and Cosine Function

Sine and cosine functions of a particular input angle can be computed using vector rotation mode to generate a  $2\pi$  sinusoidal waveform. However, the CORDIC algorithm is only valid for the first-quadrant. Therefore, an optional course and inverse rotation module is used to extend the range of the input angle (X) to the full circle in order to cover the four quadrants [58, 60].

Initialising the input vector component Y=0 into equations (2.17) and (2.18) reduces the rotation mode.

$$X' = Z_n X_0 \cos \emptyset_0 \tag{2.17}$$

$$Y' = Z_n X_0 \sin \emptyset_0 \tag{2.18}$$

By letting  $X_0 = \frac{1}{Z_n}$ , the un-scaled sine and cosine of an angle argument  $\emptyset_0$  will be produced to modulate the magnitude value. A rotator gain is used to scale the output of CORDIC. If the gain  $X_0$  does not produce satisfying results, a single multiplier can be used to place an additional gain constant before the CORDIC rotator. This step can produce unscaled results.

# 2.3.5 DAC

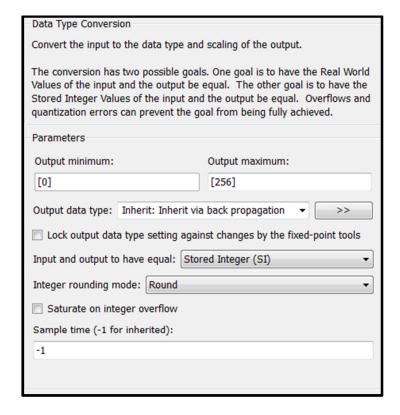

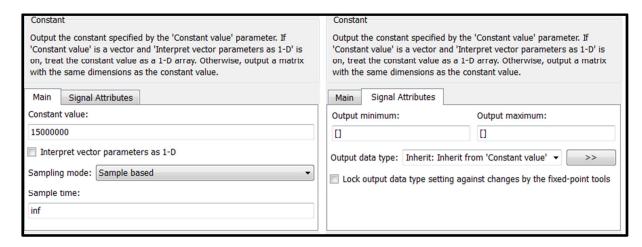

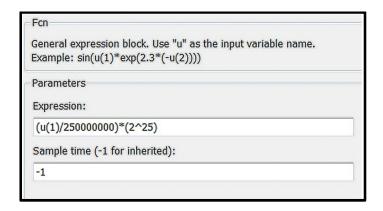

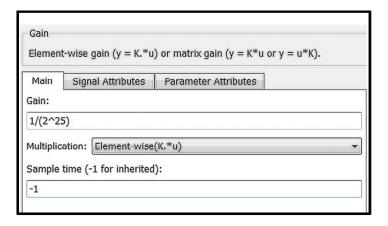

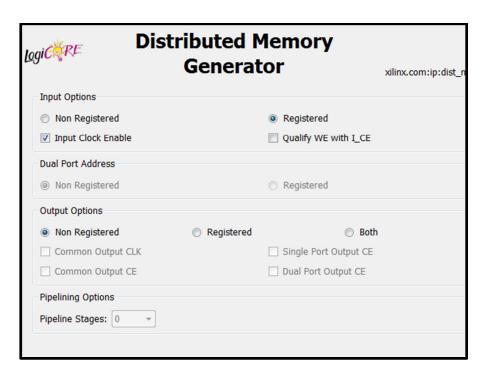

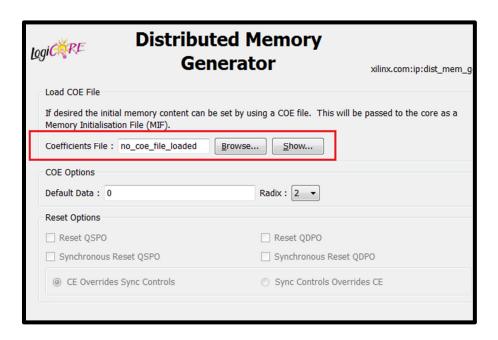

The phase accumulator generates phases, which are the addresses for a sine LUT. These digital phases cannot be used in NMR applications because the results are linear and must be converted to the corresponding values of analog voltage or current.