# Chapter 1

# Introduction

This thesis deals with the design, development and application of components for wide bandwidth signal processing in radio astronomy. In order to set the context for the work that follows, I will give a brief introduction to the field of radio astronomy. This will give sufficient information to appreciate the relevance of the work in this thesis, and in particular the need for wider bandwidth observing systems than are currently in use. As radio astronomy is an extensive science this is not a comprehensive discussion and references such as [1] should be consulted for full information.

# 1.1 A Short Introduction to Radio Astronomy

Radio astronomy is the study of the observable Universe by means of received radiation of radio wavelengths. This encompasses electromagnetic emissions with frequencies ranging from a few megahertz to over a terahertz. The mechanisms responsible for these emissions are many and varied and it is through the study of these emissions, and their interactions with other matter, that the physical processes occurring within astronomical bodies can be investigated.

Conventionally, radio astronomical observations can be classified into

three broad classes: Radiometry; Spectroscopy and Interferometry.

#### 1.1.1 Radiometry

Radiometry is the observation mode where the total power emitted by a source within a given receiver bandwidth is measured. This is useful if one is attempting to detect the presence or absence of a source, but is not interested in its spectrum. In this mode the total power is measured, and by doing on and off source measurements, the increase in received power due to the source can be determined, and with suitable calibration the source flux. Typically the presence of a source will only raise the system temperature by a few milliKelvin in a background system temperature of several hundred Kelvin. This requires the power to be measured to an accuracy of better than 1 in 10000. It is the accuracy to which the power can be measured that sets the ultimate sensitivity of the radiometer. The power measurement from the radiometer fluctuates around the true value and has to be integrated until the variance of the measurement error is a few standard deviations smaller than the increase in power due to the source, to be able to make a reliable detection. In a Nyquist sampled measurement bandwidth of B and an averaging time of T there are 2BT independent samples than can be taken. The standard deviation of an average of N normally distributed samples is  $\sqrt{\frac{2}{N}}$  so the standard deviation of the radiometer measurement is

$$\frac{\delta P}{P_0} = \frac{1}{\sqrt{BT}},\tag{1.1}$$

where  $P_0$  is the mean power. This equation is known as the radiometer equation and describes the theoretical maximum sensitivity of a radiometer system of a given bandwidth with a given integration time. A rigorous derivation of this important result can be found in [1].

### 1.1.2 Spectroscopy

Spectroscopy is concerned with measuring the frequency spectrum of a source. This is useful for determining the presence or absence of elements and molecules, the rates by which objects are receding, approaching or rotating by means of Doppler shifts, conditions of temperature and pressure, and many other uses. In order to measure the spectrum we need a device that separates the received radio signal into its separate wavelength components. In optical astronomy this is done using gratings or prisms. In the radio regime special purpose instruments must be built for this task. The design of some of the key components of such radio spectrometers is what forms the main topic of this work. The sensitivity relation 1.1 also applies to a spectrometer but with the bandwidth being the per channel bandwidth.

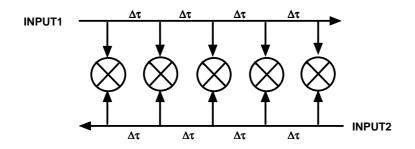

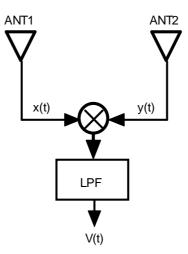

#### 1.1.3 Interferometry

Interferometry is a technique that allows an increase in resolution by observing a source with two or more telescopes separated by some distance, which can range from metres to many thousands of kilometres. Effectively, the resolution of the observation is equivalent to that of a telescope with diameter equal to the separation of the two telescopes. By repeating the observations using many pairs of telescopes with different spacings, possibly over periods of many months, and relying upon the rotation of the Earth, an image of the source in the spatial Fourier component domain can be obtained, which can then be inverted to give a true intensity image [2].

## **1.2** Importance of Wide Bandwidths

There are several reasons why using wider bandwidths for observations are very desirable. From the brief discussion above it is clear from 1.1 that the sensitivity of an observation is proportional to the square root of the bandwidth. Increasing the bandwidth by a factor of four allows sources twice as faint to be detected in the same observation time, or alternatively, sources of the same brightness can be detected in a quarter of the time, massively reducing the time required for large surveys.

In the case of spectrometers increased bandwidth is equivalent to increased velocity coverage. That is, the shift in the rest frequency of atomic and molecular emissions due to Doppler shifts. For instance, the hydrogen emission in a rotating galaxy may manifest itself as two large peaks, centred around the mean velocity of recession, due to the line of sight concentration of mass of the two edges rotating towards and away from us, with a broad velocity spread in between. If the galaxy is rotating sufficiently fast, it may be impossible to fit the entire galaxy profile within the bandwidth available, making it impossible to establish a baseline for the emission. As observing frequencies move constantly higher the same fractional bandwidth implies a greater absolute bandwidth, so that objects of the same Doppler shift observed at higher frequencies require more absolute bandwidth for the same velocity coverage.

# **1.3** List of Contributions

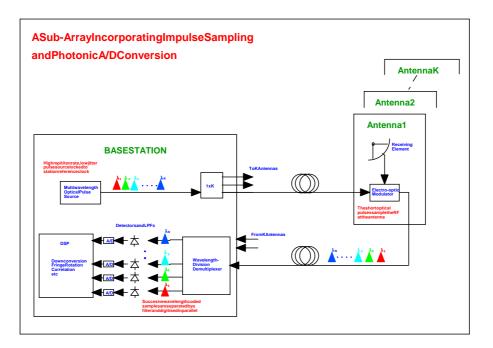

In this thesis I will deal with the design, analysis, implementation and application of wide bandwidth signal processing components to all three of the areas of radio astronomy mentioned previously.

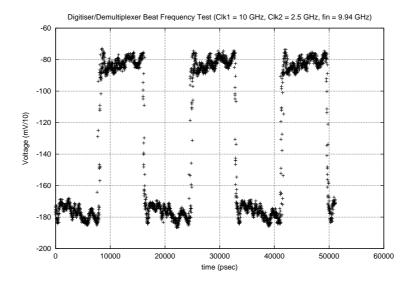

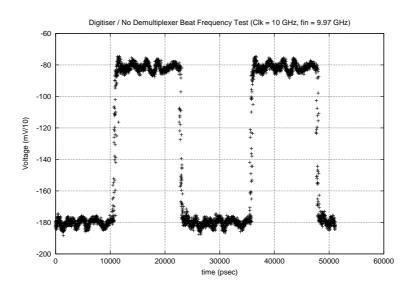

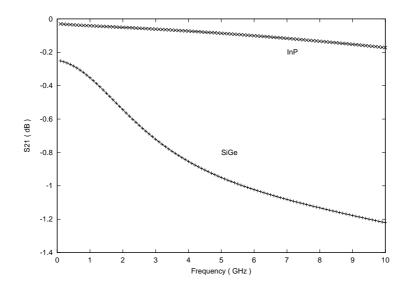

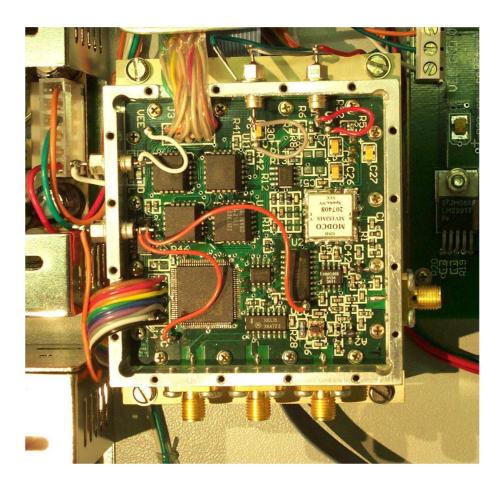

I will present the design and implementation of high speed three-level digitisers using an Indium Phosphide Heterojunction Bipolar Transistor (InP HBT) integrated circuit process. They are intended for use in autocorrelation spectrometers and crosscorrelation imaging systems. A detailed analysis of the performance limits of these designs is presented along with the solution to practical problems of packaging and system integration. These digitiser integrated circuits will be shown to operate at up to 10 giga-samples/s, significantly faster than other reported digitisers for radio astronomy, and one of these devices is integrated into a complete 4 giga-sample/s digitiser sys-

tem, along with required support hardware. This digitiser system has been installed at the Parkes radio observatory. A further novel photonic I/O digitiser is presented which contains an integrated photonic interface, which I believe is the first digitiser device reported with integrated photonic connectivity.

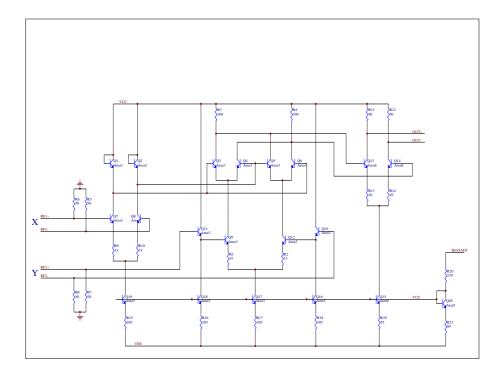

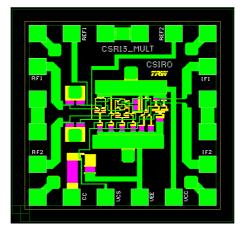

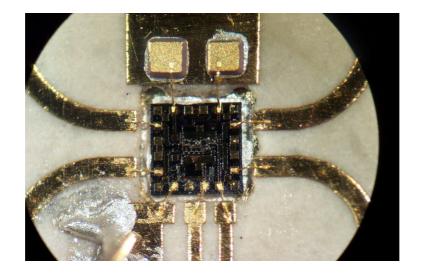

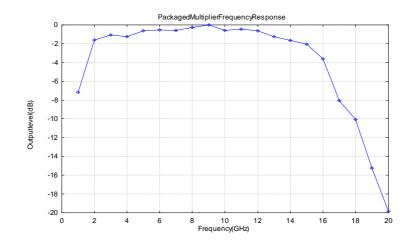

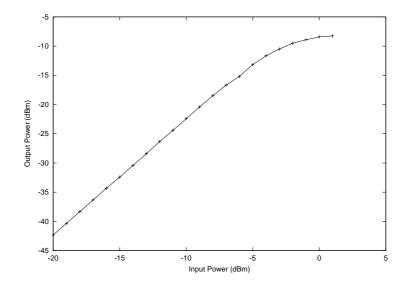

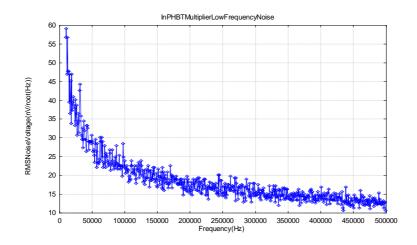

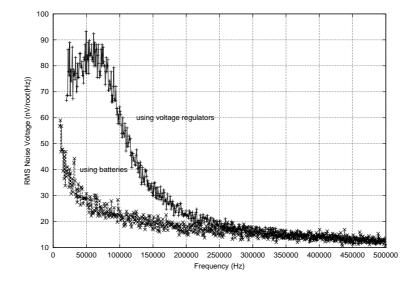

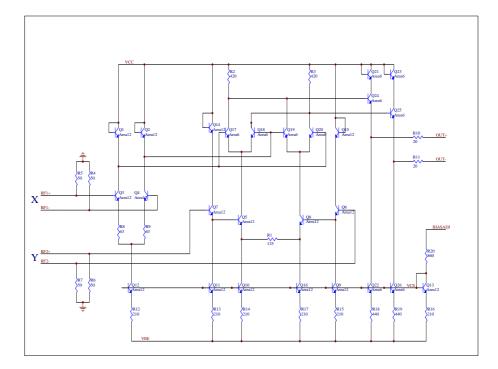

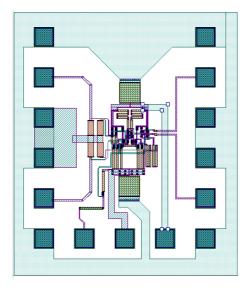

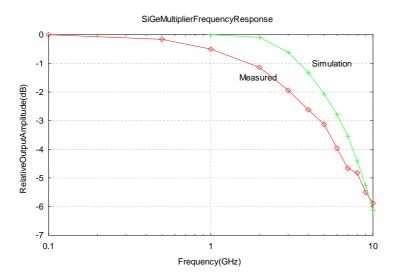

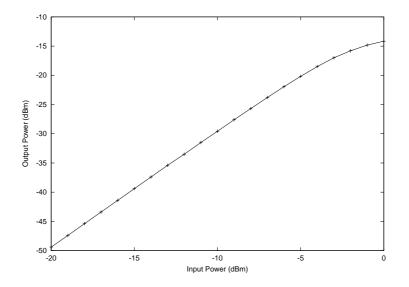

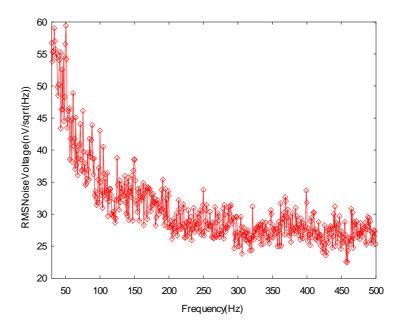

On the topic of wide bandwidth multipliers for analogue correlators, I will present the design and development of a 15 GHz bandwidth analogue multiplier IC in InP HBT technology and give a detailed noise analysis of multipliers in analogue correlators. This noise analysis will highlight the need for low noise back-end components in wide bandwidth systems, in contrast to the generally accepted wisdom at lower bandwidths. This will prompt the development of a further analogue multiplier IC in SiGe HBT technology which has the benefit of reduced low frequency noise, and which provides a better solution for analogue multipliers if problems of substrate loss can be overcome.

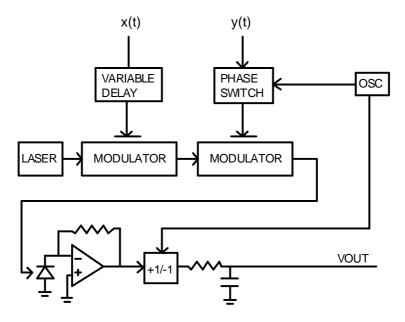

To push bandwidth capabilities further I will present a new photonic multiplier system and experimental results that confirm its operation. This photonic multiplier is capable of operating to greater bandwidths than semiconductor multipliers. A noise analysis of the photonic multiplier is provided. Finally, an application of photonic analogue-to-digital converters to radio astronomy digitisers is presented.

# Chapter 2

# High Speed Digitisers

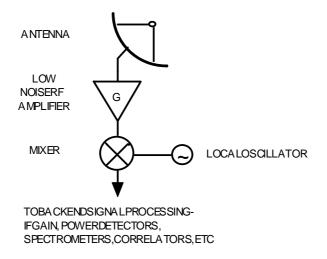

A digitiser is the component in a radio astronomical receiving system that samples and quantises the down-converted radio frequency (RF) signal for subsequent digital processing. It is a type of analogue-to-digital converter (ADC) tailored to the requirements of astronomical signal processing. In this work I will use the term digitiser to refer to such devices in order to differentiate them from general purpose ADCs. Figure 2.1 shows a simplified diagram of the receiving chain in a typical radio telescope. The source of interest is observed using a collector of some kind, for example a large parabolic dish with a feedhorn. The collected signal is then amplified with a low noise amplifier (LNA), which is typically cooled to reduce electronic noise contributions. The received signal is then mixed down and amplified, through one or more stages, to somewhere near baseband to ease the operation frequency requirements of the following components. Many variations on the above simplified signal chain exist, for instance in the case of very high observing frequencies where adequate LNAs do not exist and the received signal is directly mixed down to a convenient IF using low noise, high frequency SIS mixers, but as this is not the central topic of this work I will not go into detail on the many types of receiver systems that exist. Once the bandwidth of interest has been mixed to near baseband then the signal is typically digitised, that is, converted to a digital representation that is then

Figure 2.1: Simplified superheterodyne radio telescope receiver.

sent to a correlator or spectrometer of some type, depending on the exact instrument. The correlator is a special purpose instrument that measures the correlation function of two time varying signals supplied to its inputs. If the two signals are the same it forms the autocorrelation function, which can be inverted by virtue of the Wiener-Khinchine theorem, to give the spectrum of the input signal. The Wiener-Khinchine theorem states that the power spectral density and autocorrelation function of a stationary signal form a Fourier transform pair [3]. If the two signals are different the correlator measures the cross correlation function of the two inputs, which is the fundamental input data for interferometric synthesis imaging. This digital approach is used in almost all modern radio telescope spectrometers and correlators because of the advantages of stability, reproducibility and reliability of digital electronics, compared to analogue implementations, and the ease of varying the bandwidth by simple sample rate variation.

In the case of cross-correlators for interferometers, the order of the frequency transform and time multiplication can be reversed in the correlator with the two systems of different sequence of operations known as XF or FX [4]. Either the XF of FX architecture will be more optimal in a particular situation depending on many parameters such as number of baselines to be processed, bandwidth and ability to remove interference. This work is presented from the point of view of XF systems as this is the scheme used in all existing Australia Telescope National Facility (ATNF) correlators. The digitisers developed can be used in either architecture.

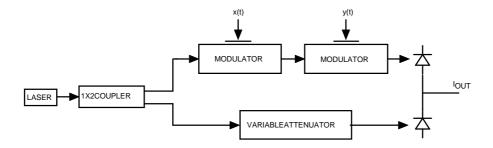

Analogue spectrometers do exist and have been used extensively and successfully, for example, acousto-optic spectrometers [5], chirp transform spectrometers [6] and filterbank spectrometers. Analogue cross correlators also exist [7] and the core multiplying component for such an analogue cross correlator forms the subject of chapter 5 of this work.

The split between analogue and digital approaches is a function of the bandwidth. In accordance with the Nyquist criterion a digital correlator must sample at a rate of at least twice the bandwidth of the signal to not introduce aliasing and loss of information. As bandwidths become larger this implies the digitisers must work at very high sample rates. The correlator portion of the system can be implemented in parallel by slicing the input signals into contiguous time chunks, so that very high sample rates can be accommodated in the correlator by using many correlator elements in parallel. However, the digitiser must operate at the full sample rate and so is the limiting component in present correlator systems. It was for this reason that I decided to look at extending the current level of performance in radio astronomy digitisers.

It is also possible to deal with large bandwidths by splitting the input analogue signal into several contiguous frequency bands, by means of an analogue filterbank, and then processing each of these with a lower bandwidth correlator. Systems of this type are known as hybrid correlators and several such implementations exist and are in use. However, they are affected by calibration problems in attempting to reassemble the contiguous bands after correlation [8]. Hybrid correlators also result in more physical hardware for the same bandwidth so that correlators that can process as much integral bandwidth as possible are preferred.

# 2.1 The Use of Digitisers in Digital Correlators

The chief use of digitisers in radio astronomy is as the analogue-to-digital conversion element in auto and cross correlators for spectrometry and imaging [9, 10]. Their end use in this application defines the key parameters of the digitisers. Most notable, compared to the conventional communications applications of ADCs, is the small number of quantisation levels generally used. Radio astronomy signals are usually the result of broadband emission from an ensemble of many uncorrelated emitters and so the resulting radiation has the form of white noise. It can be shown that the true correlation function, and therefore the frequency spectrum, can be derived from the digital correlation function of coarsely quantised bandlimited gaussian signals, with the only penalty being a loss of S/N ratio [11]. For instance, using three-level quantisation delivers 0.81 of the S/N ratio of an unquantised measurement, while four-level (two bit) quantisation yields an efficiency of 0.88 [12]. The advantage is that the implementation of the following correlator elements, usually in the form of ASICs, is simpler with one or two bit samples. This in turn allows very fast correlator ASICs to be designed giving large bandwidth coverage in a single chip. For input sample streams  $x_i$  and  $y_i$ , which may be the same for an autocorrelation, the correlator ASIC performs the operation

$$R_n = \frac{1}{N} \sum_{i=1}^{N} x_i y_{n-i}$$

(2.1)

where N is the number of samples processed and the subscript n refers to the lag number.

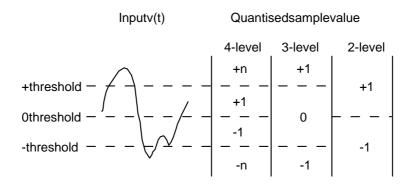

The latest correlator ASICs achieve equivalent sample rates over 1 GHz with several hundred lags in the correlation function using 3-level [13] or 4-level [14] quantisation. Almost all correlator systems currently in use in radio astronomy facilities around the world are either two-, three- or four level systems. Figure 2.2 illustrates these quantisation schemes. All the

Figure 2.2: 2-,3- and 4-level quantisation schemes.

digitisers developed in this work are three-level to be compatible with the three-level correlator ICs available at the ATNF [15]. The digitiser ICs can be used with four-level correlators, if necessary, by replacing the zero state of the three-level representation with a zero mean pseudo-random sequence in the least significant bit (LSB) of the four-level representation. Of course this does not recover the extra S/N lost in doing three-level instead of four-level quantisation. The ICs can also be used with two-level correlators by simply driving the threshold levels to the centre of the common mode range and taking one or other of the output bits.

### 2.1.1 Coarse Digitisation Basics

The previous section mentioned that for band-limited white noise signals, the spectrum derived by a correlation approach using coarse quantisation leads to only a small loss in signal-to-noise ratio, compared to a non-quantised measurement. As this is a somewhat surprising result, which is unfamiliar to people working with non-stationary communications type signals, I will go into a little more detail to show how this is the case.

Consider quantising the received signal into three levels, as the digitisers in this thesis are designed to do. This can be achieved using two threshold levels placed symmetrically about the mean DC level of the signal. For the purposes of analysis, consider the signal mean is zero and the signal variance is normalised to unity. Then, ignoring offset errors in the digitiser front-end, the threshold levels will be symmetrical about 0 of value +v and -v. The signal is quantised to value +1 if the signal, S, is > +v, 0 if the signal is between +v and -v, and -1 if the signal is < -v, at the instant of strobing the digitiser. This quantisation rule is displayed in equation 2.2.

Sample Value =

$$\begin{cases} 1 & S > v \\ 0 & -v \le S \le v \\ -1 & S < -v \end{cases}$$

(2.2)

Consider now two bandlimited white noise signals, x(t) and y(t), which have a true correlation  $\rho$ . The joint distribution of the signal voltages can be modelled by the bivariate normal distribution function for stationary, white noise signals. The probability that at any instant  $\{x(t) \ge x, y(t) \ge y\}$  is given by the integral of the bivariate normal distribution function  $L(x, y, \rho)$ defined by

$$L(x,y,\rho) = \int_{x}^{\infty} \int_{y}^{\infty} \frac{1}{2\pi\sqrt{1-\rho^{2}}} e^{-\frac{1}{2}\frac{(\bar{x}^{2}-2\rho\bar{x}\bar{y}+\bar{y}^{2})}{\sqrt{1-\rho^{2}}}} d\bar{x} d\bar{y}.$$

(2.3)

With three-level quantisation there are 9 possible states for the pair of sampled values of the two signals after quantisation. If we let the probability that the quantised samples are in state  $\{i, j\}$ , that is x(t) is quantised to iand y(t) is quantised to j, be given by  $P_{ij}$  where  $i, j \in \{-1, 0, 1\}$ , then the probabilities are defined by

$$P_{11} = P_{-1-1} = L(v, v, \rho)$$

$$P_{01} = P_{10} = L(-v, v, \rho) - L(v, v, \rho)$$

$$P_{-10} = P_{0-1} = L(-v, -\infty, \rho) - L(v, -\infty, \rho) - L(-v, -v, \rho) + L(v, -v, \rho)$$

$$P_{-11} = P_{1-1} = L(v, -\infty, \rho) - L(v, -v, \rho)$$

$$P_{00} = L(-v, -v, \rho) - 2L(v, -v, \rho) + L(v, v, \rho).$$

(2.4)

Using these, and some simplifications amongst the integral relations, the

expected mean value of the correlator output is

$$R(\rho) = \sum_{i} \sum_{j} ij P_{ij} = 2L(v, v, \rho) - 2L(v, v, -\rho).$$

(2.5)

The case of three-level quantisation leads to a fairly simple result since all of the products containing a multiplier of zero vanish. Nevertheless, in this case, as in general except for the simplest case of two-level quantisation, an analytic relationship between the correlation as measured  $R(\rho)$  and the true correlation  $\rho$  cannot be found. In order to correct the measured correlation to give the true correlation the previous expression can be inverted, usually in the form of a power series, and is applied to the measured correlation values prior to Fourier transforming to recover the spectrum. A detailed analysis of the previous result and inversion expressions over various ranges of validity can be found in [16].

To quantify the effect on signal-to-noise ratio of the quantising process we can note that the correlator usually operates with signals of low correlation. This allows several simplifications to be made. The variance of the correlator measurement given in equation 2.1 is

$$\sigma_R^2 = E\{R^2\} - E\{R\}^2, \qquad (2.6)$$

where  $E\{\ \}$  is the expectation. In the limit as the correlation approaches zero the second term approaches zero and the two processes, x(t) and y(t), become independent. Under these conditions and with Nyquist sampling so that successive samples are uncorrelated the expression for the variance reduces to

$$\sigma_R^2 = E\left\{\frac{1}{N^2} \sum_{i=1}^N \sum_{j=1}^N x_i y_i x_j y_j\right\} = \frac{1}{N^2} \sum_{i=1}^N E\left\{x_i^2 y_i^2\right\}.$$

(2.7)

$$= \frac{1}{N} E\left\{x_i^2\right\} E\left\{y_i^2\right\}$$

Hence the signal-to-noise ratio of the correlator measurement is

$$\left(\frac{S}{N}\right) = \frac{R\sqrt{N}}{\sqrt{E\left\{x_i^2\right\}E\left\{y_i^2\right\}}} \quad \rho \ll 1.$$

(2.8)

For the ideal case with no quantization this becomes

$$\left(\frac{S}{N}\right)_{ideal} = \rho\sqrt{N} \quad \rho \ll 1.$$

(2.9)

Thus, the efficiency of the correlator is

$$\eta = \frac{(S/N)_{quantized}}{(S/N)_{ideal}} = \frac{R(\rho)}{\rho\sqrt{E\{x_i^2\}E\{y_i^2\}}} \quad \rho \ll 1.$$

(2.10)

On using a first order in  $\rho$  approximation to the integral of the bivariate normal distribution function,

$$L(h,k,\rho) \approx \frac{1}{4} erfc(h/\sqrt{2}) \, erfc(k/\sqrt{2}) + \frac{\rho}{2\pi} e^{-\frac{1}{2}h^2} e^{-\frac{1}{2}k^2}, \tag{2.11}$$

in the expression for  $R(\rho)$  in equation 2.5, gives for the efficiency for threelevel quantisation

$$\eta_{threelevel} = \frac{2e^{-v^2}}{\pi \ erfc(\frac{v}{\sqrt{2}})}.$$

(2.12)

This expression is a maximum for v = 0.612, with a value of 0.81, at which point 27% of samples are in the +1 state, 27% of samples are in the -1 state, and 46% of samples are in the 0 state. This is the optimum point for threelevel quantisation and is the usual operating point of the digitiser. Similar results can be derived for slightly different schemes such as two or four level quantisation [12, 17, 18] and for correlator schemes which incorporate digital mixers for VLBI processing [19].

## 2.2 Current Digitisers for Radio Astronomy

The current state of the art in wide bandwidth digitisers for radio astronomy lies at approximately two giga-samples/s sampling rate. The widest bandwidth digitisers currently in use are the 1.6 giga-samples/s system deployed on the Green Bank Telescope in West Virginia designed at the National Radio Astronomy Observatory (NRAO) in Charlottesville, USA; the 2.0 gigasample/s system designed by the Max Plank Institute für Radio Astronomy (MPIFR) in Bonn, Germany [20]; the 2.048 giga-samples/s system deployed on the Swedish-ESO Submillimetre Telescope (SEST) in Chile designed by the author at the Australia Telescope National Facility (ATNF) [21], and the 2.048 giga-samples/s system deployed on the Nobeyama Millimetre Array designed by NTT Electronics Technology Co. [22].

The first three of these systems are based on a hybrid design approach. That is, they use individually packaged silicon-based devices assembled onto various types of microwave laminate and conventional printed circuit board (PCB). This is about the practical limit for this type of technology. There are several problems with this approach such as the bandwidth-limiting parasitics inherent in packaged devices, the problems of very high speed interconnect, the matching limitations of individually packaged components and performance degradation due to poor temperature tracking. All of these problems can be effectively dealt with by the use of integrated circuit technology.

The first integrated circuit digitiser IC for radio astronomy was the 2 bit digitiser device developed for the Nobeyama Radio Observatory in Japan by NTT Electronics Technology Co. [22]. This is a GaAs device which was designed for a sampling rate of 2.048 GHz. There was a problem with this device in that there was on-chip crosstalk between the clock and data which corrupts the digitised data to some extent, but they manage to use the devices by control of the input level [23]. The new digitisers for the Japanese 1-GBPS VLBI system do not use these devices. Instead, they have contracted the manufacturer of the Sony-Tektronix TDS784 high speed oscilloscope to modify their oscilloscope front-end to allow it to be used as a 1.024 giga-samples/s two-bit digitiser [24]. Recent work by Japanese groups has focussed on developing a high speed digitiser using individually packaged high speed GaAs decision circuit ICs, as used in fibre optic data transmission receivers, and packaged GaAs demultiplexer ICs [25]. They currently have performed tests on a one-bit prototype board and produced a 1 GHz bandwidth spectrum. Their two-bit system is constructed by splitting the input signal and sending it to three of the one-bit boards in parallel, with appropriate threshold level settings for the decision circuits. In this system achieving delay and bandpass matching would be very challenging. They mention that their next step is to move on to developing a dedicated digitiser integrated circuit.

Recently, the French team composed of groups from the Observatoire de Bordeaux, Université de Bordeaux and the Université de Grenoble have been pursuing an effort to design two and three bit digitiser ICs [26] as part of the technology effort for the Atacama Large Millimetre Array (ALMA), a large international project to build a millimetre wave array in the Atacama desert in Chile. They are using a SiGe BiCMOS process well suited for digitiser development. To date they have fabricated their first two generations of devices and presented results for their three-level device in a prototype setup which shows good performance to 5 giga-samples/s sampling rate [27]. Their digitisers have no on-chip demultiplexer and the full data rate from the flash converter is demultiplexed to a slower rate using a set of external commercial GaAs demultiplexer ICs.

## 2.3 Choice of InP-based Technology

There are several available semiconductor technologies that could be considered for implementing digitiser ICs. These include Si CMOS and BJT, GaAs HEMT and HBT, InP HEMT and HBT and SiGe HBT. Of all these semiconductor processes InP has the fastest intrinsic transistors in both HEMTs and HBTs. This is due principally to the much higher electron mobility in InP and InGaAs, of which transistors are composed in the InP material system. InGaAs has approximately 1.6 times the mobility of GaAs and 9 times the mobility of Si.

HEMT devices are unsuitable for implementing the digitiser because they lack the across wafer device matching needed for circuits with many hundreds of transistors. This is a result of the fact that the pinch-off voltage in HEMTs is a function of the device geometry, defined by lithography and etching, where as the equivalent turn-on voltage for bipolar devices is a function purely of the semiconductor material used.

GaAs and InP based processes have a strong advantage for high frequency circuits because the substrates are insulating, in combination with a backside Au ground plane and low inductance vias to ground. This allows the design of low loss and highly stable microwave circuits with well defined impedances in microstrip or conductor-backed coplanar waveguide. In contrast conventional silicon processes use a conductive silicon substrate, which has to be negatively biased, and have no backside ground plane or vias. The dielectric losses in the silicon combined with the device-to-substrate capacitance of the biased substrate lead to much greater losses, especially at higher frequencies. There are techniques such as silicon on insulator and high resistivity substrates designed to ameliorate these problems but they still do not give performance as good as the insulating substrates of GaAs and InP. The conductive silicon substrate, and considerable device-to-substrate capacitance of silicon processes, also leads to much greater signal coupling from digital nodes to sensitive analogue nodes in mixed signal designs. The digitiser devices reported previously in [27] for example contain no demultiplexer on chip, possibly because of concerns of coupling from the digital demultiplexer to the analogue portion of the chip.

SiGe HBT is a promising technology for new applications. By incorporating germanium into the base, a heterojunction bipolar transistor is formed that uses most of the process steps and manufacturing infrastructure of standard silicon processes, but with much greater speed [28]. The latest SiGe processes rival InP in performance, albeit with much smaller transistor dimensions [29, 30]. The SiGe processes still suffer from the additional losses due to the conducting silicon substrate. Nevertheless, SiGe is attractive since it offers a high speed process combined with the low-cost high-volume manufacturing of the silicon semiconductor industry.

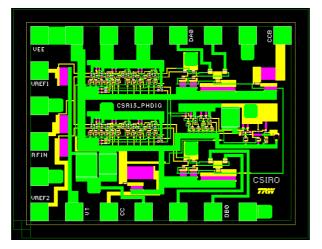

In all, the InP process offers the best combination of desirable properties for implementing the digitisers, and was the only available process at the time of beginning this project in 1998 that was sufficiently fast to meet the speed goal of 8 giga-samples/s conversion rate. The InP HBT process used was provided by TRW Corporation, Redondo Beach, California (this division has now become Velocium) and is described in [31]. This is a single heterojunction bipolar transistor process based on an InGaAs/InGaAs/InAlAs transistor structure for the collector, base and emitter respectively, grown with molecular beam epitaxy (MBE) on 3-inch semi-insulating InP wafers. The process has peak  $f_Ts$  of approximately 70 GHz, DC current gain ( $\beta$ ) of approximately 25 and breakdown voltages of  $BV_{ceo} \approx 8V$  and  $BV_{cbo} \approx 13V$ . InGaAs p-i-n photodiodes sensitive to 1.3-1.55 um light are also incorporated on wafer for opto-electronic applications. This was a non-commercial process with access enabled through a special collaborative agreement between the CSIRO and TRW. Radio astronomy provides a non-commercial, non-military application that benchmarks TRW's advanced process capabilities without commercial risk, and with the freedom to publicise results.

## 2.4 Digitisers and ADCs

The digitisers presented in this work and general analogue-to-digital converters clearly have much in common. The digitisers presented here are essentially low resolution ADCs optimised for speed and for the processing of the types of signals found in radio astronomy.

It is useful to look briefly at the characteristics of general ADCs and in particular some of their performance metrics. Whilst these are generally not directly applicable to the digitisers, they provide the standard means of comparison amongst ADCs in the literature, and will be used later in this work to place upper bounds on error mechanisms.

A fundamental property of an ADC is the number of bits, B, of the digital representation it produces, and correspondingly, the number of quantisation levels, N. These are related by  $N = 2^{B}$ . Given the number of bits the most important property of the ADC is its signal-to-noise ratio (SNR). This is conventionally derived based upon a sine wave input. This derivation can be found in any standard text on ADCs or digital communications [3]. A simple derivation will be presented to highlight the assumptions that set ADCs apart from the digitisers in this work.

The input to the ADC is a full scale sine wave of amplitude V. Despite this, it is assumed that the input is uniformly distributed across all the quantisation levels. This is a reasonable approximation when the number of quantisation levels is large. Given this assumption, the quantisation error, that is the error between the true signal and the quantised signal, is uniformly distributed across each quantisation level. If the quantisation level is of width  $\delta$  and the sample value is considered to be the centre of the quantisation level then the quantisation error, e, is uniformly distributed between  $-\frac{\delta}{2}$  and  $\frac{\delta}{2}$  with a density of  $\frac{1}{\delta}$ . There is an implicit assumption that the quantisation error is uncorrelated with the input signal. Given these definitions the expected error power due to quantisation is

$$E(e^{2}) = \int_{-\frac{\delta}{2}}^{\frac{\delta}{2}} e^{2} \frac{1}{\delta} de.$$

(2.13)

Performing the integration and noting that  $\delta$  and B are related by

$$\delta = \frac{2V}{2^B},\tag{2.14}$$

and that the sine wave rms power is  $\frac{V^2}{2}$ , gives the well known relation for SNR in db

$$SNR_{adc} = 6.02B + 1.76 \ dB.$$

(2.15)

This relation gives the theoretical maximum SNR that can be achieved. This relation is often inverted when evaluating ADCs in practice so that a SNR, or signal-to-noise-plus-distortion ratio (SNDR) including harmonics, is measured from digitised data and from this an effective number of bits derived.

In the case of low resolution digitisers the assumptions implicit in the result of equation 2.15 are not valid. The received signal is normally distributed and the quantisation error is strongly correlated with the signal. In the case of two-level quantisation the signal and quantisation error are essentially the same. For three-level quantisers the signal and quantisation error are still strongly correlated. The methods of section 2.1.1 are then the appropriate formalism for analysing the performance of systems using such quantisers.

Likewise, SNDR measurements for low resolution digitisers are not meaningful. The conventional SFDR of a low resolution digitiser is poor. These systems, however, are not designed for processing discrete tones, but for processing signals with predominantly noise like character.

# Chapter 3

# InP Digitiser Designs

The goal of the digitiser research was to realise a range of two-bit threelevel digitisers that were capable of full Nyquist sampling at up to 8 gigasamples/s.

The digitisers were designed using an all-parallel "flash" architecture because this provides the highest sample rate of all ADC architectures [32]. In this architecture the input signal is sent to a set of comparators in parallel,  $2^n - 1$  for an n bit digitiser, with appropriate threshold settings for each of the comparators. For the three-level digitisers developed two comparators are required.

The process of digitisation involves two steps, sampling and quantisation. Sampling is taking a snapshot of a signal at a particular instant. Quantisation classifies a signal into one of a discrete set of states. These operations may be performed in either order. It is common with moderate to high precision ADCs to employ a sample-and-hold circuit before the quantiser so as to provide non-slewing samples in time. This is mandatory for ADC architectures that use feedback, such as successive approximation and folding/interpolating architectures, but is also often used with flash converters to overcome problems with input capacitance from the parallel bank of comparators, and limitations in being able to equalise the wire lengths and delays to each of the comparators. The digitisers designed in this chapter contain no sample-and-hold as they contain few comparators, and the process was not well suited for realising low distortion sample-and-holds on chip. Instead, clocked comparators with matched delays are used to perform both the sampling and quantisation. Implications of this decision are treated in section 3.3.3 on error mechanisms.

The digitiser ICs were designed using a combination of emitter coupled logic (ECL) and current mode logic (CML) transistor circuit topologies, as these are well known to provide the fastest operation in bipolar technologies, due to nonsaturating operation, along with good noise immunity and ability to operate fully differentially [33, 34, 35, 36]. ECL and CML are based upon stacked emitter-coupled pair differential amplifiers as their basic logic elements. See for example [37] for a thorough treatment of ECL and CML and their use in bipolar VLSI circuits.

## 3.1 Summary of Designs

Three digitiser integrated circuits were designed and implemented:

1) A digitiser/demultiplexer. This is a two-bit/three-level flash converter with dual post converter 1-4 serial/parallel converters to reduce the output data rate to  $\simeq 2$  Gbits/s. The demultiplexed data is then at a sample rate where commercially available ECL logic can be used for processing the signals. Without the integrated demultiplexers external demultiplexer chips would have to be designed. Although fast demultiplexers for the OC-192 optical data transmission standard (10Gb/s) are available [38], these are single bit demultiplexers where there is a synchronisation problem in getting the phase of the 1/n dividers of multiple demultiplexers aligned. This can be overcome, but at higher complexity and cost than an integrated demultiplexer. See [39] for one particular solution.

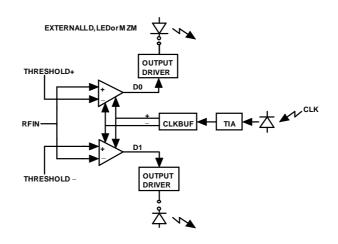

2) A digitiser without integrated demultiplexer. This design was included chiefly as a back up option in case the yield of the process was low, in which case the previous design, with six times as many transistors as the digitiser without demultiplexer, may not have yielded any working circuits. 3) A photonic I/O digitiser. This is a novel two-bit/three-level digitiser with the sampling clock delivered by fibre and received by an on-chip photodiode and transimpedance amplifier. The design also has current-switching output buffers which can be used to directly modulate an externally bonded LED, laser diode or optical intensity modulator. This allows a purely optically connected digitiser for remote antenna applications with low selfgenerated radio frequency interference (RFI).

## 3.2 Fundamental Design Parameters

I will now discuss some of the fundamental optimisations and design decisions that effect all of the circuits to follow, such as device sizing, device currents, choice of supply voltage, internal signal swings and limitations on the input signal voltage.

### 3.2.1 Device Sizing

Transistors are available in the InP HBT process in a variety of emitter widths and lengths. Fastest device operation is achieved with the narrowest base width, as this minimises the base transit time. The process used offers a minimum base width of 1.5 um, so devices of 1.5 um base width were used in all designs. A large selection of emitter lengths was available as well as devices with multiple emitters. The majority of transistors in the digitisers were minimum size single emitter transistors, with this decision made largely on the basis of power dissipation. The speed of the transistors is governed by the collector current density - A transistor of twice the emitter length requires twice the collector current to maintain the same emitter current density, and hence maintain the speed. This leads to twice the total power dissipation of the device. For integrated circuits with many hundreds to thousands of transistors it is imperative to reduce the device dissipation [40]. Larger devices are used as appropriate, for example, in the clock driver circuits and output driver circuits which must drive high load currents at high bandwidth. The choice of device for each of these sub-circuits is dealt with in more detail in the relevant section.

### 3.2.2 Signal Swing

One important question is what internal voltage swings should be used in the circuits. The larger the voltage swing the longer the internal nodes take to reach valid logic levels, and the longer it takes internal nodes to slew from one full scale state to the other. The power dissipated in internal capacitive parasitics is also higher. It is clear that the internal voltage swings should be as low as possible consistent with reliable operation. An emitter-coupled pair differential amplifier has a differential output voltage as a function of differential input voltage given by [41]

$$V_{out} = I_{EE} R_C tanh(\frac{V_{in}}{2 V_T})$$

(3.1)

where  $I_{EE}$  is the tail current,  $R_C$  the collector load resistance and  $V_T$  is the thermal voltage. The output will almost fully switch from  $I_{EE} R_C$  to  $-I_{EE} R_C$  with an input differential voltage swing of only 3 or 4  $V_T$ . At room temperature this implies a peak to peak input signal swing of 100 mV is required. Considering the circuit may have to operate at up to 150 C, and the thermal voltage increases accordingly, this becomes 140 mV. The parasitic emitter resistance of the minimum size HBTs leads to an additional loss of about 50 mV at the design current density. Thus, an input signal swing of 190 mV worst case over temperature is indicated. Allowing for process variations, offsets and imbalances by a 20% margin, a nominal signal swing of 230mV was chosen for the internal circuit nodes.

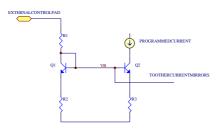

#### 3.2.3 Bias Current

The speed of operation of InP single heterojunction bipolar transistors, in terms of  $f_t$  and  $f_{max}$ , increases with collector current until the device enters the region of unsafe power dissipation. This is in contrast with conventional BJTs, which reach a definite peak before they reach their maximum dissipation level, because of effective base widening as a result of the Kirk, or base push out, effect [41]. Thus, for maximum speed we must ideally bias the transistors at the highest current that is consistent with safe operation of the device and total power dissipation constraints of the chip. The minimum size transistors have a maximum emitter current of approximately 2.0 mA. A safe current which allows for process variations and increase of current source output with temperature is 1.6 mA. As will be mentioned in section 3.3.8, all the digitiser ICs have an external pad that allows the bias current for all transistors to be varied above or below this nominal value by application of an external voltage.

### 3.2.4 Supply Voltage

In order to reduce power dissipation in the circuit, it is clear that the supply voltage should be kept as low as possible. The minimum supply for a two stacked transistor configuration (the other sub-circuits on the chip are also at most two level stacked), which prevents the current source going into saturation, is

$$V_{ee}(min) = 3V_{be} + V_{ce} + V_{rcs}, (3.2)$$

where  $V_{be}$  is the base emitter voltage,  $V_{ce}$  is the transistor saturation voltage and  $V_{rcs}$  is the voltage drop across the current source resistor. Taking typical values of  $V_{be} = 0.8V$ ,  $V_{ce} = 0.3V$  and  $V_{rcs} = 0.3V$ , this gives a minimum supply voltage of 3.0V. A reasonable choice for supply voltage which allows for process variations, and provides greater input common mode range, is 3.5V. This is referred to as VEE in the circuit schematics to follow. The upper rail voltage, referred to as VCC in the circuit schematics, was chosen to be ground. This was done for a few reasons. Firstly, the process uses a backside ground plane with low inductance vias to provide solid ground connections. Using this for one of the voltage rails allows simple connection to the rail using backside vias, without having to route another power rail to all the devices on the chip. This is very useful considering the process offers two metal layers for all signal and power connections. Secondly, with the differential amplifier based logic used in the design, noise coupled through the negative rail is rejected by the differential amplifier, whilst noise coming through the upper rail adds directly to the output voltage. It is much easier to keep ground clean, so it is prudent to use this as the upper voltage rail. This is the reason that commercial ECL logic conventionally uses an upper rail voltage of ground [42]. Thirdly, this choice makes the outputs of the IC directly compatible with commercial ECL logic which is used for further processing of the digitised data.

### 3.2.5 Input Common Mode Range

The input common mode range, for the comparator cell to be presented in 3.3.1, is limited in the positive direction by ground, assuming the positive rail is at ground potential, and in the negative direction by preventing current source saturation, so that

$$V_{ee} + (2V_{be} + V_{ce} + V_{rcs}) \le V_{in} \le 0.$$

(3.3)

Using the transistor parameters in the previous section, and a supply voltage of -3.5 V, this gives a common mode range of 1.3 V extending from 0 to -1.3 V. For an input biased about -0.65 V this sets the maximum input level for a sine wave source as 1.3 V peak-to-peak or +6 dBm, or for a Gaussian distributed source, taking an effective crest factor of 5, of 0.13 V rms or -4 dBm.

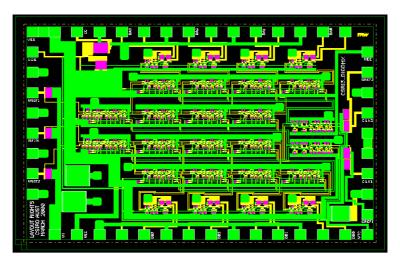

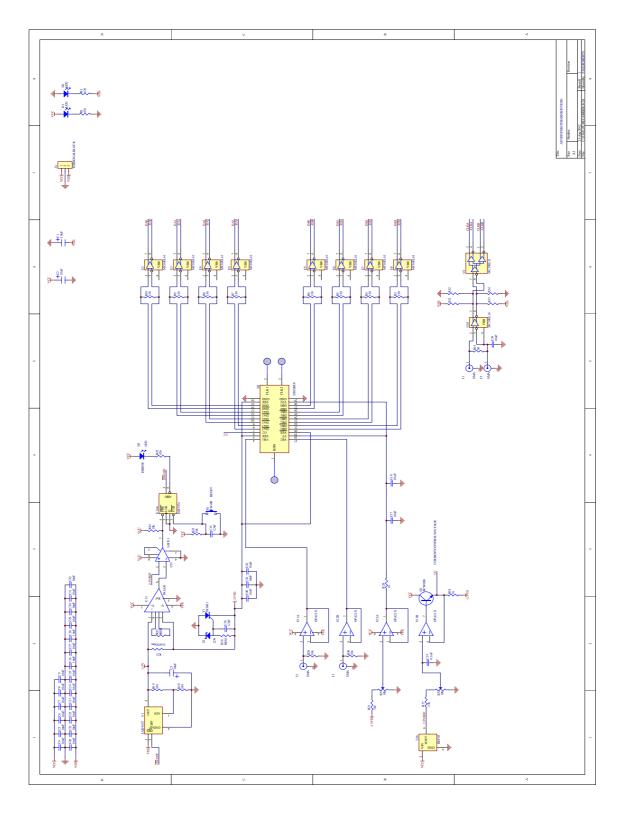

## 3.3 Digitiser/Demultiplexer

Having presented the common fundamental design decisions in the previous section, I will now move on to the detailed design and analysis of each of the digitisers that were produced. For each of the designs I will present a top level functional description of the circuit, followed by in-depth design and analysis of the sub-circuits from which the designs are composed. Some of the sub-circuits are reused in multiple designs. For instance, the same optimised comparator block is used in all the circuits, so the analysis of these common blocks will be presented in the first circuit in which they were used.

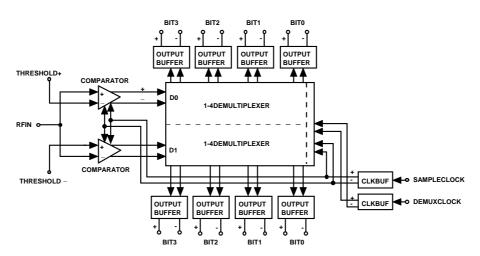

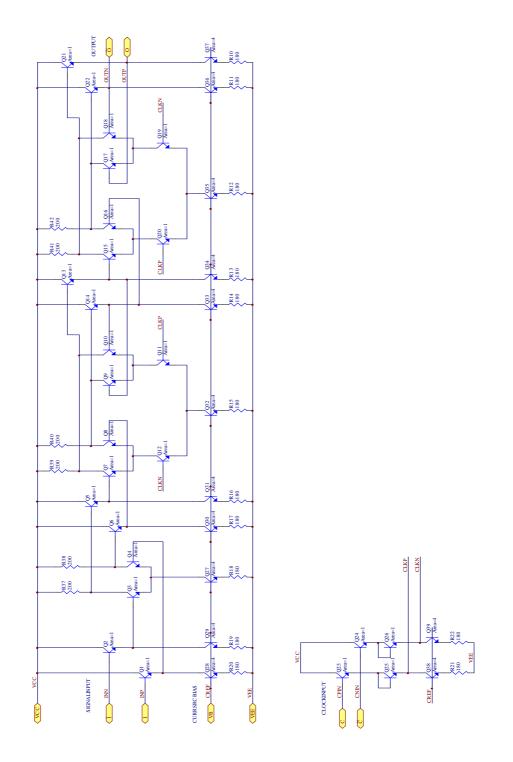

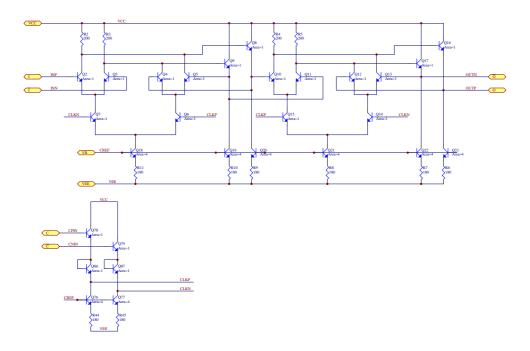

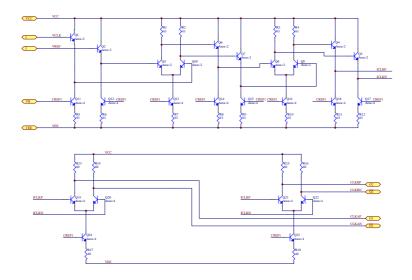

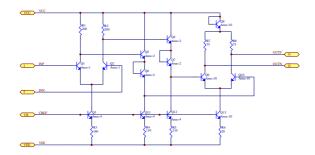

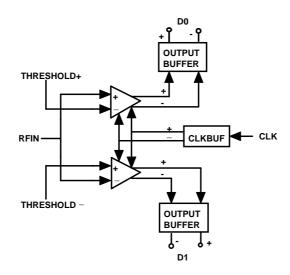

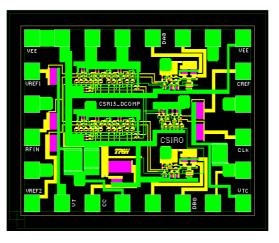

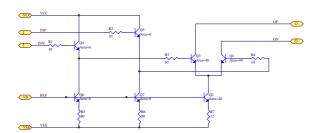

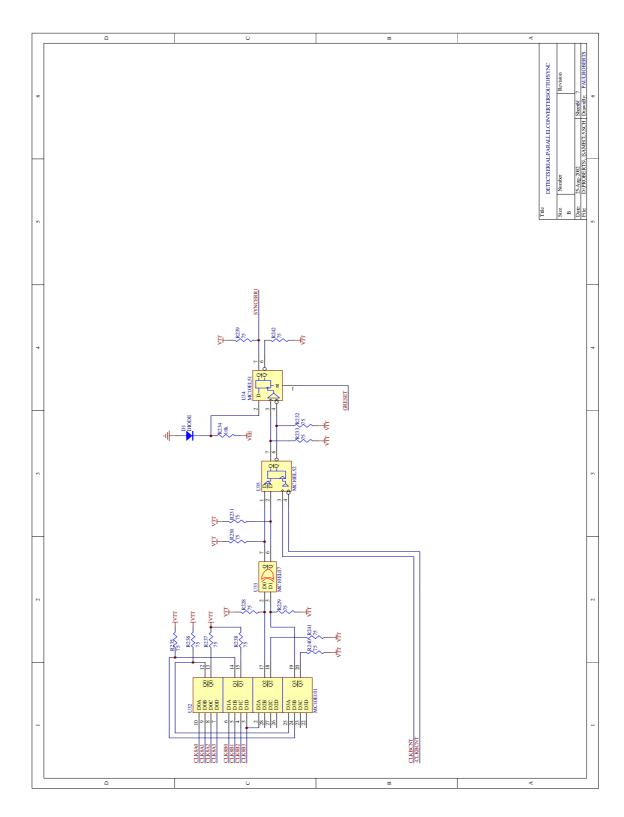

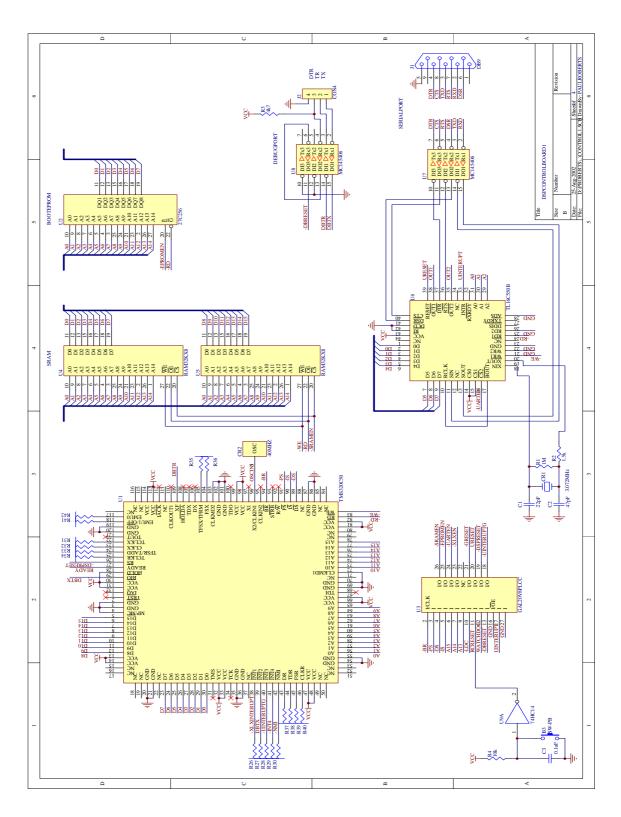

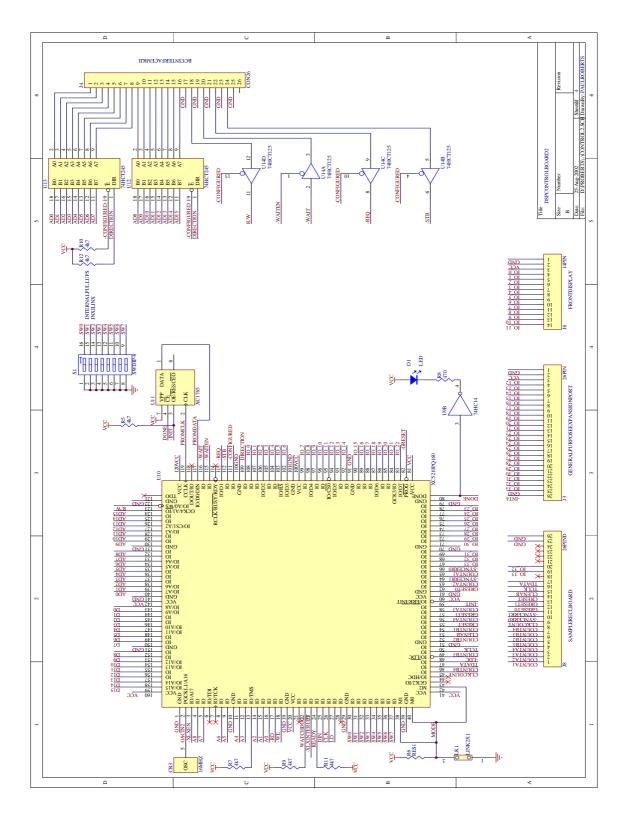

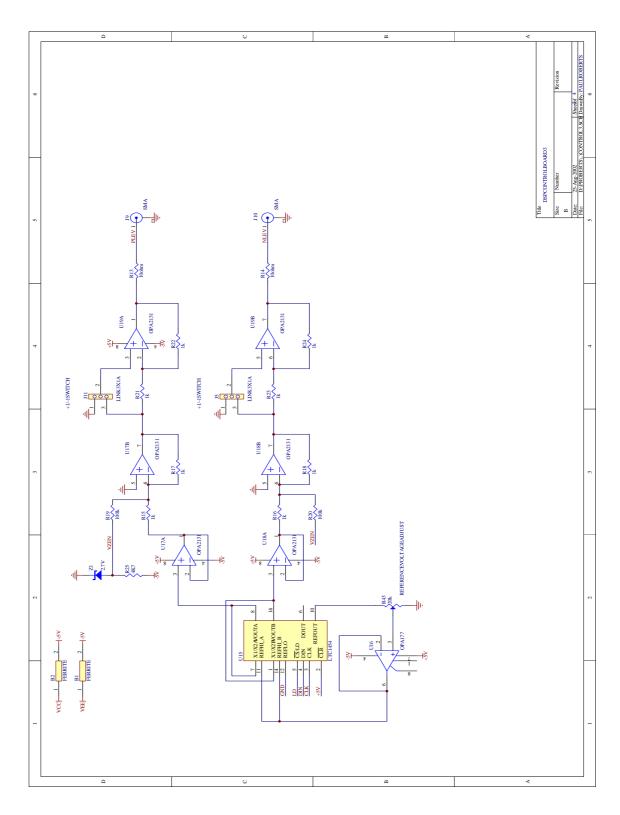

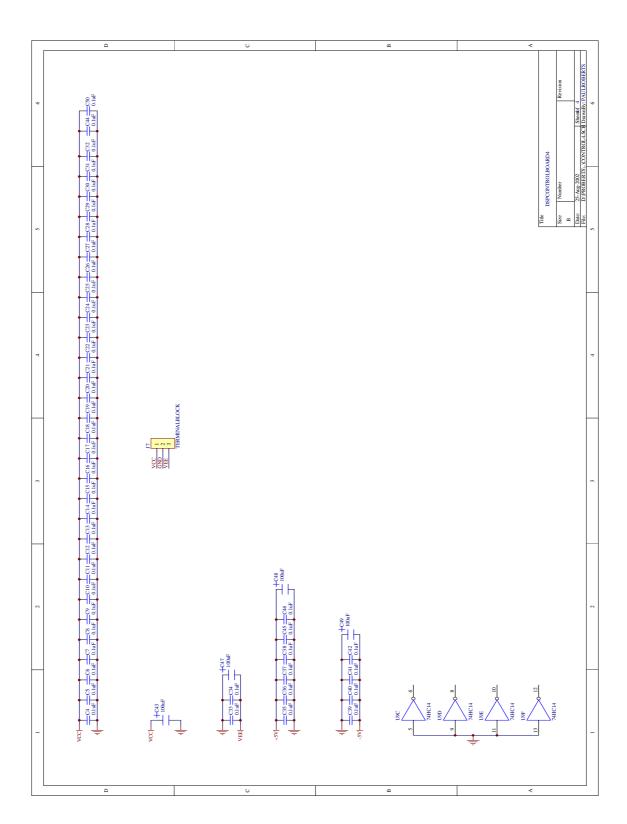

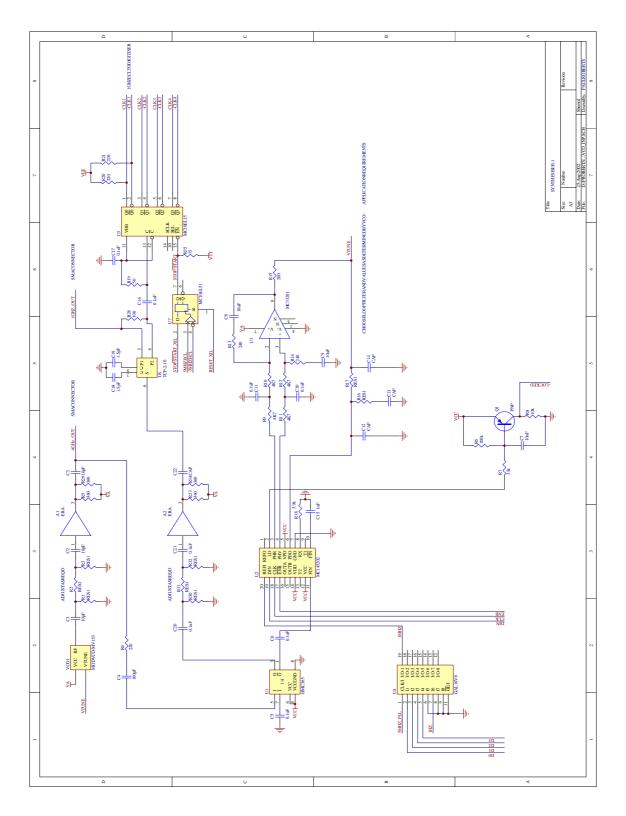

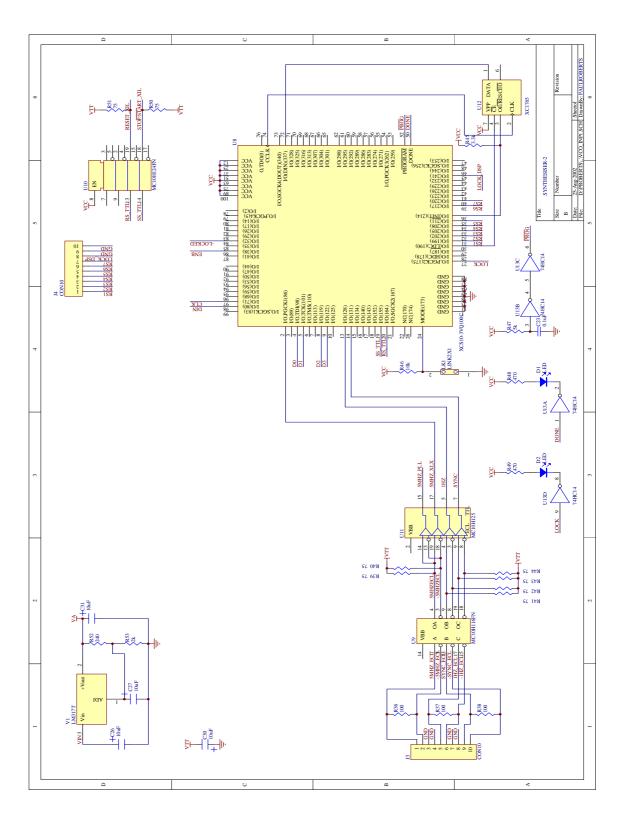

The high-level block diagram of the digitiser/demultiplexer is presented in figure 3.1. The digitiser/demultiplexer is composed of comparators, de-

Figure 3.1: Digitiser/Demultiplexer block diagram.

multiplexers, a clock buffer, output buffers and a current control block. This design, as with all the designs, was designed and laid out using the Libra Series IV microwave design package from Agilent EESOF. All connections were hand routed. The design was hierarchical, reflecting that of the block diagram, so that common cells were laid out once only and repeated where necessary and the required interconnections put in place. The layout and simulation is an iterative process as the simulation requires knowledge of the layout for correct simulation of the interconnects and parasitics. The process is then iterated, with the simulations refined in light of the current layout, until they converge.

### 3.3.1 Comparator

The basic element on which a flash converter is based is the voltage comparator. This is the device which performs the comparison between the input signal and a supplied threshold level, and outputs one of two digital states, "1" or "0", depending on whether the input signal is greater than threshold or otherwise. The performance of its constituent comparators is what ultimately sets the performance level of the overall digitiser, so this block is in many ways the most critical block in the digitisers, and the block which requires the most detailed analysis.

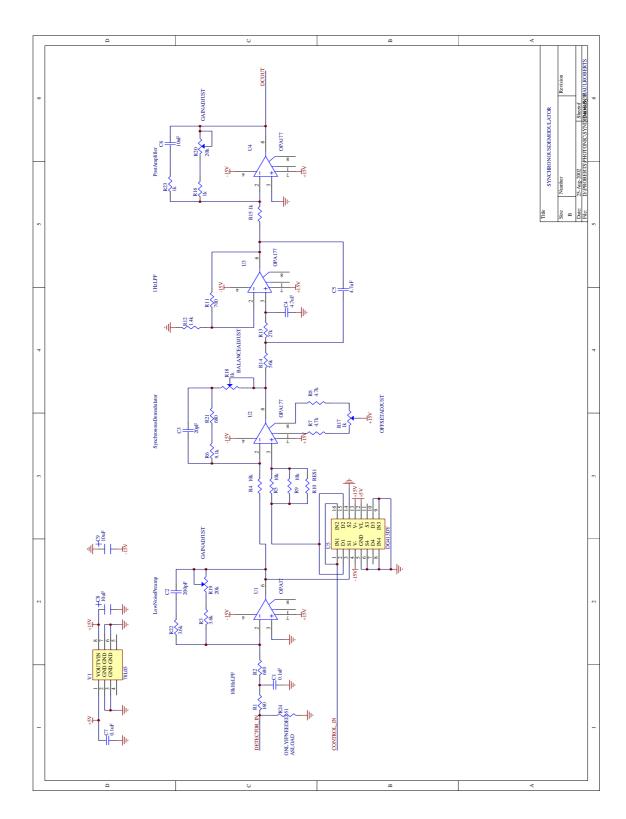

The circuit of the clocked comparator that was designed is illustrated in figure 3.2. This is based upon comparator designs presented in [43, 44, 45]. The input transistors Q1, Q2 serve to buffer the input signals and provide a relatively constant input bias current. They also prevent the following differential preamplifier Q3, Q4 from going into saturation, as the bases of Q3, Q4 are always at least a diode drop below the upper rail, ground in this case. The first preamplifier composed of Q3, Q4 serves to increase the front end gain, so enhancing the comparators response and recovery times and reducing metastability as the threshold region is traversed quicker. It also reduces clock kickback propagated to the inputs when the CLK switches. Q7-Q14 form a second preamplifier and regenerative latch. When CLKP is high and CLKN is low the preamplifier is enabled and the output tracks and amplifies the voltage difference at the input, acting as a high gain amplifier. Note that the amplifier does not have to be linear. The comparator is simply a polarity sampling device and the overriding concern is speed. This means that fast open loop configurations as in the schematic are called for.

Figure 3.2: Schematic of comparator.

As the clock is switched the latch composed of Q9,Q10,Q13,Q14 is enabled and the positive feedback serves to amplify the voltage difference present at the collectors of Q7,Q8 at the moment of switching, and hold this level until the CLK is asserted again. The output emitter followers serve to enhance the regeneration rate of the latch slightly, provide a low impedance current drive for the following stages and level shift the signal to be compatible with the differential amplifier inputs of the following stage. Q15-Q22 form a second slave latch which operates in anti-phase to the first latch. This slave latch increases the regeneration time available, leading to less probability of metastable states, and also ensures the final output of the comparator is stable for a full clock cycle, instead of tracking for half the clock period. This is the usual master-slave flip-flop arrangement and gives the following logic twice the setup time for more reliable operation. Also included on the schematic is a local level shifting cell which shifts the level of the external clock inputs down two diode drops to put them at the correct DC level for the CLKP and CLKN inputs. The reason for including the level shifting cell in each comparator will be explained in section 3.3.6.

### 3.3.2 Comparator Dynamic Performance

The key performance parameter of a comparator is the ultimate comparison rate that can be achieved. This is the fastest rate at which the comparator can be clocked and correctly respond to the polarity of the signal at its input. There are several aspects that have to be considered:

The first is the recovery rate of the comparator. This is the rate at which the comparator's preamplifiers can slew from one state to a point in the other state where the logic level will be correctly interpreted. This is dependent on the gain of the preamplifiers, their bandwidth, the size of the full scale swing, the load resistance, and parasitic resistances and capacitances. The comparator cannot be strobed at a period less than it takes the comparator to slew unambiguously between states. The second is the regeneration time constant of the latch. When the latch is strobed the differential voltage difference at its inputs is regenerated by positive feedback to full logic levels. The comparator cannot be strobed at a period smaller than required for valid logic levels to be attained. The regeneration time is dependent upon the same parameters as for the recovery rate, and also upon the differential voltage difference at the latch inputs at the time of strobing. An important implication of this is that for any given clocking rate, there will always be a minimum differential voltage that is needed to fully switch the output state of the clocked comparator.

#### **Recovery Rate**

To examine the recovery rate of the comparator consider the differential pair preamplifier composed of Q1-Q4. If we were to do a small signal analysis of this circuit we would find that, using a single pole approximation, the frequency response would roll off with a 3dB point  $\omega_{\tau}$ , or alternatively the circuit has a characteristic time constant  $\tau_0 = 1/2\pi\omega_{\tau}$ . Then the small signal response can be approximated as

$$\frac{V_{out}}{V_{in}} = \frac{-g_m R_L}{1 + j\omega_\tau}.$$

(3.4)

Here  $-g_m R_L$  is the usual low frequency gain involving the transconductance  $g_m$ , and the load resistance  $R_L$ . The time constant of the circuit is dependent on the collector current  $I_C$ , intrinsic forward base transit time, various junction capacitances and resistances, the load resistance and the parasitic load capacitances. In general, it is therefore a very complicated expression, though in various regimes it can be simplified. For instance, if the load capacitance is high the circuit response is dependent only on the load. In the case at hand though, this is not true, and the best way to proceed is through simulation.

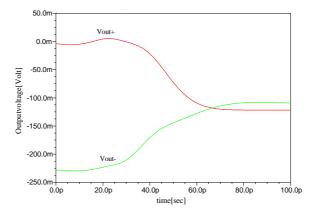

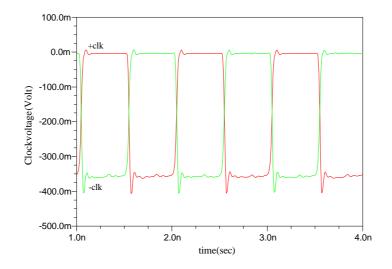

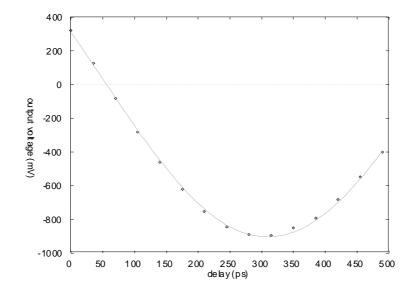

To estimate the performance of the comparator in a worst case situation, the comparator can be analysed in the condition where the input is at full scale in one direction,  $V_{fs}$ , and subsequently has to respond to a small instantaneous differential input,  $V_d$ , in the other direction. This is known as an overdrive recovery test [46]. The circuit response using the small signal response of equation 3.4 will be an exponential slew to the opposite polarity. This is very approximate, as  $g_m$  and  $\tau_0$  depend on the collector current and bias voltages, which are constantly varying. The  $g_m$ , for instance, can vary anywhere between  $I_c/V_T$  and almost zero in each transistor, depending upon the input signal. In addition, the response to a pulse cannot be regarded as small signal. The full comparator circuit of figure 3.2 has two stages of preamplification, so that the overall DC gain is squared, and the time constant doubled, compared to a single preamplifier. Using the nominal SPICE models provided, and examining the response to the situation described above where the input differential slews from full scale positive to a small negative value, gives the typical response illustrated in figure 3.3. Defining the recovery time by the time from application of the small voltage difference (0 ps in figure 3.3) until the output responses cross, indicating a change of polarity, gives an indication of the performance of the comparator in this worst case condition. For a full-scale Gaussian-distributed input, full scale

Figure 3.3: Typical comparator overdrive response.

is approximately four times the standard deviation. For a rms input level of 130 mV, determined earlier, this implies a full scale of 520mV. This is taken as full scale for the simulation. The voltage to which the comparator input is

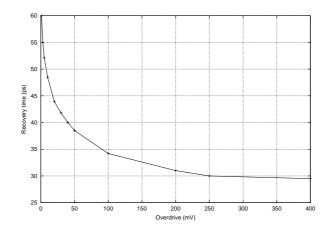

subsequently driven is known as the overdrive. As the overdrive is increased, the recovery time decreases, since in the small differential input range the preamplifiers are simply acting as linear amplifiers, and so the slew rate is proportional to the input voltage difference. Figure 3.4 gives the results of simulating the comparator recovery time as a function of overdrive, given the initial condition that the comparator is currently in opposite polarity full scale. This is a very demanding test and can be regarded as a worst case operation of the device. It can be seen that even for a very small overdrive of only 1 mV, figure 3.4 implies an ability to operate at a rate greater than 16 giga-samples/s. For applications where the overdrive is large, for example re-timing optically transmitted data in a decision circuit, figure 3.4 implies an ability to operate at greater than 33 giga-samples/s.

Figure 3.4: Comparator recovery time.

#### **Regeneration** Time

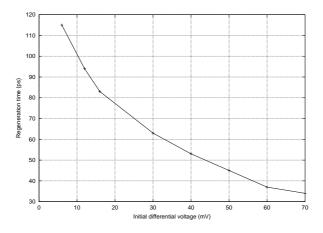

The output differential voltage produced by the preamplifier circuit dealt with in the previous section has to be latched and regenerated to valid logic levels by the latch portion of the comparator. Quite often, the differential input to the latch will be very small at the moment of strobing, if the overdrive at that instant is small. The time required for a small input to be regenerated by positive feedback to valid logic levels is, thus, another constraint on the maximum operation speed of the comparator.

The point to which the levels need to regenerate to be correctly determined is not clear. As mentioned previously, a differential amplifier will almost fully switch with a  $3V_t$  input voltage differential. So considering the amplification that will follow the latch when the signal enters the next latch or logic element, an output level of  $3V_t$  will almost certainly give correct operation. Taking this as the criterion, the regeneration time of the latch as a function of the input differential present at the instant of strobing can be derived from simulation. The results are presented in figure 3.5.

Figure 3.5: Comparator regeneration time.

This graph indicates that to operate at say 10 giga-samples/s (corresponding to 100 ps regeneration time), then at least 10 mV differential input voltage is required at the instant of switching. It is impossible to avoid falling in the uncertainty region some of the time, since there is always a finite probability of the input differential voltage lying in the uncertainty region. Hence the performance achievable is dependent upon the error rate that can be tolerated. Considering the case of a 10GHz clock rate again we can make an estimate of the error rate. If for the time being the slew rate limitation of the input preamplifiers is neglected, and they are considered to be working in their linear region when the difference between the threshold value and the input is small, then they have a gain of  $(g_m R_L)^2 = 80$ . Thus, to have an input differential voltage of 10mV at the input to the latch requires an input differential voltage of  $10/80 = 0.125 \ mV$  at the input to the comparator. The input signal is normally distributed with a variance,  $\sigma$ , of 130 mV at full scale input, as derived earlier. In normal operation, the threshold levels are held at 0.612  $\sigma$  (section 2.1), so that the probability density at this point is given by the normal distribution probability distribution function (PDF),

$$Z(x) = \frac{1}{\sqrt{2\pi\sigma}} e^{-\frac{x^2}{2\sigma^2}},$$

(3.5)

evaluated at  $x = 0.612 \sigma$ . From this, the probability that the signal lies in the uncertainty region is approximately 2.6 x 10-4. For a sample rate of 20 GS/s the probability of error increases to 9.5 x 10-4.

The above figures are pessimistic. Even if the output voltage differential does not reach  $3V_T$ , the gain in the preamplifier and regeneration in the latch of the following logic stage will aid in achieving correct operation. This is the function of the slave latch in figure 3.2 - it amplifies the regenerated voltage in the master latch and effectively doubles, to a first approximation, the regeneration time available, thus greatly reducing the probability of metastable states. It also has the property that the output from the slave latch is in hold for almost a full clock cycle, instead of tracking for half the clock cycle, giving the following logic twice the setup time.

To get some estimate of the improvement in error rate provided by the slave latch, consider an ideal latch. An ideal latch composed of two amplifiers in positive feedback has output voltage, as a function of time, expressed by [46, 47]

$$V_{out} = V_{in} e^{\frac{A-1}{\tau}t},\tag{3.6}$$

where A and  $\tau$  are the gain and characteristic time constant of the amplifier and  $V_{in}$  the applied input voltage. Fixing the output voltage at  $V_0$  and expressing t as a function of  $V_{in}$  gives

$$t = \frac{\tau}{A-1} ln(\frac{V_0}{V_{in}}). \tag{3.7}$$

This is the ideal relationship for the simulation data displayed in figure 3.5. In reality, the gain and time constant are constantly changing as the collector current and junction voltages vary in the real latch. Fitting the data of figure 3.5 to this relationship, and extrapolating to 2t, gives the  $V_{in}$  that is acceptable if twice the regeneration time is available. From this the probability of error can now be estimated at  $\approx 1x10^{-7}$  at a 10 giga-samples/s rate, or  $\approx 1.9x10^{-4}$  at a 20 giga-samples/s rate. Notice that the error rate for 20 giga-samples/s operation has decreased much less than the error rate for 10 giga-samples/s operation, as the slope of the curve in figure 3.5 is much less at this point. The error rate at 10 giga-samples/s operation is sufficiently low for the current application.

### **3.3.3** Comparator Error Sources

The previous section investigated the maximum performance level that can be achieved with the devices. In a sense, it represents the upper limit as determined by the speed of the transistors available and the associated device and interconnect parasitics. In practice, other error mechanisms are present which serve to degrade the performance of the comparators. These error mechanisms include: jitter; thermal noise; slew rate dependent sampling point; clock kickback; input signal dependent delay and capacitive junction feed-through. Thermal noise and jitter are fundamental properties of any sampling system. The remaining error mechanisms arise from the choice of comparators as both the sampling and quantising element. The following section will deal with these error mechanisms and their impact upon the digitisers.

#### Jitter

Jitter on the sampling clock is one of the most important error sources in digitisers [48, 49]. Jitter of the clock source leads to variation of the sampling point and hence error in the sampled voltage. To analyse this effect consider an input sinusoidal source  $V(t) = Asin(2\pi ft)$ . The voltage error  $\Delta V$ , introduced by a sampling time error  $\Delta t$ , is to first order

$$\Delta V = \frac{dV(t)}{dt} \Delta t. \tag{3.8}$$

If the probability distribution function (PDF) of the timing jitter, that is the variation about the true sampling point, is modelled as a Gaussian distribution of zero mean and variance  $\sigma^2$ , then the rms error voltage over the period of the sine wave input, T, is [48]

$$V_{\sigma} = \sqrt{\frac{1}{T} \int_{0}^{T} \left(\frac{dV(t)}{dt}\right)^{2} dt} \ \sigma = \sqrt{2\pi} A f \sigma.$$

(3.9)

The signal power is given by  $A^2/2$  so that the signal-to-noise ratio, due to timing jitter, is

$$SNR_{jitter} = -20\log(2\pi f\sigma) \quad dB. \tag{3.10}$$

If this result is equated with the general expression of equation 2.15 for the signal-to-noise ratio of a general B bit ADC, and the resulting equality solved for B, an effective number of bits limit due to timing jitter can be derived as

$$B_{jitter} = -3.3 \log(2\pi f\sigma) - 0.29 \quad bits.$$

(3.11)

In the ADC survey in [50] it is empirically found that all published ADCs lie above a minimum jitter value of approximately 0.5 ps. Assuming that a similar value of jitter can be achieved with the present designs, and at the highest analogue input frequency of 4 GHz, the effective number of bits is approximately 6 (i.e. 64 levels). As this is well above the three-level quantising used in the digitisers, jitter is not a limiting error source.

As well as random timing jitter in the sampling signal, constant offsets between the sampling instant at different comparators lead to distortion and loss of signal-to-noise ratio [51]. This timing skew must be reduced to a similar level as for random jitter and highlights the need to ensure that clock lines to each comparator are well balanced in length and loading.

#### Thermal noise

Thermal noise generated at the input, and internal circuit impedances, provides background noise that is indistinguishable from real input signal. Clearly, as this approaches half of a LSB in value, significant degradation of the output signal-to-noise ratio will be experienced. If all thermal noise sources are referred back to the input, they can be represented by an equivalent input noise resistance at room temperature. In the ADC survey cited in the previous section [50], it has been empirically found that state of the art ADCs lie above a noise resistance value,  $R_{th}$ , of approximately 2000 ohm. This reference also derives an effective number of bits due to thermal noise limitations given by

$$B_{th} = \log_2 \sqrt{\left(\frac{V_{fs}^2}{6kTR_{th}f_s}\right)} - 1 \quad bits, \tag{3.12}$$

where k is Boltzmann's constant, T the absolute temperature,  $f_s$  the sampling rate and  $V_{fs}$  the full scale input voltage. At the maximum intended sampling rate of 8 giga-samples/s the effective number of bits is approximately 9.6. Thermal noise is not a significant error source for the digitisers.

#### Input Slew Rate Dependent Sampling Point

This effect arises when high slew rate input signals are latched by finite rise time clock signals. As the latching signal is applied, and the latch passes from track to hold, then it is possible that a high slew rate signal, which is about to pass through the threshold level of the comparator, may pass through the threshold during the switching period and cause the latched value to be the opposite of what it was at the initial application of the latch signal. A slow slew rate signal on the other hand would be latched to give the same polarity as at the application of the latch signal. This is equivalent to a variation of the sampling point dependent upon the input slew rate. This effect has been treated in [43], where it is shown that this leads to third harmonic distortion. This effect can be minimised by insuring the rise time of the clock signals on chip is significantly faster than the maximum input slew rate. In section 3.3.6 dealing with the clock buffers, it will be seen that the clock buffers were designed for high bandwidth to minimise the clock waveform rise time. The simulated rise time was approximately 25 ps. The large quantisation steps of the digitiser also help to make the design insensitive to this effect, as the amplitude error introduced by an effective sample time variation is small compared to the quantisation step.

#### Clock Kickback

During the latch-to-track transition of the latch composed of Q7-Q14 in figure 3.2, transistors Q7 and Q8 are initially off. As Q12 turns on, and current begins to flow, the base emitter junction capacitances of Q7 and Q8 initially provide a low impedance to the fast clock transient. This allows the clock transient to propagate through the junction capacitances back to the input of the latch. This phenomenon is known as kickback noise. One of the benefits of the preamplifier before the latch is that it reduces the level of kickback noise propagated back to the input [52]. In addition, the fully differential architecture ensures that the impedance of both the positive and negative latch inputs is the same, so the differential error voltage induced by the current transient, which occurs in both inputs, is small. The low impedance of the internal collector nodes of 200 ohm, and the comparator input impedance of 50 ohm, ensures the magnitude of induced voltage is also small. The level of kickback noise was verified through simulation. The kickback noise spike induced at the emitters of Q5 and Q6 is equal to within 4 mV, and the transient completely decays within 150 ps, which shows kickback noise is not a problem at the target sampling rate, and with the large quantisation levels used.

#### Input Signal Dependent Delay

As the input signal level changes the junction capacitances of the input emitter follower change. Of most importance is the base-collector capacitance, which varies non-linearly with base-collector voltage according to the usual relation for depletion capacitance of reversed biased p-n junctions, namely

$$C_{bc} = \frac{C_0}{\left(1 + \frac{V_{bc}}{\phi}\right)^{m_j}},$$

(3.13)

where  $C_0$  is the zero bias capacitance,  $V_{bc}$  is the voltage across the junction,  $\phi$ is the base-collector built-in potential and  $m_j$  is the junction ideality factor, which is usually in the range 0.3-0.6. As this capacitance changes, the delay introduced by the emitter follower changes. This is equivalent to a variation of the effective sample point, leading to an amplitude error in the sampled signal proportional to the capacitance and the slew rate of the input signal. This mechanism is analysed in [53], where it is shown that this effect leads to harmonic distortion terms and becomes a problem when the amplitude errors approach half of a LSB. The relative amplitude of the second order distortion term is estimated as

$$HD_2 = \frac{V_0 \,\omega \, C_{j1} \,R}{2 \,\sqrt{1 + (2 \,\omega \, C_{j0} \,R)^2}}.$$

(3.14)

Here  $V_0$  is the magnitude of the fundamental,  $\omega$  the frequency,  $C_{j1}$  the linear term in a polynomial expansion of equation 3.13,  $C_{j0}$  the constant term in the same expansion and R the source resistance. For the InP process, exact data on the junction capacitances and junction properties is not available. However, the collector-base capacitance is very small, of the order of tens of femto-farads, for similar high speed transistors from other published sources [54]. Taking an upper limit of 50 fF for the capacitance, a typical built in potential of 0.5 V for InP devices, and an ideality factor of 0.5, then equation 3.14 indicates the second harmonic distortion is over 40 dB below the fundamental at the highest anticipated input frequency of 4 GHz for the current design. For high resolution flash A/D converters the many comparators in parallel lead to a high total input junction capacitance and the size of the LSB is also small, so this effect can be then problematic. In the InP digitisers designed here, the small number of comparators and low junction capacitance, combined with the large quantisation levels, means this effect is insignificant.

#### Capacitive Junction Feed-through

At high analogue input frequencies, a portion of the input signal at INP is able to couple through the base-emitter junction capacitances of Q24-Q27 and feed back to the inverting input, INN [45]. This causes distortion of the analogue input signal. It is possible to short out this feed-through by including a small capacitor of a few pF on the inverting input of each comparator, but in the present device it was preferred not to do this, as the digitiser was designed to be also usable as a dual 1-4 data demultiplexer. This is achieved by fixing what would normally be the analogue input at the centre of the input common mode range, and AC coupling the two data bits to the two inverting inputs. Placing an AC short on the inverting inputs would prevent the devices being reused in this way.

In order to verify that the level of feed-through was tolerable at the intended input frequencies, a simulation was performed to measure this effect. Up to the intended maximum input frequency of 4 GHz, the proportion of signal power coupled to the inverting input is less than -30 dB, which is acceptable for the present design.

### **3.3.4** Comparator Performance and Errors Summary

The previous performance and error analyses show that the digitisers should be able to achieve the target goal of Nyquist sampling to 8 giga-samples/s rate. The error analyses also show that the choice of using comparators for both the sampling and quantising elements in the digitiser designs, instead of incorporating an additional sample and hold, does not lead to any appreciable loss of performance for these designs.

## 3.3.5 Output Demultiplexer

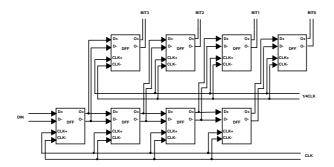

After the input analogue signal is digitised, the digital output data undergoes a 1-4 serial to parallel conversion, and the data is sent from the chip four samples at a time, at a quarter of the input sample rate. This was done to ease the burden on the following electronics that must further process the digitised data. If the data were output from the chip at the sample rate, up to 8 giga-samples/s, it would be very difficult to deal with the data at this speed. The fastest conventional commercial logic works to speeds of approximately 2 GHz [55]. Devices are available which can operate at the full data rate but are expensive and space consuming and would require very tight skew and timing control. It makes sense to include this first stage of demultiplexing on chip, where the timing and skew can be well controlled, and which will then allow cheap commercial ECL logic to be used from the chip outputs downstream.

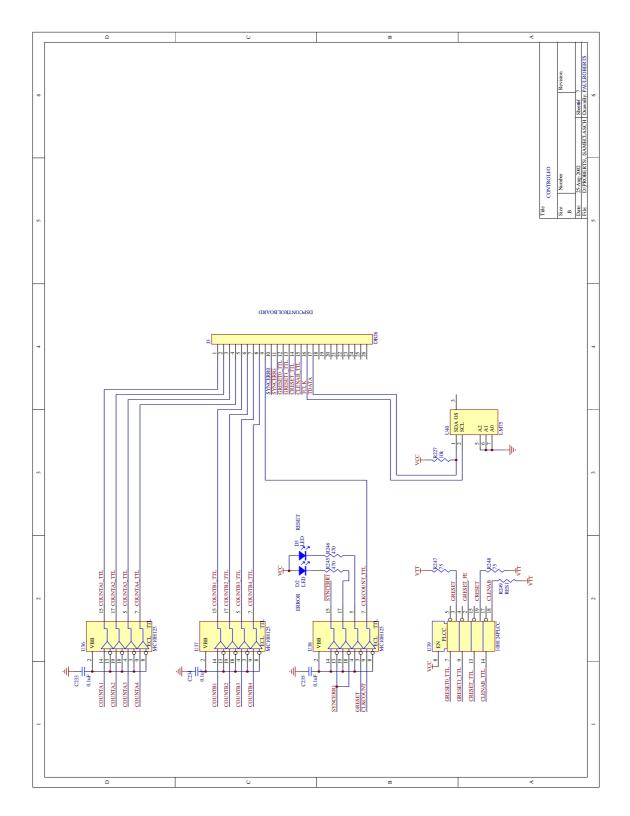

The demultiplexer is based on a shift register with output data register as shown in figure 3.6. The four bit shift register fills with four successive bits and then the output register, which operates at one quarter of the sample rate, captures the four bits and presents them to the output buffers. The

Figure 3.6: 1-4 demultiplexer block diagram.

demultiplexing clock is driven from a second clock input for maximum flexibility and ease of synchronising the demultiplexed data across several units. In general, it would be at one quarter of the input clock rate, and is phase locked to the sample clock. It can optionally be driven at different integer fractions of the sample rate for testing or undersampling applications. Using the two separate clocks makes the task of synchronising the data from multiple units much easier. In general, multiple digitiser units will be separated by large indeterminate physical distances, in terms of the wavelength of the sampling clock. If the demultiplexing clock were derived internal to the chip with a 1/n divider, there exists a phase ambiguity in the relative position of the demultiplexing clock in the multiple digitiser units. For example, with a 1/4 divider there are 4 separate phase slots in which the demultiplexing clock can reside. To synchronise multiple units a reset input to the divide-byn is needed. All the digitiser inputs must receive this reset within the same sampling clock period and with sufficient setup time to be recognised by the rising clock edge. With an 8 GHz sampling clock, this implies that the reset signal must reach all reset inputs within 125 ps of each other, a very difficult system challenge. Even then, the phase of the demultiplexed data must be measured to ensure that the reset operation has proceeded correctly, which adds to the system complexity. By using phase locked sample and demultiplexer clocks distributed to all the digitiser units in parallel all the units are guaranteed to be synchronised. The flip-flops are D-type master-slave flip-flops, composed of two cascaded latches in series which are driven in antiphase. This is similar to the master-slave latches of the comparator but does not include the front-end preamplifier. The schematic of the D-type flip-flop is shown in figure 3.7.

### 3.3.6 Clock Buffer

The sampling clock and the demultiplexing clock must be distributed to all of the clocked comparators and flip-flops on the chip. The large number of loads and interconnect transmission lines present a significant load, so a high current clock driver is needed to maintain high bandwidth and sufficient signal level. The schematic of the clock buffer circuit is shown in figure 3.8.

Figure 3.7: Schematic of D-type flip-flop.

Figure 3.8: Schematic of the clock buffer.

The circuit is composed of a cascade of three high gain differential amplifiers. The input sinusoidal clock source is AC coupled to the positive input, with the inverting input held at the same DC reference voltage as the noninverting input. The cascade of high gain amplifiers squares up the sinusoidal source and also performs a single ended to differential conversion. The clock is split in the last stage to drive two final amplifiers, so that half the loads are driven from one amplifier and half the loads from the other. All clocks are distributed differentially to provide maximum rejection of common mode noise. On the chip, the clock signals, which run over comparatively long distances of over a millimetre, are routed as differential controlled impedance transmission lines of approximately 100 ohm differential impedance. Careful

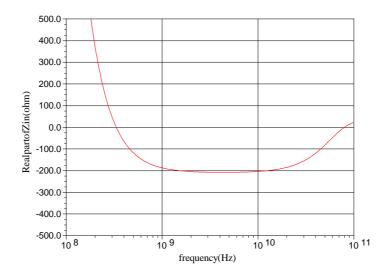

Figure 3.9: Emitter follower input impedance.

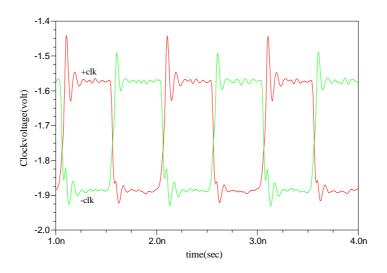

modelling of the clock transmission lines was very important, as the significant phase shift of long transmission lines provides the potential for on chip oscillation. Of particular concern are the use of emitter followers, as the combination of capacitive loading on the emitter combined with inductance in the base, for example as a result of a length of transmission line, can lead to oscillation of the emitter follower [32, 56]. Looking at the input impedance of a simple emitter follower using a minimum size InP transistor, without any loading, gives the results of figure 3.9. It can be seen that the real part of the input impedance is negative over a large part of the frequency range, and hence if the Q of the resonant circuit formed by the combination of base inductance and emitter capacitance is sufficiently high, the circuit will oscillate. The clock drivers could have provided an emitter follower level shift in the buffer and driven the transmission lines from the emitter followers. This is the generally accepted approach as it provides a low impedance drive which should be good for driving capacitive loads and the clock signal is at the correct DC level for driving the clock inputs of the flip-flops and comparators directly. Figure 3.10 shows a simulation of the clock switching waveform for a clock buffer incorporating emitter followers driving 300 um of transmission line into a differential amplifier load. It is evident that there is significant ringing and the circuit is on the verge

Figure 3.10: Clock driver with emitter followers.

of instability. By moving the emitter follower level shifting to the end of the transmission line, and using collector drive of the transmission line, the result of figure 3.11 was obtained. It is clear that this is a far more stable approach. The disadvantage is that a local level shifting block has to be included at the receiving end in every comparator and flip-flop. This incurs a penalty of six transistors per comparator or flip-flop, but was considered

Figure 3.11: Clock driver with collector drive.

the superior approach in the interests of stability. The collector drive of the transmission line provides a further advantage in that the collector resistors provide a back termination for the transmission line, so that any reflected wave from the load is absorbed in the back termination resistors, if they are well matched. The current level and device size of the drive transistors Q19-Q22 were selected so that collector load resistors could be chosen that not only provide the required clock voltage swing, but also give a good match to the impedance of the transmission lines.

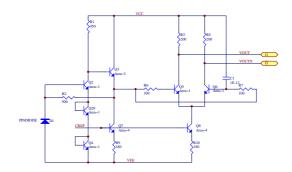

## 3.3.7 Output Buffer

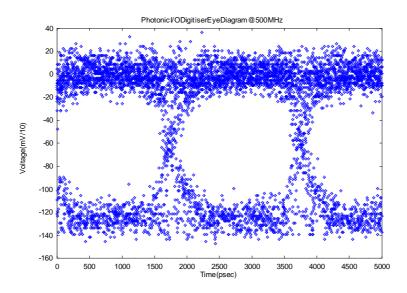

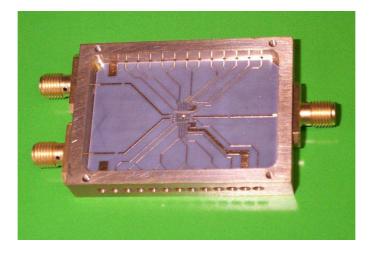

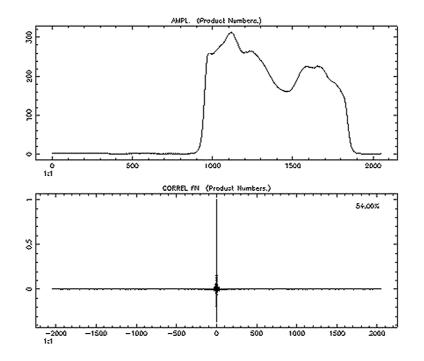

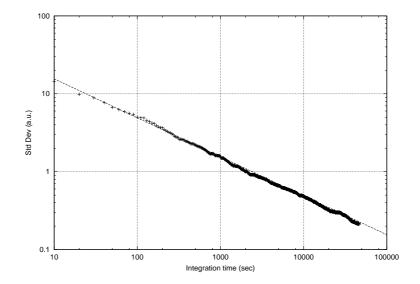

The digitised data is sent off chip through specially designed output buffers. The function of the output buffers is to provide sufficient drive to overcome any capacitive and transmission line loading on the outputs and to translate the internal voltage levels to a standard voltage level that can be interpreted by commercial logic. The only readily available commercial logic family that operates at the required speed, of up to 2 GHz, is ECL [55]. Hence the output buffers were designed to drive ECL logic. The standard ECL logic levels are -0.8 V for logic high, and -1.6V for logic low, with a signal