University of Wisconsin Milwaukee UWM Digital Commons

Theses and Dissertations

August 2020

# Health Condition Assessment of Multi-Chip IGBT Module with Magnetic Flux Density

Xueni Ding University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Ding, Xueni, "Health Condition Assessment of Multi-Chip IGBT Module with Magnetic Flux Density" (2020). *Theses and Dissertations*. 2485. https://dc.uwm.edu/etd/2485

This Thesis is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact open-access@uwm.edu.

## HEALTH STATE ASSESSMENT OF MULTI-CHIP IGBT MODULE WITH MAGNETIC FLUX DENSITY

by

Xueni Ding

A Thesis Submitted in

Partial Fulfillment of the

Requirements for the Degree of

Master of Science

in Engineering

at

The University of Wisconsin-Milwaukee

August 2020

#### ABSTRACT

# HEALTH STATE ASSESSMENT OF MULTI-CHIP IGBT MODULE WITH MAGNETIC FLUX DENSITY

by

Xueni Ding

The University of Wisconsin-Milwaukee, 2020 Under the Supervision of Professor Lingfeng Wang

To achieve efficient conversion and flexible control of electronic energy, insulated gate bipolar transistor (IGBT) power modules as the dominant power semiconductor devices are increasingly applied in many areas such as electric drives, hybrid electric vehicles, railways, and renewable energy systems. It is known that IGBTs are the most vulnerable components in power converter systems. To achieve high power density and high current capability, several IGBT chips are connected in parallel as a multi-chip IGBT module, which makes the power modules less reliable due to a more complex structure. The lowered reliability of IGBT modules will not only cause safety problems but also increase operation costs due to the failure of IGBT modules. Therefore, the reliability of IGBTs is important for the overall system, especially in high power applications. To improve the reliability of IGBT modules, this thesis proposes a new health state assessment model with a more sensitive precursor parameter for multi-chip IGBT module that allows for condition-based maintenance and replacement prior to complete failure.

Accurate health condition monitoring depends on the knowledge of failure mechanism and the selection of highly sensitive failure precursor. IGBT modules normally wear out and fail due to thermal cycling and operating environment. To enhance the understanding of the failure mechanism and the external characteristic performance of multi-chip IGBT modules, an electrothermal finite element model (FEM) of a multi-chip IGBT module used in wind turbine converter systems was established with considerations for temperature dependence of material property, the thermal coupling effect between components, and the heat transfer process. The electro-thermal FEM accurately performed temperature distribution and the distribution electrical characteristic parameters during chip solder degradation. This study found an increased junction temperature, large change of temperature distribution, and more serious imbalanced current sharing during a single chip solder aging, thereby accelerating the aging of the whole IGBT module.

According to the change of thermal and electrical parameters with chip solder fatigue, the sensitivity of fatigue sensitive parameters (FSPs) was analyzed. The collector current of the aging chip showed the highest sensitivity with the chip solder degradation compared with the junction temperature, case temperature, and collector-emitter voltage. However, the current distribution of internal components remains inaccessible through direct measurements or visual inspection due to the package. As the relationship between the current and magnetic field has been studied and gradually applied in sensor technologies, magnetic flux density was proposed instead of collector current as a new precursor for health condition monitoring. Magnetic flux density distribution was extracted by an electro-thermal-magnetic FEM of the multi-chip IGBT module based on electromagnetic theory. Simulation results showed that magnetic flux density had even higher sensitivity than collector current with chip solder degradation. In addition, the magnetic flux density was only related with the current and was not influenced by temperature, which suggested good selectivity. Therefore, the magnetic flux density was selected as the precursor due to its better sensitivity, selectivity, and generality.

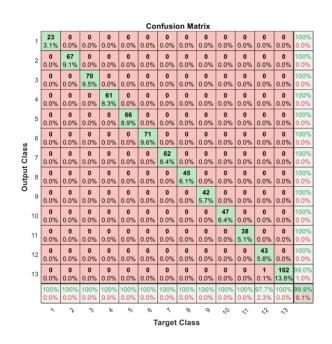

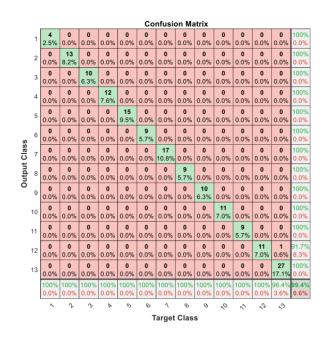

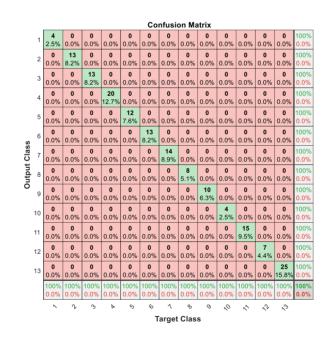

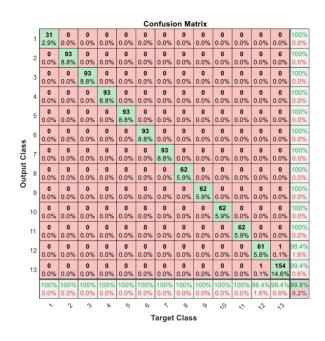

Finally, a health state assessment model based on backpropagation neural network (BPNN) was established according to the selected precursor. To localize and evaluate chip solder degradation, the health state of the IGBT module was determined by the magnetic flux density for each chip and the corresponding operating conduction current. BPNN featured good self-learning, self-adapting, robustness and generalization ability to deal with the nonlinear relationship between the four inputs and health state. Experimental results showed that the proposed model was accurate and effective. The health status of the IGBT modules was effectively recognized with an overall recognition rate of 99.8%. Therefore, the health state assessment model built in this thesis can accurately evaluate current health state of the IGBT module and support condition-based maintenance of the IGBT module.

## **TABLE OF CONTENTS**

| Chapter | 1 Introduction                                 | 1  |

|---------|------------------------------------------------|----|

| 1       | Motivation                                     |    |

| 1.2     | Background                                     | 3  |

|         | 1.1.1 Failure Mechanism of IGBT Module         | 4  |

|         | 1.1.2 Precursors for IGBT Condition Monitoring | 7  |

|         | 1.1.3 Health Condition Assessment Methods      | 9  |

| 1.3     | Research Gap                                   | 0  |

| 1.4     | Research Methodology                           | 11 |

| 1.5     | Contribution to Knowledge                      | 3  |

| 1.6     | Thesis Organization                            | 3  |

|         |                                                |    |

| Chapter | 2 Multiphysics Finite Element Modeling of IGBT Module                | 15 |

|---------|----------------------------------------------------------------------|----|

| 2.1     | Electro-thermal Coupling Theory of Finite Element Model              | 16 |

|         | 2.1.1 IGBT Module Packaging                                          | 16 |

|         | 2.1.2 Mathematical Model of Multi-physical Field Coupling            | 19 |

|         | 2.1.3 Transient Solving Process of Multiphysics Finite Element Model | 21 |

| 2.2     | Electro-thermal Finite Element Modeling of IGBT Module               | 23 |

|         | 2.2.1 Setting Material Property Parameters                           | 23 |

|         | 2.2.2 Boundary Conditions for Multiphysics Finite Element Model      |    |

| 2.3     | Validation of the Multiphysics Finite Element Model                  |    |

|         | 2.3.1 Validation of the Finite Element Model in Electrical Field     |    |

|         | 2.3.2 Validation of the Finite Element Model in Thermal Field        | 31 |

| 2.4     | Summary                                                              | 35 |

|         | •                                                                    |    |

| Chapter | <b>3 P</b> | recursor for Chip Solder Fatigue                             |    |

|---------|------------|--------------------------------------------------------------|----|

| 3.1     | The        | rmal Analysis of IGBT Module under Chip Solder Fatigue       |    |

|         | 3.1.1      | Temperature Distribution at low output frequency             |    |

|         | 3.1.2      | On-state Temperature Distribution under Chip Solder Fatigue  |    |

| 3.2     | Elec       | trical Analysis of IGBT Module under Chip Solder Fatigue     | 50 |

|         | 3.2.1      | Change of On-state Voltage under Chip Solder Fatigue         | 50 |

|         | 3.2.2      | Current Distribution of under Chip Solder Fatigue            |    |

| 3.3     | Rela       | tive Sensitivity for Fatigue Sensitive Parameters            | 53 |

| 3.4     | Mag        | gnetic Flux Density as A New Precursor                       |    |

|         | 3.4.1      | Electromagnetic Theory and Electro-thermal-magnetic FEM      | 55 |

|         | 3.4.2      | Magnetic Flux Density Distribution under Chip Solder Fatigue |    |

| 3.5     | Sun        | 1 mary                                                       |    |

|         |            | -                                                            |    |

| Chapter 4 | Health State Assessment Model | . 63 |

|-----------|-------------------------------|------|

| 4.1       | The Structure of BP Algorithm | . 63 |

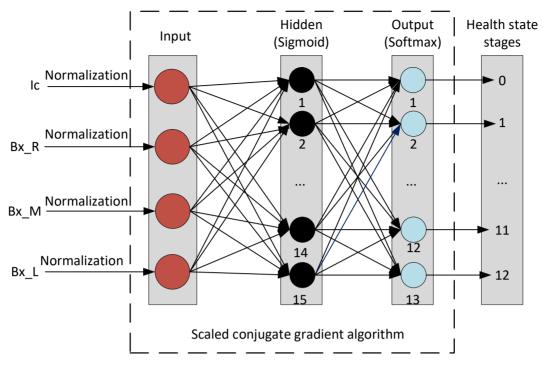

| 4.2 | Health Evaluation Model Based on BP Neural Network | . 67 |

|-----|----------------------------------------------------|------|

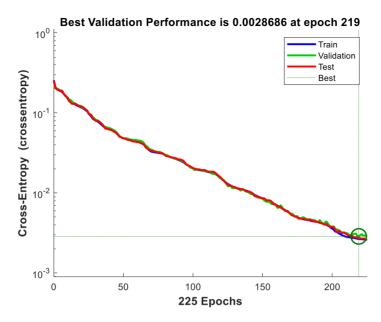

| 4.3 | Validity Analysis of the Health Evaluation Model   | . 70 |

| 4.4 | Summary                                            | . 75 |

| Chapter 5 | Conclusions and Future Work | 77 |

|-----------|-----------------------------|----|

| 5.1       | Conclusions                 | 77 |

| 5.2       | Future Work                 | 80 |

## References 81

## LIST OF FIGURES

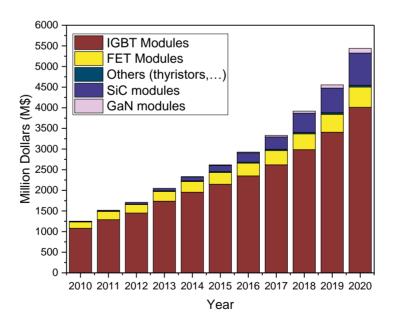

| Figure 1-1 2010-2020 power modules market [4] 1                                            |

|--------------------------------------------------------------------------------------------|

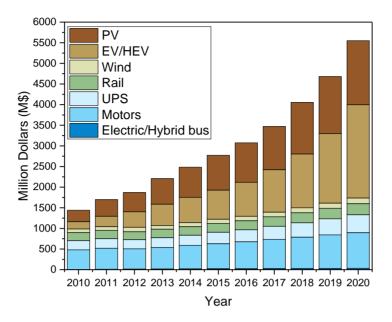

| Figure 1-2 Increasing applications of IGBT power modules in many areas [3]2                |

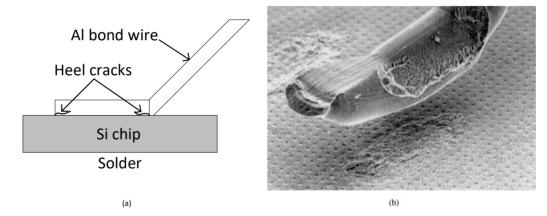

| Figure 1-3 Bond wire lift-off due to crack growth. (a) Crack propagation causing bond wire |

| lift-off. (b) SEM image of a lifted bond wire [12]5                                        |

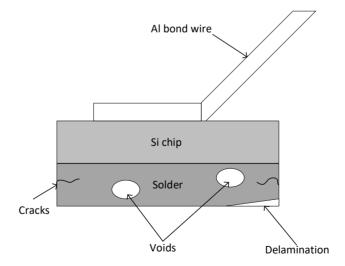

| Figure 1-4 Cracking and void formation in solder layer [12]                                |

| Figure 2-1 The multilayer structure diagram of the IGBT power module                       |

| Figure 2-2 Schematic diagram of studied multichip power module. (a) Configuration, (b)     |

| Inner structure, (c) Topology19                                                            |

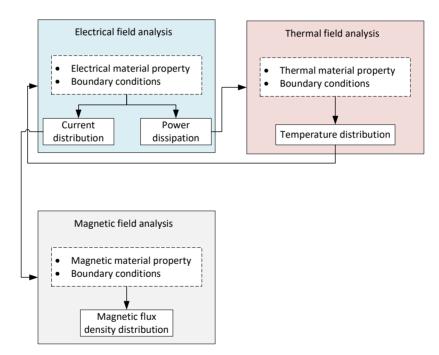

| Figure 2-3 Coupling relationship between electrical field and thermal field                |

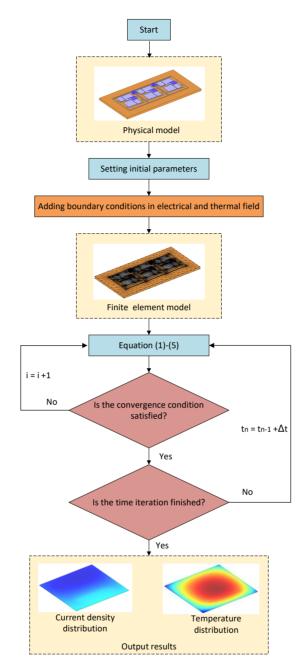

| Figure 2-4 The flowchart of calculation of electrical-thermal coupling model 23            |

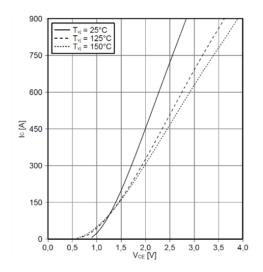

| Figure 2-5 The output characteristic curve of the IGBT chip                                |

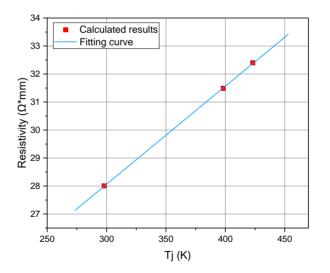

| Figure 2-6 Temperature-dependent electrical resistivity of IGBT chip                       |

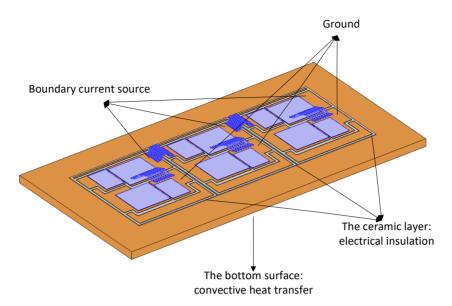

| Figure 2-7 Boundary conditions of multi-physical field model                               |

| Figure 2-8 3D finite element model of the IGBT module                                      |

| Figure 2-9 Output characteristics curves from datasheet and simulation                     |

| Figure 2-10 Comparison of transient thermal impedance curve from datasheet and simulation  |

|                                                                                            |

| Figure 2-11 Temperature distribution of the IGBT module                                    |

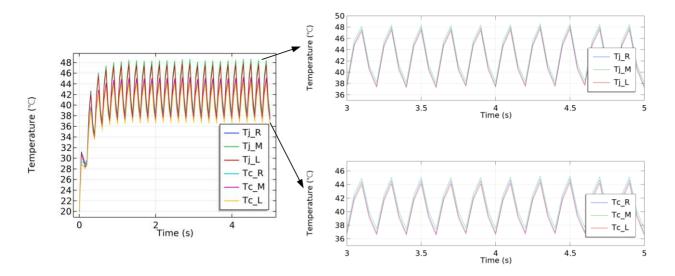

| Figure 3-1 Temperature distribution and swing when Ic=150A, f=5Hz                          |

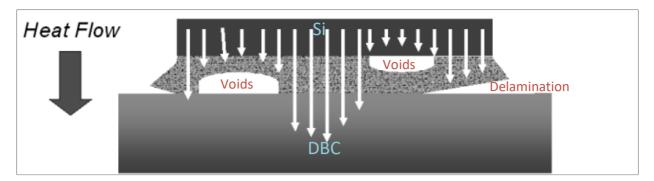

| Figure 3-2 Voids and delamination in chip solder layer [29]                                |

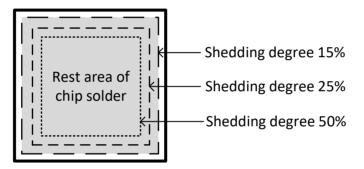

| Figure 3-3 Schematic diagram of different shedding degree of the chip solder               |

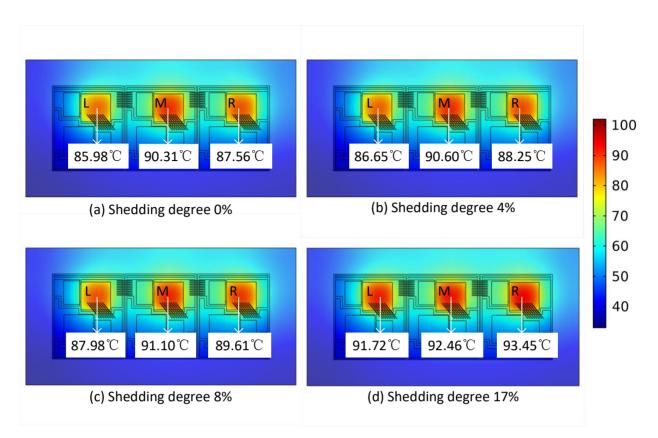

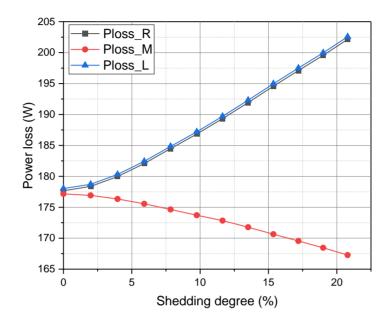

| Figure 3-4 On-state junction temperature distribution of the IGBT module under different     |

|----------------------------------------------------------------------------------------------|

| shedding degree of middle chip solder                                                        |

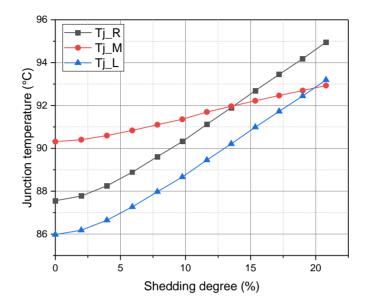

| Figure 3-5 Change of the junction temperature as the shedding degree of middle chip solder   |

| increases                                                                                    |

| Figure 3-6 Change of the power loss as the shedding degree of middle chip solder increases.  |

|                                                                                              |

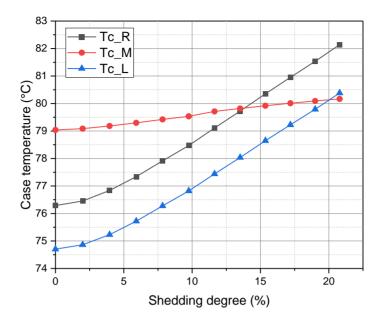

| Figure 3-7 On-state case temperature distribution under different shedding degree of middle  |

| chip solder                                                                                  |

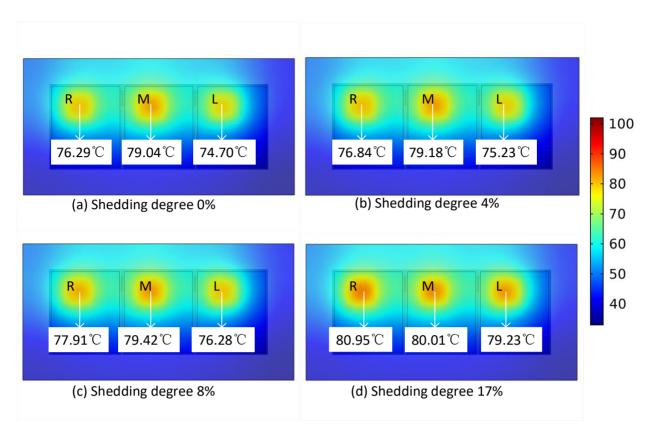

| Figure 3-8 Change of the case temperature as the shedding degree of middle chip solder       |

| increases                                                                                    |

| Figure 3-9 Change of the thermal resistance as the shedding degree of middle chip solder     |

| increases                                                                                    |

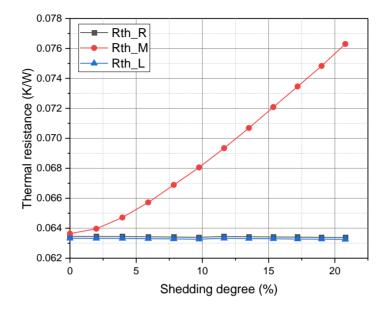

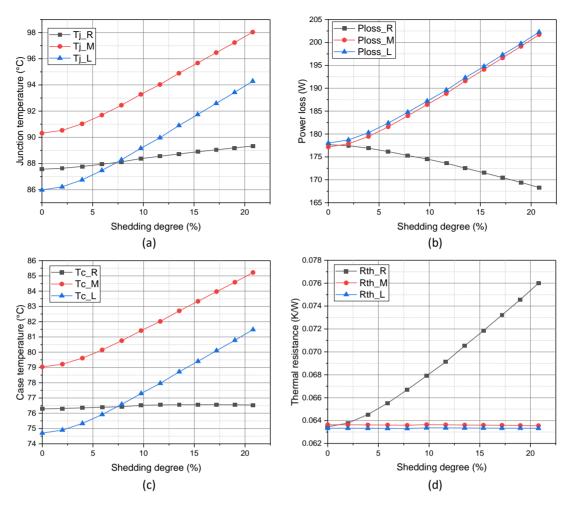

| Figure 3-10 Change of thermal characteristic parameters as the shedding degree of left chip  |

| solder increases. (a) Change of junction temperature, (b) Change of power loss, (c)          |

| Change of case temperature, (d) Change of thermal resistance                                 |

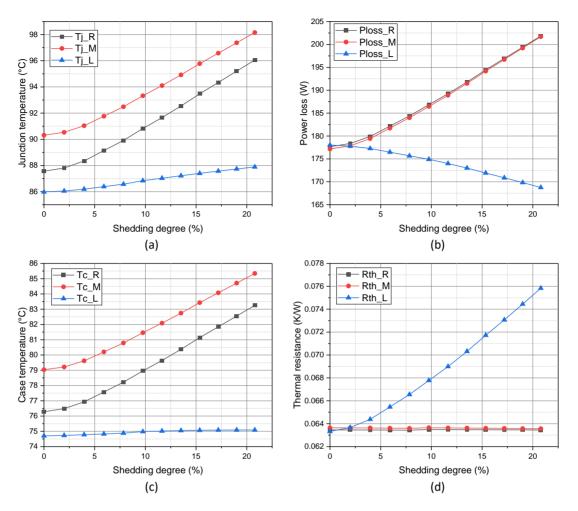

| Figure 3-11 Change of thermal characteristic parameters as the shedding degree of right chip |

| solder increases. (a) Change of junction temperature, (b) Change of power loss, (c)          |

| Change of case temperature, (d) Change of thermal resistance                                 |

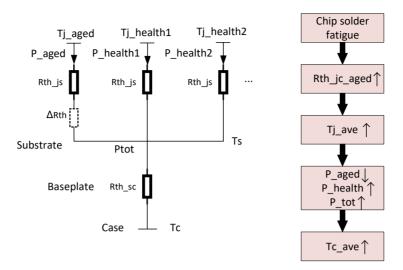

| Figure 3-12 Change of thermal network in a multi-chip IGBT module due to chip solder         |

| fatigue                                                                                      |

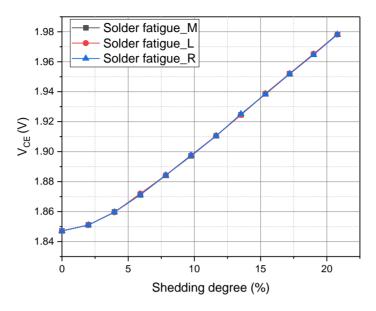

| Figure 3-13 Change of $V_{CE}$ with different shedding degree                                |

| Figure 3-14 Current distribution with different shedding degree. (a) Middle chip solder      |

| fatigue, (b) Left chip solder fatigue, (c) Right chip solder fatigue                         |

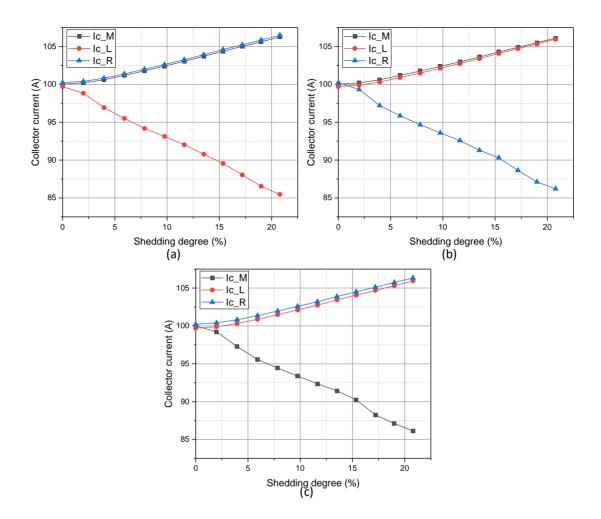

| Figure 3-15 Simplified on-state electrical circuit of the multi-chip IGBT module 52                |

|----------------------------------------------------------------------------------------------------|

| Figure 3-16 The electro-thermal-magnetic FEM                                                       |

| Figure 3-17 Multi-physics coupling relationship in the electro-thermal-magnetic FEM 57             |

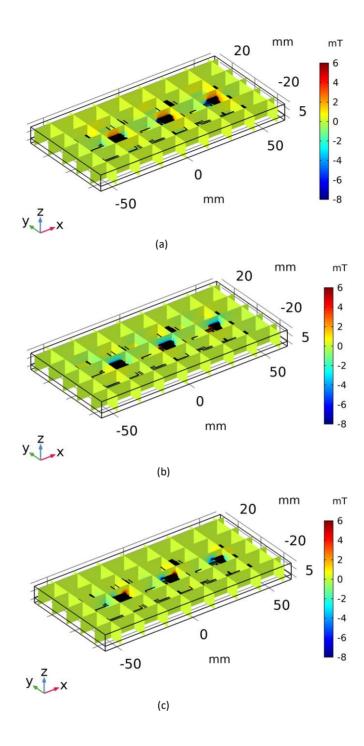

| Figure 3-18 Magnetic flux density distribution in health state of the IGBT module. (a)             |

| Magnetic flux density in X-axis direction (B <sub>X</sub> ), (b) Magnetic flux density in Y-axis   |

| direction (B <sub>Y</sub> ), (a) Magnetic flux density in Z-axis direction (B <sub>Z</sub> )58     |

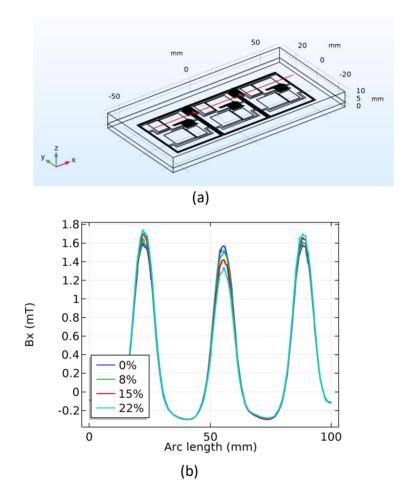

| Figure 3-19 The $B_X$ distribution with different shedding degree of middle chip solder along a    |

| 3D line. (a) The position of the 3D line, (b) The $B_X$ distribution with different shedding       |

| degree of middle chip solder                                                                       |

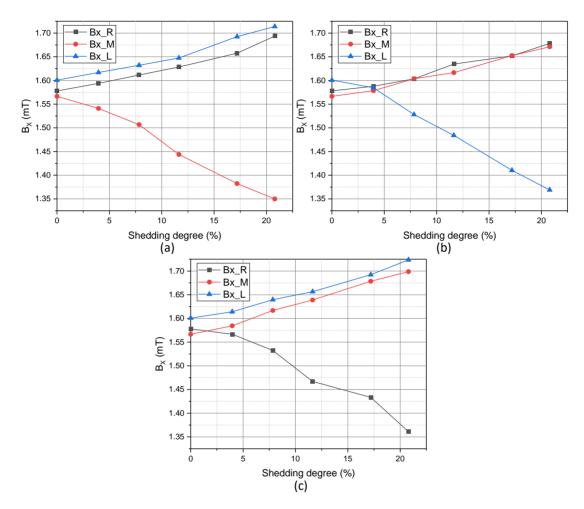

| Figure 3-20 $B_X$ distribution with different shedding degree. (a) Middle chip solder fatigue, (b) |

| Left chip solder fatigue, (c) Right chip solder fatigue60                                          |

| Figure 4-2 Structure of the health state assessment model based on BP neural network 70            |

| Figure 4-3 Change of cross-entropy for the neural network                                          |

| Figure 4-4 Classification accuracy in training                                                     |

| Figure 4-5 Classification accuracy in validation                                                   |

| Figure 4-6 Classification accuracy in testing                                                      |

| Figure 4-7 Overall classification accuracy of the model                                            |

| Figure 4-8 ROC curves about the model for health state identification                              |

## LIST OF TABLES

| Table 1-1 Existing failure precursors for health condition monitoring                                |

|------------------------------------------------------------------------------------------------------|

| Table 2-1 Parameters of the IGBT module.    24                                                       |

| Table 2-2 Material parameters of IGBT module                                                         |

| Table 2-3 Resistivity and temperature coefficient of the IGBT chips.    27                           |

| Table 2-4 Comparison of thermal resistances from simulation and datasheet                            |

| Table 2-5 Comparison of case temperature obtained from experiment and simulation at steady           |

| state                                                                                                |

| Table 3-1 Variation of junction temperature distribution and case temperature distribution as        |

| the shedding degree of middle chip solder increases                                                  |

| Table 3-2 Variation of junction temperature and case temperature as the shedding degree of           |

| left chip solder increases                                                                           |

| Table 3-3 Variation of junction temperature and case temperature as the shedding degree of           |

| right chip solder increases                                                                          |

| Table 3-4 Comparison of the relative sensitivity of the FSPs                                         |

| Table 3-5 The distribution of $B_X$ with different ambient temperature for health module 61          |

| Table 3-6 The distribution of $T_j$ with different ambient temperature for health module 61          |

| Table 3-7 The distribution of T <sub>c</sub> with different ambient temperature for health module 61 |

| Table 4-1 Division of health state stages and corresponding treatment [122].       68                |

| Table 4-2 The performance of network with different algorithms                                       |

#### ACKNOWLEDGEMENTS

I would like to thank many people who provided their kind help during my study and research so that I could finish my thesis.

First and foremost, I would like to extend my sincere gratitude to my academic advisor Professor Lingfeng Wang for his continuous support, constructive advice, and effective supervision. Without his support for this research topic and the guidance in all stages of this work, this thesis could not have reached its present form.

Furthermore, I would like to thank Dr. Zhaoxi Liu and other members from my current research group for their patient discussions and useful suggestions. I am grateful to Dr. Wei Lai and other members from my former research group in Chongqing University for their knowledge, instruction, and persistent support.

I greatly appreciate my academic advisor Professor Minyou Chen in Chongqing University for his encouragement so that I could have the chance to study in this program and finish this thesis.

Last but not least, special thanks go to my family for their loving considerations and great confidence in me throughout all these years. I also owe sincere gratitude to my friends who would listen to me and help me work out my problems during difficult stages of the thesis.

## **Chapter 1** Introduction

### **1.1 Motivation**

As the key technology that can achieve efficient conversion and flexible control of electronic energy [1], the application of power electronics has been widely used in industrial, commercial, and residential areas [2]. With an increase of the market size of power electronics, insulated-gate bipolar transistor (IGBT) modules dominate the high voltage and current market [3, 4], as shown in Figure 1-1. Because of the excellent performance such as high power density, high switching frequency, low power loss, and cost effectiveness [5, 6], the application of IGBT power modules is increasing in many areas such as electric drives, hybrid electric vehicles, railways, and renewable energy systems [3], as presented in Figure 1-2.

Figure 1-1 2010-2020 power modules market [4].

Figure 1-2 Increasing applications of IGBT power modules in many areas [3].

However, the fast growth on the application of power electronics in these areas challenges reliability of the overall systems. For instance, it is pointed out that power converters dominate the failures of wind turbines [7], and 38% faults of variable speed ac drives in industry is caused by power converters failures [8]. In addition, power semiconductor devices and solder joints account for 34% of total failures in power converter system, which indicates that power semiconductor devices are the most vulnerable components in power converter system [7, 9, 10]. Any failure of the components or the devices will lead to shutdown of the overall system. These sudden breakdowns increase maintenance and repair costs or even influence human lives. For instance, in a PV generation plant, the power electronic inverters were responsible for 37% of the unscheduled maintenance and 59% of the associated cost [10]. The increasing operating costs and unexpected disruption to services partially offsets the benefits of the application of power electronic systems.

As mentioned above, the reliability of the overall system mainly determined by the reliability of the power semiconductor devices. To satisfy the high reliability requirements of the overall system, both safety consideration as well as limitation of the system operation cost must be considered [1, 9]. It is necessary to work in power semiconductor devices health management area, such as diagnosis, prognosis, and condition monitoring [9]. The reliability of the overall system can be greatly improved by scheduling condition-based maintenance, replacing devices before failure occurs, or taking actions including prognosis, active thermal control, and fault tolerant operation for power devices according to the condition of the power devices [1]. Therefore, accurate condition monitoring (CM) is the basic technique to achieve the improvement of reliability of the overall system. Because IGBTs are the most commonly used power semiconductor devices and there is a low satisfaction level of previous condition monitoring methods [9], it is important to investigate new condition monitoring methods for IGBT modules to improve the reliability of the overall systems.

## **1.2 Background**

CM is a technology of measuring the real-time condition of a component to take an appropriate action before catastrophic failures occur [11, 12]. It is important to enable the condition-based maintenance and replacement and provide data for prognosis and diagnosis. The challenge of CM is finding the relationship between the known degradation based on the knowledge of failure mechanism and the measured operating characteristic parameters which requires practical techniques [12, 13]. Thus, the accuracy of condition assessment depends on the parameters that indicate device degradation and assessment methods. Failure mechanism, current precursors, and health condition assessment methods of IGBT modules are introduced in this section.

Press-pack and wire-bonded IGBT modules are two types of IGBT models classified according to packaging techniques. The connection between chips in press-packaging is achieved

by direct press-pack contact instead of bond wires [14]. Therefore, press-pack IGBT modules have better performance in terms of reliability, power density, and cooling capability [14-16]. However, the cost of press-pack IGBT modules is higher than that of wire-bonded IGBT modules. Therefore, wire-bonded power device modules are mainly used in power electronics area [17]. This thesis focusses on the condition monitoring of wire-bonded IGBT modules.

#### 1.1.1 Failure Mechanism of IGBT Module

Failure mechanisms of power modules are generally categorized into chip-related failure mechanisms and package-related failure mechanisms. However, chip-related failure mechanisms occur due to overstress conditions without any prior warning, which is outside of the realm of CM for wear-out fatigue and result in the destruction of the module [11, 18]. Thus, the package-related failure mechanisms are more important and practical to be monitored.

There are many parameters affecting the packaged-related failure of IGBT modules and their relationships are complex, involving multiple factors such as temperature, vibration, and humidity. However, it is found that temperature is the most dominant stressor for the failure [7, 10, 17]. In addition, the packaged-related wear-out caused by thermal stress can increases the possibility of the chip-related failure [11, 18].

Under the effect of thermal stress, the failure of the IGBT module mainly occurs in the solder layer and the bonding wire because of mismatched coefficients of thermal expansion (CTEs) of adjacent materials, such as wire bond and silicon, silicon and direct bonded copper (DBC) ceramic substrate, and DBC substrate and base plate. Therefore, solder layer fatigue and bond wire lift-off are the most common failure modes of IGBT modules [5, 12, 17, 19, 20]. Power cycling or thermal cycling is generally used to study the above two failure mechanisms under experimental conditions [21].

#### 1) Bond wire lift-off

Aluminum bonding wire is an important part to realize the function of current flowing by connecting chips, and chip and DBC. Because of the large difference in CTEs between the bond wire and the silicon chip, it bears a huge thermal stress under large temperature swings caused by the power dissipation in the chip and the ohmic self-heating of the bond wire [11]. As thermal cycling repeats, cracks propagate from the edge of joints to the center along the small grain boundaries of bond wires until bond wire lift-off occurs [22], as shown in Figure 1-3. To improve the reliability of the bonding wire connection in the industry, multiple bond wires are generally connected in parallel so that the current through other wires immediately increase after some of the wires lift-off, which accelerates lift-off of the rest bond wires [22].

Figure 1-3 Bond wire lift-off due to crack growth. (a) Crack propagation causing bond wire lift-off. (b) SEM image of a lifted bond wire [12].

Research related with bond wire fatigue have been carried out. For example, literature [23] points out that the main failure mode of the IGBT module is bond wire fatigue when the junction temperature fluctuation ( $\Delta T_j$ ) is more than 100°C in the power cycle experiment. Literatures [24, 25] research the influence of bond wire type and layout on the reliability of IGBT modules. Literature [26] analyzes the influence of IGBT module junction temperature fluctuation on the reliability of bond wires and proposes corresponding improvement methods. Literature [27] analyzes the influence of different bonding temperature on the bond wire reliability. In-depth

understanding of the failure mechanism of the bond wire is to accurately monitor its operating state, provide guidance for design and manufacture process, and improve the operating reliability.

#### 2) Solder layer fatigue

The solder layer is an important heat transfer channel of IGBT modules, and its performance directly affects the reliability of IGBT modules. The device is subjected to frequent temperature fluctuations because of the frequent switching of IGBT modules. The CTE mismatches between the silicon chip and DBC substrate, the DBC substrate and baseplate with temperature variation result in shear stress in the solder layer and produce cracks, delamination and voids [28], as shown in Figure 1-4. The solder fatigue reduces the effective area for heat conduction and increase thermal resistance, which increases the junction temperature and accelerates the degradation of itself and other failure modes such as bond wire fatigue [23, 28-31]. The corner is especially subject to large thermal stress, and cracks generally initiate here, and then gradually develop to the center of the solder layer ultimately leading to the failure [5, 32-34].

Figure 1-4 Cracking and void formation in solder layer [12].

At present, a lot of researches have been conducted on the fatigue failure mechanism of the solder layer, mainly focusing on thermal parameters and stress analysis. Research [35] indicated that the degradation occurs first on the solders at high temperature level with the same temperature fluctuation. Study in [35, 36] showed that the reliability of the solder can be developed by new solder materials, such as Sn-Ag-Cu. Literatures [23, 34] based on the aging experiments under different  $\Delta T_j$  found that the main failure mechanism is solder fatigue when  $\Delta T_j$  is small, and the bonding wire fatigues before the solder layer fatigue and then becomes the main failure mode when  $\Delta T_j$  is large. Literatures [37, 38] indicated that the most critical solder fatigue occurs in baseplate solder for passive thermal cycling, especially in the case of copper base plates because of the worst mismatch in the CTEs and the maximum temperature swing combined with the largest lateral dimensions, but chip solder fatigue determines the lifetime of the module for active power cycling.

#### 1.1.2 Precursors for IGBT Condition Monitoring

The external characteristics of the IGBT module is generally affected by the degradation. For instance, the junction temperature  $(T_j)$ , and thermal resistance  $(R_{th})$  of the device increase, and onstate collector-emitter voltage  $(V_{ce,on})$  changes when solder or bond wire fatigues [1, 11, 12]. A number of IGBT health monitoring methods exist which are mainly based on the change of the electrical characteristic parameters and the temperature characteristic parameters, summarized in Table 1-1.

| Degradation monitored | Precursor                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------|

| Bond wire lift-off    | On-state collector-emitter voltage (V <sub>CE,on</sub> ) [39-44]<br>Gate-emitter voltage (V <sub>GE</sub> ) [45] |

Table 1-1 Existing failure precursors for health condition monitoring.

|                          | V <sub>CE,on</sub> [39]                                  |

|--------------------------|----------------------------------------------------------|

| Die-attach fatigue       | Collector current change rate (dI <sub>C</sub> /dt) [46] |

|                          | Temperature gradient ( $\nabla$ T) [47]                  |

|                          | V <sub>CE,on</sub> [39]                                  |

| Baseplate solder fatigue | Case-above-ambient temperature (Tca) [48]                |

|                          | Thermal resistance (R <sub>th</sub> ) [49]               |

|                          | V <sub>CE,on</sub> [50-52]                               |

|                          | V <sub>GE(th)</sub> [53, 54]                             |

|                          | dI <sub>C</sub> /dt [55, 56]                             |

|                          | Transconductance (G <sub>M</sub> ) [56]                  |

| Junction temperature     | collector voltage slope (dV/dt) [57]                     |

|                          | Turn-off delay (toff) [51, 55]                           |

|                          | Turn-on delay (ton) [55]                                 |

|                          | Power loss [58]                                          |

|                          | Thermal model [59, 60]                                   |

A failure precursor is an indicative parameter of an impending failure [61]. From Table 1-1, it can be found that all those precursors are related to temperature. According to failure mechanism analysis, junction temperature and thermal resistance are the two parameters that directly reflect the degradation of the module. However, direct measurement of junction temperature and internal temperature distribution in the module is impractical because most sensing devices are eventually damaged by excessive junction temperature, intrusive measurement has effect on the characteristics of the module, and contactless measurement is costly [12, 61]. In addition, a great error can be caused by the position of the sensor. The external temperature like case temperature is easily measured, but the difficulty lies in understanding the electrothermal interaction, and the masking effects of a variable working condition and other mechanisms of degradation, such as bond wire lift-off [12]. The accuracy of the evaluation method based on power loss and thermal

model is strongly dependent on the measurement accuracy of instantaneous power losses and the correct identification of the thermal network. However, the thermal network also relies on aging effects and is nonlinear at high temperature [62]. Therefore, fast and cheap junction temperature estimation methods and health state monitoring methods based on temperature sensitive electrical parameters (TSEPs) and fatigue sensitive parameters (FSPs) get more attention to estimate junction temperature or the condition of the power module.

In Table 1-1,  $V_{CE,on}$  is the most widely used TSEPs. However, the measurement of  $V_{CE,on}$  is difficult with extremely high requirement for measurements accuracy because of small variation, strictly control of temperature and current to keep the same operating points, and insertion of measurement devices which needs high voltage isolation [12, 46]. The gate signals are low-voltage quantities and sensitive for degradation, but they interrupt the IGBT's normal switching operations since the measurement requires external signal injection to the gate [12, 13, 46, 62, 63]. For switch time, the duration is very short [12]. For collector current, it still needs to work on nonintrusive and contactless measurement. Thus, the limitations of existing techniques largely prevent the wide application of CM for power electronics reliability. It still needs efforts oriented to improve the sensitivity and to reduce the cost of CM.

#### 1.1.3 Health Condition Assessment Methods

Generally, existing condition assessment methods can be categorized into two sets: modelbased method and data-driven method [5]. The model-based method establishes physics of failure (PoF) model with the consideration for actual operating point and external load missions during the life cycle, and an understanding of their effect on failure mechanism [64, 65]. Both reliability prediction and lifetime prediction can be ideally done based on physics-of-failure analysis [1]. However, the PoF model is computationally costly for building relationships between different factors. In contrast, data-driven methods take advantage of the information from available measurements without prior knowledge of the failure mechanisms by statistical and probabilistic analysis [61]. Data-driven methods are computationally efficient for a complex multivariate system with different failure mechanisms [5].

There are increased researches combining the two methods in IGBT health condition assessment. Literature [66] accurately predicted the on-state resistance of the IGBT with DC link voltage and output voltage ripple based on three kinds of artificial neural network (ANN) structure. Study in [67] proposed a multiclassification fusion system leverages the strengths provided by Backpropagation Neural Networks (BPNNs), Support Vector Machine (SVM), Deep Belief Networks (DBNs), Self-organizing Maps (SOMs), and Mahalanobis Distance (MD) to form a robust classification model of IGBT health condition after identifying health parameters as inputs and dividing different health state as outputs. Paper [68] solved the complex nonlinear relationship between the electrical parameters and the junction temperature of the IGBT module from the BPNN point of view. A health condition evaluation method based on multivariable IGBT bond wire aging parameters was proposed using ANN with only 2.47% average error, which was more accurate than the univariate evaluation [69].

## 1.3 Research Gap

Multi-chip IGBT power modules are designed for large current ratings with a number of chips connected in parallel. The physical structure of the multi-chip IGBT modules are more complex than the IGBT modules with only one or two chips, which results in the increased complexity in the physics of failure as well as their characteristic formation owing to the uneven lay-out of power semiconductor chips combined with the heterogeneous construction of power modules [6], such as thermal coupling effect [70] and imbalanced current sharing [71]. Researches have been carried out in current distribution [72, 73], temperature distribution [74], bond wires degradation [6], and baseplate degradation [75] of the multi-chip IGBT modules, but the failure mechanisms and the change of external characteristics of the modules caused by wear-out is not clear till now, especially for chip solder fatigue. Chip solder fatigue cannot be ignored for lower temperature swings at active power cycling, and it even appears earlier than the bond wire degradation.

In addition, the existing techniques in Table 1-1 are mainly applied to IGBT modules with only one or two chips. It is more challenging to achieve health condition monitoring when there are more IGBT chips in parallel in multi-chip IGBT power modules. The parallel structure can accelerate chip failure and the failure signature of the chip can be concealed [6]. Hence, the investigation of new method for multi-chip IGBT power modules health condition assessment, and the failure mechanisms and change of external characteristics caused by chip solder fatigue have been identified as a research gap in this thesis.

## 1.4 Research Methodology

The main objective of this research is the development of a novel online health state evaluation method for multi-chip IGBT power modules. It is common to have parallel IGBT chips with antiparallel diode chips within the power module. This research focusses on the health condition of the IGBT chips and ignores the effect of the diode chips because IGBT chips are more susceptible to failures compared with diode chips. IGBT chips experience higher thermal stress compared with diodes due to higher turn-on and turn-off power dissipation, and IGBT chips own a more complex semiconductor structure compared with diodes which makes IGBT chips less reliable [6]. Because of the package, the internal component degradation is hard to notice until the IGBT module ceases to function. Therefore, health condition monitoring is necessary for multi-chip IGBT power modules.

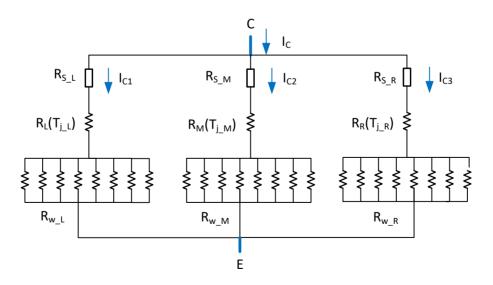

Because CM relies on the knowledge of failure mechanism and selection of failure precursor, to enhance understanding of the failure mechanism and external characteristic performance of single chip solder degradation, an electrical-thermal finite element model of Infineon FF450R17ME4 was established in COMSOL. The 3D Multiphysics FEM can generate more accurate thermal and electrical characteristic performance with considerations of temperature dependence of material property, thermal coupling effect between components, and heat transfer process. The validity of the model is verified by calibrating the output characteristic curve and transient thermal impedance curve from datasheet as well as comparing the temperature distribution with the measurement results of the experiment in other paper. Based on the simulation model with high accuracy, on-state distribution of thermal and electrical characteristic parameters under different chip solder degradation is performed, and the failure mechanism of the multi-chip IGBT module under single chip solder degradation is analyzed.

According to the change of thermal and electrical parameters with chip solder fatigue, the sensitivity of FSPs is analyzed and compared, and collector current  $I_c$  of the aging chip shows highest sensitivity. However, the internal components are inaccessible for direct measurements or visual inspection due to the package. Because the relationship between the current and magnetic field has been dug up and gradually applied in current measurement [73], magnetic flux density is proposed instead of  $I_c$  as a new precursor for health condition monitoring. An electro-thermal-magnetic finite element model of the multi-chip IGBT module is built by adding an air layer above the original model to extract magnetic flux density distribution under different chip solder degradation. The magnetic flux density distribution only depends on the current distribution. The

magnetic flux density has even higher sensitivity than I<sub>c.</sub> new precursor is verified. Therefore, the magnetic flex density is selected as the precursor due to better sensitivity, selectivity, and generality.

Finally, a health state assessment model based on BPNN is established. To localize and evaluate chip solder degradation, the health state of the IGBT module is determined by the magnetic flux density for each chip and the corresponding operating conduction current. Because the relationship between the health state and the four inputs is nonlinear, data-drive method instead of model-based method is more suitable for health state assessment model. Furthermore, BPNN is the most common type of supervised ANN which is normally used in pattern recognition and multiclass classification for its strong nonlinear processing ability and good self-learning, self-adapting, robustness and generalization ability. The trained model is tested by test set of samples, which shows high accuracy in health state evaluation.

## **1.5** Contribution to Knowledge

The main outcome of this research is the implementation of a new precursor on multi-chip parallel IGBT module health state assessment. Consequently, this research has made the following contributions:

- New failure precursor for IGBT power modules.

- New discovery of the correlation between external characteristic parameters and chip solder fatigue in the multi-chip parallel IGBT modules.

- New IGBT health state assessment model based on magnetic flux density.

## **1.6 Thesis Organization**

An electro-thermal finite element model of a multi-chip parallel IGBT power modules is built in Chapter 2, which is validated to analyze the change of external characteristic parameters of the module during the chip solder degradation. Chapter 3 analyzes the electrical parameters and thermal parameters which is widely used as precursor for condition monitoring. In addition, magnetic flux density is proposed as a new precursor, and it shows higher relative sensitivity and better selectivity and generality. Chapter 4 proposes a health state assessment model based on backpropagation neural network with the new precursor. Finally, Chapter 5 concludes the thesis.

## Chapter 2 Multiphysics Finite Element Modeling of IGBT Module

As an important part of converter, IGBT module is key part of power electronic system to work as essential energy conversion technique in many areas such as renewable energy generation, electric vehicle, and aerospace. The working condition often includes stringent stressors such as moisture, vibration, high voltage, and high temperature. Because of the adverse operation circumstances and the frequent change of output power, the IGBT module can experience large temperature fluctuation during the actual operation.

However, due to a multi-layer structure and the mismatch of the coefficient of thermal expansion (CTE) of materials of different structures, a large thermal stress can be created by temperature cycle on the material surface, which causes the fatigue of the solder layer of IGBT modules or the aging of the bonding wires. The aging of the module can further influence the temperature distribution of the module. The failure rate can accelerate when the operating temperature increases [76]. In addition, temperature sensitive electrical parameters (TSEPs), like turn-off time, turn-on time, collector-emitter saturation voltage, and current distribution are also changed when temperature distribution is changed. Therefore, temperature is an important factor which limits the reliability of the IGBT module.

As the demand for high power density devices continues to grow in the industrial field, it is necessary to carry out accurate electro-thermal modeling of the power module to save maintain cost and development time caused by over design or under design and improve the reliability when the design cycle starts [77]. In previous studies, electrical and thermal characteristics have been analyzed using analytical method in isolated electrical and thermal domain for individual component [78-81]. However, modeling the module in electrical and thermal field separately cannot accurately capture the temperature effect on the electrical characteristics, like power loss.

In [82-86], these researches have extracted electrical equivalent thermal network as electrothermal model of the power module based on the manufacture or experiment data, but component interaction such as thermal coupling phenomena has been ignored.

To solve these difficulties, physics-based modeling is extracted with the consideration of the physical structural, material properties and the environment parameters, which can clearly observe the component interaction in electro-thermal domain. However, the analytical approach to analyze electro-thermal problems is not suitable for 2D or 3D structures because of complex geometry and boundary conditions [87]. Numerical approaches such as finite element analysis (FEA) are applied in the modeling [78, 88-92]. This model built with FEA is called finite element model (FEM). The electro-thermal FEM can be used to solve coupling relationship between electrical domain and thermal domain and obtain the component interaction, which can give more accurate results. Therefore, electro-thermal FEM is built in this thesis for reliability analysis.

In this chapter, the electric-thermal FEM of a parallel multi-chip IGBT module is established with the consideration of the temperature dependence of the chip material, and the validation of the model is verified according to the datasheet and results of the experiment. By establishing the accurate multi-physical field coupling FEM, it is helpful to study thermal and electrical characteristics of the device and provide the accurate simulation to support analyzing precursor parameters of degradation and evaluating the health state of IGBT module.

## 2.1 Electro-thermal Coupling Theory of Finite Element Model

#### 2.1.1 IGBT Module Packaging

Press-pack and plastic case are two common IGBT packaging types. For plastic case packaging, there are bond wires and solder to realize electrical connection. Unlike plastic case,

press-packs use surface contact by clamping force instead of bond wires for improved reliability [14]. This research focuses on the plastic packaged IGBT power modules as they are the main packaging style for high-voltage and high-power-density application because of low manufacturing costs and easy installation.

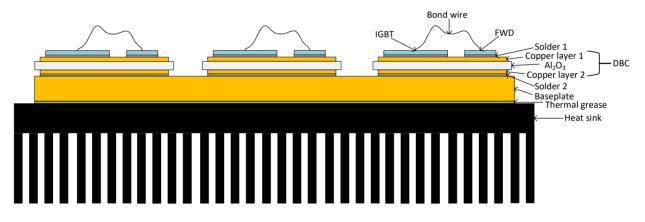

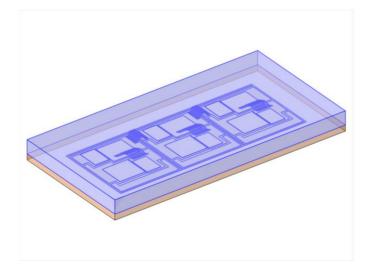

Figure 2-1 illustrates a simplified diagram of a common high-power-density IGBT module, in which IGBT chips and freewheel diode (FWD) chips are placed in anti-parallel on the direct bond copper (DBC) layer. All the chips are soldered to the copper layers through the solder layers, while the ceramic layers serve mainly as electrical insulation. The DBC layers is also soldered to the copper baseplate through the solder layers. There are bond wires between chip and chip, or chip and copper, or copper and copper to achieve electrical conduction. To get better heat dissipation effect, IGBT modules are usually placed on the heat sink by thermal grease. The common cooling methods include water cooling and air cooling.

Figure 2-1 The multilayer structure diagram of the IGBT power module.

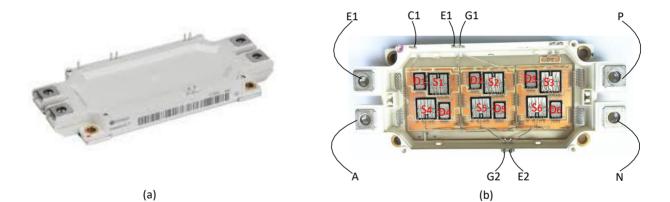

The model studied in this research is Infineon FF450R17ME4, and its configuration, inner structure, and equivalent circuit topology are demonstrated in Figure 2-2. This kind of power module is commonly applied in motor drives, servo drives, ups system, wind turbines, etc. As indicated in Figure 2-2(c), it is a half-bridge (phase-leg) power module, in which each leg comprises of three IGBTs with anti-parallel freewheel diodes (FWDs) in parallel. This parallel

structure helps the module to achieve high current specification.  $S_1$  to  $S_3$  are the parallel IGBT chips, and  $D_1$  to  $D_3$  are the anti-parallel FWD chips. They form the upper leg. In the lower leg,  $S_4$  to  $S_6$  are the parallel IGBT chips, and  $D_4$  to  $D_6$  are the anti-parallel FWD chips. The upper leg and the lower leg are in series. G, E and C represent gate terminals, emitter terminals, and collector terminals, respectively. P and N are signs for positive terminal and negative terminal in the power loop.  $i_{c1}$  to  $i_{c3}$  are collector currents of parallel chips, and  $V_{CE}$  is collector-emitter voltage.

The chips and bond wires in the module are main part to generate heat due to power dissipation in the switching and conduction states [93], and the temperature will be fluctuating during the operating process. Under the action of alternating temperature, thermal stress will be generated, which will cause failures, such as bonding wire lift-off and solder joint cracking [14, 94].

Figure 2-2 Schematic diagram of studied multichip power module. (a) Configuration, (b) Inner structure, (c) Topology.

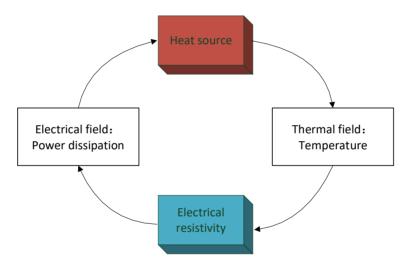

#### 2.1.2 Mathematical Model of Multi-physical Field Coupling

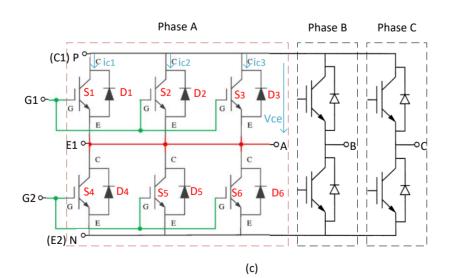

When IGBT module is in the operating condition, the power dissipation due to current and voltage in electrical filed is the heat source in the thermal field, which causes non-uniform temperature distribution in the IGBT module. Some material properties are temperature dependent, like the electrical resistivity. Therefore, the current and voltage in electrical filed can be affected by the change of temperature. Due to the coupling relationship, to obtain the temperature distribution accurately, the electro-thermal coupling effect must be considered. The interaction among the electrical field and thermal field in the IGBT module is expressed in Figure 2-3.

Figure 2-3 Coupling relationship between electrical field and thermal field.

As shown in Figure 2-2 (c), the external electrical circuit is connected to the collector terminals and emitter terminals of IGBT module during actual operation. When the chip is turned on, the temperature of the module rises because of power loss. The heating area of the module is concentrated above the DBC ceramic layer. The change of temperature makes the electrical characteristics of materials of the module change, which can change the current distribution of the module, and then affect the temperature distribution of the whole device. Therefore, the entire transient temperature change process of the IGBT module is an electro-thermal coupling dynamic equilibrium process.

There are several differential equations to describe the coupling dynamic equilibrium process in the finite element model. When there is a boundary current source, the expression equation of current in IGBT module is [47]:

$$\nabla \cdot J = \nabla \cdot \gamma(-\nabla \varphi) = Q_i \tag{1}$$

where J and  $\gamma$  are the current density and electrical conductivity, respectively.  $Q_j$  is the boundary current source.

The chips become main heat sources when they are on-state since there is power dissipation. The amount of power per unit volume, also called power density, can be calculated from the results of the current calculation [95]:

$$Q_{\nu} = \frac{1}{\gamma} |J|^2 \tag{2}$$

where  $Q_{v}$  is the power density.

Some material properties of the layers of the IGBT module temperature dependent, especially for electrical resistivity of the chips. In the linear region of output characteristic curve of the IGBT, the resistivity is approximately linear with the temperature [47], as presented in formula (3).

$$\sigma = a \cdot T_i + b \tag{3}$$

where  $T_j$  is junction temperature, a and b are constant.

According to the theory of heat transfer, if the effect of heat source in is considered, the heat transfer equation is [47]:

$$\nabla \cdot (k\nabla T) + Q_v = \rho c \frac{\partial T}{\partial t} \tag{4}$$

where k is the thermal conductivity, T is the temperature,  $\rho$  is the density of the object, c is the specific heat capacity, and t is the time.

The above heat transfer equation is mainly applicable to the main heating region, like the chips. For the non-heat source region such as ceramic layer and baseplate layer, the heat conduction equation is as expressed in formula (5).

$$\nabla \cdot (k\nabla T) = \rho c \frac{\partial T}{\partial t} \tag{5}$$

The electro-thermal coupling effect affects not only the calculation of power loss, but also the accurate description of thermal conductivity characteristics. Therefore, the consideration of electro-thermal coupling effect is the precondition of obtaining accurate temperature distribution of IGBT module.

#### 2.1.3 Transient Solving Process of Multiphysics Finite Element Model

According to the mathematical analysis of electrical-thermal coupling effect, The heat generated in the electrical field is used as the heat source in the thermal field, and the temperature becomes a feedback to the electrical field by the formula (3) until the equilibrium is reached. It is necessary to solve the coupling process in order when the finite element simulation is used to solve the multi-physical field coupling model of IGBT module, as indicated in Figure 2-4.

For the transient state simulation, the outer layer of the solving process is the time iteration, and the inner layer is the convergence iteration of the multi-physical field within each time step. The detailed steps are as follows:

Before numerical analysis, the physical model is built according to the actual size of the IGBT module, and initial material property parameters including temperature-dependent parameters of some materials need to be set in multi-physical field. Boundary conditions in each field also need to be set accurately according to actual operation condition and work principle of the IGBT module.

- 2) The finite element model needs to be divided into multi-level mesh to improve the computational accuracy.

- 3) According to the actual operating current load condition and boundary conditions of electrical field, current and voltage distribution are obtained. The power density calculated in the electrical field is loaded as the heat source in the thermal field. Temperature distribution is obtained by combining the heat source, the heat dissipation condition, and boundary conditions of thermal field.

- 4) Convergence condition needs to be satisfied to end the iteration. If the difference between the results of the last two adjacent calculations do not meet the requirements of accuracy, the number of iterations will be increased and some initial parameters, like conductivity parameters, will be updated in the beginning of new iteration according to the last calculated results. The distribution of electrical and thermal characteristics of the IGBT module can be updated by increasing the iteration times until the calculation accuracy is satisfied.

- 5) Calculation time is set to end the whole calculation at a specific time. If it has not reached the set time, the time step is increase and step 3)~4) are repeated until the calculation is completed. At the end of simulation, the results of simulation can be viewed or processed.

Figure 2-4 The flowchart of calculation of electrical-thermal coupling model.

## 2.2 Electro-thermal Finite Element Modeling of IGBT Module

## 2.2.1 Setting Material Property Parameters

Some important parameters of Infineon FF450R17ME4 is shown in Table 2-1. The physical parameters of some materials in IGBT modules change with temperature, so the temperature

characteristics must be considered. In the model, the electrical resistivity of silicon chips is assumed to change with temperature, while that of other materials is constant. This research focusses on the health condition of the IGBT chips and ignores the effect of the diode chips because IGBT chips are more susceptible to failures compared with diode chips. IGBT chips experience higher thermal stress compared with diodes due to higher turn-on and turn-off power, and IGBT chips own a more complex semiconductor structure compared with diodes which makes IGBT chip less reliable [6].

| parameters                                          | values      |

|-----------------------------------------------------|-------------|

| Rated voltage, $V_{CES}$                            | 1700V       |

| Rated collector current, $I_{C nom}$                | 450A        |

| Thermal resistance (junction to case), $R_{thJC}$   | 0.06 K/W    |

| Temperature under switching conditions, $T_{vj op}$ | -40°C~150°C |

Table 2-1 Parameters of the IGBT module.

| Rated voltage, $V_{CES}$                            | 1700V       |

|-----------------------------------------------------|-------------|

| Rated collector current, $I_{C nom}$                | 450A        |

| Thermal resistance (junction to case), $R_{thJC}$   | 0.06 K/W    |

| Temperature under switching conditions, $T_{vj op}$ | -40°C~150°C |

|                                                     |             |

Figure 2-5 The output characteristic curve of the IGBT chip.

Figure 2-5 displays the typical output characteristic curve of the IGBT chip when the turn-on gate voltage is 15V. 15V is the optimal gate voltage to keep the on-state collector-emitter voltage drop  $V_{CE}$  at a low value and cause less electrical stress in the dielectric region at the same time [96]. Figure 2-5 indicates that on-state collector-emitter voltage  $V_{CE}$  is a non-linear function of the collector current  $I_c$  and the junction temperature  $T_j$  when the turn-on gate voltage is fixed. When  $I_c$  is smaller than the value of the point of the intersection,  $V_{CE}$  decreases as  $T_j$  increases, which means negative temperature coefficient. When  $I_c$  is higher than the value of the point of the intersection,  $V_{CE}$  increases as  $T_j$  increases, which means positive temperature coefficient. The relationship of  $V_{CE}$ ,  $I_c$ , and  $T_j$  can be expressed by equation (6) in theory in the region where  $V_{CE}$  has almost linear relationship with  $I_c$  and has positive coefficient with  $T_j$  [44].

$$V_{CE}(T_j, I_C) = [V_0 - \alpha_1(T_j - T_{j0})] + [R_{CE0} + \alpha_2(T_j - T_{j0})] \cdot I_C$$

(6)

where  $V_0$  represents the threshold voltage drop and  $R_{CE0}$  represents on-state resistance of the IGBT chips at the reference junction temperature  $T_{j0}$ ;  $\alpha_1$  and  $\alpha_2$  are the temperature coefficients for on-state voltage drop and on-state resistance, respectively.

When the collector current  $I_c$  is specified, the equation (6) can be deduced to equation (7), which can be expressed by equation (8).

$$\frac{V_{CE}(T_j, I_C)}{I_C} = \left[\frac{V_0}{I_C} + R_{CE0}\right] + \left[\frac{\alpha_1(T_j - T_{j0})}{I_C} + \alpha_2(T_j - T_{j0})\right]$$

(7)

$$R_{on}(T_j) = R_{on0} + \alpha_3(T_j - T_{j0})$$

(8)

where

$$R_{on} = \frac{V_{CE}}{I_C}$$

$$R_{on0} = \frac{V_0}{I_C} + R_{CE0} = \frac{V_{CE0}}{I_C}$$

$$\alpha_3 = \frac{\alpha_1}{I_C} + \alpha_2$$

and  $R_{on0}$  represents virtual on-state resistance of the IGBT chips at the reference junction temperature  $T_{j0}$ .  $\alpha_3$  is the temperature coefficient for virtual on-state resistance. For a silicon chip, the material difference between the upper and lower layers of the chip is ignored, which can be regarded as a uniform resistance. The resistance of the IGBT chip can be obtained from the output characteristic curve and the formula (8). According to the formula (9), the resistivity of the chip can be obtained.

$$R = \sigma \frac{d}{S} \tag{9}$$

where R is the resistance,  $\sigma$  is the resistivity, and d and S are the height and the area of chips, respectively.

$$\sigma = \sigma_0 + \alpha_3 (T_j - T_{j0}) \tag{10}$$

Equation (10) can be obtained by combining equation (8) and (9). In this study, this linear fitting method is used to describe the resistivity variation of the chip with temperature change in the linear region of output characteristic curve. Figure 2-6 illustrates the temperature dependence of the resistivity of the IGBT chip.

Figure 2-6 Temperature-dependent electrical resistivity of IGBT chip.

Table 2-2 exhibits material parameters of the IGBT module [47, 75, 97, 98]. According to IGBT chip size, the electrical resistivity and temperature coefficient of IGBT chips under different current are calculated in Table 2-3.

| IGBT<br>Module | Material  | Size (mm)   | Electrical<br>Conductivity<br>(S/m) | Thermal<br>Conductivity<br>(W/(m·K)) | Poisson's<br>Ratio | Young's<br>Modulus<br>(GPa) |

|----------------|-----------|-------------|-------------------------------------|--------------------------------------|--------------------|-----------------------------|

| Bond Wire      | Al        | Radius 0.15 | 3.77×10 <sup>7</sup>                | 238                                  | 0.33               | 70                          |

| IGBT           | Si        | 13×13×0.12  | Temp.                               | 148                                  | 0.28               | 170                         |

| Chip Solder    | Sn-Ag-Cu  | 13×13×0.05  | 6.67×10 <sup>6</sup>                | 70                                   | 0.4                | 43                          |

| Copper 1       | Cu        | 32×38×0.1   | 6×10 <sup>7</sup>                   | 401                                  | 0.35               | 110                         |

| Ceramic        | $Al_2O_3$ | 32×38×0.25  | 1                                   | 55                                   | 0.27               | 275                         |

| Copper 2       | Cu        | 31×37×0.1   | 6×10 <sup>7</sup>                   | 401                                  | 0.35               | 110                         |

| DBC Solder     | Sn-Ag-Cu  | 31×37×0.05  | 6.67×10 <sup>6</sup>                | 70                                   | 0.4                | 43                          |

| Baseplate      | Cu        | 122×62×3    | 6×10 <sup>7</sup>                   | 401                                  | 0.35               | 110                         |

Table 2-2 Material parameters of IGBT module.

Table 2-3 Resistivity and temperature coefficient of the IGBT chips.

| I <sub>C</sub> /A       | 90      | 150    | 210    | 270    | 330    | 390    | 450    | 510    |

|-------------------------|---------|--------|--------|--------|--------|--------|--------|--------|

| Resistivity<br>/Ω·mm    | 69      | 47     | 37     | 31     | 27     | 24     | 22     | 21     |

| $V_{CE}$ /V             | 1.23    | 1.4    | 1.54   | 1.65   | 1.77   | 1.89   | 2.00   | 2.11   |

| Temperature coefficient | -0.0001 | 0.0178 | 0.0288 | 0.0359 | 0.0370 | 0.0388 | 0.0392 | 0.0395 |

#### 2.2.2 Boundary Conditions for Multiphysics Finite Element Model

As presented in Figure 2-2, the collector and emitter of the IGBT module are connected to external circuit, and current flows into the collector and flows out from the emitter respectively. Therefore, the coppers connected with the collectors are set as boundary current source, and the coppers connected with the emitters are set as the ground. When the current is loaded into the IGBT module, it flows through the bonding wires, coppers and chips in the module, and the

ceramic layer is set as the insulation boundary in the electrical field due to its low conductivity. Therefore, the layers under the ceramic layer are also electrical insulation.

In actual application, the IGBT module is closely connected with the heat sink through the thermal grease. If the heat sink model is taken into account in the modeling process, it needs to couple flow field with the existed field, which may bring huge amount of calculation. On the other hand, because of the difference of the physical size of the heat sink and the IGBT module is big, especially for the heat sink and the bond wire. For example, the size of the heat sink in usually exceeds 25×15 cm, and the diameter of the bond wire is less than 1mm. Even if different mesh grid method is used for different structure, it still consumes huge computing resources, and lead to non-convergence or less accurate result.

Therefore, the model of heat sink is simplified to equivalent heat transfer function. In the model, the bottom surface of the baseplate is set as the convective heat transfer boundary, and parameters of heat transfer function is obtained according to experiment cooling condition. Because the IGBT module is completely packaged in operation and the silicone gel filling into the package has low thermal conductivity and electrical conductivity which provides thermal isolation and electrical insulation, other surface of the module is set as thermal isolation surface. The bottom surface of the baseplate is the only surface to achieve hear transfer. What's more, it is supposed that there is no relative movement of the layers, and all the materials combine well. Figure 2-7 indicates the boundary condition setting of IGBT module in the finite element model.

Figure 2-7 Boundary conditions of multi-physical field model.

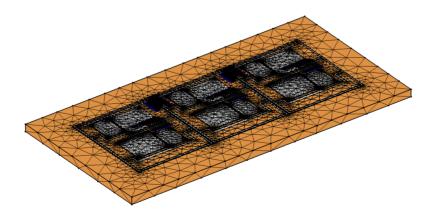

The mesh grid is directly related to the precision and accuracy of the computation results. The IGBT module studied in this research has a large difference in physical dimensions between different parts. If same mesh grid method is applied to different parts, it can lead to low accuracy and precision or the poor computation efficiency. To improve the convergence of the iteration calculation and achieve high accuracy and efficiency, a multi-level mesh grid method is adopted. For smaller parts, such as the bond wires, chips and the solder layers, are divided by fine mesh, while for larger parts, such as copper layer and ceramic layer, the grid is divided by normal mesh. Figure 2-8 displays the mesh grid of the finite element model.

Figure 2-8 3D finite element model of the IGBT module.

## 2.3 Validation of the Multiphysics Finite Element Model

During the operation of the module, only upper bridge leg or lower bridge leg is working. At the same time, IGBT chips is easier to be failure than FWD chips, which makes IGBT chips become the key component to determine the reliability of the module [6]. To reduce the computation time of the finite element model, only the IGBT chip of the upper bridge arm is studied in this research. Considering that IGBT and anti-parallel FWD have one-way conduction characteristic, FWD chips needs to be set as electrical insulation when IGBT chips is conducted. Therefore, the bond wires connected to the top of all FWD chips and the IGBT chips of the lower bridge arm are removed to achieve electrical insulation.

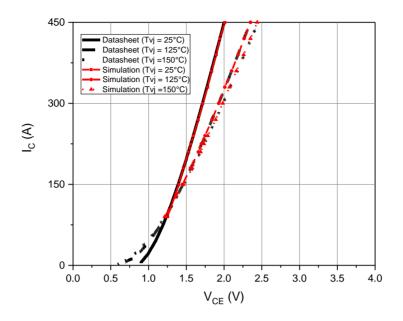

#### 2.3.1 Validation of the Finite Element Model in Electrical Field

To verify the accuracy of the finite element model built in last section, the simulation results of the model and results of the manufacture datasheet are compared under different electrical operating conditions. According to [75], the cooling method for the IGBT module is water cooling method when the module is used in wind turbines as an inverter. The speed of the cooling water is set as 1m/s, and the temperature of the water is 20°C. Thus, the finite element model sets the same cooling water speed and temperature for heat transfer function as initial condition. The current source is set as 90A, 150A, 210A, 270A, 330A, 390A, and 450A, and the cooling condition of the model is adjusted to keep the junction temperature as 25°C, 125°C, and 150°C, respectively, to verify the output characteristics of the IGBT module.

Figure 2-9 illustrates output characteristics curves from datasheet and simulation. Good consistency is observed with voltage error less than 0.03V as the collector current and junction temperature rise.

Figure 2-9 Output characteristics curves from datasheet and simulation.

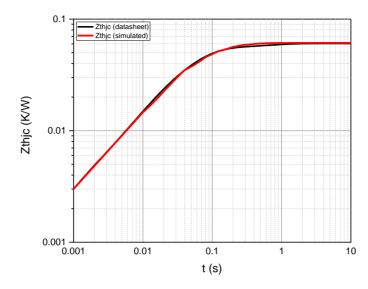

#### 2.3.2 Validation of the Finite Element Model in Thermal Field

The corresponding parameters and boundary are set for the finite element model. Firstly, the transient temperature characteristic of IGBT module is analyzed. The load current is set as 300A. The transient temperature impedance can be calculated according to Equation (11) [84]. The transient temperature impedance curve obtained from simulation is compared with transient temperature impedance curve from manufacture datasheet, as shown in Figure 2-10. The two curves basically coincide, which proves the accuracy of the finite element model.

$$Z_{thjc}(t) = \frac{T_j(t) - T_c(t)}{P_{loss}}$$

(11)

where  $Z_{thjc}$  is transient temperature impedance between junction and case, and  $P_{loss}$  is average dissipated power.

Figure 2-10 Comparison of transient thermal impedance curve from datasheet and simulation.

Before 1s, the transient thermal impedance gradually rises. After 1s, both transient thermal impedance curves enter the steady state. Under the steady state, thermal resistance between junction and case  $R_{thjc}$  can be obtained from Equation (12) [83]:

$$R_{thjc} = \frac{T_j - T_c}{P_{loss}} \tag{12}$$

The calculated thermal resistance value is 0.063 K/W, and thermal resistance value in the datasheet is 0.06 K/W. The simulation result and the datasheet value as shown in Table 2-4. It can be found that the error between simulation result and the datasheet value is small, which is 5%. The error is mainly caused by using the equivalent convective heat transfer parameters instead of the heat sink model. However, the result still confirms that the model has a high computational accuracy for the low error.

Table 2-4 Comparison of thermal resistances from simulation and datasheet.

| Chip | Simulation value | Datasheet value | Error |

|------|------------------|-----------------|-------|

| IGBT | 0.063            | 0.06            | 5%    |

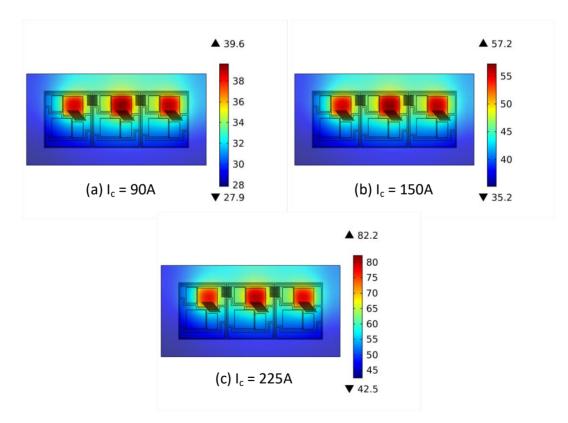

The temperature characteristic of IGBT module at steady state is analyzed. To be compared with the experimental results obtained from [75], the speed of the water is set as 1m/s, and the temperature of the water is 30°C. The conduction current is set to 90A, 150A, and 225A. Figure 2-11 displays the temperature distribution for the module under different current load. It can be found that the high temperature area is mainly concentrated in the surface of the chips and the bond wires at the steady state, and the temperature gradually decreases from the center of the chip to the edge. The junction temperature of the middle chip is the highest because of thermal coupling effect, and the junction temperature of the right chip is higher than the junction temperature of the left chip. As the load current increases, the junction temperature and the case temperature also increase. The corresponding case temperatures are shown in Table 2-5.

Figure 2-11 Temperature distribution of the IGBT module.

According to [75], temperature sensors are installed close to the bottom surface of the IGBT module and the positions are under the center of each IGBT chip to record the case temperature of

each chip. The case temperatures at steady state under different conduction current are monitored by the temperature sensors. The results are collected in Table 2-5.

|      | Current           | Case temperature |                          |                          |  |  |

|------|-------------------|------------------|--------------------------|--------------------------|--|--|

|      |                   | Chip L $(S_1)$   | Chip M (S <sub>2</sub> ) | Chip R (S <sub>3</sub> ) |  |  |

|      | Experiment values | 36.4°C           | 37.8°C                   | 36.7°C                   |  |  |

| 90A  | Simulation values | 36.4°C           | 37.3°C                   | 36.7°C                   |  |  |

|      | Error             | 0                | 1.32%                    | 0                        |  |  |

|      | Experiment values | 49.1°C           | 53.6°C                   | 51.6°C                   |  |  |

| 150A | Simulation values | 51.1°C           | 52.8°C                   | 51.7°C                   |  |  |

|      | Error             | 4.07%            | 1.49%                    | 0.19%                    |  |  |

|      | Experiment values | 67.4°C           | 73.9°C                   | 70.7°C                   |  |  |

| 225A | Simulation values | 69.7°C           | 72.5°C                   | 70.5°C                   |  |  |

|      | Error             | 3.41%            | 1.89%                    | 0.28%                    |  |  |

Table 2-5 Comparison of case temperature obtained from experiment and simulation at steady state.

The simulation results and experiment results of case temperature under different conduction current are shown in Table 2-5. The simulation results and experiment results indicate the same trend that the middle chip has the highest case temperature, and then the case temperature of the right chip is a little bit higher than the case temperature of the left chip. When the conduction current is 90A, the error only appears in the middle chip (S<sub>2</sub>). There is  $0.5^{\circ}$ C difference between the simulation result and the experiment result, and the error is about 1.32%. When the conduction current is set as 150A and 225A respectively, the maximum error appears in the left chip (S<sub>1</sub>) and the highest one is 4.07%, which is still in the acceptable range of the accuracy. This is because that the simulation sets up ideal current excitation and heat dissipation conditions, while the experiment result is affected by the environment condition and the measurement accuracy of the temperature sensor, etc. Therefore, it is inevitable to deviate from the simulation value.

The above results illustrated in this section verified the validation of the finite element model in electrical field and thermal field. It can be concluded that the model established in this research has high accuracy and is effective to obtain the electrical-thermal characteristics of the IGBT module, and it can be reliable support for follow-up research.

# 2.4 Summary

Compared with thermal analysis in isolated electrical field and thermal field, thermal analysis by building electro-thermal FEM is more accurate. In this chapter, an electro-thermal coupling FEM of multi-chip IGBT module is firstly established, which considers the temperature dependent electrical resistivity of IGBT chips and simplify the heat sink model to equivalent convective heat transfer equation.

Secondly, the validity of the model is verified by calibrating the output characteristic curve and transient thermal impedance curve from datasheet. The deviation of simulated collectoremitter voltage from the manufacture data as the collector current and junction temperature rise is less than 0.03V. There is good consistency between the simulated transient thermal impedance curve and the curve from datasheet. Moreover, the thermal resistance calculated by the simulation model is close to the original data, the maximum error is 5%.

In addition, the temperature distribution of the electro-thermal FEM is close to the measurement results of the experiment. The maximum error of the case temperature appears in the left chip  $(S_1)$ , which is 4.07% when the conduction current reaches 225A. All the error is within an acceptable range for ideal current excitation and heat dissipation condition of simulation, and measurement error of experiment.

The FEM established in this paper will provide a strong support for the electrical and thermal analysis of the multi-chip IGBT modules and precursors extraction in the following chapters.

# **Chapter 3 Precursor for Chip Solder Fatigue**

As IGBT module is a multi-layered structure of materials with different coefficient of thermal expansion (CTE), it experiences repetitive thermo-mechanical stresses during switching operations under harsh environment and temperature swings. Different failure modes such as solder fatigue, wire bond lift-off and wire bond heel cracking can be caused by this thermal-mechanical stresses. A study indicates that chip solder cracks occurs because of the thermo-mechanical stresses generated by mismatch of the CTE between the silicon chip and the substrate when the fluctuation of the junction temperature ( $\Delta T_j$ ) between maximum value of T<sub>j</sub> (T<sub>j max</sub>) and maximum value of T<sub>j</sub> (T<sub>j min</sub>) is less than 80°C, and wire bond heel cracking occurs when  $\Delta T_j$  is more than 100°C [23]. Because  $\Delta T_j$  region of most power modules is lower than 100°C, the solder degradation appears early than bond wire degradation, and becomes the dominant failure mode [23, 47]. Moreover, if there is solder fatigue, because of change of heat transfer path and increase of thermal resistance, the bond wire degradation will be accelerated [23, 47, 99]. Thus, this research extracts precursor to evaluate the health condition of multi-chip IGBT module with a focus on the IGBTs' chip solder fatigue.