# Charles University in Prague Faculty of Mathematics and Physics

# **MASTER THESIS**

# Vlastimil Babka

# Influence of Resource Sharing on Performance

Department of Software Engineering Supervisor: Doc. Ing. Petr Tůma, Dr. Study Program: Computer Science, Software Systems I would like to thank my supervisor, Doc. Ing. Petr Tůma, Dr., for his valuable support and advice.

Prohlašuji, že jsem svou diplomovou práci napsal samostatně a výhradně s použitím citovaných pramenů. Souhlasím se zapůjčováním práce.

I hereby declare that I have elaborated this master thesis on my own and listed all used references. I agree with making this thesis publicly available.

Prague, August 9, 2007

Vlastimil Babka

## Contents

| 1 | INTRODUCTION                                       |    |

|---|----------------------------------------------------|----|

|   | 1.1 Benchmarking and Resource Sharing              |    |

|   | 1.2 Goals                                          |    |

|   | 1.3 Structure of the Thesis                        |    |

| 2 | SHARED RESOURCES                                   | 12 |

| 4 | 2.1 Processor Memory Caches                        |    |

|   | <ul><li>2.1 Processor Translation Caches</li></ul> |    |

|   | 2.3 System Memory                                  |    |

|   | 2.4 Heap Management                                |    |

|   | 2.5 File systems                                   |    |

|   | 2.6 Summary                                        |    |

| 3 | BENCHMARKING EXPERIMENTS                           | 10 |

| 5 | 3.1 The benchmarking framework                     |    |

|   | 3.1.1 Mode of operation                            |    |

|   | 3.1.2 Time measurement                             |    |

|   | 3.1.3 Performance counters                         |    |

|   | 3.1.4 Hardware platforms and experiment template   |    |

|   | 3.2 Processor caches                               |    |

|   | 3.2.1 Trashing procedure                           |    |

|   | 3.2.2 Benchmarking framework overhead              |    |

|   | 3.2.3 Artificial benchmarks                        |    |

|   | 3.2.4 FFT                                          |    |

|   | 3.2.5 LZW                                          |    |

|   | 3.2.6 Transcode                                    |    |

|   | 3.3 File systems                                   |    |

| 4 | EVALUATION AND APPLICABILITY OF THE RESULTS        |    |

|   | 4.1 Reducing benchmarking infrastructure overhead  |    |

|   | 4.2 Performance models                             | 67 |

| 5 | Related work                                       |    |

| 6 | CONCLUSION                                         |    |

| U | 6.1 Open issues and future work                    |    |

| _ | -                                                  |    |

| 7 | References                                         |    |

Název práce: Vliv sdílení prostředků na výkon Autor: Vlastimil Babka Katedra: Katedra softwarového inženýrství Vedoucí diplomové práce: Doc. Ing. Petr Tůma, Dr. e-mail vedoucího: <u>petr.tuma@mff.cuni.cz</u>

Abstrakt: Sdílení prostředků nastává v případech, kdy několik současně aktivních procesů či softwarových komponent využívá stejné systémové prostředky, což ovlivňuje výkon v porovnání s individuálním během. Izolované měření dob trvání klíčových operací pro řešení modelů predikce výkonu tudíž může přinášet nepřesné výsledky. Sdílení prostředků také nastává mezi měřeným kódem a měřící infrastrukturou, která sbírá a ukládá výsledky, což nepřímo zvyšuje její režii.

Tato práce kvantifikuje vlivy sdílení na výkon pro několik často sdílených prostředků, jmenovitě procesorových caches a souborových systémů. Horní odhad možného ovlivnění výkonu sdílením caches je stanoven pomocí syntetických testů. Účinky na praktický kód a jejich závislosti na různých faktorech, jako frekvence a intenzita trashování cache, jsou poté změřeny pomocí experimentů s existujícími implementacemi algoritmů FFT a LZW a aplikací pro zpracování videa. Efekty sdílení souborového systému na rychlost jsou změřeny pomocí experimentů provádějících hromadný zápis a čtení z několika souborů. Za určitých okolností lze pozorovat významné dopady sdílení u každého z uvažovaných prostředků.

Na základě výsledků těchto měření je nadále navrženo několik rad pro řešení problému režie měřící infrastruktury. Také je zde diskutována použitelnost provedených experimentů a jejich výsledků pro účely modelování výkonu.

Klíčová slova: sdílení prostředků, měření výkonu, modelování výkonu, procesorové cache, souborové systémy

**Title:** Influence of Resource Sharing on Performance

Author: Vlastimil Babka

**Department:** Department of Software Engineering

Supervisor: Doc. Ing. Petr Tůma, Dr.

Supervisor's e-mail address: petr.tuma@mff.cuni.cz.

**Abstract:** Resource sharing occurs when multiple active processes or software components compete for system resources, which influences the observed performance compared to an individual execution. Isolated benchmarking of durations of key operations for solving of performance prediction models may therefore yield imprecise results. Resource sharing also occurs between the measured code and the benchmark infrastructure for obtaining and storing samples, imposing an indirect overhead.

This thesis quantifies the effects of sharing on performance for several resources that are often shared, namely the processor caches and the file systems. The highest possible performance impact of cache sharing is determined by synthetic benchmarks. Impact on practical code and its dependency on a number of factors such as cache trashing frequency and intensity are then determined by experiments with existing implementations of FFT and LZW algorithms and a video stream processing application. Effects of file system sharing are measured by experiments that read and write multiple files simultaneously. For both resources, situations with significant performance impact of sharing have been observed.

Based on the results of the experiments, several suggestions for dealing with the overhead of performance monitoring infrastructure are proposed, and applicability of the experiments and their results for performance modeling is discussed.

**Keywords:** resource sharing, performance evaluation, performance modeling, processor caches, file systems

## 1 Introduction

Performance is one of the key properties of software systems. Not only does the code have to be correct, it should also execute reasonably fast to be of practical use. The observed performance is determined by complexity of the individual algorithms, efficiency of the code implementing them, the architecture of the whole system, and the performance of the platform the system is being deployed on.

While complexity of the algorithms can be theoretically analyzed and performance of the system architecture predicted by modeling, the usual method of determining performance of the resulting code on a given hardware is empirical, relying on benchmarking experiments. Possible goals of benchmarking include comparing speed of hardware or competing software implementations, detecting performance regressions between versions during development, or determining durations of atomic operations for performance modeling of the system being designed.

Obtaining results applicable for these purposes becomes tricky when conducted on modern hardware and operating systems. The performance observed in such a complex environment is influenced by various factors. One of them is resource sharing, which occurs when multiple processes or parts of the same process compete for the same hardware or operating system resource. This can prolong their execution. The aim of this thesis is to examine the impact of resource sharing on code performance and the influence this has on performance modeling and monitoring.

#### 1.1 Benchmarking and Resource Sharing

The simplest way to evaluate the overall performance of an application (or the system that is executing it) is to measure the time to complete the whole task. This is suitable for applications performing relatively long tasks that require no interaction, such as file compression. In order to obtain reproducible and comparable values, the measurement is often performed on a freshly installed and booted system, and in a dedicated configuration, with practically no other interfering processes running. The experiment is repeated a number of times, discarding values obtained during the warm-up phase. The typical duration is then calculated from the remaining samples as an average, median, or using more complex approach [15].

The important question is whether the results obtained during such isolated execution really represent the performance in the target environment of the application. During the benchmark, the measured task is the only significant workload in the system, virtually no other processes can be scheduled during its work and influence its performance by resource sharing. The task can therefore take advantage of all available memory and processor caches, and has exclusive access to files or network interfaces. During the warm-up phase of the benchmark, caches and buffers are pre-filled with the task's data, and various heuristic algorithms present in modern systems can adapt to the task's resource usage patterns. This might naturally cause the task to perform better than when executed in a real environment.

This difference between the individually measured and the real performance can for example result in a wrong deployment decision. Consider two processors of the same microarchitecture where the first has a higher frequency and the second has larger caches. A task with working set that fits just in the caches of the first processor will perform faster on that processor when measured individually, but sharing the caches with other tasks when in real use can result in faster performance on the processor with larger caches.

In many cases, only durations of relatively short operations are being measured instead of the whole application's performance. These operations are usually part of a complex software system, which cannot be measured in its entirety for various reasons. Some systems inherently cannot have a simple global performance indicator such as throughput or service round-trip, and a set of representative operations has to be chosen, for example duration of a remote method invocation or marshalling for CORBA implementations benchmarking [31], or duration of TCP Ping or HTTP Ping for MONO regression benchmarking [16].

In the case of performance modeling, the entire system cannot be measured because it is obviously not fully implemented, as there would be not much use for performance modeling otherwise. For models based on interaction of components through atomic actions, benchmarking is used to measure durations of these atomic actions in prototype component implementations in order to solve the model [17][20][21][32].

Benchmark experiments with these short operations are often performed in isolation [21], with no parallelization [32] or with a fixed degree of parallelization [20]. However, in the target environment, these operations would compete for resources not only with other processes, but also with operations performed by the same process. These operations could be executed either in different parallel threads, or in the same thread, which may influence the results. For example, if a component's function invocation is interleaved with different function invocations, its code and data may be evicted from the caches upon invocation and thus its duration would significantly differ from the duration when measured alone. Results from the performance model populated with durations obtained with none or different parallelization, or omitting code that would be interleaved with the measured durations inside a same thread, would therefore become inaccurate.

To improve the precision of performance models, the durations of the function invocations used to solve the model would have to be measured under the same conditions as in the fully implemented and running system, which is not yet available for this purpose. Another approach would be to include resource sharing into the performance model. This would however increase the complexity of the model, and could be infeasible for resources that have no precise performance models, or have a model based on a different formalism than the performance model of a software system. Because of these obstacles, resource sharing is often simply omitted [20][21][32], or mentioned as high cost [17]. However, intuition suggests that the effect of resource sharing on model precision could be significant, and this thesis should prove that.

In benchmarks that resemble whole software systems, such as transaction processing applications in TPC [29], or an auction site prototype in RUBiS [28], performance sharing should be captured well, because everything that would use resources in the real system is executed as part of the benchmark. However, we think that care should be taken when preparing environment for these benchmarks, e.g. populating the database and creating images of products in the auction site. Doing

this at once may result in less scattered and fragmented files compared to a real scenario where the data is inserted, deleted and modified over a longer period of time.

Another situation where resource sharing may influence the results of benchmarking comes from the fact that the benchmark infrastructure for obtaining and storing the results of measurements also shares resources with the measured code. The code that captures and stores timestamps in the memory may trash the code and data caches, writing large results in files may interfere with usage of files by the measured system. This problem is important especially in the case of detailed performance monitoring and code profiling, where the measured code is interrupted and results collected relatively very frequently. Due to resource sharing, the overhead of the infrastructure code is not additive – we cannot simply measure the whole task duration with and without detailed monitoring, and determine the overhead by subtracting the results.

### 1.2 Goals

This thesis aims to address some of the problems with benchmarking due to resource sharing described in the previous section. The first goal is to analyze what resources are most frequently shared and how this sharing can influence performance. We will consider a scale of resources from the processor caches to the file systems.

The second and most important goal is to quantify the effects of sharing empirically, using specially designed benchmark experiments. Our aim is not to determine absolute values like durations of a function invocation with and without shared cache – these values would likely be too specific to the benchmark scenario and the hardware platform executing it to be of direct use in e.g. performance models. Rather than the absolute values, we want to determine resources and situations where sharing influences performance significantly and thus should not be ignored.

Our third goal is to analyze possibilities of applying the results obtained from the experiments to remedy the problems with resource sharing in benchmarking described earlier. Namely, we will discuss possible ways to reduce or deal with the observed resource sharing effects in the overhead of performance monitoring infrastructure, and to incorporate resource sharing into performance models.

#### **1.3 Structure of the Thesis**

With respect to the outlined goals, the structure is as follows.

Chapter 2 gives an overview of resources that are often used and therefore shared in software systems. We analyze how these resources work, the expected forms of sharing, and propose methods to quantify the effects of such sharing empirically. We proceed by choosing several of the resources for further experiments.

In Chapter 3, we introduce the framework designed and implemented to measure effects of resource sharing. Then, for each benchmarked resource, we describe the design of each benchmarking experiment in detail, with both expected and obtained results and their evaluation.

Chapter 4 evaluates the impact of the resource sharing observed in the experiments and proposes several advices for reducing the benchmarking

infrastructure overhead. Related work is discussed in Chapter 5, with Chapter 6 concluding the thesis, proposing possible tasks for future work.

## 2 Shared Resources

Computers consist of various hardware subsystems, each providing some needed functionality, also called resource. Code executed on the computer is using these resources to perform its work, some of them inherently (processor, memory), some of them usually explicitly (disk, network). One of the roles of operating systems is to abstract these hardware resources, and allow them to be used by several processes simultaneously. To facilitate this, an operating system creates and maintains own virtual resources – file systems, network sockets, virtual memory tables and so on. Similar kind of resources can be provided by runtime libraries to the running process – heap management and garbage collection, remote procedure calls and other middleware services etc.

System resources are always limited in some way, which can cause performance impact when they are being shared. One of the limitations is the amount of the resource, e.g. memory or cache size, network bandwidth. Multiple processes can use such resources simultaneously, but once the limit is saturated, processes are swapped out of memory, get their cached data evicted, or have to share bandwidth.

Another kind of a resource limitation is the need for exclusive usage. The best example of this would be a single-core processor without hyper-threading. Multiple tasks have to be scheduled for execution. The total time to execute those tasks could be naively calculated as sum of durations of each task when executed alone. But there will be certain overhead caused by the scheduling algorithm, sharing of processor caches and other reasons.

On modern hardware and operating systems, high performance is achieved not only by high clock rates, but also via sophisticated optimizations such as caching and branch prediction in the processor, buffer cache for files, often with read-ahead prefetching and delayed writing, and other heuristic algorithms. Because these optimizations dynamically adapt to the execution patterns of the running task, frequent switching between multiple tasks can render them to perform less optimally.

The next sections discuss several selected resources with details on their usage, expected behavior under sharing, and basic methods that could be used to measure effects of sharing. The resources are roughly sorted by their position on an imaginary hierarchy building from the physical resources of hardware up to the virtual resources of the operating system and applications.

## 2.1 Processor Memory Caches

A CPU Cache is a memory buffer located between the CPU and the system memory, used to achieve smaller average latency or memory accesses. This is increasingly important in modern systems, where memory access is often a performance bottleneck – many processor cycles are wasted (stalled) when waiting for memory transfers. Caches are much faster and closer to the CPU (often on-die) than the system memory and therefore have significantly lower latency. The downside is that caches are expensive, which limits their possible size. Because of this, a cache can store only small portion of system memory, divided to cache entries (also called lines) tagged with the memory addresses of the stored data. A memory access that requests data present in the cache is called a cache hit. A request for data not

currently present in the cache is called a cache miss. In this case a whole block of data the size of cache line, which contains the requested address, is fetched from the system memory and stored in a selected cache line, replacing (also called evicting or trashing) the victim data currently stored there. A common method is to keep least recently used entries, assuming the executed code will be accessing these cache lines again relatively soon.

To determine if the requested data is in the cache, all entries that can contain the requested address have to have their tag compared to the address. Since comparing many tags would need too expensive hardware to be done at once, or would be too slow when done sequentially, there may be only limited amount of cache entries that each memory address can map to, using some form of hash function applied to the virtual or physical memory address. This is called associativity [12]. Fully associative caches can map each memory address to any cache entry, while direct mapped caches can store each memory address in exactly one cache entry. Set associative caches have their entries grouped to sets with a fixed number of entries (called ways) per one set. Each memory address maps to exactly one set, but the data can be stored in any of the ways inside the set. Current processor caches are mostly 2-way, 4-way, sometimes 16-way set associative. Cache replacement algorithms, often approximation of LRU, are used to choose the way inside a set that will be replaced with the newly fetched data.

There are usually more caches than one located between the CPU core and the memory, organized in hierarchy of 2-3 levels, with smaller and faster caches closer to the CPU and larger but slower caches closer to the main memory. The first level usually consists of separate code cache and data cache. The code cache is sometimes implemented as a trace cache [27] that stores decoded instructions rather than unmodified copy of the fetched memory. The level 2 (and higher) cache is unified and can therefore contain both code and data. In the case of miss in the L1 code or data cache, code or data is fetched from the L2 cache (or from the system memory if it misses also in the L2 cache) and stored in L1, which thus duplicates subset of L2 cache the same way L2 cache duplicates subset of the main memory (inclusive design). Recent AMD processors use different, exclusive approach, where the code or data can be stored only in at most one cache. When a cache line is being fetched from the L2 cache or the system memory, the entry that is replaced in the L1 cache is transferred back to the L2 cache. In both cases, the transfer from the L2 cache back to the system memory needs to be done when the copy of the data in the caches has been modified.

As stated above, caches improve performance by lowering average latency of memory access. The efficiency of caches depends on the amount of cache hits and misses in each level of the hierarchy – best performance is gained when all memory accesses result in the L1 cache hit, worst performance occurs when all data has to be fetched from main memory as a result of the L2 cache miss. For a code that is executed alone, cache misses can be divided into three groups (paraphrasing [12]):

I compulsory misses – occur when a cache line is accessed for the first time and therefore cannot be cached yet

I capacity misses – caused by cache size being too small for the memory footprint, even if it was direct mapped

I conflict misses – caused by the limited associativity which maps more addresses to one set than fit the number of ways in the set

When multiple tasks are executed simultaneously on the same processor and thus sharing its caches, each task can evict cache entries of other tasks by replacing them with its own code or data, resulting in increased number of capacity or conflict misses. This effect, called cache trashing, can obviously occur when the processor has hyper-threading or multiple cores sharing the same caches and a number of threads is thus executed truly in parallel. The effect of cache trashing on hyper-threading has been studied for example in [13].

With respect to the goals of this thesis, we will focus on a different scenario, without true parallelism, where trashing is caused by task switching due to process scheduling or switching of different operations inside one process or more cooperating processes. To measure effects of such trashing, we need to design benchmarking experiments that would interleave execution of some measured workload with a procedure that will artificially trash given amount of data or code from the caches. By varying the size and frequency of trashing and comparing the time needed to execute the measured code, we can quantify performance impact of cache sharing on the particular code.

### 2.2 Processor Translation Caches

A page-translation cache (also called translation-lookaside buffer, or TLB for short) is an important unit in processors using virtual memory addressing. On such architectures, the address of each instruction or data reference needs to be translated to physical addresses in order to be accessed in the system memory. A TLB is an associative cache, storing the virtual to physical memory mapping for a fixed number of (usually least recently used) memory pages.

Successful queries to the TLB (called hits) are considerably faster than actions that need to be performed if the address is not found there (a TLB miss). The missed mapping is then either looked up in the page table hierarchy automatically by the hardware (the faster case, used for example by processors of the Intel IA-32 architecture), or need to be handled by the operating system (used for example in the MIPS family of processors). The result of the lookup is then stored in the TLB and the instruction that referenced the memory address can continue to be executed, but with significant delay.

The effect of TLB sharing should be roughly similar to the memory caches, because the size of TLB is also limited and the executed tasks compete for them. Additionally, on some architectures including IA-32, each context (address space) switch results in TLB being completely emptied, except for entries set as global by (and practically reserved only for) the operating system. This needs to be done, because different processes have different mapping and the TLB on these architectures is not designed to keep any address space identification with the mappings.

The experiments for quantifying the effect of TLB sharing will be also similar to the memory caches, interleaving the measured workload with code that will artificially replace the TLB entries by accessing different memory pages.

#### 2.3 System Memory

The code and data of all running tasks, including the operating system, share the system memory. If the memory gets filled up, the system uses secondary storage (usually hard disk drive) to swap out data that was not recently used, and fetches it back in when it is needed again. This process is very slow compared to memory access – much slower than system memory latency compared to the processor caches. If swapping occurs frequently because the working set of the executed code does not fit, performance is reduced drastically, which is called thrashing. Benchmarking this scenario thoroughly is not so interesting, because practically it is something highly undesirable and avoided as much as possible.

Thus, there are not practically only two possible states. The first state is when everything fit in the memory and runs optimally, and the second with frequent trashing. Performance prediction can thus simply compute sum of memory occupation of all components and compare it with the available memory size.

Since the system memory is also used to buffer data from files, the amount of available memory can also affect the performance of file operations. This will be discussed in the section about file systems.

#### 2.4 Heap Management

Most applications that allocate objects of varying sizes dynamically in memory use heap for managing the allocations and deallocations. Sharing the heap increases its size and therefore possibly increases the duration of the heap operations. Dynamic allocation also causes some memory fragmentation, which could potentially increase through sharing because the multiple components sharing the heap can increase the diversity in size of the allocated objects. This may result in the combined memory usage to be higher than the sum of usages of individual components. There are two types of heap which we will discuss separately. The first type requires explicit object deallocation, the second type uses garbage collection to detect and free the unused objects automatically.

Because contemporary allocators with explicit deallocation have close to O(1) complexity and low fragmentation [19], the performance of the heap operations should be significantly affected neither by the heap size nor by the number of components. We thus probably do not need to focus on this type of allocation.

For allocators with garbage collection, memory allocation costs nothing if the collector is compacting, which also eliminates fragmentation. Because deallocation is not done explicitly, performance is affected only by the execution of garbage collection. This is performed asynchronously, usually when the heap size limit is reached, and the total performance impact depends on the frequency and duration of the collector runs. Note that the impact can be both direct – running the garbage collections consumes CPU cycles, and indirect – due to the cache sharing affecting performance of the interrupted code.

The performance impact of garbage collection has been studied in [18]. The indirect impact has been found to be negligible. On the other hand, the direct impact can be significant and cause over 100% slowdown in the worst case. The authors have also observed that the impact depends mostly on the frequency of garbage collection runs and less on the heap size. The duration of individual garbage collections grows roughly linearly with heap size and with the number of objects, but

the decreased frequency thanks to larger heap size reduces the total cost garbage collection significantly.

We can therefore conclude that it is important to include the garbage collection overhead during benchmarks. Individual benchmarks of components using large enough heap size may complete without any collection performed, tampering with the precision of such results for performance prediction. A possible way to include the overhead would be to limit the heap size to reflect the portion of memory available to the component when running in the target environment, which would result in the frequency to be similar. After the overhead for individual components is known, the combined overhead could be determined easily because of the linear dependency of the duration of the garbage collection on the heap size and the number of objects.

#### 2.5 File systems

Files, organized in file systems, are a frequently used resource for storing permanent data used by the applications. In contrast to the compact resources described earlier, files are a complex abstract resource provided by the operating system, which is backed by many individual but related resources. These resources are described below together with expected effects of sharing.

*Directory structure*. File systems are traditionally organized into trees of directories. Each directory may contain additional subdirectories and files, together called directory entries. A large number of entries in a directory may affect file system performance when working with files in that directory, which therefore can be considered a shared resource. This effect depends on the data structures that the particular file system uses to represent the directory, which may for large directories influence the performance by a factor of 50 - 100 [6].

*System memory.* Another resource occupied by files is the system memory. Each opened directory or file is represented by a kernel structure allocated in memory in order to hold its metadata. Free memory (not occupied by applications) is also used for *buffer cache* that stores the file data that was recently read or written in order to take advantage of data locality. The operating system may also detect sequential reading and perform a read ahead to prefetch data that is likely to be used in the near future. Similarly, writes can be delayed, the data accumulated in the buffer cache and later flushed to the disk in larger blocks.

Naturally, more memory available to buffer the data of a file can result in better performance, and working with several files simultaneously can reduce the amount of memory available for each file. This amount is also limited by the memory occupied by running applications, which makes this kind of resource sharing even more complex. Many buffer cache replacement algorithms exist to decide what pages to evict from the memory when a free page is needed. One of the most known is the WSCLOCK [7], an approximation of LRU.

Note that too aggressive buffer cache may even cause the application code and data to be swapped out and result in thrashing [23]. Another interaction exists between the prefetching and buffer cache replacement efficiency [5].

Hard drives. Files are typically stored on a hard disk, which is a very slow resource compared to the processor and main memory. It has its own hardware

buffer, which works similarly to the buffers in main memory (performing read-ahead and delayed write), but has much smaller size (typically 8 - 16 MB). Hard drives have limited read and write speeds, typically tens of megabytes per second, thus simultaneous read or write requests may get queued and the processes performing them are blocked unless they can perform other tasks in the meantime. The main bottleneck of hard drives is the latency of seek, which is the time needed for the disk to position its head to the cylinder containing the requested sector (few milliseconds for contemporary drives). This time depends on the distance between the current and the desired head position. Because file systems try to organize file data in a minimal number of continuous fragments, sequential reading or writing of one file is not affected much by seek latency. But random accesses to a large file which spans many cylinders, or simultaneous accesses to a number of files result in significant seek latencies, affecting performance greatly.

Creating continuous files is easiest when the file is being written alone and the disk has enough space. However, writing more files simultaneously can result in the fragmentation of the data. The amount of fragmentation also depends on the particular file system implementation and amount of free space. File fragmentation can have residual effect on performance – future reading of fragmented files can result in more seeking, even if the reading is sequential and one file at a time.

## 2.6 Summary

We have discussed some of the most shared resources and the expected causes of performance impact due to sharing. We will now select some of the resources for benchmarking experiments that will quantify the expected sharing effects empirically:

- Processor caches Both translation and memory caches promise significant sharing effects and their sharing is inevitable because all code uses them for their operations. To quantify the effects of sharing, we will interleave the execution of measured workload with code that will artificially trash the caches by accessing or executing data or code located in a different memory region that the working set of the measured code.

- File systems Working with multiple files simultaneously should yield significant slowdown compared to working with one file, because it increases the seek rate and the latency of a seek is relatively high. To determine the slowdown, we will interleave the reads or writes of a file with the same operations on different files and compare the measured duration with duration of operations performed individually. Files used for reading will be also created either by separated or interleaved writes, to measure the residual effect of file fragmentation.

The resources we will not experiment with and the reasons for this decision are listed below:

• System memory – The effects of exceeding the available memory with working sets of active operations are already known to degrade performance drastically and are avoided at all costs. Prediction of memory usage of the whole system

from the memory occupation of individual components is simple, even if pessimistic.

• Heap management – Heap operations in heaps without garbage collection should not exhibit resource sharing effects. The overhead of garbage collection has been already studied and found to be significant for some workloads, but we believe that predicting overhead of the whole system from the overhead of individual components should be simple.

## **3** Benchmarking experiments

In this chapter, we will design and execute experiments to quantify effects of sharing on the resources we have selected in the previous section – processor caches and files. To achieve this, most of our experiments will be interleaving the execution of two separate operations – the first is the measured workload, the second is artificially trashing the given resource. Both will have parameters, affecting their use of the resource. Benchmarking with different combinations of these parameters would show their effects in detail.

## 3.1 The benchmarking framework

For the purpose of our experiments, a simple benchmarking framework called RIB has been designed and implemented in C++ and Linux environment. Individual benchmarks incorporated to this framework have to provide unified description of their parameters and interface to prepare and invoke their operation. Some of the benchmarks were implemented specifically for the purpose of the experiments, and a number of existing implementations of standard algorithms was incorporated via wrappers providing the needed interfaces.

### 3.1.1 Mode of operation

The operation of the framework is controlled by a experiment description file which specifies two workloads to be run (the second can be specified as none) as well as values for their parameters, which can be a single value, set of values, or a range of values with linear or exponential step. There are also two general parameters, determining the number of repeat in a single run, and number of values to discard during the warm-up phase.

After the framework is executed, it will perform the measurements with all possible combinations of the parameters' values. This means that for each combination of the values chosen from supplied sets or ranges, the measurement is performed repeatedly as many times as specified, storing the results in a preallocated memory array. Then the next combination of parameters is chosen and executed. When all combinations are exhausted, the framework flushes out the obtained samples to the results file and exits. Further repeated executions of the framework append their new samples.

Because performance is affected by the initial random state upon execution [15], we will obtain relatively low number of samples per run, repeatedly executing the benchmark many times to reduce the initial state impact. This is especially important for the cache experiments, where the virtual to physical address mapping, performed by the operating system in a non-deterministic way, can affect the number of cache misses greatly.

#### 3.1.2 Time measurement

All experiments we will perform need to measure time to complete some operation. Because this operation can be very short (only few microseconds), we need a precise timing method. Although it is usually possible to measure with less precise timing by executing the operation multiple times, and calculating the average, we cannot use this approach here. Because we interleave the measured workload with trashing which has no fixed duration (the influence of cache sharing is mutual), we would not be able to separate the duration of trashing from the whole duration precisely. Also, average timing involves a loss of potentially interesting information.

The precision offered by the operating system calls is not enough. Linux increments its internal clock by the value of a so-called jiffy. On the IA-32 platform, this value is determined by the frequency of timer interrupts, which defaults to 100 and can be raised to 1000, which corresponds with a milisecond precision. This determines the precision of the times(2) syscall, which has the advantage of accounting time per process and distinguishing user and kernel mode. The *gettimeofday*(2) syscall provides only real-time timing, with theoretical microsecond precision. However, the real precision is also based on jiffies, and may be extended by interpolation. The actual implementation varies with Linux kernel versions and the presence of optional hardware such as HPET timers.

Fortunately, modern IA-32 compatible processors come with an elegant solution to this problem, providing own timestamp counter (TSC). This is a special register incremented with each CPU clock cycle, thus giving the ultimate precision. The measured values can be divided by the processor frequency to obtain the real time duration. Only care must be taken so that the BIOS or operating system is not configured to dynamically adjust the frequency on demand. The TSC is easily accessible by a special instruction RDTSC, which can be executed in user mode and stores the result into general registers. Thus, in our experiments we will use RDTSC timing wherever possible.

#### **3.1.3 Performance counters**

Aside from measuring time, we can also take advantage of several more performance counters implemented in modern processors. These counters can be used to collect various events inside the logical units of the CPU, such as floating-point operations, registers usage, memory access details, branch prediction efficiency etc. The set of available counters is different for each processor family and even revision. Obviously, the most interesting for our experiments are the counters related to the TLB and the caches, in particular number of hits and misses in the TLB, the L1 data cache, the L1 code cache and the L2 cache.

Unfortunately, using these counters is not as simple as executing the RDTSC instruction to obtain the value of timestamp counter. The processor does not collect all of the supported events automatically, but there is a limit on the number of events that can be collected simultaneously, and these events have to be selected beforehand. Additionally, some combinations of events can be impossible. The instructions for setting the events and reading of the results can only be executed in kernel mode and thus needs special syscalls to be used from user mode. Although the Linux kernel does not have such support natively, it can be added via the Perfctr [26] patch. The PAPI library [25] provides a portable user interface to performance counters, using platform-specific backends (e.g. Perftctr on Linux and Intel compatible processors).

PAPI can work with two kinds of performance events, native and preset. Native events are directly provided by the processor, and there is a utility to detect which events are available. Preset events is a set of predefined events that should be supported on most of processors, either mapped directly to some native event, or calculated using two or more different native events. For example, the number of the L1 data cache misses events can be calculated by subtracting the number of the L2 data cache misses from the number of total data cache misses. This means the limit of events counted simultaneously can be lower when using preset events.

Additionally, during first experiments with PAPI we have found that some preset events give clearly wrong results on the Athlon 64 processor - PAPI was not mapping them correctly to native events. The actual mapping also is not documented. Thus, we will use only native events. Care must be taken to read the events description in the processor documentation properly, to interpret the results correctly. There can be subtle details, like hardware prefetching and speculative accesses resulting in extra cache hits or misses that can distort the results.

Because the calls to the PAPI functions are not as trivial as the RDTSC instruction, they cost more CPU cycles and could potentially trash some code or memory cache. We will measure the overhead experimentally.

#### **3.1.4** Hardware platforms and experiment template

The rest of this chapter presents in detail each of the performed benchmark experiments for given shared resource. The platforms used to run the experiments are described below.

- Platform 1: AMD Athlon 64 3000+ Venice DH7-CG 1.8 Ghz with exclusive 64 KB data L1, 64 KB code L1, 512 KB unified L2 caches; 2×512 MB dual-channel DDR RAM; Hitachi Deskstar T7K250 250 GB, 7200 rpm, 8 MB buffer, SATA-2 without NCQ; Gentoo Linux with 2.6 kernel, gcc 3.4, ext3 file system

- Platform 2: Intel Pentium 4 Northwood 2.2 Ghz wich inclusive 8 KB data L1, 12 Kops L1 trace cache, 512 KB unified L2 cache; 512 MB RAM; Hitachi Deskstar T7K250 250 GB, 7200 rpm, 8 MB buffer, ATA UDMA5; Fedora Core 6 with 2.6 Linux kernel, gcc 4.1, ext3 file system

- Platform 3: Dual CPU Intel Pentium 4 Xeon 2.2 GHz HyperThreading<sup>1</sup>; Maxtor DiamondMax Plus D740X 80GB; 7200 rpm, 2 MB buffer, ATA UDMA5; Fedora Core 5; ext3 file system

<sup>&</sup>lt;sup>1</sup> Only one CPU was enabled and hyper-threading disabled for the experiments; the platform was used in file system benchmarks, the processor cache sizes are thus not important.

For each experiment, we first explain why is the benchmark (or set of benchmarks) performed, what is the measured workload and what parameters it has, and what we expect to learn from the results. Then we use the following template to present the experiment details and results:

**Experiment:** An identifier of the experiment for reference.

**Purpose:** The reason for the experiment in short.

**Platforms:** Where is the benchmark performed.

Measured: Short description of the code which duration is measured.

**Parameters:** Used values of parameters that the measured code has.

**Expected results:** What should the results generally show, and why, based on the theoretical knowledge.

Actual results: An analysis of the observed results. If different from the expected results, possible explanation of why that happened and how to prove or refute it with another experiment.

## 3.2 Processor caches

The benchmarking experiments for processor caches will first examine the cache sizes and latencies of the processors used in the tested platforms, and then measure the effects of cache sharing on several types of workloads. For this, many of the experiments use a special procedure described below, to artificially trash the caches. This operation is interleaved with the measured code. Such experiments include the following line in the experiment template described in Section 3.1.4:

Trashing: Used values for the parameters of trashing procedure.

## 3.2.1 Trashing procedure

The code used for trashing the caches works by accessing addresses in a previously allocated area of memory, which fetches them to the caches, potentially trashing cached data or code of the measured workload. The amount of evicted cache lines depends obviously on the cache size, the number of lines in the cache used by measured code and amount of memory accessed by the trashing procedure. Due to the limited cache associativity described in Section 2.1, the actual memory addresses of the cache lines of both measured code and trashing procedure also play an important role, affecting the number of addresses accessed by trashing that actually conflict with the addresses used by the measured code. If we wanted to control the exact number of these conflicts and thus the exact number of lines evicted by trashing, we would need the trashing code to access memory addresses in a specific patterns, which would be hard for following reasons:

I We would have to know the exact memory access pattern of the measured code for each set of its parameters.

I Because the code works with virtual addresses and some caches use physical addresses for mapping to index, we would need to know mapping between physical and virtual addresses created by the kernel.

I We would need to know the implementation details of the cache precisely, namely the hash function used to map memory addresses to indexes and the replacement policy.

This information could be infeasible to obtain and it would be only useful for the given instance of measured code and the CPU running the experiment. Another option is to give up on the exact knowledge of lines evicted by trashing, and design the trashing procedure to be as much independent on the benchmarked code and the processor cache implementation details, as possible. This way, it could be easily used anywhere. We assume that the memory addresses that would trash the caches in a real scenario are independent of the addresses used by the benchmarked code. Under these circumstances, trashing random addresses in random order should yield the best results. We do not know how many lines occupied by the measured code are actually evicted by the given number of lines we access during trashing, but the randomness should result in low distortion. To achieve this, the trashing function has three parameters:

I Mode of trashing. Code or data, depending on which caches we want to trash.

I Memory range allocated for trashing. We cannot simply access arbitrary memory addresses, the memory needs to be allocated first, as a continuous virtual memory area. Should be large enough to cover all cache entries (through virtual to physical memory mapping and memory address to cache index mapping) so that accessing all addresses in the area trashes the caches completely. The very minimum is thus the cache size. It will be determined experimentally.

I Memory access granularity. Because an access of one address will trash the whole cache line, there is no reason to access more addresses inside the line - it would only make the trashing unnecessary slower. Thus, the granularity is best set to the cache line size, which can be obtained from the processor specification, or determined experimentally.

I The amount of accessed memory. Must not exceed the allocated memory range, and must be a multiple of access granularity (this value divided by the granularity yields the number of memory addresses the trashing function will access).

The data trashing procedure then works as follows. Before the actual measurements, the memory range for trashing is allocated. Also created is a temporary array of pointers to this area, initialized linearly with the granularity setting determining the distance between the target address of two adjacent pointers. The array is then randomly shuffled. Number of pointers (corresponding with the amount of memory we want to access) from the beginning of the array is then copied to the allocated memory range, so that to the n+1-th pointer in the array is copied to the address given by n-th pointer. The address of the first pointer is stored separately and the resulting linked list is terminated by a *NULL* pointer. The trashing procedure thus simply walks through this list. The accessed addresses are randomly distributed inside the allocated memory range, and each address is read at most once. Code trashing is almost the same. Instead of the linked list, a chain of instructions that just load and jump to the address of the next instruction, is created and executed as a procedure – the last instruction in the chain is a *RET* instruction. *NOP* instructions are used for padding.

#### **3.2.2** Benchmarking framework overhead

When we study the effect of resource sharing, we should keep in mind that the benchmarking framework is also using some resources - processor, memory, files to store the results, thus potentially affecting the performance of measured code. Because in the RIB framework, we flush the results to file after all samples are obtained, here we are concerned only about the use of processor and memory, which can have impact on the processor caches, adding some extra trashing influencing the measured code indirectly. This effect can be minimized by repeating the measured code multiple times and computing average duration, but this is not possible if we want to interleave the code with trashing. We will therefore assume that our code, which calls *RDTSC* before and after the measured code and stores the difference in a memory array, should not cause significant impact on the measured code.

In addition to the abovementioned indirect impact, a direct overhead of the time or performance counter measurement may obviously exist. This overhead at first seems to be relatively easy to determine by measuring an empty operation – if the observed duration or performance counter value is non-zero, it can be subtracted from all future measurements to eliminate this overhead. However since this "overhead code"

itself uses resources, it might not just affect the measured code, but also be mutually affected by the measured code itself, and subtracting the results obtained individually may not be precise. We will quantify these effects by experiments for both RDTSC and performance counters, comparing the values obtained with no cache trashing and full trashing of code, data, or both caches. Note that we have to perform the cache trashing outside of the time or performance counter measurement so that we can measure an empty operation, but the real overhead caused by the code executed inside the measurement might be slightly higher.

#### **Experiment:** Overhead.1

- **Purpose:** Determine the overhead of the RDTSC time measurement and its dependency on code and data trashing.

- Platforms: 1, 2

- Measured: The difference in values obtained from two immediately following RDTSC calls.

- **Trashing:** Mode: code and data; allocated: 2 MB; accessed: none, 2 MB; granularity: 64 B.

- **Expected results:** Because the code between the two RDTSC calls just moves the result from two 32-bit registers into the memory by two instructions, it is accessing just one or two cache lines of stack, thus it should be affected by data cache trashing only when this line is evicted. Chance of hitting this line with trashing grows with the amount of trashing. Similarly for instruction cache because the whole code fits into one line, at worst two cache lines, it should be affected only if this line or lines get evicted.

Actual results: The difference in the number of clocks observed with no cache trashing on Platform 1 is 5. Code trashing prolongs the time to 8 clocks, while data trashing has no effect. On Platform 2, the results are always 84 clocks, not affected by any cache trashing. Possible explanation is that RDTSC on this processor is serializing, thus the second RDTSC instruction waits for the first one to retire before it is executed. This waiting probably masks any effect of cache trashing on the following instructions.

#### **Experiment:** Overhead.2

**Purpose:** Determine the overhead of performance counters, duration of the calls, which start and stop the counters, and their dependency on the code and data cache trashing as well as on the number of events counted simultaneously.

#### **Platforms:** 1, 2

**Measured:** The duration of *PAPI\_start()* and *PAPI\_stop()* calls, which are used to start the counting of previously selected performance events, and to stop the counters and return their results, respectively. Also measured are values of various available cache and TLB related events, obtained by starting and immediately stopping the counters.

**Parameters:** Number of simultaneously counted events: 1 - 4.

**Trashing:** Mode: code and data; allocated: 2 MB; accessed: none, 2 MB; granularity: 64 B.

Expected results: Unlike the simple RDTSC instruction, PAPI calls are much more

complex – they need to switch into the kernel mode in order to program or read the performance counters, accessing more cache lines and TLB entries in the process. Thus, we expect the duration of the *PAPI\_start()* and *PAPI\_stop()* calls to be much more than just few clocks, and more greatly affected by the cache trashing. Number of events counted simultaneously should also affect the duration. The results obtained from the counters might be non-zero and also affected by the trashing.

Actual results: The results are presented in Table 3.1 for Platform 1 and Table 3.2 for Platform 2. Values obtained with no trashing are in the upper part of a row and values obtained with full data and code trashing in the lower part of a row. We can see a slight increase in the values of the counters and the duration of PAPI operations as the number of simultaneously counted events increases. The trashing has significant impact especially on code misses in both the L1 code cache and the L2 cache, and on the L2 cache accesses (caused probably by the L1 data cache misses) on Platform 2. We should therefore consider the overhead when using these counters on a relatively short code. The duration of PAPI operations does not concern us, as we query the timestamp counter inside the *PAPI\_start()* and *PAPI\_stop()* calls.

|                  | number of simultaneously counted events |                |                 |                  |

|------------------|-----------------------------------------|----------------|-----------------|------------------|

|                  | 1                                       | 2              | 3               | 4                |

| PAPI_start()     | $3551 \pm 175$                          | $3598\pm88$    | $3625\pm73$     | $3730 \pm 1817$  |

| [cycles]         | $19355 \pm 972$                         | $19670\pm862$  | $19694 \pm 960$ | $19619 \pm 1961$ |

| PAPI_stop()      | $2368 \pm 174$                          | $2427 \pm 112$ | $2584 \pm 130$  | $2666 \pm 230$   |

| [cycles]         | $5814 \pm 516$                          | $6192\pm355$   | $6408\pm503$    | $6562\pm344$     |

| L1 data misses   | $1.1 \pm 0.5$                           | $1.0 \pm 0.6$  | $1.5\pm0.9$     | $2.3 \pm 0.9$    |

| L1 uata misses   | $6.1 \pm 1.8$                           | $6.1 \pm 1.9$  | $6.8 \pm 2.1$   | $8.1\pm1.8$      |

| L1 code misses   | $0.0 \pm 0.2$                           | $0.0 \pm 0.2$  | $0.0 \pm 0.2$   | $0.0\pm0.1$      |

| L1 code misses   | $24.5\pm1.0$                            | $24.5\pm1.7$   | $25.0\pm1.4$    | $25.3\pm0.8$     |

| L2 data misses   | $0.0\pm0.0$                             | $0.0\pm0.0$    | $0.0 \pm 0.0$   | $0.0\pm0.0$      |

| L2 uata misses   | $3.6 \pm 1.5$                           | $3.6\pm0.9$    | $3.6 \pm 1.4$   | $3.6 \pm 1.3$    |

| L2 code misses   | $0.0 \pm 0.1$                           | $0.0\pm0.0$    | $0.0\pm0.0$     | $0.0\pm0.0$      |

| L2 code misses   | $22.7\pm0.9$                            | $22.7\pm1.3$   | $23.1\pm0.9$    | $22.9 \pm 1.0$   |

| L1 DTLB misses   | $0.0\pm0.0$                             | $0.0\pm0.0$    | $0.0\pm0.0$     | $0.0\pm0.0$      |

| LI DILD misses   | $0.0 \pm 0.1$                           | $0.0\pm0.0$    | $0.0\pm0.0$     | $0.0\pm0.0$      |

| L1 ITLB misses   | $0.0 \pm 0.3$                           | $0.0 \pm 0.2$  | $0.0 \pm 0.3$   | $0.0\pm0.2$      |

| LI II LD IIISSES | $0.0 \pm 0.2$                           | $0.0 \pm 0.3$  | $0.0 \pm 0.2$   | $0.0\pm0.2$      |

| L2 DTLB misses   | $0.0 \pm 0.1$                           | $0.0\pm0.0$    | $0.0\pm0.0$     | $0.0\pm0.0$      |

|                  | $1.0 \pm 0.1$                           | $1.0 \pm 0.1$  | $1.0 \pm 0.1$   | $1.0\pm0.1$      |

| L2 ITLB misses   | $0.0 \pm 0.2$                           | $0.0\pm0.0$    | $0.0 \pm 0.2$   | $0.0 \pm 0.3$    |

|                  | $2.0 \pm 0.0$                           | $2.0 \pm 0.0$  | $2.0 \pm 0.0$   | $2.0\pm0.0$      |

Table 3.1: The overhead of performance counters on Platform 1 with no trashing (upper values) and full code and data trashing (lower values)

|                | number of simultaneously counted events |                  |                  |                  |

|----------------|-----------------------------------------|------------------|------------------|------------------|

|                | 1                                       | 2                | 3                | 4                |

| PAPI_start()   | $9637\pm2688$                           | $10209 \pm 2348$ | $11241 \pm 6212$ | $11619 \pm 1381$ |

| [cycles]       | $36281 \pm 3167$                        | $36976 \pm 3573$ | $38106 \pm 4151$ | $38589 \pm 5251$ |

| PAPI_stop()    | $5868 \pm 627$                          | $6138 \pm 5222$  | $6233 \pm 2187$  | $6428 \pm 964$   |

| [cycles]       | $12187\pm2181$                          | $12619 \pm 1907$ | $13137 \pm 1944$ | $13069 \pm 2839$ |

| L1 code misses | $1.3 \pm 1.0$                           | $1.5 \pm 1.0$    | $1.2 \pm 1.2$    | $1.1 \pm 0.9$    |

| L1 coue misses | $5.6 \pm 1.3$                           | $5.7 \pm 1.7$    | $6.7\pm1.6$      | $6.9\pm1.5$      |

| L2 accesses    | $20.6\pm5.2$                            | $21.8\pm6.3$     | $23.3 \pm 10.4$  | $23.9 \pm 10.2$  |

| L2 accesses    | $98.7\pm9.4$                            | $97.7 \pm 11.3$  | $99.8 \pm 13.4$  | $99.5 \pm 12.4$  |

| L2 misses      | $0.0 \pm 0.4$                           | $0.0 \pm 0.3$    | $0.0 \pm 1.1$    | $0.0\pm0.6$      |

| 1.2 1115565    | $23.5\pm3.5$                            | $23.5\pm3.8$     | $23.4 \pm 3.8$   | $23.4\pm4.4$     |

| DTLB misses    | $0.0 \pm 0.2$                           | $0.0 \pm 0.2$    | $0.0 \pm 0.4$    | $0.0 \pm 0.2$    |

| DTLD IIIISSES  | $1.0 \pm 0.6$                           | $1.0 \pm 0.7$    | $1.0 \pm 0.7$    | $1.0 \pm 0.8$    |

| ITI D migaog   | $0.0 \pm 0.8$                           | $0.1 \pm 1.2$    | $0.0 \pm 1.0$    | $0.0 \pm 0.8$    |

| ITLB misses    | $2.4 \pm 0.6$                           | $2.4 \pm 0.7$    | $2.5 \pm 0.9$    | $2.3 \pm 0.7$    |

Table 3.2: The overhead of performance counters on Platform 2 with no trashing (upper values) and full code and data trashing (lower values)

Note that while we measured the duration of whole PAPI calls, the counters are activated only at some point during the *PAPI\_start()* call, not immediately upon the invocation. Similarly in *PAPI\_stop()*, the counters are stopped possibly long before the call returns, because it stores the results. Thus, we will not be able to see all the events generated during the calls. While this reduces the number of events recorded but not generated by the measured code, it is still possible that these hidden events (for example cache misses) affect the performance of the measured code. That is why we will primarily measure only time and employ performance counters only when needed, checking whether the duration obtained with the counters does not significantly

#### 3.2.3 Artificial benchmarks

Before measuring the effect of cache trashing on practical code, we will perform several benchmarks with artificial code. Because these algorithms are designed to simply access memory addresses in certain parameterized patterns, the results should be as we expect them, based on theoretical knowledge about caches. These experiments should also prove that the framework works, and help to find out or confirm the declared parameters (capacity, line size) of the caches, and to determine the static parameters for trashing operation, as described in the previous section.

In the first experiment, we will measure the effects of sharing the TLB by accessing a number of memory pages by reading one address inside each page. To avoid using extra memory that would interfere with the TLB, the data we read contains a pointer to the next page, forming a circular list. We walk through this list hundred times and calculate average duration per one iteration to reduce overhead of the measurement. In order to avoid or minimize the number of data cache misses, we determine the offsets of cache lines inside a page (from the cache line size), and assign one of the offsets to each page, distributing them evenly. This minimizes the number of accesses to cache lines that have the same index and thus the number of conflict misses. We will also use the results of performance counters to verify the number of misses in TLB and caches.

**Experiment:** TLB.1

**Purpose:** Determine the size of the TLB and the latency of a TLB miss.

Platforms: 1, 2

**Measured:** Time to access number of memory addresses from different memory pages (4 KB large), as described above.

**Parameters:** Pages allocated: 1024; pages accessed: 0 – 1024

**Expected results:** The number of CPU cycles per one access should be constant as long as the number of addresses fits in the TLB, then raise to a higher value and remain constant again The length of the transition will depend on how close to the ideal LRU the TLB replacement algorithm is. The Athlon 64 processor used in Platform 1 has two levels of TLB, so we should see two such raises.

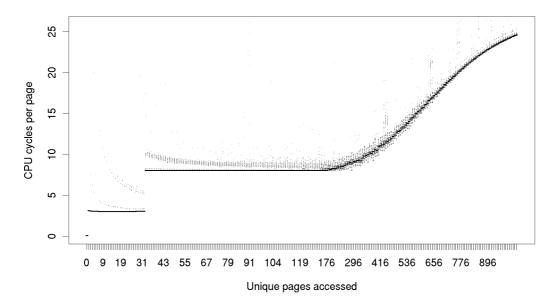

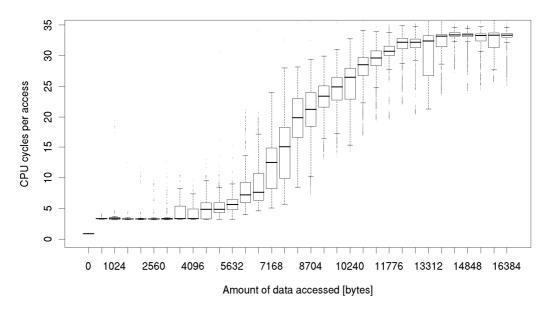

Actual results: The results from Platform 1 are shown in Figure 3.1 as a graph of CPU cycles per page access. There is a clear jump from 3 to 8 cycles per access when the number of accessed pages reaches 33, which matches the number of declared L1 DTLB entries (32) for the Athlon 64 used. Performance counter for the *L1 DTLB Miss and L2 DTLB hit* events confirms that the slowdown is indeed caused by these events. We can therefore conclude that the impact of L1 DTLB miss is 5 clocks, and the replacement algorithm does perfect LRU for a FIFO access pattern that our algorithm produces.

Figure 3.1: The effect of TLB trashing on Platform 1

For accesses that miss both in L1 and L2 DTLB, the situation is a bit more complex. We can see a gradual increase in duration after the number of accessed pages reaches approximately 168, while the declared number of entries is 512. Performance counter for the *L1 DTLB Miss and L2 DTLB miss* event shows similar

behavior, increasing from zero after the same number of accessed pages. The L1 cache miss counter remains zero, which means that the cache misses are not influencing the results. We can thus compute the impact of L2 DTLB miss by dividing the number of cycles added by the misses (which means subtracting 8 from the total number of cycles per access) with the L2 DTLB miss value where it is non-zero. The resulting average latency is  $20.5 \pm 2.1$  cycles in addition to the L1 DTLB latency. Note that the counters have also shown that the processor is caching the translation tables in the L2 cache, but not in the L1 cache – the number of the TLB misses (it would be lower were the tables cached in L1) and the counter for victim transfer from L1 to L2 is always zero, which means nothing is replacing entries in the L1 caches.

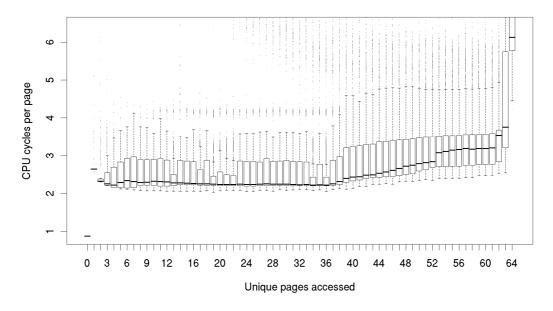

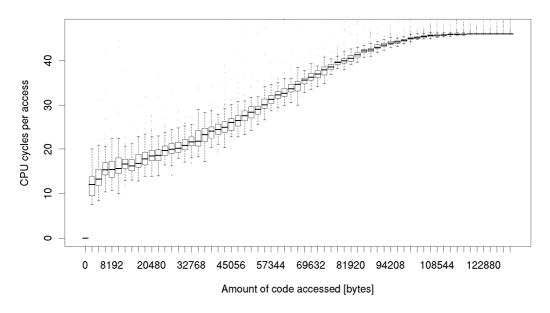

The results from Platform 2, which has only one level of DTLB, are shown in Figure 3.2 and are similar to the L2 DTLB results from Platform 1 in the aspect of gradual increase which occurs after the number of accessed pages reaches 27 (the declared size is 64 entries). The performance counter for the TLB miss event confirms this increase, and the performance counter for the L2 cache access event shows that the increase is not caused by the L1 data cache misses (the Pentium 4 processor in Platform 2 provides no separate counters for the L1 data cache). The computed average number of cycles per access with no miss is 2.5 and the calculated TLB miss latency is approximately 60 cycles.

Figure 3.2: The effect of TLB trashing on Platform 2

Although the impact of TLB miss on a single memory access may be significant, especially on Platform 2, we believe that it is not so important to determine its impact separately from the cache trashing. With small working sets and high locality, TLB miss would occur only on the first access to a page and its relative impact would get lower with each subsequent access to the same page. With large working set and low locality, the L1 data cache and the L2 cache are likely to be under similar pressure, and this is very unlikely to cause more TLB misses than cache misses. This

is why we will not measure the effect of TLB trashing separately in the later experiments with real-world code examples. The TLB effect will be a part of the effect caused by our cache trashing.

The following experiments will determine the cache line used in the processor, the code L1, data L1 and L2 sizes and latencies and the memory range we need to allocate for the trashing so that it can trash the caches completely when the whole range is accessed.

**Experiment:** Caches.1

- **Purpose:** Determine or confirm the cache line size used in the processor.

- Platforms: 1, 2

- **Measured:** The same workload as the data trashing procedure performs, but in a different memory area.

- **Parameters:** Mode: data; allocated: 512 KB; accessed: 512 KB; granularity: 4 bytes

- **Trashing:** Mode: data; allocated: 512 KB; accessed: 512 KB; granularity: 4 B 512 B increasing exponentially.

- **Expected results:** The effect of trashing and thus the measured duration should be the same for all granularity values up to cache line size, because the whole line is evicted on the first access and subsequent accesses to other words in the line do not make a difference. Increasing granularity over the cache line size should result in decreasing the number of evicted lines, thus decreasing the duration of the measured code.

Actual results: On Platform 1, the results were as expected – the measured duration is roughly constant for trashing granularity up to 64 bytes, which is the declared cache line size, and decreases with larger granularity. However, results on Platform 2 indicate cache line size of 128 bytes, although declared size is 64 bytes. This can be attributed to the fact that Pentium 4 fetches two lines into the L2 cache at once [14]. We will thus use the granularity of 128 bytes for the following artificial experiments. However, we will use 64 bytes granularity in order to trash the L1 cache properly. Although this might result in more memory trashed from the L2 cache than expected in general, there will be no difference when the whole allocated range for trashing is accessed.

**Experiment:** Caches.2

**Purpose:** Determine the sizes of the L1 data cache and the L2 unified cache and latencies of data cache hits and misses.

Platforms: 1, 2

- **Measured:** The duration of reading a memory area of given size and with given read granularity either linearly or randomly.

- **Parameters:** Access pattern: random, linear; area size: 0 1024 KB with 4 KB step; granularity: 64 B (Platform 1), 128 B (Platform 2)

- **Expected results:** Although there is no trashing performed in the benchmark, increasing the memory area should eventually exceed the size of the L1 data cache and later the L2 unified cache, which should increase the average duration per one access by the latency of the L1 cache miss and the L2 cache miss respectively.

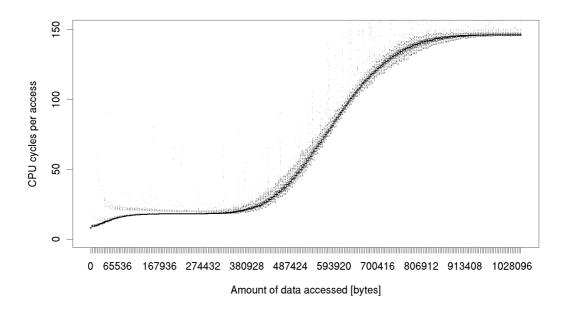

Actual results: The results of random access on Platform 1 are shown in Figure 3.3. We can see a gradual increase caused by the L1 data cache misses, roughly centered around the declared L1 size of 64 KB, and another increase caused by the L2 cache misses, centered roughly around the sum of L1 and L2 sizes (576 KB). The performance counters confirm that the causes are the L1 data cache and the L2 cache misses, and also indicate that each access causes a L1 TLB miss in the whole range, because of the random access in area of more memory pages that fit in the L1 TLB. Accesses that cause both L1 data cache and L1 TLB miss therefore cost approximately 18 cycles, which is six times the cost of access that hits (3 cycles). Accesses causing L2 data caches miss and L1 TLB miss cost about 146 cycles.

Figure 3.3: The L1 and L2 data cache miss latencies (including the L1 TLB miss latency) on Platform 1 with random access

The costs of cache misses are not so large with linear access, as shown in Figure 3.4. The number of TLB misses per access diminishes, as each page is accessed 64 times in a row, reusing the TLB entry. Linear access also triggers hardware prefetch of the next cache line before its address is decoded from the previous line. As a result, accesses causing L1 miss cost approximately 15 cycles compared to 18 cycles with random access. The L2 cache miss latency, which reflects the system memory latency, is much lower here – only 29 cycles compared to 146 with random access. This is because DRAM memory also yields better performance with linear access patterns [33].

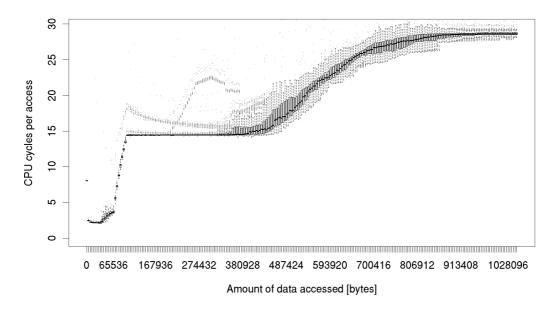

On Platform 2, the results of random access show similar behavior as on the Platform 1. Average cost per access is 3.5 CPU cycles with no cache nor TLB misses, 60 cycles with both L1 cache miss and TLB miss, and almost 400 cycles with L2 and TLB misses. The experiment was also performed using only 16 KB memory range and with step of 512 bytes in order to eliminate the TLB misses and see the effect on the L1 data cache more precisely. Figure 3.5 shows how the increase of cycles per access centered around the L1 data cache size (8 KB). The cost of access causing pure L1 miss without TLB miss is therefore approximately 33 cycles.

Figure 3.4: The L1 and L2 data cache miss latencies on Platform 1 with linear access

Figure 3.5: The L1 data cache miss latency on Platform 2 with random access

The results of linear access on Platform 2 showed surprisingly low cost of access with L1 miss – just about 5 cycles, compared to 15 on Platform 1. The cost of access with L2 miss was approximately 106 clocks.

**Experiment:** Caches.3

- **Purpose:** Determine the sizes of the L1 code cache and the L2 unified cache and latencies of code cache hits and misses.

- **Platforms:** 1, 2

- **Measured:** The duration of executing a code consisting of jump instructions in a memory area of given size and with given jump granularity. The addresses of the jumps are either linear or random.

- **Parameters:** Access pattern: random, linear; area size: 0 1024 KB with 4 KB step; granularity: 64 B (Platform 1), 128 B (Platform 2)

- **Expected results:** The results should be similar to the previous experiment with data caches with respect to possibly different L1 code cache size. The miss latencies should not differ significantly from the data access latencies.

Actual results: On Platform 1, the results with random code access show similar behavior to the previous experiment with data access, except that the increase of duration related to L2 misses starts and ends roughly 150 KB earlier. The performance counter for the L1 code cache misses shows that each access causes almost two misses, although our jump instructions fit into one line. This could be caused by the hardware prefetch which probably fetches always the next cache line and does not try to adapt to the access pattern, because code is usually executed linearly. The duration of one access is approximately 5 CPU cycles without misses, 35 cycles with the L1 code cache misses and the L1 ITLB miss, and 142 cycles with the L2 cache miss and the L1 ITLB miss.

The results of linear code access support the hypothesis of prefetch of the following cache line – the number of L1 cache misses is at most one per access, and the increase of duration related to L2 misses is no longer shifted. The duration per one access is approximately 26 cycles with the L1 code cache miss, and 66 cycles with the L2 cache miss.

The results of random code access on Platform 2 show the expected behavior for the L2 cache miss effect. The L1 code cache miss effect is more interesting as shown in Figure 3.6 for the experiment repeated with a smaller memory area to eliminate the TLB misses. Because the Pentium 4 processor uses a trace cache as the L1 code cache, only the decoded micro-operations of the instructions that have been executed are stored instead of the whole cache lines. Because of this, it needs more accesses with the 128 bytes granularity to fully saturate the cache, which has a capacity of 12 K micro-operations.

The duration per access is approximately 10 cycles with no misses, 47 cycles with the L1 code cache miss, 63 cycles with both the L1 code cache miss and ITLB miss, and 400 cycles with L2 cache miss and ITLB miss. The results of linear code access on Platform 2 yield also 47 cycles with L1 code cache miss (which indicates there is no code prefetch), and 138 cycles with the L2 cache miss.

Figure 3.6: The L1 code cache miss latency on Platform 2 with random access

#### **Experiment:** Caches.4

**Purpose:** Determine the memory area size needed for trashing all caches **Platforms:** 1, 2

- **Measured:** The same workload as the data trashing procedure performs, but in a different memory area.

- Parameters: Mode: data; allocated: 512 KB; accessed: 128 KB, 512 KB, 1024 KB; granularity: 64 B

- **Trashing:** Mode: data; allocated: 256 KB 8 MB with 256 KB step; accessed: all that is allocated; granularity: 64 B

- **Expected results:** The measured duration should increase as the memory range allocated for trashing increases, to a point where the whole buffer of the measured workload is evicted from both the L1 data cache and the L2 cache, and the duration should stay constant from that point on.

Actual results: On both platforms, the point where more trashing did not prolong the measured duration anymore, was below 2 MB for all buffer sizes, and therefore 2 MB will be used in further experiments as the memory range allocated for trashing and maximum amount of memory accessed during trashing.

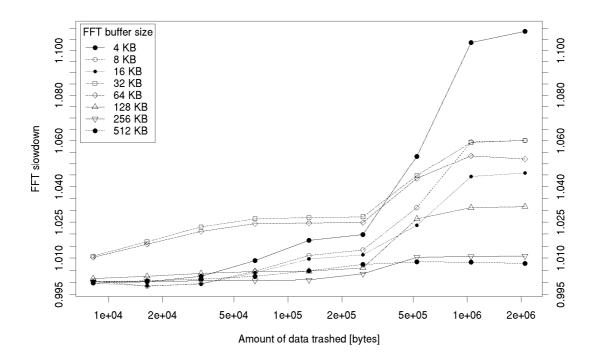

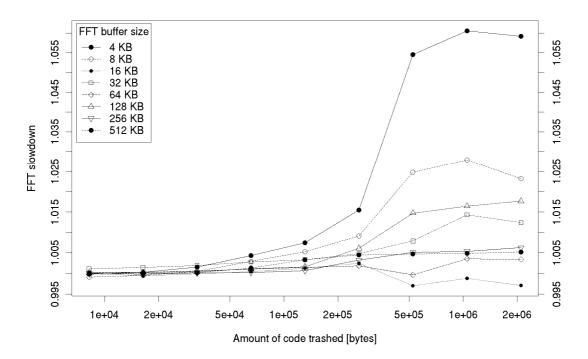

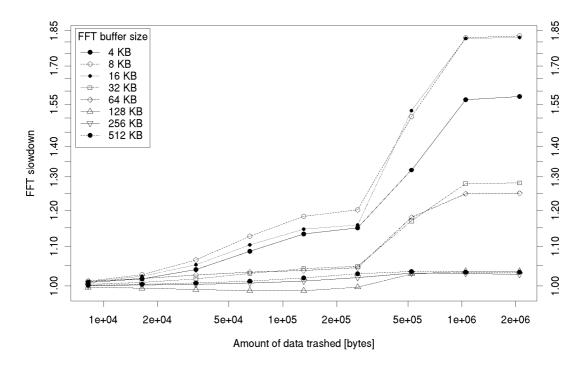

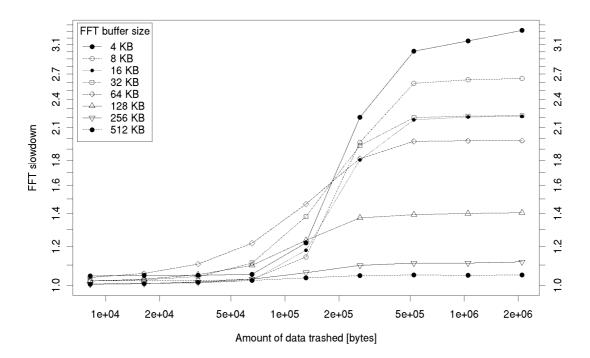

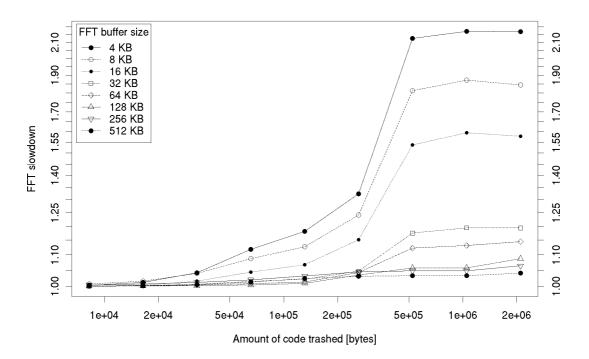

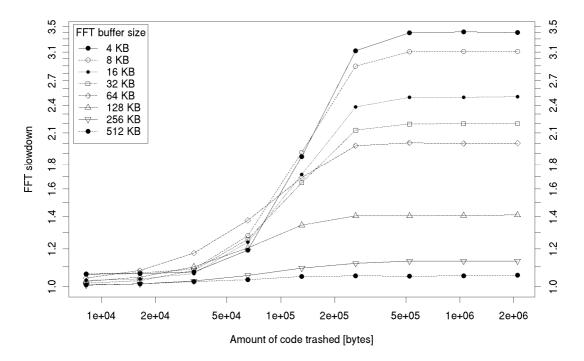

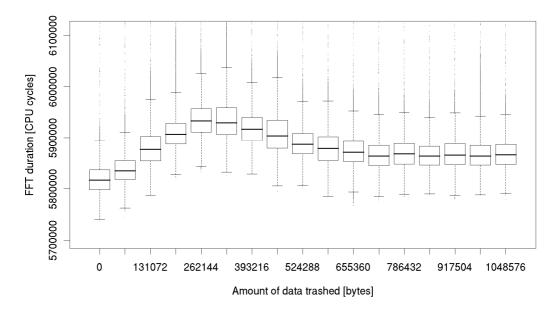

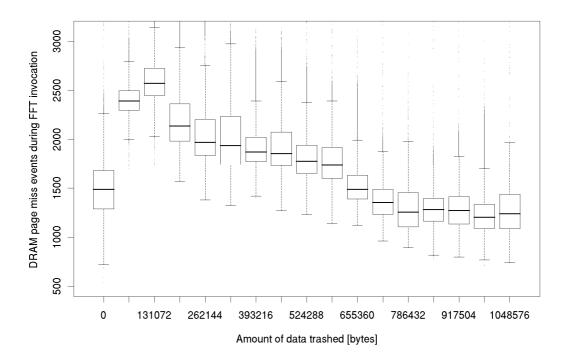

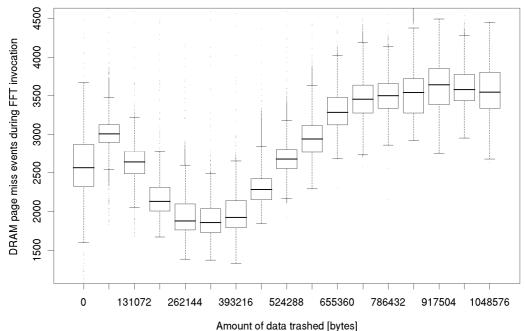

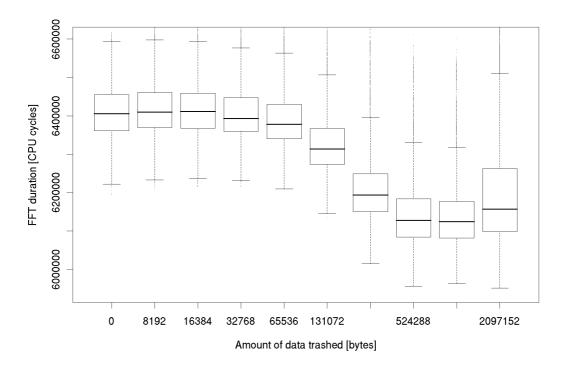

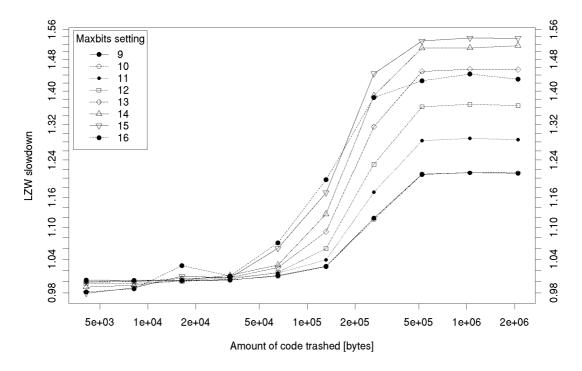

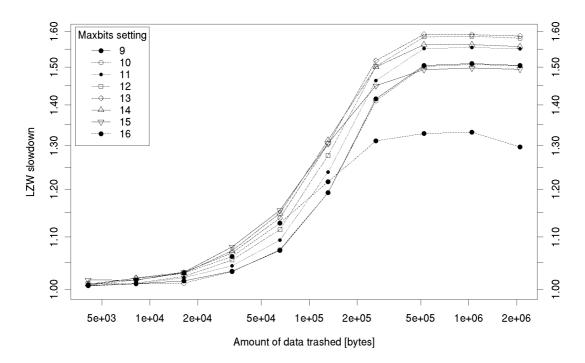

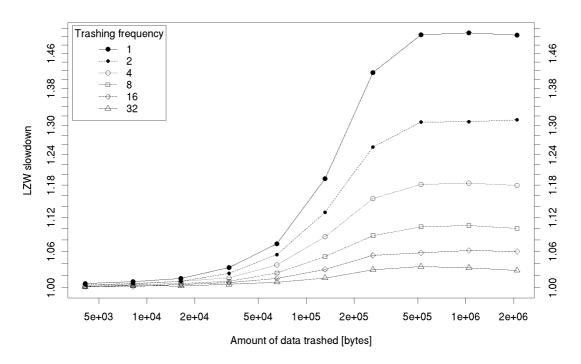

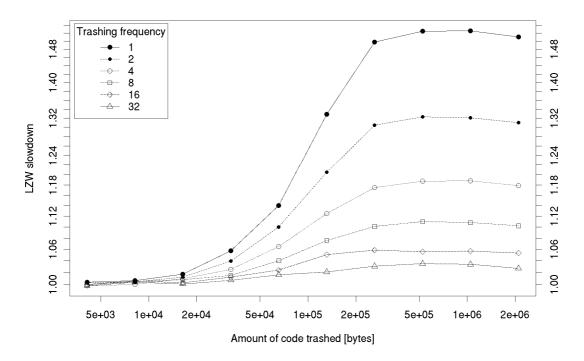

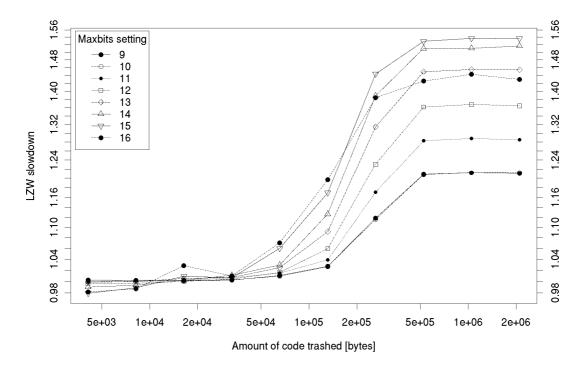

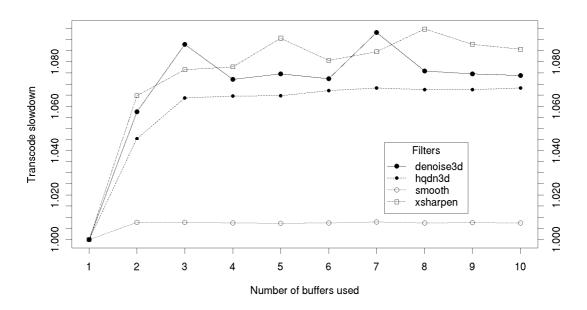

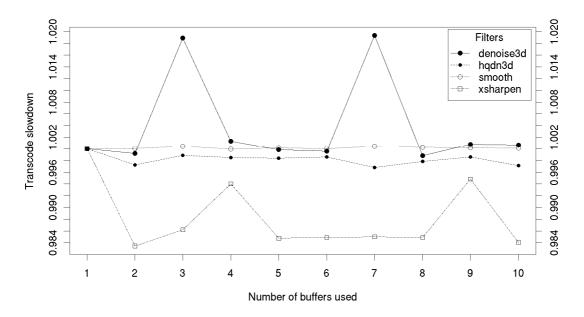

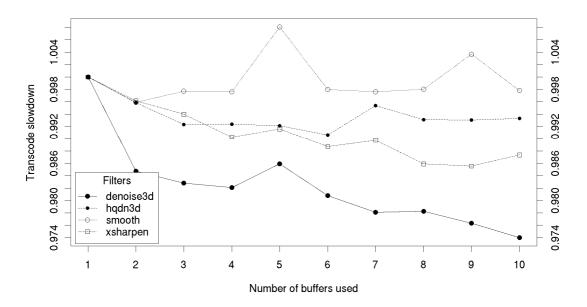

## 3.2.4 FFT