# IMPROVING THE HARDWARE PERFORMANCE OF ARITHMETIC CIRCUITS USING APPROXIMATE COMPUTING

A Thesis Submitted to the College of Graduate and Post Doctoral Studies in Partial Fulfillment of the Requirements for the Degree of Master's in the Department of Electrical and Computer Engineering University of Saskatchewan Saskatoon

By

## ELIZABETH ADAMS

© Elizabeth Adams, December, 2020. All rights reserved. Unless otherwise noted, copyright of the material in this thesis belongs to the author.

# PERMISSION TO USE

In presenting this thesis/dissertation in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis/dissertation in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis/dissertation work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis/dissertation or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis/dissertation.

Requests for permission to copy or to make other uses of materials in this thesis/dissertation in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan S7N 5A9 Canada

OR

Dean of the College of Graduate and Postdoctoral Studies College of Graduate and Postdoctoral Studies University of Saskatchewan 116 Thorvaldson Building, 110 Science Place Saskatoon, Saskatchewan S7N 5C9 Canada

# Abstract

An application that can produce a useful result despite some level of computational error is said to be error resilient. Approximate computing can be applied to error resilient applications by intentionally introducing error to the computation in order to improve performance, and it has been shown that approximation is especially well-suited for application in arithmetic computing hardware. In this thesis, novel approximate arithmetic architectures are proposed for three different operations, namely multiplication, division, and the multiply accumulate (MAC) operation. For all designs, accuracy is evaluated in terms of mean relative error distance (MRED) and normalized mean error distance (NMED), while hardware performance is reported in terms of critical path delay, area, and power consumption.

Three approximate Booth multipliers (ABM-M1, ABM-M2, ABM-M3) are designed in which two novel inexact partial product generators are used to reduce the dimensions of the partial product matrix. The proposed multipliers are compared to other state-ofthe-art designs in terms of both accuracy and hardware performance, and are found to reduce power consumption by up to 56% when compared to the exact multiplier. The function of the multipliers is verified in several image processing applications.

Two approximate restoring dividers (AXRD-M1, AXRD-M2) are proposed along with a novel inexact restoring divider cell. In the first divider, the conventional cells are replaced with the proposed inexact cells in several columns. The second divider computes only a subset of the trial subtractions, after which the divisor and partial remainder are rounded and encoded so that they may be used to estimate the remaining quotient bits. The proposed dividers are evaluated for accuracy and hardware performance alongside several benchmarking designs, and their function is verified using change detection and foreground extraction applications.

An approximate MAC unit is presented in which the multiplication is implemented using a modified version of ABM-M3. The delay is reduced by using a fused architecture where the accumulator is summed as part of the multiplier compression. The accuracy and hardware savings of the MAC unit are measured against several works from the literature, and the design is utilized in a number of convolution operations.

# ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to my supervisor Dr. Seok-Bum Ko for his continuous support throughout the course of my M.Sc. studies. His immense knowledge and experience in the field has given him an excellent eye for worthwhile research opportunities, and I can not thank him enough for the patience, compassion, and encouragement he has shown me. Without his guidance, this dissertation would not have been possible.

I would like to extend a special thanks to Suganthi Venkatachalam for her role as an excellent research partner. I deeply appreciate the patience she expressed while I was becoming oriented with our research as a new graduate student, and I am indebted for the countless occasions on which she took time out of her day to lend me a helping hand. It was because of her warmth that my transition to becoming a graduate student was so much less intimidating. I would also like to express sincere gratitude to my labmate Hao Zhang for his vast technical knowledge and the prompt assistance he always gave me when troubleshooting issues in the lab. My labmates have continuously taken the extra step to help me out when I need it, and I can not overstate how much I appreciate their support.

I thank my mom, my dad, my sister, and my boyfriend for their endless patience throughout my studies. It goes without saying that research can impose a sense of intimidation and frustration from time to time. I am so incredibly grateful for the support provided by my family and friends during those times that I was feeling under-confident. It was because of their encouraging words that I was also able to experience the joy and accomplishment of seeing my research through.

My sincere thanks to the Natural Sciences and Engineering Research Council of Canada (NSERC), the R&D program of the Korean Ministry of Trade, Industry and Energy (MOTIE), the Korea Institute for Industrial Economics and Trade (KIET), and the Department of Electrical and Computer Engineering, University of Saskatchewan.

To to all those who are patient and persistent in encouraging me, you have shown me that I am much more capable than I thought myself to be.

# Contents

| Pe            | ermis  | sion to | o Use                                       | i    |

|---------------|--------|---------|---------------------------------------------|------|

| A             | bstra  | ct      |                                             | ii   |

| A             | cknov  | wledge  | ments                                       | iii  |

| Ta            | able ( | of Con  | tents                                       | vii  |

| Li            | st of  | Tables  | 5                                           | viii |

| Li            | st of  | Figure  | 2S                                          | x    |

| $\mathbf{Li}$ | st of  | Abbre   | eviations                                   | xi   |

| 1             | Intr   | oducti  | on                                          | 1    |

|               | 1.1    | Motiv   | ation                                       | 1    |

|               |        | 1.1.1   | Trends in Semiconductor Scaling             | 1    |

|               |        | 1.1.2   | Trends in Data Processing Applications      | 3    |

|               | 1.2    | Appro   | ximate Computing as a Field of Research     | 4    |

|               |        | 1.2.1   | Software-Level Techniques                   | 4    |

|               |        | 1.2.2   | Architecture-Level Techniques               | 5    |

|               |        | 1.2.3   | Circuit-Level Techniques                    | 7    |

|               | 1.3    | Contr   | ibutions of the Thesis                      | 8    |

|               | 1.4    |         | ations and Submissions during M.Sc. Study   | 9    |

|               |        | 1.4.1   | Published Journal                           | 9    |

|               |        | 1.4.2   | Published Conference                        | 9    |

|               |        | 1.4.3   | Submitted Journal                           | 9    |

|               | 1.5    | Organ   | ization of the Thesis                       | 10   |

| <b>2</b>      | Rev    | view of | Contemporary Approximate Arithmetic Designs | 11   |

|               | 2.1    | Appro   | ximate Adders                               | 11   |

|               | 2.2    | Appro   | ximate Multipliers                          | 12   |

|               |        | 2.2.1   | Approximate AND-Array Multipliers           | 13   |

|          |     | 2.2.2  | Logarithmic Multipliers                                           | 14 |

|----------|-----|--------|-------------------------------------------------------------------|----|

|          |     | 2.2.3  | Approximate Booth Multipliers                                     | 15 |

|          |     | 2.2.4  | Multiplication using Approximate Compressors                      | 16 |

|          | 2.3 | Appro  | eximate Dividers                                                  | 17 |

|          | 2.4 | Appro  | oximate MAC Units                                                 | 18 |

| 3        | App | proxim | ate Booth Multipliers                                             | 20 |

|          | 3.1 | Autho  | or Contributions                                                  | 20 |

|          | 3.2 | Radix  | -4 Booth Multipliers                                              | 21 |

|          | 3.3 | Appro  | eximate Radix-4 Booth Multipliers                                 | 22 |

|          |     | 3.3.1  | Approximate Booth Multiplier Model 1 (ABM-M1) $\ . \ . \ . \ .$ . | 23 |

|          |     | 3.3.2  | Approximate Booth Multiplier Model 2 (ABM-M2)                     | 25 |

|          |     | 3.3.3  | Approximate Booth Multiplier Model 3 (ABM-M3)                     | 26 |

|          | 3.4 | Exper  | imental Results                                                   | 27 |

|          | 3.5 | Applie | cations                                                           | 28 |

|          |     | 3.5.1  | Image Transformation                                              | 28 |

|          |     | 3.5.2  | Matrix Multiplication                                             | 30 |

|          |     | 3.5.3  | FIR Filter Implementation                                         | 30 |

| 4        | App | proxim | ate Array-Based Restoring Dividers                                | 32 |

|          | 4.1 | Autho  | or Contributions                                                  | 32 |

|          | 4.2 | Exact  | Restoring Dividers                                                | 33 |

|          | 4.3 | Appro  | eximate Restoring Dividers                                        | 33 |

|          |     | 4.3.1  | Approximate Restoring Divider Model 1 (AXRD-M1)                   | 35 |

|          |     | 4.3.2  | Approximate Restoring Divider Model 2 (AXRD-M2)                   | 37 |

|          | 4.4 | Exper  | imental Results                                                   | 42 |

|          |     | 4.4.1  | Accuracy Evaluation                                               | 42 |

|          |     | 4.4.2  | Hardware Evaluation                                               | 44 |

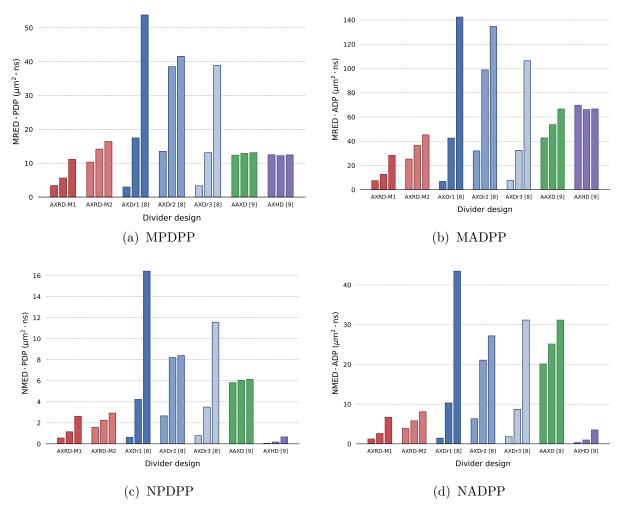

|          |     | 4.4.3  | Accuracy-Performance Tradeoff                                     | 45 |

|          | 4.5 | Applie | cations                                                           | 47 |

|          |     | 4.5.1  | Change Detection                                                  | 47 |

|          |     | 4.5.2  | Foreground Extraction                                             | 47 |

| <b>5</b> | App | proxim | ate Fixed-Point MAC Unit                                          | 52 |

|          | 5.1 | Autho  | or Contributions                                                  | 52 |

|          | 5.2 | Appro  | eximate Booth Multiplier (ABM-M3)                                 | 52 |

|          | 5.3 | Appro  | eximate Booth Multiplier-Based MAC (ABM-MAC)                      | 53 |

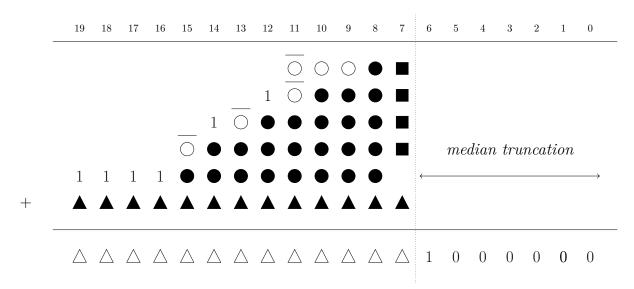

|          |     | 5.3.1  | Partial Product Compression                                       | 54 |

|          |     | 5.3.2  | Median Value Truncation                                           | 55 |

|          | 5.4 | Exper  | imental Results                                                   | 57 |

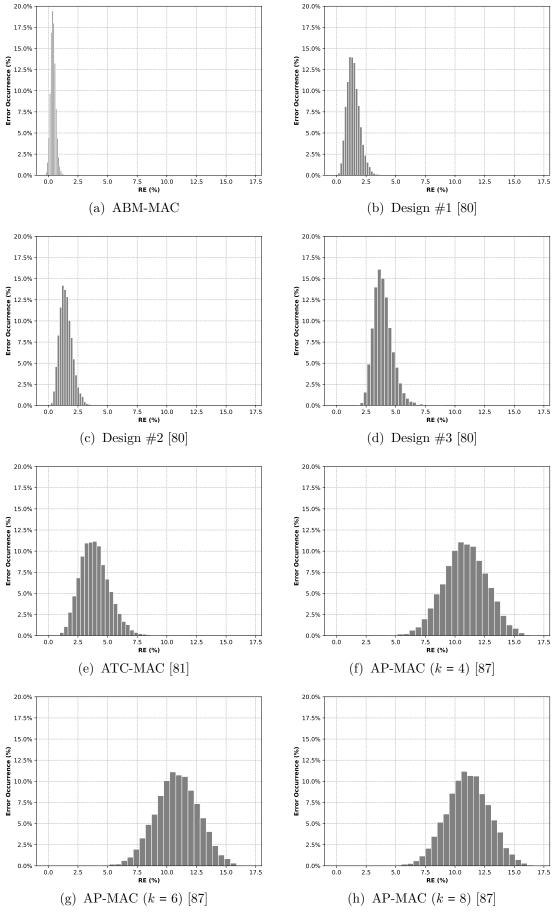

|   |     | 5.4.1   | Accuracy Analysis                        | 58 |

|---|-----|---------|------------------------------------------|----|

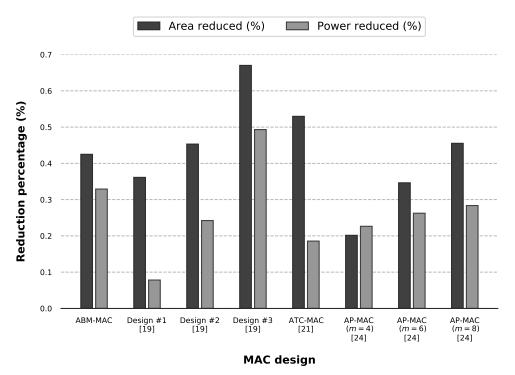

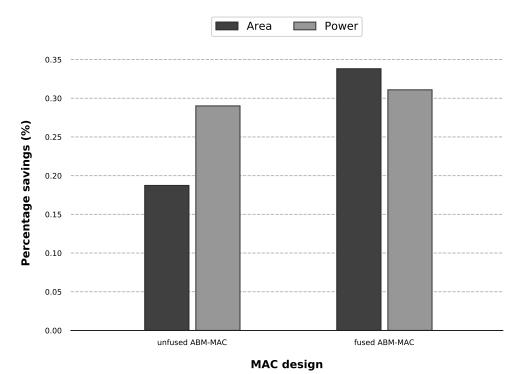

|   |     | 5.4.2   | Hardware Analysis                        | 58 |

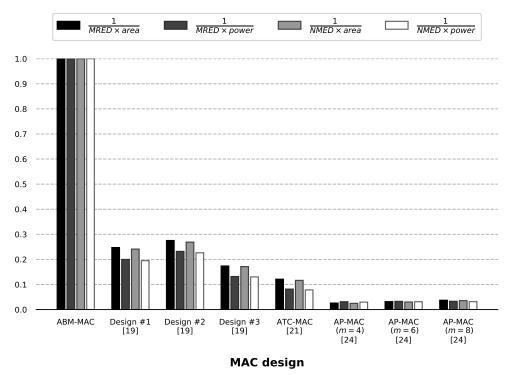

|   |     | 5.4.3   | Accuracy-Performance Tradeoff Evaluation | 59 |

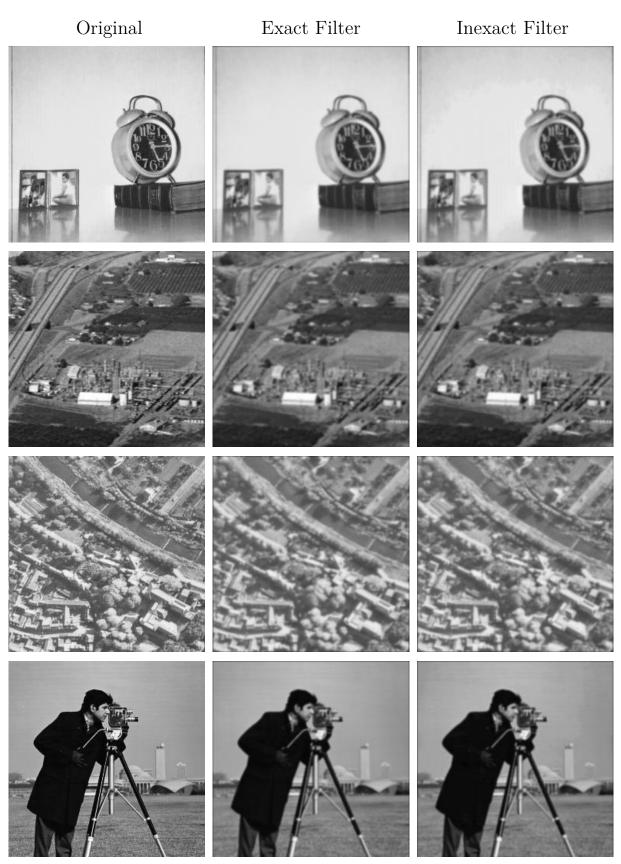

|   | 5.5 | Gaussi  | an Blur Application                      | 61 |

|   |     |         |                                          |    |

| 6 | Con | clusior | as and Future Work                       | 66 |

| 6 |     |         | as and Future Work                       | 00 |

| 6 | 6.1 | Conclu  |                                          | 66 |

# LIST OF TABLES

| 3.1 | Radix-4 Booth encoding                                                                                              | 21 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Accurate radix-4 encoding vs. approximate encoding via PPG-2S $\ .$                                                 | 24 |

| 3.3 | Accuracy and hardware metrics for approximate multipliers $\ldots$ .                                                | 27 |

| 3.4 | MRED and NMED of multipliers for matrix multiplication $\hdots$                                                     | 30 |

| 3.5 | MSE of multipliers in FIR filter application                                                                        | 31 |

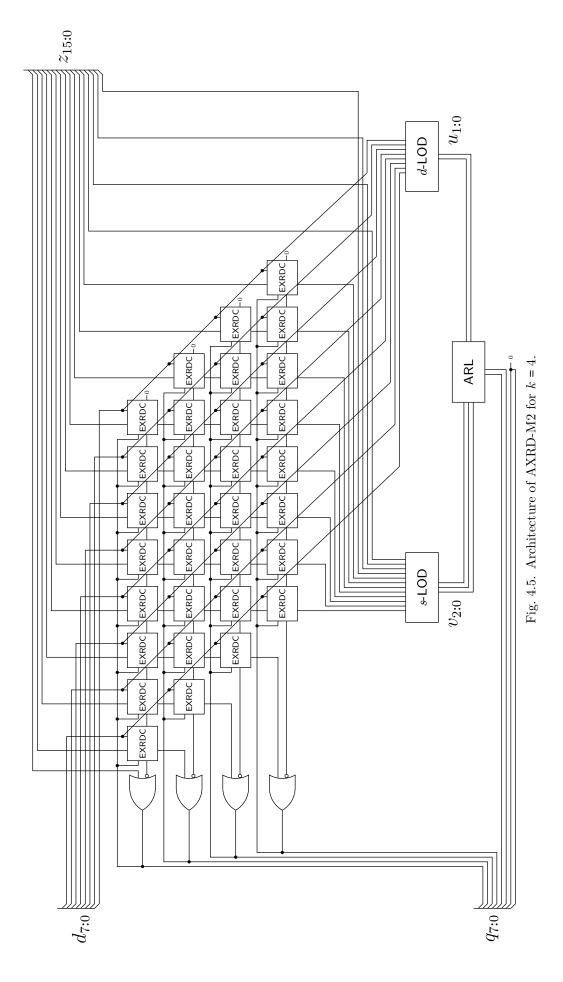

| 4.1 | Divisor rounding and encoding to generate $u$                                                                       | 39 |

| 4.2 | Partial remainder rounding and encoding to generate $v$                                                             | 39 |

| 4.3 | Use of encoded values $u$ and $v$ to produce approximate quotient bits for                                          |    |

|     | $k = 4 \dots \dots$ | 41 |

| 4.4 | Accuracy and hardware metrics for approximate dividers $\ldots \ldots \ldots$                                       | 43 |

| 4.5 | Accuracy-hardware tradeoff metrics for approximate dividers                                                         | 46 |

| 4.6 | Application metrics for approximate dividers                                                                        | 49 |

| 5.1 | Accuracy and hardware metrics for approximate MAC units $\ldots \ldots \ldots$                                      | 57 |

| 5.2 | PSNR and SSIM measurements for Gaussian blur application                                                            | 62 |

# LIST OF FIGURES

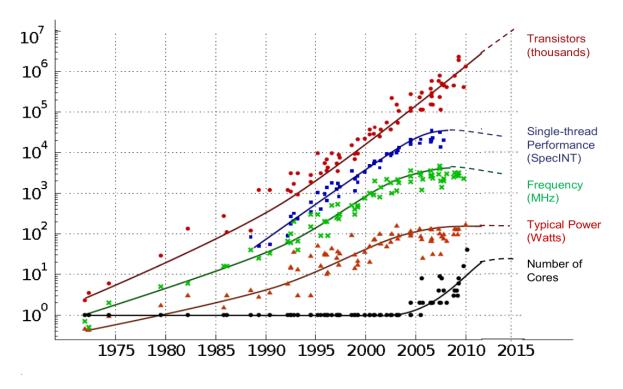

| 1.1  | Decay of Dennard scaling in recent years. [5]                               | 2  |

|------|-----------------------------------------------------------------------------|----|

| 3.1  | Example of overlapping encoding groups.                                     | 22 |

| 3.2  | Gate-level schematic for exact PPG                                          | 22 |

| 3.3  | Partial product matrix of the exact $16 \times 16$ radix-4 Booth multiplier | 22 |

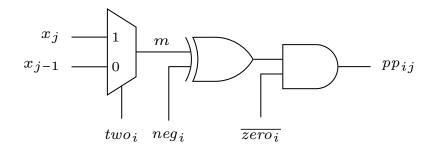

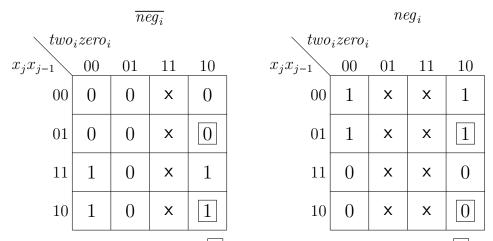

| 3.4  | Karnaugh-map for PPG-2S                                                     | 23 |

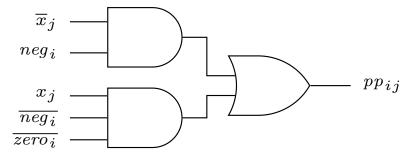

| 3.5  | Circuit-level schematic for PPG-2S                                          | 24 |

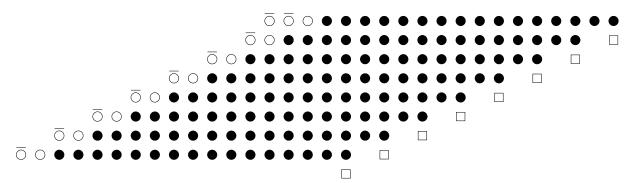

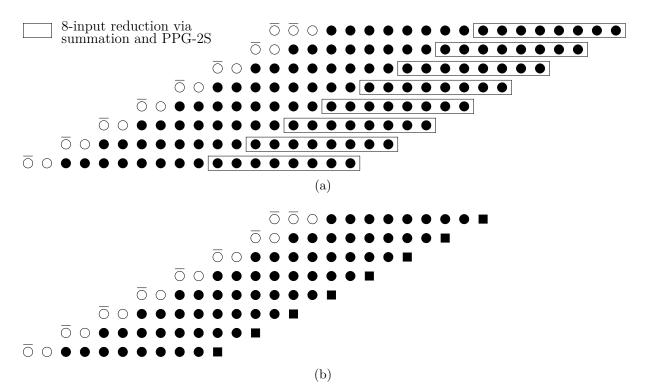

| 3.6  | Partial product matrix of ABM-M1 for $k = 12$                               | 24 |

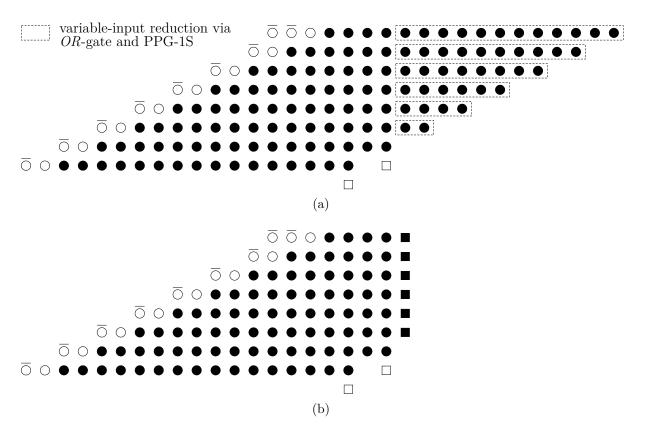

| 3.7  | Partial product matrix of ABM-M2 for $k = 8$                                | 25 |

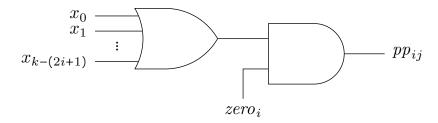

| 3.8  | Circuit-level schematic for PPG-1S                                          | 26 |

| 3.9  | Partial product matrix of ABM-M3 for $k = 12$                               | 26 |

| 3.10 | Input image and generated outputs for image transformation application      | 29 |

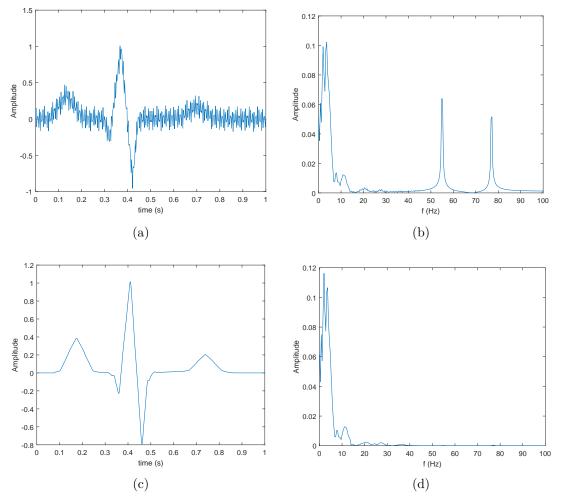

| 3.11 | Input and output signals for FIR filter application.                        | 31 |

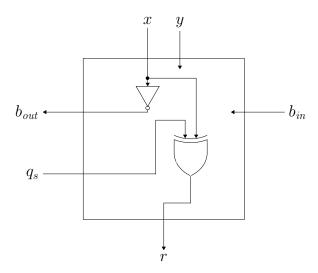

| 4.1  | Circuit-level schematic for EXRDC                                           | 34 |

| 4.2  | Architecture of exact 8/4 restoring divider                                 | 34 |

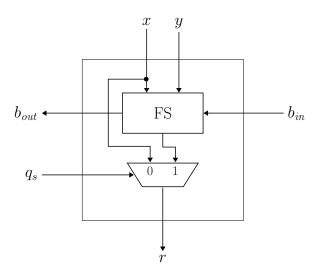

| 4.3  | Circuit-level schematic for AXRDC                                           | 35 |

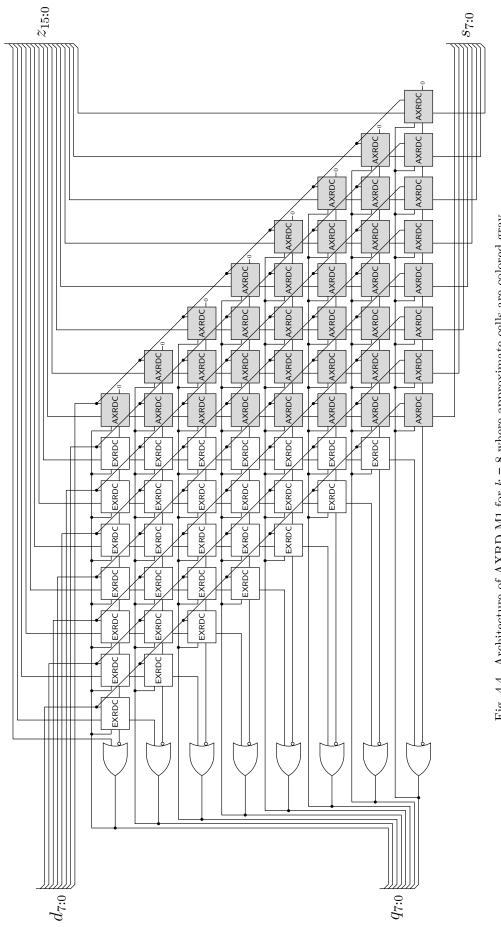

| 4.4  | Architecture of 16/8 AXRD-M1 for $k = 8$                                    | 36 |

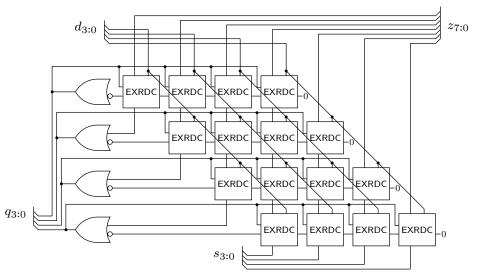

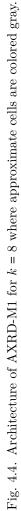

| 4.5  | Architecture of AXRD-M2 for $k = 4$                                         | 38 |

| 4.6  | Karnaugh-map for approximating $q_3$ and $q_2$ in AXRD-M2                   | 40 |

| 4.7  | Graphs illustrating accuracy-hardware tradeoff metrics for the implemented  |    |

|      | dividers                                                                    | 45 |

| 4.8  | Change detection results computed using various dividers                    | 48 |

| 4.9  | Foreground extraction results computed using various dividers               | 51 |

| 5.1  | Bit matrix of ABM-MAC.                                                      | 53 |

| 5.2  | Relative error distribution for implemented MAC units                       | 56 |

| 5.3  | Hardware savings for approximate MAC units compared to the accurate         |    |

|      | design                                                                      | 59 |

| 5.4  | Comparison of hardware savings delivered by fused vs. non-fused ABM-MAC.    | 60 |

| 5.5  | Inverse multiplication of error metrics by hardware parameters to evaluate  |    |

|      | tradeoff                                                                    | 60 |

| 5.6  | Discrete $5 \times 5$ Gaussian filter                                       | 62 |

| 5.7  | Images used in $5 \times 5$ Gaussian blur application.                      | 63 |

| 5.8 | Discrete $7 \times 7$ Gaussian filter                  | 64 |

|-----|--------------------------------------------------------|----|

| 5.9 | Images used in $7 \times 7$ Gaussian blur application. | 65 |

# LIST OF ABBREVIATIONS

| AAXD                | Adaptive approximation-based divider [79].                 |  |  |  |  |  |

|---------------------|------------------------------------------------------------|--|--|--|--|--|

| ABM-M1              | Approximate Booth multiplier model 1.                      |  |  |  |  |  |

| ABM-M2              | Approximate Booth multiplier model 2.                      |  |  |  |  |  |

| ABM-M3              | Approximate Booth multiplier model 3.                      |  |  |  |  |  |

| ABM-MAC             | Approximate Booth multiplier-based MAC.                    |  |  |  |  |  |

| ABM1                | Approximate Booth multiplier 1 [71].                       |  |  |  |  |  |

| <b>ABM2-C9</b>      | Approximate Booth multiplier 2 with 9-bit truncation [71]. |  |  |  |  |  |

| ADP                 | Area-delay product.                                        |  |  |  |  |  |

| AP-MAC              | Approximate MAC [87].                                      |  |  |  |  |  |

| APP                 | Area-power product.                                        |  |  |  |  |  |

| ARL                 | Approximate recoded logic.                                 |  |  |  |  |  |

| ATC-MAC             | Approximate tree compressor-based MAC [81].                |  |  |  |  |  |

| AXDr                | Approximate restoring divider [77].                        |  |  |  |  |  |

| AXDr1               | Approximate restoring divider 1 [77].                      |  |  |  |  |  |

| AXDr2               | Approximate restoring divider 2 [77].                      |  |  |  |  |  |

| AXDr3               | Approximate restoring divider 3 [77].                      |  |  |  |  |  |

| AXHD                | Approximate hybrid divider [66].                           |  |  |  |  |  |

| AXRD-M1             | Approximate restoring divider model 1.                     |  |  |  |  |  |

| AXRD-M2             | Approximate restoring divider model 2.                     |  |  |  |  |  |

| AXRDC               | Approximate restoring divider cell.                        |  |  |  |  |  |

| $\mathbf{CLA}$      | Carry-lookahead adder.                                     |  |  |  |  |  |

| $\mathbf{CSA}$      | Carry-select adder.                                        |  |  |  |  |  |

| $\mathbf{D}_{\max}$ | Maximum error distance.                                    |  |  |  |  |  |

| DRAM                | Dynamic RAM.                                               |  |  |  |  |  |

| $\mathbf{ED}$       | Error distance.                                            |  |  |  |  |  |

| $\mathbf{ER}$       | Error rate.                                                |  |  |  |  |  |

| EXRDC               | Exact restoring divider cell.                              |  |  |  |  |  |

| $\mathbf{FIR}$      | Finite impulse response.                                   |  |  |  |  |  |

| FPGA                | Field-programmable gate array.                             |  |  |  |  |  |

| $\mathbf{FS}$       | Full substractor.                                          |  |  |  |  |  |

|                     |                                                            |  |  |  |  |  |

| LMLogarithmic multiplier.LODLeading-one detector.LSBLeast-significant bit.MACMultiply accumulate.MADPPMRED-ADP product.MAEMean absolute error.MBEModified Booth encoder.MEDMean error distance. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSBLeast-significant bit.MACMultiply accumulate.MADPPMRED-ADP product.MAEMean absolute error.MBEModified Booth encoder.                                                                         |

| MACMultiply accumulate.MADPPMRED-ADP product.MAEMean absolute error.MBEModified Booth encoder.                                                                                                  |

| MADPPMRED-ADP product.MAEMean absolute error.MBEModified Booth encoder.                                                                                                                         |

| MAEMean absolute error.MBEModified Booth encoder.                                                                                                                                               |

| <b>MBE</b> Modified Booth encoder.                                                                                                                                                              |

|                                                                                                                                                                                                 |

| MED Mean error distance                                                                                                                                                                         |

| WED Mean citor distance.                                                                                                                                                                        |

| <b>MPDPP</b> MRED-PDP product.                                                                                                                                                                  |

| <b>MRED</b> Mean relative error distance.                                                                                                                                                       |

| MSB Most-significant bit.                                                                                                                                                                       |

| MSE Mean squared error.                                                                                                                                                                         |

| <b>NADPP</b> NMED-ADP product.                                                                                                                                                                  |

| <b>NMED</b> Normalized mean error distance.                                                                                                                                                     |

| <b>NOD</b> Nearest-one detector [64].                                                                                                                                                           |

| <b>NPDPP</b> NMED-PDP product.                                                                                                                                                                  |

| <b>NPU</b> Neural processing unit.                                                                                                                                                              |

| PDP Power-delay product.                                                                                                                                                                        |

| <b>PPG</b> Partial product generator.                                                                                                                                                           |

| <b>PPG-1S</b> 1-signal partial product generator.                                                                                                                                               |

| <b>PPG-2S</b> 2-signal partial product generator.                                                                                                                                               |

| <b>PSNR</b> Peak signal-to-noise ratio.                                                                                                                                                         |

| <b>R4ABM</b> Approximate radix-4 Booth multiplier [70].                                                                                                                                         |

| <b>RAD256</b> Approximate multiplier with radix-256 LSB encoding [72].                                                                                                                          |

| <b>SSIM</b> Structural similarity index measurement.                                                                                                                                            |

| <b>VOS</b> Voltage overscaling.                                                                                                                                                                 |

# CHAPTER 1

# INTRODUCTION

This chapter provides an introduction to the topics discussed in this thesis. Section 1.1 presents the motivation behind the research, Section 1.2 features a high-level survey of approximate computing techniques, Section 1.3 describes the novel research contributions presented in this thesis, Section 1.4 lists the publications and submissions made during the course of the M.Sc. study, and Section 1.5 details the organization of the thesis.

## 1.1 Motivation

While energy consumption has always been an important metric in the design of computing systems, a number of recent trends have led power efficiency to become the paramount concern in the field. Computing systems are becoming increasingly mobile, and there is a strong demand for high performance computing on power-constrained devices. Even in the context of more traditional devices that do not rely on battery power, emerging high performance applications, such as multimedia streaming and machine learning, require increasingly large datasets to be processed with high efficiency.

#### 1.1.1 Trends in Semiconductor Scaling

In 1965, Gordon Moore observed that the number of transistors per integrated circuit was doubling every year, and he predicted that this trend would continue for at least the next decade [1]. A decade later and the co-founder of Intel, Moore revised his forecast to project that the doubling would occur every two years [2]. Now widely known as Moore's law, his projection has held strong for decades, perhaps having acted as a sort of self-fulfilling prophecy due to the fact that it has been widely used as a guide for establishing timelines and setting targets in the semiconductor industry. In 1974, Robert Dennard observed that power density remained constant as transistor dimensions shrank, a phenomenon referred to as Dennard scaling [3]. Dennard proposed a method of scaling voltage and current proportional to transistor dimensions, thereby yielding higher speed and reduced power consumption. It is crucial to note that Moore's law alone does not provide any insight into performance. While Moore's law predicts that transistors will shrink, it is

Original data collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond and C. Batten Dotted line extrapolations by C. Moore

Fig. 1.1. Decay of Dennard scaling in recent years. [5]

Dennard scaling that connects the reduction of transistor dimensions with smaller energy consumption and higher clock frequencies.

The scaling of transistor density, clock frequency, and power consumption from 1975 to 2015 is shown in Fig. 1.1. For many decades, Dennard scaling allowed for increasing clock frequencies and decreasing power consumption to match the rate of Moore's law. However, as visible from Fig. 1.1, Dennard scaling began to break down in 2005, despite the fact that transistors are still shrinking. The cause of this breakdown lies in an oversight made by Dennard when formulating his scaling technique, in which he assumed that threshold voltage would scale with operating voltage. While sub-threshold voltage leakage was rather negligible in 1974, transistors have now scaled to the point where sub-threshold leakage has a major impact on overall chip power, thereby presenting serious challenges with regards to further reducing operating voltage [4]. As a result, while transistor sizes continue to shrink in accordance with Moore's law, we can no longer rely on performance gains provided by Dennard scaling, and thus transistor size is no longer a reliable representative of single-core computing performance.

Even if sub-threshold leakage can be addressed, there are additional issues associated with the fact that performance improvements under Dennard scaling intrinsically rely on Moore's law. While there is still much debate as to how quickly the rate of progress will saturate, transistor dimensions are already approaching atomic measurements and can only become so small before they are fundamentally limited by physical constraints [6]. In a 2005 interview with Techworld, Moore confirmed that the eventual obsolescence of the law is unavoidable:

It can't continue forever. The nature of exponentials is that you push them out and eventually disaster happens.

In terms of [transistor] size you can see that we're approaching the size of atoms which is a fundamental barrier, but it'll be two or three generations before we get that far—but that's as far out as we've ever been able to see. We have another 10 to 20 years before we reach a fundamental limit. By then they'll be able to make bigger chips and have transistor budgets in the billions. [7]

The International Technology Roadmap for Semiconductors has used Moore's law as a primary driving force behind their industry roadmaps since 1998. However, in 2016, with the general acknowledgement that Moore's law is slowing down, a final roadmap was published and the organization was succeeded by the International Roadmap for Devices and Systems, whose aim is to provide a more generalized approach to roadmapping [8], [9].

Historically, the semiconductor industry has considered transistor miniaturization to be among the most effective design paradigms in terms of generally improving computing power. While there is still some room to further shrink transistors, the breakdown of Dennard scaling and deceleration of Moore's law indicate that we must look beyond transistor scaling if we hope to continue driving performance. This presents a unique opportunity in that there is an unprecedented push to explore alternate methods of improving computational performance. This push to develop new techniques for improving performance has been a significant driving force behind the emergence of approximate computing as a field of research.

#### 1.1.2 Trends in Data Processing Applications

An application is said to be error resilient if it can produce useful results despite some level of computational error. In [10], several application characteristics corresponding to error resilience are identified. The ability to handle input noise is indicative of error resilience, due to the fact that noise is essentially the consistent occurrence of small, unpredictable errors. Similarly, the ability to handle redundant inputs also improves error resilience, as it suggests that certain computations may be entirely skipped over without significant issue. The absence of a unique golden output also corresponds to error resilience, where a perfect output may be lacking due to the occurrence of multiple equally-desirable outcomes, or because the optimality of the result is inherently unknown. Applications also tend to be error resilient if their result is interpreted by limited human perception, e.g. a computer will analyze an image and detect erroneous pixels with much greater speed and accuracy than a human. Finally, an application may be error resilient due to certain algorithmic features that favor the mitigation of errors. For example, any application implementing iterative refinement will be error resilient because errors generated are naturally reduced by the algorithm.

The decreasing cost of storage, commodification of data sensors, and widespread use of complex computational models for a variety of applications has lead to the emergence of data-intensive computing as a field of research. Popular applications involving large datasets include multimedia processing, data mining, data analytics, neural networks, and computer vision. In [11], Gorton defines data-intensive computing as "managing, analyzing, and understanding data at volumes and rates that push the frontier of current technologies." By definition, conventional processing techniques tend to be ineffective in handling data-intensive applications, and thus new approaches must be explored. Many data-intensive applications are error resilient since input noise and redundant data are so common, and the lack of a golden output is also not unusual. Additionally, applications such as machine learning make use of highly iterative techniques, and therefore exhibit a high degree of error tolerance. The prevalence of error resilient applications has been a significant driving factor behind the development of approximate computing techniques, and the unique challenges associated with data-intensive processing deepens this motivation.

## **1.2** Approximate Computing as a Field of Research

Approximate computing in the most general sense involves the intentional introduction of error to a computation in order to improve performance. This section provides a survey of approximation techniques applied at all levels of the computing hierarchy. Softwarelevel techniques are discussed in Section 1.2.1, architecture-level techniques are reviewed in Section 1.2.2, and circuit-level techniques are examined in Section 1.2.3. Because this thesis focuses on the application of approximate computing to arithmetic hardware, a study of these techniques is omitted from Section 1.2.3, and a comprehensive literature review is instead provided in Chapter 2.

#### 1.2.1 Software-Level Techniques

Software approximation encompasses a wide variety of methods at varying levels of abstraction. At the higher level, approximation-aware programming languages enable the programmer to directly indicate acceptable levels of accuracy for various computations executed in their program. In the programming language Eon [12], paths through a program occupy different energy states set by the programmer, which generally correspond to rate of execution priority. Eon's automatic energy management then dynamically adapts these states according to currently available and predicted energy levels. In [13], a Java extension EnerJ uses type qualifiers to declare data for which approximate computations may be performed. These type qualifiers indicate to the system how the data should be handled, where approximate data is mapped to low-power storage, operated on using low-power computations, etc. The programming language Rely proposed in [14] supports quantitative reliability specifications for results produced by a function, which essentially defines the minimum acceptable reliability for the function to be called. A static quantitative reliability analysis is used to verify the quantitative requirements on the reliability of a program, effectively verifying that the program satisfies its reliability specification when executed on the underlying unreliable hardware.

Approximate computing can also be applied in software at lower levels of abstraction. Loop perforation is a technique in which computation loops are transformed to execute only a subset of their iterations. In [15], a criticality testing phase filters out all critical loops to identify tunable loops, i.e. any loop whose perforation does not result in unacceptable accuracy degradation. Loop perforation is also utilized in [16], in which the accuracy loss produced by approximation is modelled and subsequently used to make approximation decisions, such as determining whether to terminate a loop early. In parallel systems, relaxed synchronization introduces approximation by waiving some of the synchronization requirements preventing concurrent accesses to shared data. Relaxed synchronization is used in [17] to improve per-core utilization for the computation of large-scale quadratic programming problems by relaxing the requirement that full synchronization be achieved after each iteration and additionally permitting mid-iteration synchronization.

#### 1.2.2 Architecture-Level Techniques

Approximate computing can be applied at the architecture-level in a variety of ways. Memoization is an instruction-reuse technique in which the result of an instruction or group of instructions is stored so that it may be reused in the case of an identical instruction call. However, the storage of these results requires resources and therefore it is only beneficial if there is a certain level of data reuse. In fuzzy memoization, stored data may be reused not only in the case of identical inputs but also for similar inputs, allowing for a greater level of data reuse. The tolerance of multimedia applications is exploited in [18], where fuzzy memoization is used for floating-point operations, resulting in energy improvements of 12%. In the case of a load miss in a private cache, data typically needs to be retrieved from main memory or higher-level caches, resulting in additional energy consumption and latency. These costs can be mitigated using a technique called load value approximation [19] in which value patterns are learned so that an approximate data value may be generated in the case of a load miss, thereby avoiding the need to stall during the time it takes to fetch the data and improving speedup by an average of 8.5%.

While a variety of approximate accelerators have been proposed for use in specialized applications, the development of neural network accelerators has received notable atten-

tion. A general-purpose limited-precision code accelerator for error tolerant applications is introduced in [20] in which approximable regions of code are automatically transformed from a von Neumann model to an analog neural model. An approximate computing framework for artificial neural networks is proposed in [21] in which the impact of neurons on the output quality is characterized so that the computations and memory accesses for less critical neurons may be approximated. In [22], the Parrot transformation is presented which selects and trains a neural network to mimic a region of imperative code. Once the learning stage is complete, the compiler replaces the code with an instance of a low power accelerator, i.e. a neural processing unit (NPU). A new approach to implementing hardware-efficient large-scale neural networks is presented in [23] in which neural networks are approximated by firstly adapting the backpropagation technique to indicate the impact of approximating a given neuron, and secondly approximating the neurons found to have the smallest impact on output quality. In [24], an accelerator is used to address the issue of branch divergence in single instruction, multiple data architectures by training neural networks offline to approximate those regions of code with degraded performance due to branch divergence, and subsequently replacing the code regions with their neural network approximations. In [25], approximate programs are accelerated via a NPU implemented in a field-programmable gate array (FPGA), where the proposed accelerator is designed for use with a compiler workflow that automatically configures the neural network topology and weights, rather than the programmable logic itself.

A number of approximate general-purpose processors have been proposed in the literature. These architectures generally provide some degree of configurability as to allow for use not only in error-tolerant applications, but also generic applications with stricter accuracy requirements. An error resilient system architecture is proposed in [26], where high error resilience is achieved by mixing processor cores with varying reliability levels, utilizing error resilient algorithms at the core of probabilistic applications, and performing intelligent software optimizations. In [27], the minimum error-protection required for streaming applications is analyzed, and microarchitectural techniques are proposed to mitigate errors arising in a general-purpose processor built from an unreliable fabric. A processor is designed in [28] for use in recognition and mining, where a 2-D array of processing elements, a streaming memory hierarchy, and an interconnect network allow for the efficient execution of dominant computational kernels from a wide range of recognition and mining applications. This work is extended in [29] in which the authors present an automatic resilience characterization framework designed to quantitatively evaluate the intrinsic error resilience of a given application. This framework is used alongside accuracyscalable hardware that can be dynamically configured at runtime according to application requirements and data characteristics. The authors extend this work again in [30], where they further refine the scalable effort design approach, stating that mechanisms for modulating computational effort should be sought at all levels of design abstraction,

emphasizing that maximal exploitation of error resilience requires the cross-layer optimization of scaling mechanisms identified at all layers of abstraction. An energy efficient, quality programmable vector processor is proposed in [31], where the notion of quality is explicitly codified in the instruction set architecture (ISA) via the use of instructions for which an associated quality field indicates the minimum level of accuracy that must be met during execution. In [32], the authors observe that the memory hierarchy tends to be overlooked in favor of applying approximation in the data path. In order to realistically model the relationship between performance improvements and accuracy, errors occurring both along the data path and in the memory hierarchy are analyzed using an energy model that expresses its findings in terms of operations per virtual Joule, a relative metric that is independent of implementation technology.

#### 1.2.3 Circuit-Level Techniques

While the majority of circuit-level approximation techniques feature inexact arithmetic units as explored in Chapter 2, there are several other methods worth discussing here. While dynamic RAM (DRAM) memory tends to be fast, the storage capacitor within each memory cell must be periodically recharged for it to maintain its data value, resulting in additional power usage. Approximation can be applied by reducing the rate of DRAM refresh, thereby lowering power consumption at the risk of corrupting data stored in the DRAM cells. An application-level technique is proposed in [33] which allows developers to specify critical and non-critical data for their programs, where the storage location for the data is selected by the runtime system accordingly. The refresh rate for the memory containing non-critical data can then be reduced, resulting in lowered power consumption. In [34], embedded DRAM-based frame buffers are segmented into four tiers, each with a different refresh rate, reducing power consumption by an impressive 48% while maintaining adequate performance. Voltage overscaling (VOS) is a technique in which the supply voltage for a given circuit is reduced without modifying the operational frequency, lessening power consumption at the risk of analog values. An early example of approximate computing can be found in [35], where a digital signal processing block is approximated by pairing VOS with algorithmic noise tolerance schemes which perform error compensation. In [36], several meta-functions are characterized as computational kernels common to error resilient applications. An assortment of design techniques are utilized to allow the hardware implementation for these meta-functions to scale more gracefully under VOS. In [37], hardware for a proposed ISA extension utilizes dual-voltage operation, where high voltage is used for precise computations, and low voltage is used for inexact operations.

## 1.3 Contributions of the Thesis

The main contributions of this thesis are as follows:

#### 1. Approximate Booth multipliers

Two approximate partial product generators PPG-1S and PPG-2S are proposed which utilize only one or two encoding signals, respectively. The first multiplier ABM-M1 utilizes PPG-2S to approximate the partial products in its least-significant columns. The second multiplier ABM-M2 uses PPG-2S to replace the least-significant partial products of each row with a signal approximate partial product. The third multiplier ABM-M3 utilizes PPG-1S to replace all bits in each row, for a significance below a certain value, with a single approximate partial product. The designs are evaluated in terms of accuracy and hardware, and their operation is verified using several image processing applications.

#### 2. Approximate restoring dividers

Two approximate restoring dividers are proposed, where the first design AXRD-M1 utilizes a novel approximate restoring divider cell in its least-significant columns to reduce hardware cost. The second divider AXRD-M2 eliminates several rows from the cell array such that only a subset of the trial subtractions are computed, after which the partial remainder the divisor are rounded and encoded in order to estimate the remaining quotient bits. The accuracy and hardware performance of the dividers is investigated, and their functionality is verified using change detection and foreground extraction applications.

#### 3. Approximate MAC unit

The Booth multiplier ABM-M3 is used as a basis for designing an approximate Booth multiplier-based MAC (ABM-MAC) unit, where the critical path delay is reduced by fusing the accumulation with the multiplier compression. The accuracy and hardware performance of ABM-MAC are evaluated alongside several other approximate MAC units for benchmarking purposes. The accuracy-performance tradeoff is additionally evaluated using combined accuracy-hardware metrics, and the proposed design is functionally verified using a convolution application.

## 1.4 Publications and Submissions during M.Sc. Study

## 1.4.1 Published Journal

S. Venkatachalam, E. Adams, H. J. Lee, and S. Ko, "Design and analysis of area and power efficient approximate Booth multipliers," *IEEE Trans. Comput.*, vol. 68, no. 11, pp. 1697–1703, 2019. DOI: 10.1109/TC.2019.2926275

A Major portion of this paper is included in Chapter 3: Approximate Booth Multipliers.

E. Adams, S. Venkatachalam, and S. Ko, "Approximate restoring dividers using inexact cells and estimation from partial remainders," *IEEE Trans. Comput.*, vol. 69, no. 4, pp. 468–474, 2020. DOI: 10.1109/TC.2019.2953751

A Major portion of this paper is included in Chapter 4: Approximate Array-Based Restoring Dividers.

### 1.4.2 Published Conference

E. Adams, S. Venkatachalam, and S. Ko, "Energy-efficient approximate MAC unit," in *Proc. 2019 IEEE Int. Symp. Circuits and Syst. (ISCAS)*, 2019, pp. 1–4. DOI: 10.1109/ISCAS.2019.8701880

A Major portion of this paper is included in Chapter 5: Approximate Fixed-Point MAC Unit.

S. Venkatachalam, E. Adams, and S. Ko, "Design of approximate restoring dividers," in *Proc. 2019 IEEE Int. Symp. Circuits and Syst. (ISCAS)*, 2019, pp. 1–5. DOI: 10.1109/ISCAS.2019.8702363

A Major portion of this paper is included in Chapter 4: Approximate Array-Based Restoring Dividers.

## 1.4.3 Submitted Journal

E. Adams, S. Venkatachalam, H. J. Lee, and S. Ko, "Convolution using an approximate radix-4 Booth multiplier-based MAC unit," *IEEE Trans. Circuits Syst. I*, 2020, submitted.

A Major portion of this paper is included in Chapter 5: Approximate Fixed-Point MAC Unit.

## 1.5 Organization of the Thesis

The thesis is organized as follows:

- Chapter 1: Introduction describes the motivation behind the research presented in this thesis, the history of approximate computing as a field of research, the contributions provided in this thesis, the publications and submissions made during the M.Sc. study, and the organization of this thesis.

- Chapter 2: Review of Contemporary Approximate Arithmetic Designs provides a review of contemporary works in the literature which feature approximate arithmetic hardware. The approximate designs reviewed include adders, multipliers, dividers, and MAC units.

- Chapter 3: Low-Power Approximate Booth Multipliers presents three inexact radix-4 Booth multipliers which utilize approximation techniques in the partial product generation stage via the use of two novel inexact partial product generators (PPGs).

- Chapter 4: Approximate Array-Based Restoring Dividers proposes two inexact array-based restoring dividers in which approximation is applied using inexact divider cells as well as quotient estimation from rounded and encoded values.

- Chapter 5: Approximate Fixed-Point MAC Unit presents an inexact MAC unit which utilizes one of the PPGs introduced in Chapter 3 alongside other approximation techniques.

- Chapter 6: Conclusions and Future Work provides a summary of this thesis and discusses potential future works.

# Chapter 2

# Review of Contemporary Approximate Arithmetic Designs

This chapter provides an overview of approximate arithmetic hardware in the literature. Approximate adders are reviewed in Section 2.1, inexact multipliers are surveyed in Section 2.2, inexact dividers are discussed in Section 2.3, and approximate MAC units are examined in Section 2.4. For each type of arithmetic unit, the most prominent approximate designs in the literature are explored.

### 2.1 Approximate Adders

The half-adder and full-adder architectures are simple and make use of few logic gates. Thus, the works in the literature that propose approximate half- and full-adder designs generally involve modifying the adder architecture at the transistor-level to improve hard-ware efficiency. In [43], the logical complexity of the conventional mirror adder is reduced to generate four approximate designs exhibiting a substantial reduction in power dissipation. Similarly, approximate XOR/XNOR-based adders are introduced in [44], where the adder designs are based on XOR/XNOR-gates modified at the transistor-level for which the multiplexer operation is implemented using pass transistors.

A wide variety of inexact multi-bit adders utilizing gate-level approximation can be found in the literature. Considering the addition of *n*-bit operands X and Y, a conventional parallel adder generally computes a given carry-out  $c_i$  as a function of all previous input bits, i.e.  $c_i = f(x_{i-1}, y_{i-1}, \ldots, x_0, y_0)$ , meaning that the critical path delay of the adder is proportional to log *n*. One of the earliest approximate adders in the literature is a modified parallel adder introduced by Lu et al. in [45], for which the carry of a given stage considers only up to the previous k inputs, i.e.  $c_i = f(x_{i-1}, y_{i-1}, \ldots, x_{i-k}, y_{i-k})$  where  $0 \le k \le i + 1$ . Consequently, the critical path delay of the adder is proportional to log k, and the selection of  $k = \sqrt{n}$  reduces the delay by half. A fast inexact adder based on the carry-lookahead adder (CLA) architecture is proposed in [46], where a kill signal indicates that the carry bit be set to zero in the case that both input bits are zero, resulting in the dependence of the current carry on the previous carry only if neither kill nor generate are high. This inexact adder is then used as a component in a reliable variable latency adder which utilizes error detection and error recovery to guarantee a correct result. In [47], an inexact adder is proposed in which the addition is split so that the k most-significant bits are computed using a precise adder and the remaining n - k bits are computed in parallel by OR-ing the respective input bits.

Numerous approximate adders in the literature make use of segmentation, a technique in which the inputs of a parallel addition are divided into k-bit segments and the carryout for a given segment is computed using only its k input bits. Zhu et al. [48] introduce an error tolerant adder whose inaccurate part is comprised of a carry-free addition block and a control block, where the carry-free addition utilizes a modified XOR-gate. In [49], this work is extended with the proposal of a second adder architecture in which the carry propagation path is split into several segments over which carry propagation is performed concurrently. A modified version of this design is also presented in [49], where the carry generators of each segment are cascaded as to improve accuracy in the most-significant block at the expense of increased delay. This work is again extended in [50], where a third error tolerant adder utilizes a selector circuit to determine the number of bits to be divided into the accurate and inaccurate parts. Zhu et al. extend this work a final time in [51] by proposing a carry-select adder (CSA)-based design in which the addition is segmented into k-bit blocks whose carry chains are each broken into two stages, thereby improving the accuracy of the most-significant block without incurring additional delay. In [52], a novel function speculation technique is proposed which takes advantage of the low probability of long carry chains. The addition operands are segmented into windows of k consecutive input bits, where the carry-out of each window is speculated using only the k input bits of the window. A variable latency CSA is also proposed in [52], in which a fast addition is performed by utilizing speculation-based adders.

The literature also features adder designs in which accuracy can be configured at runtime. In [53], the proposed accuracy-configurable adder is divided into four stages, i.e. an approximate addition followed by three error correction stages, where the error correction stages can be selectively enabled or disabled to provide different levels of computational accuracy. In [54], an approximate adder is proposed where the addition operands are split into k-bit segments each implemented by a k-bit adder. The adder units are connected using multiplexers which select a carry-in from either the previous adder unit or the carry-in prediction component of the given adder unit, allowing for runtime configurability.

### 2.2 Approximate Multipliers

The application of approximate computing to multipliers has been widely explored in the literature. Section 2.2.1 discusses approximate multiplier designs derived from the AND-

array architecture, Section 2.2.2 reviews logarithmic multipliers, Section 2.2.3 surveys approximate Booth multipliers, and Section 2.2.4 explores multipliers utilizing approximate compression techniques.

#### 2.2.1 Approximate AND-Array Multipliers

For an *n*-bit multiplication  $X \times Y$ , the AND-array multiplier architecture produces a partial product matrix for which the partial product bit  $pp_{ij}$  corresponding to the *j*th bit of the *i*th partial product is generated using a single AND-gate to compute  $x_i y_j$ . In [55], an error tolerant multiplier is proposed in which the input operands are split into a higher-order part and a lower-order part. A reduced width multiplier is used to compute the product of the higher-order bits, while the remaining product bits are approximated according to the position of the leading-one within the lower-order bits of each operand. The carry propagation path in the resulting architecture is limited to that of the higher-order part, and the reduction of the partial product matrix results in substantial power savings. An underdesigned multiplier architecture is proposed in [56], where an inaccurate  $2 \times 2$  multiplier block is used to implement larger multipliers. Tunable accuracy can then achieved by selectively replacing inaccurate  $2 \times 2$  blocks with the accurate version. In [57], a novel inaccurate 4:2 counter is used to build an approximate  $4 \times 4$  Wallace multiplier. The  $4 \times 4$  multiplier can then be used to build arbitrarily large multipliers for which power consumption is substantially reduced. An accurate version of the multiplier is also proposed, where error detection and error correction compensate fully for all inaccuracies while only marginally increasing area and power consumption. Similarly, an approximate Wallace-tree multiplier is proposed in [58] in which a  $2n \times 2n$  multiplication is implemented using an accurate  $n \times n$  multiplier for the most-significant block and three inaccurate  $n \times n$  multipliers for the remaining blocks. Additionally, carry-in precomputation is used to exploit the fact that the occurrence of at least two 1s in the critical column of the partial product matrix results in a carry of at least 1 being propagated to the next column. A dynamic segmentation method proposed in [59] extracts a continuous k-bit segment from an n-bit operand for  $k \ge n/2$ , where the segment may only start from one of several fixed positions dependent on the location of the leadingone in the operand. The multiplication is then implemented using a  $k \times k$  multiplier, several multiplexers, and a few additional gates, resulting in a significant power reduction over the conventional architecture. In [60], a multiplier is designed to have an unbiased error distribution, leading to lower computational errors during application. The multiplier utilizes a leading-one detector (LOD) to locate the leading-one in each operand, and then selects the following k-2 bits, where k is a designer-defined value selected in accordance with accuracy requirements. Error is reduced by assuming a uniform error distribution and setting the value of the remaining lower bits to the nearest one-hot median value. An inexact multiplier is proposed in [61] in which the operands are rounded to their nearest power of two, allowing for a simplified multiplication to be performed using three shift operations and two addition/subtraction operations. Three hardware implementations are presented which utilize computation blocks for sign detection, rounding, shifting, addition, subtraction, and sign selection.

#### 2.2.2 Logarithmic Multipliers

The logarithmic multiplier (LM), originally introduced in [62], converts the multiplication operands to inexact logarithmic numbers so that an inexact product may be computed using only bitshifting and addition. More specifically, the binary operands of the multiplication  $X \times Y$  can be expressed as

$$\log_2 X = k_1 + \log_2(1 + x_1), \quad \text{where } 0 \le x_1 < 1, \tag{2.1}$$

$$\log_2 Y = k_2 + \log_2(1 + x_2), \quad \text{where } 0 \le x_2 \le 1, \tag{2.2}$$

in which  $k_1$  and  $k_2$  are the characteristics of X and Y, respectively, meaning that they indicate the position of the leading-one in the unsigned binary representations. The product P and its logarithm can then be expressed as

$$P = X \times Y = 2^{k_1 + k_2} (1 + x_1) \times (q + x_2), \tag{2.3}$$

$$\log_2 P = k_1 + k_2 + \log_2(1 + x_1) + \log_2(1 + x_2).$$

(2.4)

As  $\log_2(1 + x) \approx x$  when  $0 \leq x < 1$ , the logarithmic product can be approximated as

$$\log_2 P \approx k_1 + k_2 + x_1 + x_2. \tag{2.5}$$

The computation described in (2.1)–(2.5) is implemented by performing leading-one detection on each operand, converting the operands to their logarithmic equivalents, summing  $k_1 + x_1$  and  $k_2 + x_2$ , and converting the result to its binary form. The LM does not generate partial products and thus does not require the use of partial product generators or partial product accumulation trees, allowing for substantially reduced hardware complexity. The LM generates significant errors, so contemporary works have aimed to refine the design and improve its accuracy. In [63], the size of the approximate fraction in the LM is kept proportional to its precision via the use of truncation. The least-significant bits are rounded off in the approximate log and anti-log conversions, resulting in reduced hardware costs. In [64],  $\log_2 x$  is approximated by rounding x to its nearest power-of-two rather than the highest power-of-two smaller than or equal to x. The multiplication can be rewritten as

$$X = m_1 + q_1$$

, where  $m_1 = 2^{k_1}$ , (2.6)

$$Y = m_2 + q_2$$

, where  $m_2 = 2^{k_2}$ , (2.7)

$$X \times Y \approx \left(2^{k_1 + k_2} + q_2 2^{k_1} + q_1 2^{k_2}\right) + q_1 q_2. \tag{2.8}$$

As indicated in (2.8), the least-significant term is ignored as approximation error. Based on the LOD structure, a nearest-one detector (NOD) circuit determines the nearest powerof-two for each operand. The required number of shifts is then determined using a priority encoder according to the output of the NOD. The three terms are then summed using a combination of exact and approximate adders.

A LM implementation utilizing an iterative approach is proposed in [65], where a correction term is computed and added to the approximate product to increase accuracy. The correction term is computed concurrent to the product, and therefore no additional delay is incurred. A new truncation scheme is introduced to reduce the area overhead of the iterative error correction. Designs for both iterative and non-iterative LMs are proposed in [66], where inexact adders are utilized during the mantissa addition. The lower-part OR-adder from [47], the third inexact mirror adder design from [43], and a novel inexact adder architecture are utilized in the mantissa addition, allowing for a substantial reduction in power-delay product (PDP).

#### 2.2.3 Approximate Booth Multipliers

The radix-4 Booth multiplication algorithm, also known as the modified Booth algorithm, is a popular multiplication architecture in which the number of partial products is reduced by encoding the multiplicand as a set of radix-4 digits. The multiplicand is examined in overlapping 3-bit groups  $\{y_{2i+1}, y_{2i}, y_{2i-1}\}$ , and each group is encoded as a radix-4 value in the range [-2, 2] via the use of a modified Booth encoder (MBE) circuit. Each encoded digit is expressed using three encoding signals, i.e.  $neg_i$ ,  $two_i$ , and  $zero_i$ . A PPG takes as input the encoding signals along with multiplier bits  $x_j$  and  $x_{j-1}$  to compute the *j*th bit of the *i*th partial product  $pp_{ij}$ . For a signed  $n \times n$  multiplication, the height of the resulting partial product matrix is reduced to  $\lceil n/2 \rceil$ . Because the partial product generation of the Booth multiplier has additional complexity, a number of works apply approximation to the MBE or the PPG to reduce hardware cost. In [67], a MBE is proposed in which four novel encoding signals are generated. The delay incurred in the encoder is equal to that of the fast conventional encoder, and the decoder requires two fewer transistors when compared to the conventional design. The structure of the partial product matrix is also modified by combining the least-significant bit (LSB) of each row with its corresponding signcorrection term as to make the matrix more regular. The final summation is performed using a novel adder which combines the properties of the conditional-sum adder and the conditional-carry adder. An approximate Wallace-Booth multiplier is proposed in [68], where an inexact MBE, an approximate 4:2 compressor, and an approximate tree structure are utilized. Rather than generating encoding signals and passing them to the PPG, the approximate MBE computes the partial product bit in terms of three multiplier bits and a single multiplicand bit, generating errors in only 2/16 input combinations. The approximate 4:2 compressor utilized during compression is the second design from [69]. Finally, the approximate tree structure eliminates a compression stage by utilizing the approximate compressor in the n/2 least-significant columns of the matrix and eliminating the most-significant sign-correction term. An approximate Booth multiplier is presented in [70], where two inexact encoding algorithms are utilized alongside an approximate Wallace tree. Both of the proposed encoders express the partial product as a direct function of the multiplier and multiplicand bits, introducing error in 4/32 and 8/32 cases, respectively. Similar to [68], the number of compression stages in the Wallace tree is reduced by ignoring the most-significant sign-correction term.

The literature also features a number of approximate multipliers that make use of higher-radix Booth encoding. The radix-8 Booth algorithm tends to be less popular due to the complexity in generating partial products corresponding to  $\pm 3X$ . In [71], an approximate 2-bit adder is designed for calculating this partial product by summing  $\times 1X$  and  $\times 2X$ . Two approximate radix-8 multipliers utilizing this adder are proposed, where each multiplier is implemented for several truncation widths. In [72], a hybrid high-radix encoding scheme is used to improve multiplier performance. In the proposed encoding scheme, the *n*-bit multiplicand is divided into two parts: the higher-order part of n-k bits, and the lower-order k-bit part, where the configuration parameter k is an even number such that  $k \geq 4$ . The higher-order part is encoded using radix-4 Booth encoding to maintain accuracy, while the lower-order part utilizes a high radix- $2^k$  encoding to reduce hardware cost. Three multipliers are implemented for which the lower-order part is encoded using radix-64, radix-256, and radix-1024 encoding, respectively. Compared to the accurate radix-4 multiplier, the proposed designs reduce area and power consumption by up to half while producing an error with a Gaussian distribution and a near-zero average.

#### 2.2.4 Multiplication using Approximate Compressors

Partial product accumulation is often the most resource-intensive stage of the multiplication operation. Thus, a number of approximate compressors have been proposed for use in reducing the complexity of the accumulation tree. In [69], two inexact 4:2 compressors are proposed and subsequently verified for use in partial product accumulation. The first approximate compressor leverages the fact that the *carry* output for an exact compressor is equal to  $c_{in}$  in 24 of 32 input states by simplifying *carry* to  $c_{in}$ . Because the *carry* output has a higher weight than the other outputs and produces a difference of 2 when incorrect, partial error compensation is provided by setting the sum output to 0 in the case that  $c_{in} = 1$ . The  $c_{out}$  output is also modified to compensate for errors associated with *carry* and *sum*. The result of these modifications is an incorrect output in 12/32 cases. Because the carry and  $c_{out}$  outputs have the same weight, their equations are simply interchanged in the second compressor design, resulting in an output error rate of 4/16. Several  $n \times n$  multipliers are implemented, where exact compressors are replaced with one of the proposed compressors for either the entire partial product matrix or the n-1 least-significant columns. The use of approximate compressors in the n-1 least-significant columns provides a good balance between improving hardware performance and maintaining accuracy. Three approximate 4:2 compressors are proposed in [73], where the  $c_{in}$  and  $c_{out}$  signals are ignored. The inexact compressors are utilized in a  $8 \times 8$  multiplier with Dadda-tree accumulation, where the four least-significant product bits are truncated and the next four least-significant product bits are accumulated using the proposed compressors. In [74], the compressor designs from [69] and [73] are modified for use alongside error recovery modules, resulting in a multiplier design with higher accuracy, smaller area, and lower power consumption. Approximate designs for a 2:1 compressor, 3:2 compressor, 4:2 compressor, 5:3 compressor, and 6:3 compressor are introduced in [75], where the optimal allocation of approximate compressors for a given multiplier is determined using a novel algorithm. The proposed compressors and allocation algorithm are tested for several operand lengths and are shown to provide substantial reductions in power and delay.

## 2.3 Approximate Dividers

Division as an operation is not nearly as ubiquitous as multiplication. In the an average computer program, multiplications occur with a much greater frequency than divisions. Because of its lower utilization, the design of approximate dividers has received relatively little attention. Additionally, while the partial products of a multiplication can be generated in parallel, division is a sequential operation and thus is more challenging to approximate, due to the fact that the error produced at a given stage will propagate to all following stages. Division is commonly implemented using an array-based architecture which implements either a restoring or non-restoring division algorithm. A restoring 2n/n division performs the operation over *i* iterations, where each iteration involves the subtraction of the divisor from the shifted partial remainder to produce a trial difference. If the result of the subtraction is non-negative, the quotient bit for the current iteration is set to 1 and the partial remainder is loaded with the value of the trial difference. If the subtraction produces a negative result, the quotient bit is set to 0 and the partial remainder is restoring division, the result of the subtraction instead selects a quotient bit from the set  $\{-1, 1\}$  so that restoring the value of

the partial remainder is not necessary. The non-restoring division architecture requires an additional remainder correction circuit to correct the final remainder in the case that it is negative. Array-based division utilizes a matrix of divider cells, where each row computes an iteration of the division. In [76], three transistor-level approximations of the full-subtractor are presented. Three corresponding designs are then proposed in which the conventional subtractor of the divider cell is replaced with the approximate subtractor for a portion of the array, where four different cell-replacement schemes are explored. The authors of [76] extend their work to restoring dividers in [77], where the inexact subtractor cells proposed in [76] are utilized in three restoring divider designs. In [78], the proposed divider computes the division of a *n*-bit dividend by a n/2-bit divisor by utilizing a LOD to dynamically select for each operand a predefined number of consecutive bits starting at the leading-one, which are then routed to an accurate core divider. The parameter krefers to the number of bits that are divided in the core divider, meaning that k dividend bits and k/2 divisor bits are selected. Priority encoders and multiplexers are used to route the selected bits to the core divider to compute a k/2-bit quotient which is then adjusted to a width of n/2 using a barrel shifter. A similar design is presented in [79], where LODs are used to select a portion of the bits from each input operand for routing to an accurate reduced-width divider. An additional error-correction block utilizes OR-gates to recover the error introduced by the shifter. In [66], the architectures of the logarithmic divider and the conventional array-based divider are combined in an approximate hybrid divider. Restoring divider cells are used to generate the most-significant bits (MSBs) of the quotient as to maintain accuracy, while the use of logarithmic division to compute the LSBs reduces hardware cost.

## 2.4 Approximate MAC Units

While approximate computing has been widely applied to atomic arithmetic operations, comparatively little work has been done to utilize approximation techniques in the MAC unit hardware. In [80], an inexact MAC unit is proposed in which the partial product terms of the multiplier are compressed using OR-gates to implement approximate counters, and a compensation term is introduced to improve accuracy. Designs are implemented for three levels of truncation, and the function of the proposed MAC unit is verified using a Gaussian kernel application. An inexact MAC unit is proposed in [81], which utilizes an approximate compression tree to improve hardware performance. The MAC operation is divided into two stages: (1) AND-based partial product generation, and (2) partial product accumulation via the compression tree. The proposed design implements a fused MAC architecture, where the previous accumulator value is inserted at the bottom of the generated partial product matrix so that it may be accumulated during partial product compression. The compression tree performs an approximate compression

over three stages to produce an intermediate product and two accuracy compensation vectors. The intermediate product and compensation vectors are subsequently compressed into a sum and carry, which are then summed to generate the final result. The functionality of the proposed MAC unit is verified in a Gaussian smoothing application, as well as a convolution operation within a neural network.

# CHAPTER 3

# Approximate Booth Multipliers

In this chapter, approximation is applied to the radix-4 Booth multiplication architecture to produce three inexact multiplier designs. Approximation is introduced in the partial product generation stage of the multipliers using two novel inexact PPGs which utilize a reduced number of encoding signals. In two of the proposed multipliers, the use of the approximate PPGs results in the reduction of the partial product matrix. The designs are evaluated alongside other state-of-the-art approximate multipliers, where MRED and NMED are used to measure accuracy, and hardware performance is evaluated in terms of area, power consumption, and area-power product (APP). The multipliers are utilized in applications for image transformation, matrix multiplication, and a finite impulse response (FIR) filter, where application performance is evaluated using peak signal-to-noise ratio (PSNR), MRED/NMED, and mean squared error (MSE), respectively.

Author contributions are firstly outlined in Section 3.1. Section 3.2 provides a background of radix-4 Booth multipliers, and Section 3.3 presents the inexact multiplier designs. Accuracy and hardware performance are evaluated in Section 3.4, and signal processing applications are presented in Section 3.5.

### **3.1** Author Contributions

S.V. conceived of and designed the proposed multiplier models. E.A. provided minor design contributions to the proposed models. S.V. and E.A. carried out the implementation of benchmarking models from the literature. S.V. and E.A. carried out the functional simulations and synthesis simulations. S.V. and E.A. analyzed the accuracy and hardware metrics of the implemented models. S.V. carried out the simulations for the signal processing applications. S.V. and E.A. wrote the manuscript in consultation with S.K.

|            | Input    |            | Encoded Signals |         |          | $(pp_{ij})_4$ |

|------------|----------|------------|-----------------|---------|----------|---------------|

| $y_{2i+1}$ | $y_{2i}$ | $y_{2i-1}$ | $neg_i$         | $two_i$ | $zero_i$ | $(rrij)_4$    |

| 0          | 0        | 0          | 0               | 0       | 1        | +0            |

| 0          | 0        | 1          | 0               | 0       | 0        | +X            |

| 0          | 1        | 0          | 0               | 0       | 0        | +X            |

| 0          | 1        | 1          | 0               | 1       | 0        | +2X           |

| 1          | 0        | 0          | 1               | 1       | 0        | -2X           |