### UNIVERSITÉ DE GRENOBLE

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Électronique

Arrêté ministériel : 7 août 2006

Présentée par

### Jae Woo LEE

Thèse dirigée par Mireille MOUIS et Gérard GHIBAUDO

préparée au sein du **Laboratoire IMEP-LAHC** dans **l'École Doctorale EEATS**

### Caractérisation électrique et modélisation des transistors à effet de champ de faible dimensionnalité

Thèse soutenue publiquement le **5 décembre 2011** devant le jury composé de :

M. Gérard GHIBAUDO DR CNRS Alpes-IMEP/INPG, Président M. Jong-Tae PARK Dr Incheon University, Rapporteur M. Jongwan JUNG Dr Sejong University, Rapporteur M. Gyu Tae KIM Dr Korea Univeristy, Co-directeur de thèse M. Laurent MONTÈS DR CNRS Alpes-IMEP/INPG, Membre Mme. Mireille MOUIS MCF INP Grenoble-IMEP, Directeur de thèse

Thesis for the Degree of Doctor

# Electrical Characterization and Modeling of Low Dimensional Nanostructure FET

by

Jae Woo LEE

# School of Electrical Engineering Graduate School Korea University

February 2012

金 奎 兌 教授指導 博 士 學 位 論 文

## **Electrical Characterization and Modeling of Low Dimensional Nanostructure FET**

이 論文을 工學博士 學位論文으로 提出함

2012 年 2月

高麗大學校 大學院

電子電氣工學科

李在祐

李 在 祐 의 工學博士 學位論文 審査를 完了함

2012 年 2 月

委員長 71 千 町 行乳 委員プレー 委員 이 제 杨 Mouis 委員 GHiBANDOG mand 委員 Mineille Trouis

# **Electrical Characterization and Modeling of Low Dimensional Nanostructure FET**

Ph.D. Thesis

Jae Woo, LEE

Thesis Advisor

Prof. Gyu Tae KIM School of Electrical Engineering, Korea University, Seoul 136-701, Republic of Korea

Prof. Mireille MOUIS (Dr. CNRS) and Prof. Gérard GHIBAUDO (Dr. CNRS) IMEP-LAHC, Grenoble INP-MINATEC, 3 Parvis Louis Néel, 38016 Grenoble, France

This Ph.D thesis prepared at Korea University, Korea and at IMEP-LAHC laboratory, INP-Grenoble, France under co-supervising program.

### The journey is the reward.

- Steve Jobs

### **English Abstract**

At the beginning of this thesis, basic and advanced device fabrication process which I have experienced during study such as top-down and bottom-up approach for the nanoscale device fabrication technique have been described. Especially, lithography technology has been focused because it is base of the modern device fabrication. For the advanced device structure, etching technique has been investigated in detail.

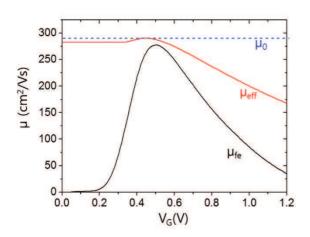

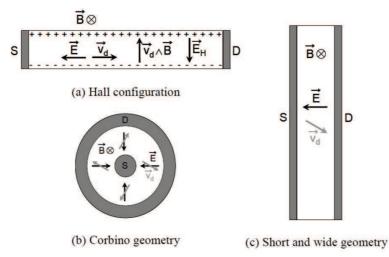

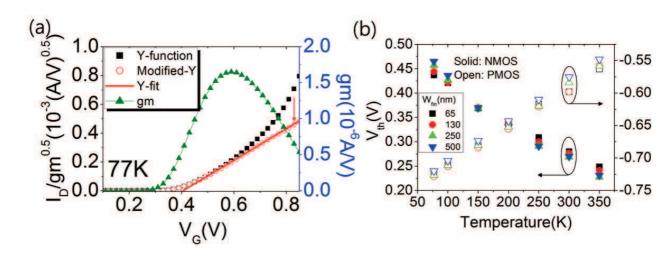

The characterization of FET has been introduced. For the practical consideration in the advanced FET, several parameter extraction techniques have been introduced such as Y-function, split C-V etc.

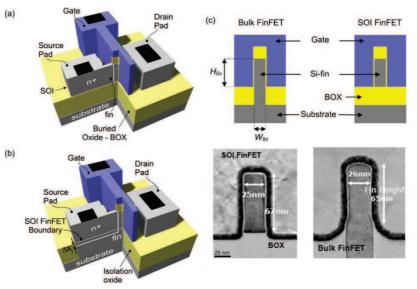

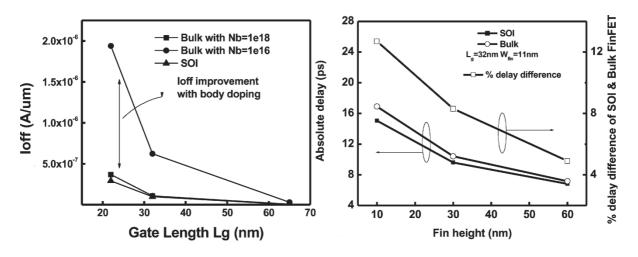

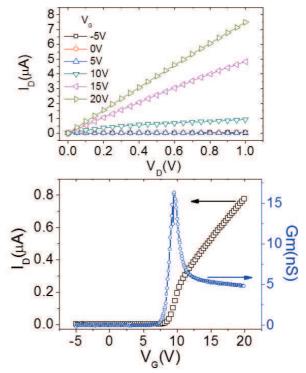

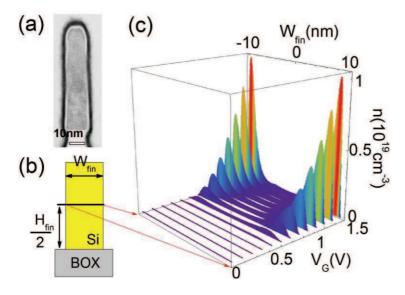

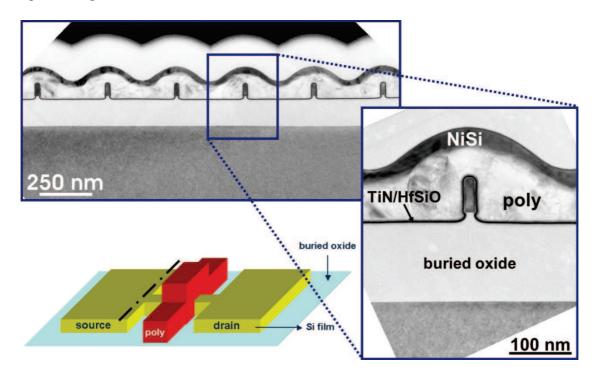

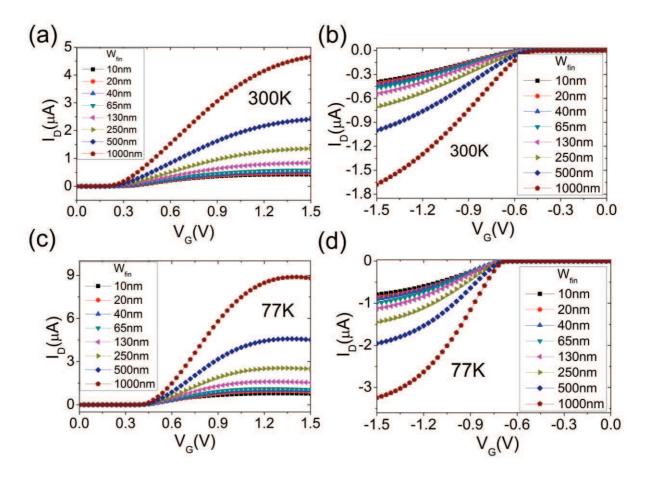

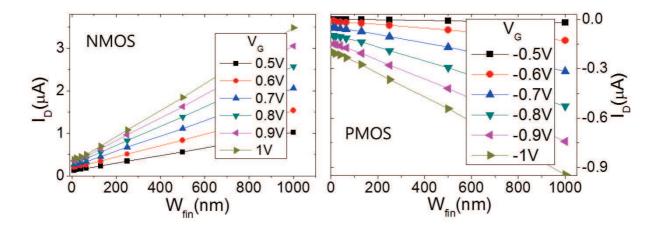

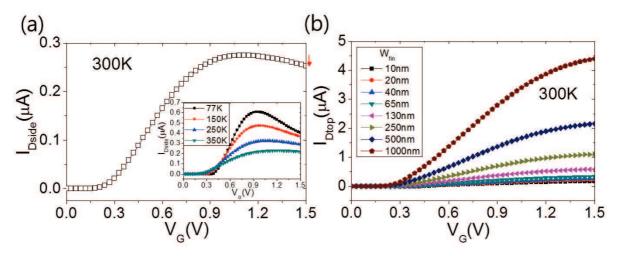

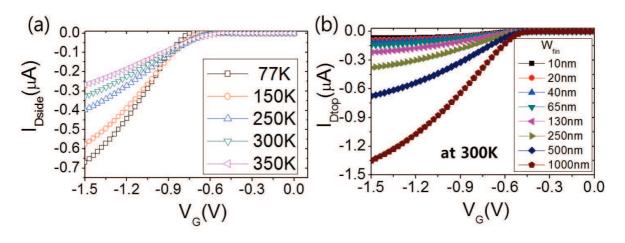

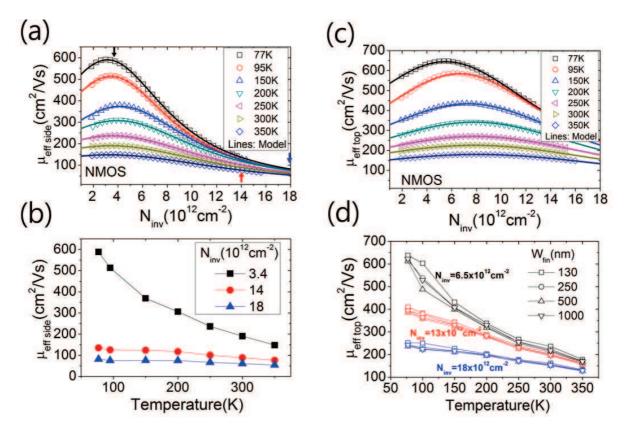

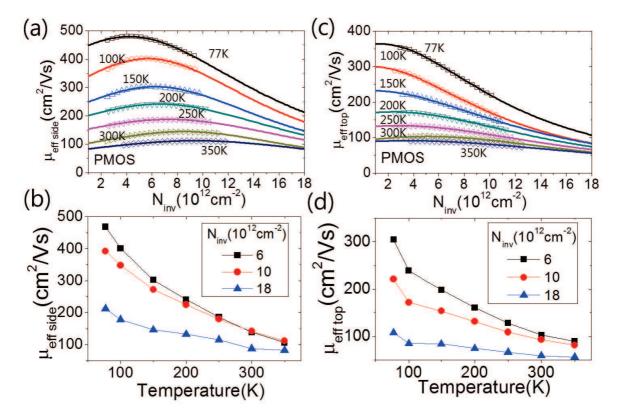

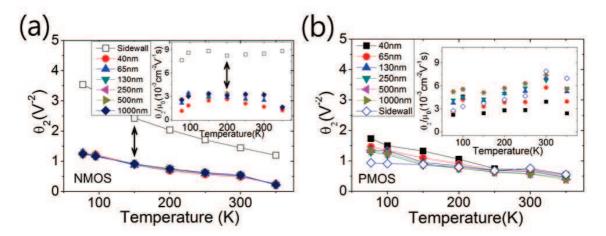

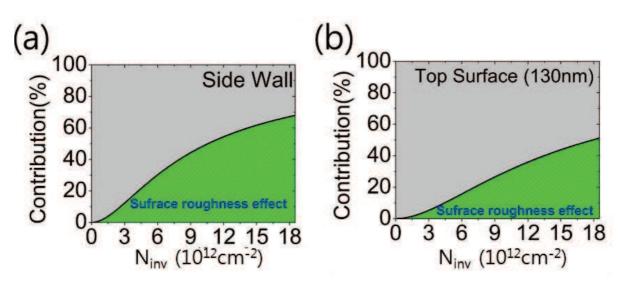

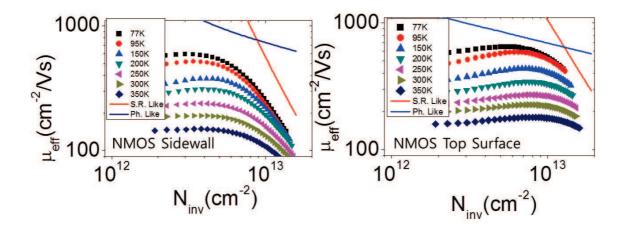

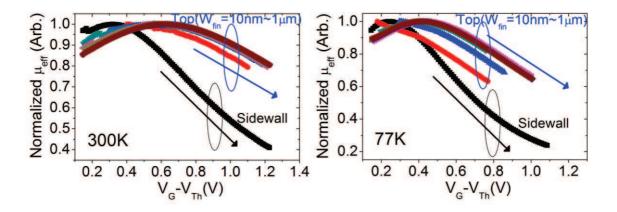

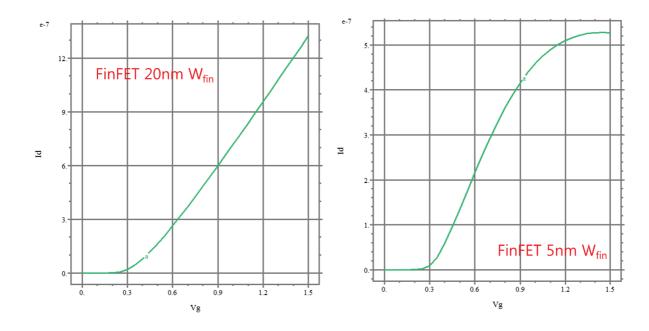

FinFET is one of promising alternatives against conventional planar devices. Problem of FinFET is surface roughness. During the fabrication, the etching process induces surface roughness on the sidewall surfaces. Surface roughness of channel decreases the effective mobility by surface roughness scattering. With the low temperature measurement and mobility analysis, drain current through sidewall and top surface was separated. From the separated currents, effective mobilities were extracted in each temperature conditions. As temperature lowering, mobility behaviors from the transport on each surface have different temperature dependence. Especially, in n-type FinFET, the sidewall mobility has stronger degradation in high gate electric field compare to top surface. Low temperature measurement is nondestructive characterization method. Therefore this study can be a proper surface roughness measurement technique for the performance optimization of FinFET.

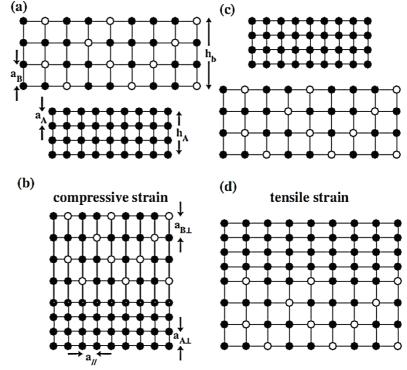

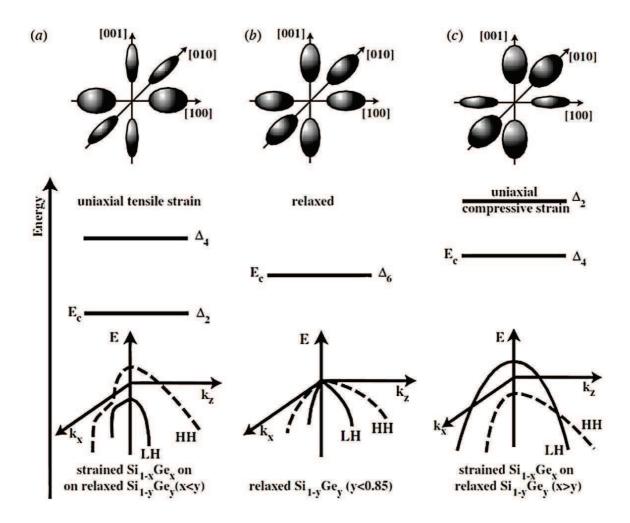

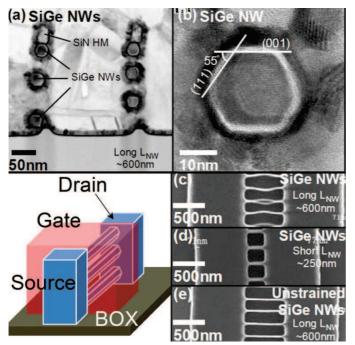

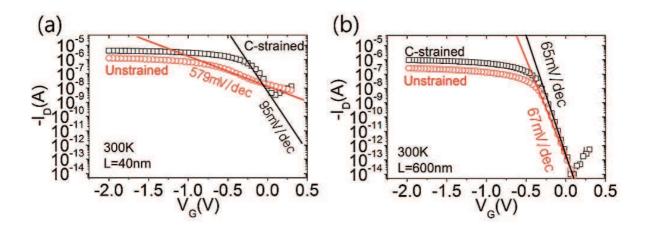

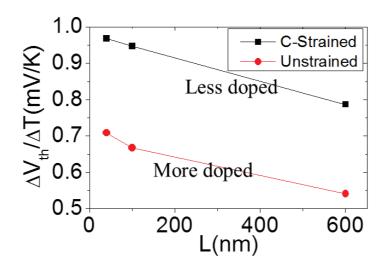

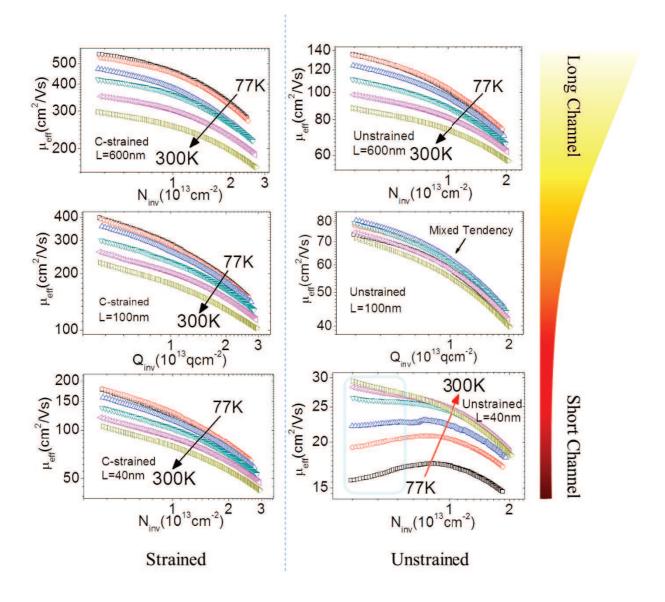

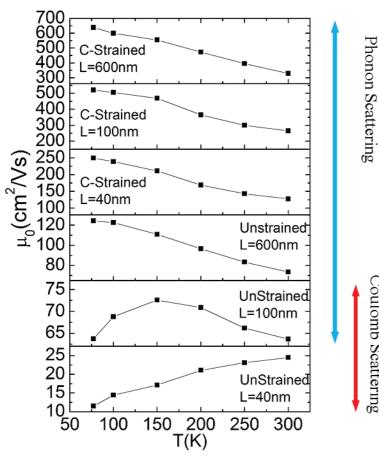

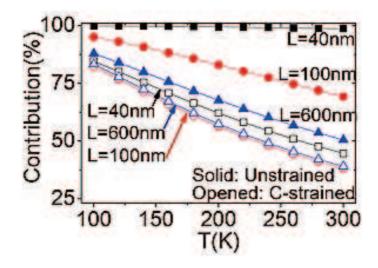

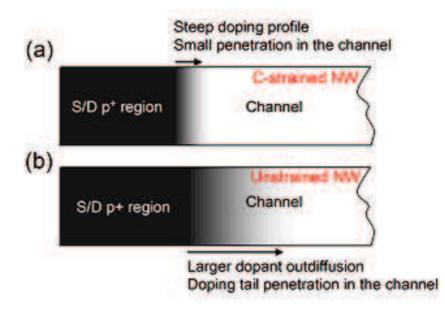

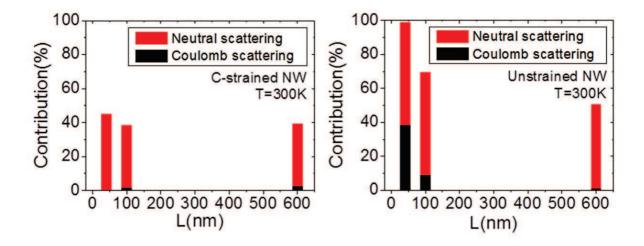

As another quasi-1 D nanowire structure device, 3D stacked SiGe nanowire has been introduced. Important of strain engineering has been known for the effective mobility booster. The limitation of dopant diffusion by strain has been shown. Without strain, SiGe nanowire FET showed huge short channel effect. Subthreshold current was bigger than strained SiGe channel. Temperature dependent mobility behavior in short channel unstrained device was completely different from the other cases. Impurity scattering was dominant in short channel unstrained SiGe nanowire FET. Thus, it could be concluded that the strain engineering is not necessary only for the mobility booster but also short channel effect immunity.

Junctionless FET is very recently developed device compare to the others. Like as JFET, junctionless FET has volume conduction. Thus, it is less affected by interface states.

Junctionless FET also has good short channel effect immunity because off-state of junctionless FET is dominated pinch-off of channel depletion. For this, junctionless FET should have thin body thickness. Therefore, multi gate nanowire structure is proper to make junctionless FET.

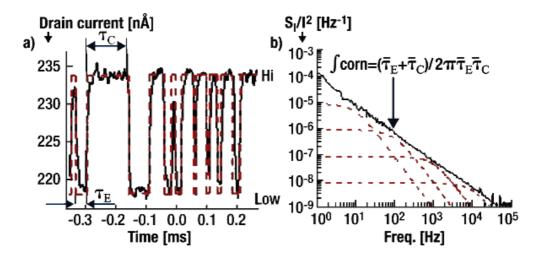

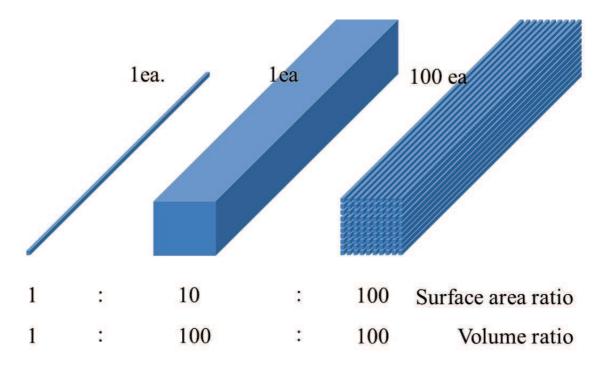

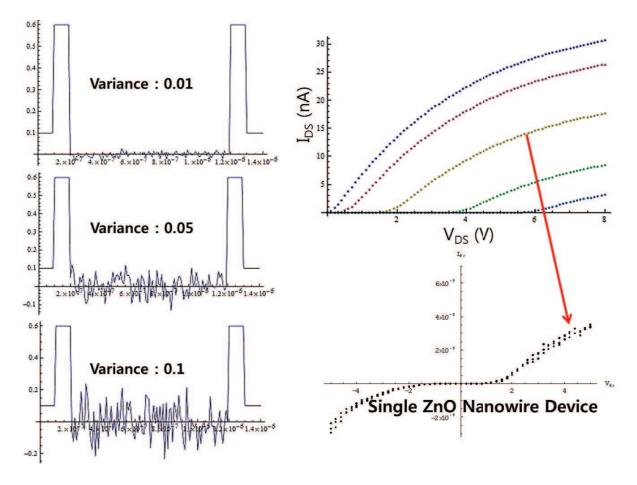

Because of the surface area to volume ratio, quasi-1D nanowire structure is good for the sensor application. Nanowire structure has been investigated as a sensor. Using numerical simulation, generation-recombination noise property was considered in nanowire sensor. Even though the surface area to volume ration is enhanced in the nanowire channel, device has sensing limitation by noise. The generation-recombination noise depended on the channel geometry. As a design tool of nanowire sensor, noise simulation should be carried out to escape from the noise limitation in advance.

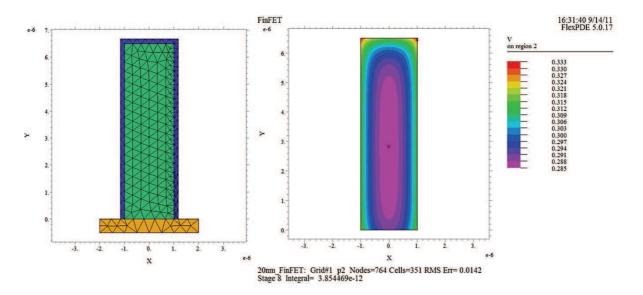

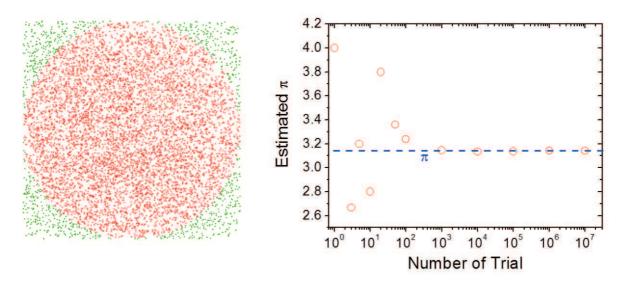

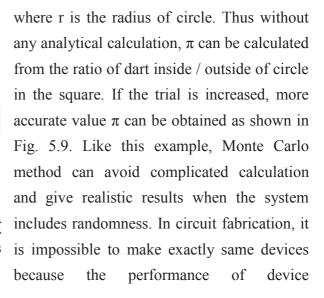

The basic principles of device simulation have been discussed. Finite difference method and Monte Carlo simulation technique have been introduced for the comprehension of device simulation. Practical device simulation data have been shown for examples such as FinFET, strongly disordered 1D channel, OLED and E-paper.

### Contents

| 1. Overview of Semiconductor Device Trends                                     | 1  |

|--------------------------------------------------------------------------------|----|

| 1.1 Economical Consideration: Market Trend Overview                            | 3  |

| 1.2 Device Scaling                                                             | 5  |

| 1.3 Short Channel Effects                                                      |    |

| 1.3.1 Threshold Voltage Shift, Punchthrough and Drain-induced Barrier Lowering | 8  |

| 1.3.2 Velocity Saturation                                                      | 10 |

| 1.3.3 Hot Carrier Effects                                                      | 12 |

| 1.4 Challenges to Overcome Short Channel Effects                               | 12 |

| 1.4.1 High-k and Metal Gate                                                    | 12 |

| 1.4.2 Silicon on Insulator                                                     | 14 |

| 1.4.3 Multi Gate and Pseudo 1D Structure                                       | 16 |

| 1.5 Conclusion                                                                 |    |

| References                                                                     | 19 |

| 2. Nano-device Fabrication Technology                                          | 21 |

| 2.1 Introduction                                                               | 23 |

| 2.2 Top-down and Bottom-up                                                     | 24 |

| 2.2.1 Bottom-up approach                                                       | 24 |

| 2.2.2 Top-down approach                                                        |    |

| 2.2.3 Conclusion: Convergence of Top-down and Bottom-up                        |    |

| 2.3 Conclusion                                                                 |    |

| References                                                                     |    |

| 3. Characterization and Parameter Extraction of FET                            | 43 |

| 3.1 Introduction                                                               | 45 |

| 3.2 Basic MOSFET Operation                                                     | 46 |

| 3.2.1 Linear Regime (at Small V <sub>D</sub> )                                 |    |

| 3.2.2 Saturation Regime (at high $V_D$ )                                       |    |

| 3.2.3 Transfer characteristics: Threshold Voltage and Subthreshold Swing       |    |

| 3.2.4 Mobility                                                                 |    |

| 3.2.5 Low Frequency Noise                                                      |    |

| 3.3 Characterization and Parameter Extraction Technique                        |    |

| 3.3.1 Series Resistance                                                   |             |

|---------------------------------------------------------------------------|-------------|

| 3.3.2 Effective Channel Geometry                                          |             |

| 3.3.3 Y-function Method                                                   |             |

| 3.3.4 Split C-V                                                           |             |

| 3.4 Conclusion                                                            | 63          |

| References                                                                | 64          |

| 4. Transport of Quasi-1D nanostructure FET                                | 67          |

| 4.1 FinFET – Surface Roughness Scattering                                 | 70          |

| 4.1.1 FinFET overview                                                     |             |

| 4.1.2 Experimental Conditions: Device Fabrication and Measurement         |             |

| 4.1.3 Threshold Voltage                                                   |             |

| 4.1.4 Surface Current Separation Technique                                | 77          |

| 4.1.5 Temperature Dependence of FinFET Effective Mobility                 |             |

| 4.1.6 Quantification of the Surface Roughness Scattering Effect           |             |

| 4.1.7 Conclusion                                                          |             |

| 4.2 SiGe Nanowire FET – Phonon Scattering and Impurity Scattering         |             |

| 4.2.1 Device overview: Strain Engineering                                 |             |

| 4.2.2 Experimental Conditions: Device Fabrication and Measurement         |             |

| 4.2.3 Short Channel Effects in SiGe Nanowire FET                          |             |

| 4.2.4 Analysis of Transport Mechanism                                     |             |

| 4.2.5 Conclusion                                                          |             |

| 4.3 Junctionless Transistor – Volume Conduction and Reduced Short Channel | Effects 104 |

| 4.3.1 Device Overview                                                     |             |

| 4.3.2 Transport of Junctionless Transistor                                |             |

| 4.3.3 Conclusion                                                          |             |

| 4.4 Si Nanowire Sensor – Low Frequency Noise and Sensing Limitation       | 111         |

| 4.4.1 Overview: Nanowire for Sensor Application                           |             |

| 4.4.2 Simulation Environment and Conditions.                              |             |

| 4.4.3 Sensitivity Estimation: Numerical Simulation and Analytical Model   |             |

| 4.4.4 Low Frequency Noise in Nanowire Sensor                              |             |

| 4.4.5 Conclusion                                                          |             |

| References                                                                | 119         |

| 5. Device Simulation                                                      | 125         |

| 5.1 Overview: Types of Simulation                                         | 127         |

### Contents iii

| 5.2 Simulation of Quasi 1D Nanowire Devices                                      | 129         |

|----------------------------------------------------------------------------------|-------------|

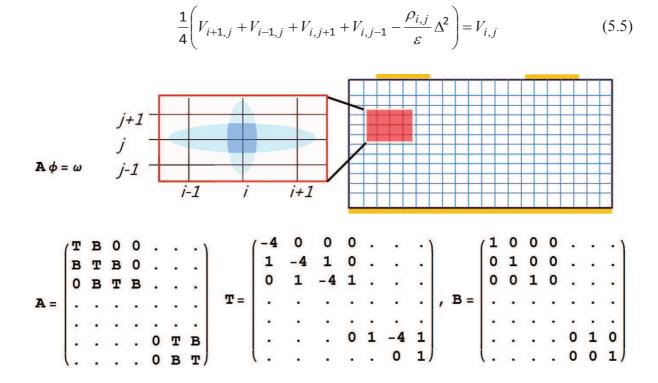

| 5.2.1 Finite Difference Method                                                   | 129         |

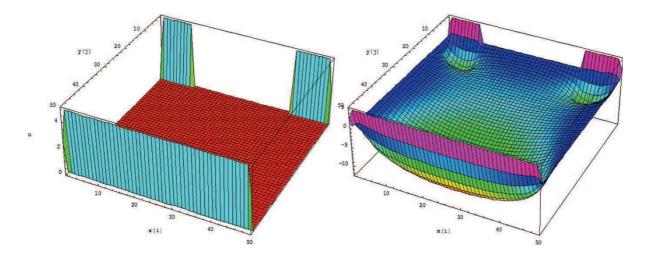

| 5.2.2 Simulations in Specific 1D Systems: Variable Range Hopping in Disordered S | System. 131 |

| 5.2.3 Practical Device Simulation                                                |             |

| 5.3 Other Device Simulations: OLED and E-paper                                   | 134         |

| 5.3.1 Monte Carlo Method                                                         | 134         |

| 5.3.2 Device Simulations: OLED and E-paper                                       |             |

| 5.4 Conclusion                                                                   |             |

| References                                                                       | 140         |

| Conclusion                                                                       | 141         |

| Appendix                                                                         |             |

| Appendix 1: Physical Constants                                                   | 146         |

| Appendix 2: General Properties of Si, Ge and SiGe                                | 147         |

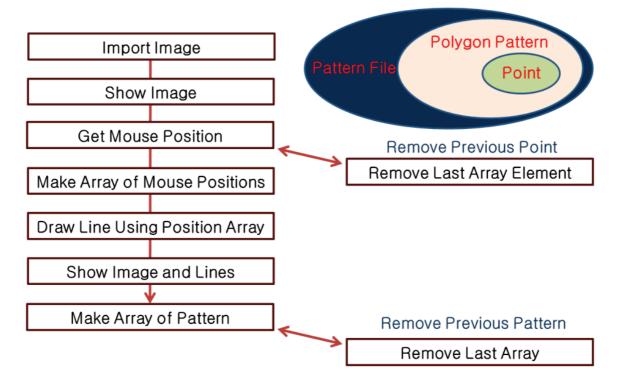

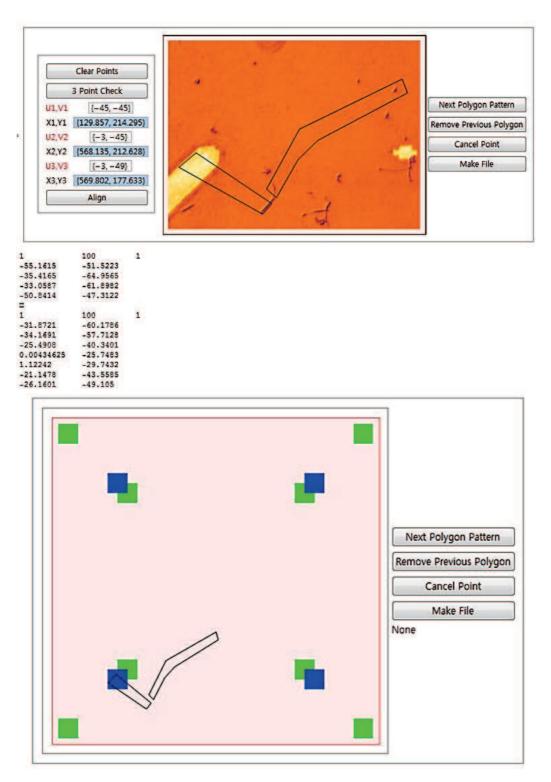

| Appendix 3: E-beam Lithography Pattern Design Program using Mathematica          | 150         |

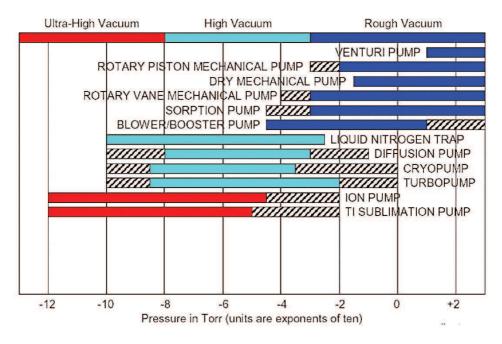

| Appendix 4: Fundamental Vacuum System                                            | 155         |

| Appendix 5: Publication List                                                     |             |

| 국문 초록                                                                            |             |

### 1. Overview of Semiconductor Device Trends

### 1. Overview of Semiconductor Device Trends

### 1.1 Economical Consideration: Market Trend Overview

- 1.2 Device Scaling

- 1.3 Short Channel Effects

- 1.3.1 Threshold Voltage Shift, Punchthrough and Drain-induced Barrier Lowering

- 1.3.2 Velocity Saturation

- 1.3.3 Hot Carrier Effects

### 1.4 Challenges to Overcome Short Channel Effects

- 1.4.1 High-k and Metal Gate

- 1.4.2 Silicon on Insulator

- 1.4.3 Multi Gate and Pseudo 1D Structure

1.5 Conclusion

### Chapter Overview of Semiconductor Device Trends

### 1.1 Economical Consideration: Market Trend Overview

Currently, the appearance of smart devices such as smartphone, tablet PC changes semiconductor market trends.

The origin of smart devices was IBM Simon which was released in 1993 as a world first smart device as a convergence between mobile phone and PC [1]. It included a schedule manager, address book, world clock, fax, games and calculator etc. With evolutions, smart devices have been continuing like personal digital assistant, iPhone and Galaxy Tab etc. Especially after iPhone and Android smartphone has been released in the market, numerous smart applications which use simple user interface, global positioning system (GPS), motion sensors and Wi-Fi etc., play a role as a bridge between human and smart devices.

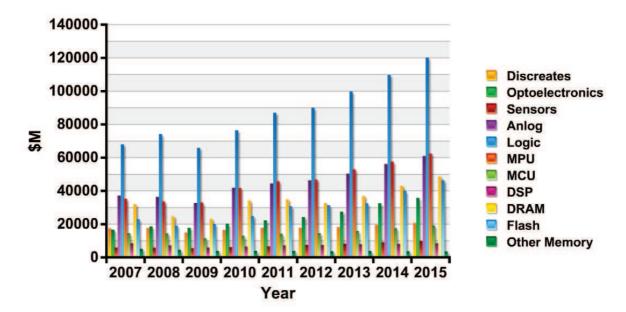

Figure 1.1 : Worldwide semiconductor revenue forecast by product type [2].

The harmonious combination between application and hardware has created the exponential market explosion of smart devices. The markets of smartphone and tablet PC have been forecasted as 49% and 162% growth in 2011 comparing with 2010 [3, 4].

According to the increased demand of smart devices, semiconductor memory market trends are changing for instance from PC DRAM to mobile DRAM and from HDD to NAND flash memory. For example, the market share of mobile DRAM in DRAM market will be growing up to 7.1% in 2011 comparing with 5.5% in 2010 and the total growth rate will be over 100% [5]. To be applied in mobile devices, mobile DRAM should be cost effective with high device density and developed as high performance and low power consumption.

Non-memory (representatively system IC) device market vends are also changing due to the enlargement of smart device market.

Centering around application processor (AP) for smart device, system IC market is growing up. Marching in step with this trend, strategic industrial feature 'fab-less company' has appeared. (Table 1.1) The fabless company means a semiconductor vendor which design, test and selling the chips without semiconductor manufacturing facilities. It relies on the other foundries for the fabrication of chips. The memory devices need the integrated device manufacturer, whereas non-memory device need a capability to correspond with requests of customer through the small quantity batch production. Thus the fabless companies which focus on the chip design are promising business core for the non-memory device.

| 2010 | 2010<br>Rank | Heedenertons | 2010         |

|------|--------------|--------------|--------------|

| Rank |              | Headquarters | <b>(\$M)</b> |

| 1    | Qualcomm     | U.S.         | 7204         |

| 2    | Broadcom     | U.S.         | 6589         |

| 3    | AMD          | U.S.         | 6494         |

| 4    | Marvell      | U.S.         | 3592         |

| 5    | MediaTek     | Taiwan       | 3590         |

| 6    | Nvidia       | U.S.         | 3575         |

| 7    | Xilinx       | U.S.         | 2311         |

| 8    | Altera       | U.S.         | 1954         |

| 9    | LSI Corp.    | U.S.         | 1616         |

| 10   | Avago        | U.S.         | 1187         |

Table 1.1 : 2010 top 20 fabless IC suppliers [6].

Although the fabless company is one of the recent trend in non-memory devices, the research and development of device scaling down and advanced transistor technology such as finFETs, gate-all around (GAA) nanowire is still very important to improve the fabrication yield, low power consumption and the device performance, etc.

### 1.2 Device Scaling

As device dimensions reduced, it becomes difficult to carry out device fabrications. For instance, the integrated circuit becomes denser and more complicated as devices scale down. Thus, problems occur in lithography, interconnects and processing.

Device Scaling down to the small dimension is required to increase device performance such as enhanced switching speed and decreased power consumption. As an example, circuit delay time  $\tau$  can be reduced as a function of gate length L because  $\tau$  is given as:

|                                  | MOSFET Device and Circuit<br>Parameters                 | Multiplicative<br>Factor |

|----------------------------------|---------------------------------------------------------|--------------------------|

| Scaling Assumption               | Device Dimensions (t <sub>ox</sub> , L, W)              | 1/α                      |

|                                  | Doping Concentration (N <sub>a</sub> , N <sub>d</sub> ) | α                        |

|                                  | Voltage (V <sub>D</sub> )                               | 1/α                      |

|                                  | Electric Field (E)                                      | 1                        |

|                                  | Depletion-layer Width (w <sub>d</sub> )                 | 1/α                      |

|                                  | Capacitance (C= $\epsilon A/t_{ox}$ )                   | 1/α                      |

|                                  | Inversion-layer Charge density (Q <sub>i</sub> )        | 1                        |

| Derived Scaling                  | Carrier Velocity                                        | 1                        |

| Behavior of Device<br>Parameters | Drain Current in Drift Region (I <sub>D</sub> )         | 1/α                      |

|                                  | Circuit delay time $(\tau)$                             | 1/α                      |

|                                  | Power dissipation ( $P=I_DV_D$ )                        | 1/α <sup>2</sup>         |

|                                  | Circuit density                                         | α <sup>2</sup>           |

|                                  | Power Density (P/A)                                     | 1                        |

Table 1.2 : Scaling parameters from constant-field scaling [7].

#### 6 1. Overview of Semiconductor Device Trends

$$\tau = \frac{C_G V_D}{I_D} , \qquad (1.1)$$

where  $I_D$  is the drain current,  $C_G$  the gate capacitance and  $V_D$  the drain voltage. With same  $V_D$ , the decrease of  $C_G$  or the increase of  $I_D$  reduces circuit delay time. The drain current  $I_D$  is inversely proportional to the gate length L, thus the reduction of L decreases  $\tau$ . Like as  $\tau$ , circuit density is proportional to the L<sup>2</sup> (Table 1.2). Moreover, power dissipation per circuit decreases by a factor of L<sup>2</sup> which is related to the reduction of the device heating problem.

The potential contours are parallel to the gate insulator and channel interface in long channel device. Thus, if the channel is long enough, the carriers are distributed along the channel surface. However, as gate length decreases, the potential distribution is changed. Aligned potential distributions are dispersed to the direction of body and induce uncontrolled device operation.

The scaling law of MOSFET transistor has followed constant-field scaling. In the constant-field scaling, the electric field is constantly maintained as device is scaled down. To keep the constant electric field, the lateral and perpendicular dimensions (for the constant electric field maintenance of both directions), operating voltage bias and doping concentration have to be changed with scaling factor  $\alpha$ . The unchanged electric field pattern is necessary to maintain gate control and short channel behavior. As shown in Table 1.2, the thinner gate oxide thickness (decreased by  $\alpha$ ) is also needed to make gate oxide field constant. Channel doping level has to be increased by  $\alpha$  to reduce the depletion width w<sub>d</sub> to prohibit punch-through breakdown.

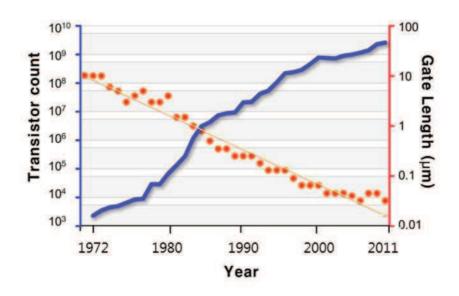

Figure 1.2 : Number of transistor and gate length versus per year (Microprocessor).

Intel co-founder Gordon Moore states that the number of transistor on a chip will be double about every two years, which is well known as Moore's law. For over about 40 years, Moore's law has driven the industry (Fig. 1.2). It seems to work so far. However device dimension has almost reached the end of the scaling limit. Currently 32 nm process node has been used in mass production. According to the Moore's law, several nm of gate length which is physical limitation of MOSFET will be used in several years. Thus, the new concept of device scaling is necessary to continue the device yield and performance enhancement beyond Moore's law.

Lots of alternative device concept has been researched such as multi gate structure, strained channel and junctionless transistor [8-10]. In 2011, Intel has demonstrated that trigate transistor will be adopted in 22 nm microprocessor named Ivy Bridge as world first high volume chip using 3D transistor [11]. It will be the first practical case that the conventional device concept molts.

### 1.3 Short Channel Effects

Device scaling causes unintended effects of device performance. These effects can be categorized according to the different sources [12];

- Electric field profile changes as two dimensional

- 1. Drain-induced barrier lowering

- 2. Mobility reduction by gate-induced surface field

- Electric field strength becomes very high in the channel

- 1. Velocity saturation

- 2. Impact ionization near drain

- 3. Gate oxide charging

- 4. Parasitic bipolar effect

- Physical separation between the source and the drain decreases.

- 1. Punchthrough

- 2. Channel length modulation

Some of them have similar result even though they have different physics. Moreover, sometimes, it is too ambiguous to separate each phenomenon. Thus, here simply classified short channel effects will be investigated for the clear comprehension.

# 1.3.1 Threshold Voltage Shift, Punchthrough and Drain-induced Barrier Lowering

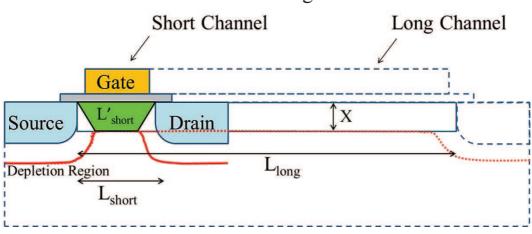

Figure 1.3 : Yau charge sharing model for the short channel device.

For a long channel device,  $V_G$  completely control depleting the semiconductor channel. However in short channel devices, part of channel depletion is under the control of source and drain bias. As the channel length shortens, the close proximity of the source and drain region occurs the fraction of the depletion charge in the channel. In other words, both the gate and source–drain voltages share control of the charge density below the gate. This effect is described by the charge-sharing model (Fig. 1.3) [13]. As a result, the channel can be depleted with lower gate voltage in short channel device. Thus,  $V_{th}$  becomes lower.

With the substrate doping concentration  $N_b$ , the bulk (depletion) charge per unit area  $Q_b$  in the depletion region under the gate could be approximated as rectangular thus  $|Q_b|=qN_bW_d$ with depletion width  $W_d$  by  $V_G$  [13]. In this approximation, the charges near the source and drain, which terminate the built-in field from the junction edges, are neglected. The depletion region from the source and drain are overlapped with the channel charge. In long channel devices, this part is negligible comparing with the area of effective device channel. However, in short channel device, this overlapped part cannot be neglected anymore and the previous approximation does not work. With the consideration of overlapped parts, the shape of the depletion charge cross-section can be described as trapezoid and  $Q_b$  can be calculated as [14, 15]:

$$Q_b = q N_b W_d \left( \frac{L'_{short} + L_{short}}{2L_{short}} \right).$$

(1.2)

The variation of V<sub>th</sub> due to the short channel effect is:

$$\Delta V_{th} = \frac{Q_{b, \ long channel} - Q_{b, \ shortchannel}}{C_{ox}} = \frac{Q_{b, \ long channel}}{C_{ox}} \frac{W_j}{L} \left( \sqrt{1 + \frac{2W_d}{W_j}} - 1 \right), \quad (1.3)$$

where  $W_j$  is the junction depth in channel from the source and drain. From this equation, the decrease of channel length increases threshold shift. As we described previously, depletion charge can be formed easily with small L. Thus,  $V_{th}$  becomes lower in short channel. According to this relationship, parameters to avoid  $V_{th}$  variation due to the short channel effect can be known as following. 1. The reduction of gate oxide thickness; thin oxide thickness increase  $C_{ox}$  thus  $\Delta V_{th}$  can be decreased. 2. The increase of substrate doping  $N_b$ ; it decreases  $W_d$  and  $\Delta V_{th}$ . 3. The steep junction depth; the reduction of  $W_j$  decreases  $\Delta V_{th}$ .

When the depletion region around the drain extends to the source in short channel device, two depletion layers can merge into a single depletion region as shown in Fig. 1.4 [15, 16]. The depletion region of the drain is mainly affected by the drain bias  $V_D$  [17]. Punchthrough occurs when  $V_D$  affects the formation of inversion layer. Punchthrough leads to the rapid increase of drain current with  $V_D$  increase and the weak gate control.

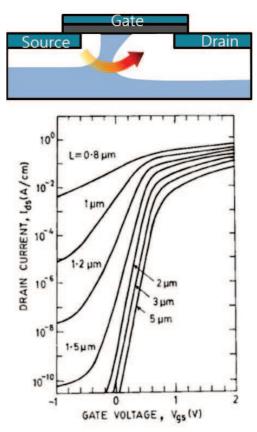

Figure 1.4 : (Above) Schematic of punchthrough. (Below) Calculated subthreshold characteristics  $V_{DS}=2V$ ,  $V_{SB}=0$  V [15].

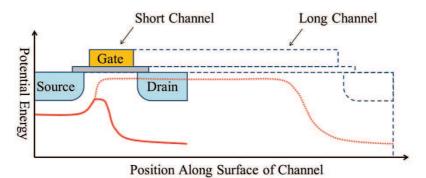

There is similar but different consideration. This potential barrier is confirmed by the builtin potential of the source and channel p-n junction [17]. On the other hand, for a short channel device,  $V_{DS}$  lowers the potential barrier between source and channel, which is named drain-induced barrier lowering (DIBL) as shown in Fig. 1.5.

Figure 1.5 : Drain-induced barrier lowering in short channel device. Drain is biased and it pulls down the potential energy around drain.

This effect limits the maximum operation voltage of device [18]. To avoid DIBL, the enhancement of gate control or the separation of merged depletion region is needed. Thus, increase of substrate doping level, delta doping into the substrate and pocket or halo implant has been used in typical planar devices [19-21].

#### 1.3.2 Velocity Saturation

In a short channel, electron transport is governed by the combined effects of electric field E and scattering with the lattice, impurity atoms and other carriers. At low electric field, this results in a mean velocity proportional to the electric field. [14]:

$$v_d = \mu E \left( cm/s \right). \tag{1.4}$$

The constant  $\mu$  is called carrier mobility and  $v_d$  the drift velocity.

However, due to the energy dependence of scattering relaxation time, its linear relationship is not valid at high electric field. The field dependence of drift velocity is then described by [22]:

$$v_d = \frac{\mu E}{\mathbf{1} + E/E_c}$$

for  $E < E_c$  and (1.5)

$$v_d = v_{s\ a\ l} \text{ for } E > E_c. \tag{1.6}$$

The dividing factor  $E_c$  named as critical field, is approximately  $10^6$  V/m ( $10^4$  V/cm) for the silicon as shown in Fig. 1.6. When E is above  $E_c$ , carrier velocity is saturated to  $v_{sat}$ . This consideration changes the drain current  $I_D$  in nonlinear region from:

Figure 1.6 : Short channel effect by velocity saturation.

$$I_{D} = \mu C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

to (1.7)

$$I_D = k(V_{DS})\mu Cox \frac{W}{L} \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^2}{2} \right], \text{ where}$$

(1.8)

$$k(V_{DS}) = \frac{1}{1 + (V_{DS}/E_C L)}.$$

(1.9)

For the large value of L, k approaches 1. However for the short channel, k is smaller than 1 and  $I_D$  will be decreased by velocity saturation.

The short channel model can be simplified with the assumption of abrupt constant velocity at  $E_{c}$ .

$$v_d = v_{sat} = \mu E_c$$

for  $E > E_c$  and (1.10)

$$V_{DSAT} = L E_c = \frac{L v_{sat}}{\mu} , \quad \text{thus}$$

(1.11)

$$I_{DSAT} = v_{SAT} Cox W \left[ (V_{GS} - V_{th}) - \frac{V_{DSAT}}{2} \right].$$

(1.12)

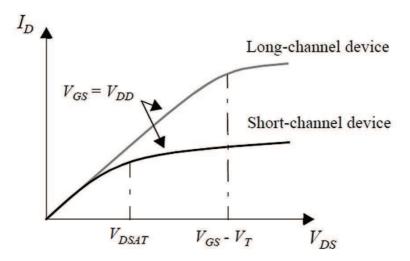

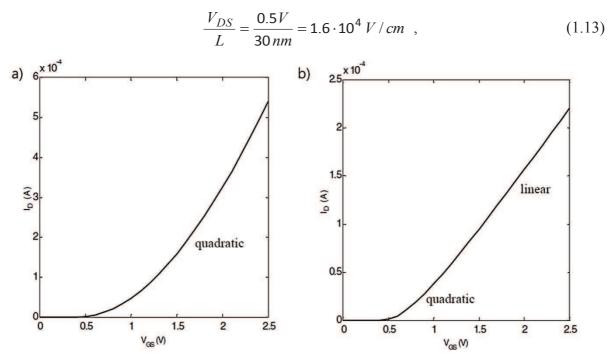

Comparing with the quadratic  $V_{GS}$  behavior in long channel devices, the linear behavior in short channel device has been proved empirically as shown in Fig. 1.7. Recently, 30nm devices has been used and the scaling down will be continued. In the case of a transistor which has 30 nm gate length, the effective electric field between source and drain is:

Figure 1.7 :  $I_D$ -V<sub>G</sub> characteristic for long (L=10  $\mu$ m) and short (L=0.25  $\mu$ m) channel at V<sub>D</sub> =1.5 V [23].

with 0.5 V V<sub>DS</sub>. At 0.5V, it is already reached about  $10^4$  V/cm which is enough value to cause the velocity saturation of the carrier in the channel of the device.

#### 1.3.3 Hot Carrier Effects

If carriers gain very high kinetic energy due to the strong electric field, it can be hot carriers. Hot carrier effect can be classified as [24]: 1) drain avalanche hot carrier injection, 2) channel hot carrier injection, 3) substrate hot electron injection, 4) secondary generated hot electron injection.

At high drain voltage bias, carriers are accelerated by high electric field near the drain. With stress conditions with high  $V_D$  and lower  $V_G$ , drain avalanche hot carrier injection occurs. When accelerated carriers are injected into the depletion region of drain, electron-hole pairs are generated, which is also called as impact ionization. Generated hot electrons and holes are injected into the gate oxide or flow out as a bulk current. Normally it happens at  $V_D > 2V_G$ .

Without electron-hole pair generation, accelerated channel hot carriers can be directly injected into the gate oxide by high  $V_G$ . It causes gate leakage current, interface and oxide degradation. It can occur around  $V_G = V_D$ .

From the high positive or negative bias at the substrate, substrate hot carrier injection occurs. In this condition, carriers optically or electrically generated in the substrate (bulk body) injected into the gate oxide and body. These injected carriers cause gate leakages and substrate current

### 1.4 Challenges to Overcome Short Channel Effects

In this chapter, advanced MOSFET technologies will be introduced. Advanced MOSFET technologies have been researched to overcome short channel effects and to enhance the device performances. They can be categorized as gate stack, silicon on insulator (SOI), channel engineering. There are several parts in channel engineering: channel structure, material and strain engineering. In the case of strain engineering, it will be detailed in chapter 4.2.1.

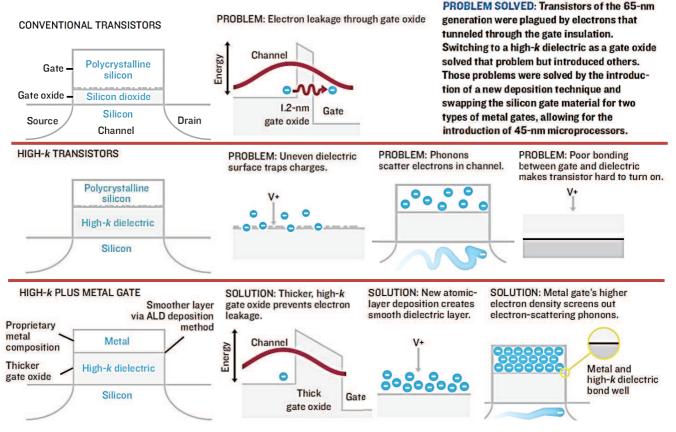

#### 1.4.1 High-k and Metal Gate

As shown in table 2 (Ch. 1.2), the thickness of gate oxide should be decreased to maintain proper electric field according to the device scaling down. ITRS referred to sub 1 nm effective oxide thickness gate stacks are required at the roadmap in 2009 [25]. When the  $SiO_2$  reaches thickness

below 1 nm, it causes the gate leakage problem due to the quantum mechanical tunneling [26]. Thus, as gate insulator,  $SiO_2$  should be replaced with higher permittivity (high-*k*) dielectric material. With high-*k* dielectric layer, effective oxide thickness can be expressed as following:

$$EOT = \frac{k_{SiO2}}{k_{high-k}} = 3.9 \frac{t_{high-k}}{k_{high-k}},$$

(1.14)

where  $k_{SiO_2}$  and  $k_{high-k}$  are the dielectric constant of SiO<sub>2</sub> and high-*k* material, and  $t_{high-k}$  the physical thickness of high-*k* dielectric layer. For instance, with a dielectric constant of 20 and 5 nm physical thickness, effective oxide thickness of 1 nm SiO<sub>2</sub> can be replaced. According to quantum mechanics,

Figure 1.8 : Schematics of high-k gate dielectric. If one gate oxide has twice k of another, a given voltage will draw twice charge into the transistor channel. Or, the same amount of charge will accumulate, if the higher-k dielectric is made twice as thick [26].

tunneling probability increases exponentially as a function of the barrier (gate dielectric layer in this case) thickness [27]. Thus, increased dielectric thickness can avoid tunneling induced gate leakage (Fig. 1.9).

Figure 1.9 : High-k and metal gate for the solution of gate dielectric thinning and phonon scattering [26].

To select high-*k* material as a gate dielectric, several properties should be additionally considered such as semiconductor/gate dielectric band offset, thermodynamic stability, interface quality, film morphology, gate metal compatibility, process compatibility and reliability [28]. Hafnium based dielectric material such as HfO<sub>2</sub> and HfSiO, is one of promising materials for the high-*k* dielectric. From 45 nm process technology, Intel has been using hafnium based gate dielectric [29]. Comparing to 65 nm poly-Si/SiON structure, the gate leakage current of 45 nm metal/high-k gate stacked transistor was 1000 times reduced in PMOS and 25 times reduced in NMOS.

However, high-k gate dielectric has problems [27]. The quality of interface between high-k and poly-silicon gate is very poor so that the oxygen vacancy in the dielectric layer induce Fermi level pinning which causes high threshold voltages of device operation. Additionally, dipoles in the high-k dielectric vibrate like taut rubbers and induce strong vibrations in the lattice of Si channel. This surface phonon scattering in high-k is a primary source of mobility degradation.

Significantly increased electrons in metal gate electrode can screen the dipole vibrations in high-k dielectric [27]. Thus surface phonon scattering is reduced. Moreover, the quality of interface can be improved and Fermi level pinning is reduced.

The use of high-k and metal gate stack requires the correct work function matching for both PMOS and NMOS for the higher device performance.

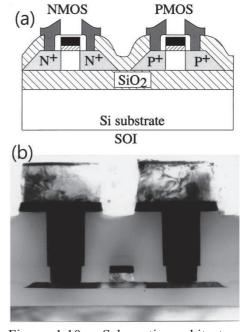

#### 1.4.2 Silicon on Insulator

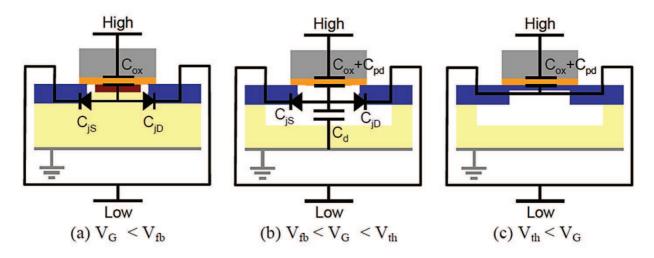

Silicon on insulator (SOI) is sandwiched silicon-oxide layer-silicon substrate. As shown in Fig. 1.10, the entire transistor is completely isolated from other transistors and back substrate by buried oxide (BOX) [30]. Vertically isolated device layer is protected from parasitic effects. Leakage current, radiation induced photocurrent and latch-up etc. can be induced in bulky substrate. SOI wafer reduce junction surface, leakage current and junction capacitance.

SOI wafer can be fabricated by several methods. Separated by implantation of oxygen (SIMOX) method uses oxygen ion beam implantation [31]. After thermal annealing, buried  $SiO_2$  layer is formed into the Si wafer.

Figure 1.10 : Schematic architecture and TEM cross-section image of planar SOI MOSFET [29].

ELTRAN process uses epitaxial layer grown on the porous Si [32]. After transfer using wafer bonding technique, it is separated to handle wafer. Smart Cut method developed by Soitec [33] utilizes hydrogen ion implantation as an atomic scalpel which cuts through the crystalline lattice. Clean and uniform transfer of thin film Si layer can be achieved by Smart Cut method.

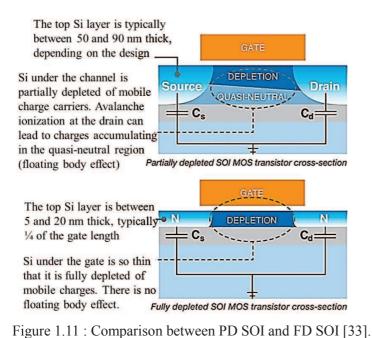

According to the thickness of SOI wafer, it can be classified as

partially depleted SOI (PD SOI) and fully depleted SOI (FD SOI) (shown in Fig. 1.11) [34]. PD SOI has relatively thick ( $t_{si} > 45$  nm) device layer. In PD SOI, top gate and back gate (handle substrate) are decoupled due to the thickness of device layer. The depletion charge in the channel does not extend from the channel surface to the device layer / BOX interface. Thick enough device layer has floating body. PD SOI wafer has several problems from floating body effects [30]. Majority carriers can be collected in the neutral region of PD SOI MOSFET. When impact ionization trigger collected majority carriers, excess current and low frequency noise can be induced. Floating body also induce transient variation of body

potential and threshold voltage.

FD SOI has thin body below 45 nm (typically below 20 nm). Due to its extremely small thickness, the whole body is depleted and the depletion charge is constant. The excellent coupling between gate voltage and channel inversion improves drain current, subthreshold swing and gate response time. Back gate is also more effective than PD SOI therefore threshold voltage control is possible using back gate bias. Floating body effects are strongly reduced in FD SOI devices.

However, there are issues to overcome of course. Low thermal conductivity of BOX induce Self-heating problem in FD SOI device. In saturation region, device temperature increases and current is lowered because of self-heating. Defect coupling is also a problem in FD SOI. The presence of defects at the device interface highly affects performance degradation. Carrier transport affected by defect scattering reduces effective mobility.

Even though SOI technology has few disadvantages, it obviously leads higher performances of device operation. To minimize short channel effects, SOI technology is one of the promising alternatives with multi gate and nanowire structure which is following next chapter.

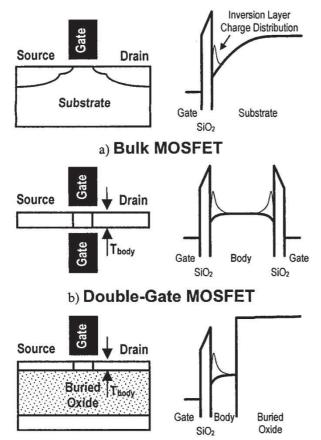

#### 1.4.3 Multi Gate and Pseudo 1D Structure

Multi gate structure shown in Fig. 1.12 has been developed to enhance the immunity to short channel effects of classical single planar gate devices. Even in the SOI FETs, the body

Figure 1.12 : Device structure and energy band diagram of standard single gate bulk MOSFET, double gate MOSFET and ultra-thin body MOSFETs. In standard single gate bulk MOSFET, the body far from the gate is difficult to control [32]

thickness  $t_{si}$  should be scaled down up to  $L_{eff}/5$  for the good control of the short channel effects [35]. Due to the limitation of the process, it is very difficult to be uniform all over a SOI wafer. This variation makes the fluctuation of the device performances in nano-scale transistors [36, 37].

In the case of double gate, two systematic gates make inversion layers on both interfaces between the silicon layer and gates. Double gate FET can be fabricated both being planar and vertical. Gate electrodes are located at the side of vertical fin which has  $w_{si}$  as a fin width in the vertical double gate FET and at the top and bottom of the channel in the planar double gate FET. While  $t_{si}$  should be smaller than  $L_{eff}/5$ in planar SOI transistor,  $w_{si}$  should be scaled down up to  $L_{eff}/2$  [38]. Thus the gate control is enhanced without channel dopants. The absence of

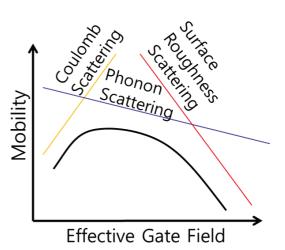

dopant induce no depletion charge ( $Q_{depl}=0$ ). Effective gate electric field  $E_{eff}$  (vertical electric field in channel) consists of linear combination between  $Q_{depl}$  and  $Q_{inv}$ . A reduction of  $E_{eff}$  yields a higher carrier mobility scince the limitation due to the impurity scattering diminishes. It can also reduce interface scattering between Si layer and gate insulator and direct tunneling into the gate dielectric.

In this point of view, the electrostatic control of the gate electrodes can be enhanced by the

increased number of gates. Intel has announced that the next generation CPU platform named Ivy Bridge will be 22 nm manufacturing process instead of 32 nm process of Sandy Bridge. Ivy Bridge will use tri-gate finFET to solve the problem of short channel effects. It will bring lower power consumption and high clock speed due to the advantage of scaling down. Intel expects that 22 nm process finFET will be 37 % faster than current 32 nm process and will save the 50 % of active power.

Beyond the tri-gate finFET, Gate-All-Around (GAA) will be the optimized gate structure in 3D multi gate MOSFETs. GAA FET has gate electrodes wrapped around the channel region. Extremely narrow nanowire channel body has pseudo-1D channel structure. The short channel effect immunity of nanowire FET can be quantitatively analyzed by using natural length  $\lambda$  which can be derived from Poisson's equation (Table 1.3) [39].

| Single Gate     | $\lambda = \sqrt{\frac{\varepsilon_{Si}}{\varepsilon_{ox}} t_{si} t_{ox}}$                                                                  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Double Gate     | $\lambda = \sqrt{\frac{\varepsilon_{Si}}{2\varepsilon_{ox}} t_{si} t_{ox}}$                                                                 |

| Triple Gate     | $\lambda = \sqrt{\frac{\varepsilon_{Si}}{3\varepsilon_{ox}} t_{si} t_{ox}}$                                                                 |

| Gate-All-Around | $\lambda = \sqrt{\frac{\varepsilon_{Si}}{8\varepsilon_{ox}} t_{si}^{2} \ln\left(1 + \frac{2t_{ox}}{t_{si}}\right) + \frac{t_{si}^{2}}{16}}$ |

Table 1.3 : Natural length of devices depending on different gate structures [39].

The natural length is the length of the channel region controlled by the drain. It means that the smaller  $\lambda$ , the smaller short channel effect can be driven in given device structures. To be free of short channel effects,  $\lambda$  should be at least 5 times shorter than the effective gate length. From the equation of  $\lambda$  with single, double and triple gates, it can be simply guessed that approximately the value of  $\lambda$  can be estimated by division with the square root of gates number. Because the smaller  $\lambda$  can reduce the short channel effects, the device has good immunity from increased gate number.

Moreover, from these equations, it should be notable that the reduction of  $t_{ox}$  decreases short channel effects as it was discussed in previous section. Decreasing  $t_{ox}$  has a limitation due to the tunneling current leakages below 1.5 nm gate oxide thickness. Thus high-k gate dielectric can effectively reduce  $\lambda$ . The effect of  $t_{si}$  thinning is also essential to decrease  $\lambda$  and short channel effects. A quantum confinement induced by  $t_{si}$  reduction enhances the volume inversion effect and yield the increase of  $V_{th}$ . However, ultra-thin body raises the mobility degradation even though the reduction of  $t_{si}$  can decrease short channel effects [40]. Thus, the optimization of the device scaling in the GAA MOSFET is still necessary to improve device performances.

### 1.5 Conclusion

In this chapter, recent trends and issues of semiconductor devices are investigated. Because the information technology is dramatically improved, the requirements of device such as smart phone and tablet PC have been exponentially increased. Coming up to these requirements and the fabrication cost down, semiconductor industries have been researching and developing device technologies.

Focused on the field effect transistors, a simple but the most critical issue is device scaling. While device scaling down increases device performances and decreases fabrication cost, it induces unintended short channel effects which affect performance degradation.

To overcome short channel effects, many technologies have been studied. High-k / metal gate stack helps as an alternative to gate oxide thinning. SOI technology has been introduced as substrate engineering. Even though SOI wafer is more expensive than conventional substrates, it obviously decreases short channel effects. For channel engineering, multi gate structure has been studied. Multi gate structure has better gate control.

As device dimension shrunk, recent device structures are converging toward the one dimensional structures like FinFETs or nanowire FETs. Based on this introduction, several topics will be discussed for the transport in quasi-1D nanostructure FETs. In chapter 2, device fabrication technology will be introduced based on my experience during study. In chapter 3, characterization techniques will follow. Transport in quasi-1D nanostructure FET (main topic of this thesis) will be discussed in chapter 4. In chapter 5, device simulation technique will be mentioned. As appendices, physical parameters and material properties of Si and SiGe which were used in my study are attached. Additionally, the development of e-beam lithography pattern generator and basic vacuum technology is supplemented.

### References

- 1. Schneidawind, J, Big Blue unveiling, USA Today, November 23, 1992, page 2B.

- 2. Worldwide Industrial Semiconductor Revenue Forecast by Product, http://www.databeans.net/.

- 3. Ramon T. Llamas, W.S., Stephen D. Drake, Stacy K. Crook, *Worldwide Smartphone 2011–2015 Forecast and Analysis* 2011. p. 227367.

- 4. *IDC Releases Worldwide Quarterly Media Tablet and eReader Tracker Results* 2011.

- 5. *The top 10 strategic technologies for 2011.* Gartner Symposium/ITxpo, 2010.

- 6. IC Insights' Stratagic Revies Database, http://www.icinsights.com/.

- 7. Taur, Y., T.H. Ning, and Books24x7 Inc., *Fundamentals of modern VLSI devices, second edition*, 2009, Cambridge University Press: Cambridge, U.K. ; New York.

- Colinge, J.P., *Multi-gate SOI MOSFETs.* Microelectronic Engineering, 2007. 84(9-10): p. 2071-2076.

- 9. Jang, D., et al., *Low-frequency noise in strained SiGe core-shell nanowire p-channel field effect transistors.* Applied Physics Letters, 2010. **97**(7).

- Colinge, J.P., et al., *Nanowire transistors without junctions*. Nature Nanotechnology, 2010.

5(3): p. 225-229.

- 11. Bruner, J., Intel 22nm 3-D Tri-Gate Transistor Technology. Intel Newsroom 2011.

- 12. Brennan, K.F. and A.S. Brown, *Theory of modern electronic semiconductor devices*. Wiley Online Library.

- Yau, L.D., A simple theory to predict the threshold voltage of short-channel IGFET's. Solid-State Electronics, 1974. 17(10): p. 1059-1063.

- 14. Streetman, B.G. and S. Banerjee, *Solid state electronic devices*. 6th ed. Prentice Hall series in solid state physical electronics2006, Upper Saddle River, N.J.: Pearson/Prentice Hall.

- 15. Arora, N., *Mosfet modeling for VLSI simulation : theory and practice*. International series on advances in solid state electronics and technology2007, New Jersey: World Scientific. xxiii, 605 p.

- Barnes, J.J., K. Shimohigashi, and R.W. Dutton, *Short-channel MOSFET's in the punchthrough current mode.* Electron Devices, IEEE Transactions on, 1979. 26(4): p. 446-453.

- Roy, K., S. Mukhopadhyay, and H. Mahmoodi-Meimand, *Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits.* Proceedings of the Ieee, 2003. **91**(2): p. 305-327.

- 18. Kotani, N. and S. Kawazu, *Computer analysis of punch-through in MOSFETs.* Solid-State Electronics, 1979. **22**(1): p. 63-70.

- 19. Sohn, Y. and S. Joo, *Method for fabricating semiconductor device with ultra-shallow supersteep-retrograde epi-channel by decaborane doping*, 2002, US Patent App. 20,030/215,991.

- 20. Wolf, S., *Silicon Processing for the VLSI Era: Volume III-The Submicron MOSFET, chapters 1&2*, 1995, Lattice Press.

#### 20 1. Overview of Semiconductor Device Trends

- 21. Hueting, R.J.E. and A. Heringa, *Analysis of the subthreshold current of pocket or halo-implanted nMOSFETs.* Electron Devices, IEEE Transactions on, 2006. **53**(7): p. 1641-1646.

- 22. Müller, W. and I. Eisele, *Velocity saturation in short channel field effect transistors.* Solid State Communications, 1980. **34**(6): p. 447-449.

- 23. Class note of device physics from http://bwrc.eecs.berkeley.edu/Classes/icdesign/ee141\_s00/Notes/chapter3.pdf.

- 24. Hitachi Semiconductor Device Reliability Handbook, 5th Edition.

- 25. http://www.itrs.net.

- 26. Chau, R., et al., *High-k/metal-gate stack and its MOSFET characteristics.* Electron Device Letters, IEEE, 2004. **25**(6): p. 408-410.

- 27. Bohr, M.T., et al., *The High-k Solution.* Spectrum, IEEE, 2007. **44**(10): p. 29-35.

- 28. Balestra, F., *Nanoscale CMOS : innovative materials, modeling, and characterization*2010, London, UK; Hoboken, NJ: ISTE : Wiley.

- 29. www.intel.com.

- Shvets, R.K.I.V., et al., *APPLIED PHYSICS REVIEWS--FOCUSED REVIEW*. J. Appl. Phys, 2003.

93(9).

- 31. Izumi, K., M. Doken, and H. Ariyoshi, *CMOS devices fabricated on buried SiO2 layers formed by oxygen implantation into silicon.* Electronics Letters, 1978. **14**(18): p. 593-594.

- 32. Bruel, M., *Silicon on insulator material technology.* Electronics Letters, 1995. **31**(14): p. 1201-1202.

- 33. Aspar, B., et al., *Basic mechanisms involved in the Smart-Cut¢ç process.* Microelectronic Engineering, 1997. **36**(1-4): p. 233-240.

- 34. www.advancedsubstratenews.com/2008/05/fully-depleted-fd-vs-partially-depleted-pd-soi/.

- 35. Trivedi, V.P. and J.G. Fossum, *Scaling fully depleted SOI CMOS.* Electron Devices, IEEE Transactions on, 2003. **50**(10): p. 2095-2103.

- 36. Choi, Y.K., T.J. King, and C. Hu, *Nanoscale CMOS spacer FinFET for the terabit era.* Electron Device Letters, IEEE, 2002. **23**(1): p. 25-27.

- 37. Chang, L., et al. *Reduction of direct-tunneling gate leakage current in double-gate and ultra-thin body MOSFETs.* 2001. IEEE.

- Yang, J.W. and J.G. Fossum, On the feasibility of nanoscale triple-gate CMOS transistors.

Electron Devices, IEEE Transactions on, 2005. 52(6): p. 1159-1164.

- 39. Colinge, J., *Multi-gate SOI MOSFETs.* Microelectronic Engineering, 2007. **84**(9-10): p. 2071-2076.

- 40. Dixit, A., et al., *Analysis of the parasitic S/D resistance in multiple-gate FETs.* Electron Devices, IEEE Transactions on, 2005. **52**(6): p. 1132-1140.

# 2. Nano-device Fabrication Technology

# 2. Nano-device Fabrication Technology

- 2.1 Introduction

- 2.2 Top-down and Bottom-up

- 2.2.1 Bottom-up approach

- 2.2.2 Top-down approach

- 2.2.2.1 Photolithography

- 2.2.2.2 Electron Beam Lithography

- 2.2.2.3 Immersion Lithography

- 2.2.2.4 Wet Etching

- 2.2.2.4 Dry Etching

- 2.2.3 Convergence of Top-down and Bottom-up approach

- 2.3 Conclusion

# Chapter **2** Nano-device Fabrication Technology

# 2.1 Introduction

As the size of the device is scaled down, fabrication process has been aggressively researched and developed. The limitations of the device fabrication instruments have been successfully overcome yet. Most of device fabrication is based on the CMOS fabrication process. Selective patterning with lithography technology has been making various device structures. Film deposition and etching technology build or carve the target materials for the intended structure.

Currently the geometry of device has been changed. The channel geometry of FET has become 3D structure compared to the previous planar device structures. The improvement of micro (or nano)-electromechanical systems (MEMs or NEMs) also makes the micronanostructure possible to be more complicated. Additionally the boundary line of the research field is getting ambiguous. For example, in the bio-medical engineering, nanostructure patterning is necessary to make bio sensors or chemical sensors. Thus the nano-scale device fabrication technology is not limited to the electrical engineering nowadays.

In this chapter, two main schemes of fabrication technology, (top-down and bottom-up) will be delineated. Principles of each fabrication process and the instruments which were used during the study will be described.

# 2.2 Top-down and Bottom-up

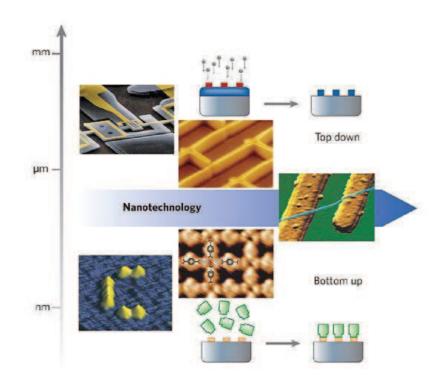

The concept of top-down and bottom-up approach was introduced by Foresight Institute in 1989.

It has been used to help people understand the differences between conventional manufacturing (the mass-production of large non-atomically precise objects) and molecular manufacturing (the mass production of large atomically precise objects). Currently nanotechnology has been researched and developed in both top-down and bottom-up field.

Figure 2.1 : Comparison between top-down and bottom-up approach [1].

# 2.2.1 Bottom-up approach

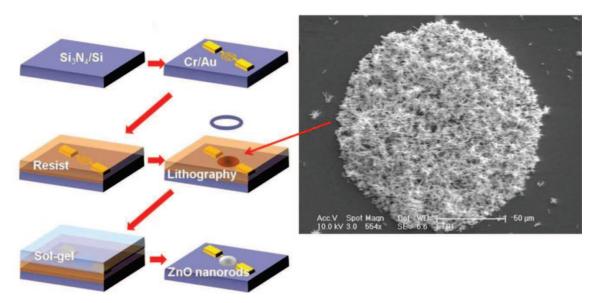

In nanotechnology, the bottom-up approach is the method to build up the nano-scale structure using molecular engineering such as self-organized growth and self-assembly.

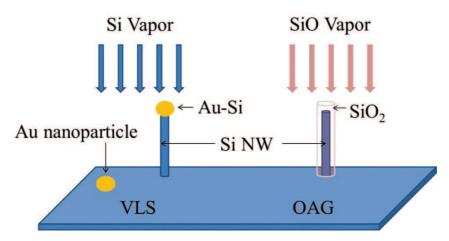

To grow up nanowire structure, Vapor-Liquid-Solid (VLS) growth is widely used [2, 3]. As shown in Fig. 2.2, this method use metal nanoparticles or a metal pattern as a catalyst. From the gas flow support materials (for example, Si) and it is dissolved into the metal catalyst which is in the liquid phase at high temperature. Three phases exist in this process; vapor phase of gas flow, liquid phase of the catalyst and solid states of the growing structure (nanowire). The size of the synthesized structure depends on catalyst size.

In the case of thermal evaporation Oxide-Assisted Growth (OAG), no metal catalyst is needed during the process [3, 4]. There is no metal contamination. Thus the final products of OGA have good quality. The yield and the growth rate of the final products are high due to the reduction of the pre- and post-treatment process.

Figure 2.2 : Difference between VLS and OAG.

The laser ablation method is also used to synthesize nanowire structure [5]. In a furnace with high temperature, a heated target is ablated by a laser beam. The evaporated molecule is transported by inert gas and deposited as nanowires. This method has high yield and high purity.

In addition, there are other methods to synthesize nano-structure such as Molecular-Beam Epitaxy (MBE), and solution-phased synthesis (sol-gel method) [6, 7].

The device fabrication using bottom-up approach faced hard tasks in the view point of device integration for mass production. Highly integrated arrays with controlled orientation and spatial position are necessary to introduce nanowire into the mass production [8]. Nowadays this problem is getting solved through continuous challenge of research. Since the beginning of study, the electrophoresis has been used to align nanowire and nanotubes. However, it could not be available in mass production but for single device fabrication at academic level due to the difficulty of fine control for the moment [9]. Shear flow has also

been used. Passing nanowire suspension through microfluidic channel, well ordered nanowire array device fabrications have been shown [10]. Alignment can be controlled by flow rate and the size of nanowire can be limited by the diameter of microfluidic channel. However, there is no commercial device by using bottom-up approach yet. To be applied to the commercial product, the problems originally from the randomness of bottom-up fabrication process have to be solved.

## 2.2.2 Top-down approach

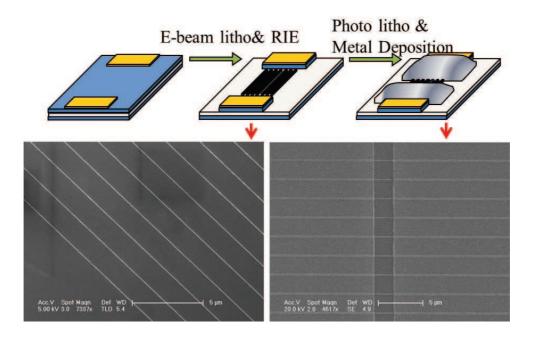

The top-down methods start from bulk structure while the bottom-up start from building up atomic structure. Conventional CMOS fabrication technology is based on the top-down approach. Previously the size of nanowires (or the width of fins) fabricated by top-down approach was not really 'nano' scale because the diameter or width of nanowire depends on the resolution of lithography. Alongside the improvement of the lithography technology, nanowire device can be fabricated with several nanometer diameters [11, 12] and eventually it can be called quasi-1D nanostructure. In academic research e-beam lithography has been used to fabricate quasi-1D nanostructure but it is not suitable for mass production. To be close to mass production, other advanced lithography technologies are aggressively challenged. Not only lithography but also etching is very important for the fabrication of quasi-1D nanostructure. For quasi-1D nanostructure, the uniform isotropic etching is necessary. Especially, when dimension reach 10 nm range, surface roughness becomes critical. Surface roughness affects device structure and quality. The carrier transport of quasi-1D nanostructure device is directly affected by device structure. In this chapter, various CMOS fabrication technologies will be covered. Advanced lithography technologies and etching techniques will be introduced and the results of top-down fabricated quasi-1D nanostructure will be shown.

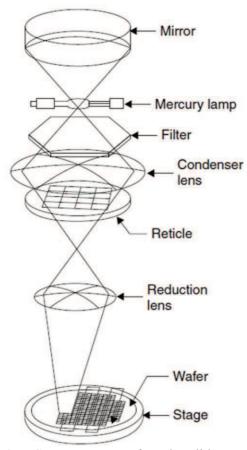

### 2.2.2.1 Photolithography

In the IC industry, photolithography is the most widely used technique to transfer the pattern from mask onto the target. Photolithography is matured rapidly and continuously improved associated with the challenges of IC integration. Basically, photolithography needs a mask for the pattern transfer. An optically flat glass or quartz plate is used as a mask base. The metallic pattern covers the mask base to block the transfer of light. Chrome is widely used for the metallic pattern layer. Laser beam or electron beam lithography is used to define tiny patterns. For the smallest feature size, a phase shift mask can be used to take advantage of the interference by the difference of phase. For

Figure 2.3 : Stepper system for photolithography [15].

example, Intel has used the alternating phase shift mask for below 65 nm process [13-15]. Currently, leading edge photo masks have 4~5 times shrunken pattern than the final chip pattern. This kind of mask has been used with stepper (Fig. 2.3). In stepper, the wafer stage is rapidly stepped under the optical column from position to position until exposure is fully achieved [16].

Usual photolithography process is as following: 1. Cleaning wafer; standard wafer cleaning named RCA clean is necessary for wafer preparation before the resist coating. RCA clean includes organic clean, oxide strip and ionic clean [17]. 2. Photoresist coating; basically the photoresist consists of a polymer, a sensitizer (photo active compound) and a solvent [18]. 3. Soft baking; the soft baking removes solvent and

stress. 4. Exposure. 5. Development.

According to the desired process, post-baking can be added after exposure process. There are two types of photoresist 'positive' and 'negative'. Positive photoresist is the most common photoresist. The exposed area will be developed and then filled with metal or etched. Negative photoresist is widely used as etching mask. The exposed negative photoresist is not soluble in the developer. Thus only unexposed layer will be removed. After all the other post-exposure process including metallization or etching, photoresist is removed from the substrate by resist remover (wet process) or oxygen plasma ashing (dry process).

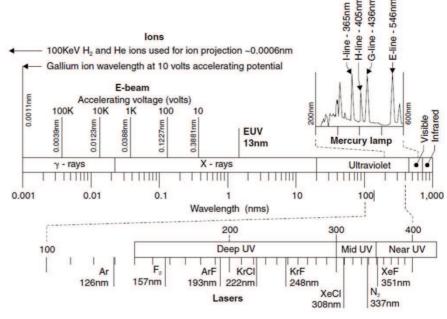

### 2.2.2.2 Electron Beam Lithography

Electron Beam (E-beam) Lithography offers higher patterning resolution than the photo lithography. It is based on the wave nature of electrons. According to the de Broglie equation,

$$\lambda = \frac{h}{p} \quad , \tag{2.1}$$

where  $\lambda$  is de Broglie wave length, h Plank's constant and p the relative momentum of the electron. From the kinetic energy of the electron, accelerated electron velocity in the electric field is,

$$v = \sqrt{\frac{2E_k}{m_0}} = \sqrt{\frac{2qU}{m_0}}$$

(2.2)

F = qE and  $F = \frac{dU}{dx}$ , where  $E_k$  is the kinetic energy of electron, v the electron velocity, q the elementary charge, U the electric potential. SEM is typically used with the acceleration voltage of 10 kV and electron is accelerated about 20 % of the light speed. In the case of

because  $E_k = \frac{1}{2}m_0v^2$ ,

Figure 2.4 : Exposure source and wavelength [15].

TEM, 200 kV is normally used and the speed of electron is about 70 % of the light speed. From de Broglie equation,  $\lambda$  can be described as:

$$\lambda = \frac{h}{p} = \frac{h}{m_0 v} = \frac{h}{\sqrt{2m_0 \, q \, U}} \,. \tag{2.3}$$

However, the speed of accelerated electron is close to the light one. Thus, relative expression should be used as following:

$$\lambda = \frac{h}{\sqrt{2m_0 \, q \, U}} \frac{1}{\sqrt{1 + \frac{q \, U}{2m_0 \, c^2}}} \tag{2.4}$$

c is the speed of light. In 10 kV SEM,  $\lambda$  is about 12 pm even while the wavelength of X-ray is 100 pm order.

E-beam lithography doesn't need masks. Electron beam directly draws the pattern on the sample surface. Thus it is helpful to produce various patterns without wasting the cost of photo masks. However the direct drawing makes the process slower than photo lithography.

E-beam lithography is not suitable for mass production yet because of its throughput. However, it is commonly used for the fabrication of advanced nanostructure.

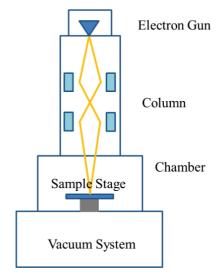

E-beam lithography can be carried out from following systems as shown in Fig. 2.5.

A) An electron gun makes electron. There are two types (thermionic and field emission) of electron source. In thermionic source, electrons are emitted by heating the source material such as W or LaB<sub>6</sub>. LaB<sub>6</sub> source has higher brightness and longer life time than W while W source does not need high

Figure 2.5 : E-beam lithography system

vacuum condition like LaB<sub>6</sub>. In field emission source, a biased sharp tip emits electrons with high electric field. Field emission type has better resolution and brightness than thermal type. However, Field emission source need ultrahigh vacuum condition and extremely expensive cost.

B) An electron column focuses the electron beam. It is designed to make the definite beam diameter or beam shape. Focusing and defocusing lenses and apertures are equipped in the electron column to control it. There is beam blanker to switch the beam on and off.

C) Sample stage control the spot position to draw the pattern properly. Because the

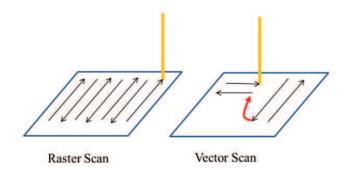

Figure 2.6 : Schematics of raster scan mode and vector scan mode.

deflection system can only address a field of hundreds of micron, it is necessary to move the sample under the beam. An interferometer measures the position of the stage and about several nanometer accuracy can be achieved.

Whole system should be under high vacuum to form the electron beam and

strongly shielded by electromagnetic field and external vibrations to control definite beam condition and position.

To draw the pattern, pattern files have to be prepared by Computer-aided Design (CAD) tool or others. Normally Graphic Database System II (GDSII) format is used to design patterns but ACSII format can be available. In the case of ASCII, protocols could be different depending on the instruments company. With pattern filed, electron beam or stage moves on the proper position of design and beam blanker switch to draw it. There are two different drawing schemes (raster scan and vector scan, shown in Fig. 2.6). In raster scan, every points of the design addressed by sample stage and deflection system and beam blanker switch the e-beam according to the structure. In vector scan, points which have structures are only addressed so that exposure time is shorter than raster scan mode.

Time to expose is defined by following relationship.

$$T \cdot I = D \cdot A, \tag{2.5}$$

where T is the exposure time, I the beam current, D the area dose and A the area exposed. According to this relationship, D can be determined as  $D = T \cdot I/A$ .

Accelerated electrons lose their energy by scattering with the surface. When patterns are close enough, scattered electrons are overlapped and proximity effects appeared. It depends on the pattern size, pattern shape, resist thickness, acceleration voltage and exposure dose. Proximity effects can be controlled by proximity correction programming.

### 2.2.2.3 Immersion Lithography

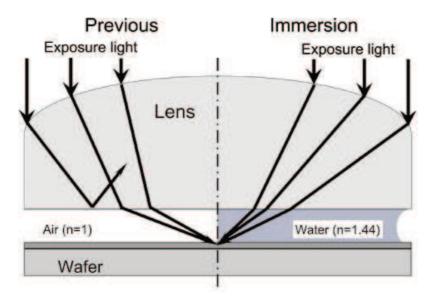

As it mentioned in previous part, the throughput of E-beam lithography is not suitable for mass production. Immersion lithography is a promising photolithography alternative resolution enhancement technology. Immersion lithography uses a liquid medium between final lens and the wafer surface instead of air gap in usual photolithography. The refractive index of liquid medium, bigger than 1, is used. For example, the refractive index of water used in immersion lithography with 193 nm wavelength ultraviolet light is 1.44 at room temperature.

The resolution of minimum feature size (R) and the depth of focus (DOF) in photo lithography is according to the Rayleigh resolution limit (or called angular resolution limit) [19, 20].

$$R = k_1 \frac{\lambda}{NA} = k_1 \frac{\lambda}{n \sin \theta} = k_1 \frac{\lambda/n}{\sin \theta}$$

(2.6)

$$DOF = k_2 \frac{\lambda}{n \sin^2 \theta} = k_2 \frac{\lambda/n}{\sin^2 \theta} = k_1 \frac{\lambda n}{NA^2}$$

(2.7)

NA is the lens numerical aperture, n the refractive index, k1, k2 the process factor from engineering experiences.

Figure 2.7 : Difference between previous photo lithography and immersion lithography [21].

To enhance the resolution, the reduction of  $\lambda$  or increase of NA is needed. In the DOF point of view, increase of NA makes small DOF and the manufacture of huge microscope is impractical [22]. Thus  $\lambda$  has to be mainly decreased.

With air medium, the resolution of ArF light source lithography (193 nm) can be calculated as:

$$R = k_1 \frac{\lambda}{NA} = 0.25 \frac{193}{0.93} = 52 \, nm \,. \tag{2.8}$$

It is not enough to arrive at 45 nm process which is popular nowadays. However, using the liquid medium as shown in Fig. 2.7, effective wavelength can be reduced as:

$$NA = 0.23 - 0.93$$

$O.93 = 0.000 - 0.000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.00000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.0000 - 0.$

$$R = k_1 \frac{\lambda/n}{NA} = 0.25 \frac{1.44}{0.93} = 35 \, nm \,. \tag{2.9}$$

Table 2.1 : Effective wavelength a variety of lithography technology [23]

The molecular fluorine ( $F_2$ ) excimer LASER lithography (157 nm) is also possible to decrease effective wave length but there are lots of problems due to its expensive cost, light absorption in lens and hard pellicle etc. Thus currently ArF immersion lithography has been widely researched and developed.

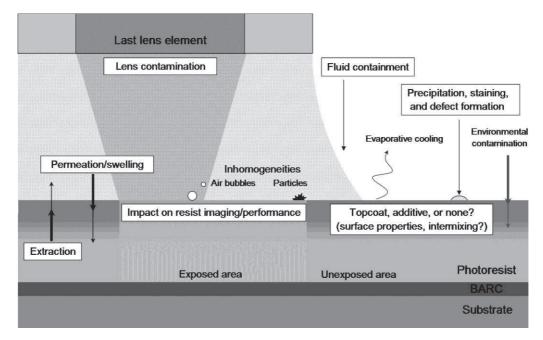

Figure 2.8 : Interactions between liquid medium and photoresist in immersion lithography [23].

However, there are several issues to optimize immersion lithography technology. The interaction between photoresist and water is the most representative problem (Fig. 2.8). For example, water can penetrate photoresist and the component of photoresist can be dissolved into water [24]. The lens can be contaminated by liquid medium. After exposure, the formation of air bubbles [25, 26], particles [27, 28], watermark defect by residue of the liquid medium [29, 30], bridging [31, 32], resist swelling [30] and drying strain [33, 34] can also be created.

The residual bubble can be reduced by additional super-hydrophobic top-coating layer. It prevents direct contact between water and photoresist. For the transparency with ArF light source, cyclic fluorine or acrylate material can be used. Moreover, top-coatless photo resist has been developed to reduce cost and process time [35, 36]. There is no big difference in the basic properties from the photoresist of ArF but it includes original functions of top-coating layer.

### 2.2.2.4 Wet Etching

An etching process is necessary to remove material from bare or pre-patterned substrate. The etching process is roughly categorized as wet etching and dry etching. For the fabrication of nanowire or the other micro/nano structures, selected regions on the surface of wafer are masked using lithography techniques and uncovered area is removed.

Etching rate (ER) is expressed in nm/min or  $\mu$ /min and the etching rate of more than 50 nm/min is required for high fabrication throughput [37]. Etching process needs uniformity. Poor etching uniformity enhances surface roughness of nanostructure. Uniformity of etching process can be defined as :

$$U = \frac{ER_{high} - ER_{low}}{ER_{high} + ER_{low}},$$

(2.10)

where  $ER_{high}$  is the maximum etch rate and  $ER_{low}$  the minimum etch rate. The geometry of pattern can affect the uniformity of etching rate. Etching selectivity is also important. For selective patterning, the etching mask has to endure during the etching process. It can be described with the mask etching rate versus substrate etching rate.

Wet etching can be orientation-independent (isotropic) or orientation-dependent (anisotropic) depending on etchant. The anisotropy of etching process is defined as following:

$$A = 1 - \frac{ER_L}{ER_V} \qquad (2.11)$$

where  $ER_L$  is the lateral etching rate and  $ER_V$  the vertical etching rate. In the case of ideal isotropic etch, A becomes zero and the value of  $ER_L$  is same as  $ER_V$ . For the isotropic etchant of Si, the mixture of HF, HNO<sub>3</sub> and acetic acid (called HNA) is used. SiO<sub>2</sub> and silicon nitride can be isotropically etched using HF and H<sub>3</sub>PO<sub>4</sub> respectively.

Anisotropic etching is based on

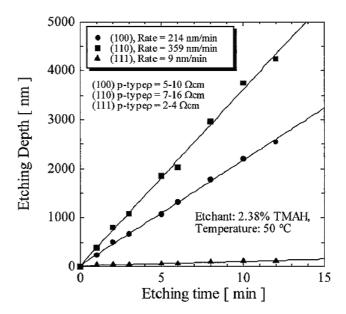

Figure 2.9 : Orientation-dependent etching using TMAH. [38]

orientation-dependent etching speed. For example, the etch rate of Si at  $\{111\}$  surface is obviously slower than  $\{110\}$  and  $\{100\}$ . It is caused by crystal surface properties. The differences in surface density of silicon bonds, bonding energy of silicon atoms and

### 34 2. Nano-device Fabrication Technology

interstitial space on the interface between silicon and silica result in differences in etching rates. From these reasons, the etch rate of Si on {110} surface is several hundred times higher than {111} surface. KOH is one of the most widely used anisotropic etchant for Si. With KOH, the etch rates of {110}:{100}:{111} are in the ratio of 600:400:1. However KOH is corrosive. KOH causes damage to Al and the other metals. Moreover potassium ion is a serious contamination source during the process. Inserted K<sup>+</sup> ions result in device reliability problem. Thus KOH is not used in IC clean room nowadays. Tetramethylammonium hydroxide (TMAH) is another useful Si etchant for anisotropic etching (Fig. 2.9). It does not have any alkali ion. Thus TMAH is suitable for the IC clean room process. Relative etching rates can be reached up to several hundred [38]. For the fabrication of finFET, orientation-dependent etching of (100) SOI wafer using TMAH is emulatively researched as an alternative to dry etching technique.

Wet etching is good for the process of wide surface. Thus it is low cost process. However, there are many problems in the wet etching. Etching rates are varied by shaking condition, temperature and doping concentration. Many etchants are not adaptable for the CMOS process due to the contamination problems. Undercut below etching mask cannot be perfectly solvable which can be critical for the nanostructures.

### 2.2.2.5 Dry Etching

#### 2.2.2.5.1 Plasma

Dry etching is assisted by plasma (it is also calls plasma assisted etching). The term plasma was coined by American physicist Irving Langmuir. Simply the plasma can be considered as a heavily ionized gas. Plasma is a nearly neutral mixture composed of excited neutral species (radicals), ions and electrons [39]. The degree of ionization is the proportion of atoms which lose or gain electrons, and it is related to the plasma density. Thus plasma has charges at local scale but globally it is neutral.

To induce the plasma, molecules should be excited with a high energy. Using the high energy, the link among atoms can be broken up and ions will be separated. For the general usage, the increase of temperature or an electromagnetic excitation is used to induce plasma. However, the electromagnetic excitation method is used for the dry etching technique. For the excitation, strong RF power source (13.56 MHz) is used.

#### 2.2.2.5.2 Plasma Etching (PE)

Plasma etching is preceded by ionized gas mixture inside a chamber. RF excitation makes the gases ionized in the chamber. A target wafer is located on the ground electrode in the low pressure chamber which has the range from several mTorr to hundreds of mTorr. Induced plasma by RF power directly contacts with the target wafer. The chemical reaction between the plasma and the wafer etches the target wafer. The output products of PE can be highly isotropic etched.

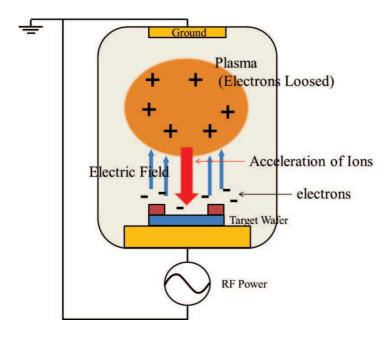

#### 2.2.2.5.3 Reactive Ion Etching (RIE)

Reactive ion etching is a variation of PE. In RIE, the target wafer is located on the RF power source and the top electrode is connected to the ground as shown in Fig. 2.10. Because the electrons are lighter than positive ions, the target wafer connected to the RF signal is more frequently contacted with electrons. Thus the target wafer is negatively charged by electrons. At the same time, globally neutral plasma changed

Figure 2.10 : Schematics of the RIE process.

to positively charged due to the loss of electrons. Polarization of the chamber inside induces the electric field and it accelerates the positive ions toward the target wafer. RIE process is basically combination of chemical and physical etching. The impact of accelerated ion strip away the molecules on the target wafer. It has very low selectivity but is highly anisotropic. In the case of PE, the movements of ions are Brownian random motion. In contrast, in RIE, the direction of ions movements is aligned by induced electric field.

To get the highly anisotropic ratio, target material should have a high capacity to adsorb electrons. Without the electric field due to the charging effect, RIE is similar to PE. Dielectric materials have a poor capacity of electron adsorption comparing to the semiconductors and metals. Thus, normally, dielectric materials are not well suitable for the highly anisotropic etching in RIE.

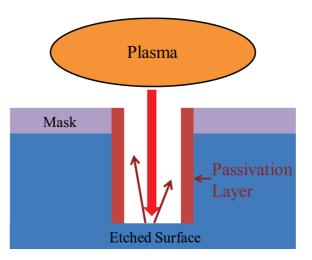

#### 2.2.2.5.4 Inductively Coupled Plasma – RIE (ICP-RIE) and Bosch Process

Inductively coupled plasma – reactive ion etching (ICP-RIE) is a variation of RIE. As the wafer size is getting larger, the distance between top electrode and the target wafer should be longer to get the uniformly etched output in the RIE system. In this case, higher voltage should be used for the RF source. ICP-RIE chamber is surrounded by inductive coil. The RF coils induces an alternating magnetic field. This alternating magnetic field induces an electric field which smashes the plasma with accelerated

Figure 2.11 : Schematics of Bosch process.

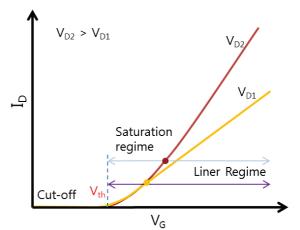

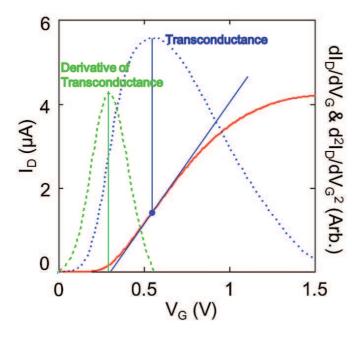

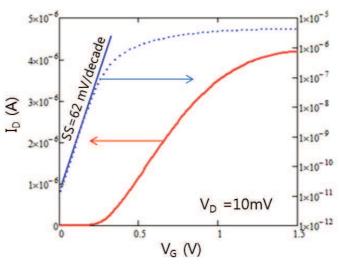

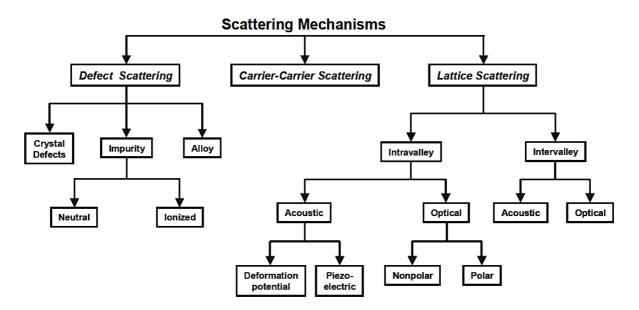

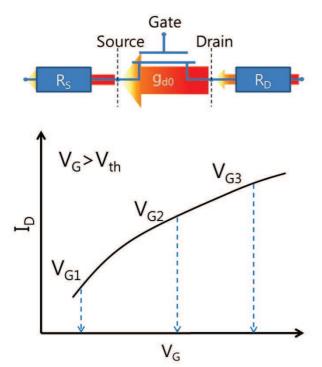

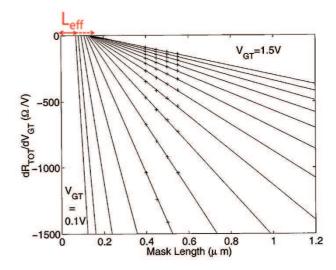

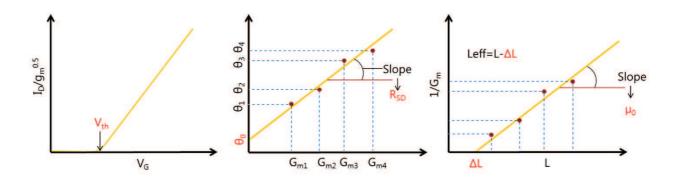

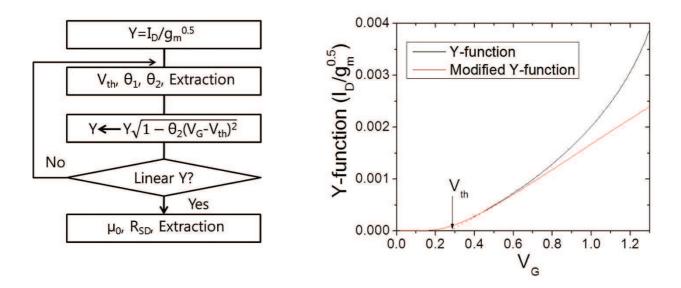

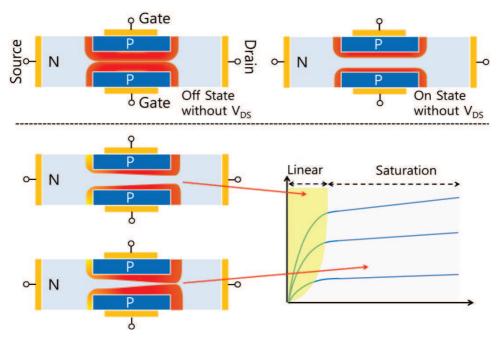

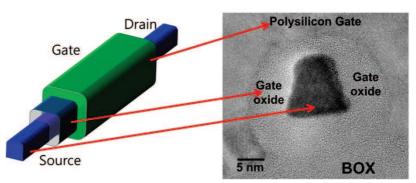

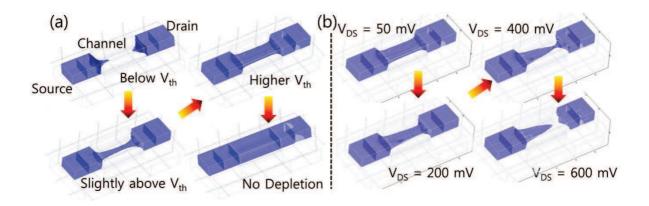

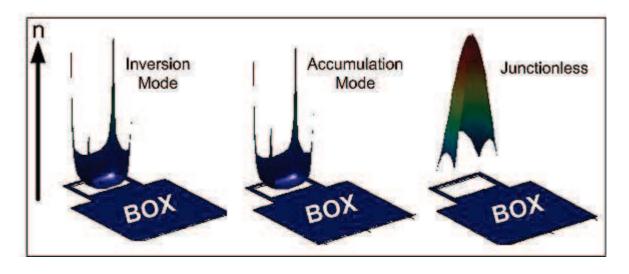

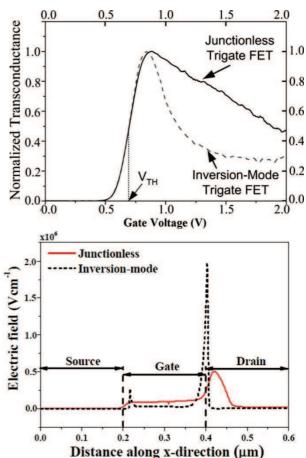

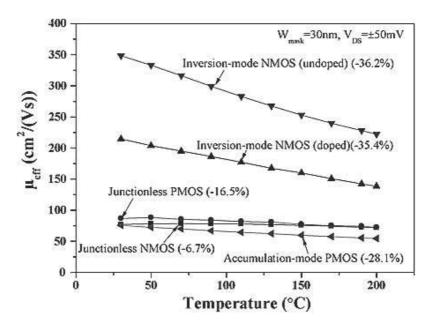

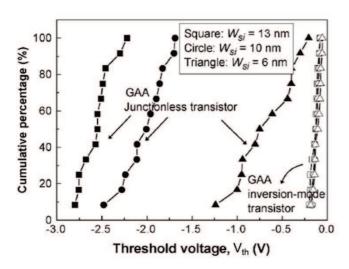

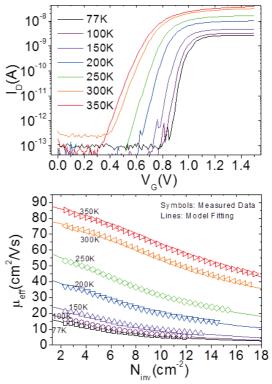

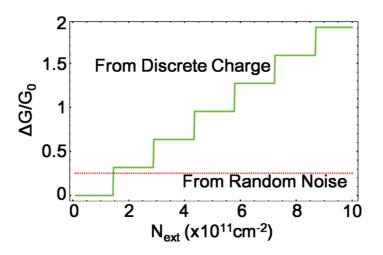

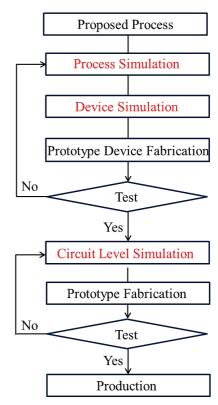

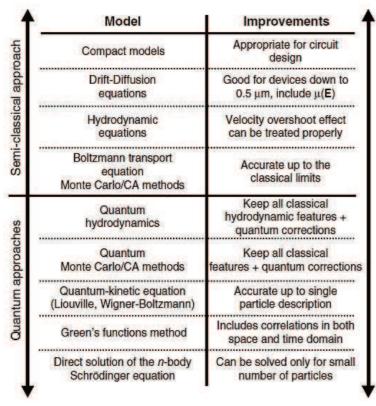

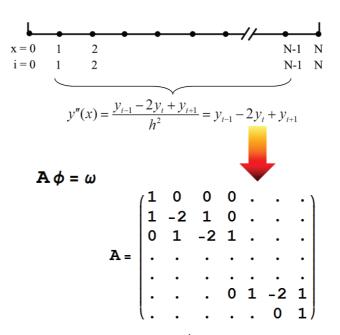

electrons. It helps to generate high-density plasma. This is related to the major advantage of ICP-RIE system. It is possible to control almost independently the plasma density and ion energy while an etching process is executed. It is also possible to get more anisotropic patterns, and faster etch rates depending on the parameters of the system. Thus, compared to the RIE, ICP-RIE has several advantages, such as higher etch rate, enhanced vertical profile, clean and low damaged surface [40].