## Enhancing the Usability of Rely-Guarantee Conditions for Atomicity Refinement\*

Thesis by Kenneth G. Pierce

A thesis submitted for the degree of Doctor of Philosophy (PhD) at Newcastle University.

School of Computing Science, Newcastle University, Newcastle-upon-Tyne, UK.

December 2009

<sup>\*</sup>This is the electronic / technical report version of this document. It has been reformatted into double-sided, single-spaced format. This has altered the page numbering. The author suggests that you use this document for references to specific pages, since it is the version that will be most easily accessible. A few typos have been fixed in Chapter 6.

To my parents, Ron and Gill.

"Für die Wahrheit! Wie vielfach ist sie? Jeder glaubt sie zu haben und jeder hat sie anders."

Gotthold Ephraim Lessing (1729–1781)

### Abstract

Formal methods are a useful tool for increasing the confidence in the *correctness* of computer programs with respect to their specifications. Formal methods allow designers to model specifications and these formal models can then be reasoned about in a rigourous way.

Formal methods for sequential processes are well-understood, however formal methods for concurrent programs are more difficult, because of the *interference* which may arise when programs run concurrently. Rely-guarantee reasoning is a well-established formal method for modelling concurrent programs. Rely-guarantee conditions offer a tractable and compositional approach to reasoning about concurrent programs, by allowing designers to reason about the interference inherent in concurrent systems.

While useful, there are certain weaknesses in rely-guarantee conditions. In particular, the requirement for rely-guarantee conditions to describe whole-state updates can make large specifications unwieldy. Similarly, it can be difficult to describe problems which exhibit distinct phases of execution. The main contribution of this thesis is to show ways in which these two weaknesses of rely-guarantee reasoning can be addressed. In turn, this enhances the usability of rely-guarantee conditions.

Atomicity refinement is a potentially useful tool for simplifying the development of concurrent programs. The central idea is that designers can record (possibly unrealistic) atomicity assumptions about the eventual implementation of a program. This fiction of atomicity simplifies the design process by avoiding the difficult issue of interference. It is then necessary to identify ways in which this atomicity can be relaxed and concurrent execution introduced. This thesis also argues that the choice of data representation plays an important role in achieving atomicity refinement.

In addition, this thesis presents an argument that rely-guarantee conditions and VDM offer a potentially fruitful approach to atomicity refinement. Specifically, rely-conditions can be used to represent assumptions about atomicity and the refinement rules of VDM allow different data representations to be introduced. To this end, a more *usable* approach to rely-guarantee reasoning would benefit the search for a usable form of atomicity refinement.

All of these points are illustrated with a novel development of Simpson's Four-Slot, a mechanism for asynchronous communication between processes.

# Declaration

I certify that no part of the material offered has been previously submitted by me for a degree of other qualification in this or any other University. The work in Chapter 8 was carried out in collaboration with my supervisor. An early, incomplete version of the development appears in [JP08], while [JP09] contains the same development, but uses different arguments for correctness.

# Acknowledgements

There are many people I wish to thank for their help and support during the course of this work. First and foremost, I would like to thank my supervisor, Cliff Jones, without whom this thesis would not have been possible. Cliff has taught me many things and always finds time for his students, despite his often hectic schedule.

I would also like to extend thanks to my other colleagues here at Newcastle University, as well as those I have met from other institutions, for their invaluable advice and guidance. Similarly to my peers, many of whom have become close friends, for their advice, friendship and laughter; and to those other friends, both close to home and farther afield, who have each helped me in their own way.

I would like to thank my family, especially my parents and two younger brothers, whose unwavering support, faith — and on numerous occasions, patience — have shaped who I am today. Without them, I would never have come this far.

Finally, I wish to thank the EPSRC, who funded this research.

# Contents

| $\mathbf{A}$ | bstra            | .ct      |                                                          | i  |

|--------------|------------------|----------|----------------------------------------------------------|----|

| D            | eclar            | ation    |                                                          | ii |

| $\mathbf{A}$ | cknov            | wledge   | ements                                                   | iv |

| Ta           | able o           | of Con   | tents                                                    | vi |

| Li           | $\mathbf{st}$ of | Figure   | es                                                       | xi |

| 1            | Intr             | oducti   | ion                                                      | 1  |

|              | 1.1              | Forma    | d Methods                                                | 1  |

|              | 1.2              | Concu    | arrency and Atomicity                                    | 2  |

|              | 1.3              | The A    | ppeal of Formal Methods                                  | 4  |

|              |                  | 1.3.1    | The Benefits                                             | 4  |

|              |                  | 1.3.2    | Desirable Properties of a Formal Method                  | 5  |

|              |                  | 1.3.3    | The Drawbacks                                            | 5  |

|              | 1.4              | Contri   | ibution                                                  | 6  |

|              | 1.5              | Thesis   | S Outline                                                | 6  |

|              | 1.6              | The A    | tomic Manifesto                                          | 7  |

|              |                  | 1.6.1    | Atomicity in Formal Methods                              | 8  |

|              |                  | 1.6.2    | Atomicity in Database and Transaction Processing Systems | 8  |

|              |                  | 1.6.3    | Atomicity in Dependable Systems                          | 8  |

|              |                  | 1.6.4    | Atomicity in Hardware Architecture                       | 9  |

|              |                  | 1.6.5    | Final Thoughts                                           | 9  |

| <b>2</b>     | Bac              | køranr   | nd and Related Work                                      | 11 |

| _            | 2.1              | Overvi   |                                                          | 11 |

|              | 2.2              | 0 101 1. | etness of Sequential Programs                            | 11 |

|              |                  | 2.2.1    | Pre-Post Conditions                                      | 11 |

|              |                  | 2.2.2    | Refinement                                               | 12 |

|              | 2.3              | VDM      |                                                          | 14 |

|              |                  | 2.3.1    | Refinement in VDM                                        | 15 |

|              |                  | 2.3.2    | Refinement in Special Cases of Non-Determinism           | 16 |

|              | 2.4              |          | etness of Concurrent Programs                            | 17 |

|              |                  | 2.4.1    | Linearizability                                          | 18 |

|              |                  | 2.4.2    | Process Algebras                                         | 20 |

|              | 2.5              | Other    | Relevant Work                                            | 21 |

|              | 2.6              |          | ary                                                      | 21 |

viii CONTENTS

| 3 | Rel            | y-Guar  | cantee Conditions                               |   |       |   |   |   |   | 23  |

|---|----------------|---------|-------------------------------------------------|---|-------|---|---|---|---|-----|

|   | 3.1            | Overvi  | iew                                             |   |       |   |   |   |   | . 2 |

|   | 3.2            | Reason  | ning About Interference                         |   |       |   |   |   |   | . 2 |

|   |                | 3.2.1   | Pre-Post Conditions                             |   |       |   |   |   |   | . 2 |

|   |                | 3.2.2   | Interference and Environment                    |   |       |   |   |   |   | . 2 |

|   |                | 3.2.3   | Rely-Guarantee Conditions                       |   |       |   |   |   |   | . 2 |

|   |                | 3.2.4   | Correctness in Rely-Guarantee Reasoning         |   |       |   |   |   |   |     |

|   | 3.3            | Rely-C  | Guarantee by Example                            |   |       |   |   |   |   |     |

|   | 3.4            |         | Guarantee Conditions in Wider Context           |   |       |   |   |   |   |     |

|   | 3.5            |         | nesses of Rely-Guarantee Reasoning              |   |       |   |   |   |   |     |

|   |                | 3.5.1   | Phases of Execution and Complex Rely-Guarantee  |   |       |   |   |   |   |     |

|   |                | 3.5.2   | Whole-State Updates                             |   |       |   |   |   |   |     |

|   |                | 3.5.3   | Static State                                    |   |       |   |   |   |   |     |

|   |                | 3.5.4   | Relying on Definites                            |   |       |   |   |   |   |     |

|   | 3.6            |         | ary                                             |   |       |   |   |   |   |     |

|   |                |         | ·                                               | • | <br>• | • | • | • | • |     |

| 4 |                |         | cation and Atomicity Refinement                 |   |       |   |   |   |   | 33  |

|   | 4.1            |         | iew                                             |   |       |   |   |   |   |     |

|   | 4.2            |         | P Example                                       |   |       |   |   |   |   |     |

|   |                | 4.2.1   | Concurrent Specification                        |   |       |   |   |   |   |     |

|   | 4.0            | 4.2.2   | Data Reification                                |   |       |   |   |   |   |     |

|   | 4.3            |         | Example                                         |   |       |   |   |   |   |     |

|   | 4.4            | _       | on's Four-Slot Algorithm                        |   |       |   |   |   |   |     |

|   |                | 4.4.1   | Asynchronous Communication Mechanisms           |   |       |   |   |   |   |     |

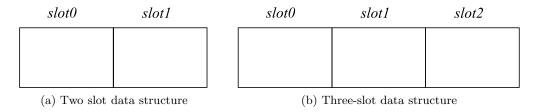

|   |                | 4.4.2   | Multiple Slots                                  |   |       |   |   |   |   |     |

|   |                | 4.4.3   | Two- and Three-Slots                            |   |       |   |   |   |   |     |

|   |                | 4.4.4   | Four-Slots                                      |   |       |   |   |   |   |     |

|   | 4.5            | Summ    | ary                                             | • | <br>٠ | • |   | • | • | . 4 |

| 5 | $\mathbf{Sep}$ |         | n Logic                                         |   |       |   |   |   |   | 4   |

|   | 5.1            |         | iew                                             |   |       |   |   |   |   |     |

|   | 5.2            | Separa  | ation Logic                                     |   |       |   |   |   |   |     |

|   |                | 5.2.1   | The Language of Separation Logic                |   |       |   |   |   |   | . 4 |

|   |                | 5.2.2   | Separating Conjunction                          |   |       |   |   |   |   | . 4 |

|   |                | 5.2.3   | The Frame Rule                                  |   |       |   |   |   |   |     |

|   |                | 5.2.4   | Parallel Composition Rule                       |   |       |   |   |   |   | . 4 |

|   | 5.3            | RGSep   | )                                               |   |       |   |   |   |   | . 4 |

|   | 5.4            | Evalua  | ation of Separation Logic Methods               |   |       |   |   |   |   | . 5 |

|   |                | 5.4.1   | Potential Disadvantages                         |   |       |   |   |   |   | . 5 |

|   |                | 5.4.2   | Taking Inspiration from RGSep                   |   |       |   |   |   |   | . 5 |

|   | 5.5            | Summ    | ary                                             |   |       | • |   |   |   | . 5 |

| 6 | Sim            | plifyin | g Rely-Guarantee with Frames                    |   |       |   |   |   |   | 5.  |

|   | 6.1            |         | iew                                             |   |       |   |   |   |   | . 5 |

|   | 6.2            |         | nt Concurrency and Rely-Guarantee               |   |       |   |   |   |   |     |

|   | 6.3            |         | s in VDM                                        |   |       |   |   |   |   |     |

|   |                | 6.3.1   | The VDM Externals Clause                        |   |       |   |   |   |   |     |

|   |                | 6.3.2   | Declaration of Exclusive Write Access with owns |   |       |   |   |   |   |     |

|   |                | 6.3.3   | Example: Frames and FINDP                       |   |       |   |   |   |   |     |

CONTENTS

|              | 6.4                    | Formal Tr    | eatment of Framed Operations                       |   |     |   |     | 59        |

|--------------|------------------------|--------------|----------------------------------------------------|---|-----|---|-----|-----------|

|              |                        | 6.4.1 Fra    | ame Notation                                       |   |     |   |     | 59        |

|              |                        | 6.4.2 De     | finitions and Theorems                             |   |     |   |     | 60        |

|              |                        | 6.4.3 Fu     | rther Applications of Framing                      |   |     |   |     | 61        |

|              | 6.5                    | Compariso    | on with Separation Logic Ideas                     |   |     |   |     | 62        |

|              | 6.6                    | Summary      |                                                    |   |     |   |     | 63        |

| 7            | Usiı                   | ng Proced    | ural Ordering in Specifications                    |   |     |   |     | 65        |

|              | 7.1                    |              |                                                    |   |     |   |     | 65        |

|              | 7.2                    | 0            | Actions in Specifications                          |   |     |   |     | 65        |

|              |                        |              | dering Actions with Auxiliary Variables            |   |     |   |     | 66        |

|              |                        |              | dering Actions with Phasing                        |   |     |   |     | 67        |

|              |                        | _            | ecification of ACMs with Phasing                   |   |     |   |     | 69        |

|              | 7.3                    |              | for Addressing Deeper Issues with Phasing          |   |     |   |     | 70        |

|              |                        |              | asing and Control Variables                        |   |     |   |     | 70        |

|              |                        |              | asing and Rely-Guarantee Conditions                |   |     |   |     | 71        |

|              | 7.4                    | Summary      |                                                    | • |     | • |     | 72        |

| 8            | Ato                    | ·            | finement Applied to Simpson's Four-Slot            |   |     |   |     | <b>75</b> |

|              | 8.1                    |              |                                                    |   |     |   |     | 75        |

|              | 8.2                    |              | ulties of ACM Specifications                       |   |     |   |     | 76        |

|              | 8.3                    |              | Specification: Unbounded Memory                    |   |     |   |     | 77        |

|              |                        |              | oof Obligations                                    |   |     |   |     | 80        |

|              | 8.4                    |              | ate Specification: Reusing Locations               |   |     |   |     | 81        |

|              |                        |              | ification of $data$ - $w$                          |   |     |   |     | 82        |

|              |                        |              | exiliary Variable and Example Code                 |   |     |   |     | 84        |

|              |                        |              | oof Obligations                                    |   |     |   |     | 85        |

|              |                        |              | est Refinement: Abstract to Intermediate           |   |     |   |     | 86        |

|              | 8.5                    | _            | ation Specification: Simpson's Four-Slot           |   |     |   |     | 88        |

|              |                        |              | exiliary Variables and Example Code                |   |     |   |     | 90        |

|              |                        |              | oofs Obligations                                   |   |     |   |     | 90        |

|              | 0.0                    |              | cond Refinement: Intermediate to Representation .  |   |     |   |     | 94        |

|              | 8.6                    |              | n of Development                                   |   |     |   |     | 96        |

|              | 8.7                    | Summary      |                                                    | • | • • | • | • • | 97        |

| 9            |                        |              | and Further Work                                   |   |     |   |     | 99        |

|              | 9.1                    |              | ns                                                 |   |     |   |     | 99        |

|              | 9.2                    | Further W    | Vork                                               |   |     | • |     | 100       |

| Bi           | bliog                  | raphy        |                                                    |   |     |   |     | 102       |

| $\mathbf{A}$ | $\mathbf{V}\mathbf{D}$ | M-SL Not     | ation                                              |   |     |   |     | 111       |

| В            | Pro                    | ofs for $FD$ | NDP and SIEVE                                      |   |     |   |     | 115       |

| _            | B.1                    |              | Decomposition Inference Rules                      |   |     |   |     | 115       |

|              | B.2                    | _            | Program FINDP                                      |   |     |   |     | 116       |

|              |                        |              | roducing Concurrency                               |   |     |   |     | 116       |

|              |                        |              | hieving Atomicity Refinement with Data Reification |   |     |   |     | 118       |

|              |                        |              | om Specification to Code                           |   |     |   |     | 119       |

|              | В.3                    |              | Program SIEVE                                      |   |     |   |     | 120       |

CONTENTS

|              |       | B.3.1   | Introducing Concurrency                              | 120 |

|--------------|-------|---------|------------------------------------------------------|-----|

|              |       | B.3.2   | Achieving Atomicity Refinement with Data Reification | 121 |

|              |       | B.3.3   | From Specification to Code                           | 122 |

| $\mathbf{C}$ | Four  | r-Slot  | Specifications                                       | 123 |

|              | C.1   | Top-Le  | evel Specification                                   | 123 |

|              | C.2   | Abstra  | act Level                                            | 123 |

|              |       | C.2.1   | State                                                | 123 |

|              |       | C.2.2   | Atomic Specification                                 | 123 |

|              |       | C.2.3   | Specification                                        | 124 |

|              | C.3   | Interm  | nediate Level                                        | 124 |

|              |       | C.3.1   | State                                                | 124 |

|              |       | C.3.2   | Specification                                        | 125 |

|              |       | C.3.3   | An Argument for Four-Slots                           | 125 |

|              | C.4   | First I | Refinement                                           | 127 |

|              |       | C.4.1   | Linking Invariant                                    | 127 |

|              | C.5   | Repres  | sentation Level                                      | 129 |

|              |       | C.5.1   | State                                                | 129 |

|              |       | C.5.2   | Specification                                        | 129 |

|              | C.6   | Second  | d Refinement                                         | 130 |

|              |       | C.6.1   | Retrieve Function                                    | 130 |

| Al           | terna | ative T | Citle Page                                           | 131 |

# List of Figures

| 2.1  | Standard VDM commutativity diagram                             | 13 |

|------|----------------------------------------------------------------|----|

| 2.2  | Specification of $ARB0$                                        | 15 |

| 2.3  | Illustration of post-conditions as relations                   | 15 |

| 2.4  | VDM domain rule; adapted from [Jon90]                          | 16 |

| 2.5  | Standard VDM result rule; adapted from [Jon90]                 | 16 |

| 2.6  | VDM adequacy rule (surjectivity of retr); adapted from [Jon90] | 16 |

| 2.7  | Specification of $ARB1$                                        | 17 |

| 2.8  | VDM refinement diagram with Nipkow's refinement rule           | 17 |

| 2.9  | Nipkow's VDM result rule                                       | 17 |

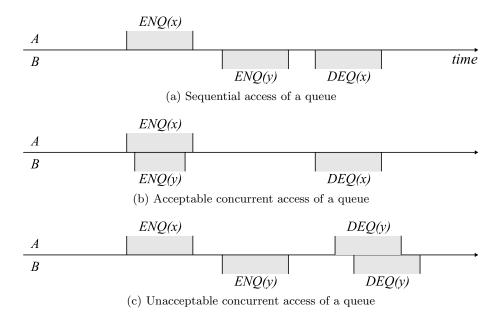

| 2.10 | Possible executions of a FIFO queue; adapted from [HW90]       | 19 |

| 3.1  | Illustration of rely-guarantee conditions                      | 24 |

| 3.2  | Standard rely-guarantee rule for parallel composition          | 26 |

| 3.3  | Sequential specification of XPLUS1                             | 27 |

| 3.4  | Concurrent specification of XPLUS1                             | 27 |

| 3.5  | Concurrent specification of XPLUS1 and YLESSX                  | 27 |

| 3.6  | Concurrent execution of XPLUS1                                 | 27 |

| 3.7  | An example of locking with rely-guarantee conditions           | 27 |

| 3.8  | Rely-condition using a phase ghost variable                    | 30 |

| 4.1  | Sequential specification of FINDP                              | 34 |

| 4.2  | Specification of SEARCH                                        | 35 |

| 4.3  | Specification of SEARCH-Odd                                    | 36 |

| 4.4  | Sequential specification of SIEVE                              | 37 |

| 4.5  | Specification of <i>REM</i>                                    | 37 |

| 4.6  | Specification of REM-Mask                                      | 38 |

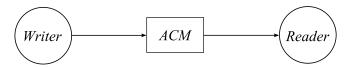

| 4.7  | A single writer and reader communicating via an ACM [Sim90]    | 39 |

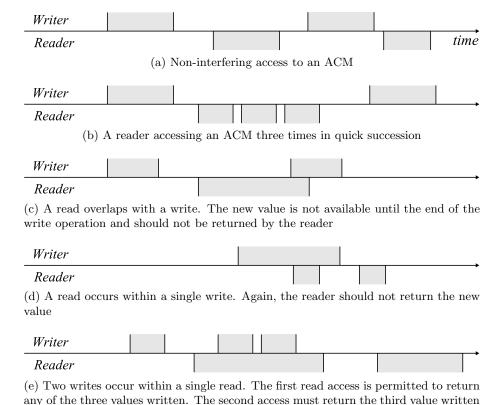

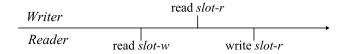

| 4.8  | Possible interactions of write and read operations in an ACM   | 40 |

| 4.9  | Visual representation of two- and three-slot ACMs              | 42 |

| 4.10 | Non-atomic assignment to control variables                     | 42 |

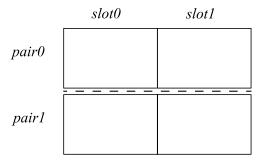

| 4.11 | Logical structure of the four-slot                             | 43 |

| 4.12 | Code for an implementation of the four-slot                    | 44 |

| 5.1  | Heap assertions in separation logic [VP07] [Vaf07]             | 48 |

| 5.2  | Rule of constancy; adapted from [Rey02]                        | 48 |

| 5.3  | An invalid assertion in separation logic; adapted from [Rey02] | 48 |

| 5.4  | The frame rule of separation logic; adapted from [Rey02]       | 49 |

| 5.5  | The par rule of separation logic; adapted from [VP07]          | 49 |

| 5.6  | The parallel composition rule of RGSep: adapted from [VP07]    | 50 |

xii LIST OF FIGURES

| 5.7  | RGSep actions for locking and unlocking a list node; adapted from [VP07]      | 50  |

|------|-------------------------------------------------------------------------------|-----|

| 6.1  | Externals clause of a VDM operation                                           | 57  |

| 6.2  | Spectrum of externals declarations                                            | 58  |

| 6.3  | Original specification of SEARCH-Odd                                          | 59  |

| 6.4  | SEARCH-Odd with simplified rely-condition (due to <b>owns wr</b> )            | 59  |

| 6.5  | Functions to access read-write frame information of an operation $\dots$ .    | 60  |

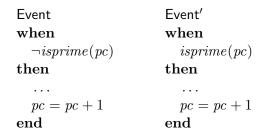

| 7.1  | Example events in Event-B which use a pseudo program counter                  | 67  |

| 7.2  | A triple modular redundancy example in VDM using auxiliary variables          | 68  |

| 7.3  | A triple modular redundancy example in VDM as a phased specification          | 69  |

| 7.4  | Example of a system with an unbounded pseudo program counter                  | 72  |

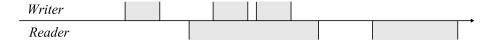

| 8.1  | Writes occurring during a read in an ACM                                      | 76  |

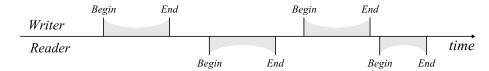

| 8.2  | Begin and end events for ACM operations                                       | 77  |

| 8.3  | Abstract ACM state                                                            | 77  |

| 8.4  | Top-level ACM specification                                                   | 78  |

| 8.5  | Abstract ACM specification with rely-guarantee conditions                     | 79  |

| 8.6  | Intermediate ACM state                                                        | 82  |

| 8.7  | Intermediate ACM specification                                                | 83  |

| 8.8  | Example code for the intermediate ACM                                         | 85  |

| 8.9  | Linking invariant between abstract and intermediate states                    | 87  |

| 8.10 | Representation ACM state                                                      | 89  |

| 8.11 | Relationship between intermediate and representation state components         | 90  |

| 8.12 | Representation ACM specification                                              | 91  |

| 8.13 | Code for an implementation of the four-slot                                   | 92  |

| 8.14 | Retrieve function between intermediate and representation states              | 94  |

| C.1  | Modified intermediate specification illustrating the need for four slots $$ . | 126 |

| C.2  | Failure mode of a three-slot implementation                                   | 126 |

### Chapter 1

### Introduction

#### 1.1 Formal Methods

The goal of much of the field of computer science is eventually to write *programs*. A computer program is a series of instructions that a computer executes to compute a result. These instructions take the form of binary information, which the computer interprets in order to perform calculations and move data around in memory.

While programmers (those who write programs) originally dealt directly with these machine codes on punch cards, higher level languages have since been invented that allow them to think in terms of variables, assignments and loops [Som88] (for example, the ALGOL family [BBG<sup>+</sup>63]).

There are a number of programming paradigms, the most common of which is the *imperative* style<sup>1</sup>. An imperative program directly instructs the computer what to do [Set96]. It consists of a set of variables that represents a program's *state* and a number of operations<sup>2</sup> which manipulate that state. The field of object-oriented languages can be seen as an extension to this basic paradigm [DN66].

No program is complete however without a purpose. Whether it is a scribble on the back of a napkin or the result of hundreds of hours of requirements analysis, all programs have some form of *specification*. At a basic level, a specification describes the expected functionality of a computer program [WLBF09].

For example, a simple, natural language specification might read: "the program should compute the square root of any natural number." Most competent programmers should be able to write a program to satisfy this specification in their favourite programming language. Questions arise however — how does one know if the program is working correctly? Does it meet the specification?

In order to answer this questions, the approach familiar to most programmers is testing [Som88]. Given the input 4, the square root program should return the result 2; given 9 it should return 3. Any deviation from these expected results indicates a problem with the program; each agreement increases confidence in its correctness.

There are an infinite number of natural numbers however, so it is impossible to test them all. After a certain number of tests, a programmer might be confident enough in

<sup>&</sup>lt;sup>1</sup>The *imperative* style is typically contrasted with the *functional* style, in which the program describes what must occur, but not necessarily how [Set96].

<sup>&</sup>lt;sup>2</sup>The term 'operation' is used throughout this thesis to refer to functions that modify program state. This matches the terminology of VDM [Jon90]. Other terms in use include procedure, subroutine, method, etc.

an implementation. Testing alone can only increase confidence so far however, especially for large programs — and for fields such as safety- or security-critical systems, confidence in "correctness" is paramount.

Another approach (and the one upon which this thesis focuses) is to define the specification formally [Hoa69, WLBF09], using a language free from the ambiguities of natural language (which is subject to misinterpretation). For example, the square root program might be defined as<sup>4</sup>:

$$sqrt(x: \mathbb{N}) \ r: \mathbb{R} \stackrel{\triangle}{=} x = r * r$$

Here, the result, r, of the square root of a number, x, is defined such that x is the square of the result. No details are given in this specification of how the result should be achieved in an implementation, but the specification defines exactly what the program should do, albeit in an abstract way.

The art of formal methods can be seen as defining models, which abstract from the delicacies and nuances associated with an implementation [WLBF09]. These abstract models can then be reasoned about in a structured way. Techniques exist for refining abstract specifications into implementable code [Hoa72a, Jon90]. The practice of refinement is discussed in Section 2.2.2.

By defining formal models, it is possible to *prove* certain properties of the specification. Techniques such as refinement can show that an implementation is correct *with respect* to a specification. A formal model is subject to many assumptions, especially in the choice of abstraction. Whether these assumptions are valid is a matter for other research [HJJ03]. As such, formal modelling cannot show that a system is totally correct, only increase confidence in its correctness (see Section 1.3.3).

### 1.2 Concurrency and Atomicity

The square root program from the previous section is likely to be implemented sequentially. The few calculations required can be executed in sequence in order to calculate a result. Since early on in the history of computing science however, it has been possible to run multiple programs at the same time, concurrently. Concurrent systems allow more than one *thread of execution* to exist at any one time [Set96]. Threads of execution may constitute separate programs, or a single program forking into two (or more) threads.

Parallel execution can be achieved on a single processor by halting (preempting) the execution of one program and beginning (or continuing) execution of another [Ber93]. This causes the programs' executions to become interleaved. To the average end user, this gives the illusion of executing multiple programs simultaneously, allowing for multitasking.

It is also possible to have multiple processing units executing programs at the same time, achieving true concurrency. Early multiprocessor systems attempted to disguise multiple processors from the user [Hoa78], but today multiprocessor systems are a reality, particularly as a solution to the power requirements and heat generation of ever larger

<sup>&</sup>lt;sup>3</sup>Note that the abstract of this thesis clearly points out that correctness is defined with respect to some specification. In order to simplify explanation, the correctness of a program is used throughout this thesis as a shorthand for "correct with respect to its specification".

<sup>&</sup>lt;sup>4</sup>This is an implicit VDM function (see Section 2.3).

single processors. True concurrency can allow tasks to be completed faster. For example, a concurrent searching algorithm may find items more quickly (see Chapter 4).

When talking about concurrently executing programs, it is useful to give a name to a program that is running, but which has not finished executing. This is called a *process*<sup>5</sup>. A concurrent process is considered to be a sequential program executing at the same time as one or more other processes, as in [Hoa78].

In order to use concurrent execution to achieve a single task successfully, it is necessary for processes to communicate with each other [Hoa78]. The two main paradigms of process synchronisation are shared memory and message passing. The shared memory paradigm is used throughout this thesis, while the message passing paradigm is only considered within the context of process algebras (in Section 2.4.2). This is justified because the two systems can be shown to be duals of each other [LN79].

The problem with concurrent processes sharing memory is one of *interference* [Jon03a]. More than one process may modify the value of a variable during execution. The state of each program is therefore subject to interference from the *environment* in which it is executed. This environment is formed by other processes executing simultaneously.

The way in which variables change depends on the interleaving of concurrent programs. These interleavings are non-deterministic, hence the values of variables may change non-deterministically. This non-determinism may lead to *race* conditions [BH72], in which the outcome of a program differs depending on the specific interleaving of processes.

Race conditions may produce unexpected results. Testing of a concurrent program is particularly difficult, because it is almost impossible to test all possible interleavings, a small number of which may result in incorrect behaviour [BH72]. For example, the outcome of the following sequential process will increase the value of x by 2.

$$x \leftarrow x + 1 \; ; \; x \leftarrow x + 1$$

A concurrent version, which replaces the sequential composition (;), with parallel composition ( $\parallel$ ), may behave differently [Jon03a]. The following program is not guaranteed to increase x by 2. For example, both processes may read the same initial value of x, increase this value by 1, then write the value back to x. In this case, x will only increase by 1.

$$x \leftarrow x + 1 \parallel x \leftarrow x + 1$$

What has been lost in the concurrent program is the *atomicity* present in the sequential program. The sequential version executes atomically — the value of x cannot be changed and the internal state *cannot be observed*. (For discussions on "atomicity" see [JLRW05, BJ05a, BJ05b, Bur04, CJ07].) In order to guarantee that the concurrent program increases x by 2 (i.e. exhibits the same behaviour as the sequential one), it is necessary to restore some degree of atomicity. In the following program, angle brackets [Lam88] indicate that the assignments should occur atomically.

$$\langle x \leftarrow x + 1 \rangle \parallel \langle x \leftarrow x + 1 \rangle$$

The atomic brackets require that the assignments occurs in isolation, such that after the program has finished, the value of x will have increased by 2. In this case, the assignments happen sequentially, but in a non-deterministic order. In order to implement these atomic brackets in a real machine, it would be necessary to protect x, such that each process could access it atomically. This could be achieved with a lock [Gra70]. A

<sup>&</sup>lt;sup>5</sup>In this thesis, the term 'process' encompasses a 'thread' (of execution).

process must acquire the lock before accessing x. While a process owns the lock, no other process may access x.

Semaphores [Dij68], monitors [Hoa72b] or conditional critical regions [BH75] offer related solutions. The Java programming languages provides the synchronized keyword [GJSB05]. Only a single synchronized operation may run within a single object instance at any one time, hence synchronized operations can be considered to execute with a degree of atomicity.

Whatever the choice of mechanism, it can be seen that performance may suffer. For example, a process may be forced to wait (indefinitely) until a lock is released by another process. On the other hand, the increase in efficiency offered by concurrent execution is gained from allowing multiple processes to run simultaneously. So often the important choice is where to set the *granularity* of atomicity, in order to find a balance between efficiency and "safe" concurrency [Jon07].

For example, at a high level of granularity, whole programs could execute atomically. Thus there would be no interference, but also no concurrent execution. Atomicity could be reduced to the level of operations (as with Java's synchronized keyword). Compilers typically offer some guarantees of atomicity of individual statements, but it is even possible to reason about systems in which the atomicity of a simple assignments is not guaranteed [Col08].

In order to decide on the level of atomicity, a formal method that can deal with atomicity as a concept would be desirable [Jon07]. The notion of atomic execution of statements (i.e. the atomic brackets) could also be a useful design tool. Atomic execution simplifies the design of concurrent programs by reducing the need to consider interference.

Developing under a fiction of atomicity [BJ05b] could allow designers to gain traction on difficult concurrent programs. It may be difficult or inefficient to realise these brackets in hardware, so this atomicity could then be relaxed to permit interference. It would then be necessary to show that the interference introduced allowed the program to function without introducing race conditions. This notion could be called splitting atoms [Jon07]. Chapter 4 discusses the choice of data representation as a key component of relaxing atomicity.

### 1.3 The Appeal of Formal Methods

#### 1.3.1 The Benefits

The benefits of formal specifications are numerous [WLBF09]. The obvious benefit, as covered in the previous section, is the ability to reason about the behaviour of specifications (and in turn, programs) in a structured and rigorous way. Properties such as invariants can be defined to constrain their behaviour and through techniques such as refinement, these properties can be shown to hold of final implementations. This should increase confidence in the correctness of code.

While it is possible, if difficult, to perform *post-hoc* verification formally, it is the author's view that the major attraction of a top-down formal approach is the focus on the design early in the development cycle. The principal purpose of a (functional) specification is to define what a program must do. The precision of a formal language requires that these decisions are made and do not languish ambiguously in natural language.

Furthermore, a formal development *records* these design decisions for future reference. An examination of the code of an implementation may give some insight into what it

does, but not necessarily why, or specifically, why a particular approach was chosen. Formal specifications can go a long way to improving this.

#### 1.3.2 Desirable Properties of a Formal Method

While the most expressive formal method may be an intellectual marvel, it is no more than a technical exercise if it is not used in practice. In order for a formal method to be used, one would expect it to be usable, by humans. It is the author's opinion that a usable formal method will exhibit — at a minimum — two properties: tractability and compositionality.

**Tractability** is the property of being easy to manage and easy to work with [CJ00]. Tractability implies that it is obvious to a user of the formal method how the desired functionality can be expressed and that the user is able to comprehend both the problem that is being tackled and the form of the solution that is required.

Compositionality is the property of enabling larger specifications to be composed from smaller, independent specifications [Jon03a]. This could also be called *modularity*. Large problems are often solved by first solving smaller subproblems — the 'divide and conquer' approach. Thus a formal method which enables problems to be tackled using this intuitive human approach is at an inherent advantage.

In order to retain compositionality (and hence usability) in a formal method, it must be possible to specify subproblems without reference to the context in which they appear in the larger specification. If this is achieved and maintained, it is then possible for these specifications to be reused and contribute to a body of work surrounding the formal method. In turn, this reusability contributes directly to usability, by saving time and effort.

Compositional specifications also benefit a stepwise development process (such as refinement, see Section 2.2.2). New steps in the development do not invalidate the assumptions of previous steps, avoiding the "scrap and rework" policy that may be required of non-compositional methods [Jon07] (see Section 2.4 for a discussion of early, non-compositional approaches to concurrent verification).

#### 1.3.3 The Drawbacks

Formal methods are not a panacea. As mentioned in the previous section, formal models are only as good at the assumptions made about the world which they represent. These assumptions will always exist and no model can perfectly capture the intricacies of a universe.

Formal methods work well for *verification* ([Som88]). Proofs done within the framework of a formal model can show that various properties hold of the model and that design steps are consistent. In terms of *validation* ([Som88], see also [Mih72]) however, it is perfectly possible to build a 'correct' formal specification that does not match its requirements. Similarly, it is still perfectly possible to make poor design decisions. Though the benefit remains that those design decisions which are made (rightly or wrongly) are recorded formally.

Formal modeling also requires time, effort and esoteric knowledge. One could argue that the time spent on formal design should reduce time spent on testing and maintenance. One way to reduce the effort required to use formal methods is to create libraries of verified software, which can then be used by designers without the need to understand their formal verification. Investigation into this area is one aim of UKCRC's<sup>6</sup> "Grand Challenge"<sup>7</sup> on "Dependable Systems Evolution"<sup>8</sup> (GC06) [Woo06]. In theory, tool support for formal methods also reduces the burden on the designer. This issue is not considered in this thesis.

It is the author's view that the ability of formal methods to add rigour to the specification of programs and record design decisions in a precise way outweighs these flaws. Formal methods can greatly increase confidence in the correctness of specifications (particularly 'tricky' concurrent programs) and record design decisions in an unambiguous way.

#### 1.4 Contribution

The work in this thesis makes a contribution to the use of formal methods for verifying the correctness of concurrent programs, specifically within the field of rely-guarantee [Jon83a] reasoning. This thesis argues:

- that there is a clear link between data representation and successful relaxation of atomicity.

- that *read-write frames* in VDM [Jon90] can be used to reduce the complexity of rely-guarantee conditions.

- that adding procedural constructs to top-level specifications can allow the order of actions to be controlled in state-based specifications and in turn this could provide a solution to certain weaknesses in current rely-guarantee reasoning.

All three of the above points are illustrated with a novel treatment of Simpson's Four-Slot [Sim90], an asynchronous communication mechanism (ACM). This new development is also compared to other work within the same area.

#### 1.5 Thesis Outline

The remaining section of this chapter discusses the notion of *atomicity* in greater detail, specifically by looking at how various disciplines within the computer science field view atomicity as a concept.

Chapter 2 presents a discussion of the technical background to this thesis and other related work. It includes an exploration of current methods for reasoning about both sequential and concurrent programs and of VDM (Vienna Development Method) [Jon90], the formal method used through the majority of this thesis.

Chapter 3 presents a discussion of rely-guarantee conditions [Jon83a], one method of reasoning about concurrent programs. Rely-guarantee conditions permit reasoning about interference. The chapter illustrates the usefulness of rely-guarantee with a series of simple examples and also includes a discussion of some of the weaknesses of current rely-guarantee theory.

<sup>&</sup>lt;sup>6</sup>See http://www.ukcrc.org.uk/

<sup>&</sup>lt;sup>7</sup>See http://www.ukcrc.org.uk/grand\_challenges/index.cfm

<sup>&</sup>lt;sup>8</sup>See http://www.bcs.org/server.php?show=ConWebDoc.4721

Chapter 4 argues that there is a clear link between data representation and successful relaxation of atomicity. The argument is supported by three examples, the third of which is an introduction to Simpson's Four-Slot [Sim90] algorithm.

Chapter 5 presents a discussion of separation logic [Rey02], another method of reasoning about concurrent programs. It includes a discussion of two attempts to combine separation logic with rely-guarantee reasoning, namely RGSep [Vaf07] and Deny-Guarantee reasoning [DFPV09].

Chapter 6 argues that read-write frames in VDM can be used to reduce the complexity of rely-guarantee conditions, inspired by the work on separation logic. A denotational semantics for parallel composition of *framed operations* is given to support the argument.

Chapter 7 introduces the notion of controlling order in state-base specifications using procedural constructs, which might also offer a solution to certain weaknesses in current rely-guarantee reasoning.

Chapter 8 presents a novel development of Simpson's Four-Slot [Sim90], which draws upon the work of Chapter 4, Chapter 6 and Chapter 7.

Chapter 9 draws conclusions from the work in this thesis and discusses possible future work.

#### 1.6 The Atomic Manifesto

In April 2004, a workshop was held in Schloss Dagstuhl in Germany entitled "Atomicity in System Design and Execution"<sup>9</sup>. Its purpose was to bring together experts (both academic and industrial) from various fields, to whom the term 'atomicity' held significance as a concept.

There were four main disciplines present at the workshop, which are detailed below. The goal was to discuss the *meaning* of atomicity in the various disciplines and the problems faced in its use, as well as to engender an atmosphere of collaboration. The workshop was highly successful and led to the publication of The Atomic Manifesto [JLRW05] and a second Dagstuhl workshop entitled "Atomicity: A Unifying Concept in Computer Science" During the same year, a project entitled "Splitting Atoms Safely (in Software Design)" was accepted by the EPSRC, through which this thesis was funded.

The following section gives a brief overview of the views of the disciplines represented at the workshop (with details taken from [JLRW05]), to highlight the issues surrounding atomicity as a concept. Some of these issues are considered in this thesis, though many remain as open problems. The four disciplines represented at the original workshop were:

- database and transaction processing systems

- fault tolerance and dependable systems

- formal methods for system design and correctness reasoning

- hardware architecture and programming languages

$<sup>^9\</sup>mathrm{See}\ \mathrm{http://drops.dagstuhl.de/portals/04181}$

<sup>10</sup> See http://drops.dagstuhl.de/portals/06121

#### 1.6.1 Atomicity in Formal Methods

The view of the formal methods community described in [JLRW05] is broadly the view taken in this thesis: that formal methods are beneficial in understanding and verifying systems. Atomicity is discussed at a semantic level, in terms of statements grouped into atomic blocks that behave as a single block. It is noted that these groupings (within "atomic brackets") are difficult to realise practically, but do however provide a convenient and tractable logical framework in which to discuss atomicity.

#### 1.6.2 Atomicity in Database and Transaction Processing Systems

The system model in the database community is of large DBMSs (Database Management Systems) providing transaction processing for a set of applications. These applications have typically been independent, fast-executing programs. While there is some responsibility on the programmer to consider data consistency, it is the sole responsibility of the DBMS to ensure that data is stored and retrieved correctly, in the presence of partial execution, system failures and concurrent execution.

Databases ensure data integrity internally with various complex mechanisms, including locking, logging and two-phase commit. They present, in essence, a black box to the application programmer, to which the interface is composed of "ACID transactions". ACID stands for Atomicity, Consistency, Isolation and Durability. So within this field, the term 'atomicity' is a correctness property imposed upon transactions. It means that a transaction will either commit (complete in its entirety) or abort. This "all or nothing" approach requires that, if a transaction (or part of a transaction) fails, the system will be rolled back to the state immediately before the transaction occurred.

It was noted at the workshop that this traditional model of small, independent applications accessing a database is being replaced, especially with the advent of web technologies. Modern systems often require multiple applications to cooperate and interactions that last much longer, on the order of hours or weeks. The "all or nothing" approach is perhaps draconian and the ability to continue despite errors is desirable. In the area of security, the model is different again. It is often the case that "immediate results are more important than precise ones" [JLRW05].

These new models require alternative models of transactions, a number of which have been suggested. The key point that was identified was that the application of formal methods would be desirable in modeling these new transactions and the DBMSs that provide them.

#### 1.6.3 Atomicity in Dependable Systems

Methods for engineering dependable systems can be broken down into a number of separate, though related, areas. The main tasks involved are fault removal (in which formal methods may already play a part), fault forecasting of those faults which remain (with a view to fault removal) and fault tolerance.

The fault tolerance community accepts that faults will occur and cause errors, despite the best effort of system designers and programmers. Atomicity as a concept can be used in error confinement strategies. An atomic action (termed a *conversation*) is a communication which multiple processes enter (and leave) at the same time. The effects of an atomic action should only become visible when it completes. Errors may occur during an atomic action, but are also isolated by it (making reasoning about the system

simpler). When an error occurs, all parties within the conversation cooperate to resolve it. Strategies include retry, rollback (much like in database transactions), or exception handling.

Atomic actions have been extended for use in situations where parties compete for shared resources, moving towards the original database model of multiple applications competing for a single database. The manifesto identifies that the formal methods community can help in the need for rigourous methods for dealing with atomic actions, much like the need to model new classes of database transactions.

Distributed systems presents an open problem for the fault tolerance community, namely the need for each component to maintain a consistent view of the system and allow asynchronous components to form a consensus, despite the presence of faults and errors. One suggestion is the need for notions of "relaxed" atomicity, in which components are not necessarily engaged for the full length of an action. Much like the fiction of atomicity of the formal methods community, various notions of relaxed atomicity will be necessary for different problems.

#### 1.6.4 Atomicity in Hardware Architecture

As mentioned previously in this introduction, access to concurrent hardware is increasingly common these days. So far, the onus has been on the programmer to deal with the issues raised by parallel programming. The complexity of multi-threaded programs is set to increase further, leading to problems of tractability and debugging. Support for concepts in languages such as threading is increasing, but as a software solution, it is characterised as being slow.

Atomicity at a hardware level concerns executing one or more operations on memory atomically, such that they can't be interrupted. One goal would be to allow the programmer to choose which parts of the program need to execute atomically, the details of which would be met by the hardware. This outwardly appears to differ somewhat from the database persecutive in that a programmer would typically wish for these memory operations to 'just work' (and in that sense complete successfully), having made the decision to have them execute atomically.

There are a number of atomic operations typically available at the hardware level, such as test&set, fetch&add and compare&swap (CAS). These are examples of read-modify-write operations, which read a memory location before writing to it and return an indication of whether the write was successful. A discussion of these operations is given in [Her91]. These instructions are used in the implementations of atomic access structures such as semaphores.

Semaphores (and other atomic concepts such as critical sections) typically block processes that are not accessing a resource, forcing them to wait. Work has been done however on transactional and lock-free memory models. For example, [Col08] describes a semantics of transactional memory with rely-guarantee conditions. What is currently lacking however is a *common* abstraction between software and hardware for atomic memory and hence also a lack of support in real hardware.

#### 1.6.5 Final Thoughts

Though the various disciplines differ somewhat on the exact meaning of the term 'atomicity' and on the details of its use, it is clear that it is a unifying concept between a

number of fields of computer science. Atomicity is a powerful *abstraction*, that has the potential to help designers and programmers in dealing with the myriad complexities of modern systems. This applies to the creation of software and hardware components as well as reasoning formally about these components and system as a whole.

What is also clear is that there is much work to be done in all fields of atomicity. Of particular relevance to this thesis is the notion of the fiction of atomicity as a design tool. In this area, it is necessary to develop theories of the ways in which this fiction can be relaxed, so as to gain the full benefit of modern computing systems without revealing hell's maw to the designer.

The fiction of atomicity can to be applied at the software level (see Chapter 4 and Chapter 8). It is arguably already present in database systems, where ACID transactions hide the complexity of concurrent databases from the application programmer. It is also relevant to the hardware level where, as described above, atomic memory could lead to better, more robust memory models with atomic memory operations as a linchpin.

### Chapter 2

# Background and Related Work

#### 2.1 Overview

This chapter discusses the technical background to the work presented in this thesis. This includes a discussion of methods for reasoning about sequential programs (namely pre-post conditions [Hoa69]), refinement [Hoa72a, Jon90] as a notion for correctness of implementation and of VDM [Jon90] (the main formal method used in later chapters). This chapter also includes a discussion of various approaches for reasoning about concurrent programs. Two of these methods are explored in greater detail in later chapters — rely-guarantee reasoning [Jon83a] in Chapter 3 and separation logic [Vaf07] in Chapter 5.

### 2.2 Correctness of Sequential Programs

#### 2.2.1 Pre-Post Conditions

A partial history of reasoning about programs is given in [Jon03b]. Jones divides the discussion pre- and post-Hoare eras, based around the publication of [Hoa69] (also available in [HJ89]). The post-Hoare era is of most importance to this section. In [Hoa69], Hoare introduces the notions of pre- and post-conditions. Pre-post condition reasoning allows programs to be defined in terms of their properties. The standard example is the *abs* function, which computes the absolute value of an integer. The result of the *abs* function "must be non-negative and equal to either its argument or the negation thereof" [Jon03b].

The description of the results of the *abs* function constitutes its post-condition, which describes the properties of the result. The post-condition is an assertion that must be true after the execution of a program [Hoa69]. Hoare notes however that the result of a program will depend on the values of variables beforehand, thus he also introduces the notion of a pre-condition, which is an assertion about the state before the execution of a program.

Based on Hoare's work, the pre-condition, P, program text, S, and post-condition, Q, are widely written as a "Hoare-triple". A Hoare triple is a program text annotated by pre-post condition assertions. Hoare suggests that this be interpreted as follows: "if the assertion P is true before the initiation of a program S, then the assertion Q will be

true on its completion.<sup>1</sup>"

$${P} S {Q}$$

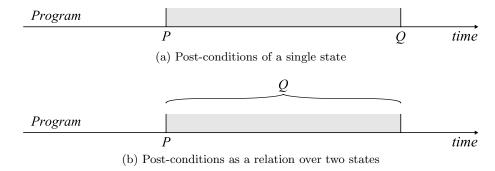

The post-condition of a program defines a contract which the programmer must fulfil. The programmer is however also allowed to set the conditions under which this contract will be filled. This can be seen as part of 'assumption-commitment' reasoning. Under the assumption P, the program S makes a commitment to fulfil Q. Note that [Hoa69] uses post-conditions of a single state (the final state), whereas VDM uses post-conditions of two states (the initial and final states) [Jon90]. As such post-conditions in VDM are relations and this makes it easier to state how the value of a variable changes over the course of an operation (or indeed to assert that is does not).

The major benefit of pre-post conditions is that, as well as being precise about the operation of a program, it is not necessary to have any knowledge of S in order to reason about its behaviour. As long as the program fulfils the specification defined by P and Q, these pre-post conditions are sufficient to describe the program — they define its interface.

This means that pre-post condition specifications can be used to reason about programs without reference to the context in which they appear. Specifications can be realised as multiple steps, which together meet a final post-condition (under a set of initial assumptions) and linked together by further pre-post conditions in a chain. Furthermore, various different implementations can be written for a single specification, as long as they all respect the interface. Thus pre-post condition reasoning forms a tractable, compositional method for reasoning about programs.

Pre-post condition reasoning is used almost universally in formal methods. It is a key component of refinement [Hoa72a] (see the next section), VDM [Jon90] (see Section 2.3), rely-guarantee reasoning [Jon83a] (see Chapter 3) and separation logic [Vaf07] (see Chapter 5).

#### 2.2.2 Refinement

The aim of refinement [Hoa72a, Jon90] is to define a method for showing that an abstract top-level specification is *consistent* with a low-level, concrete one. At the simplest level, this involves verifying that the concrete design correctly implements the abstract specification — that the data representation and operations at the low-level are in some sense *equivalent* and showing that the behaviour of the concrete specification is *essentially* the same as at the abstract level [McD89].

For simplicity of explanation, the terms 'abstract' and 'concrete' are used here to refer to a high-level and a lower-level specification. In practice, they may form a link in a longer chain of refinement. An abstract specification may implement a yet more abstract specification and a concrete specification may be further refined. Note that an important concept is that of abstract specifications being *under-determined*. Under-determined specifications permit more than one deterministic implementation (or in some cases non-deterministic implementation) [LH96]. This notion is used in the VDM refinement rules (see Section 2.3.1).

The practice of refinement lends itself to a stepwise approach to development. Development begins with a highly abstract specification that captures the essential functionality

<sup>&</sup>lt;sup>1</sup>This quote has been modified to use the choice of letters P,S and Q over Hoare's original P,Q and R.

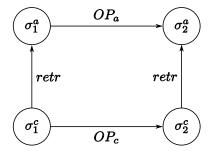

Figure 2.1: Standard VDM commutativity diagram

of the system. At each step, more details of the data representation and operations are added, steering the development towards an implementation. Each step is verified to be consistent with the previous step. The stepwise process eventually leads to an implementable, concrete specification, which can be considered to be correct with respect to the original specification.

The use of formal methods should engender confidence in the correctness of the final concrete design. The practice of refinement provides a framework within a formal method to specify and verify design steps. The details of each refinement step record design decisions clearly and in an unambiguous manner. There are notions of refinement within many different formal methods and notations. Each is slightly different, with varying refinement rules that result in differing strengths and weaknesses.

As an aside, the varying views on refinement became abundantly clear during an exercise undertaken for GC-6 (see Section 1.3.3). Various teams from a wide range of formal methods groups undertook experiments with the formal development of an electronic purse system, known by it's earlier name of "Mondex" [SCW00]. The original development required two stages of refinement. Haneberg et al. were proud to have discovered a single stage refinement [HSGR07]. On the other hand, Butler and Yadav presented an Event-B model with nine levels of refinement [BY07] following an as abstract as possible approach<sup>2</sup>. Broadly speaking however, at each step of refinement it is necessary to show adequacy and satisfaction [McD89].

Adequacy is a property of the chosen data representation. It requires that "all data which can be represented at the high level can similarly be represented at the low level" [McD89] (p. 2). To show this, the abstract and concrete states must be related in some way. In VDM (see Section 2.3) a retrieve function is defined. A retrieve function is a surjective function that builds an abstract state from a concrete one. An adequacy proof obligation must be discharged to show (via the retrieve function) that the chosen representation is adequate (that all abstract states can be represented by the chosen concrete representation).

Satisfaction is a property of operations. It requires that each concrete operation reaches the same final state (after applying the retrieve function) as the corresponding abstract operation. This is illustrated in Figure 2.1, which is the standard VDM commutativity diagram, as presented in [Jon90]. Discussion of the details of this diagram are deferred until the discussion of refinement in VDM (see Section 2.3.1). Note that VDM has a notion of 'operation decomposition', in which multiple concrete operations connected by pre-post conditions may implement a single abstract operation. Further details of

<sup>&</sup>lt;sup>2</sup>This was however partially to gain a high degree of automatic proof (see Section 2.5).

refinement in VDM are given in Section 2.3.1.

#### 2.3 VDM

The Vienna Development Method (VDM) is a formal method used for defining functional specifications of systems and reasoning about their behaviour. It is a mature method that has been used and taught widely. The canonical reference is [Jon90]. The method as a whole consists of a specification language (VDM-SL), techniques for data reification and operation decomposition and a proof framework [BFL+94]. The VDM-SL notation has been standardized in [Int96] and the VDM++ extension introduces object-oriented features to the method [FLM+05]. Numerous tools have been created to aid in the construction and analysis of specifications, including mural [JJLM91], VDMTools<sup>3</sup> and Overture<sup>4</sup>.

VDM is model-oriented formal method, in which specifications are defined in terms of a state and operations that act upon that state. As such it reflects the imperative style of programming. Data abstraction and refinement (typically called 'reification') are central to the VDM philosophy<sup>5</sup>. A typical VDM development contains an abstract specification and one or more refinement steps in which the data representation and operations are reified to create more concrete (and eventually executable) specifications. At each stage, proofs obligations must be discharged to show that the data representation and operations of the new specification satisfy the previous step. VDM-SL has basic data types to represent booleans, natural numbers and so on. It also includes set, sequence and map types, union types and record types (composite types with named components, of which the state is one example). A brief overview of the types and syntax of VDM-SL is given in Appendix A.

Functions and operations (functions that access state components) can be specified implicitly, in terms of pre-post conditions, or explicitly, where programming language constructions can be used. Explicit definitions may also be guarded by pre-conditions. Typically, explicit definitions are introduced during the final steps of a development and allow specifications to be executed (interpreted) for the purposes of testing and animation.

VDM differs from many other formal methods in that post-conditions are predicates over two states — the initial and final states of an operation. Figure 2.2 gives a simple VDM specification of an implicit operation called ARB0 [Jon89]. This operation is an abstract specification for an operation that returns new (unseen) number every time it is called. The result, r, of ARB0 is a natural number. The operation uses a set, s, to remember the values that it has returned before; the post-condition states that r is selected such that it is not in the s and that r is added to s (so that it won't be returned again by a subsequent call).

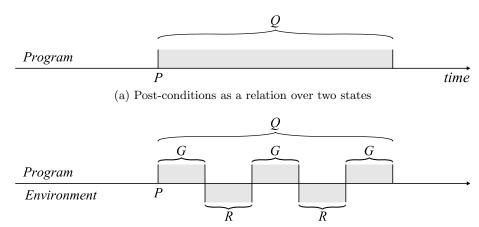

Note the 'hook' notation  $(\bar{s})$  indicates the initial value of a variable. The addition of r to the set is accomplished by stating that (the final value of) s is formed by the union of the initial value  $(\bar{s})$  and r. The idea of post-conditions as relations between states is illustrated in Figure 2.3. It allows the nature of *changes* to the values of variables to be captured. This is also an important idea in rely-guarantee reasoning (see Chapter 3).

<sup>&</sup>lt;sup>3</sup>See http://www.vdmtools.jp/en/

<sup>&</sup>lt;sup>4</sup>See http://www.overturetool.org/

<sup>&</sup>lt;sup>5</sup>It should be noted that *philosophy* is a good term here — limitations of notation or lack of current theory should be no barrier to the exploration of new ideas.

2.3 VDM 15

$$ARB0() r: \mathbb{N}$$

**wr**  $s: \mathbb{N}$ -**set**

**post**  $r \notin s \wedge s = s \cup \{r\}$

Figure 2.2: Specification of ARB0

Figure 2.3: Illustration of post-conditions as relations

Note that before the post-condition on ARB0, there is an externals clause. An externals clause, in the simplest case, contains the names of variables which the operation may access. An externals clause also differentiates between read-only and full write access to variables, using the keywords  $\mathbf{rd}$  and  $\mathbf{wr}$ , respectively. The externals clause of an operation becomes more important in Chapter 6.

#### 2.3.1 Refinement in VDM

Early refinement theory in VDM arose from work on the earlier VDL method (Vienna Development Language). VDL was developed by IBM in order to specify programming language semantics (mainly for PL/I) with the view to aid correct compiler design. At one time, two different Universal Language Descriptions existed for PL/1 (ULD2 from IBM Hursley and ULD3 from IBM Vienna) that differed in their treatment in the semantics of program blocks<sup>6</sup>.

The question was raised — were these two definitions equivalent? Did they describe the same semantics? To find an answer, Lucas [Luc68] struck upon the idea of a twin machine, in which two theoretical machines are started, each running a version of the ULD. If these machines then proceed in lock-step and can be shown to reach the same state for all possible operations, they are considered equivalent. In essence, one can 'rub out' one of the machines. In order to show that the two machines proceed in lock step correctly, the two states are combined into one and an invariant defined to describe when the states are synchronised. If this linking invariant is established at each step of the twin machine, then the languages can be considered equivalent.

Jones noted in [Jon70] that when considering an abstract specification and reification thereof, for most well-defined programs, the reified state will contain more information than the abstract state. A many-to-one relationship exists between reified and abstract states. Thus the linking invariant can be specialized into a function that maps from a reified to an abstract state — a retrieve function.

<sup>&</sup>lt;sup>6</sup>This account is based on a discussion with Cliff Jones.

In order to show that a representation satisfies an abstract specification, two proof obligations must be discharged for each operation — these are the *domain* rule and the *result* rule. Formulations of these two rules are given in Figure 2.4 and Figure 2.5, respectively. The general form of the adequacy rule for VDM is given in Figure 2.6.

$$\forall \sigma^c \in \Sigma^c \cdot pre\text{-}OP_a(retr(\sigma^c)) \Rightarrow pre\text{-}OP_c(\sigma^c)$$

Figure 2.4: VDM domain rule; adapted from [Jon90]

$$\forall \sigma_1^c, \sigma_2^c \in \Sigma^c \cdot \mathit{pre-OP}_a(\mathit{retr}(\sigma_1^c)) \land \mathit{post-OP}_c(\sigma_1^c, \sigma_2^c) \Rightarrow \mathit{post-OP}_a(\mathit{retr}(\sigma_1^c), \mathit{retr}(\sigma_2^c))$$

Figure 2.5: Standard VDM result rule; adapted from [Jon90]

$$\forall \sigma^a \in \Sigma^a \cdot \exists \sigma^c \in \Sigma^c \cdot retr(\sigma^c) = \sigma^a$$

Figure 2.6: VDM adequacy rule (surjectivity of retr); adapted from [Jon90]

The domain rule "requires that the pre-condition on the representation is not too narrow." [Jon90] (p. 190). The result rule describes the commutativity presented in the standard refinement diagram for VDM Figure 2.1. In VDM it is necessary to show that this diagram commutes for each operation — that retrieval followed by an abstract operation is the same as the performing the corresponding concrete operation followed by retrieval. More precisely, the initial concrete state,  $\sigma_1^c$  (lower left), retrieves to the initial abstract state,  $\sigma_1^a$  (upper left). Performing  $OP_a$  reaches the abstract final state,  $\sigma_2^a$  (upper right). It is necessary to show that the concrete final state,  $\sigma_2^c$  (lower right), reached by performing  $OP_c$  from  $\sigma_1^c$ , retrieves to the abstract state,  $\sigma_2^a$ .

If it is impossible to define a retrieve function, then the abstract specification is described as biased. A biased specification is one in which the abstract state contains more information than the reified state and hence in which it is impossible to reconstruct an abstract state. In order to define a retrieve function, this abstract state information would need be held in the reified state, in which case the abstract representation has biased the reified specification [Jon90]. A major tenet of VDM is to avoid specification bias.

#### 2.3.2 Refinement in Special Cases of Non-Determinism

Unfortunately, it is sometimes necessary to consider apparently biased specifications as the 'correct' choice of representation. It is entirely possible to define concrete specifications for which the inarguably sensible choice of abstract specification must be, apparently, biased. This is best illustrated by reconsidering the example from above, namely ARB0. A sensible implementation of ARB0 (which must return a new, unseen number on each call) is to simply add 1 to the previous number returned. A definition for such a realisation (ARB1) is given in Figure 2.7 [Jon89].

ARB1 uses a counter, n, to remember the last number returned and increments this value at each call. ARB1 however only exhibits one of the *possible* behaviours of ARB0

$$ARB1() r: \mathbb{N}$$

**wr**  $n: \mathbb{N}$

**post**  $r = \overleftarrow{n} \land n = \overleftarrow{n} + 1$

Figure 2.7: Specification of ARB1

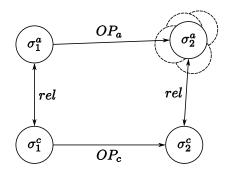

Figure 2.8: VDM refinement diagram with Nipkow's refinement rule

and a retrieve function cannot be defined. The key factor in this example (and common to many examples of this type) is the requirement for the abstract state to retain *history information*. In the above example, this is the set of previously returned numbers. The implementation shows only one possible behaviour of the abstract specification — the non-determinism present in the abstraction is not present in the implementation (it is "unused" [Jon89]).

In order to deal with the resolution of non-determinacy, it was necessary to extend the standard VDM rules for refinement. Work in the area was undertaken separately at Oxford [HHH<sup>+</sup>87] and Manchester [Nip86], though it is now typically referred to (based on the latter of the two), as Nipkow's rule. The major difference from the standard result rule is that the retrieve function is replaced with a relation (as in a twin machine). It is necessary show that, for any concrete step beginning in a state that corresponds to an abstract step, there *exists* a corresponding final abstract state. Nipkow's result rule is given in Figure 2.9 (compare to Figure 2.5 above).

$$\forall \sigma_1^c, \sigma_2^c \in \Sigma^c, \sigma_1^a \in \Sigma^a \cdot rel(\sigma_1^a, \sigma_1^c) \land post\text{-}OP_c(\sigma_1^c, \sigma_2^c) \Rightarrow \\ \exists \sigma_2^a \in \Sigma^a \cdot post\text{-}OP_a(\sigma_1^a, \sigma_2^a) \land rel(\sigma_2^a, \sigma_2^c)$$

Figure 2.9: Nipkow's VDM result rule