Imperial College London Department of Electrical and Electronic Engineering

### A MICROMACHINED ZIPPING VARIABLE CAPACITOR

by

Suan Hui Pu

MEng, Mechanical Engineering Imperial College London, 2006

Prof. Andrew S. Holmes and Prof. Eric M. Yeatman Supervisors

> Prof. Neil M. Alford Internal Examiner

Dr. Harrie A. C. Tilmans External Examiner

A dissertation submitted to Imperial College London for the degree of **Doctor of Philosophy** April 2010

## Abstract

Micro-electro-mechanical systems (MEMS) have become ubiquitous in recent years and are found in a wide range of consumer products. At present, MEMS technology for radio-frequency (RF) applications is maturing steadily, and significant improvements have been demonstrated over solid-state components.

A wide range of RF MEMS varactors have been fabricated in the last fifteen years. Despite demonstrating tuning ranges and quality factors that far surpass solid-state varactors, certain challenges remain. Firstly, it is difficult to scale up capacitance values while preserving a small device footprint. Secondly, many highly-tunable MEMS varactors include complex designs or process flows.

In this dissertation, a new micromachined zipping variable capacitor suitable for application at 0.1 to 5 GHz is reported. The varactor features a tapered cantilever that zips incrementally onto a dielectric surface when actuated electrostatically by a pulldown electrode. Shaping the cantilever using a width function allows stable actuation and continuous capacitance tuning. Compared to existing MEMS varactors, this device has a simple design that can be implemented using a straightforward process flow. In addition, the zipping varactor is particularly suited for incorporating a highpermittivity dielectric, allowing the capacitance values and tuning range to be scaled up. This is important for portable consumer electronics where a small device footprint is attractive.

Three different modelling approaches have been developed for zipping varactor design. A repeatable fabrication process has also been developed for varactors with a silicon dioxide dielectric. In proof-of-concept devices, the highest continuous tuning range is 400% (24 to 121 fF) and the measured quality factors are 123 and 69 (0.1 and 0.7 pF capacitance, respectively) at 2 GHz. The varactors have a compact design and fit within an area of 500 by 100  $\mu$ m.

### Declaration

The results reported in Section 3.3.2 consist of joint work with Andrew J. Laister from the University of Leeds. All other results reported in this thesis are primarily due to the author, except for background results, which are clearly referenced. Some of the results in Chapters 3 to 5 have been published elsewhere [104, 122, 134].

### Acknowledgements

I would like to extend my profound gratitude towards my supervisors Prof. Eric Yeatman and Prof. Andrew Holmes for their support throughout this work. This dissertation would not have been possible without their intellectual and financial support, and I am gratefully indebted to them. I am also thankful for the additional financial support from Prof. Richard Syms through my role as the IT administrator of the Optical and Semiconductor Devices group.

Throughout the duration of this project, many individuals have provided help in the form of technical collaboration and stimulating discussions. I thank Dr Stepan Lucyszyn for his advice on RF design and testing. Through the EPSRC flagship collaboration, my interaction with Mr Robert Wright and Mr David Darbyshire from Cranfield University has been particularly important for the work on designing a zipping varactor with a high-permittivity dielectric. I am also thankful for the assistance of Mr Andrew Laister from the University of Leeds in running electromagnetic simulations.

The OSD group has been a great place to work precisely because of the wonderful friends and colleagues who share the space on Level 7. My thanks are extended to Tzern Tzuin, Yasaman, Kaushal, Cairan, Jiebin, Xuguo, Justin, Kai, Zhou Yun, Zhao Li, Ingrid, Sanjay, Pei Wern, Dave (and Anna), and everyone else in the OSD group for sharing the lighter moments as well as the pains of research. Numerous discussions with Guangbin, Werner, Anshu, Michalis, Bob and Anisha enabled me to refine my own research work. In addition, special mention has to be made of Susan's help in all administrative matters.

At every stage of my project, I have received input, in various forms, on my experimental work. I would like to thank Dr Munir Ahmad for his help with process issues and for keeping the lab running. I am also grateful for Dr Tom Tate's SEM training as well as for his equipment troubleshooting. I thank the researchers at Microsaic for sharing their knowledge on MEMS fabrication. In particular, I would like to extend my thanks to Guodong, Shane, Richard, Kham and Sunil. I have also enjoyed my conversations with Dr Steven Wright on the topic of thin film deposition. The support of many friends has been instrumental in the success of my research over the last three years. I would like to thank Feng Huai, Teck Por, Eda, Shaun, Alwyn, Gabriel, Ting Jun, Justin and Yvonne for all the laughter shared. I am also grateful for my fellowship group from All Souls Langham Place for their continued encouragement and prayers. Special thanks go out to Hugh for his cakes from Hong Kong. I would also like to thank the wardening team at Falmouth and Keogh Halls (Dan, Tina, Paul, Aidan and Fathima) with whom I had the pleasure of working with for two wonderful years.

I am greatly indebted to three individuals for voicing their support at critical moments in my studies, namely Ronica, Prof. Hoon Hian Teck and Dr Ho Weng Kin. Their practical advice and godly discipline have been inspiring.

Most of all, I would like to thank my family who have supported me wholeheartedly throughout my studies in London. Words cannot express my depth of gratitude to my parents, to whom this thesis is dedicated to, for their love and encouragement. I thank also my sister Chui Yin, my brother Suan Hau, Uncle Raymond and Auntie Serene for their continued support. Finally, I would like to thank Valerie for her unconditional love and for renewing my motivation to complete this work.

To my parents

"For the LORD is good; his steadfast love endures forever, and his faithfulness to all generations." (Psalm 100:5)

## Contents

| 1        | Intr            | ntroduction 2 |                                            |    |

|----------|-----------------|---------------|--------------------------------------------|----|

|          | 1.1             | RF M          | EMS Variable Capacitors                    | 23 |

|          | 1.2             | Resear        | rch Objectives                             | 27 |

|          | 1.3             | Thesis        | Structure                                  | 28 |

| <b>2</b> | ME              | MS Va         | ractors: A Literature Survey               | 29 |

|          | 2.1             | Figure        | s of Merit                                 | 30 |

|          | 2.2             | Gap-T         | uned Varactors                             | 31 |

|          |                 | 2.2.1         | Dual-Gap Varactors                         | 33 |

|          |                 | 2.2.2         | Interdigital Gap-Tuned Varactors           | 34 |

|          |                 | 2.2.3         | Varactors with Piezoelectric Actuation     | 36 |

|          |                 | 2.2.4         | Gap-Tuned Varactors with Thermal Actuation | 38 |

|          | 2.3             | Area-7        | Γuned Varactors                            | 39 |

|          |                 | 2.3.1         | Rotational Varactors                       | 40 |

|          |                 | 2.3.2         | Other Area-Tuned Varactors                 | 42 |

|          | 2.4             | Zippin        | g Varactors                                | 43 |

|          | 2.5             | Digita        | l MEMS Varactors                           | 47 |

|          | 2.6             | Other         | Micromachined Varactors                    | 49 |

|          | 2.7             | RF M          | EMS Varactor Library                       | 53 |

| 3        | $\mathbf{Desi}$ | ign and       | l Simulation                               | 57 |

|          | 3.1             | Zippin        | g Varactor Concept                         | 58 |

|          | 3.2             | Electro       | omechanical Modelling                      | 60 |

|          |                 | 3.2.1         | 3D FEM/BEM Model                           | 60 |

|          |                 | 3.2.2         | 2D Semi-Analytical Model                   | 64 |

|          |             | 3.2.3   | 2D FEM Model with Equivalent Elastic Modulus | 71  |  |

|----------|-------------|---------|----------------------------------------------|-----|--|

|          |             | 3.2.4   | Simulation Results                           | 74  |  |

|          |             | 3.2.5   | Parametric Studies                           | 80  |  |

|          | 3.3         | RF De   | sign                                         | 82  |  |

|          |             | 3.3.1   | Quality Factor                               | 82  |  |

|          |             | 3.3.2   | Electromagnetic Simulation                   | 83  |  |

|          |             | 3.3.3   | Coplanar Waveguide Design                    | 85  |  |

| 4        | Fabrication |         |                                              |     |  |

|          | 4.1         | Process | s Flow                                       | 88  |  |

|          |             | 4.1.1   | Bottom Wafer Process                         | 88  |  |

|          |             | 4.1.2   | Top Wafer Process                            | 90  |  |

|          | 4.2         | Device  | Assembly                                     | 91  |  |

|          | 4.3         | Process | s Optimisation                               | 93  |  |

|          |             | 4.3.1   | Lithography                                  | 93  |  |

|          |             | 4.3.2   | Gold Plating                                 | 95  |  |

|          |             | 4.3.3   | Wet Etching                                  | 101 |  |

|          |             | 4.3.4   | RF Sputtering                                | 103 |  |

|          | 4.4         | Assem   | bly Optimisation                             | 107 |  |

|          |             | 4.4.1   | Thermosonic Bonding                          | 107 |  |

|          |             | 4.4.2   | Mechanical Reliability of Assembled Dies     | 108 |  |

|          | 4.5         | Summa   | ary                                          | 110 |  |

| <b>5</b> | Vara        | actor C | haracterisation                              | 112 |  |

|          | 5.1         | RF Me   | easurements                                  | 112 |  |

|          |             | 5.1.1   | Experimental Setup                           | 112 |  |

|          |             | 5.1.2   | Equivalent Circuit Model                     | 114 |  |

|          |             | 5.1.3   | Results                                      | 115 |  |

|          | 5.2         | Discuss | sion                                         | 116 |  |

|          |             | 5.2.1   | Deviation from Idealised Geometry            | 117 |  |

|          |             | 5.2.2   | Modified 3D Model                            | 119 |  |

|          | 5.3         | Q-facto | or Measurement                               | 120 |  |

| 6        | Con         | clusion | S                                            | 122 |  |

|          | 6.1         | Zipping | g Varactor Performance                       | 123 |  |

|              | 6.2                   | Future Work                                         | 124 |

|--------------|-----------------------|-----------------------------------------------------|-----|

|              | 6.3                   | List of Publications                                | 125 |

| $\mathbf{A}$ | MAT                   | <b>FLAB</b> Code for Semi-Analytical Varactor Model | 127 |

| в            | ANS                   | YS Code for 2D FEM Varactor Model                   | 132 |

| $\mathbf{C}$ | Process Parameters 13 |                                                     | 139 |

|              | C.1                   | Bottom Wafer (Soda Lime Glass)                      | 139 |

|              | C.2                   | Top Wafer (Soda Lime Glass/Fused Silica)            | 141 |

|              | C.3                   | Die-Level Assembly                                  | 142 |

| Re           | References 14         |                                                     |     |

# List of Figures

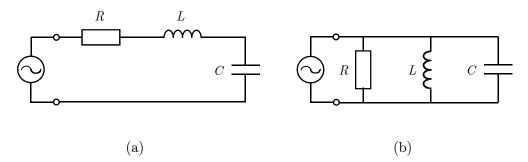

| 1.1 | Resonant circuits: (a) series RLC resonator; (b) parallel RLC resonator     | 21 |

|-----|-----------------------------------------------------------------------------|----|

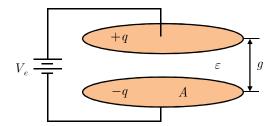

| 1.2 | Parallel-plate capacitor                                                    | 22 |

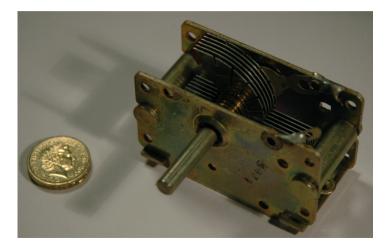

| 1.3 | A<br>mateur radio air variable capacitor (100 pF maximum capacitance)       | 23 |

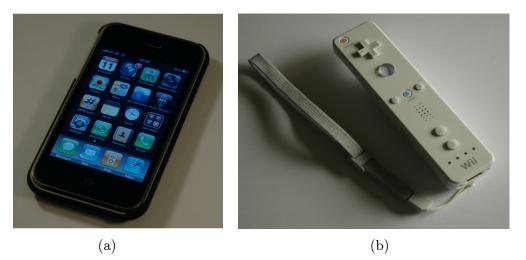

| 1.4 | Popular consumer products with MEMS components: (a) Apple iPhone            |    |

|     | 3GS; (b) Nintendo Wii remote controller                                     | 24 |

| 1.5 | p- $n$ junction varactor model                                              | 25 |

| 1.6 | A micromachined MEMS varactor [37]                                          | 25 |

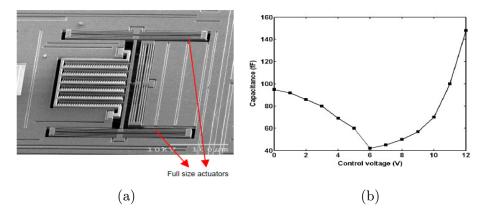

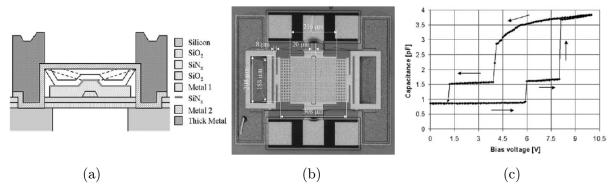

| 2.1 | UC Berkeley gap-tuned parallel-plate varactor: (a) SEM image; (b)           |    |

|     | C-V characteristic [18]                                                     | 32 |

| 2.2 | Columbia three-plate varactor: (a) SEM image; (b) schematic cross-          |    |

|     | section [52]                                                                | 32 |

| 2.3 | Nikon three-plate varactor: (a) SEM image; (b) schematic cross-section;     |    |

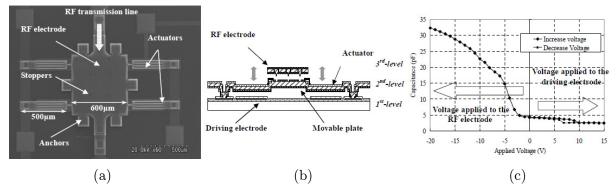

|     | (c) $C-V$ characteristic [54]                                               | 33 |

| 2.4 | UIUC dual-gap varactor (a) SEM image; (b) schematic cross-section [57].     | 34 |

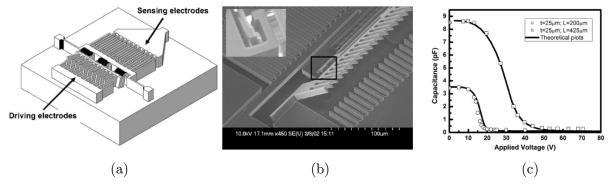

| 2.5 | NJIT interdigital varactor: (a) microscope image; (b) close-up view of      |    |

|     | drive and sense electrodes; (c) $C-V$ characteristic [66]                   | 35 |

| 2.6 | Georgia Tech interdigital varactors: (a) HARPSS varactor [67]; (b) high     |    |

|     | aspect-ratio silver varactor [68]                                           | 36 |

| 2.7 | LG Electronics piezoelectric varactor: (a) SEM image of movable plate       |    |

|     | and actuators; (b) plot of $C_r$ versus voltage and device schematic [70]   |    |

|     | (figures reproduced from [48])                                              | 36 |

| 2.8 | USC piezoelectric varactor: (a) SEM image; (b) $C-V$ characteristic [71]    | 37 |

| 2.9 | Toshiba piezoelectric varactor: (a) optical image; (b) $C-V$ characteristic |    |

|     | [73]                                                                        | 38 |

| 2.10 | CU Boulder thermally-actuated varactor: (a) optical image; (b)              |    |

|------|-----------------------------------------------------------------------------|----|

|      | C-V characteristic [75]                                                     | 38 |

| 2.11 | RSC area-tuned interdigital varactor: (a) optical images showing change     |    |

|      | in finger overlap area with bias voltage; (b) C-V characteristic [51]       | 40 |

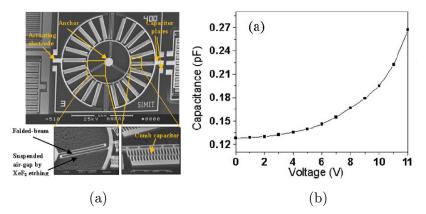

| 2.12 | UCLA interdigital rotational varactor: (a) device schematic; (b) SEM        |    |

|      | image of drive and sense electrodes; (c) $C-V$ characteristics of devices   |    |

|      | with different finger lengths [19]                                          | 40 |

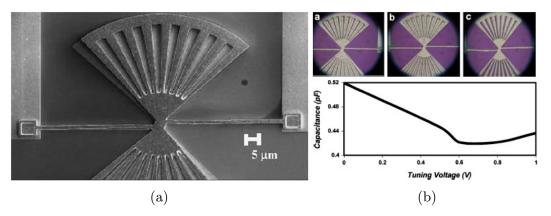

| 2.13 | SIMIT rotational varactor: (a) SEM image; (b) C-V characteristic [82]       | 41 |

| 2.14 | EPFL segmented rotational varactor: (a) SEM image; (b) optical images       |    |

|      | showing various states of actuation (above), and $C-V$ characteristic       |    |

|      | (below) [83]                                                                | 42 |

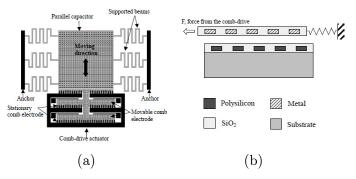

| 2.15 | Lateral segmented varactor: (a) varactor design; (b) tuning principle [85]. | 42 |

| 2.16 | CMU thermally-actuated interdigital varactor: (a) SEM image [87]; (b)       |    |

|      | C-V characteristic [86]                                                     | 43 |

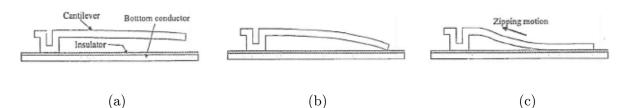

| 2.17 | MIT zipping varactor operation: (a) initial beam displacement; (b)          |    |

|      | cantilever pull-in; (c) zipping regime [94]                                 | 44 |

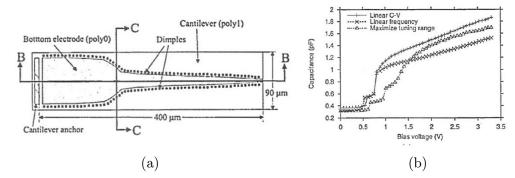

| 2.18 | MIT varactor: (a) optimised bottom electrode shape; (b)                     |    |

|      | C-V characteristics of three different zipping varactors [94]               | 44 |

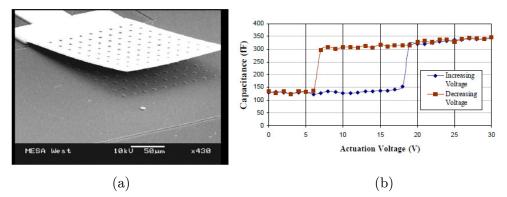

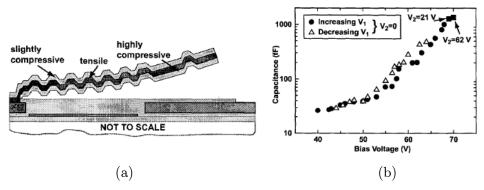

| 2.19 | Sandia varactor: (a) SEM image; (b) C-V characteristic [98]                 | 45 |

| 2.20 | Lincoln Lab varactor: (a) device schematic; (b) $C-V$ characteristic [100]  | 45 |

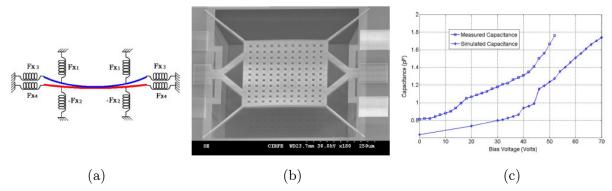

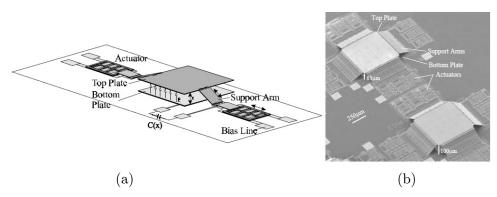

| 2.21 | UW dual-zipping varactor: (a) device schematic; (b) SEM image; (c)          |    |

|      | model and prototype $C-V$ characteristics [102]                             | 46 |

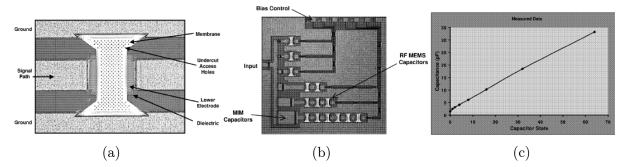

| 2.22 | Raytheon digital MEMS varactor: (a) individual switch; (b) switch array     |    |

|      | topology; (c) discrete capacitance values [105]                             | 47 |

| 2.23 | CU Boulder cascading-switch varactor: (a) optical image; (b)                |    |

|      | C-V characteristic [109]                                                    | 48 |

| 2.24 | Nokia three-state varactor: (a) schematic cross-section; (b) fabricated     |    |

|      | device; (c) $C-V$ characteristic [58]                                       | 49 |

| 2.25 | Scratch-drive actuated varactor: (a) operating principle; (b) SEM image     |    |

|      | [113]                                                                       | 49 |

| 2.26 | UoM varactor with movable dielectric: (a) operating principle; (b) SEM      |    |

|      | image [114]                                                                 | 50 |

| 2.27 | KU Leuven torsion beam varactor: (a) microscope image; (b)                  |    |

|      | C-V characteristic [115]                                                        | 50 |

|------|---------------------------------------------------------------------------------|----|

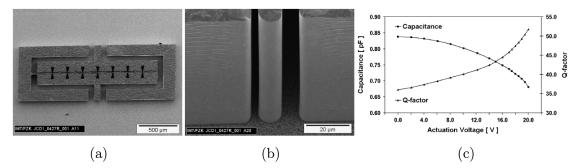

| 2.28 | U of S vertical varactor: (a) top view of fabricated device; (b) close-up       |    |

|      | view of cantilever tip; (c) measured $C-V$ characteristic and $Q$ -factor at    |    |

|      | 4 GHz [117]                                                                     | 51 |

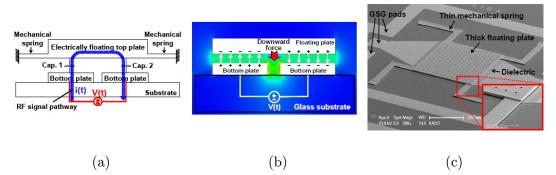

| 2.29 | KAIST varactor with electrically floating plate: (a) device schematic; (b)      |    |

|      | simulated electrostatic field; (c) SEM image [118]                              | 52 |

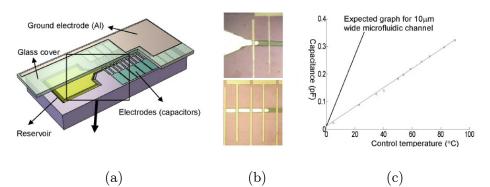

| 2.30 | MU microfluidic varactor: (a) device schematic; (b) actual device               |    |

|      | showing mercury flow in the micro-channel; (c) capacitance-temperature          |    |

|      | characteristic [119]                                                            | 52 |

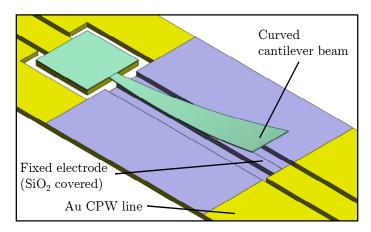

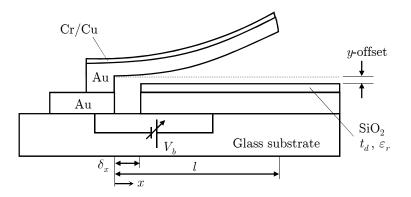

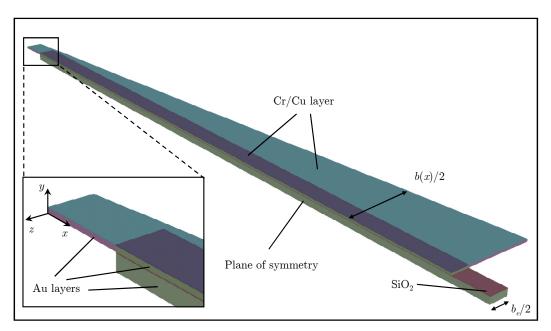

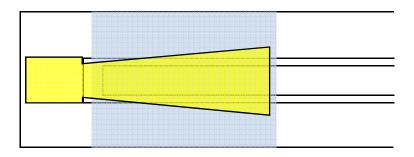

| 3.1  | Zipping varactor illustration                                                   | 59 |

| 3.2  | Schematic cross-section of device                                               | 59 |

| 3.3  | Coventor 3D varactor model with symmetry about the z-plane                      | 60 |

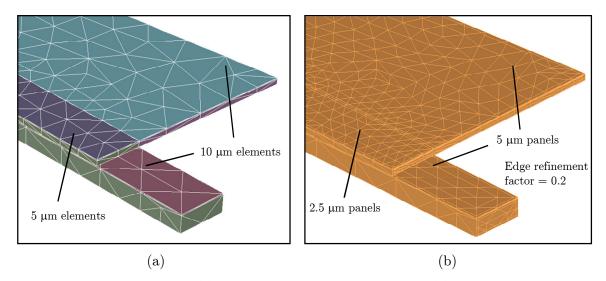

| 3.4  | Coventor mesh: (a) mechanical domain FEM mesh; (b) electrical domain            |    |

|      | BEM mesh                                                                        | 62 |

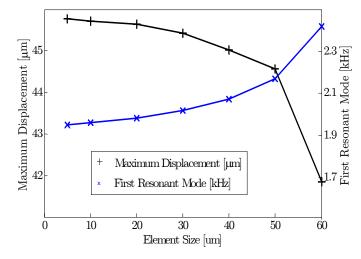

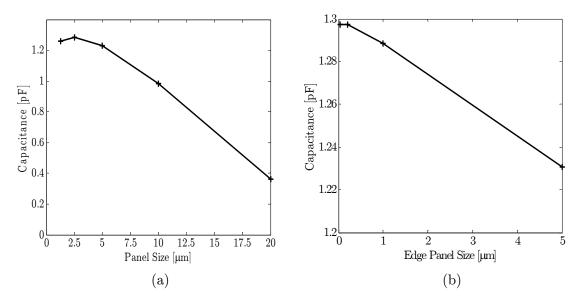

| 3.5  | FEM mesh convergence                                                            | 63 |

| 3.6  | BEM mesh convergence: (a) capacitance versus global panel size; (b)             |    |

|      | capacitance versus edge panel size (5 $\mu m$ global panel size)                | 63 |

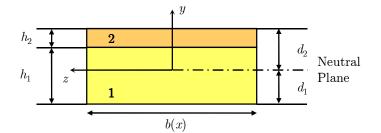

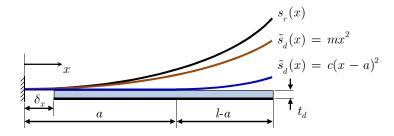

| 3.7  | Cantilever cross-section at arbitrary x-location                                | 65 |

| 3.8  | Cantilever stress in $x$ -direction: (a) as deposited; (b) after relaxation but |    |

|      | before bending                                                                  | 66 |

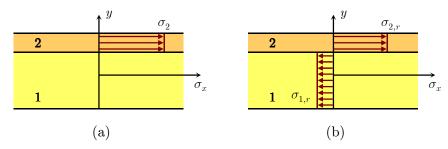

| 3.9  | Cantilever profile after release and when deflected electrostatically           | 68 |

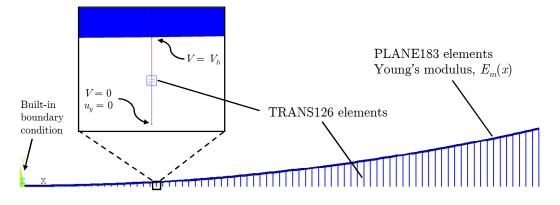

| 3.10 | ANSYS 2D varactor model                                                         | 73 |

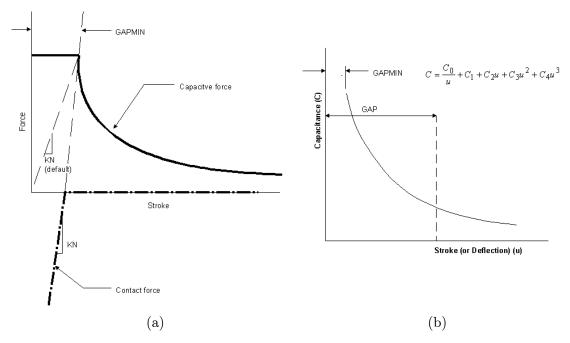

| 3.11 | ANSYS TRANS126 element properties: (a) force versus stroke; (b)                 |    |

|      | capacitance versus stroke [133]                                                 | 74 |

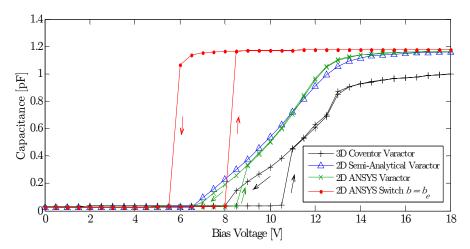

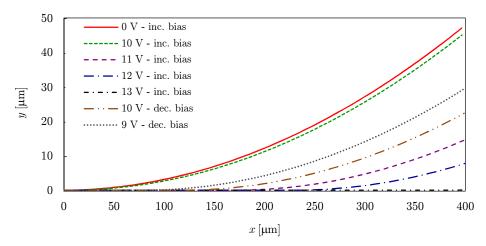

| 3.12 | Zipping varactor simulation results                                             | 75 |

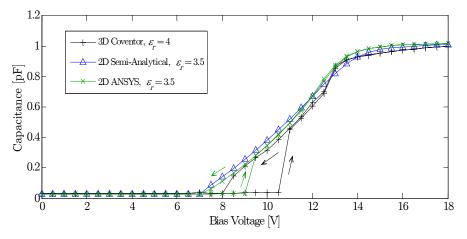

| 3.13 | Simulation results using an effective $\varepsilon_r$ for the 2D models         | 77 |

| 3.14 | Cantilever axial profile in the plane of symmetry $(z = 0)$                     | 78 |

| 3.15 | Cantilever transverse profile at $x = l/2$ for increasing bias                  | 78 |

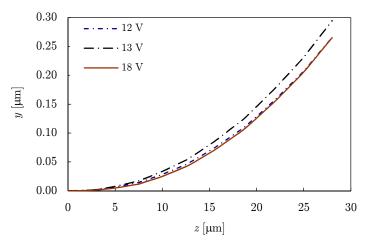

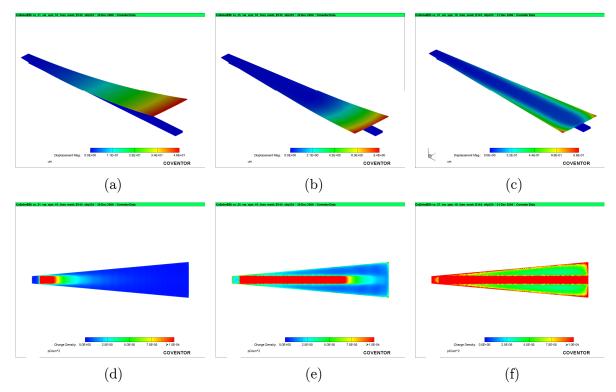

| 3.16 | Cantilever deflection (top) and charge density (bottom) for 10 V (a, d),        |    |

|      | 12 V (b, e) and 18 V (c, f) when the bias is increased                          | 79 |

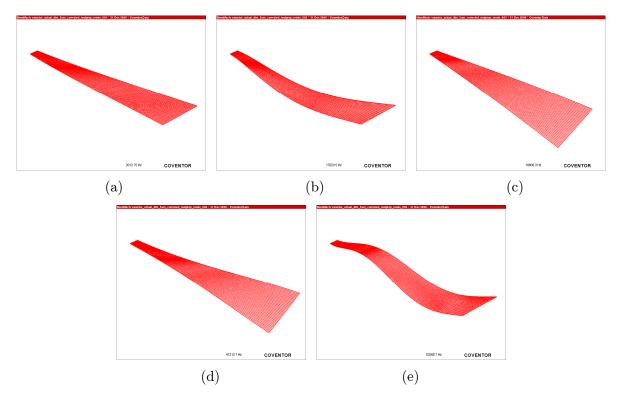

| 3.17 | First five vibration modes for varactor cantilever: (a) $2.0 \text{ kHz}$ ; (b) |    |

|      | 17.0 kHz; (c) 18.6 kHz; (d) 41.3 kHz; (e) 52.6 kHz                              | 79 |

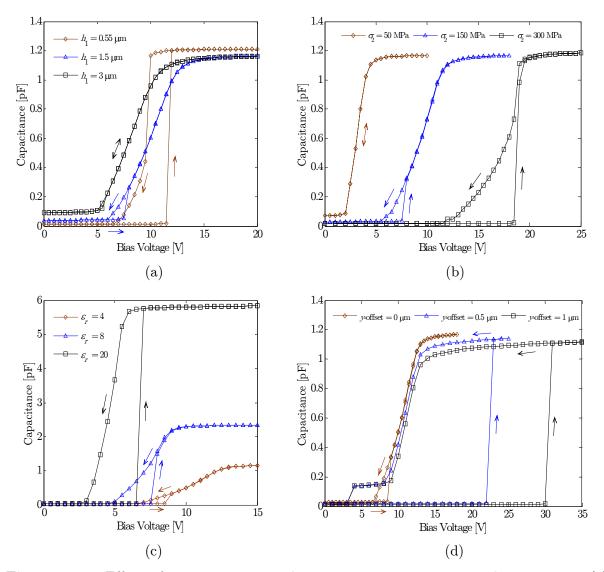

| 3.18 | Effect of zipping varactor design parameters on tuning characteristics: (a)     |    |

|      | thickness of cantilever bottom layer; (b) tensile stress in cantilever top |     |

|------|----------------------------------------------------------------------------|-----|

|      | layer; (c) dielectric constant; (d) additional gap between cantilever and  |     |

|      | dielectric                                                                 | 81  |

| 3.19 | Series RLC model of a capacitor                                            | 83  |

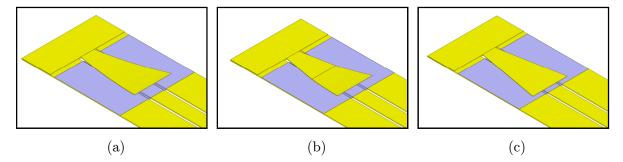

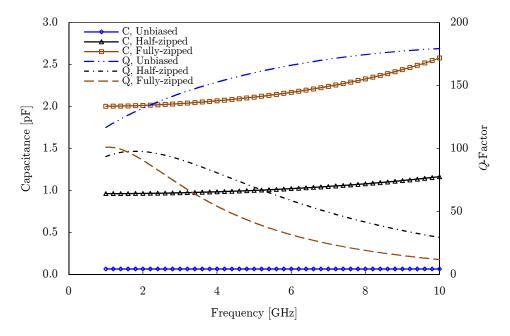

| 3.20 | Tuning states for zipping varactor HFSS model: (a) unbiased; (b) half-     |     |

|      | zipped; (c) fully-zipped                                                   | 84  |

| 3.21 | HFSS electromagnetic simulation results                                    | 85  |

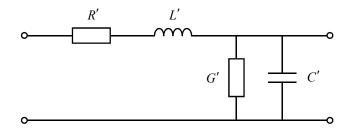

| 3.22 | Transmission line equivalent circuit model                                 | 86  |

| 3.23 | CPW lumped element model: (a) series resistance per unit length; (b)       |     |

|      | lossless characteristic impedance                                          | 86  |

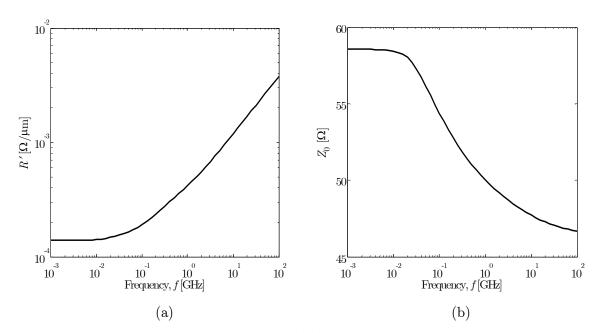

| 4.1  | Bottom wafer fabrication steps.                                            | 89  |

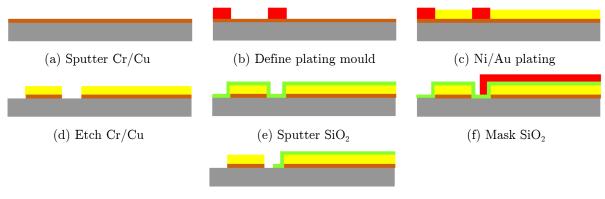

| 4.2  | Top wafer fabrication steps                                                | 91  |

| 4.3  | Wafer dicing, device assembly and release                                  | 92  |

| 4.4  | Aligner-bonder for die-level thermosonic bonding                           | 93  |

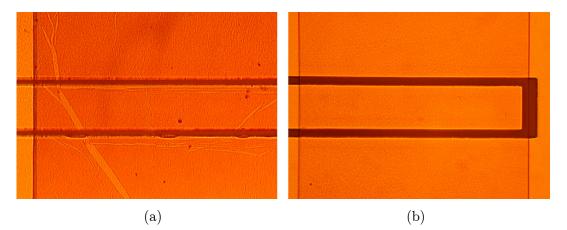

| 4.5  | Gold under-plating leading to transmission line shorts                     | 94  |

| 4.6  | CPW lines with under-plating completely eliminated                         | 95  |

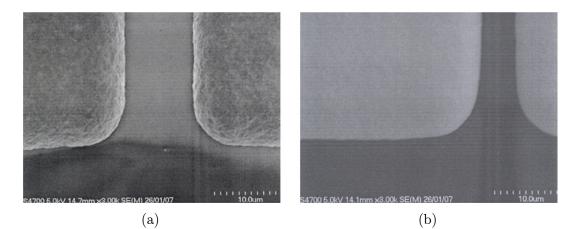

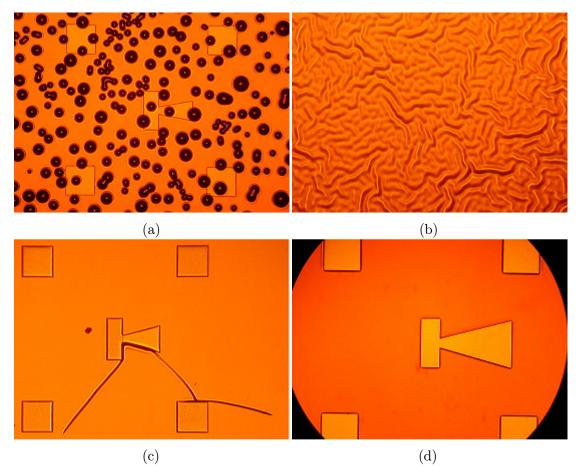

| 4.7  | Post-RIE resist strip: (a) without ashing step; (b) with ashing step       | 95  |

| 4.8  | Gold plating surface finish: (a) ECF60; (b) ECF64 (photos courtesy of      |     |

|      | Mike Wild, Metalor Technologies UK).                                       | 96  |

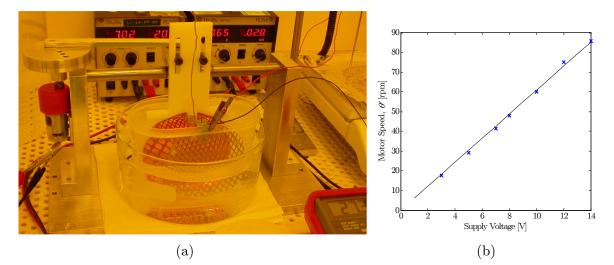

| 4.9  | ECF64 gold plating issues: (a) high surface roughness; (b) film            |     |

|      | delamination due to excessive stress.                                      | 97  |

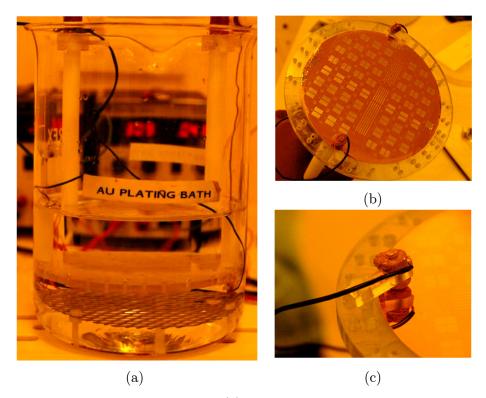

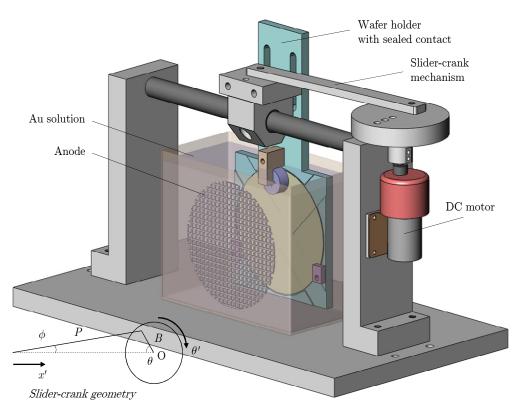

| 4.10 | Horizontal gold plating setup: (a) wafer holder and platinised titanium    |     |

|      | mesh in gold solution; (b) wafer holder with exposed contacts; (c) close-  |     |

|      | up view of exposed contact                                                 | 98  |

| 4.11 | New gold plating setup with vertical plating configuration and cathode     |     |

|      | agitation.                                                                 | 99  |

| 4.12 | Actual gold plating setup: (a) plating a 4-inch wafer; (b) motor speed     |     |

|      | versus supply voltage                                                      | 100 |

| 4.13 | Seed layer over-etch: (a) copper over-etch causing chromium peeling in     |     |

|      | assembled device; (b) underside view of over-etched chromium and           |     |

|      | copper underneath CPW lines                                                | 102 |

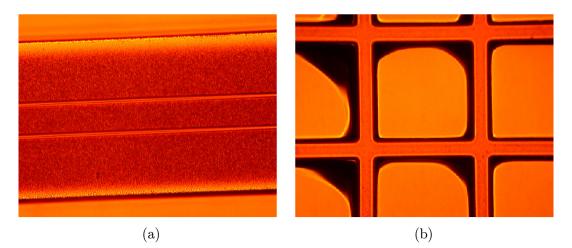

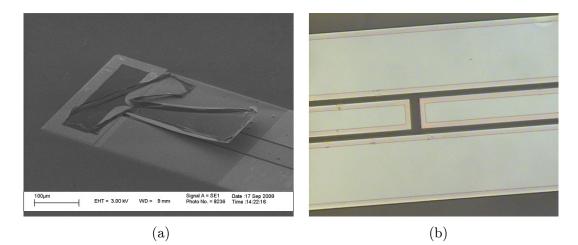

| 4.14 | Cr/Cu sputtering issues: (a) bubbling in sacrificial layer; (b)            |     |

|      | delamination due to overheating; (c) cracking in seed and sacrificial      |     |

|      | layers; (d) good top wafer structures.                                                         | 104 |

|------|------------------------------------------------------------------------------------------------|-----|

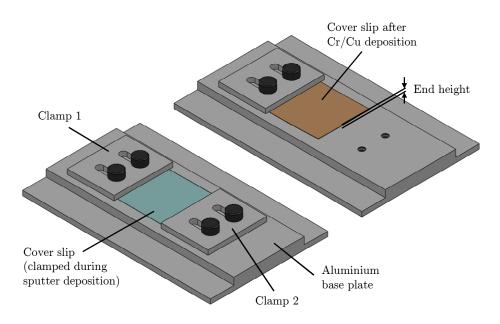

| 4.15 | Device for measuring stress in sputtered films                                                 | 106 |

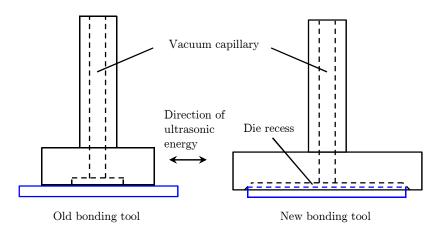

| 4.16 | Tungten carbide bonding tools                                                                  | 108 |

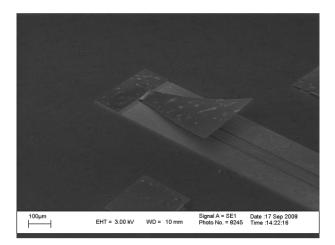

| 4.17 | Varactor anchor damaged during assembly                                                        | 109 |

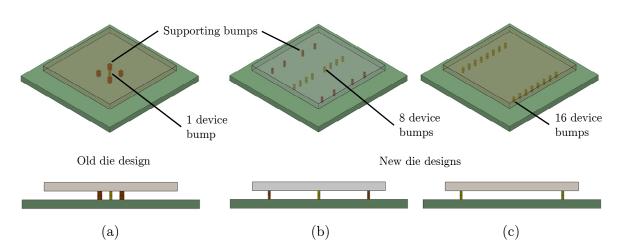

| 4.18 | Varactor die designs showing isometric and front views: (a) old version                        |     |

|      | with one device and four supporting bumps; (b) new series varactor die                         |     |

|      | with 16 bumps (8 devices); (c) new shunt varactor die with 16 bumps (all                       |     |

|      | devices)                                                                                       | 109 |

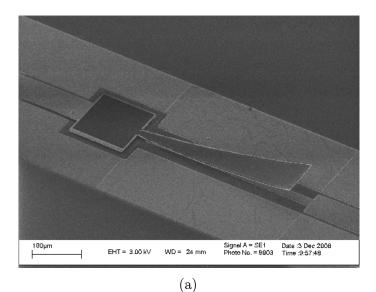

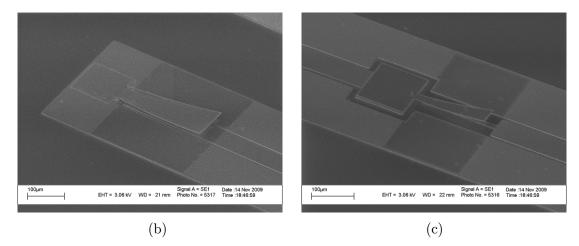

| 4.19 | Zipping varactor prototypes: (a) series device $(l = 400 \ \mu m)$ ; (b) shunt                 |     |

|      | device $(l = 300 \ \mu m)$ ; (c) series device $(l = 200 \ \mu m)$                             | 110 |

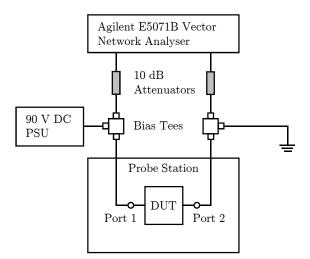

| 5.1  | RF characterisation setup.                                                                     | 113 |

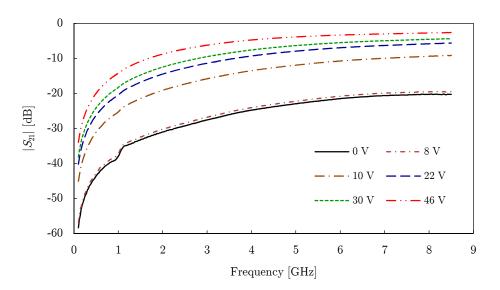

| 5.2  | Measured $ S_{21} $ for 400 µm series varactor (including CPW lines)                           | 113 |

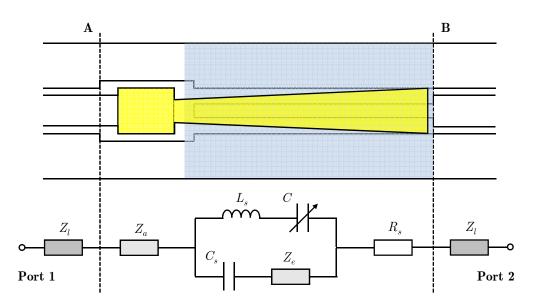

| 5.3  | Series varactor layout and its equivalent circuit model                                        | 114 |

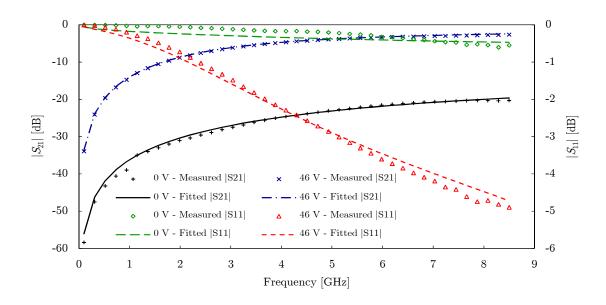

| 5.4  | Measured and fitted $S$ -parameter magnitude at extreme bias values                            | 115 |

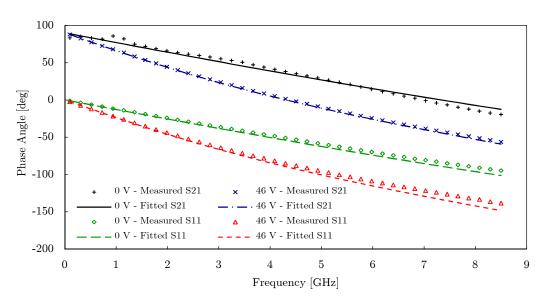

| 5.5  | Measured and fitted S-parameter phase at extreme bias values                                   | 115 |

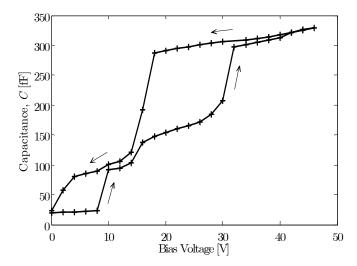

| 5.6  | Measured $C-V$ characteristic of zipping varactor prototype                                    | 116 |

| 5.7  | Wyko scan of varactor: (a) misalignment in cantilever; (b) transverse                          |     |

|      | profile at $x = l/2$                                                                           | 117 |

| 5.8  | SEM image of tested varactors showing electrode lift-off from substrate                        | 118 |

| 5.9  | Cross-section of dielectric-covered bottom electrode                                           | 119 |

| 5.10 | $C\!\!\!\!-V$ characteristic of modified 3D model and varactor prototype                       | 120 |

| 5.11 | Shunt varactor layout.                                                                         | 120 |

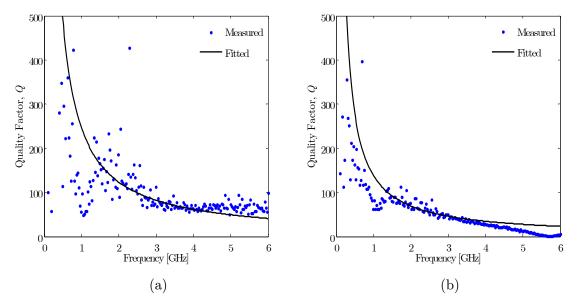

| 5.12 | Zipping varactor quality factor: (a) $0.1 \text{ pF}$ device capacitance; (b) $0.7 \text{ pF}$ |     |

|      | device capacitance                                                                             | 121 |

# List of Tables

| 2.1 | Gap-tuned MEMS varactors.                                   | 54  |

|-----|-------------------------------------------------------------|-----|

| 2.2 | Area-tuned MEMS varactors                                   | 55  |

| 2.3 | Zipping varactors                                           | 55  |

| 2.4 | Digital MEMS varactors                                      | 56  |

| 2.5 | Other micromachined varactors.                              | 56  |

| 3.1 | Varactor model parameters                                   | 61  |

| 3.2 | Model complexity and solution time                          | 76  |

| 3.3 | Variation of z-curvature with bias voltage                  | 78  |

| 3.4 | Varactor parameters for HFSS model                          | 84  |

| 4.1 | ECF64 supplier operating conditions.                        | 96  |

| 4.2 | Etch time for 170 nm thick Cu film on 7.1 mm by 7.1 mm dies | 103 |

| 4.3 | Stress in sputtered Cr/Cu layers                            | 107 |

### Nomenclature

- <sup>'</sup> Prime denotes parameter values per unit distance in Chapter 3

- <sup>'</sup> Prime denotes derivative with respect to time in Chapter 4

- $\sim$  Tilde denotes trial function (with the exception of the biaxial modulus)

- $\alpha_i$  Parabolic fitting curve parameters (i = 1 to 3)

- $\delta_x$  Electrode offset

- $\varepsilon$  Permittivity of dielectric material

- $\varepsilon_0$  Permittivity of free space

- $\varepsilon_c$  Biaxial contraction strain

- $\varepsilon_r$  Relative permittivity (i.e. dielectric constant)

- $\phi$  Angle between connecting rod and horizontal reference

- $\kappa$  Curvature due to bending

- $\lambda$  Wavelength of RF signal

- u Poisson's ratio

- $\nu_1$  Poisson's ratio of gold

- $\nu_2$  Poisson's ratio of chromium/copper

- $\Pi$  Total elastic potential energy

- $\theta$  Angle between crank position and horizontal reference

- $\sigma$  Conductivity

- $\sigma_2$  Biaxial stress in chromium/copper

- $\sigma_{1,r}$  Biaxial stress in gold after relaxation

- $\sigma_{2,r}$  Biaxial stress in chromium/copper after relaxation

- $\omega$  Angular frequency

- a, c, m Trial function parameters for displaced cantilever axial profile

- A Area

- *b* Cantilever width

- $b_e$  Electrode width

- *B* Radius of crank

- $c_i$  Capacitance parameters for TRANS126 element (i = 0 to 4)

- C Capacitance

| $C_1$       | Lowest capacitance in continuously tunable range                       |

|-------------|------------------------------------------------------------------------|

| $C_{2}$     | Highest capacitance in continuously tunable range                      |

| $C_r$       | Capacitance ratio                                                      |

| $C_{s}$     | Series capacitance in varactor circuit model                           |

| $C_{max}$   | Maximum capacitance                                                    |

| $C_{min}$   | Minimum capacitance                                                    |

| $d_1$       | Distance from bottom surface of bi-layered cantilever to neutral axis  |

| $d_2$       | Distance from top surface of bi-layered cantilever to neutral axis     |

| D           | Flexural rigidity of plate in bending                                  |

| $D_1$       | Flexural rigidity of gold layer                                        |

| $D_2$       | Flexural rigidity of chromium/copper layer                             |

| E           | Young's modulus                                                        |

| $E_1$       | Young's modulus of gold                                                |

| $E_2$       | Young's modulus of chromium/copper                                     |

| $E_d$       | Young's modulus of dielectric                                          |

| $E_m$       | Young's modulus function of cantilever in ANSYS model                  |

| $\tilde{E}$ | Biaxial modulus                                                        |

| f           | Frequency of RF signal                                                 |

| $f_e$       | Electrostatic force per unit length                                    |

| $f_r$       | Electrical self-resonance frequency                                    |

| $F_s$       | External surface force                                                 |

| ${F}_{b}$   | External body force                                                    |

| g           | Plate separation in parallel-plate capacitor                           |

| G           | Conductance                                                            |

| h           | Cantilever total thickness                                             |

| $h_1$       | Thickness of gold layer in cantilever                                  |

| $h_2$       | Thickness of chromium/copper layer in cantilever                       |

| $h_m$       | Cantilever thickness in ANSYS model                                    |

| $I_1$       | Area moment of inertia of gold layer about the neutral axis            |

| $I_2$       | Area moment of inertia of chromium/copper layer about the neutral axis |

| $I_m$       | Area moment of inertia of cantilever in ANSYS model                    |

| $K_{c}$     | Stress intensity factor                                                |

| $k_n$       | Normal stiffness of TRANS126 element after closure to minimum gap      |

| l           | Cantilever length                                                      |

| L       | Inductance                                                           |  |  |

|---------|----------------------------------------------------------------------|--|--|

| $L_s$   | Series inductance                                                    |  |  |

| M       | Bending moment                                                       |  |  |

| $M_{m}$ | Bending moment of cantilever in ANSYS model                          |  |  |

| Р       | Length of connecting rod                                             |  |  |

| q       | Electric charge                                                      |  |  |

| Q       | Quality factor                                                       |  |  |

| R       | Resistance                                                           |  |  |

| $R_s$   | Series resistance                                                    |  |  |

| 8       | Gap between signal and ground conductors of CPW                      |  |  |

| $s_{d}$ | Axial profile of cantilever under electrostatic load                 |  |  |

| $s_r$   | Initial axial profile of cantilever due to residual stress           |  |  |

| S       | Surface of elastic body                                              |  |  |

| t       | Time                                                                 |  |  |

| $t_d$   | Thickness of dielectric                                              |  |  |

| $t_{e}$ | Equivalent air thickness of dielectric                               |  |  |

| TR      | Tuning range                                                         |  |  |

| u       | Displacement of elastic body                                         |  |  |

| $u_y$   | Stoke (vertical displacement) of TRANS126 element                    |  |  |

| $U_{e}$ | External work due to electrostatic force                             |  |  |

| v       | Vertical displacement of cantilever under electrostatic load         |  |  |

| V       | Volume of elastic body                                               |  |  |

| $V_e$   | Electrical potential difference                                      |  |  |

| $V_{b}$ | Bias voltage                                                         |  |  |

| w       | Width of signal conductor in CPW                                     |  |  |

| W       | Strain energy                                                        |  |  |

| $W_m$   | Internal elastic potential energy                                    |  |  |

| x, y, z | Cartesian coordinates                                                |  |  |

| $Z_0$   | Characteristic impedance of transmission line                        |  |  |

| $Z_a$   | Line element representing device anchor in varactor circuit model    |  |  |

| $Z_{e}$ | Line element representing the fixed electrode in varactor circuit me |  |  |

| $Z_l$   | Line element representing CPW in varactor circuit model              |  |  |

|         |                                                                      |  |  |

model

## Abbreviations

| APDL                 | ANSYS Parametric Design Language                            |

|----------------------|-------------------------------------------------------------|

| BCB                  | Benzocyclobutene                                            |

| BEM                  | Boundary Element Method                                     |

| CMOS                 | Complementary Metal-Oxide-Semiconductor                     |

| CMU                  | Carnegie Mellon University                                  |

| CPW                  | Coplanar Waveguide                                          |

| CU Boulder           | University of Colorado at Boulder                           |

| <i>C</i> - <i>V</i>  | Capacitance-Voltage                                         |

| DC                   | Direct Current                                              |

| DI                   | Deionised                                                   |

| DRIE                 | Deep Reactive Ion Etch                                      |

| EPFL                 | Swiss Federal Institute of Technology at Lausanne           |

| FEM                  | Finite Element Method                                       |

| FM                   | Frequency Modulation                                        |

| GPS                  | Global Positioning System                                   |

| $\operatorname{GSM}$ | Global System for Mobile Communications                     |

| HARPSS               | High Aspect-Ratio combined Poly- and Single-crystal Silicon |

| IC                   | Integrated Circuit                                          |

| IPA                  | Isopropyl Alcohol                                           |

| KAIST                | Korea Advanced Institute of Science and Technology          |

| KU Leuven            | Catholic University of Leuven                               |

| LAN                  | Local Area Network                                          |

| MEMS                 | Micro-Electro-Mechanical Systems                            |

| MIT                  | Massachusetts Institute of Technology                       |

| MOS                  | Metal-Oxide-Semiconductor                                   |

| MU                   | University of Missouri                                      |

| MUMPs                | Multi-User MEMS Processes                                   |

| NJIT                 | New Jersey Institute of Technology                          |

| PSU                  | Power Supply Unit                                           |

|                      |                                                             |

| PTFE        | Polytetrafluoroethene                                        |

|-------------|--------------------------------------------------------------|

| PZT         | Lead Zirconate Titanate                                      |

| RF          | Radio-Frequency                                              |

| RIE         | Reactive Ion Etch                                            |

| RMS         | Root Mean Square                                             |

| RSC         | Rockwell Science Center                                      |

| SEM         | Scanning Electron Microscope                                 |

| SIMIT       | Shanghai Institute of Microsystem and Information Technology |

| SOLT        | Short-Open-Load-Through                                      |

| TEM         | Transverse Electromagnetic                                   |

| UC Berkeley | University of California at Berkeley                         |

| UCLA        | University of California at Los Angeles                      |

| UIUC        | University of Illinois at Urbana-Champaign                   |

| UoM         | University of Michigan                                       |

| U of S      | University of Saskatchewan                                   |

| USC         | University of Southern California                            |

| UW          | University of Waterloo                                       |

| UV          | Ultraviolet                                                  |

| VCO         | Voltage-Controlled Oscillator                                |

|             |                                                              |

## Chapter 1

## Introduction

In electrical circuits, capacitors and inductors function as the energy storage elements with the former storing electrical energy and the latter storing magnetic energy [1]. When combined in series or in parallel, capacitors and inductors can be used to implement resonators that are integral to radio communication systems. An RLC circuit consisting of a resistor, an inductor and a capacitor can be connected either in series or in parallel to form a resonant circuit (see Figure 1.1). For both the series and the parallel circuits, the resonance frequency, in radians per second, is given by

$$\omega = \frac{1}{\sqrt{LC}} \tag{1.1}$$

where L and C are the circuit inductance and capacitance, respectively. By tuning either the capacitance or the inductance, the resonant frequency of the circuit can be tuned accordingly.

Figure 1.1: Resonant circuits: (a) series RLC resonator; (b) parallel RLC resonator.

Figure 1.2 shows the geometry of a simple parallel-plate capacitor consisting of two conductor plates separated by an insulating region known as the dielectric. If the charge that exists on the two plates is +q on one plate and -q on the other, the capacitance is defined as the constant of proportionality relating the potential difference,  $V_e$  to the charge, q i.e.

$$C \equiv \frac{q}{V_e} \tag{1.2}$$

This relationship is true in general for any two conductors. For the case of the parallelplate capacitor, the relationship between capacitance and the device geometry can be expressed as [2]

$$C = \frac{A\varepsilon}{g} \tag{1.3}$$

where A is the overlap area of the plates, g is the plate separation and  $\varepsilon$  is the permittivity of the dielectric. Equation (1.3) is valid provided the area is large relative to the plate separation [3].

Figure 1.2: Parallel-plate capacitor.

Variable or tunable capacitors are designed with a variety of capacitance ranges and are packaged into different sizes depending on the application. By varying the capacitance area, the plate separation distance or the dielectric permittivity, the device capacitance can be tuned. An air variable capacitor used in amateur radio communication equipment is shown in Figure 1.3. In this design, turning the tuning shaft varies the amount of overlap area between capacitor stator and rotor plates, resulting in a change in capacitance.

The focus of this dissertation is on the development of a new continuously tunable, micromachined capacitor suitable for applications in the 0.1 to 5 GHz frequency range. An introduction to the context of this work, the research objectives and a brief description of the thesis organisation is given in the following sections.

Figure 1.3: Amateur radio air variable capacitor (100 pF maximum capacitance).

### 1.1 RF MEMS Variable Capacitors

Micro-electro-mechanical systems (MEMS), also known as microsystems, encompass a broad range of miniaturised components fabricated using batch processing techniques derived from the microelectronics industry [4]. From its early beginnings in the 1970's, the MEMS industry has grown tremendously and a recent market study by iSuppli Corp predicts that the global MEMS market will expand to \$8.8 billion by 2012 [5]. Typical MEMS applications include automotive motion sensors, actuators for digital light processing, and ink-jet printer heads, while newer growth areas are fuelled by motion sensors for consumer electronics. Two well-known products employing MEMS technology are the Nintendo Wii game console and the Apple iPhone mobile handset (see Figure 1.4) [6].

The development of the MEMS industry opened new possibilities for implementing tunable radio-frequency (RF) circuit components with enhanced performance [7-11]. Improvements in performance are due, in part, to the development of new materials and the novel use of surface- and bulk-micromachining techniques [12]. On the other hand, MEMS technology opened the possibility of incorporating mechanical motion in integrated-circuit (IC) components. The first MEMS switch was reported by Petersen of IBM in 1979 [13]. Subsequently, Larson et al. from Hughes Research Laboratories demonstrated a rotating MEMS switch for microwave applications in 1991 [14]. Since then many high-quality RF MEMS components have been demonstrated, including switches [15-17], tunable capacitors [18, 19], inductors [20, 21], resonators [22, 23] and their associated application circuits [24-27].

**Figure 1.4:** Popular consumer products with MEMS components: (a) Apple iPhone 3GS; (b) Nintendo Wii remote controller.

Reconfigurable microwave circuits traditionally employ solid-state varactors to provide variable capacitance. The word 'varactor' comes from the term 'variable reactor', i.e. the device capacitive reactance is changed by tuning its capacitance [28]. Varactors in common RF applications include p-n junction diodes [29, 30], Schottky diodes [31, 32] and metal-oxide-semiconductor (MOS) capacitors [33, 34]. The main advantages of MEMS varactors over these traditional solid-state varactors include a higher quality factor (Q-factor), larger tuning range, lower power consumption (with electrostatic actuation), lower temperature sensitivity and high linearity with respect to RF power.

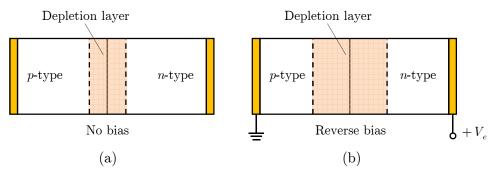

The Q-factors of semiconductor varactors are typically less than 50 for frequencies greater than 1 GHz [8] whereas Q-factors larger than 100 are relatively easy to obtain in MEMS varactors [35]. A physical model of a p-n junction varactor is shown in Figure 1.5, where the device consists of n- and p-type semiconductors sandwiched between metal ohmic contacts. The majority charge carriers in the n- and p-regions are electrons and holes, respectively. A 'depletion layer', characterised by an absence of charge carriers, exists in the middle of the device. Hence, the depletion layer is analogous to the dielectric in a parallel-plate capacitor. When a reverse bias is applied (see Figure 1.5(b)), the width of the depletion layer increases, leading to a decrease in capacitance [36]. Since the varactor series resistance includes the bulk resistance of the semiconductors [28], the Q-factor of a p-n junction varactor is relatively low. In contrast, MEMS varactors can be designed with electrodes that are made using high-conductivity metals such as aluminium or gold.

Figure 1.5: *p*-*n* junction varactor model.

In addition, MEMS varactors have demonstrated tuning ranges greater than 3000% [19] while semiconductor varactors are limited to tuning ranges of 500% or less. The negligible power consumption of electrostatically-actuated MEMS varactors is also particularly attractive for portable consumer electronics since the battery life can be extended. Finally, the linearity of MEMS varactors with respect to RF power is a strong selling point since signal distortion can be reduced in the presence of voltage swings [35]. An example of a MEMS varactor is shown in Figure 1.6 where the device capacitance can be tuned by changing the overlap area between interdigitated structures using a comb-drive actuator.

Figure 1.6: A micromachined MEMS varactor [37].

Other variable capacitors are also available such as ferroelectric varactors [38-40], heterostructure barrier varactors [41, 42] and liquid crystal varactors [43] among others [35, 44]. However, at present only MEMS varactors are able to provide the combination of a high *Q*-factor (i.e. low-loss), large tuning range, low power consumption, low temperature sensitivity and linearity with RF power.

The disadvantages of the MEMS approach to implementing varactors are in some ways similar to the disadvantages associated with MEMS switches [8, 35, 44-47]. For one, MEMS varactors have a greater sensitivity to external vibration due to the use of mechanically compliant parts. Hence, careful design is required to ensure that the varactor will be robust enough for the intended application. In addition, reliability is a concern since a design with moving parts introduces numerous modes of failure such as fracture and creep deformation. Where contact between the moving and fixed parts of a varactor occurs, additional failure modes such as stiction and surface wear can also occur. The problem of moisture- or contaminant-induced stiction can be reduced by encapsulating the varactor within a hermetic package. This increases overall system complexity and cost, and thus the selection of a suitable packaging must be done with careful consideration. Stiction can also be caused by dielectric charging and hence designers may have to select appropriate material combinations or alter certain design features [48] to avoid device failure.

Another disadvantage of MEMS varactors is the slower tuning speed relative to solid-state varactors. Typical tuning speeds for MEMS varactors are on the order of microseconds while tuning speeds for solid-state varactors are in the region of nanoseconds. Nevertheless, this is sufficient for most RF applications except certain communication and radar components that require extreme frequency agility [49]. One way of increasing mechanical response speed is by increasing the stiffness of the compliant suspensions with the trade-off being a higher DC actuation voltage. However, using stiffer mechanical parts will help to reduce the problem of stiction since the mechanical restoring forces are increased. It is also often stated that the high actuation voltages of MEMS components pose difficulties for portable consumer electronics since the supply voltage is usually around 5 V or less. In reality, it is not difficult to scale these voltages to the level required by MEMS components (up to 50 V) through the use of high efficiency DC-DC converters such as charge pumps [46]. The drawback of such an approach would be the increase in system cost.

#### 1.2 Research Objectives

Relative to established RF technologies based on III-V compound semiconductors (GaAs, GaN, InP, InSb) and silicon semiconductors (SiC, SiGe, CMOS, i.e. complementary metal-oxide-semiconductor), RF MEMS is in a relatively early stage of development. Nevertheless, reliability issues are actively being addressed and reasonable actuation cycles (greater than 100 billion) have been achieved for MEMS switches [35, 50]. Research effort into MEMS varactors has only recently picked up momentum and it is expected that similar levels of reliability can be achieved since MEMS varactors share many similar design characteristics with MEMS switches. Once the teething problems are ironed out, it is expected that RF MEMS will become commonplace in the near future, with switches paving the way for other components. Suitable application areas for MEMS varactors include tunable LC-tanks of voltage-controlled oscillators (VCO), impedance matching, tunable filters and loaded-line phase shifters.

In this thesis, the design, simulation, fabrication and experimental characterisation of a novel MEMS varactor is reported. After the switch, the varactor is arguably the next most important component in RF systems. Hence, the goal of this work is to provide a strong design candidate for future commercialisation of MEMS varactors. The primary design challenges include realising a large (greater than 300%), continuous tuning range and a high *Q*-factor (above 100) in order to maximise the versatility of the device in terms of application.

The intended deployment for the new MEMS varactor is in mobile communications, where there is an increasing amount of industry interest in MEMS varactors [8, 46, 47]. The nature of consumer demands for mobile phones is such that an ever increasing level of functionality is required within a smaller and lighter handset. Furthermore, modern mobile phones are required to provide clearer reception and yet demonstrate increased battery life. It is also not uncommon for a modern handset to provide reception over a large number of frequency bands such as GSM (4 bands), wireless LAN, GPS, Bluetooth, FM radio and imminently, mobile television. A low-loss MEMS varactor with a large tuning range is well-placed to meet such requirements and hence the proposed varactor will be aimed for application at the 0.1 to 5 GHz range.

Due to the benefits associated with a more compact varactor in mobile applications, a key specification for the proposed varactor is a small device footprint. To this end, the possibility of integrating a dielectric with very high-permittivity, such as lead zirconate titanate (PZT), is explored. By increasing the dielectric permittivity, the size of the varactor can be reduced for a given capacitance. In addition, it is difficult to achieve large capacitances in MEMS varactors [48] with standard dielectric materials (e.g. silicon dioxide or silicon nitride). Although the capacitance of a device with a lowpermittivity dielectric can be increased by reducing the dielectric thickness, there are practical limitations such as excessive surface roughness, dielectric breakdown and pinhole defects. Therefore, using high-permittivity dielectrics may be the only practical way of providing larger capacitances (greater than 20 pF) for low frequency applications (less than 0.5 GHz).

#### **1.3 Thesis Structure**

The remainder of this thesis is organised into five chapters. In the next chapter, a comprehensive review of MEMS varactors in the open literature is given. The review provides a classification of varactors based on their design features and a varactor library is compiled as a design resource for RF engineers. A new varactor design is proposed in Chapter 3 and detailed electromechanical simulation results are presented. RF simulation results for the varactor *Q*-factor are also reported. Chapter 4 provides a fabrication method developed for the varactor prototypes, with discussion on the process issues and the steps taken to overcome certain developmental challenges. Subsequently, experimental characterisation results for the varactors are reported in Chapter 5. The conclusions arising from the research in this dissertation, and recommendations for future work are summarised in Chapter 6.

## Chapter 2

# MEMS Varactors: A Literature Survey

This chapter is a review of the state of the art in RF MEMS varactor technology. The advantages and disadvantages of various varactor designs are highlighted relative to key figures of merit. The main focus of this literature survey is on *analog* MEMS varactors, where continuous tuning is possible over a range of capacitances. Another method of achieving variable capacitance is by implementing an array of capacitive switches. Such varactors, also known as *digital* MEMS varactors, are also included in the review. From this literature survey, a library of micromachined varactors is compiled as a resource for RF design engineers.

The first MEMS varactor was fabricated at the University of California at Berkeley by Young and Boser [18]. Since then, the MEMS research community has been actively pursuing a high-Q, low-loss tunable capacitor with large tuning range. MEMS varactor designs can be broadly categorised into gap-tuned devices, in which the gap between the capacitor electrodes is varied to achieve tuning, and area-tuned devices, where the electrode overlap area is varied instead. The majority of these varactors employ electrostatic actuation for its relative ease of implementation compared to other actuation methods. In addition, electrostatic actuators consume very little power and hence the device power consumption can be kept low.

#### 2.1 Figures of Merit

In the literature, two parameters are often quoted as an indication of a varactor's capacitance range, namely the capacitance ratio and the tuning range. The capacitance ratio  $(C_r)$  is defined as

$$C_r = \frac{C_{\max}}{C_{\min}}$$

(2.1)

where  $C_{\text{max}}$  is the maximum capacitance and  $C_{\text{min}}$  is the minimum capacitance. A related parameter known as the tuning ratio is given by

tuning ratio

$$= \frac{C_{\text{max}} - C_{\text{min}}}{C_{\text{min}}} = C_r - 1$$

(2.2)

Although the capacitance and tuning ratios give an indication of the absolute capacitance range of a varactor, they do not provide any information on the presence of discontinuity in the capacitance-voltage (C-V) characteristic. Both are functions of the extreme values of capacitance and hence a varactor with a large tuning ratio may not necessarily have a smooth C-V characteristic. Furthermore, the term capacitance ratio is also used to describe bistable capacitive switches operating at two discrete capacitance values. Hence, it can be misleading to use the term capacitance (or tuning) ratio to describe the continuous tuning of varactors. The tuning range (TR) of a varactor, expressed as a percentage, can be defined as

$$TR = \frac{C_2 - C_1}{C_1} \times 100\%$$

(2.3)

provided the device capacitance can be tuned continuously between  $C_1$  and  $C_2$   $(C_2 > C_1)$ . For certain designs, the value of  $C_1$  corresponds to the minimum capacitance although this is not the case for some MEMS varactors that have discontinuous C-V characteristics.

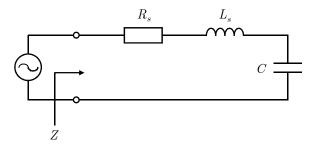

Apart from specifying a varactor's tuning range, the specific value of  $C_1$  (or  $C_2$ ) is required to determine its application frequency. For frequencies between 30 and 600 MHz, capacitance values of around 5 to 50 pF are required [48]. Correspondingly, lower capacitance values of around 0.1 pF are required for applications up to 12 GHz [51]. In MEMS varactors, the capacitance value in the unactuated state is sometimes termed the nominal capacitance. To minimise the loss attributed to a varactor in an RF circuit, its *Q*-factor at the frequency of operation must be maximised [9]. If a varactor is modelled as a capacitance, a resistance and an inductance in series, the *Q*-factor is given by [48]

$$Q = \frac{1}{2\pi f C R_s} \tag{2.4}$$

where f is the frequency of operation, C is the device capacitance and  $R_s$  is the series resistance. This equation is valid provided the frequency is much less than the electrical self-resonance which is defined as

$$f_r = \frac{1}{2\pi\sqrt{L_s C}} \tag{2.5}$$

where  $L_s$  is the series inductance. At the self-resonant frequency, the device Q-factor becomes zero. Therefore, for a varactor to be useful as a tuning component, its intended application frequency must be well below its electrical self-resonance.

The following two sections review gap- and area-tuned varactors, respectively. Section 2.4 introduces *zipping* varactors: devices with parts that zip together to provide capacitance tuning. Digital MEMS varactors are reviewed in Section 2.5 and finally, certain unique varactor designs that are less widely explored are presented in Section 2.6. The performance parameters of MEMS varactors in this review are summarised in a MEMS varactor library in Section 2.7.

#### 2.2 Gap-Tuned Varactors

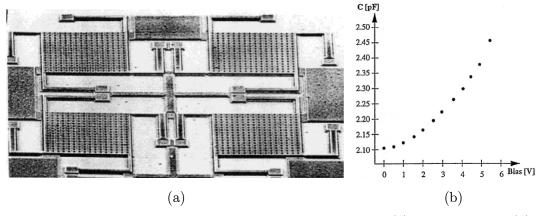

The first successful implementation of a MEMS varactor was Young and Boser's gaptuned device [18]. In this design, a movable aluminium top plate is suspended by four folded beams over a fixed aluminium bottom electrode. The aluminium electrodes ensure a low series resistance and are important for achieving a high *Q*-factor. Capacitance is tuned by varying the bias voltage between the two electrodes. An increase in the bias voltage leads to an increase in the electrostatic force of attraction between the electrodes, and hence, a decrease in the gap separating them. In such a configuration, the maximum displacement of the top plate is a third of the gap at zero bias due to the electrostatic pull-in instability [4]. This corresponds to a theoretical maximum tuning range of only 50%. To obtain the required capacitance, four micromachined varactors were connected in parallel, resulting in a capacitance range of 2.11 to 2.46 pF (16% TR). Although the demonstrated tuning range was far lower than expected due to parasitic capacitances, the reported Q-factor of 62 at 1 GHz was much better than typical solid-state varactors. Figure 2.1 shows a scanning electron microscope (SEM) image of this varactor and its C-V characteristic.

**Figure 2.1:** UC Berkeley gap-tuned parallel-plate varactor: (a) SEM image; (b) *C-V* characteristic [18].

Subsequently, Dec and Suyama [52] at Columbia University implemented a gaptuned varactor using the Cronos/MEMSCAP MUMPs process [53]. With a polysilicon fixed electrode and a gold-coated polysilicon movable electrode, they achieved a TR of approximately 50% ( $C_1 = 2.05 \text{ pF}$ ). In order to extend the tuning range even further, a three-plate varactor design was also reported where a movable electrode is suspended equidistant between two fixed electrodes. By separately biasing the movable plate and either of the two fixed plates, the range of travel can be extended. A TR of 87% was demonstrated out of a theoretical maximum of 100%. However, due to the high resistivity of polysilicon relative to metals such as aluminium and gold, the measured Q-factors were low: 20 and 15 at 1 GHz for the two-plate and three-plate designs, respectively.

Figure 2.2: Columbia three-plate varactor: (a) SEM image; (b) schematic cross-section [52].

The need for suspensions of sufficient mechanical compliance also contributes to increasing device series resistance. Figure 2.2 shows an SEM image and a schematic of the Columbia three-plate varactor.

Recently, two new designs for three-plate varactors have been reported [54, 55]. Unlike the design in [52], these varactors were not designed for bi-directional actuation. Conversely, only one of the fixed electrodes is used for actuation while the other fixed electrode forms the RF varactor together with the movable plate. In addition, the zerovoltage varactor state corresponds to a minimum gap in the RF varactor. When actuated, the gap of the varactor increases, resulting in a decrease in capacitance. The three-plate varactor fabricated by Konishi et al. at Nikon Corporation demonstrated a TR of 1180% along with a relatively large  $C_{\text{max}}$  of 32 pF [54]. They were able to achieve such a large maximum capacitance by using the built-in stress of the movable plate to deform it towards the fixed electrode, achieving a small minimum gap. Electrode shorting is prevented by rigid stoppers that also define the initial gap size. Figure 2.3 shows the Nikon three plate varactor design. Leidich et al. [55] demonstrated a three-plate design with a high Q-factor (larger than 100 up to 2 GHz) although the TR was comparatively low at 167% ( $C_1 = 1.5$  pF).

**Figure 2.3:** Nikon three-plate varactor: (a) SEM image; (b) schematic cross-section; (c) *C*-*V* characteristic [54].

#### 2.2.1 Dual-Gap Varactors

To achieve an extended tuning range with parallel-plate, electrostatically-actuated varactors, Zou et al. [56, 57] from the University of Illinois at Urbana-Champaign (UIUC) implemented a varactor with a stepped profile in the movable plate. This allows the use of a different gap size for the actuation electrodes and the RF varactor (see Figure 2.4). By designing the gap of the actuation electrode to be more than three

times the gap of the RF varactor, the travel range of the varactor is no longer limited by the pull-in instability.

Figure 2.4: UIUC dual-gap varactor (a) SEM image; (b) schematic cross-section [57].

However, tuning will still be limited by the lack of perfect planarity (e.g. due to stressinduced warpage) and excessive surface roughness in the electrodes. The need to maintain insulation between the varactor electrodes also imply that in practice a dielectric layer must be present (or a sufficient air gap must be maintained). A TR of 70% and a Q-factor of 30 at 5 GHz was reported for the UIUC dual-gap varactor.

A variety of other dual-gap varactors have been reported [58-65]. These varactors, implemented using both non-standard and commercial foundry processes, have achieved tuning ranges of up to 520% [64]. Varactors with high *Q*-factors that are suitable for application at Ka-band (26 to 40 GHz) operation have also been demonstrated [59, 61, 64].

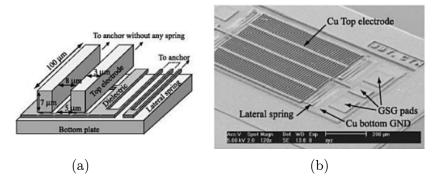

#### 2.2.2 Interdigital Gap-Tuned Varactors

Several researchers have reported gap-tuned varactor designs where the RF capacitor consists of interdigitated comb structures [66-68]. The gap between these comb fingers is varied using electrostatic actuation. Unlike the previous designs where the electrode motion is out-of-plane, these comb structures have in-plane actuation.

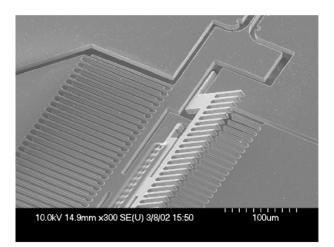

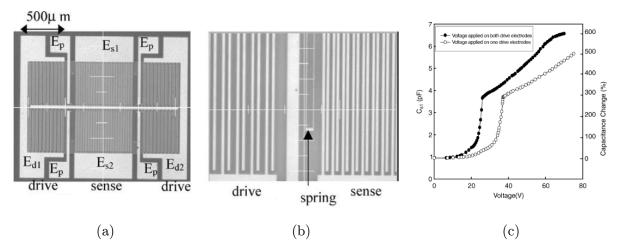

Xiao et al. from the New Jersey Institute of Technology (NJIT) reported gap-tuned interdigital varactors fabricated using a deep reactive ion etching (DRIE) process [66]. The silicon varactor electrodes are capped with aluminium for lower series resistance. A TR of 595% (0.945 to 6.57 pF) was demonstrated although the Q-factor was only 100 at 1 MHz. The authors attributed the low Q-factor to the lossy silicon substrate. It is also possible that the series inductance of the device is very high due to the suspension design, limiting the use of this varactor at low frequencies. Figure 2.5 shows an image of one of the NJIT varactors and its C-V characteristic.

Figure 2.5: NJIT interdigital varactor: (a) microscope image; (b) close-up view of drive and sense electrodes; (c) C-V characteristic [66].

Subsequently, Monajemi and Ayazi from Georgia Institute of Technology reported a gap-tuned interdigital varactor suitable for applications at higher frequency (1 GHz) [67]. The varactors were implemented using high aspect-ratio combined poly- and single-crystal silicon (HARPSS) technology. Using low-inductance suspensions and an additional gold layer above the silicon comb fingers, a Q-factor of 49 at 1 GHz was obtained for a  $C_1$  value of 2.5 pF. The reported TR of 100% was modest but on the other hand, the actuation voltage required was only 2 V. A different interdigital varactor with high aspect-ratio, electroplated silver electrodes was reported by Rais-Zadeh and Ayazi [68]. In this design, a high Q-factor greater than 200 at 1 GHz was obtained through the use of highly-conductive silver electrodes and a low-loss polymer substrate. The device was fabricated on a silicon substrate coated with a 20 µm thick Avatrel polymer (based on polynorbornene, see [69]) and the backside silicon beneath the varactor was removed to reduce substrate loss. This varactor can be tuned for capacitances between 0.68 to 1.56 pF (129% TR). Figure 2.6 shows SEM images of the Georgia Tech varactors.

The main advantage of interdigital varactors is that the shape of the varactor comb structure can be lithographically defined in one mask step. Hence, the fabrication process of such varactors is considerably straightforward relative to parallel-plate designs.

Figure 2.6: Georgia Tech interdigital varactors: (a) HARPSS varactor [67]; (b) high aspectratio silver varactor [68].

#### 2.2.3 Varactors with Piezoelectric Actuation

As an alternative to electrostatic actuation, parallel-plate varactors with piezoelectric actuation have been proposed by various research groups [70-73]. The advantages of using piezoelectric actuators include a larger stable displacement range, low voltage operation (less than 10 V), bi-directionality and the absence of dielectric charging effects.

Figure 2.7: LG Electronics piezoelectric varactor: (a) SEM image of movable plate and actuators; (b) plot of  $C_r$  versus voltage and device schematic [70] (figures reproduced from [48]).

Park et al. from LG Electronics demonstrated the first varactors employing piezoelectric actuators in 2001 [70]. Each unimorph actuator consists of a 380 nm thick layer of PZT sandwiched between platinum and ruthenium oxide electrodes. The varactor achieved a TR of 210% (around 0.1 to 0.3 pF) at a low actuation voltage of

6 V. A Q-factor of 210 at 1 GHz was reported. Due to the high processing temperatures (up to 650 °C) required to anneal the PZT, the actuators and movable plate of the device were first fabricated on a silicon substrate and then flip-chip bonded onto the final device substrate. The silicon substrate was then removed in the device region via backside etching. Figure 2.7 shows the LG Electronics varactor design and its tuning characteristics.

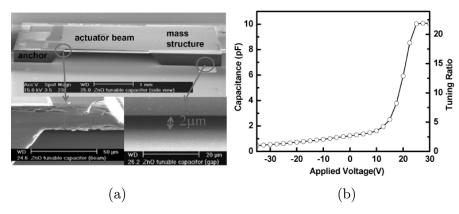

To improve compatibility with standard microelectronic fabrication, Lee and Kim from the University of Southern California (USC) implemented a varactor with zinc oxide (ZnO) actuators [71]. The device was fabricated on silicon using a combination of surface and bulk micromachining and then transferred onto a glass substrate. The actuator has a unimorph design, consisting of a 350 nm thick layer of ZnO sandwiched between aluminium electrodes. As the maximum process temperature was 300 °C, it is more compatible with standard IC fabrication technology. A very large TR of 2000% (0.46 to 10.02 pF) was achieved through the use of bi-directional actuation. However, the maximum actuation voltage of 35 V was high for a piezoelectric varactor (see Figure 2.8). This could be due to the lower piezoelectric constant of ZnO (relative to PZT) as well as excessive stiffness in the varactor beam. The measured *Q*-factor of the device was around 10 at 2 GHz which is comparatively low.

Figure 2.8: USC piezoelectric varactor: (a) SEM image; (b) C-V characteristic [71].

A third varactor with piezoelectric actuation has been reported by Kawakubo et al. from Toshiba Corporation [73]. This varactor uses actuators with a bimorph design, where there are two layers of aluminium nitride each sandwiched between aluminium electrodes. By applying an opposite electric field to the two layers, one layer contracts while the other expands resulting in vertical displacement. A very low actuation voltage of 3 V was used and a TR of 100% was reported (10 to 20 fF). Although varactors with TR values greater than 900% were reported by the same authors [72], this was due to the movable varactor plate coming into contact with the silicon nitride insulation over the fixed electrode, resulting in a large jump in capacitance. Like the USC varactor, this device was also designed to be CMOS compatible.

Figure 2.9: Toshiba piezoelectric varactor: (a) optical image; (b) C-V characteristic [73].

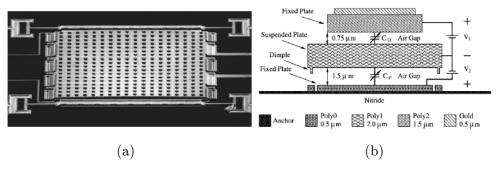

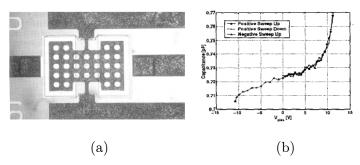

### 2.2.4 Gap-Tuned Varactors with Thermal Actuation

Apart from using electrostatic and piezoelectric actuation, parallel-plate varactors with thermal actuation have also been demonstrated. Thermal actuators translate differential expansion of *hot* and *cold* arms into vertical motion in the movable plate of a varactor, changing the gap and hence capacitance. Harsh et al. from the University of Colorado at Boulder (CU Boulder) reported a flip-chip integrated MEMS varactor that is tuned using polysilicon thermal actuators [74, 75]. The actuators and the movable plate were fabricated using the commercial MUMPs process and subsequently transferred onto a ceramic substrate. A large TR of 600% (0.5 to 3.5 pF) was demonstrated along with a measured Q-factor of 100 at 10 GHz.

Figure 2.10: CU Boulder thermally-actuated varactor: (a) optical image; (b) C-V characteristic [75].

However, thermal actuators consume much more power relative to electrostatic or piezoelectric actuators due to the current that is required to heat up the actuator arms. In addition, thermal actuators have longer response times relative to electrostatic actuators and hence tuning speeds are correspondingly lower. An optical image of the CU Boulder varactor and its tuning characteristics is shown in Figure 2.10. A summary of gap-tuned varactors is given in

Table 2.1 of Section 2.7. Some varactors that were not explicitly reviewed have also been included here for the purpose of comparison [76-78].

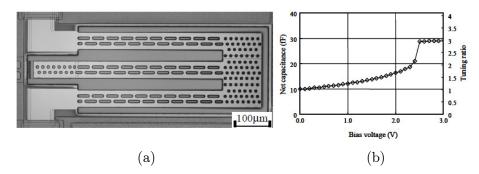

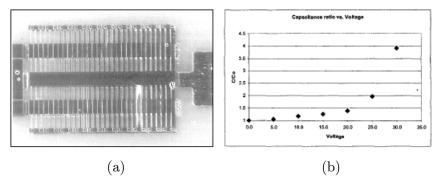

## 2.3 Area-Tuned Varactors

The second method of tuning MEMS varactors is by actuating a change in the overlap area between the varactor electrodes. Larson et al. from Hughes Research Laboratories presented a conceptual micromachined area-tuned varactor in 1991 [14]. Using interdigital electrodes, a change in capacitance was demonstrated by manually moving the electrodes to vary the overlap area. Subsequently, Yao et al. from the Rockwell Science Center (RSC) reported the first area-tuned MEMS varactors [51, 79]. These varactors feature a suspended array of interdigitated comb fingers that is mechanically linked to a comb-drive actuator. The actuator varies the amount of overlap area in the interdigital varactor when biased. Several designs were fabricated with tuning ranges of around 100 to 200% and maximum actuation voltages as low as 5 V. The interdigitated comb-finger array was formed in deep-etched silicon and subsequently covered with an aluminium thin-film to reduce device series resistance. A Q-factor of 34 at 500 MHz was measured in a 5.19 pF device. Figure 2.11 shows the same varactor in different stages of tuning and its corresponding C-V characteristic.

One of the main advantages of the RSC varactors is the ease of fabrication: like the interdigital gap-tuned designs, only one or two masks are required. In addition, the actuators are isolated from the variable capacitor and hence do not affect the RF performance. The device capacitance values are also easily scalable and can be designed to either decrease or increase with actuator bias voltage. In a subsequent design, the RSC group reported another interdigital area-tuned varactor with a TR of 740% and a Q-factor greater than 100 (at 500 MHz) [80, 81]. The capacitance of this device varied from 1.4 to 11.9 pF with a maximum bias of 8 V.

**Figure 2.11:** RSC area-tuned interdigital varactor: (a) optical images showing change in finger overlap area with bias voltage; (b) *C-V* characteristic [51].

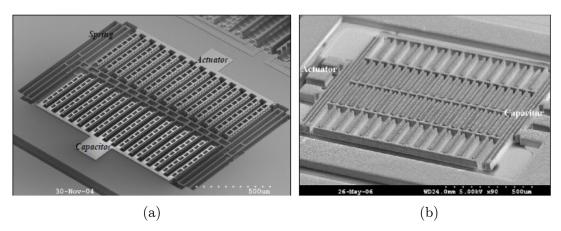

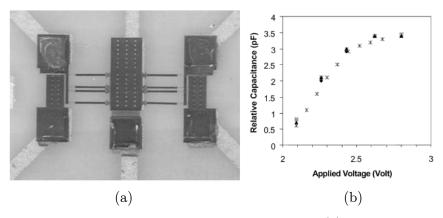

### 2.3.1 Rotational Varactors

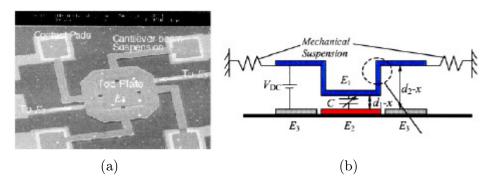

Interdigital area-tuned varactors with lateral actuation share the same disadvantage as the interdigital gap-tuned varactors, i.e. they tend to have a larger device footprint. In order to obtain a large tuning range while keeping the device compact, Nguyen et al. from the University of California at Los Angeles (UCLA) implemented an area-tuned interdigital varactor with electrodes that rotate out-of-plane [19, 37]. The device consists of actuator and RF comb fingers connected via benzocyclobutene (BCB) hinges (see Figure 2.12). A surface tension self-assembly technique using BCB reflow creates an initial offset angle in the driving electrode, while the RF electrode has maximum overlap area at zero bias. When the driving electrode is actuated, the RF electrode rotates upwards, leading to a decrease in capacitance.

**Figure 2.12:** UCLA interdigital rotational varactor: (a) device schematic; (b) SEM image of drive and sense electrodes; (c) *C-V* characteristics of devices with different finger lengths [19].

A very large TR of 3085% (0.27 to 8.6 pF) was reported with a maximum actuation voltage of 50 V. By coating the silicon comb fingers with aluminium, a high Q-factor of 273 at 1 GHz was measured.

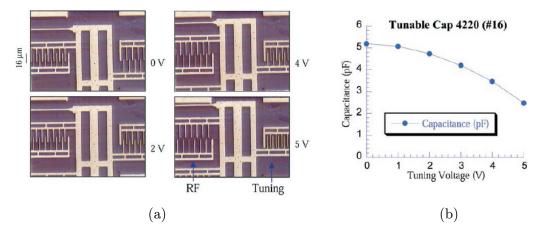

Recently, Gu and Li from the Shanghai Institute of Microsystem and Information Technology (SIMIT) reported an interdigital varactor with in-plane rotational actuation (see Figure 2.13) [82]. By designing the stiffness of the varactor in the radial direction to be much greater than the stiffness in the tangential direction, a key advantage of this design is its insensitivity to low frequency vibration. Although its sensitivity to vibration-induced noise has not been measured, simulated acceleration loads suggest that this design could be useful for reducing mechanical noise when implemented into a tunable circuit. The device is fabricated using a post-CMOS process and the comb electrodes are made of nickel and gold (10  $\mu$ m and 200 nm respectively). A *TR* of 108% (0.13 to 0.27 pF) was measured for actuation voltages up to 12 V. The measured *Q*-factor is 51.3 at 1 GHz due to high parasitic inductance in the folded-beam suspension.

Figure 2.13: SIMIT rotational varactor: (a) SEM image; (b) C-V characteristic [82].

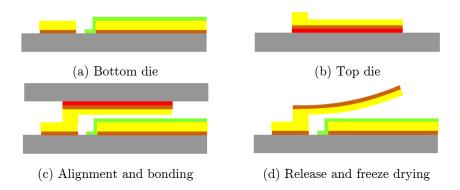

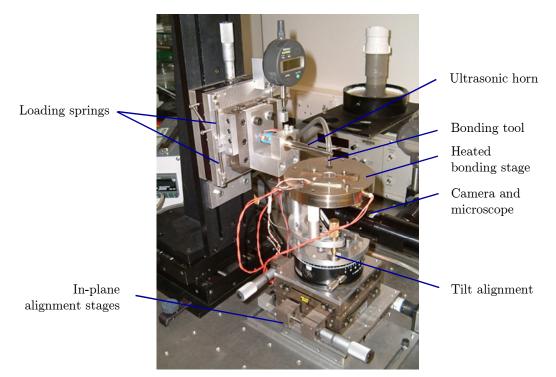

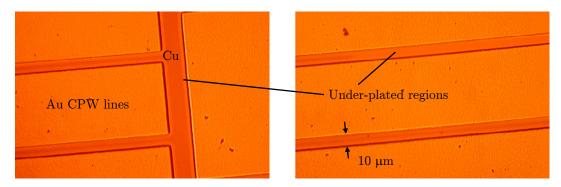

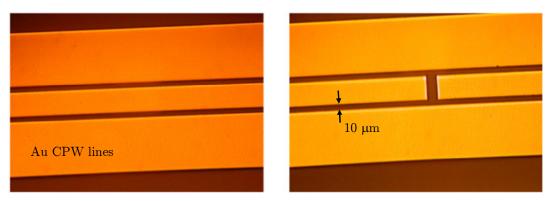

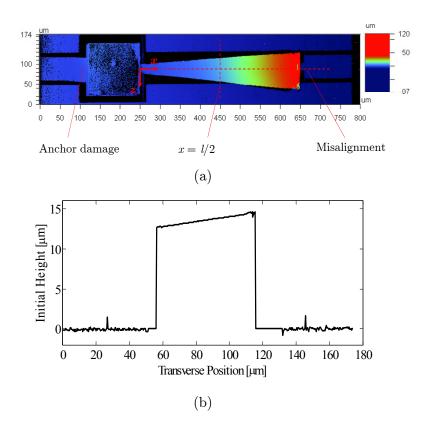

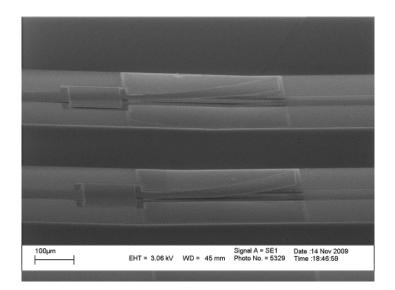

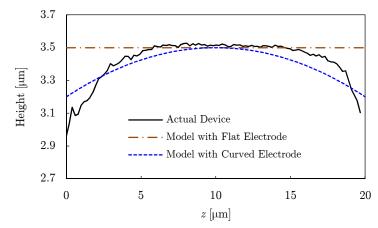

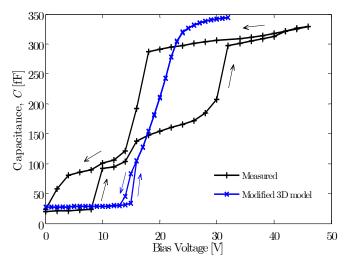

Another rotational varactor design has been proposed by Mehdaoui et al. from the Swiss Federal Institute of Technology at Lausanne (EPFL) [83]. Instead of interdigitated comb fingers, the movable and fixed electrodes consist of segmented regions that form an overlap area. Thermal actuators were used create an angular rotation, changing the capacitance area. Due to the mechanical design of the actuators, the TR was limited to only 30% as buckling occurred during testing. A similar varactor design was first proposed in [84] but no experimental results were reported in that paper. Figure 2.14 shows the thermally actuated rotational varactor in different stages of actuation.