# SCALABLE EVENT-DRIVEN MODELLING ARCHITECTURES FOR NEUROMIMETIC HARDWARE

A THESIS SUBMITTED TO THE UNIVERSITY OF MANCHESTER FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

2011

By Alexander D. Rast School of Computer Science

# Contents

| $\mathbf{A}$ | Abstract 8 |         |                                              |    |

|--------------|------------|---------|----------------------------------------------|----|

| $\mathbf{D}$ | eclar      | ation   |                                              | 9  |

| C            | opyri      | ight    |                                              | 10 |

| $\mathbf{A}$ | ckno       | wledge  | ements                                       | 12 |

| 1            | Intr       | roduct  | ion                                          | 13 |

|              | 1.1        | Appro   | opriate Neural Development Systems           | 14 |

|              |            | 1.1.1   | Effective Tools for Model Exploration        | 15 |

|              |            | 1.1.2   | Effective Tools for Hardware Implementation  | 16 |

|              | 1.2        | The In  | ntegral Role of the Development System       | 16 |

|              |            | 1.2.1   | The Debate Over the Biological Model         | 16 |

|              |            | 1.2.2   | The Search for the Computational Model       | 18 |

|              |            | 1.2.3   | The Limitations of the Simulation Model      | 19 |

|              | 1.3        | Contr   | ibutions                                     | 20 |

|              |            | 1.3.1   | Achievements                                 | 20 |

|              |            | 1.3.2   | Outline                                      | 22 |

|              |            | 1.3.3   | Significance                                 | 24 |

| 2            | Net        | ıral Ne | etwork Architecture Trends                   | 28 |

|              | 2.1        | Conte   | xt                                           | 29 |

|              | 2.2        | Archit  | tectures: Hardwired, FPGA, Neuromorphic      | 30 |

|              |            | 2.2.1   | Hardwired Architectures                      | 31 |

|              |            | 2.2.2   | Reconfigurable Architectures                 | 32 |

|              |            | 2.2.3   | Neuromorphic Architectures                   | 34 |

|              | 2.3        | Applie  | cations: Computational, Biological, Embedded | 36 |

|   |     | 2.3.1   | Computing Applications of Neural Hardware      |

|---|-----|---------|------------------------------------------------|

|   |     | 2.3.2   | Hardware for Biological Simulation             |

|   |     | 2.3.3   | Embedded Neural Systems                        |

|   | 2.4 | Chips:  | Digital, Analogue, Mixed-Signal 41             |

|   |     | 2.4.1   | Digital                                        |

|   |     | 2.4.2   | Analogue                                       |

|   |     | 2.4.3   | Mixed-Signal                                   |

|   | 2.5 | The St  | ate of the Art: A Summary                      |

|   |     | 2.5.1   | Chips                                          |

| 3 | A U | Jnivers | al Neural Network Chip 48                      |

|   | 3.1 | Overvi  | ew                                             |

|   | 3.2 | The No  | euromimetic Architecture                       |

|   |     | 3.2.1   | Native Parallelism                             |

|   |     | 3.2.2   | Event-Driven Processing                        |

|   |     | 3.2.3   | Incoherent Memory                              |

|   |     | 3.2.4   | Incremental Reconfiguration                    |

|   | 3.3 | Hardw   | are Abstraction of Time and Space              |

|   |     | 3.3.1   | Topological Abstraction                        |

|   |     | 3.3.2   | Process Abstraction                            |

|   |     | 3.3.3   | Temporal Abstraction                           |

|   | 3.4 | SpiNN   | aker: A Universal Neuromimetic Chip            |

|   |     | 3.4.1   | The SpiNNaker local processor node             |

|   |     | 3.4.2   | SpiNNaker global resources 61                  |

|   |     | 3.4.3   | Nondeterministic process dynamics 65           |

|   | 3.5 | Summa   | ary of the SpiNNaker Architecture              |

| 4 | The | Libraı  | ry Architecture and Tools 67                   |

|   | 4.1 | Roadn   | nap                                            |

|   | 4.2 | An Ev   | ent-Driven Neuromimetic Configuration Chain 69 |

|   |     | 4.2.1   | System Components                              |

|   |     | 4.2.2   | Modelling Components                           |

|   |     | 4.2.3   | User Components                                |

|   | 4.3 | Event-  | Driven Model Requirements                      |

|   |     | 4.3.1   | Design Abstraction                             |

|   |     | 4.3.2   | Design Automation                              |

|   |     | 4.3.3    | Verification and Evaluation             |

|---|-----|----------|-----------------------------------------|

|   | 4.4 | Design   | Decisions                               |

|   |     | 4.4.1    | Existing Design and Simulation Software |

|   |     | 4.4.2    | The Limits of Reuse                     |

|   |     | 4.4.3    | The Neural Function Pipeline 81         |

|   |     | 4.4.4    | 3-level system                          |

|   | 4.5 | Summ     | ary of the Development Architecture     |

| 5 | Pha | se I: D  | Definition - Test Networks 89           |

|   | 5.1 | Outlin   | e 90                                    |

|   | 5.2 | The Iz   | hikevich/STDP Model                     |

|   |     | 5.2.1    | Neuron                                  |

|   |     | 5.2.2    | Synapse                                 |

|   |     | 5.2.3    | Networks                                |

|   | 5.3 | The M    | ILP Model                               |

|   |     | 5.3.1    | Neuron                                  |

|   |     | 5.3.2    | Synapse                                 |

|   |     | 5.3.3    | Dynamics                                |

|   |     | 5.3.4    | MLP event definition                    |

|   |     | 5.3.5    | Network                                 |

|   | 5.4 | The L    | IF/NMDA Model                           |

|   |     | 5.4.1    | Neuron                                  |

|   |     | 5.4.2    | Synapse                                 |

|   |     | 5.4.3    | Network                                 |

|   | 5.5 | Neural   | Model Summary                           |

| 6 | Pha | se II: S | Simulation - Modelling 127              |

|   | 6.1 | Guide    |                                         |

|   | 6.2 | Izhikev  | vich/STDP Issues                        |

|   |     | 6.2.1    | Voltage-Domain Performance              |

|   |     | 6.2.2    | Time-Domain Performance                 |

|   | 6.3 | MLP 7    | Test Issues                             |

|   |     | 6.3.1    | Model Exploration                       |

|   |     | 6.3.2    | Hardware Functionality                  |

|   | 6.4 | LIF/N    | MDA Issues                              |

|   |     | 6.4.1    | Single Neuron Dynamics                  |

|    |                 | 6.4.2 Neural Subcircuits                           | 137         |  |  |

|----|-----------------|----------------------------------------------------|-------------|--|--|

|    | 6.5             | Summary                                            | 139         |  |  |

| 7  | Pha             | se III: Execution - Hardware Testing               | L <b>41</b> |  |  |

|    | 7.1             | Plan                                               | 142         |  |  |

|    | 7.2             | The Izhikevich Model in Hardware                   | 143         |  |  |

|    |                 | 7.2.1 Comparison with Brian                        | 143         |  |  |

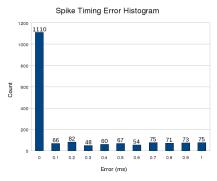

|    |                 | 7.2.2 Real time simulation of a 500 neuron network | 143         |  |  |

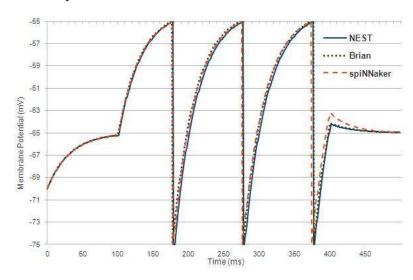

|    | 7.3             | The LIF Model in Hardware                          | 146         |  |  |

|    |                 | 7.3.1 Single neuron testing                        | 146         |  |  |

|    |                 | 7.3.2 Network tests                                | 146         |  |  |

|    | 7.4             | Heterogeneous On-Chip Modelling                    | 148         |  |  |

|    |                 | 7.4.1 Mixed LIF/Izhikevich model networks          | 148         |  |  |

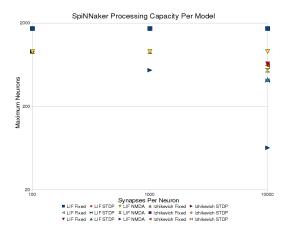

|    |                 | 7.4.2 Hardware scalability                         | 150         |  |  |

|    | 7.5             | Summary                                            | 151         |  |  |

| 8  | Implications 15 |                                                    |             |  |  |

|    | 8.1             | Agenda                                             | 154         |  |  |

|    | 8.2             |                                                    | 155         |  |  |

|    |                 |                                                    | 156         |  |  |

|    |                 | 8.2.2 Abstract Space                               | 158         |  |  |

|    |                 | 8.2.3 Abstract Time                                | 161         |  |  |

|    | 8.3             | Scaling to Very Large Systems                      | 163         |  |  |

|    |                 | 8.3.1 Hardware Scaling Challenges                  | 163         |  |  |

|    |                 | 8.3.2 Neural Model Scaling Challenges              | 164         |  |  |

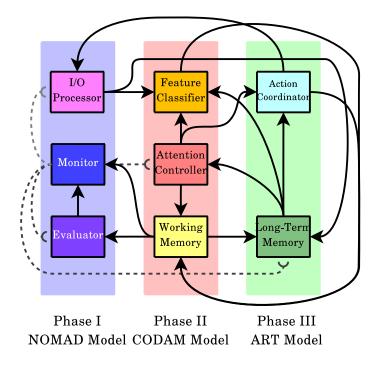

|    | 8.4             | Computational Cognitive Neuroscience               | 167         |  |  |

|    | 8.5             | Summary                                            | 170         |  |  |

| 9  | Cor             | aclusions 1                                        | L <b>73</b> |  |  |

|    | 9.1             | Now                                                | 177         |  |  |

|    | 9.2             |                                                    | 180         |  |  |

|    | 9.3             | •                                                  | 181         |  |  |

| Bi | ibliog          | graphy 1                                           | 185         |  |  |

Word Count: 62848

# List of Figures

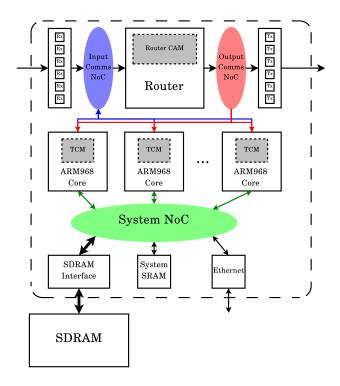

| 3.1  | SpiNNaker Architecture                                       |

|------|--------------------------------------------------------------|

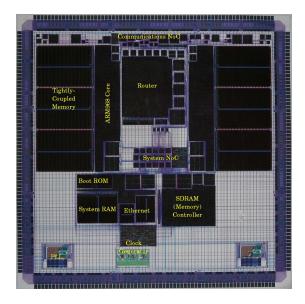

| 3.2  | SpiNNaker test chip                                          |

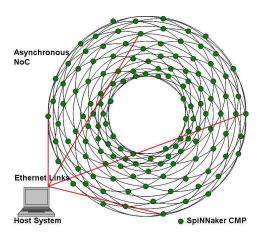

| 3.3  | Multichip SpiNNaker CMP System                               |

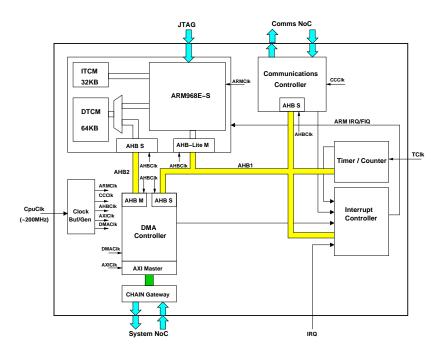

| 3.4  | Processor node block diagram                                 |

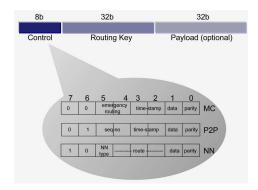

| 3.5  | SpiNNaker AER packet format                                  |

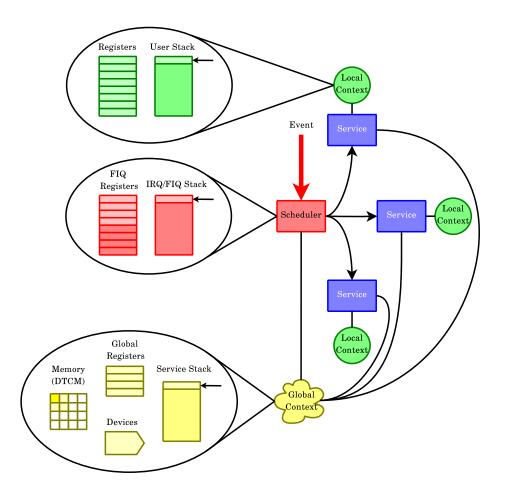

| 4.1  | SpiNNaker event-driven software model                        |

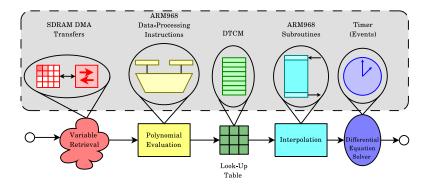

| 4.2  | A function pipeline for neural networks                      |

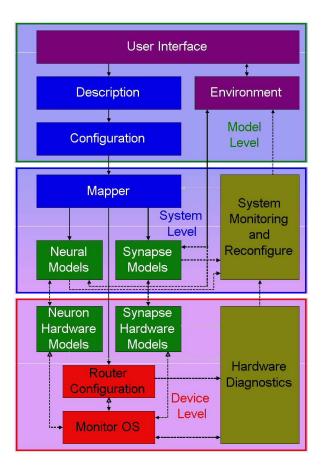

| 4.3  | SpiNNaker system tool flow                                   |

| 5.1  | SpiNNaker Neuron Binned Input Array                          |

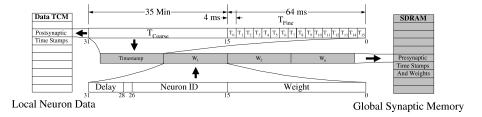

| 5.2  | Synapse Data Format                                          |

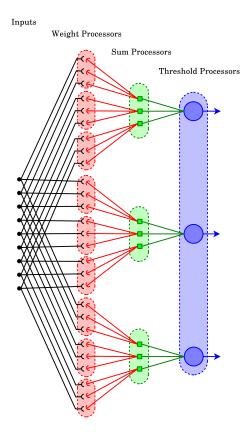

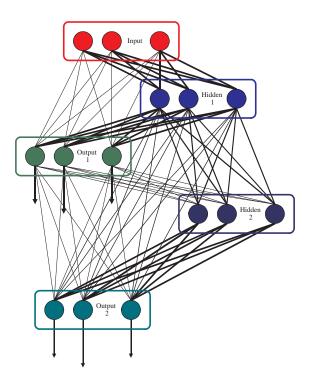

| 5.3  | SpiNNaker MLP mapping                                        |

| 5.4  | SpiNNaker MLP data representations                           |

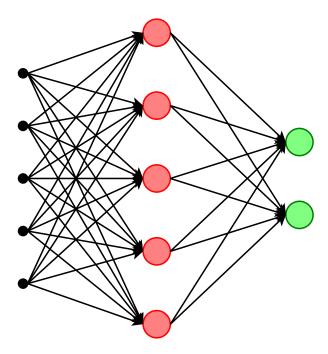

| 5.5  | Typical MLP network                                          |

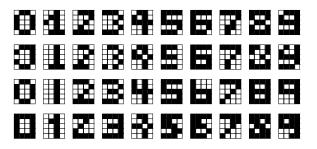

| 5.6  | Test inputs used with MLP networks                           |

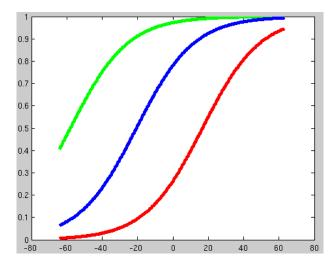

| 5.7  | Large phonetic network used in tests                         |

| 5.8  | NMDA gating factor                                           |

| 5.9  | Proposed full-scale model                                    |

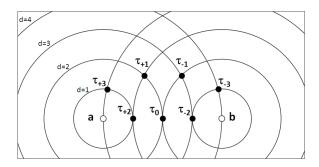

| 5.10 | Interpulse interval detection                                |

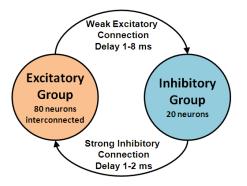

| 5.11 | Oscillatory Network Structure                                |

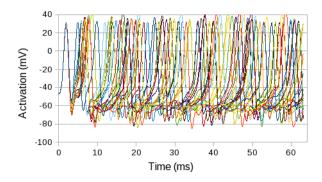

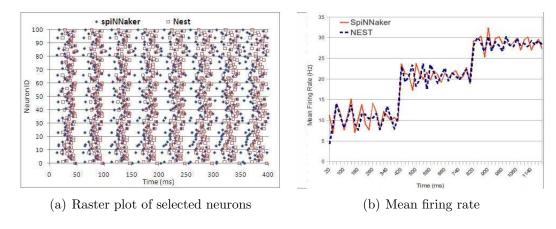

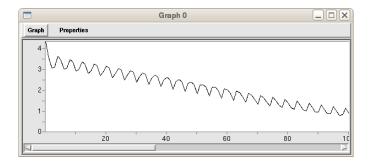

| 6.1  | SpiNNaker top-level output of the spiking network            |

| 6.2  | SpiNNaker time-domain behaviour                              |

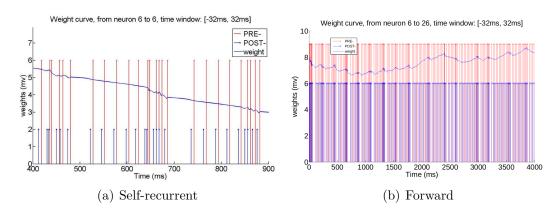

| 6.3  | STDP updates, self-recurrent and forward connections 131     |

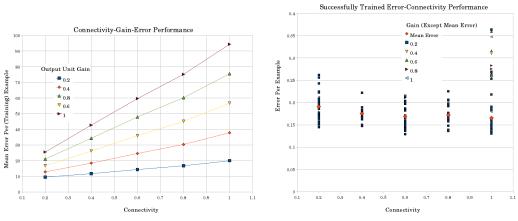

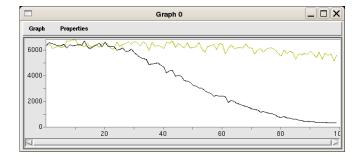

| 6.4  | Performance of the hand-digits application                   |

| 6.5  | Error-Connectivity results, phonetic recognition network 134 |

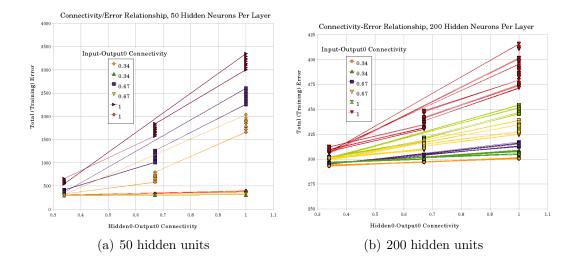

| 6.6  | SpiNNaker MLP test, weight changes                           |

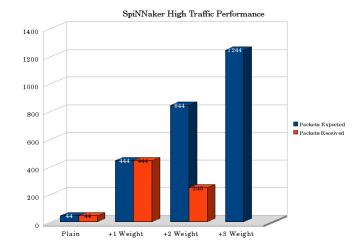

| 6.7  | SpiNNaker packet handling performance                        |

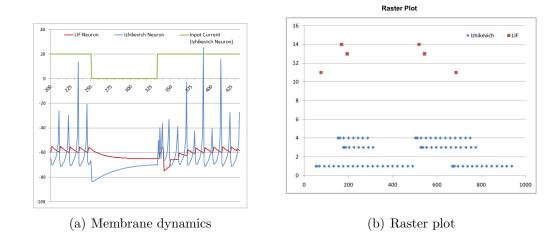

| 6.8  | Single (LIF) neuron dynamics                                     |

|------|------------------------------------------------------------------|

| 6.9  | Spike Propagation                                                |

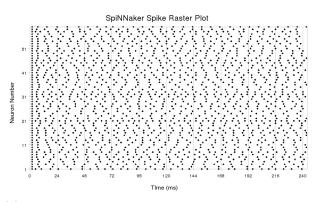

| 6.10 | Oscillatory Network Raster Plot                                  |

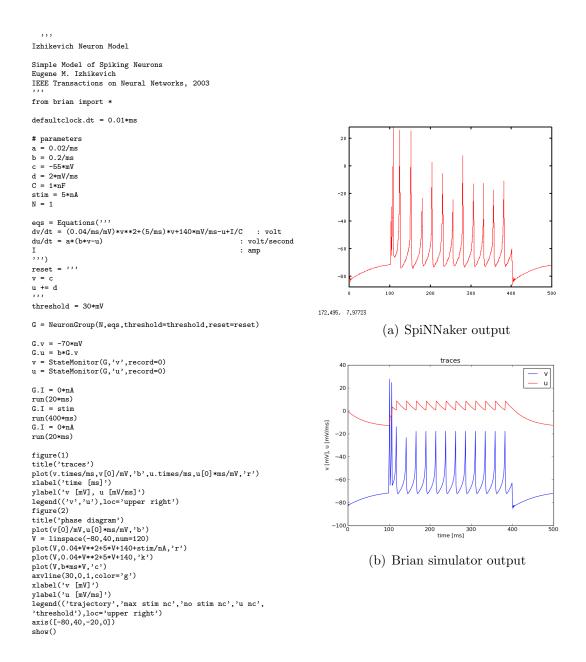

| 7.1  | Izhikevich network: script and output                            |

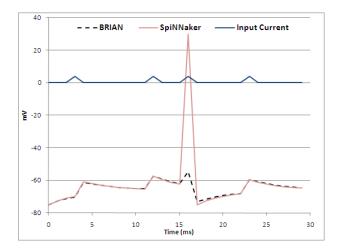

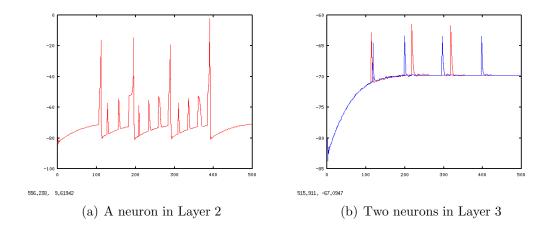

| 7.2  | Izhikevich model: Membrane potentials                            |

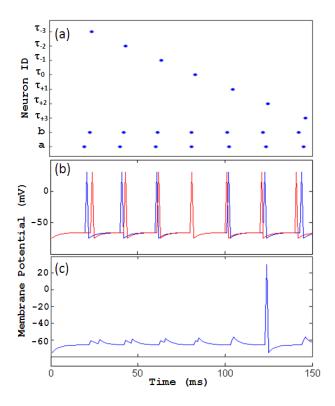

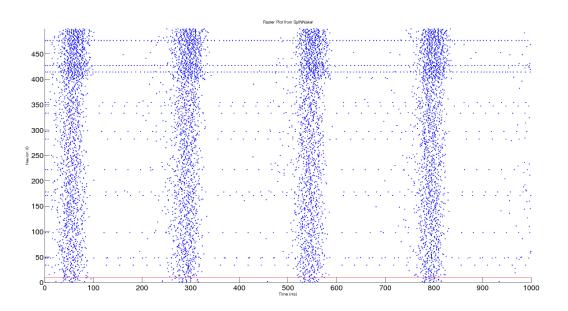

| 7.3  | Raster plot for the 500 neuron Izhikevich model simulation $145$ |

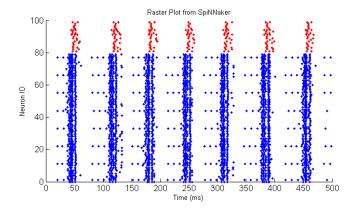

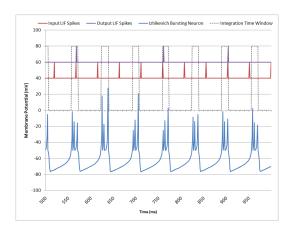

| 7.4  | SpiNNaker LIF membrane potential                                 |

| 7.5  | 500-neuron LIF population                                        |

| 7.6  | Dynamics of the first (heterogeneous) network                    |

| 7.7  | Second test network dynamics                                     |

| 7.8  | Number of Neurons Per SpiNNaker Processor                        |

| 8.1  | Digits early training error                                      |

| 8.2  | Settling time during early training                              |

| 8.3  | Error propagation                                                |

#### Abstract

The University of Manchester

Alexander Rast

For the degree of Doctor of Philosophy

Scalable Event-Driven Modelling Architectures for Neuromimetic Hardware

26 January, 2011

Neural networks present a fundamentally different model of computation from the conventional sequential digital model. Dedicated hardware may thus be more suitable for executing them. Given that there is no clear consensus on the model of computation in the brain, model flexibility is at least as important a characteristic of neural hardware as is performance acceleration. The SpiNNaker chip is an example of the emerging "neuromimetic" architecture, a universal platform that specialises the hardware for neural networks but allows flexibility in model choice. It integrates four key attributes: native parallelism, event-driven processing, incoherent memory and incremental reconfiguration, in a system combining an array of general-purpose processors with a configurable asynchronous interconnect.

Making such a device usable in practice requires an environment for instantiating neural models on the chip that allows the user to focus on model characteristics rather than on hardware details. The central part of this system is a library of predesigned, "drop-in" event-driven neural components that specify their specific implementation on SpiNNaker. Three exemplar models: two spiking networks and a multilayer perceptron network, illustrate techniques that provide a basis for the library and demonstrate a reference methodology that can be extended to support third-party library components not only on SpiNNaker but on any configurable neuromimetic platform. Experiments demonstrate the capability of the library model to implement efficient on-chip neural networks, but also reveal important hardware limitations, particularly with respect to communications, that require careful design.

The ultimate goal is the creation of a library-based development system that allows neural modellers to work in the high-level environment of their choice, using an automated tool chain to create the appropriate SpiNNaker instantiation. Such a system would enable the use of the hardware to explore abstractions of biological neurodynamics that underpin a functional model of neural computation.

### Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts, and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see

- http://www.campus.manchester.ac.uk/medialibrary/policies/intellectual-property.pdf), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see

http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

### Acknowledgements

This work could not have been carried out without the support of the EPSRC and ARM. I would like to thank Steve Furber for his insightful advice and brilliant suggestions - particularly in bringing to light the *principles* behind neural design. I would also like to thank Stephen Welbourne and Francesco Galluppi for their tireless efforts in model experimentation and the inspiration they brought from the psychological community. Two collaborators, Sergio Davies and Mukaram Khan, assisted repeatedly with low-level debugging and technical issues; without their help the models I built might never have worked in practice. Luis Plana gave critical debugging support at critical times - with a level of professionalism and skill I stand in awe of. David Lester made sure that my ideas remained grounded in reality - along with offering not a few good ideas of his own! All the members of the SpiNNaker team provided encouragement and assistance along the way and demonstrate to the full the value of a collaborative effort. Finally, I give special thanks to Viv Woods who assisted countless times in practical matters and in navigating the complexities of "the system" - without whose help I might well have ended marooned in Hong Kong, Italy, or other points around the world, to say nothing of within the University!

# Chapter 1

# Introduction

#### 1.1 Appropriate Neural Development Systems

Neural networks offer a different model of computation from conventional sequential digital computers, and one that achieves in biology what (thus far) technology has been unable to do: *intelligence*: the ability to compute unprompted and produce meaningful output. If there is a sense that figuring out the neural model of computation would make it possible to realise computational intelligence, as well as better understand how the brain works, there is also a recognition that neural science is at least as far away from being able to give a definitive answer to this as computer science is from creating an artificial intelligence. Vexing problems of model scaling and parameter proliferation make it difficult to decide what parts of the neural model of computation are critical, and formal models of structure and dynamics tend to exist only for narrow subdomains of neurocomputing. The easiest approach appears to be to come at the problem from the reverse direction: instead of trying to understand biological observations and use them to construct computers, build computational models and see what they can tell us about the biology.

The basic purpose of computational neural networks in this approach is to answer the question: what does neural computation do?. For many years, researchers have attempted to address this question using conventional computers. Yet given that neural networks present an emphatically different model of computation from the sequential digital model it is unclear whether running neural networks on industry-standard computer architectures represents a good, much less an optimum, implementation strategy. With further progress on understanding neural computing also appearing to depend on radical model scaling [IE08] dedicated neural hardware also looks more and more like a prerequisite [JL07], if only for the purposes of model acceleration. If in the past, however, the purpose of neural hardware was obvious: model acceleration; the nature of the research question for new chips has changed. Now it is not simply a matter of how to scale a neural model to large sizes but what model to scale.

The question of which neural network models are the "right" ones depends rather critically on what the purpose of the model is. A "one-size-fits-all" hardware neural model is thus unrealistic and somewhat irrelevant. Different research groups, with different goals, may want to use neural hardware in different ways, and it is unrealistic to expect them to have, or acquire, the low-level hardware familiarity necessary to develop efficient models for such chips. All of these considerations form part of the background for the subject of this work: development systems for neural hardware, a problem largely overlooked to date in neural research.

Current neural systems suffer from an accessibility gap: fixed hardware and nonstandard software tools make it difficult for a potential user to model anything beyond simple applications. But adapting industry-standard tools and hardware is usually not an option because in them the synchronous digital model of computation tends to be an assumption taken as a given. Effectively, the neural model design and development stages become the exclusive domain of system specialists. The neural systems accessibility gap is, in essence, a symptom of an architectural gap. An important and biologically relevant alternative exists: event-driven computing, using inputs themselves to drive updates rather than an independent clock. For event-driven neural computation to be a viable architecture, however, it must overcome the accessibility gap. To bridge that gap, this work develops tools, methodologies, and libraries for general-purpose event-driven neural systems that a modeller can use to implement an arbitrary model.

#### 1.1.1 Effective Tools for Model Exploration

At the level of the neural model, two important considerations emerge that an architecture for neural modelling libraries must address: universality - the ability to describe and run any model, and abstraction - the ability to describe a model independently of hardware or biological detail. Lack of clear consensus on what constitutes an adequate neural model has led to a tremendous diversity of different models, their characteristics determined as much by research priorities as by agreement with observation. On the one hand, this places a high value on neural development systems that can support any model - so that it provides the maximum scope for model exploration. On the other, it emphasizes the need for abstraction - so that it is possible to compare different neural models at a high level. Yet in practice existing neural hardware has tended to support only a small model subset, with correspondingly specialised development tools, and thus the concept of universal modelling libraries for hardware has been largely overlooked. With a new class of neural hardware emerging, however, that supports a wide variety of models on a dedicated, yet flexible hardware platform, this study reexamines the architecture of neural modelling systems, to create a system that can

meet the needs of universality and abstraction on specialised neural hardware.

#### 1.1.2 Effective Tools for Hardware Implementation

The existence of universal neural hardware has begun to address a need for systems for large-scale neural model exploration - but is only half of the system. To be effective such chips need to be part of an integrated system architecture, with hardware and tools designed together for universal neural modelling [Rey03]. In particular, a bare chip needs a development system that can specify and configure what neural model the chip runs. To be useful to the end user, this system should provide enough hardware abstraction that the modeller can describe and run the neural network entirely at the level of the model, without having to consider the hardware specifications. At the same time it must make optimal use of hardware resources, or it becomes questionable whether the system as a whole is a dedicated neural modelling platform. In emerging neural hardware the event-driven computing model is rapidly becoming an architectural standard. The event-driven model provides a useful generalised framework for abstraction, both from the point of view of isolating hardware details from the modeller and from the point of view of decoupling neural models from biophysical dependencies. To use this model in the configuration tool chain requires a method for recasting existing functional models into an event-driven format. This study considers an "ideal" architecture for the neural hardware development environment under consideration, taking the form of an event-driven system with a clearly-defined abstract computing model and a method to convert an arbitrary neural network to this model.

# 1.2 The Integral Role of the Development System

#### 1.2.1 The Debate Over the Biological Model

While biological investigations have revealed much, particularly recently, about low-level neural processes, there is as yet scanty information and little consensus on higher-level neural function and how it produces behaviour [MSK98]. The

result has been a proliferation of models, each with different and possibly conflicting objectives and claims to biological realism [Izh04]. Solving large-scale behavioural questions with biological accuracy requires impractical simulation times on conventional computers [IE08], [HMS08]; it seems virtually self-evident that dedicated neural hardware is essential. Neural network chips have been around for about 20 years now, however, the biological community has not received chips that attempt a literal hardwiring of a specific neural model in silicon enthusiastically, for two important reasons. Obviously, if the "correct" model of biological neural network operation is still under debate, hardwiring model assumptions into the design makes blind compromises while limiting the group of modellers who can use the device at all. Secondly, many of the model approximations in the hardware do not have enough theoretical support to be justifiable to biologists, whose models often involve very careful curve fitting. But a neural network system that attempts to learn by imitation, precisely replicating every detail of the biology or every line of an algorithm is unlikely to yield any fundamental insights. It is simply an implementation of what the researchers already know. If their utility is to extend beyond verification of pre-existing models, neural systems need a mechanism for abstraction.

To address these problems, a new device that implements a type of neural "blank slate" has been introduced: SpiNNaker, a chip with a neural network architecture but general-purpose components that can, in principle, simulate any model. However, by suggesting a form for the appropriate hardware architecture for neural modelling, SpiNNaker reopens the question of the appropriate system architecture: how are modellers to implement a given neural model on such a blank-slate device? In a system where the nature of its function depends on a model it has been configured to run, the tool architecture has a large part in determining the system's capabilities. Without a whole-system architectural approach the chip would be no different from earlier hardwired designs in that it essentially presented a chip to modellers and expected them to use it. This work addresses the critical need to develop an exemplar flow for neural implementation on universal hardware such as SpiNNaker, valid for multiple heterogeneous network models.

#### 1.2.2 The Search for the Computational Model

Regardless of any biological insights, neural networks as a computational tool have proven to be a useful alternative to the conventional sequential digital computer for many practical problems. Given a bare neural chip, it is quite likely that individual developers would develop applications tightly optimised for the specific problem they were trying to solve, giving little scope for interoperability or design reuse. This reason alone is sufficient to justify libraries for neural instantiation on chips such as SpiNNaker. However, a more fundamental reason is that, just as the asynchronous parallel nature of biology can contribute insights to computation, the universal abstraction power of computational techniques may suggest better models for cognitive neuroscience. There remains a gap between observations and applications that needs improved theoretical support to narrow. Neural network design, even for simple problems, remains today very much a process of trial and error; extensive parameter tuning is the normal order of the day [GAS08]. Meanwhile, much of current neural computation theory consists of highly abstract proofs of formal properties. There are in contrast very few practical, concrete "design rules" that permit a modeller to *calculate* parameters or connectivity. This study introduces a library-based development model for neural hardware to permit like-for-like comparisons at a high level, allowing direct verification by experiment of principles which up to now could only be elaborated on paper.

The event-driven model is an important process abstraction with direct biological relevance as well as interesting computational properties. Real biological neural networks use spikes, and it is natural to abstract a spike to an event (assuming the precise spike shape is unimportant). There is some theoretical evidence to suggest that spiking neural networks have greater computational power than nonspiking systems [ŠO03], indeed, it is possible in biology that spiking systems with asynchronous dynamics are necessary to certain behaviours [THA+10]. This makes the event-driven model the process dynamic of choice for a neural system architecture. Neural hardware such as SpiNNaker is already adopting event-driven communications as a standard, and thus the development systems for such hardware must likewise follow an event-driven model to maintain a unified system architecture. Since many classical computational neural models use continuous, nonspiking activations, the tool chain also needs to provide a method of translating nonspiking models into an event-driven representation. Event-driven development is nontrivial, however, and event-driven tools are scarce for

any platform, much less a dedicated neural device. This work therefore develops *event-driven* libraries that can automate the process of instantiating a neural model: a basic requirement for a configurable neural system whose purpose is to uncover the principles of neural computation.

#### 1.2.3 The Limitations of the Simulation Model

Without an integrated tool chain, bare hardware by itself is useless: it is cumbersome to run, much less design, models. Furthermore the typical neural modeller has little interest in or possibly even opportunity to learn a nonstandard, hardware-specific software system. Classical programming languages like C or Java do not intrinsically incorporate events and so are likely to fit poorly with the neural model; existing neural simulators like NEURON or GENESIS, or even Matlab, offer no easy extensibility to hardware and are unrealistic for real-world environments. Hardware design languages include native event support that fits elegantly with the chip and the neural model, but are unfamiliar outside a specialised audience. An approach that hides a hardware-design "back end" behind a neural-modelling "front end" is the type of integrated tool chain necessary. In this model the back-end contains prewritten, probably precompiled, "neural function" libraries that standard neural simulators can instance and use as if the hardware were part of the simulator itself. Thus the libraries provide the event-driven support and the neural simulator can deal purely in model-level abstractions. Note also that such an approach would be impossible without a universal neural device; "hardwired" chips would force the simulator to conform to its internal configuration, prohibiting model-level abstraction. To demonstrate the viability of this neural modelling architecture, this study demonstrates the core of the back-end libraries: efficient, non-trivial event-driven model implementations on the target hardware, and methods to integrate these into existing neural simulators, prototypes of the front-end interface. It will become clear through actual neural network implementations that an integrated, event-driven, library-based hardware system permits more efficient modelling of large-scale neural networks than either software simulators or bare custom hardware alone.

#### 1.3 Contributions

#### 1.3.1 Achievements

Development of an integrated modelling architecture for neural hardware establishes the value of **an event-driven library for universal neural hardware**. Within the framework of this overarching achievement, the following key contributions stand out as significant advances.

#### A system architecture for mapping a neural network to dedicated hardware:

If a universal dedicated neural device like SpiNNaker represents the most promising approach to large-scale modelling in light of debates over the model, it is also virtually useless without an integrated development system to instantiate models on the hardware. This work develops that model. It emphasises a view that considers the entire hardware/software platform as a unified *system*, and creates an architecture suitable for implementing neural networks not only on SpiNNaker but on other hardware platforms.

#### A general-purpose event-driven representation for neural models:

The neural library which represents the core of this work includes multiple heterogeneous models. Managing such models would be difficult without a common specification that makes it possible to build general interfaces into which the model details can simply be "plugged in". An important contribution is the development of a function pipeline, suitable for broad classes of neural model, and designed around considerations of what event-driven hardware like SpiNNaker can efficiently implement, that forms a "building-block" specification for neural models.

#### Scalable implementation of neural models in event-driven hardware:

Especially when large-scale networks containing more than  $\sim 65 K$  neurons are under consideration, design automation is critical. In addition to the software architecture and libraries, this work develops a functional automated tool chain that allows a user to specify a model in a high-level description environment and have the tools automatically configure, map, and implement the model on SpiNNaker hardware. Implementation of functional neural networks able to operate in real-world conditions demonstrates

21

the utility of this architecture and provides an exemplar template for future large-scale model implementations.

Important details on these contributions have appeared in the following:

- A.D. Rast, S. Yang, M. Khan, and S.B. Furber, "Virtual Synaptic Interconnect Using an Asynchronous Network-on-Chip". In Proc. 2008 Int'l Joint Conf. on Neural Networks (IJCNN2008), pp. 2727-2734, 2008.

- A.D. Rast, X. Jin, M. Khan, and S. Furber, "The Deferred-Event Model for Hardware-Oriented Spiking Neural Networks". In Proc. 2008 Int'l Conf. Neural Information Processing (ICONIP 2008). pp. 1057-1064, 2009.

- 3. A.D. Rast, M. M. Khan, X. Jin, L. A. Plana, and S.B. Furber, "A Universal Abstract-Time Platform for Real-Time Neural Networks". In Proc. 2009 Int'l Joint Conf. on Neural Networks (IJCNN2009), pp. 2611-2618, 2009.

- 4. A.D. Rast, S. Welbourne, X. Jin, and S.B. Furber, "Optimal Connectivity in Hardware-Targetted MLP Networks". In Proc. 2009 Int'l Joint Conf. on Neural Networks (IJCNN2009), pp. 2619-2626, 2009.

- A.D. Rast, X. Jin, F. Galluppi, C. Patterson, M.M. Khan, L.A. Plana, and S.B. Furber, "Scalable Event-Driven Native Parallel Processing: the SpiN-Naker Neuromimetic System" In Proc. 2010 ACM Int'l Conf. Computing Frontiers, pp. 21-29, 2010

- A.D. Rast, F. Galluppi, X. Jin, and S.B. Furber, "The Leaky Integrate-and-Fire Model: A Platform for Synaptic Model Exploration on the SpiNNaker Chip" In Proc. 2010 Int'l Joint Conf. Neural Networks, pp. 3959-3966, 2010

- M.M. Khan, D.R. Lester, L.A. Plana, A. Rast, X. Jin, E. Painkras, and S.B. Furber, "SpiNNaker: Mapping Neural Networks onto a Massively-Parallel Chip Multiprocessor". In Proc. 2008 Int'l Joint Conf. on Neural Networks (IJCNN2008), pp. 2849-2856, 2008.

- 8. X. Jin, A. Rast, F. Galluppi, M. M. Khan, and S. Furber. "Implementing Learning on the SpiNNaker Universal Neural Chip Multiprocessor", In Proc. 2009 Int'l Conf. Neural Information Processing (ICONIP 2009). Springer-Verlag, 2009.

- M.M. Khan, J. Navaridas, A.D. Rast, X. Jin, L.A. Plana, M. Luján, J.V. Woods, J. Miguel-Alonso and S.B. Furber, "Event-Driven Configuration of a Neural Network CMP System over a Homogeneous Interconnect Fabric", In Proc. Int'l. Symp. on Parallel and Distributed Computing (ISPDC2009), pp. 54-61, 2009.

- X. Jin, M. Lujan, M.M. Khan, L.A. Plana, A.D. Rast, S. Welbourne, and S.B. Furber, "Efficient Parallel Implementation of a Multi-Layer Backpropagation Network on Torus-connected CMPs" In Proc. 2010 ACM Int'l Conf. Computing Frontiers, pp. 89-90, 2010

- 11. X. Jin, M. Lujan, M. Khan, L.A. Plana, A. Rast, S. Welbourne and Steve Furber "Algorithm for Mapping Multilayer BP Networks onto the SpiN-Naker Neuromorphic Hardware" In Proc. 9th Int'l Symp. Parallel and Distributed Computing (ISPDC 2010), pp. 9-16, 2010

- 12. X. Jin, A. Rast, S. Davies, F. Galluppi, and S. Furber. "Implementing Spike-Timing Dependent Plasticity on SpiNNaker", In Proc. 2010 Int'l Joint Conf. Neural Networks, pp. 2302-2309, 2010

- X. Jin, F. Galluppi, C. Patterson, A. Rast, S. Davies, S. Temple, and S. Furber. "Algorithm and Software for Simulation of Spiking Neural Networks on the Multi-Chip SpiNNaker System", In Proc. 2010 Int'l Joint Conf. Neural Networks (IJCNN 2010), pp. 649-656, 2010

#### 1.3.2 Outline

The rest of the work will develop the themes and contributions this Introduction has outlined briefly, through the following sections:

#### Review of Hardware-Based Neural Systems

This chapter will discuss the historical context of neural modelling on hardware. It will outline previous important architectures and findings, and give some feeling for the overall direction of research trends through time.

#### Introduction to the SpiNNaker Chip

SpiNNaker is the chosen hardware platform to demonstrate event-driven models, and the exemplar universal neural device. It is essential in order to understand the actual model development to have a working knowledge of

23

the hardware design and features of SpiNNaker. This chapter will discuss SpiNNaker in overview.

#### The Library Architecture

This chapter introduces the core architectural concepts that form the central subject of the research. It goes through the process of selecting and defining the design tools and the development model for SpiNNaker. Such a process is not trivial because most tools incorporate an implicit synchronous system assumption. The question is how to implement a system that allows the user to create event-driven models without detailed hardware knowledge.

#### **Network Implementation**

This chapter describes the actual networks implemented on the SpiNNaker platform. It will describe their structural and dynamic design to make test results intelligible, but will focus on presenting the networks in the general context of an event-driven function pipeline. The emphasis of this chapter, therefore, will be the architectural model rather than the details of any given network.

#### Software Testing: Pre-Hardware Implementation

This chapter will report results from testing in simulation. Most of the development work used Verilog and SystemC simulators to present a virtual chip test environment, and this chapter both presents the simulation results and indicates the limitations of software simulation. Finally, it will examine the importance of software testing as part of an overall neural system design process.

#### Hardware Testing: On-Chip Implementation

This chapter will report results from testing on physical SpiNNaker hardware. Real hardware permits testing of much larger-scale networks, thus the chapter will focus on large-scale tests. It will only note smaller scale tests where there is a significant observed deviation from software testing.

#### **Discussion: Overall Findings**

This chapter will present the implications of the event-driven model: what it reveals about necessary models of computation for neural systems. It will also discuss what the benefits of such a model are: what new computing capabilities become available. Finally, it will try to give some perspective on

lessons learned: what building and testing revealed about the assumptions built into current models and design tools, which implementation tactics work and which turn out to be impractical.

#### Architectures for the Present and the Future

This chapter will offer some conclusions. The presentation will reflect a strong opinion that real conclusions consist not in extracting the immediate implications of the research (this is the role of a discussion section), but on what influences the research might have on the field as a whole. In this case, the central point is that neural networks introduce an alternative model of computation that will mean entirely new system architectures, and that it is through this architectural reconceptualisation that it will become possible to understand how the brain works.

#### 1.3.3 Significance

What is the impact of event-driven libraries for neural hardware? If there is one central notion that this thesis wishes to show it is that **neural computation is** a fundamentally different model of computing than sequential digital computation. To that end, this research makes and will attempt to support the following central claims.

#### Neural networks need universal dedicated hardware.

A neural network simulation running on a general-purpose serial computer is two virtually independent computational models trying to run at the same time. This is inefficient, impractical for very large networks, and eliminates one of the central benefits of neural computing: parallelism. Indeed, it is not even clear whether a serial, synchronous system can model all the dynamics of a parallel network, some of which may depend explicitly on the architecture. Therefore, hardware that offers a native implementation of the neural computing model is essential.

# Useful neural modelling requires abstraction of space, time, and function.

As long as the debate exists over the precise nature of neural computation, no design that fixes the model in silicon can be authoritative. However, a "silicon copy" of the brain provides no insight either, for replication of

25

known neurobiology is simply empirical repetition. A neural network model must therefore be able to provide an abstraction that successfully predicts neural behaviour if it is to increase understanding. Since neither the internal function, topology or temporal dynamics of neural networks are fully understood, the model must provide a mechanism to abstract each.

#### Event-driven neural computation provides a general means for temporal abstraction.

No system that depends upon an external clock can provide a complete abstraction of time, because the external clock introduces an absolute reference. Synchronous sequential computation is thus inadequate and inappropriate for neural networks. The event-driven model introduces a new and fundamentally different model of time: event rate. Events can carry arbitrary time labels (including no time marker), thus it is possible to implement any model of time simply by specifying the label for each event to carry.

#### An integrated, library-based tool set is a core architectural component of a universal neural system.

If the critical feature of universal neural hardware is user configurability, it must needs have development tools that make it possible for the user to configure the chip. Tools that only provide low-level, assembly-language-like programs consign the hardware to a small audience because very few users are willing to negotiate the steep learning curve and long development cycle necessary at such a low level. Libraries are an easy way to provide this high-level functionality without losing implementation efficiency. If the tool set contains prewritten, low-level libraries of neural function, that the user can instantiate via a script-based system or GUI at a high level, a new user can quickly create and run neural networks on the hardware.

# A function pipeline containing retrieval, evaluation, lookup table, interpolation, and differential equation solution is a block-level abstraction sufficient to implement an arbitrary neural model.

If different neural model implementations use a completely different module architecture, library management becomes too complex and interoperability in the same simulation nearly impossible. A system based on block-level replication of standardised function templates makes it easy to create the high-level structure while retaining model flexibility through parameterisation. Such a system, furthermore, resembles the architecture of the brain and this close correspondence to an evolved solution suggests that it will be an efficient method with a minimum of implementation complexities. Considering what circuit fragments can implement what operations efficiently, and what operations neural networks require, the general block template should have variable retrieval, polynomial evaluation, table lookup, polynomial interpolation, and differential equation solution as its subcomponents.

#### Abstracted models running on generalised hardware can reveal enough biological insight to be meaningful in understanding the brain.

There is no reason to believe a working abstract model running on abstract hardware inherently has any claims to biological plausibility. This makes it difficult to justify the validity of the model, especially in the eyes of neurobiologists. On the other hand, if the biological model of computing depended on all the biophysical minutiæ, neural computation would be a sterile research field: there would be no way to derive theoretical principles of neurocomputing, leaving it a purely empirical discipline. Therefore if neural computing research is to be fruitful it *must* be the case that abstract models can replicate the essential functionality of the brain. A model running on universal neural hardware that duplicates important behavioural characteristics and has strong predictive power with respect to other, previously uncorrelated behaviours, is powerful evidence for the value to biology of the event-driven architecture and and the universal neural chip.

# A universal event-driven system architecture is the critical abstraction necessary to achieve brain-like levels of neural modelling and computing capability.

Attempts to emulate full-brain function on synchronous digital systems run into increasingly intractable scaling barriers. On the other hand, attempts to duplicate neural behaviour even on small scales with increasing levels of biophysical fidelity run into increasing intractable analysis barriers. When computation is completely deterministic it is, indeed, questionable whether any model can fully explain or achieve brain-like computation. Changing

27

the model to an event-driven architecture relieves scaling difficulties while providing a level of non-determinism that can sustain spontaneous activity. Combining the event-driven model with a universal neural hardware system contains the analytical explosion while moving towards a native neural execution platform rather than a force-fit adaptation of digital systems.

# Event-driven neural computation presents a meaningful alternative to sequential digital computation.

Progress in computing will continue to stagnate so long as the serial uniprocessor computing model is taken as an unquestioned given - the situation that prevails today. Clearly, neural networks are not serial uniprocessors: attempts to fit them to this model will fail. Ultimately, the brain solves a different class of computing problem from the digital computer. Solving this class of problem may well require brain-like neural computing. Dedicated, nondeterministic parallel systems thus become a basic requirement for neural computation, at least at large scales; it is the event-driven architecture that provides a usable execution model for such systems.

# Chapter 2

Neural Network Architecture Trends 2.1. CONTEXT 29

#### 2.1 Context

This chapter will attempt to put neural network hardware in historical context and review the main research developments. The first part considers the architectures: basic platforms for neural networks that have historically dictated available capabilities. These architectures fall into three basic types, "hardwired" networks which have attempted a direct hardware implementation of a specific neural network algorithm, FPGA-type networks which offer reconfigurability and wider model choice in exchange for somewhat reduced speed and scalability, and neuromorphic networks, which move beyond simplified computational algorithms to attempt biorealistic modelling, often with some level of configurability. A pervasive theme permeating all these approaches has been "direct implementation" - the alluring but ultimately somewhat misleading concept that it should be possible to make the hardware a literal embodiment of the model of computation.

The second part asks a critical question that affects the value of a "direct" implementation: what is the hardware going to be used for? There is no reason to believe, a priori, that hardware designed for biological simulation will perform well in computational applications, and it is important within the biological domain to consider what part of the neural network is most important within the context of a given study: network dynamics, neural behaviour, synaptic response. In the computational domain, meanwhile, neural networks perform well for specific applications but are not necessarily good for general-purpose computation. One domain where neural networks may be particularly valuable, however, is embedded systems. Such applications usually demand real-time adaptability to dynamic environments, often under tight power constraints. Standard digital processing is frequently unsuitable in such situations and here neural networks can have compelling advantages. Event-driven computing emerges as a particularly suitable model for the types of applications that neural hardware performs well in, with clear biological relevance, offering a path to standardisation which unifies the disparate applications for neural networks into a single architectural model.

The third part examines actual concrete implementations in hardware. Specifically, it looks at chips: while there have been some neural network hardware platforms that make original use of standard hardware, in the main the development has been in custom IC's or FPGA's. The story of chip development follows two major routes: analogue hardware which hopes to emulate neurons with silicon

device physics, and digital systems, which hope to leverage the advantages of standard and fast-improving process technology along with vastly more predictable device characteristics in order to create accessible neural hardware that minimises the need for careful parameter tuning. However, the signal development in the field has been the introduction and rapid adoption of Address-Event Representation (AER), a mixed-signal communications standard that permits easy interfacing between heterogeneous components, transforming the analogue/digital choice from a hard commitment into an implementation convenience. AER is perhaps the most important advance in neural hardware systems and paves the way for "neuromimetic" hardware: chips with an abstract, configurable internal structure but an overall architecture optimised for neural processing.

### 2.2 Architectures: Hardwired, FPGA, Neuromorphic

A neural network is a structural architecture that naturally suggests hardware implementation. Dedicated hardware can fully replicate the parallelism of the network, and neural networks provide a classic example of an "embarrassingly parallel" application [NS92]. Unsurprisingly, therefore, neural network chips emerged almost as soon as the process technology reached the point that this was feasible [TH86], [GHJdV87], [Gar87]. Since the first neural network chips, however, process technology has evolved, and so has research opinion on the actual biological operation of neural networks [MJH<sup>+</sup>03]. As a result there has been a comparable evolution in the prevailing hardware neural network architectures over time [RTB+07]. The research community has had 3 main phases of development. In the first, the "hardwired" phase, the emphasis was on pure connectionist functionality in silicon, whether analogue or digital [LL95]. Devices in this phase also tended to use non-dynamic "timeless" models employing either continuoustime or synchronous update behaviour. In the second, "reconfigurable" phase, designs moved onto reprogrammable hardware, mostly digital FPGA's, either to time-multiplex functions or to permit dynamic network remapping [JS03]. At this point event-driven implementations begin to emerge, primarily for efficiency rather than biological realism. In the third, "neuromorphic" phase (still currently prevalent), focus shifts to greater biological plausibility with spiking networks, often analogue, frequently with extensive reconfigurability [JC09]. During this evolution, process technology tends to determine progress to a greater extent than biological (or even computational) research findings.

The dynamic model: how the neural network "state" evolves with time, has been an important strand of development. From the outset it has been clear that conventional sequential processing is a poor fit for modelling neural systems. [JSR<sup>+</sup>97] It is not clear that the model of a single master clock to drive internal state updates is optimal for parallel systems [YB09], and it certainly is not biologically plausible [TMS93]. This has given scope for researchers to experiment with various dynamic models, using neural processing as a "silicon canvas" to try their ideas [PWKR02b], [MJH<sup>+</sup>03], [ICD06]. In spite of this freedom, however, one major timing assumption continues to limit most current designs: the need to maintain a coherent system state. This is a stipulation that at any point the modeller can stop the chip in mid-process and get a complete "system snapshot" of the entire neural state [PLGW07]. Such an assumption distorts the model of parallel computation. A truly parallel computer is a set of independent processing modules; if system state must be coherent then the computer is not actually parallel but a set of coupled subprocesses in an overall serial architecture [CJ92], [MR94]. Historically, this is how early models of neural computation emerged [Ros58] [Hop82] but the result has been to create a dominant architectural model in the chip design community that persisted for some time after the neural modellers had already moved on to dynamic, spiking models. Not until FPGA implementations started to examine creative solutions to resource limitations [LSLG94] did researchers begin systematically to examine the temporal model, and it has only been relatively recently that neuromorphic systems have started to implement spiking [APR+96] as the standard model [Maa01]. There remain still strong traces of the coherent architecture even in state-of-the-art devices, however, and on the whole it appears that observability has had a controlling influence on the evolution of the dynamic model in hardware.

#### 2.2.1 Hardwired Architectures

Early neural network chips were mostly hardwired [GHJdV87], [FWA88], [YMY<sup>+</sup>90]. In the hardwired approach, hardware, usually custom ASICs, directly implements a specific neural model and topology. Only minimal configuration of the chip is possible, if the device allows any programmability at all [HTCB89]. Hardwired designs achieve the highest speeds possible for the available process

technology, since the hardware is a literal translation of the model into circuitry. While this architecture is the "obvious" approach it has significant drawbacks. There has tended to be no tool chain other than a basic interface, usually in the form of a device driver [SBS05]. With minimal tool support, using such chips has, historically, been difficult [ICK96]. The would-be modeller usually has to have intimate knowledge of the low-level details of the hardware. Integrating these chips, containing proprietary interfaces, into larger systems is equally difficult because the entire system must be built from the ground up [Ker92]. But the critical limitation of such chips is the obvious one: they can only model one, or at most a few, neural models. Therefore there is minimal scope for model experimentation, and unless the implemented model exactly matches the experimenter's preferred neural model, the device is in effect useless [SBS05]. Chips implementing true dynamic models are rare [SHS95]; those with any hardware support for events, rarer still. The effect has been to confine the use of these chips to the original developers, along with, at most, a small group of related researchers sympathetic to the model implemented. Given the very high up-front investment required to produce a full-custom ASIC, it has been very difficult to justify producing such devices, and hardwired architectures ended up being something of a research dead-end [Omo00].

#### 2.2.2 Reconfigurable Architectures

Reconfigurable architectures use FPGA devices to implement neural networks with dynamic internal logic [EH94b]. FPGA implementations became popular when it became clear that the ASIC approach was gaining little adoption and when coincidentally FPGA densities started to become large enough that implementing full-scale neural networks on them was practical [PWKR02a]. They use commercially available, off-the-shelf hardware and development tools, making hardware neural modelling accessible, at least in principle, to those without the resources to develop a full-custom IC. However, FPGA's bring with them several significant limitations. Dynamic reconfigurability is only possible with some FPGA's, and furthermore the tools usually limit the scope for reconfiguration [SVS+09]. Such reconfiguration takes time and is very complex to program, FPGA programming sequences being typically arcane and proprietary [KdlTRJ06]. FPGA's have digital components with a very specific structure, placing further limits on what functions and dynamics are implementable, and

often requiring careful optimisation, particularly with expensive synaptic multiplication operations [HAM07]. Most importantly, FPGA's impose a clocked synchronous model of computation: any neural model that uses other models of time must transform or adapt its dynamics into the synchronous environment [WL06], [ROA+06].

There have been 2 types of reconfigurable architecture: componentmultiplexing and programmable-model. Component-multiplexing architectures use the reconfigurability to implement a much greater number of individual neural elements than would be possible with fixed hardware of the same size [EH94a]. The device multiplexes individual components, either performing different processing stages or implementing different neurons [GMM<sup>+</sup>05], while in operation [LSLG94], [BHS98]. The component-multiplexing approach was the first to hint at an event-driven architecture, particularly with bit-stream applications that suggest an atomic message: an event, per bit [GSM94]. Using an event-driven approach to drive the multiplexing itself, however, remains a future research area [GMM+05]. In part this is because the multiplexing itself incurs a time overhead, making it suitable mostly in coherent update applications where scheduling the multiplexing in the presence of asynchronous input does not present problems [HAM07]. For similar reasons the actual neural model implemented on chip is usually static, thus they do not exploit the intrinsic programmability of the FPGA.

Programmable-model architectures use the dynamic reconfiguration capabilities to change the actual topology of the neural model, or its internal dynamics [PWKR02b]. Many of the early implementations, given the known limitations of partial reconfigurablity, focussed on changing the topology [PUS96] [UPRS05]. A severe limitation with FPGA's is the circuit-switched architecture, which hampers the ability to create the dense connectivity patterns realistic neural networks require [HMH+08b]. Attempts to create reconfigurable or event-driven dynamics do not appear in most cases to have proceeded beyond the design-exploration phase [EKR06], [ROA+06]. This seems, in fact, to be somewhat of a summary of the development of neural networks on FPGA's: useful for design exploration, but not pursued for full-scale modelling [HMH+08b].

Recently there has been experimentation with programmable-model architectures using graphics processors (GPU's) [OJ04]. The attractiveness of GPU's comes from massive parallelism with standard parts at minimal cost. Because of

their particular design, it is also easier to incorporate reconfigurable dynamics on GPU's than FPGA's. However, the nature of the GPU: an application-specific processor optimised for a different application than neural networks, imposes FPGA-like architectural limitations [BK06]. GPU's use an emphatically synchronous, coherent model. Maintaining process coherency, in fact, turns out to be one of the most challenging research topics [NDKN07]. Various similar limitations mean that mapping a neural network to a GPU is nontrivial, limiting its use in practical terms to people with extensive hardware expertise [BK06].

Ultimately the critical limitation for both platforms is probably limited scalability. FPGA's use a circuit-switched architecture, and this in turn means wire density limits achievable connectivity [HMH $^+$ 08b]. It is not difficult to note that while model connectivity scales potentially as  $N^2$  (where N is the number of neurons), FPGA wire density scales linearly with area (hence with number of neurons) and quickly runs out of routing resources with large networks. With GPU's, the external interfaces do not permit easy scalability to multichip systems [FRSL09]; not particularly surprising given that the design of the GPU assumes a single chip sitting on a graphics card. FPGA's are also very power-hungry: a design with 60% resource utilisation might consume 50W on a large FPGA like the Virtex-5. Meanwhile, GPU power requirements are crippling: an nVidia GeForce GTX280 can consume 236 W. Although reconfigurable architectures have proven useful for small-scale modelling and proof-of-concept experimentation, they are inadequate for large-scale neural networks.

#### 2.2.3 Neuromorphic Architectures

Neuromorphic architectures are more intimately concerned with biological plausibility than previous designs, usually implementing spiking networks with full dynamics [PRAP97], [WNE99]. Relative to the FPGA, neuromorphic systems appear like a return to older hardwired architectures, possessing considerably less general-purpose reconfigurability than FPGA designs, but this reflects an integration of the knowledge gained in the previous generations [VMC+07]. If the era of hardwired architectures revealed that fixing the model in hardware was overly limiting, the reconfigurable era showed that general-purpose reconfigurability sacrificed too many efficiencies in the name of universal application [HMH+08a]. In particular, the FPGA design leads to a synchronous digital model of computation that is too power-hungry and area-intensive for elegant neural

implementations [NdSMdS09]. Thus the neuromorphic approach accepts that some application-specific components are necessary, possibly using combinations of analogue and digital techniques [IWK99], along with enough general-purpose reconfigurability to tailor the system for various models [VMVC07]. There has therefore been a subtle shift of emphasis from which model to implement to what level of reconfigurability is appropriate to achieve an optimally efficient modelling platform.

Equally importantly, neuromorphic architectures incorporate the time domain integrally, in contrast to "timeless" hardwired architectures [WCIS07]. Therefore they can model biological networks with much greater realism than previous designs [VMVC07]. Typically, however, the networks integrate time explicitly in the hardware, as a parameter in analogue circuitry which usually tries to approximate the actual biophysics of neurons [MS08], [YC09]. Time is therefore fixed, with some scaling factor relative to "real" time, not abstract or programmable [KBSM09]. Where there are digital components they often (and increasingly, typically) use events [CWL<sup>+</sup>07], but only as an implementation convenience: events are merely the unit of translation between analogue and digital domains. Usually such systems also preserve time-coherency, in the sense that it is possible to interrogate the digital interface and get a complete readout of the network state [PVLBC<sup>+</sup>06], [CWL<sup>+</sup>07]: this represents a major departure from biological realism where the notion of a global state is meaningless because no one local unit or region possesses an instantaneous global view [Ban01]: neural transmission involves real delays [CEVB97], [Izh06]. While undoubtedly the neuromorphic approach allows the closest hardware approximation to the biology thus far, limited ability to abstract time still means that the fundamental question modellers ask is how accurately the hardware models the biology rather than what models they could use with the hardware to find out more about the biology [BI07].

This problem deflects attention away from the central question: if much of the actual computational model of the brain remains unknown, how can hardware provide insights into its function by modelling the biology realistically [VMVC07]? In this regard current neuromorphic architectures suffer from several deficiencies. One is in the area of model support: existing implementations have tended to emphasize hardware efficiency at the expense of reconfigurability, bringing them closer to the hardwired chips with all their known limitations [KGH09]. The

other major gap is tool support: neuromorphic architectures tend not to integrate seamlessly into existing simulators [BMD<sup>+</sup>09]. The user cannot therefore simply run a predeveloped model on the hardware: it needs translation, assuming, furthermore, that the target model is compatible with what the hardware supports [BGM<sup>+</sup>07]. Being outside mainstream commercial technology, such translation tools are scanty to nonexistent [BMD<sup>+</sup>09]. When it is difficult, such as here, to get even standard reference models to run, an understandable reaction of the biological modeller is to express scepticism about the validity of the models the chip implements [CSF04] - because he cannot test it against a model he is familiar with and trusts [RD07]. Thus neuromorphic chips have not to date provided a compelling platform for discovering valid biological abstractions, because it has been difficult to make direct comparisons against detailed models. The "ideal" architecture would be more of an integrated software/hardware system [OWLD05], containing a device that combined general-purpose programmability with the biological realism of current neuromorphic architectures, and a tool chain with direct support for existing simulators, native parallelism, and the ability to present neural networks at different levels of hardware abstraction.

# 2.3 Applications: Computational, Biological, Embedded

Whatever the potential benefits of a given neural architecture are, they have little meaning outside the context of an application in which to run. Neural network architecture is much more application-specific than digital computing, where the microprocessor realises a reasonably good solution to any problem that can be posed as a sequential algorithm, with an architecture that has stabilised to a standard form [Kön97]. Some of this may be intrinsic: it is possible that the physical form of the neural network model is tightly coupled to the task it performs [STE00], [ST01]. Evidence from neurobiological studies, however, indicate that such "hard-wiring" is limited and important only for primitive behavioural response or early processing stages; indeed, it may not even remain active after development [CHC06]. Much of the observed tailoring of architecture to application in the computational domain occurs rather because current applications come from fields with completely different priorities. There are applications in "classical" computation: more or less parallel data processing where the need

is to solve a specifiable problem. There are biological modelling applications: neural network simulations where the need is to approximate, hence to understand, brain function. And there are embedded systems applications: sensing and control tasks where the need is autonomous dynamic response in changing environmental conditions, often within power and area constraints.

#### 2.3.1 Computing Applications of Neural Hardware

Neural networks have already proven useful for some standard computer applications. In fields such as economic modelling [ASAW06], fraud detection [GR94], and image or character recognition [Kli90], [MGS05] commercial neural network software has existed for years. Generally, however, where such applications have been successful is when they can be transformed into an off-line process running as conventional clocked sequential algorithm [GT02]. In software, neural networks run relatively slowly and may not provide real-time dynamic response, e.g. a software-based neural network fraud detection system is unlikely to be able to provide on-line credit card approval at the point of sale, not with millions of transactions occurring simultaneously. In such an application, requiring real-time response with large data streams, an event-driven model is more appropriate [GSW02].

Conventional hardware is a poor architectural match for the event-driven model, suggesting a dedicated chip [JSR<sup>+</sup>97], [JH92]. However, this requires a large initial investment for a technology with substantial risks [MLS04]. Compared against the virtual certainty of progress in conventional processing technology during the time needed to design and fabricate the chips, this commitment usually looks unjustifiable [NG03], [ICK96]. There is no reason to expect that a chip designed for a specific neural network will perform well with a random application, certainly not that it will perform well in applications beyond a target application for which it was designed, and so pre-existing neural chips offer no definite benefits to the new user and few opportunities for reuse to the user already having such hardware [Rey03]. If, however, there were a system that allowed easy event-driven applications development for standardised neural hardware, neural computation would look increasingly attractive for large-scale real-time applications. Users could invest in a single system which would then be reusable for future applications and which provided an effective alternative computing resource to traditional mainframes.

#### 2.3.2 Hardware for Biological Simulation

Further progress in understanding biological neural networks virtually mandates dedicated hardware [JL07]. Simulating large-scale biological neural networks using software has become increasingly difficult if not completely impractical, with biologists expecting ever-more detail from ever-larger models [MCL<sup>+</sup>06]. Widespread use of spiking models has made event-driven processing standard in current software simulators [HC97], [DT03]; however, these run on sequential hardware, resulting in an inefficient layering of emulation: synchronous hardware, simulating event-driven execution, to drive a simulation of a neural network. Unsurprisingly performance is poor [JSR<sup>+</sup>97]. Meanwhile, there is a mismatch between available neural hardware and the models used in biology. Where the former usually use very simple spiking models such as leaky-integrate-andfire, (when they implement spiking models at all) [MJH<sup>+</sup>03], [ICD06], the latter are commonly complex multicompartmental conductance-based models such as Hodgkin-Huxley [HC97], [BPS10]. This points to a gap in mutual understanding: the divergent goals of the hardware designers, who typically are interested in the nature of the neural model of computation [WNE97], and the neurobiologists, who tend to be more interested in the causes and effects of neural computation [YC10].

The typical process of the biological modeller is to build into the model as many properties and components as practicable that have been observed in actual biological studies [MCL+06], [Dur09]. Such an attempt to learn by imitation, however, usually results in a model that yields very poor predictive power. If the model replicates the biological behaviour, all is well and good, but the experiment has not revealed anything the researchers did not already know. Meanwhile if it does not, there is one more mystery unsolved. In either case the researchers gain very little real insight. There can be no understanding of the properties of neural computing, beyond simply cataloguing phenomena, without an understanding of its nature [Ban01].

Hardware designers tend to use the engineers' approach: start with a simple model and progressively add features until it works [FT07], [WNE97]. While this approach readily leads to a series of design abstractions containing testable predictions [Hil97], it is important to differentiate a genuine *abstraction* from a mere *simplification*. An abstraction conveys general computational properties that continue to apply whatever additional detail is added; a simplification may

actually change the behaviour quantitatively even at the general level [Maa01]. The problem with current hardware is that it usually provides no method to separate the former from the latter, especially since many chips involve various adhoc design decisions taken as an implementation convenience [FSM08], [WNE97]. It is virtually certain that understanding neural computation must needs involve some abstraction of the biology, but what the appropriate abstraction is is not clear [WNE97]

What is needed is a general-purpose neural device that can model neural networks at any level of abstraction, so that while it can model very large-scale networks using simple models, it can at least in principle model detailed conductance-based models and provide meaningful acceleration to biologists using such models [HMH<sup>+</sup>08b]. Equally imperative is that this device have an integrated tool chain that can plug in with minimal interfacing to biological simulators like NEU-RON or high-level computational simulators like JNNS, so that modellers are not forced to learn a completely different specification and simulation environment [ASHJ04]. A universal neural network system that integrated with current simulators would permit direct Model A/Model B comparisons [BMD<sup>+</sup>09], making it feasible for biologists to identify conclusively which computational abstractions are valid and begin to attack the question of the biological model of computation systematically.

#### 2.3.3 Embedded Neural Systems