University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

# A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/4515

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

# NOVEL IMPLEMENTATION TECHNIQUE FOR A WAVELET-BASED BROADBAND SIGNAL DETECTION SYSTEM

By

Sheng Cheng

Department of Engineering

University of Warwick

A thesis submitted to the University of Warwick for the degree of Doctor of

Philosophy

August 2010

# **Contents**

| Cha   | pter I. |                                   | 1  |

|-------|---------|-----------------------------------|----|

| Intro | ocutio  | n                                 | 1  |

|       | 1.1.    | Overview of Active Sonar System   | 2  |

|       | 1.2.    | Motivation                        | 3  |

|       | 1.3.    | Layout of this Thesis             | 4  |

|       | 1.4     | Contributions made by this Thesis | 6  |

| Cha   | pter II | [                                 | 9  |

| Lite  | rature  | Review                            | 9  |

|       | 2.1 U   | Jnderwater Sonar Detection        | 9  |

|       |         | 2.1.1 Sound propagation           | 10 |

|       |         | 2.1.2 Scattering                  | 11 |

|       |         | 2.1.3 Sonar Detection System      | 14 |

|       | 2.2 V   | Vavelet Transform                 | 18 |

|       | 2.3 A   | Adaptive Noise Canceller          | 26 |

|       | 2.4 (   | Conclusion                        | 30 |

|       | 2.5 R   | References                        | 31 |

| Chapter III                                             |

|---------------------------------------------------------|

| Theoretical Background                                  |

| 3.1 Introduction42                                      |

| 3.2 Introduction & Specification of the system43        |

| 3.3 Wideband Sonar Detection45                          |

| 3.4 Wavelet Transform51                                 |

| 3.5 Local Optimum Search56                              |

| 3.6 Adaptive Noise Canceller59                          |

| 3.6.1 Fuzzy Inference System60                          |

| 3.6.2Adaptive Network61                                 |

| 3.6.3 Adaptive-Network-based Fuzzy Inference System63   |

| 3.7 Conclusion                                          |

| 3.8 References69                                        |

| Chapter IV72                                            |

| High-level System Architecture and Simulation Results72 |

| 4.1 Introduction                                        |

| 4.2 High level System Architecture73                    |

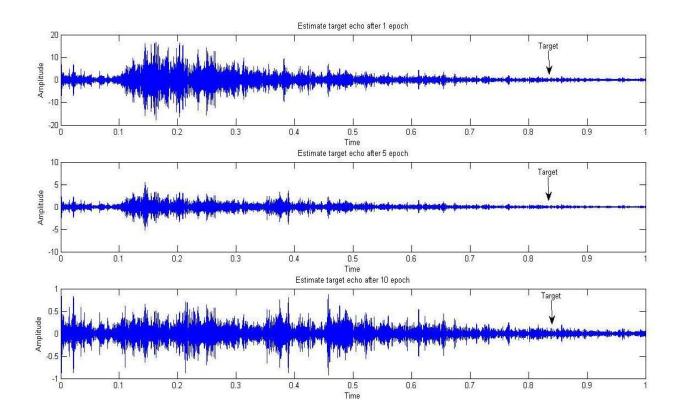

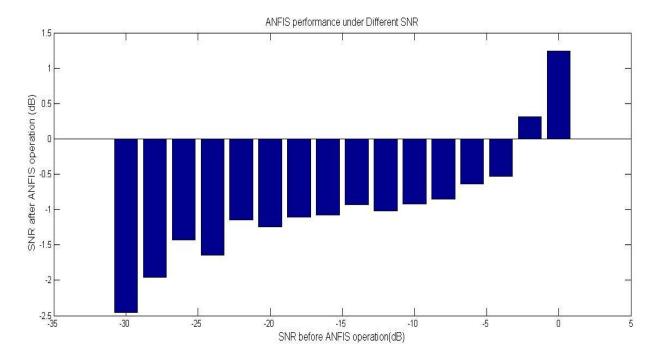

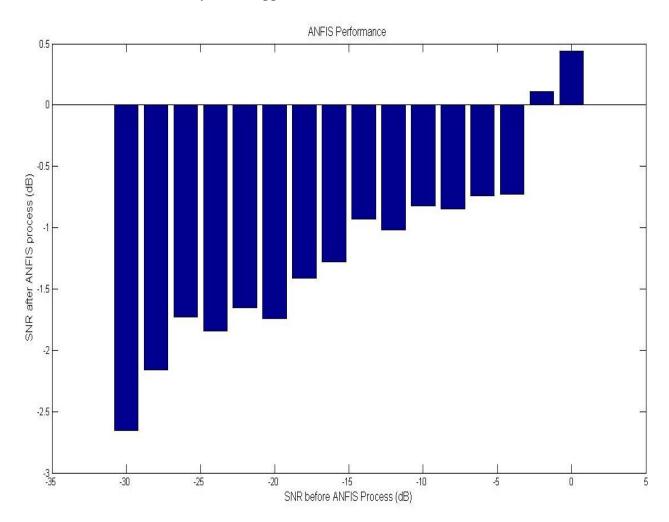

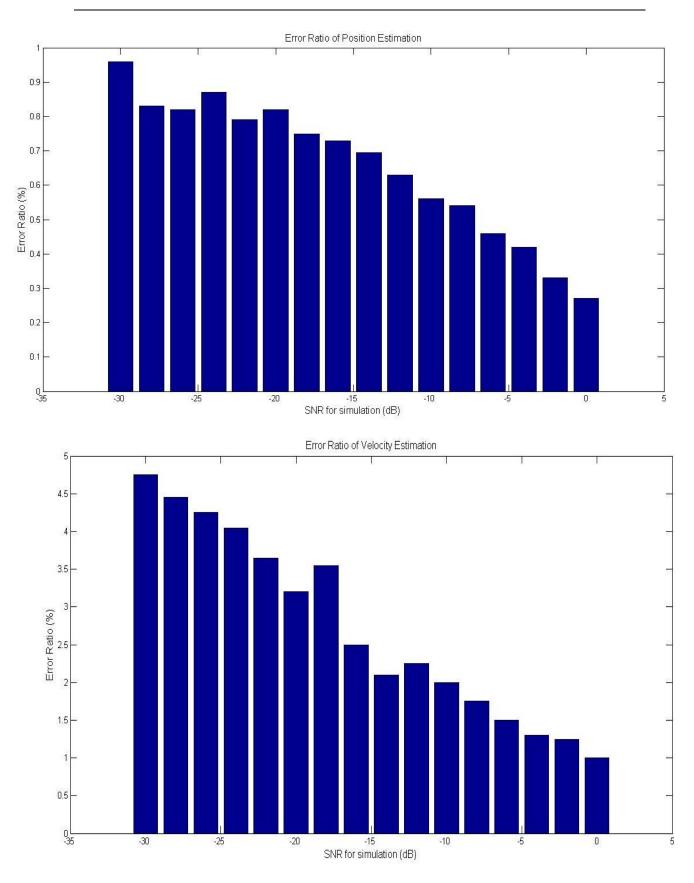

| 4.3 ANFIS modelling75                                   |

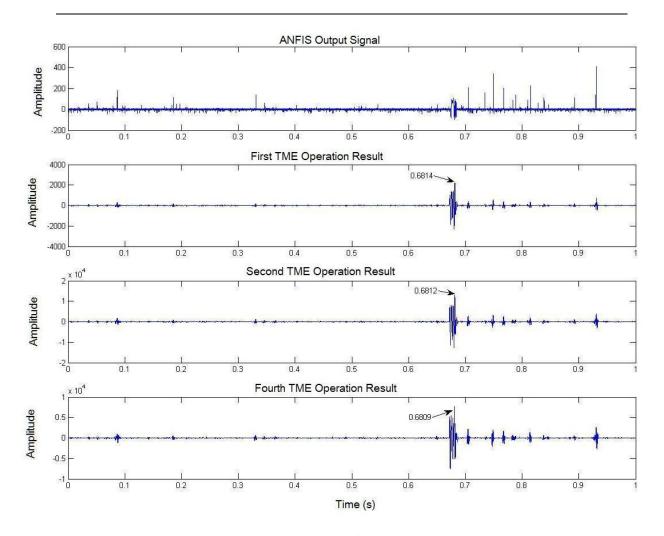

| 4.4 TME algorithm88                                     |

| 4.5 Conclusion                                          |

| 4.6 References                                          |

| Chapter V                                     | 102 |

|-----------------------------------------------|-----|

| Hardware Implementation                       | 102 |

| 5.1 Introduction                              | 102 |

| 5.2 Hardware Structure                        | 103 |

| 5.3 ANFIS Implementation                      | 104 |

| 5.4 TME Implementation                        | 109 |

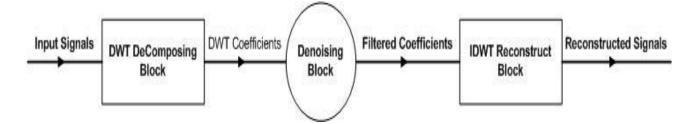

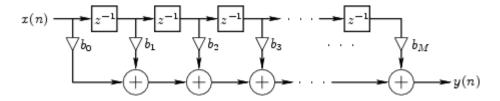

| 5.4.1 DWT Denoising filter bank               | 110 |

| 5.4.2 Optimization Block                      | 119 |

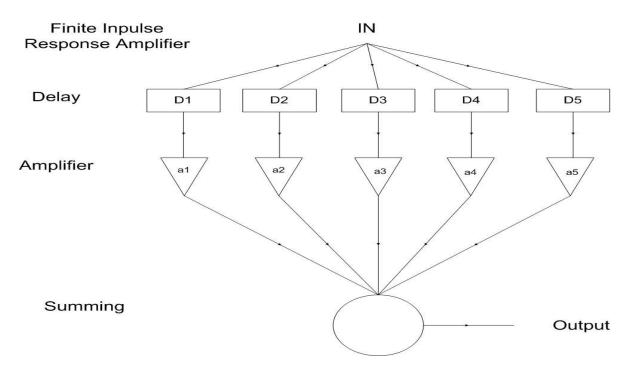

| 5.4.3 CWT convolver                           | 122 |

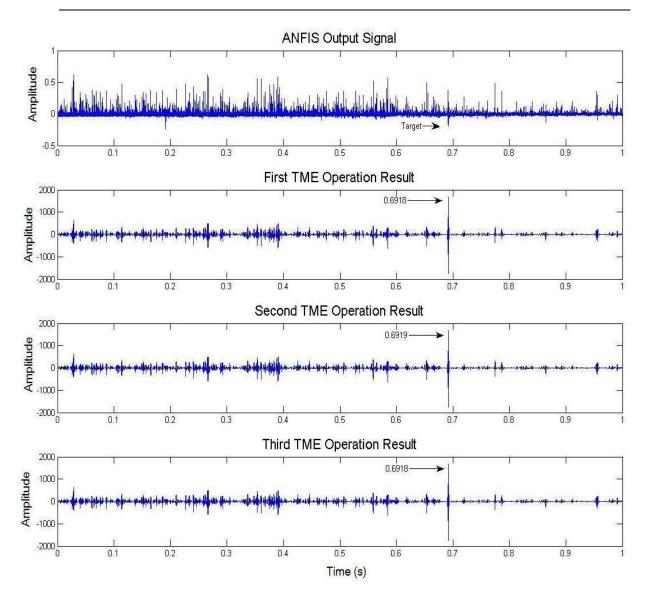

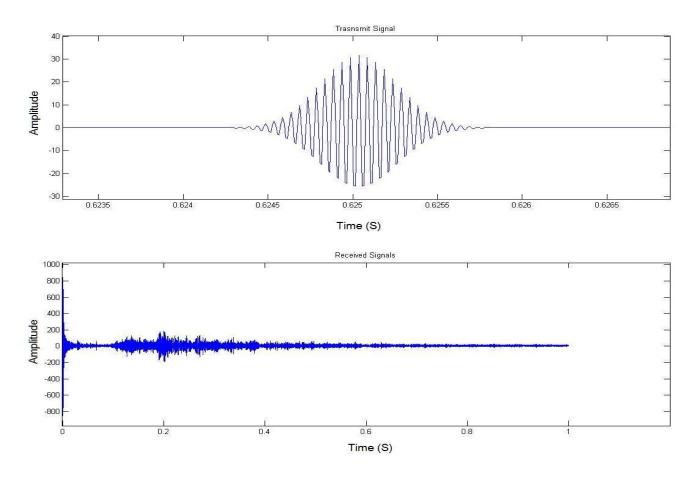

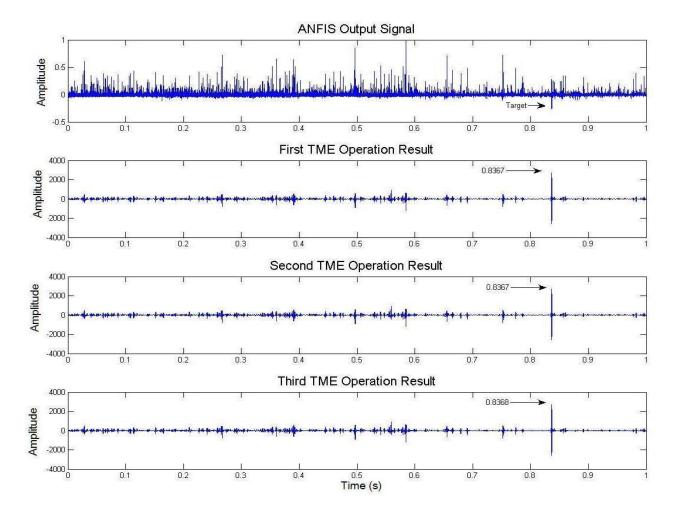

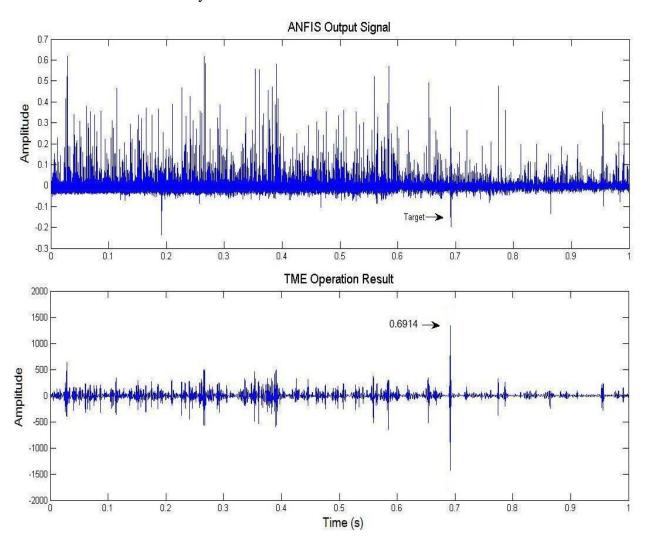

| 5.5 Simulation Results                        | 127 |

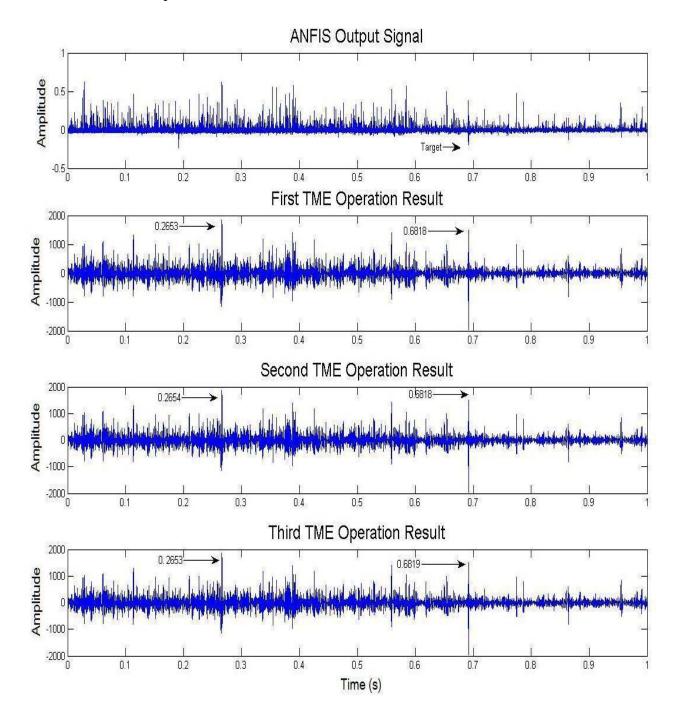

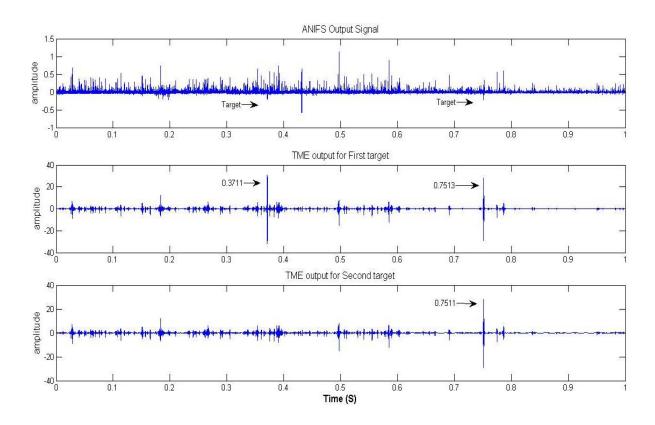

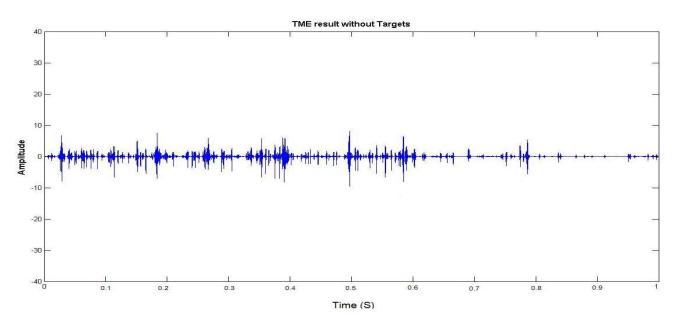

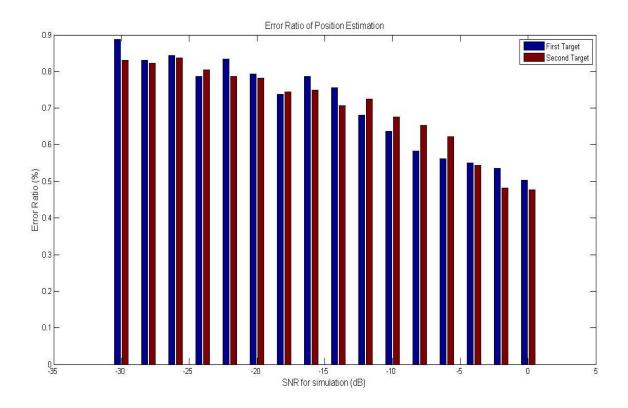

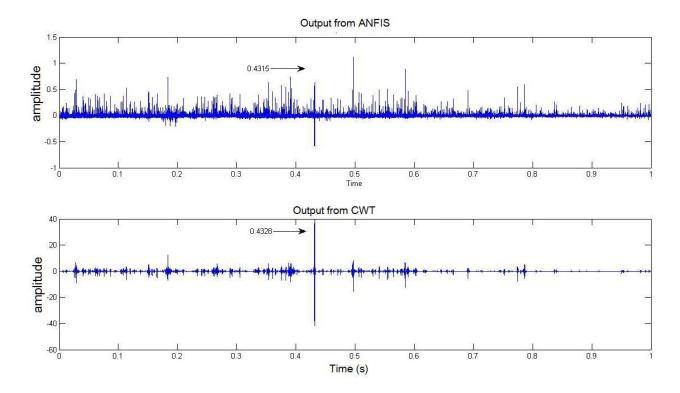

| 5.6 Multiple Target Detection                 | 139 |

| 5.7 Conclusion                                | 142 |

| Chapter VI                                    | 145 |

| Testing of Hardware System                    | 145 |

| 6.1 Introduction                              | 145 |

| 6.2 Testing Environment and Hardware Platform | 146 |

| 6.3 Single Target Detection Test              | 148 |

| 6.4 Multiple Target Detection Test            | 153 |

| 6.5 Conclusion                                | 157 |

| Chapter VII                                   | 158 |

| Analysis & Discussions                        | 158 |

| 7.1 Introduction                                       | 158 |

|--------------------------------------------------------|-----|

| 7.2 Single Target Detection                            | 159 |

| 7.3 Multiple Target Detection                          | 162 |

| 7.4 Discussions                                        | 162 |

| Chapter VIII                                           | 170 |

| Conclusions and Future Work                            | 170 |

| 8.1 Aimed Reviewed                                     | 170 |

| 8.2 Future Work                                        | 174 |

| 8.2.1 Performance improvement of ANFIS                 | 174 |

| 8.2.2 Improving the speed for CWT operation            | 174 |

| 8.2.3 ASIC implementation of proposed design           | 175 |

| Appendix A Design and Simulation Environment and Tools | 177 |

| Software                                               | 177 |

| Hardware                                               | 177 |

| Source Code                                            | 178 |

| Publications                                           | 250 |

# ACKNOWLEDGEMENTS

I would like to express my great appreciations to Dr. Marina Cole for her supervision, guidance and continuous support.

I also would like to give my thankfulness to Chien-Hsun Tseng, who cooperate with me in this project and helped me a lot in realization of the project, and Mr Hugh Dumbrell from Defense Science and Technology Laboratory (DSTL) of Ministry of Defense (MOD) who provides the real sonar data used for simulation in this project.

I want to express my gratitude for all the people helping me in the project implementation. To the staff in the School of Engineering, especially Dr. Richard Staunton, for his support on development tools.

Most of all, I would like to thank my family and Jiayu Yao, my girlfriend for their patience, love and inspiration.

# **DECLARATION**

This thesis is presented according to the regulations for the degree of Doctor of Philosophy.

The work described in this report is original and is the result of my own work and investigations except where otherwise indicated.

The Matlab model presented in chapter IV of this work was development in collaboration with Dr. Chien-Hsun Tseng.

The thesis has not been submitted in any previous application for a degree at another university.

Parts of this work have been presented at international conferences:

- Sheng Cheng; Chien-Hsun Tseng; Cole, M.;" A Novel FPGA Implementation of a Wideband Sonar System for Target Motion Estimation", Reconfigurable Computing and FPGAs, 2008. Page(s):349 – 354

- Sheng Cheng; Chien-Hsun Tseng; Cole, M.; ICECS 2007" Efficient and Effective VLSI Architecture for a Wavelet-based Broadband Sonar Signal Detection System". Page(s):593 - 596

# **ABSTRACT**

This thesis reports on the design, simulation and implementation of a novel Implementation for a Wavelet-based Broadband Signal Detection System.

There is a strong interest in methods of increasing the resolution of sonar systems for the detection of targets at sea. A novel implementation of a wideband active sonar signal detection system is proposed in this project. In the system the Continuous Wavelet Transform is used for target motion estimation and an Adaptive-Network-based Fuzzy inference System (ANFIS) is adopted to minimize the noise effect on target detection. A local optimum search algorithm is introduced in this project to reduce the computation load of the Continuous Wavelet Transform and make it suitable for practical applications.

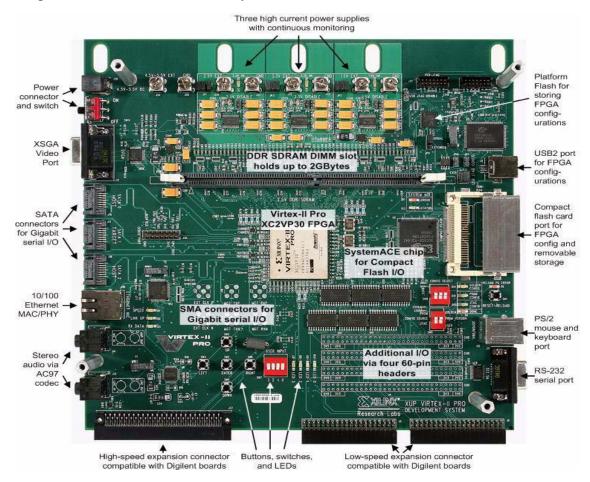

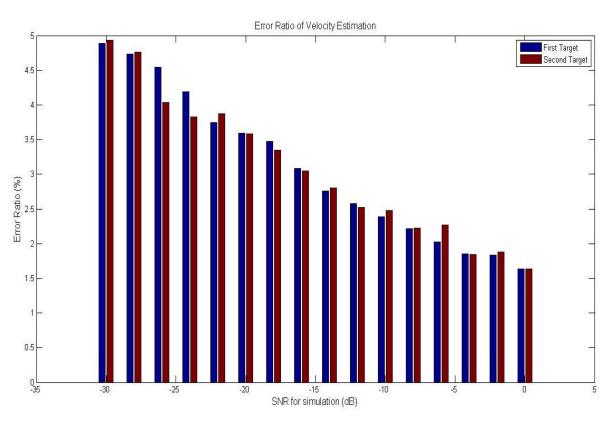

The proposed system is realized on a Xilinx University Program Virtex-II Pro Development System which contains a Virtex II pro XC2VP30 FPGA chip with 2 powerPC 405 cores. Testing for single target detection and multiple target detection shows the proposed system is able to accurately locate under reverberation-limited underwater environment with a Signal-Noise-Ratio of up to -30db, with location error less than 10 meters and velocity estimation error less than 1 knot. In the proposed system the combination of CWT and local optimum search algorithm significantly saves the computation time for CWT and make it more practical to real applications. Also the implementation of ANFIS on the FPGA board indicates in the future a real-time ANFIS operation with VLSI implementation would be possible.

# **ABBREVIATIONS**

ANC Adaptive Noise Canceller

ANFIS Adaptive-Network-based Fuzzy inference System

CWT Continuous Wavelet Transform

DWT Discrete Wavelet Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

SNR Signal-Noise-Ratio

SONAR SOund NAvigation and Ranging

TME Target Motion Estimator

# **CHAPTER I**

# **INTROCUTION**

This thesis presents the results of a research project into the application of Wavelet-based Broadband Signal Detection techniques for high resolution sonar system. The development of an end-to-end simulation of wideband active sonar is presented, along with the analysis of the effects of unknown target motion and techniques for accurately estimating sonar target movement. The active sonar techniques are discussed. The Wavelet Transform, originally for data analysis of seismic survey in oil and mineral exploration, was proven to be highly suited for sonar imaging. Several enhancements to the wavelet transform algorithm are presented in this thesis. Techniques for adaptive noise cancelling are demonstrated and a new strategy for reducing computation complexity of wavelet transform is presented in the context of this thesis. Real sonar data has been made available to the project, enabling the performance of the developed techniques to be demonstrated both analytically and practically.

This chapter begins with the introduction of the concepts of sonar imaging and the principles of active sonar system. The motivation for this project along with the discussion of the need to use the wavelet transform is then described. The contributions made by this work and the thesis layout are presented.

#### 1.1. Overview of Active Sonar System

SOund NAvigation and Ranging (SONAR) covers a broad range of techniques for detecting and imaging objects using sound. Sonar is one of the most commonly used techniques for forming images of objects underwater; this is mainly due to the much lower attenuation of sound compared to electromagnetic radiation of a comparable wavelength, which makes optical and radar systems unusable over large distances. Sonar systems range in complexity from simple passive listening devices to sophisticated active systems, the subject of this work.

Active side-scan sonar is commonly used for forming high resolution images of underwater scenes. Side-scan systems form an image of a target scene by transmitting a succession of sound pulses (referred to as 'pings') and recording the echoes from the target scene using a very narrow beam width receiver. An image of a target scene is built up a line at a time by moving the transmitting / receiving platform past the target area. The azimuth resolution of a side-scan sonar system can be increased by using a higher pulse frequency and / or a larger physical aperture. The attenuation of sound in water increases with frequency, creating a tradeoff between azimuth resolution and maximum range of side-scan sonar systems. The maximum physical length of the sonar array is limited by practical constraints.

The advantage of side-scan sonar is that it is able to provide a through image for underwater scenes in a certain area, however, this image cannot provide any velocity information for a certain target and post-processing of imaging is required to extract

certain target motion information. The wavelet-based active sonar applications, on the other hand, provide another way to examine target motion parameters. Following the principles of active sonar, a succession of sound pulses is transmitted and echoes from the target scene are recorded with a receiver. With the similar representation form between the returned echo in a wideband sonar system and the transformed signal by the Continuous Wavelet Transform (CWT), the seeking of target motion parameters can be achieved by finding parameters of returned echo through CWT. The thesis presents a wavelet-based active sonar system using both real and simulated data.

A requirement for very accurate knowledge of the position of the sonar system, and high computational complexities present a number of problems for a wavelet-based sonar system. This thesis discusses, and proposes solutions to some of these problems.

# 1.2. Motivation

There is a strong interest in methods of increasing the resolution of sonar systems for the detection of targets at sea. Systems currently used by the Royal Navy to detect targets are based on conventional side-scan and forward looking sonar systems. Such systems require post-processing on imaging of sonar scenes to identify location of mines or fish torpedoes, and are unable to provide the velocity of targets. Wavelet-based active sonar system can provide a solution for extracting target location and velocity information at the same time.

The detection of low- and zero-Doppler signals in real-time is computationally expensive if we are to use the optimum technique using the correlation matrix in a active

sonar system in reverberation-limited environment. Previous reseach on narrowband case shows an Adaptive Noise Canceller can be useful and computationly efficient. The proposed research aims at investigation of the broadband case, in which doppler-shift model, used in the narrowband case, is no longer valid. In particular, since the family of scaled wavelets better models the behaviour of pulses in a reverberation-limited broadband and shallow-water environment, the use of wavelets is proposed. Furthermore, the proposed method allows the possibility of designing a customized wavelet to minimize the noise effect on target detection. Therefore, the proposed active sonar system is able to provide an alternative method of side-scan sonar system to extract target motion parameters more efficiently.

#### 1.3. Layout of this Thesis

The thesis starts with an introduction to wavelet-based wideband active sonar system, this project, the motivation and requirement of this thesis. (This chapter)

**Chapter 2**: introduces the basic principles of sonar relevant to the proposed sonar system, along with a number of signal processing techniques used to extract target motion parameters in this work. Previous research on related techniques adopted in this project is also introduced.

**Chapter 3**: The chapter introduces necessary background theory for understanding the project. First of all it introduces the specifications and expectations for this sonar

detection system and then it illustrates respectively why specific techniques such as wavelet transform, ANFIS and Local Optimum Search are adopted in the proposed system and how these techniques work. The chapter also shows the integration of all these techniques into a complete system.

**Chapter 4**: The theoretical model of the proposed system is presented and the design details of the high-level system are explained. The simulation results in Matlab for the high level system are used to estimate the performance of the proposed system.

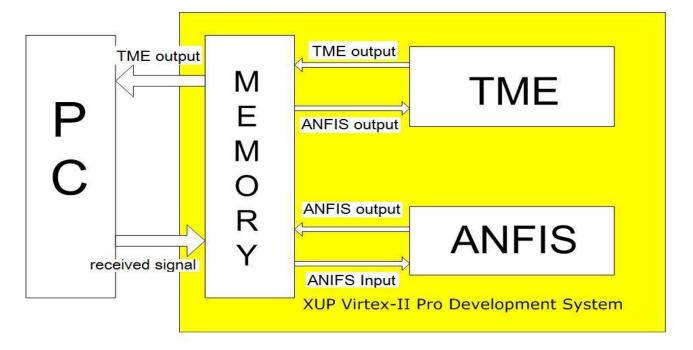

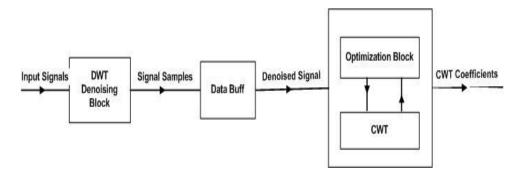

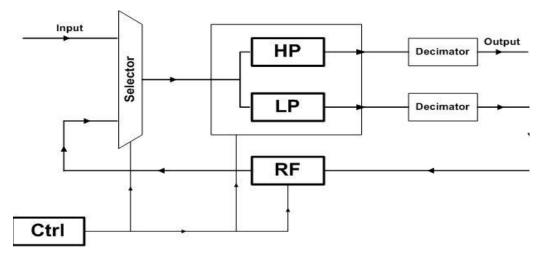

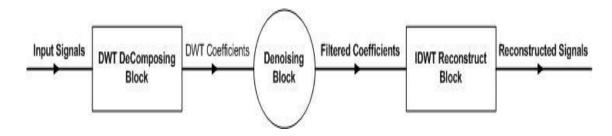

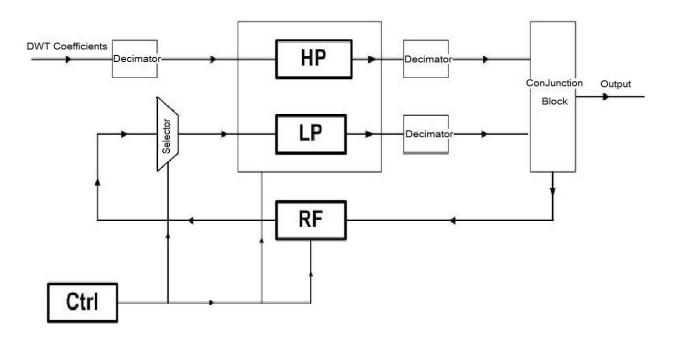

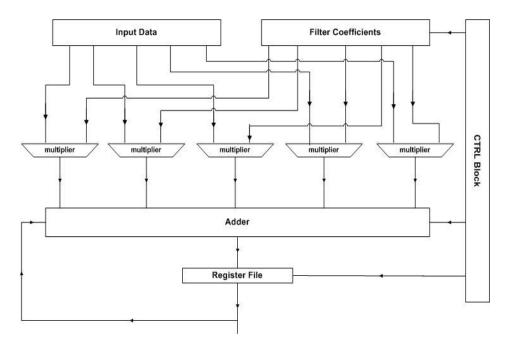

**Chapter 5**: This chapter gives the details of the hardware implementation of the proposed system. At the beginning of the chapter the hardware structure is introduced. The system is composed of two major functions: Adaptive Noise Canceller (ANC) and target Motion Estimation (TME). The chapter introduces the implementation of both functions sequentially as well as the presentation of hardware implementation; simulation results are presented to justify design alternatives.

**Chapter 6**: The chapter presents the testing environment of the proposed sonar detection system. The hardware platform is introduced and details of the platform are given. Afterwards two different tests, single target detection and multiple target detection, of the proposed system on a hardware platform are described. The test results are used to evaluate the performance of the proposed system.

**Chapter 7**: The high-level simulation results, hardware application simulation results and the testing results on the hardware platform are examined and compared to characterize the performance of the system developed in this work.

**Chapter 8**: presents conclusions and suggestions for future work.

# 1.4 Contributions made by this Thesis

Few studies on actual hardware implementation of active sonar system have been mostly theoretical; this work has not only developed new target detection techniques but also demonstrated their real world potential using generated, as well as real, sonar data.

A principal contribution of this project is a demonstration that the continuous wavelet transform can be used in a sonar system to detect targets with a computation time that is applicable for real time systems. Continuous Wavelet Transform is well known for its high resolution as well as its high data redundancy and computation complexity. It reduces the chances of CWT utilization in real applications. With the proposed system in this thesis, the computation complexity is reduced to a level that makes the real time implementation is possible.

An Adaptive-Network-based Fuzzy inference System (ANFIS) is adopted in the proposed system as the algorithm for Adaptive Noise Canceller. ANFIS is utilized in various theoretical systems for its ability to work with the chaotic nature of the

impulsive noise, but seldom in real work due to its heavy computation load. Implementations of ANFIS on a single FPGA chip in this project demonstrated the possibility to employ this algorithm in real applications, even in real time under certain circumstances. The hardware working frequency is increased so that in a unit time the hardware can complete more computations and therefore reduce the processing time. The FPGA has more hardware resources such as multipliers and adders, making parallel computation more applicable.

The combination of local optimum search algorithm and Continuous Wavelet Transform presented in this thesis is a novel method to reduce the computation complexity of its CWT. The simulation results also show this method is able to reduce the computation load of CWT by 8 to 10 times and enable CWT to be utilized in real time applications.

A final contribution is the publication of a large number of real sonar results for target detection using a number of data sets contributed by the Defense Science and Technology Laboratory (DSTL) of Ministry of Defense (MOD) in the project. Many previous studies into wavelet-based sonar system have been mostly theoretical, and have not concentrated on forming images with real sonar data.

Publications resulting from this work are listed below:

Sheng Cheng, Chien-Hsun Tseng and Marina Cole, "An Efficient and Effective VLSI

Architecture for a Wavelet-based Broadband Sonar Signal Detection System", ICECS

07, pp593-596

2. Sheng Cheng, Chien-Hsun Tseng and Marina Cole," A Novel FPGA Implementation of a Wideband Sonar System for Target Motion Estimation", ReConfig'08, Mexico

# **CHAPTER II**

# LITERATURE REVIEW

This chapter will introduce previous research on active sonar systems and outline the rationale behind techniques adopted in this thesis. First the background of the underwater sonar system is described, and research in this area will be briefly introduced. Then the reason why an adaptive noise canceller is proposed in the system is demonstrated and the chosen algorithm for it is presented. Finally an investigation in the wavelet transforms area is described to demonstrate the suitability of the continuous wavelet transform for application in an active sonar system.

# 2.1 Underwater Sonar Detection

Sight and hearing are two primary sources we use to get information from surroundings. The two types of radiant energy related to these two senses, sound and light travel well in air. However, in an underwater environment, sound propagates over longer distances than any other source of radiant energy [1]. Therefore, SOund NAvigation and Ranging (SONAR) systems are primarily adopted for gathering information in an underwater environment. Systems that use acoustic echoes for detection are known as

sonar systems [2].

The detection, classification and localization performance of sonar systems depends on the environment and the receiving equipment, as well as the transmitting equipment.

# 2.1.1 Sound propagation

Sonar operation is affected by variations in sound speed, particularly in the vertical plane. Sound travels slower in fresh water than in sea water, though the difference is small. The speed is determined by the water's bulk modulus and mass density. The bulk modulus is affected by temperature, dissolved impurities (usually salinity), and pressure. The density effect is small. The speed of sound is approximately:

$(4388 + (11.25 \times \text{temperature (in } \mathbb{F})) + (0.0182 \times \text{depth/0.3048}) + \text{salinity (in parts-per-thousand)})/0.3048.$

This empirically derived approximation equation is reasonably accurate for normal temperatures, concentrations of salinity and the range of most ocean depths.

Water pressure also affects sound propagation: higher pressure increases the sound speed, which causes the sound waves to refract away from the area of higher sound speed. The mathematical model of refraction is called Snell's law [3].

If the sound source is deep and the conditions are right, propagation may occur in the 'deep sound channel'. This provides extremely low propagation loss to a receiver in the channel. This is because of sound trapping in the channel with no losses at the boundaries. Similar propagation can occur in the 'surface duct' under suitable conditions. However in this case there are reflection losses at the surface.

In shallow water propagation is generally by repeated reflection at the surface and bottom, where considerable losses can occur.

The energy of sound will be absorbed as long as it travels through sea water. Sound propagation is affected by absorption in the water itself as well as at the surface and bottom. Absorption of low frequency sound is week. Viscosity is the main cause of sound attenuation at high frequency in sea water. Sound may be absorbed by losses at the fluid boundaries. Near the surface of the sea losses can occur in a bubble layer or in ice, while at the bottom sound can penetrate into the sediment and be absorbed.

# 2.1.2 Scattering

The major difficulty in detecting a specific target underwater is the presence of other objects. When the pulse is emitted into the water, it not only strikes the target but also other objects underwater. The pulse is reflected off these objects and is retrieved by the receiver. The signal from these objects underwater is known as reverberation and the objects are called scatters [4, 5].

The scattering of sound underwater can be described either by Rayleigh's law or by geometrical acoustic scattering [6]. Rayleigh scattering (named after the British physicist Lord Rayleigh) is the elastic scattering of electromagnetic radiation by particles much smaller than the wavelength of the pulse, which may be individual atoms or molecules. Rayleigh scattering is a function of the electric polarizability of the particles. Therefore, Rayleigh's law only applies when the size (d) of particles is much smaller than the wavelength ( $\lambda$ ) of the incident sound. Geometric acoustic scattering, on the other hand, is

valid when d is much larger than  $\lambda$ . Therefore, when d<< $\lambda$ , the pressure of scattered sound is proportional to the square of acoustic frequency and to the volume of scatterer, regardless of its shape (Rayleigh's law). If d is similar to  $\lambda$ , the pressure of scattered sound is combination of functions of sound frequency, acoustic properties of scatterer and characteristics of the underwater medium or boundaries. However, if d>> $\lambda$ , the scattering of sound is only dependant on acoustic properties of scatterer and its cross-section, not on sound frequency anymore (Geometrical acoustic scattering).

This situation leads to the development of two different approaches for reverberation modeling underwater: cell-scattering and point-scattering models.

In cell-scattering models, it is assumed that the scatterers are uniformly distributed through the ocean. The ocean then can be divided into cells, each containing a large number of scatterers. Summing up the contribution each cell makes together leads to the reverberation form.

In point-scattering models, the scatterers are assumed to be randomly distributed throughout the ocean. The reverberation waveform is calculated by summing the echoes from each individual scatterer. It is a statistical based approach.

Simplifying assumptions are often necessary to make reverberation models feasible. "These assumptions may seem to set the results to pure idealized situations, however, the resulting expressions for reverberation have been found to be practical for many sonar design and predictions"[6]. The assumptions are [7]:

1. Straight-line propagation paths. All sources of attenuation other than spherical

spreading are neglected.

- 2. A pulse length short enough to ensure propagation effects over the range extension of the elemental volume or area can be neglected.

- An absence of multiple scattering. (I.e. the reverberation produced by reverberation is negligible)

In cell-scattering models, the reverberation usually is combined with three scatterings: surface scattering, volume scattering and bottom scattering, which are reverberation from ocean surface, scattering in ocean and ocean bottoms. Detail equations can be found in [6]. Cell-scattering is widely used in sonar modelling, and lots of experimental models are built based on it, such as DOP (Doppler Content), BAM (bidirectional associative memory), MAM (monostatic associative memory), PERVE (Tappert's PE Reverberation model), etc [6].

Point-scattering models are based on a statistically approach which assumes the scatterers are randomly distributed in the ocean. The scatters from each individual object are then summed up to compute the reverberation level. It is not widely used as cell-scattering models; however, when processing scatterers with dimensions comparable to the acoustic wavelength, the point-scattering models are probably preferred alternative. Due to the use of modem, high resolution, wideband sonar systems, the characteristics of individual scatterers become increasingly important. Therefore, non-Rayleigh point-scatter models attract more and more researchers and lots of researches have been done in this area such as [8-11], etc.

Reverberation models are typically combined with environmental, propagation, noise and signal processing models to form a new class of models referred as active sonar models [6]. Reverberation and ambient noise are usually jointly considered as background noise against target pulse which must be detected in sonar model evaluation. It is important to understand which of them, ambient noise or reverberation, is most responsible for creating the interference background.

#### 2.1.3 Sonar Detection System

Sonar systems fall into two categories known as passive and active sonar systems [3, 4]. Passive sonar systems detect objects by detecting the acoustic echoes emitted from the object being looked for. In the case of active sonar systems, a pulse whose characteristics are known is transmitted. The pulse is then reflected back to the transmitter from the target to be detected. From the returned pulse it is possible to compute the range and speed of the target.

Sonar systems have been used for more than a century to detect underwater objects using sound. Probably the first recorded use of the sonar principle (although not referred to as sonar at the time) was by Leonardo da Vinci in 1490:

If you cause your ship to stop, and place the head of a long tube in the water and place the outer extremity to your ear you will hear ships at a great distance.

The system described can be considered to be a very basic passive sonar system.

Although simple, the system has a number of important features such as covert operation (the system is passive) and, with user training, the ability to classify target

type (a large ship will sound different to a small boat). The design of this system is based purely on empirical observation. Given a modern knowledge of the physics of the propagation of sound through water, Leonardo da Vinci may have been able to predict the likely sounds of different vessels under different ocean conditions.

Issac Newton made the first theoretical prediction of the speed of sound in water in Book II of the *Principia*, showing that the speed of sound is related to the density of the medium through which it is travelling.

Due to the development of transducter technology after World War II, which converts underwater acoustic energy into electrical signals (and vice versa), and the ability to implement signal processing algorithms with digital computers, the use of underwater sound for target detection has also been progressed [1].

The major problem for sonar systems is to identify pulse bounced back from target within all received pluses containing background noises, which includes reverberation from scatterers in ocean, ocean surface and bottoms, and ambient noises [6]. Usually the amplitude of background noises is much larger than pulse reflected back from the target, which is the signal the system must detect. Therefore it is hard for sonar system to abstract desired signal from received pulses directly. Signal processing algorithms such as convolution, wavelet transform, adaptive noise canceller, etc, is then required to extract desired signal out of received signals.

Digital signal processing algorithms developed fast for active and passive sonar systems since 1960's. Much of the work in 1960's was based on concepts brought by

Vic Anderson such as DELTIC correlator, Digital multibeam steering beamformer [12], and the adaptive array processor[13]. In the 1970's and early 1980's, adaptive and high resolution underwater acoustic signal processing became the focus of research. Works from Howells [14], Anderson [15], Widrow [16], Griffiths [17] etc contributed a lot for the research in this area.

Maximum likehood forms the basis for high-resolution signal processing. Results of work by many authors including Slepian [18], Youla [19] and Schweppe [20] point it out. Tuefs and Kumaresan [21-24] reduce computation load for extract exact maximum likehood by implicit substitution of linearly entering parameters.

Driven by tremendous technical development on computation capacity and speed, which allows computationally intensive techniques to be implemented, research on adaptive signal processing algorithms to sea test data, wideband processing on both active and passive sonar, detection on transient signals with unknown parameters, reverberation processing and etc developed very fast since 1980's to present.

The use of continuous wavelet transforms to detect transient signals, proposed in this project, in the application of active sonar system has been investigated by various researchers such as A.C. Dubey, C.Yan and M.R.Azimi-Sadjadi[27] and Lora.G.Weiss [28,29]. The work of A.C, Dubey, C.Yan and M.R.Azimi-Sadjadi investigated the application of the Discrete Wavelet Transform (DWT) [27]. They used an application known as wavelet shrinkage which proposes that if a signal f(t) contains the echo of a target (i.e. target to be detected) and environment noise, the noise will contribute to

most of the wavelet coefficients while the target echo contributes to only a few coefficients. Therefore by making the smaller coefficients zero in an appropriate method, the noise can almost be eliminated whist preserving the target echo. The results from their work showed that this method worked well but as they stated and as seen in their work the method only works well in environments where the effects of reverberation are not severe.

Their subsequent work using DWT in underwater acoustic signal recognition is reported in [30, 31, 32]. Their work shows the wavelet transform is a powerful method for underwater sonar recognition.

The work carried out by Lora.G, Weiss [29] is very beneficial since it looks at the application of wavelets to wideband processing. Although her work does not focus directly on their applications in active sonar it provides a good introduction into wideband signals and their properties and at the same time shows how wavelets can be easily fitted into this model. In her work a wideband model is used to model the target echo and good insight to the effects of the target echo shift when it is modelled on the wideband equation is given. The paper investigates both active and passive methods of sonar and describes both deconvolution and convolution in order to determine the motion parameters of several targets. The method presumed that there is more than one target to be detected and a cross wavelet transform is performed in order to gain and estimate the parameters of the targets. Moreover, in this paper the Continuous Wavelet Transform is preferred to the Discrete Wavelet Transform due to its ability to provide

high resolution in both the frequency and time domains.

Though the work on the application of wavelets to active sonar is still not well established there has been a number of works carried out on target detection of underwater objects. One of the well established processes of detecting targets can be accredited to Harry L.Van Trees [33]. He proposes the idea of a correlation matrix also referred to as a correlation process. However, the methods seem complicated and cumbersome, the heavy computation load makes it is hard for real-time application.

#### 2.2 Wavelet Transform

Wavelet transform is a mathematical method to decompose signals into different frequency components, and then study each component with a resolution matched to its scale. The word wavelet means "small wave", referring to the fact that the window function is of finite length [32]. Wavelet theory is seen as an extension of Fourier analysis.

The basic idea of wavelet transform is to analyze target signals according to scale. It uses functions which satisfy certain mathematical requirements to represent target signals. However, the representation methods using superposition of certain functions which is used in wavelet transform is not original. In the early 1800's, Joseph Fourier had already discovered that he can superpose sines and cosines to represent other functions and this representation method is now well known as the Fourier Transform. The wavelet Transform is similar to the Fourier Transform in the sense that both of them decompose

the target signals into their constituent parts for analysis. Whereas the Fourier Transform breaks signals into sine waves and cosine waves, the Wavelet Transforms breaks signals into their wavelets, the dilated and translated versions of mother wavelet. However, when compared with Fourier Transform, wavelet transform can provide the possibility to acquire a 2D plot of the time and scale (1/Frequency) information in a signal via translations and dilations of the mother wavelet. Thus it has advantages over traditional Fourier methods in analyzing physical situations where the signal contains discontinuities and sharp spikes that need to be localized in time. Wavelet transform is widely used in the fields of data compression, signal and image processing, acoustics, radar, human vision, etc. O. Rioul et .al give more details about wavelet transform features in [35, 36].

A wavelet w is a function with zero average:

$$\int_{-\infty}^{+\infty} w(t)dt = 0, \qquad (2.1)$$

which is dilated with a scale parameter s, and translated by u:

$$W_{u,s}(t) = \frac{1}{\sqrt{s}} w(\frac{t-u}{s}).$$

(2.2)

The wavelet transform of f (t) at the scale s and position u is computed by correlating f (t) with a wavelet atom [14]

$$Wf(u,s) = \int_{-\infty}^{+\infty} f(t) \frac{1}{\sqrt{s}} w^* (\frac{t-u}{s}) dt.$$

(2.3)

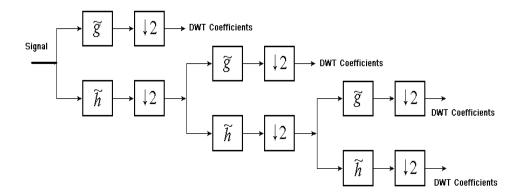

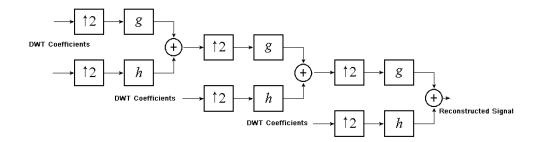

O. Rioul and M. Vetterli introduce the DWT (Discrete Wavelet Transform) and CWT (Continuous Wavelet Transform) in [35], which are two different kinds of wavelet transform. In DWT, the signal is broken into dyadic blocks where only specific scale

values can be used [35]. In the CWT implementation, the discrete sample data is also used, however the scaling range can be defined as any value by the user, thus giving much better resolution for target analysis. Also the CWT is shifted along the analyzed signal smoothly and therefore the CWT is highly redundant in both time and scale. The trade off is between improved resolution and increase in computational time and required memory to calculate the redundant wavelet coefficients.

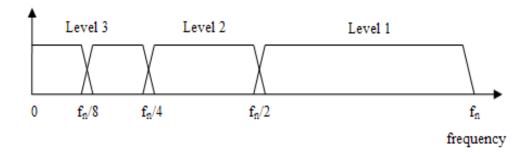

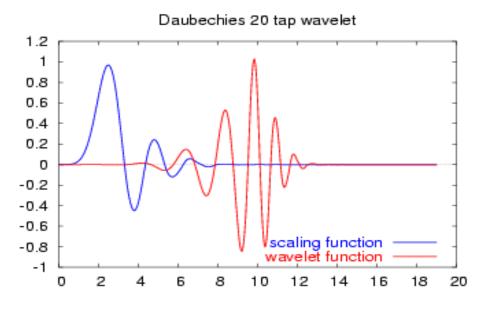

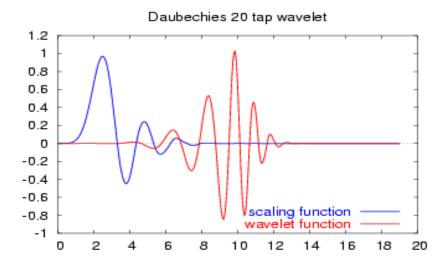

The main idea of the CWT is to obtain time-scale digital signals using digital filter techniques by correlating wavelets at different scales with target signals at the scale to measure the similarity. The Continuous Wavelet Transform is computed by changing the scale of the analysis window, shifting the window in time, multiplying by the signal, and integrating over all times as shown in Eq. 2.3 [37]. In order to implement the CWT by computer methods, discretely sampled data are used for CWT. In this case, filters of different cutoff frequencies are used to analyze the signal at different scales. Theoretically researchers can obtain any scale they want by using the CWT; however this will also bring heavy computation loads. CWT provides very fine details of target signals but in some applications not all of them are needed. The discrete wavelet transform (DWT), on the other hand, provides sufficient information both for analysis and synthesis of the original signal, with a significant reduction in the computation time [38]. Generally DWT coefficients are samples from the CWT in dyadic grids. i.e.,  $s_0 = 2$  and  $u_0 = 1$ , yielding  $s=2^{j}$  and  $u=k*2^{j}$ , where j is usually called the number of octave. Also, DWT is considered easier to implement when compared to CWT.

Fast wavelet Transform algorithms are widely investigated to reduce the computation complexity of WTs (Wavelet Transforms) and to make the WT implementations realistic. The Mallat Algorithm [40], also known as PA (Pyramid Algorithm), is one of the best fast DWT algorithms and is widely adopted for orthogonal wavelets. In this algorithm, the DWT coefficients at any stage can be calculated from the DWT coefficients of previous stages as follows:

$$W_{L}(n,j) = \sum_{m} W_{L}(m,j-1)h(m-2n)$$

(2.4)

$$W_h(n,j) = \sum_{m} W_L(m,j-1)g(m-2n)$$

(2.5)

where  $W_L(p,q)$  and  $W_h(p,q)$  is the pth scaling coefficient and wavelet coefficient at qth stage, respectively, and h(n), g(n) are the dilation coefficients corresponding to the scaling and wavelet functions, respectively [39]. In practice, h (n) and g (n) represent a low pass and high pass filter, respectively. The computation complexity is O (N) each octave instead of  $O(N \log N)$  each octave. Recursive Pyramid Algorithm (RPA) is introduced in [40]. This algorithm reduces the words of storage from O (N) to  $L(\log N-1)$  when compared with traditional PA, where L is the length of wavelet filter. This is achieved by reformulating the classical Pyramid Algorithm. The order of N outputs is rearranged so that an output can be scheduled at the earliest time slot. Several VLSI architectures for 1-D DWT based on RPA are proposed in [41], which include systolic, semisystolic and RAM-based architectures. The difference between these architectures is only in their routing network architectures. Also M-band DWT and 2-D DWT architecture are also discussed in the paper. VLSI architecture for 2-D DWT which

is also based on RPA is proposed in [42]. However, Several VLSI architectures which are lifting-based are discussed in [43] [44]. The lifting-based architecture uses less hardware resources than RPA but have relatively long critical path. A detailed analysis of different VLSI architectures for 1-D and 2-D DWT is given in [45].

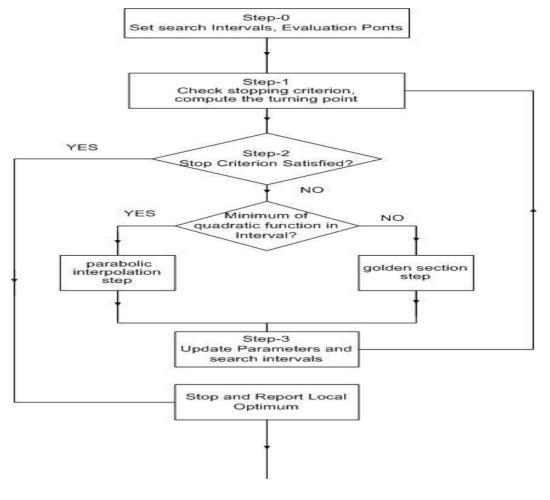

Though the Mallat Algorithm is very successful in DWT, it is not perfect for CWT. First of all, it can only be used for WT on a dyadic grid, but the scaling and shifting of CWT could be any value. Secondly, the translation invariance is lost due to the decimation in the Mallat Algorithm. Thirdly, the decimation (reduction in the number of samples) reduces the redundancy provided by CWT, which is also used as finer details of the target signal. In [46] a fast WT algorithm, the "A Trous" algorithm is proposed. This algorithm is proposed for DWT at first, but is widely used as a basis for fast WT transforms of CWT. It is similar to the Mallat Algorithm but with no decimation after filters at each octave and the lowpass filter should be an a trous filter by satisfying  $f_{2k} = \partial(k)/\sqrt{2}$ . Thus the product of this algorithm is 2N, which is the double the size of the input signal. Reorganization of the "A Trous" computational structure is proposed in [47] and is used for CWT. The filters which are used in "A Trous" are usually Lagrange interpolators [48]. However, there is no evidence that this filter is most suitable for all applications. Thus the filter design for "A Trous" is also an interesting topic to investigate. K.C.Ho and Y.T.Chan proposed several filters for "A Trous" in [49] and give a detailed comparison in [50]. However, generally the octave-by octave computation of the DWT is not enough in signal analysis. A method which can provide better resolution

is proposed in [51] [52]. It over samples the discretization to obtain "M voice per Octave" [51] [52], that is  $s = 2^{j+m/M}$  instead of  $2^j$ , m=0, 1...M-1, where m is called "voice", and this is achieved by applying octave-by-octave computation M times with different dilated wavelets

$$2^{-(j+m/M)/2} \partial (2^{-(j+m/M)} (t-k2^{j})),$$

$$j,k \in \mathbb{Z}, m = 0,..., M-1$$

(2.6)

Obviously this method requires about M times the computation load of the octave-by-octave algorithm. In fact precision and computation workload is always a trade-off.

Another CWT algorithm called the *Bertrands and Ovarlez* algorithm is proposed in [53]. It uses the scaling property of the wavelet instead of the convolution form. It needs pre-computation of the whole Fourier Transform of the input signal, and it is difficult to estimate the approximation error. To overcome the disadvantage of this algorithm that it is not suitable to handle continuous data flow, a variation of the *Bertrands and Ovarlez* algorithm is also introduced in [53]. Assume the signal and wavelet are casual, (i.e., supported by t>=0), and assume  $T=\ln t$ , One can obtain a convolution in  $a=\ln a$ :

$$CWT\{x(t); s, u\} = \int e^{T/2} x(e^{T} + b)e^{(T-a)/2} \partial^{*}(e^{T-a}) dT$$

(2.7)

In this algorithm the computation load will be higher than in the algorithms described previously. But on the other hand, it gives a required resolution of ln a. This property is useful if high resolution is needed in applications.

M. Unser et al introduce another CWT algorithm which provides fast CWT in integer

scales [48] [54]. In this method the input signal and the wavelet are represented by polynomial splines. A combination of moving sum and zero-padding filters is adopted in this method and a computation complexity of O (N) per scale is provided by this algorithm. However, scales in integer may not be sufficient for some applications which require very good resolutions.

In [55] two architectures for 1-D CWT are introduced, one is a parallel filter architecture, and the other is a Single Instruction Multiple Data (SIMD) linear array. These two architectures are also discussed in [56], which also provides a detailed comparison for several other architectures of 1-D CWT and 2-D CWT implementations. From these comparisons it is hard to tell which architecture has the best performance. The decision of which implementation architecture will be used bases on the specific application and requirements.

Most of the architectures mentioned above can be categorized into convolution-based, lifting-based, and B-spline based. RPA and "A Trous" are convolution—based; VLSI architectures mentioned in [43] [44] are based on the lifting-scheme, and M. Unser proposes a B-spline based architecture in [48] [54]. The Table 1 below shows the performance of different algorithms and VLSI architectures mentioned above. The contents of the tables are based on 1-D Wavelet transforms on dyadic grids. The table shows that B-spline based architectures can provide the smallest area, and lifting-based algorithms can use fewest registers with a relatively short critical path. However, the hardware complexity of convolution based architecture is better than those two. It shows

the tradeoff between speed, hardware complexity and area. For different applications and requirements the most suitable architecture will be different. Using different methods such as introducing M-voice in each octave or represent the input signal and wavelets in different splines, a better resolution and finer details can be achieved. The exact expressions of critical path or area will differ when these modifications are made, but the relations of these architectures will not change.

|                          | Convolution Based |                  | Lifting-based          |            | B-Spline based     |               |

|--------------------------|-------------------|------------------|------------------------|------------|--------------------|---------------|

| Implementation<br>Method | Parallel Filter   | Serial<br>Filter | Conventional           | Flipping   | Parallel<br>Filter | Serial Filter |

| Critical Path            | Tm+(log2F)Ta      | Tm+2Ta           | F/2(Tm+2Ta)            | Tm+(F/2)Ta | Tm+(F/2+ log2F)Ta  | Tm+(F/2)Ta    |

| Registers                | F                 | FH+FG            | F/2                    | F/2        | FH+FG              | FH+FG         |

| Multipliers              | FH+FG             |                  | (FH+1)/2 +( FG+1)/2 +3 |            | (FH+FG)/2          |               |

| Adders                   | FH+FG-2           |                  | (FH+1)/2 +( FG+1)/2 +1 |            | 3(FH+FG)/2-2       |               |

Table 1 Approximation of performances of 1-D WT algorithms [50]

- F<sub>H</sub> and F<sub>G</sub> are filter lengths of high-pass filter and low-pass filter, respectively.

- T<sub>m</sub> and T<sub>a</sub> are logic delays of multipliers and adders, respectively

- $F = max (F_H F_G)$

There are various forms of non-orthogonal wavelets from the well known Morlet wavelet, Car wavelet, Difference of Gaussian wavelet, and Mexican hat wavelet [57]. The choice of wavelets is vast.

Many functions can be used as wavelets as long as they satisfy two conditions, which are:

- 1) The function is continuous and has an exponential decay;

- 2) The integral of the function is zero, i.e., shown in Equation 2.1.

These conditions can be easily satisfied and therefore the choice of mother wavelet can be very flexible and allow users to define their own wavelets to suit their application environment best. Research on wavelets applications on active sonar signal processing has been carried out, but most of them investigate the Discrete Wavelet Transform, which has very limited success in reverberation limited environments [27]. Therefore, the Continuous Wavelet Transform is chosen for this project, enabling motion parameters extraction of the target including range and velocity to be assessed in this research.

#### 2.3 Adaptive Noise Canceller

As mentioned previously in Chapter I, the motivation of this project is to build an active sonar system which is able to identify accurate motion information of targets from received echoes and in a reverberation-limited environment. The received echoes contain the target echo as well as noise, which normally are composed of reverberation noise and white Gaussian noise. Convolution based digital signal processing algorithms can give satisfactory results for cancelling noise effects from white Gaussian noise, but the performance is limited regarding to reverberation noises due to the similarity between target echo and reverberation noises. Therefore, algorithms which are efficient on removing reverberation noises are required in order to minimize the effect of noise during target extraction. Therefore, Adaptive Noise Cancelling algorithm is introduced

in the proposed project.

Although various work have been done on ANC, very few researches has been done on ANC implementation on underwater sonar detection. Alexandrou and De Moustier [82] used Least-Square Lattice filter to reject sea beam sidelobe interference in building reference models. Lawson [83] investigated the performance of a simple ANC in narrowband signal detection in reverberation-limited environment by using Least-Squares Lattice filter again.

The conventional way to detect a target buried in additive noise is to feed whole signals into a filter which is designed to suppress noise while leaving the target relatively unchanged [58-62]. The filter could be fixed or adaptive. The fixed filter is build based on prior knowledge of the target and noise; the adaptive filter on the other hand, can adjust its parameters automatically, and with little or no prior knowledge of target or signals [63]. Adaptive noise cancelling has been successfully applied to a number of additional problems, including some aspects of electrocardiography, to the elimination of periodic interference in general [64], and to the elimination of echoes on long-distance telephone transmission lines [65, 66].

For white Gaussian Noise, Adaptive Noise Cancelling with linear filtering can give a satisfactory performance on removing it [67-69]. However, for non-linear noises like reverberation noise, an Adaptive Noise Canceller with linear filtering is no longer effective to suppress noise and keep the target echo unchanged at the same time. Therefore, an Adaptive-Network-based Fuzzy Inference Systems (ANFIS) is introduced

in the system described in this thesis due to its ability of working with the chaotic nature of the impulsive noise. It is the combination for Fuzzy logic and neural network and it has advantages of both techniques. Therefore, more accurate results are expected from ANFIS than least-square Lattice filters used in [82] [83].

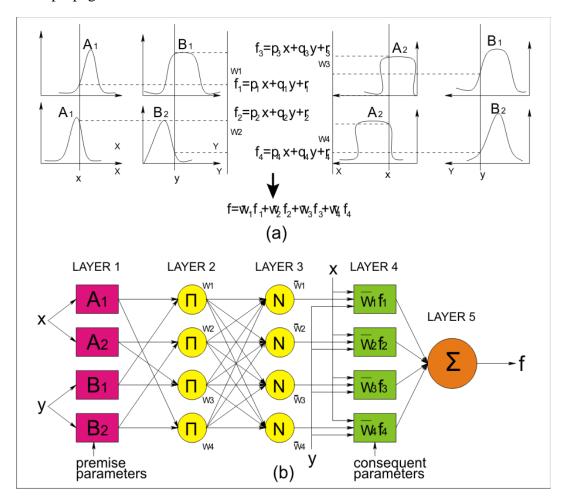

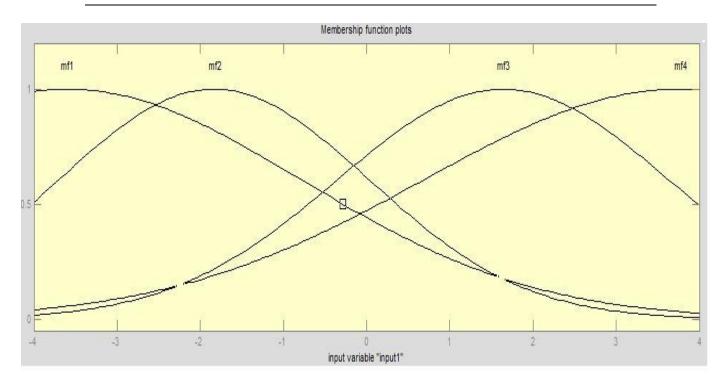

An ANFIS is proposed by J.S. Roger Jang in [70, 71]. It is a combination of Fuzzy inference system and adaptive networks. It proposes a class of adaptive networks which are functionally equivalent to fuzzy inference systems. It serves as a basis for constructing a set of fuzzy if-then rules with proper membership rules to generate the stipulate input-output pairs [70].

Fuzzy if-then rules or fuzzy conditional statements are expressions of the form IF A THEN B, where A and B are labels of fuzzy sets [72] characterized by appropriate membership functions. Due to their concise form, fuzzy if-then rules are often employed to capture the imprecise modes of reasoning that play an essential role in the human ability to make decisions in an environment of uncertainty and imprecision.

In 1985 Takagi and Sugeno propose a non-linear fuzzy inference system, which is known as Takagi and Sugeno's model [73]. It combines the advantage of both a fuzzy inference system and a neural network to improve the traditional fuzzy inference system's design. Traditionally in fuzzy inference system the parameters are required to be updated manually to minimize error rate. In Takagi and Sugeno's model, the parameters are undated automatically through a hybrid learning algorithm [73].

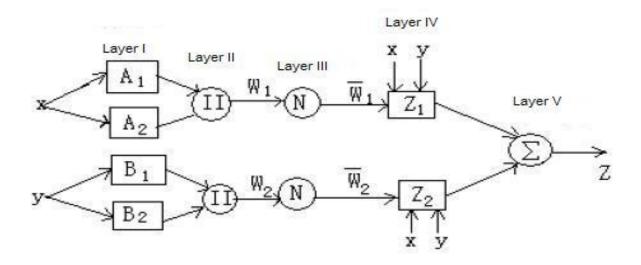

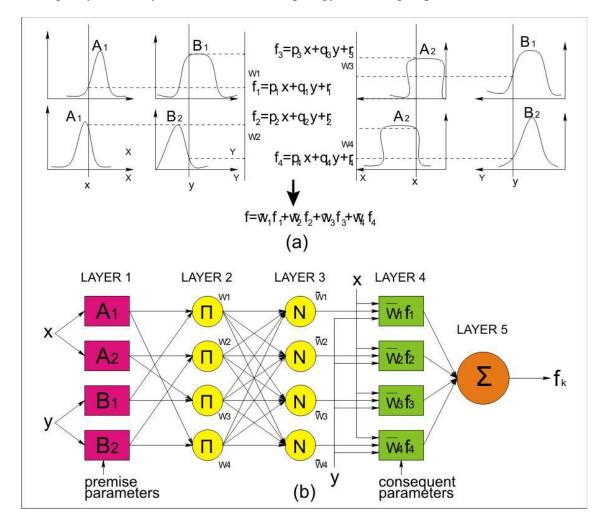

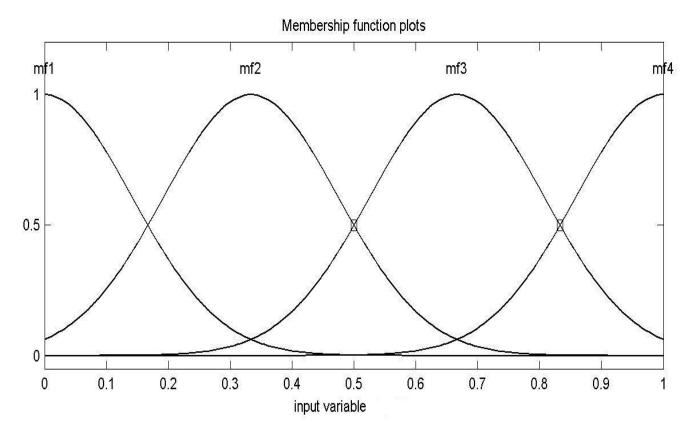

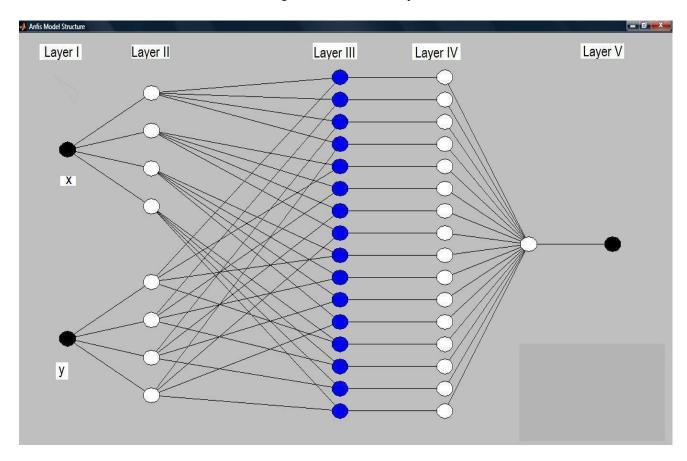

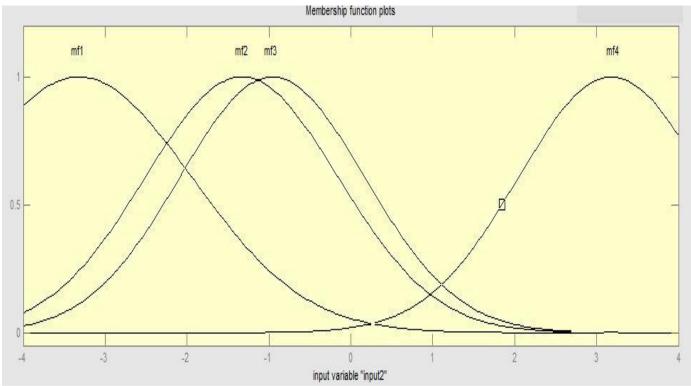

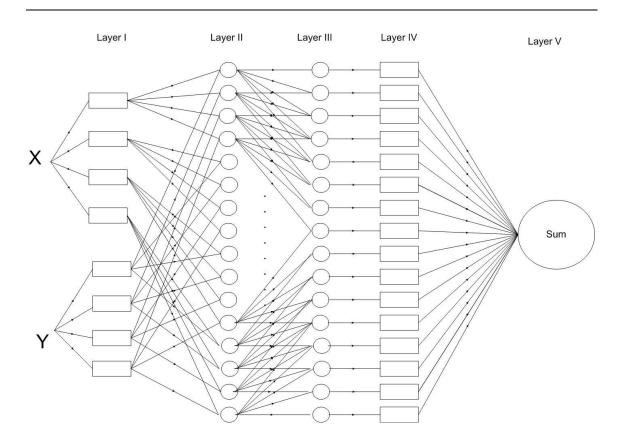

ANFIS represents Sugeno & Tsukamoto fuzzy models based on neural network, which is a multi-layer forward pass network, as shown in Fig 2.1:

Fig 2.1 ANFIS network Structure

Fig 2.1 shows a two-input and 2 membership for each input ANFIS structure. There are five layers in the system. X and Y represent input data for the system and Z is the estimate output of ANFIS. Ai and Bi represents membership functions under different parameters. The details of ANFIS will be described in Chapter III.

ANFIS is capable to provide satisfactory noise reduction performance under a severe non-linear noisy environment and is adopted in many areas such as noise cancelling, signal analysis, behaviour prediction or modelling, etc [74-81]. However, most of them only investigate the implementation of ANFIS theoretically. Also little research has been done on utilizing ANFIS in an active sonar system. Therefore the system proposed in this thesis combing ANFIS along with the Continuous Wavelet

Transform to realize an active sonar system on a hardware platform is a new challenge and an exploration in a new direction.

### 2.4 Conclusion

The history of underwater sonar system is introduced in this chapter, and the development of researches on wavelet theory is given. In literature the continuous wavelet transform is shown to have an advantage in sonar target detection for its capability of providing high resolution analysis in both frequency domain and time domain. Then research relative to implementation of wavelet transform is also reviewed. It shows that due to the high computation redundancy, Continuous Wavelet Transform is seldom adopted in practical applications. Therefore, the simplification of the computation process for Continuous Wavelet Transform is the first and new challenge in the proposed system. The Adaptive Noise Canceller is also introduced into the proposed system to minimize the noise effect for target detection. The development of Adaptive-Network-based Fuzzy Inference Systems used as Adaptive Noise Canceller is given afterwards. Literatures shows ANFIS is a powerful way to reduce noises in sonar signals, however, the efficiency of implementation of ANFIS is also a major concern in practical applications. All the relative research works indicates the proposed active sonar system is a new challenge to solve.

#### References

- Underwater Acoustic Signal Processing Technical Communite,"The Past, Present and Future of Underwater Acoustic Signal Processing", IEEE Signal Processing Magazine, pp21-51, July, 1998.

- H.Naparst,"Dense Target Signal Processing", IEEE Trans. Inform Theory, Vol 37(2), pp 317-327, 1991.

- 3. Andrew S. Glassner, "An Introduction to Ray Tracing". Morgan Kaufmann, 1989

- William S. Burdic, "Underwater Acoustic System Analysis", Prentice Hall, Second Edition, 1991

- 5. Pierre Faure,"Theoretical Model of Reverberation Noise", The Journal of the Acoustical Society of America, Vol 36(2), pg 259-266, 1964

- Paul C. Etter, "Underwater acoustic modeling and simulation", Spons Architecture

Price Book, 2003

- 7. Robert J. Urick," Principles of Underwater Sound", McGraw-Hill, 1983

- 8. Hodgkiss, W., Jr.; Alexandrou, D," Under-ice reverberation rejection", IEEE Journal of Oceanic Engineering, Volume: 10, Issue 3, 1985

- 9. Alexandrou, D, C. de Moustier, G. Haralabus, "Evaluation and verification of bottom acoustic reverberation statistics predicted by the point scattering model", The Journal of the Acoustical Society of America Vol.91, No.3, March 1992

- 10. Abraham, D.A, "Choosing a non-Rayleigh reverberation model", OCEANS '99 MTS/IEEE, Vol 1, Pg 284 288, 1999

- 11. Lew, H,Drumheller, D.M," Estimation of non-Rayleigh clutter and fluctuating-target models", Radar, Sonar and Navigation, IEE Proceedings, Vol 149, Issue 5, 2002, Pg 231 241

- 12. V.C.Anderson, "Digital array phasing", The Journal of the Acoustical Society of America, Vol. 32, pp 867-870, 1960

- 13. V.C.Anderson, "DICANNE, a realizable adaptive process", The Journal of the Acoustical Society of America, vol 45, pp 398-405, 1969

- P. Howells, "Intermediate frequency side-lobe canceller", U.S. Patent NO 3202990,

1959

- 15. V.C. Anderson and P. Rudnick, "Rejection of a coherent arrival at an array", The Journal of the Acoustical Society of America, vol 45, pp 406-410, 1969

- 16. B. Widrow, P.E. mantey, L.J.Griffiths, and B.B. Goode, "Adaptive antenna systems", Proc. IEEE, vol 55, pp 2143-2159, 1967

- 17. L.S. Griffiths, "A simple adaptive algorithm for real-time processing in antenna arrays", Proc. IEEE vol 57, pp, 1696-1704, 1969

- D. Slepian, "Estimation of signal parameters in the presence of noise", IRE Tras.

Inform, Theory, p.68, 1954

- 19. D.C. Youla,"The use of maximum likehood in estimating continuous-modulated intelligence which has been corrupted by noise". IRE Trans. Inform Theory, pp 90-106, 1954

- 20. F.C. Schweppe, "Sensor-array data processing for multiple signal sources", IEEE

- Trans. Inform, Theory, pp 294-305, 1968

- 21. D.W. Tufts and R. Kumerasan, "Improved spectral estimation", Proc. IEEE, vol. 68, pp. 419-420, March 1980

- 22. D.W. Tufts and R. Kumaresan, "Estimation of frequencies of multiple sinusoids: Making linear prediction perform like maximum likehood", Proc. IEEE, vol. 70, pp. 975-989, Sept. 1982

- 23. D.W. Tufts and R. Kumaresan, "Improved spectral resolution II," Proc. ICASSP'80, pp 592-597, 1980

- 24. R. Kumaresan, "Optimal frequency estimation of sinusoidal signals in noise and applications," Master's thesis, Univ. Rhode Island, 1979

- 25. Coates Rodney F,W., "Underwater Acoustic Systems", Macmillan, 1990

- 26. Richard O. Nielsen, "Sonar Signal Processing", Norwood: Artech House, 1991.

- 27. A.C. Dubey, C.Yuan and M.R.Azimi-Sadjadi, "Comparison of two different wavelet-based approaches for target detection in activesonar data", Proceedings of SPIE, vol 3079, pp225-230,1997

- 28. Lora.G, Weiss, "Wavelets and Wideband Correlation Processing", IEEE Signal Processing Magazine, pp 1-32, Jan 1994

- 29. Lora.G.Weiss,et,al.,"Wideband Processing of Acoustic Signals using wavelet

Transform", The Journal of the Acoustical Society of America, vol 96(2), pp 857-866,

1994

- 30. Quinquis, A.; Kalkoff, I.; Rossignol, S.;" Underwater detection of transient magnetic

- signals: an application of wavelet packets", OCEANS '96. MTS/IEEE. 'Prospects for the 21st Century'. Conference Proceedings, Volume 2, pp 919 924 vol.2, 23-26 Sept. 1996

- 31. Chu-Kuei Tu; Yi-Chiu Lin;" Using wavelet packet decomposition technique on fuzzy classify model for underwater acoustic signal recognition", Underwater Technology, Proceedings of the 2002 International Symposium, Page(s):302 306, April 2002

- 32. Fargues, M.P.; Bennett, R.;" Comparing wavelet transforms and AR modeling as feature extraction tools for underwater signal classification", Conference Record of the Twenty-Ninth Asilomar Conference, Volume 2, Page(s):915 919, 1995

- 33. Harry L, Van Trees,"Detection, Estimation and Modulation Theory Part 3", John Wiley and Sons, 1971.

- 34. Albert Boggess, Francis J. Narcowich, "A First Course in Wavelets with Fourier Analysis", Prentice Hall, 2001

- 35. O. Rioul and M. Vetterli, "Wavelets and Signal Processing", Signal Processing Magazine, IEEE, Volume 8, Issue 4, Page(s):14 38, Oct. 1991

- 36. Stephane Mallat, "A Wavelet Tour of Signal Processing", Academic Press, 1997

- 37. Robi Polikar, "The Wavelet Tutorial", http://users.rowan.edu/~polikar/WAVELETS/

- 38. Ho, K.C.; Chan, Y.T, "Filter design and comparison for two fast CWT algorithms", IEEE Transactions on Signal Processing, , Volume 47, Issue 11, Page(s):3013 3026, 1999

- 39. Aleksander Grzeszczak, Mrinal K. Mandal, Sethuraman Panchanathan and Tet Yeap,

- "VLSI Implementation of Discrete Wavelet Transform", IEEE Transactions on Very Large Scale Integration (VLSI) SYSTEMS, VOL. 4, NO. 4, 1996

- 40. M. Vishwanath, "The recursive pyramid algorithm for the discrete wavelet transform", IEEE Transactions on Signal Process, Vol. 42, no.3, pp. 673-677, Mar. 1994

- 41. M. Vishwanath, R.M. Owens, M.J.Irwin, "VLSI Architectures for the Discrete Wavelet Transform", IEEE trans. Circuits and Systems-II: Analog and Digital Signal Processing, Vol. 42, No.5, May 1995

- 42. Chien-Yu Chen, Zhong-Lan Yang, Tu-Chih Wang, Liang-Gee Chen, "A Programmable VLSI Architecture for 2-D Discrete Wavelet Transform", IEEE International Symposium on Circuits and Systems, May 28-31, 2000

- 43. Jer Min Joii, Yeu-Horng Shiati, Chin-Chi Liu," Efficient VLSI Architectures For The Biorthogonal Wavelet Transform By Filter Bank and Lifting Scheme", Circuits and Systems, Page(s):529 532 vol. 2, ISCAS 2001

- 44. Chao-Tsung Huang; Po-Chih Tseng; Liang-Gee Chen, "Flipping structure: an efficient VLSI architecture for lifting-based discrete wavelet transform", IEEE Transactions on Signal Processing, Volume 52, Issue 4, Page(s):1080 1089, 2004

- 45. Chao-Tsung Huang, Po-Chih Tseng, and Liang-Gee Chen," Analysis and VLSI Architecture for 1-D and 2-D Discrete Wavelet Transform", IEEE Transactions on Signal Processing, Vol. 53, No. 4, April 2005

- 46. M. J. Shensa, "The discrete wavelet transform: wedding the A trous and Mallat algorithms", IEEE Trans. Signal Processing, vol. 40, pp. 2464-2482, 1992.

- 47. O. Rioul and P. Duhamel, "Fast algorithms for discrete and continuous wavelet transforms", IEEE Trans Information Theory, vol. IT-38, pp. 569-586, 1992.

- 48. M. Unser, "Fast Gabor-like windowed Fourier continuous wavelet transforms," IEEE Signal Processing Lett., vol. 1, pp. 76–79, May 1994.

- 49. Ho, K.C.; Chan, Y.T, "Optimum filter design for the A trous algorithm",

Time-Frequency and Time-Scale Analysis, 1998. Proceedings of the IEEE-SP

International Symposium, Page(s):125 128, 1998

- 50. Ho, K.C.; Chan, Y.T, "Filter design and comparison for two fast CWT algorithms", IEEE Transactions on Signal Processing, Volume 47, Issue 11, Page(s):3013 3026, Nov. 1999

- 51. I. Daubechies, "The wavelet transform, time-frequency localization and signal analysis," IEEE Transactions on Information Theory, vol. 36, pp. 961-1005, Sept. 1990.

- 52. J. M. Combes, A. Grossmann, Ph. Tchamitchian, Eds., Wavelets, Time-Frequency Methods and Phase Space, Berlin: Springer, IPTI, 1989.

- 53. J. Bertrand, P. Bertrand, and J. P. Ovarlez, "Discrete Mellin transform for signal analysis," in IEEE Int. Conf. Acoustic., Speech, Signal Processing, Albuquerque, NM, pp. 1603-1606, 1990.

- 54. M. Unser, A. Aldroubi, and S. J. Schiff, "Fast implementation of the continuous wavelet transform with integer scales," IEEE Trans. Signal Processing, vol. 42, pp. 3519–3523, Dec 1994.

- 55. Chaitali Chakrabarti, Mohan Vishwanath and Robert M. Owens," Architectures for Wavelet Transforms", VLSI Signal Processing, VI, Page(s):507 515, Oct. 1993

- 56. Chaitali Chakrabarti, and Mohan Vishwanath, "Efficient Realizations of the Discrete and Continuous Wavelet Transforms: From Single Chip Implementations to Mappings on SIMD Array Computers", IEEE Transactions on Signal Processing, Vol. 43, No. 3, March 1995

- 57. Bruce W.Suter,"Wavelets: what kind of signal processing is that?" Proceeding of SPIE, vol. 2750, Pp118-128, 1996.

- 58. N. WIENER, "EXTRAPOLATION, INTERPOLATION AND SMOOTHING OF STATIONARY

TIME SERIES, WITH ENGINEERING APPLICATIONS." NEW YORK, WILEY, 1949.

- 59. H. BODE AND C. SHANNON, "A simplified derivation of linear least squares smoothing and prediction theory," Proceedings of IRE, vol. 38, pp. 417-425, Apr. 1950.

- 60. R Kalman, "On the general theory of control," in Proc. 1<sup>st</sup> IFAC Congress. London: Buttenvorth, 1960.

- 61. R. Kalman and R. Bucy, "New results in linear filtering and prediction theory", Trans. ASME, Eng., vol. 83, pp95-107, Dec 1961.

- 62. T. Kailath, "A view of three decades of linear filtering theory," IEEE Transactions of Information Theory, vol. IT-20, pp. 145-181, Mar. 1974

- 63. Widrow, B.; Glover, J.R., Jr.; McCool, J.M.; Kaunitz, J.; Williams, C.S.; Hearn, R.H.; Zeidler, J.R.; Eugene Dong, Jr.; Goodlin, R.C.;" Adaptive noise cancelling: Principles

- and applications", Proceedings of the IEEE Volume 63, Issue 12, Page(s):1692 1716, 1975

- 64. J. Kaunitz, "Adaptive filtering of broadband signals as applied to noise cancelling," Stanford Electronics Lab., Stanford Univ., Stanford, Calif., Rep. SUSEL-72-038, Aug. 1972 (Ph.D dissertation).

- 65. M. Sondhi," adaptive echo canceller," Bell System Technical Journal, vol.46, pp497-511, Mar 1967

- 66. J. Rosenberger and E. Thomas, "Performance of an adaptive echo canceller operating in a noisy, linear, time-invariant environment," Bell System Technical Journal, vol. 50, pp. 785-813, 1971.

- 67. Markovich, S.; Gannot, S.; Cohen, I.; "Multichannel Eigenspace Beamforming in a Reverberant Noisy Environment With Multiple Interfering Speech Signals", IEEE Transactions on Audio, Speech, and Language Processing, Volume 17, Issue 6, pp 1071 1086, 2009

- 68. Khorram, S.; Sameti, H.; Veisi, H.; "LP-based over-sampled subband Adaptive Noise Canceller for speech enhancement in diffuse noise fields", 9th International Conference on Signal Processing, Page(s):157 161, 2008

- 69. Himel, T.; Allison, S.; Grossberg, P.; Hendrickson, L.; Sass, R.; Shoaee, H.; "An adaptive noise cancelling system used for beam control at the Stanford Linear Accelerator Center" Proceedings of IEEE workshop on Real time Applications, Page(s):212 215, 1993

- 70. J.-S. Roger Jang, `` ANFIS: Adaptive-Network-Based Fuzzy Inference Systems," IEEE Transactions on Systems, Man, and Cybernetics, Vol. 23, No. 03, pp 665-685, May 1993.

- 71. J.-S. Roger Jang and C.-T. Sun, "Neuro-Fuzzy Modeling and Control", The Proceedings of the IEEE, Vol. 83, No. 3, pp 378-406, March 1995.

- 72. L. A. Zadeh. "Fuzzy sets", Information and Control, 8:338-353, 1965.

- 73. T. Takagi and M. Sugeno, "Derivation of fuzzy control rules from human operator's control actions," in Proc. IFAC Symp. Fuzzy Inform. Knowledge Representation and Decision Analysis, pp. 55-60, July 1983

- 74. Wen Ding; Deliang Liang;" Modeling of a 6/4 Switched Reluctance Motor Using Adaptive Neural Fuzzy Inference System", IEEE Transactions on Magnetics, Volume 44, Issue 7, Part 1, Page(s):1796 1804, 2008

- 75. Limpatthamapanee, S.; Phichaisawat, S.; "Determination of transfer capability using ANFIS with system condition separability", 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, 2009, Volume 01, Page(s):14 17, 2009

- 76. Mar, J.; Feng-Jie Lin; "An ANFIS controller for the car-following collision prevention system", Vehicular Technology, IEEE Transactions on Volume 50, Issue 4, Page(s):1106 1113, July 2001

- 77. Ubeyli, E.D.; "Adaptive Neuro-Fuzzy Inference System for Analysis of Doppler Signals", Engineering in Medicine and Biology Society, 2006. EMBS '06. 28th

- Annual International Conference of the IEEE, Page(s):2167 2170, 2006

- 78. Chen Bao-ping; Ma Zeng-qiang; "Short-Term Traffic Flow Prediction Based on ANFIS", International Conference on Communicatin Software and Networks, Page(s):791 – 793, 2006

- 79. Paramasivam, S.; Vijayan, S.; Vasudevan, M.; Arumugam, R.; Krishnan, R.; "Real-Time Verification of AI Based Rotor Position Estimation Techniques for a 6/4 Pole Switched Reluctance Motor Drive", IEEE Transactions on Magnetics, Volume 43, Issue 7, Page(s):3209 3222, July 2007

- 80. Yu-Shan Chen; Ke-Chiun Chang; "The Application of the Neuro-Fuzzy Computing Technique for the Forecasting of the R&D Project Performance", Technology Management for the Global Future, 2006. PICMET 2006 Volume 5, Page(s):2228 2235, 8-13 July 2006

- 81. Drake, J.T.; Prasad, N.R.; "ANFIS for parameter estimation in coherent communications phase synchronization", Neural Networks for Signal Processing XI, Proceedings of the 2001 IEEE Signal Processing Society Workshop, Page(s):433 442, 2001

- 82. Alexandrou, D.; de Moustier, C, "Adaptive noise canceling applied to Sea Beam sidelobe interference rejection", IEEE Journal of Oceanic Engineering, Volume: 13, Issue 2, pp 70 76, 1988

- 83. Aineto, M.; Lawson, S," Narrowband signal detection in a reverberation-limited environment", OCEANS '97. MTS/IEEE Conference Proceedings, Volume: 1, pp 27

*−* 32, 1997

# **CHAPTER III**

# THEORETICAL BACKGROUND

### 3.1 Introduction

The chapter introduces necessary background theories for understanding the project.

The specifications and expectations for this sonar detection system will be introduced and together with specific techniques relevant to the project such as the wavelet transform, ANFIS and the Local Optimum Search adopted in the proposed system. Finally this chapter shows an integration of all these techniques into a complete system.

## 3.2 Introduction & Specification of the system

The purpose of this project is to seek an optimum solution for sonar signal detection in a reverberation-limited broadband and shallow-water environment. Given a specific environment, the Signal-Noise-Ratio(SNR) is expected to be less than -20dB. Therefore, the proposed system should be able to deal with signals buried in severe noise. Also in real life situations such as the requirement of the MOD, the system should be able to determine the speed of a moving target up to 50 knots with the resolution of 1 knot.

Since the family of scaled wavelets model the behavior of sonar pulses in a reverberation-limited broadband environment better than other signal detection techniques as explored in Chapter II[1,2], the use of a wavelet is proposed. However, reverberation noises have similar forms to the target pulses of the system, and previous research shows reverberation poses a serious problem in many active sonar applications. This is especially true in shallow water environments [3, 4, 5]. Therefore, an Adaptive-Noise-Canceller is also proposed in this system to filter unwanted noise and make the environment suitable for a wavelet transform to process target motion parameters.

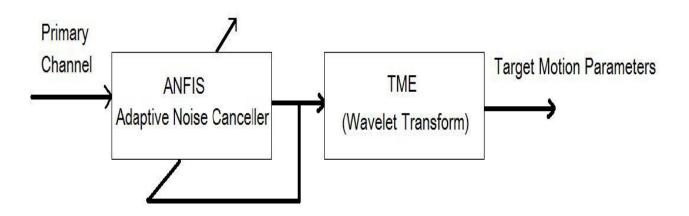

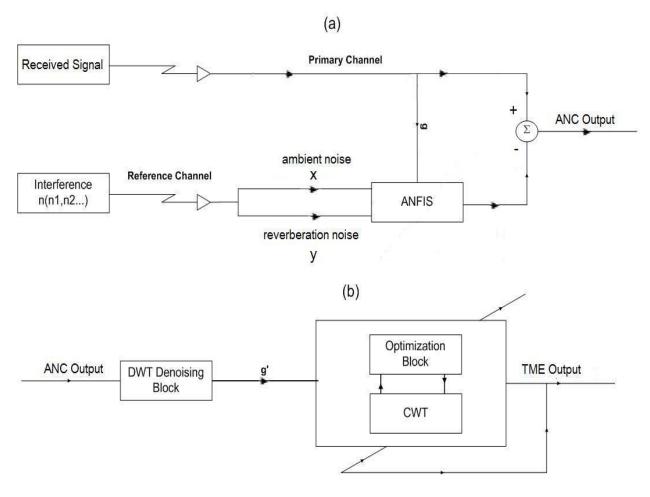

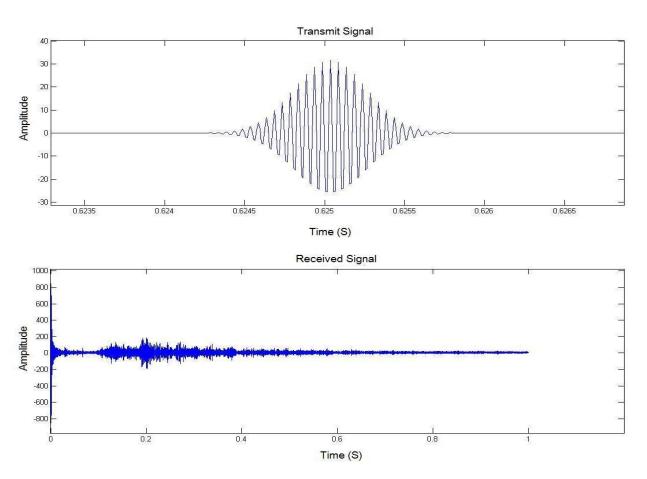

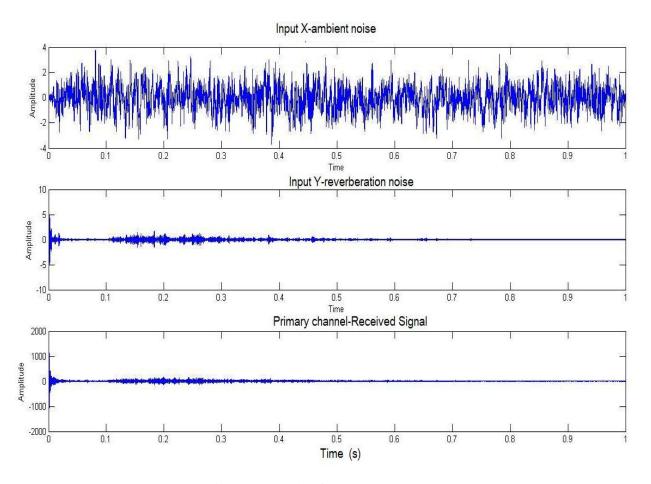

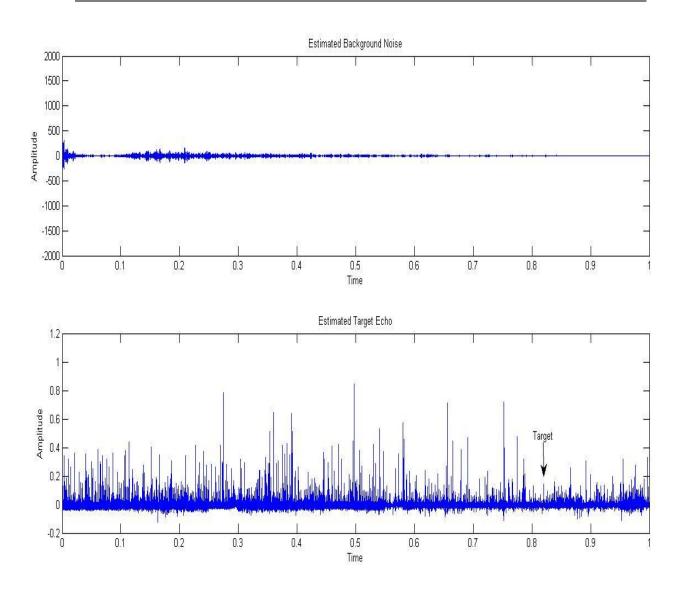

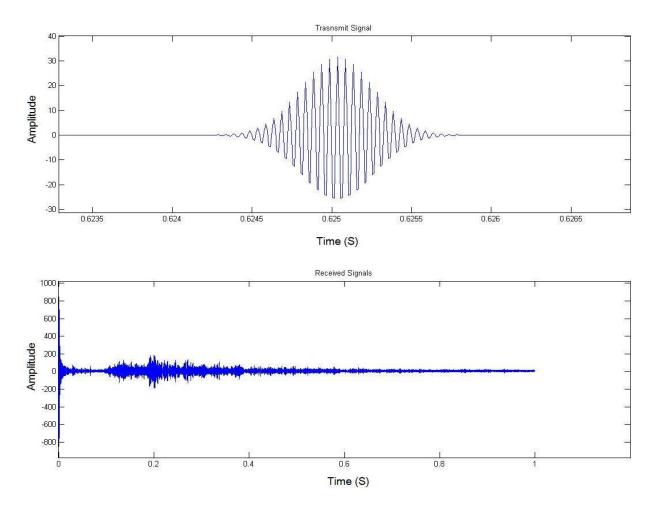

To address the above considerations, the system shown in Fig 3.1 is proposed. The system sends out a sonar pulse at certain time inteveals, and the pulse will be bounced back from a moving target. The returned signal, which is shown in Fig 3.1 as primary channel, composed of target return pulses, reverbertion noises and white noise will be recorded by the receiver. The returned signal will be used as the input of the ANC first

to remove most of the noise by ANFIS operation as shown in Fig 3.1, then the wavelet transform will examine the remainder of the signals with the family of scaled wavelets, which is the sonar pulse the sytem sent out, to determine which signal is the right target as shown in Fig 3.1 as TME(Target Motion Estimator). When the reflected pulse is extracted from background noise, the location of the target relative to the receiver and the speed of the target can be calculated based the travel time to the target and the scale information from the wavelet transform result. The following paragraphs will introduce the theoritical background of the system.

Fig 3.1 System Overview

#### 3.3 Wideband Sonar Detection

The basic concept of transmitting and receiving signals and processing them to identify and localize objects is known as active *echo* location [1]. The processing is called sonar when the sound waves are used, which stands for Sound Navigation and Ranging. Systems used sound waves for detection are known as sonar systems [1].

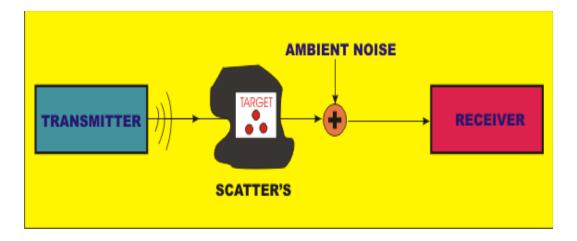

There are two categories of sonar systems: passive and active [6, 7]. Passive sonar systems estimate objects by detecting the acoustic waves emitted from the object which is being looking for. In active sonar systems, a pulse whose characteristics are already known is transmitted and then this pulse is reflected back from the target to be detected and recorded by a receiver. Active sonar systems will then compute the velocity and the location of the target from the returned pulse as shown in Fig 3.2. In the Figure it is clear that on the receiver side the received signals contains reverberation from all scatters, including target which must be detect, in the ocean and ambient noise.

Fig 3.2 Active Sonar System

In this project an active sonar system is investigated and implemented. The active sonar system is more flexible since it can choose a pulse whose characteristics are most

suitable to describe the characteristics of target.

Methods used to identify and localize objects are commonly known as correlation processing or matched filter processing [8, 9, 10, 11], which measures the range and Doppler (frequency) components of the target echo by the cross-correlation operation of overlapping segments of the returned signal with a set of stored references (hypothesized signals). Narrowband model and the wideband model are two commonly used models for representing returned signal in cross-correlation. Which model should be selected for processing the signal can be decided based on applications for which characteristics of the received signal are assumed. Assuming that the object is moving with constant velocity v relative to the speed of sound c and for the duration T, the signal transmitted has bandwidth B. For the narrowband model, the main constraint is then subject to the assumption of

$$\frac{2v}{c} << \frac{1}{TB} \tag{3.1}$$

which is called the narrowband condition [12, 13, 14]. A typical TB product in active sonar would be around 800 and c is of the order of 1500m/s, therefore Eq. 3.1 would give v << 0.9m/s ( $\simeq$  1.8knots) as the narrowband condition [15]. Even for slow moving objects, the narrowband condition would be violated. Removing the narrowband restrictions thus allows for wideband processing, which possesses several advantages including greater gain, better noise immunity and increased range resolution. Therefore the wideband model of underwater signal detection is adopted in the system described in the thesis.

The returned emitted signal after it strikes the target is referred to as the target echo, which can be defined mathematically in wideband model as [7]:

$$g(t) = \sqrt{S} f(S(t-\tau)) + n(t)$$

(3.2)

Where

$$g(t) = Target Echo$$

$\sqrt{s}$  = Normalization term keep the transmitted signal and received Signals at the same energy.

$$f(S(t-\tau)) =$$

Scaled and delayed version of transmitted pulse  $n(t) =$  noises

The target echo is scaled and delayed in Eq 3.2. This is due to the fact that when a pulse is transmitted and reflects off an object (target) the received signal is created. It differs from the transmitted signal because of the speed and position of the object. In Equation 3.2 g (t) presents the returned signal from one single object in the ocean. In practical there are much more scatterers in the environment and therefore the signals received at the receiver will contain all g (t)s from different scatters with different scales and delays. Apart from the target echo from real target, all other g (t)s are categorized as reverberation noises. As introduced in Chapter II, reverberation and ambient noises are jointly considered as the background noises in wideband active sonar system. In most situations the background noises is dominating and therefore the major concern of a wideband sonar detection system is to extract the desired target echo out of the received signals. It is obvious that the form of reverberation noises is very similar to the target

echo. Understandings on similarity and difference between desired signal and noises would be huge benefit for sonar system development. As introduced in Eq 3.2, the target echo which is reflected off the target is what a sonar system wants to extract. Amplitude, nature of function of the signal, frequency and time are parameters which can affect a signal. In a sonar model, there are many factors which can affect amplitude of target echo, such as characteristics of scatters, ocean bottom or surface, nature of water, pressure or temperature, etc. However, there is little relation between amplitude and target's speed and location which are the two desired parameters the sonar system wants. Therefore, even we retrieve the amplitude of reflected signal, there are too many variables on this parameter and it is hard to identify any target motion parameters from it. In the mean time, the nature of the signal would not be changed during reverberation process; the frequency of target echo only relates to the velocity of the target scatter, and the arrival time only relates to the underwater acoustic propagation speed and the location of the target. In shallow water environment, the speed of acoustic propagation can be treated as a constant value. Therefore, the arrival time in equation 3.2 is only related to the location of the target. By extracting these two parameters-speed and location the target's speed and velocity can be easily obtained. Details of reverberation noise models can be found in Chapter II, and in the following text the characteristics of signal reflected from target are presented.

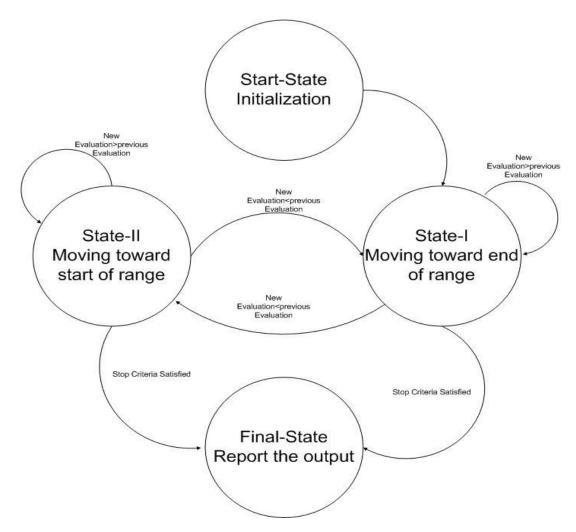

When a transmitted signal, f (t), reflects off a single object (a point scatterer), the received signal, g (t), is created. These signals differ due to the position and motion