# ADVANCED HIGH FREQUENCY SWITCHED-MODE POWER SUPPLY TECHNIQUES AND APPLICATIONS

A thesis submitted to The University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2010

**Daniel Robert Nuttall**

The School of Electronic and Electrical Engineering

### Abstract

This Thesis examines the operation and dynamic performance of a single-stage, singleswitch power factor corrector, S<sup>4</sup>PFC, with an integrated magnetic device, IM. Also detailed is the development and analysis of a high power light emitting diode, HP LED, power factor correction converter and proposed voltage regulation band control approach.

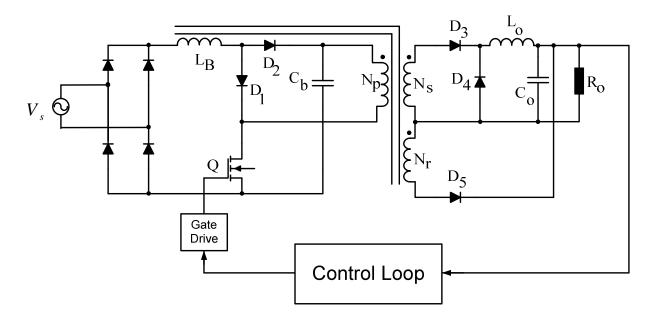

The S<sup>4</sup>PFC consists of a cascaded discontinuous current mode, DCM, boost stage and a continuous current mode, CCM, forward converter. The S<sup>4</sup>PFC achieves a high power factor, low input current harmonics and a regulated voltage output, utilising a single MOSFET. A steady-state analysis of the S<sup>4</sup>PFC with the IM is performed, identifying the operating boundary conditions for the DCM power factor correction stage and the CCM output voltage regulation stage. Integrated magnetic analysis focuses on understanding the performance, operation and generated flux paths within the IM core, ensuring the device does not affect the normal operation of the converter power stage. A design method for the S<sup>4</sup>PFC with IM component is developed along with a cost analysis of this approach. Analysis predicts the performance of the S<sup>4</sup>PFC and the IM, and the theoretical work is validated by MATLAB and SABER simulations and measurements of a 180 W prototype converter.

It is not only the development of new topological approaches that drives the advancement of power electronic techniques. The recent emergence of HP LEDs has led to a flurry of new application areas for these devices. A DCM buck-boost converter performs the power factor correction and energy storage, and a cascaded boundary conduction current mode buck converter regulates the current through the LED arrays. To match the useful operating lifetime of the HP LEDs, electrolytic capacitors are not used in the PFC converter. Analysis examines the operation and dynamic characteristics of a PFC converter with low capacitive energy storage capacity and its implications on the control method. A modified regulation band control approach is proposed to ensure a high power factor, low input current harmonics and output voltage regulation of the PFC stage. Small signal analysis describes the dynamic performance of the PFC converter, Circle Criterion is used to determine the loop stability. Theoretical work is validated by SABER and MATLAB simulations and measurements of a 180 W prototype street luminaire.

## **Dedication**

For my parents, for your constant drumming into me 'never to give up'.... its been a long time in the making. And for all those school summers forced to do extra homework.... well.... this is the result!!

For Isabel, without you, your unquestionable support, your inspiration and your belief...this would have never been possible.

### **Copyright Statement**

The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the "Copyright") and he has given The University of Manchester the right to use such Copyright for any administrative, promotional, educational and/or teaching purposes.

Copies of this thesis, either in full or in extracts, may be **only** made in accordance with the regulations of the John Rylands University of Manchester. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

The ownership of any patents, designs, trade marks and any and all other intellectual property rights except for the Copyright (the "Intellectual Property Rights") and any reproductions of copyright works, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission if the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

Further information on the condition under disclosure, publication and exploitation of this thesis, the Copyright and any Intellectual Property Rights and/or Reproductions described in it may take place is available from the Head of School of Electrical and Electronic Engineering (or the Vice-President).

# **List of Contents**

| Abstract                                                    | 1  |

|-------------------------------------------------------------|----|

| Dedication                                                  | 2  |

| Copyright Statement                                         | 3  |

| List of Contents                                            | 4  |

| List of Figures                                             | 9  |

| List of Tables                                              | 16 |

| List of Tables                                              | 16 |

| Nomenclature                                                | 18 |

| Declaration                                                 | 23 |

| Acknowledgement                                             | 24 |

| About The Author                                            | 25 |

| 1 Advanced High Frequency Power Supply Techniques           | 26 |

| 1.1 Introduction                                            | 26 |

| 1.2 Literature Review                                       | 33 |

| 1.2.1   Power Factor Correction Techniques                  | 33 |

| 1.2.2   Passive Power Factor Correction                     | 33 |

| 1.2.3 Active Power Factor Correction                        | 35 |

| 1.2.4 Single-Phase Single-Stage Power Factor Correction     | 38 |

| 1.2.5 Power Factor Correction Regulation Control Strategies | 45 |

| 1.2.6 Magnetic Modelling and Integrated Magnetic Concepts   | 48 |

| 1.2.7 Devices and Components                                | 49 |

| 1.2.7.1 Power Diodes                                        | 50 |

| 1.2.7.2 High Power Light Emitting Diodes                    | 51 |

| 1.2.7.3 MOSFET                                              | 54 |

| 1.2.7.4 | Capacitors55                                                             |

|---------|--------------------------------------------------------------------------|

| 1.2.8   | Street Lighting Considerations and Regulations                           |

| 1.3     | Summary of Literature Review                                             |

| 1.4     | Thesis Structure                                                         |

| 2 Sin   | gle-Stage Single-Switch Converter Analysis with Integrated Magnetic . 61 |

| 2.1.1   | Introduction                                                             |

| 2.1.2   | Principles of Operation of S <sup>4</sup> PFC61                          |

| 2.1.3   | Integrated Magnetic Principles of Operation72                            |

| 2.2     | S <sup>4</sup> PFC Prototype                                             |

| 2.2.1   | Single-Stage Single Switch Power Factor Correction Specification 76      |

| 2.2.2   | Design Procedure                                                         |

| 2.2.3   | Design Summary                                                           |

| 2.2.4   | Integrated Magnetic Design                                               |

| 2.3     | Component Selection and Loss Audit                                       |

| 2.4     | Steady-State SABER Simulation                                            |

| 2.5     | Summary 103                                                              |

|         | gle-Stage Single-Switch PFC Converter Dynamic Behaviour and Control      |

| 3.1     | Introduction                                                             |

| 3.2     | Line-to-Output                                                           |

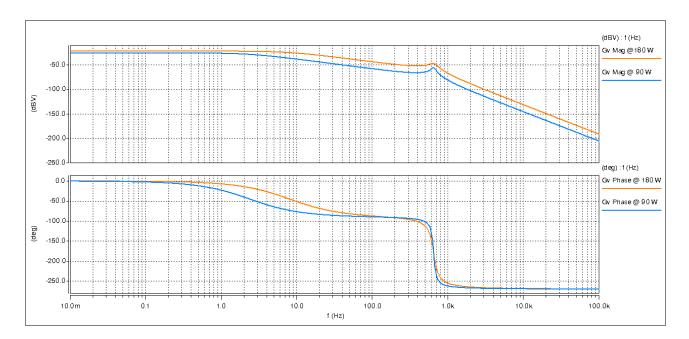

| 3.3     | Control-to-Output                                                        |

| 3.4     | Identification of Suitable Control Approach the S <sup>4</sup> PFC 110   |

| 3.5     | Design of Control Loop 114                                               |

| 3.6     | SABER and MATLAB Simulation Verification119                              |

| 3.7     | Summary 123                                                              |

| 4 Exp   | perimental Performance of S <sup>4</sup> PFC with IM                     |

| 4.1    | Introduction                                             |

|--------|----------------------------------------------------------|

| 4.2    | Circuit Construction and Experimental Setup 124          |

| 4.3    | Experimental Verification and Performance Comparisons    |

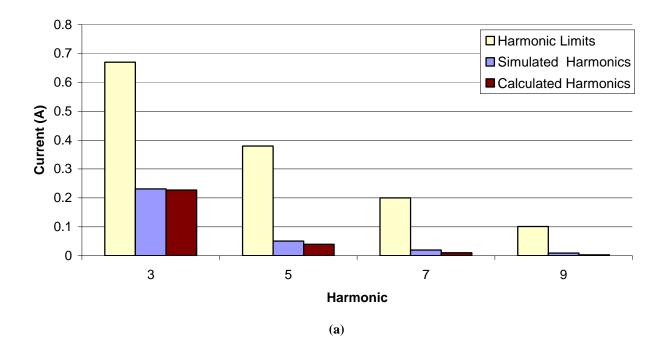

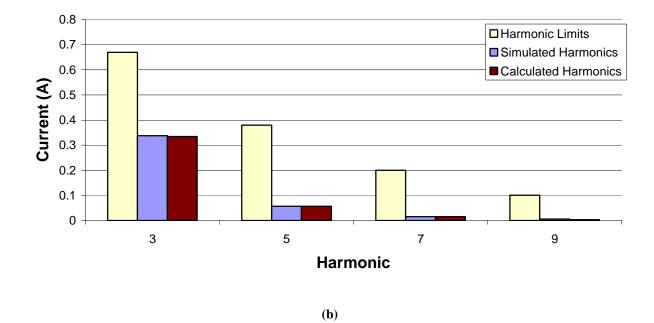

| 4.3.1  | Input Current Quality and Harmonic Content               |

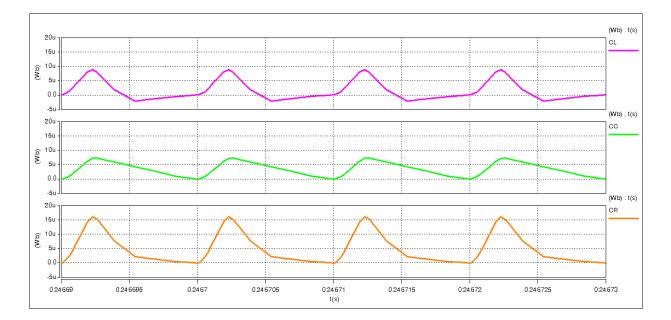

| 4.4    | Steady State Waveforms                                   |

| 4.5    | Cost Analysis                                            |

| 4.6    | Summary 135                                              |

| 5 Ultr | a Bright White Light Emitting Diode Driver               |

| 5.1    | Introduction                                             |

| 5.2    | HP LED Power Converter Requirements                      |

| 5.3    | Power Factor Correction Converter Selection              |

| 5.4    | Principles of Operation of Power Factor Correction Stage |

| 5.5    | Buck Boost Power Factor Correction Specification         |

| 5.6    | Converter Optimisation and Component Selection           |

| 5.7    | Selection of Magnetic Components 155                     |

| 5.8    | Loss Audit                                               |

| 5.9    | Summary of PFC Design                                    |

| 5.10   | PFC SABER Simulation                                     |

| 5.11   | Power Factor Correction Converter Prototype Design       |

| 5.11.1 | Design Specifications163                                 |

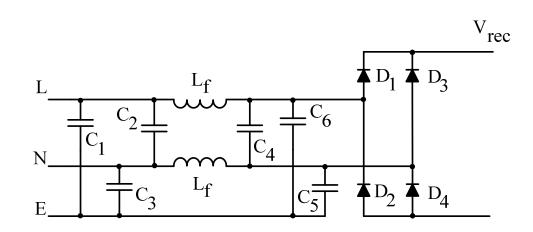

| 5.11.2 | EMC Filter 163                                           |

| 5.12   | Summary 164                                              |

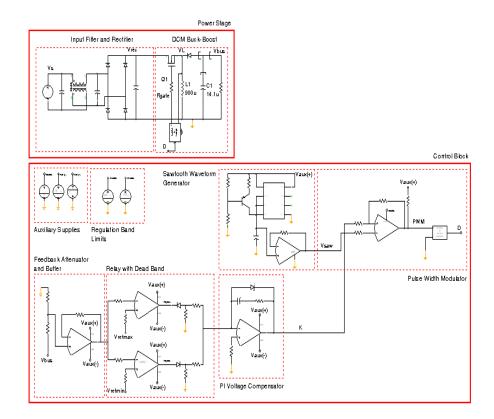

| 6 HP   | LED Power Factor Correction Control Stage Design         |

| 6.1    | Introduction                                             |

| 6.2    | Identification of Control Approach166                    |

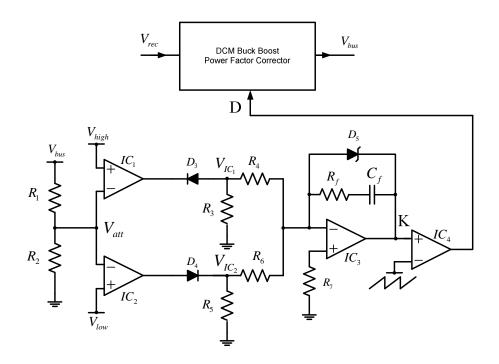

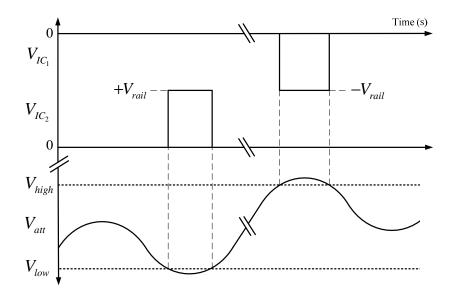

| 6.3    | Principles of Operation                                  |

| 6.4    | Design of Voltage Regulation Band Control 171             |

|--------|-----------------------------------------------------------|

| 6.5    | Open Loop Analysis                                        |

| 6.6    | Proportional Integrator Compensator Design 179            |

| 6.7    | Voltage Loop Response at Regulation Band Limits           |

| 6.8    | SABER Simulation PI Compensator Design                    |

| 6.9    | SABER Simulation Verification of Control Loop             |

| 6.10   | Summary 191                                               |

| 7 Exp  | perimental Verification and System Performance            |

| 7.1    | Introduction                                              |

| 7.2    | HP LED Constant Current Regulators                        |

| 7.3    | Principles of Operation of the Constant Current Converter |

| 7.4    | Control of Buck Converter                                 |

| 7.5    | Constant Current Converter Optimisation                   |

| 7.6    | Constant Current Regulator Specifications                 |

| 7.7    | Constant Current SABER Simulation                         |

| 7.8    | Experimental and Laboratory Setup                         |

| 7.8.1  | Power Factor Corrector Circuit Layout                     |

| 7.9    | Constant Current Regulator Circuit Layout                 |

| 7.10   | HP LED String                                             |

| 7.11   | Verification and Results                                  |

| 7.11.1 | Power Factor Corrector                                    |

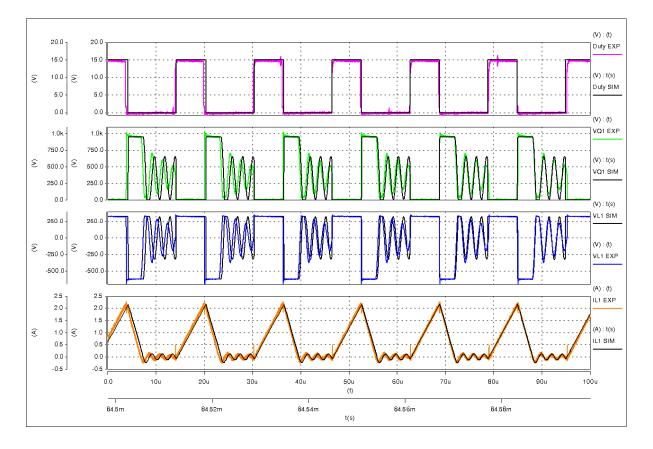

| 7.11.2 | Buck boost steady state experimental waveforms            |

| 7.11.3 | Parasitics                                                |

| 7.11.4 | Buck boost transient experimental waveforms               |

| 7.12   | Summary                                                   |

| 8 Cor  | clusions and Further Work                                 |

| 8.1      | Introduction                   |  |

|----------|--------------------------------|--|

| 8.2      | Summary of the Thesis          |  |

| 8.3      | Contributions of this Research |  |

| 8.4      | Future Development             |  |

| Referenc | es                             |  |

| Appendiz | x A                            |  |

| Appendix | x B                            |  |

| Appendiz | x C                            |  |

| Appendiz | x D                            |  |

| Appendiz | x E                            |  |

| Appendix | x F                            |  |

# List of Figures

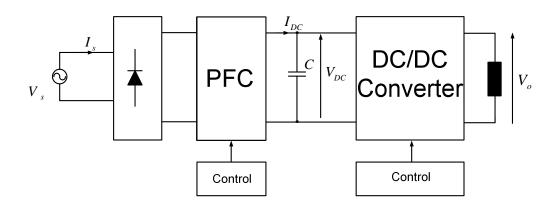

| Figure 1-1 Conventional two-stage power factor correction block diagram                                                                 | 28   |

|-----------------------------------------------------------------------------------------------------------------------------------------|------|

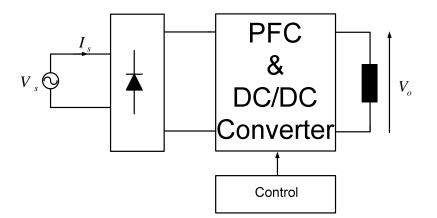

| Figure 1-2 Proposed Single-Stage Power Factor Corrector                                                                                 | 29   |

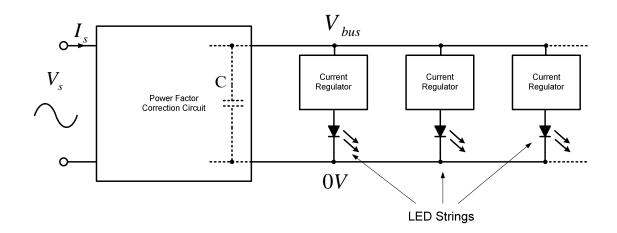

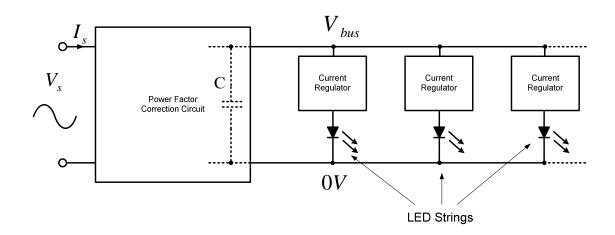

| Figure 1-3 LED PSU block diagram                                                                                                        | 32   |

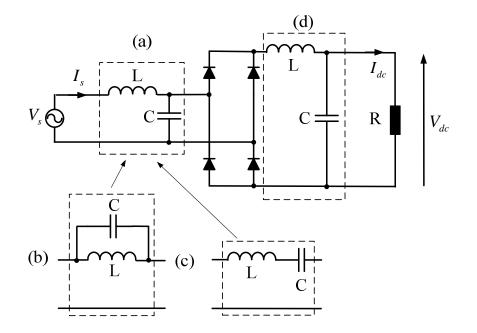

| Figure 1-4 Passive power factor correction (a) AC side LC filter, (b) Parallel resonant PFC, series resonant PFC, (d) DC side LC filter |      |

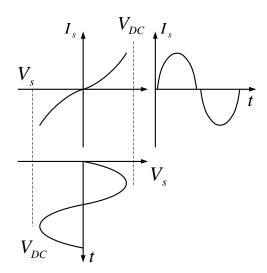

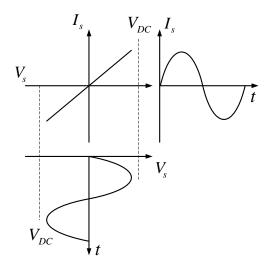

| Figure 1-5 DCM boost converter input I-V characteristics                                                                                | 37   |

| Figure 1-6 DCM Buck-boost input I-V characteristic                                                                                      | 37   |

| Figure 1-7 Energy storage performed by PFC capacitor                                                                                    | 38   |

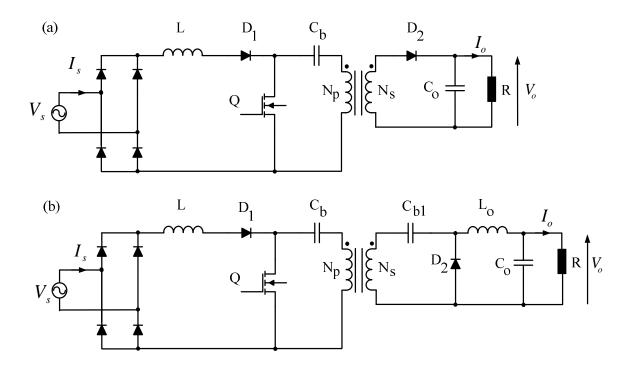

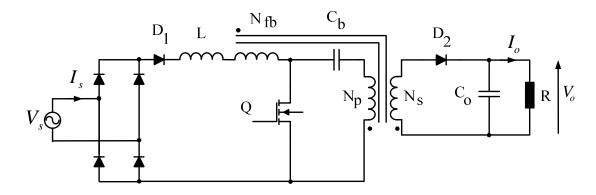

| Figure 1-8 (a) BIFRED single-stage PFC, (b) BIBRED single-stage PFC                                                                     | 40   |

| Figure 1-9 BIFRED with series voltage feedback winding                                                                                  | 40   |

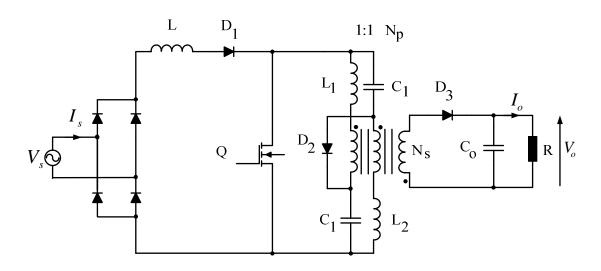

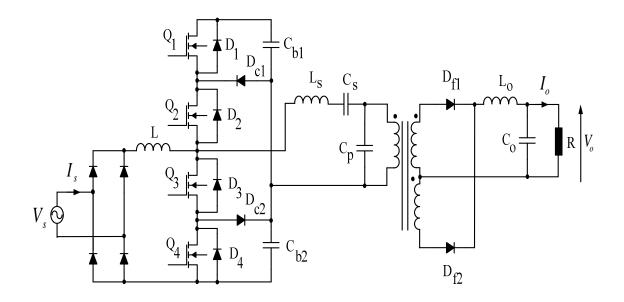

| Figure 1-10 Cascaded single-stage PFC with two switch DC/DC converter                                                                   | 42   |

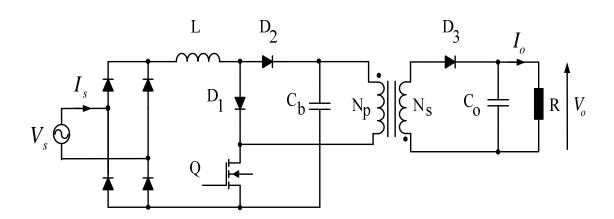

| Figure 1-11 Parallel capacitor in single-stage PFC BIFRED                                                                               | 43   |

| Figure 1-12 Single stage PFC converter prososed in [74]                                                                                 | 44   |

| Figure 1-13 Single stage LLC PFC converter                                                                                              | .44  |

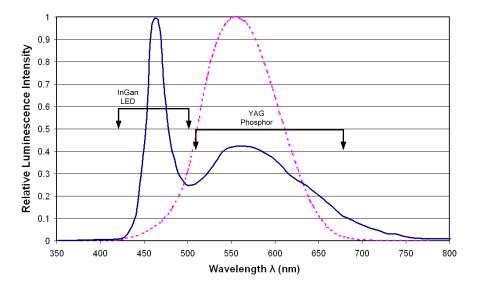

| Figure 1-14 Typical HP LED spectral distribution (solid) and standard luminous sensitivity the eye (dashed)                             |      |

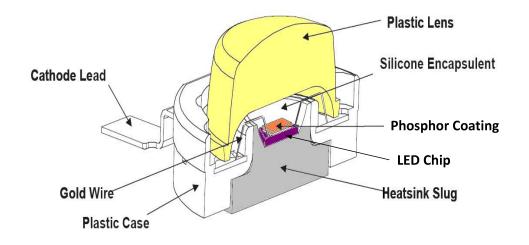

| Figure 1-15 Schematic of a high power white LED.                                                                                        | 53   |

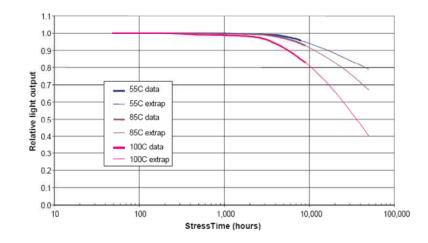

| Figure 1-16 Relative HP LED light output lifetimes at various temperatures [29]                                                         | 54   |

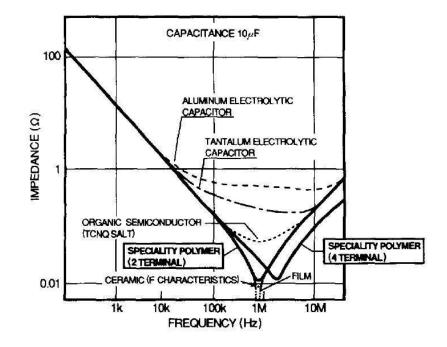

| Figure 1-17 Capacitor impedance/frequency characteristics [44]                                                                          | 57   |

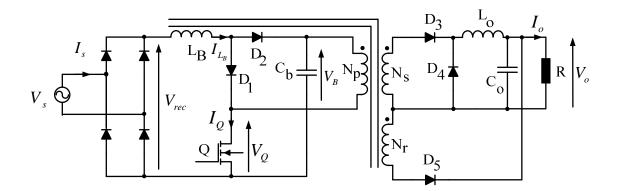

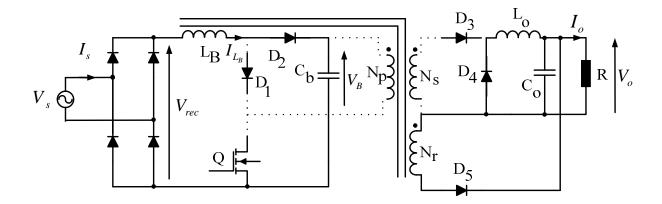

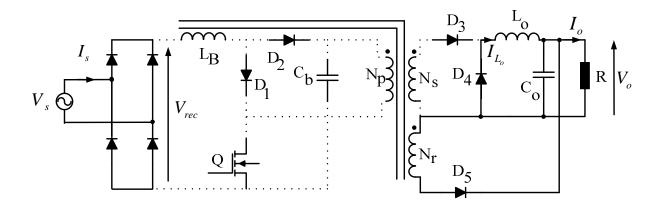

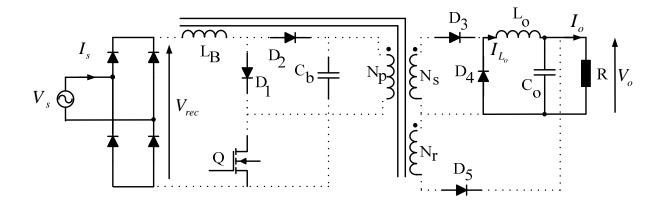

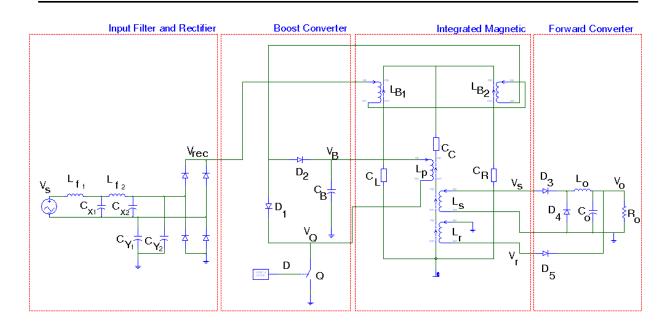

| Figure 2-1 Single-stage, single-switch power factor corrector with an integrated magnetic component                                     | . 61 |

| Figure 2-2 Schematic diagram of the S <sup>4</sup> PFC with an IM during time $t_0$ to $t_1$                                            | . 62 |

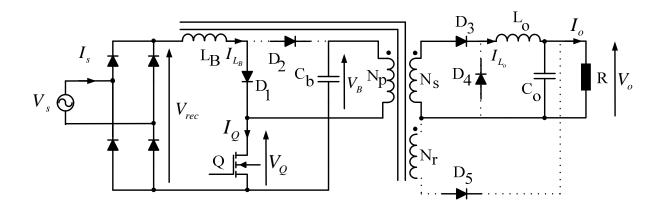

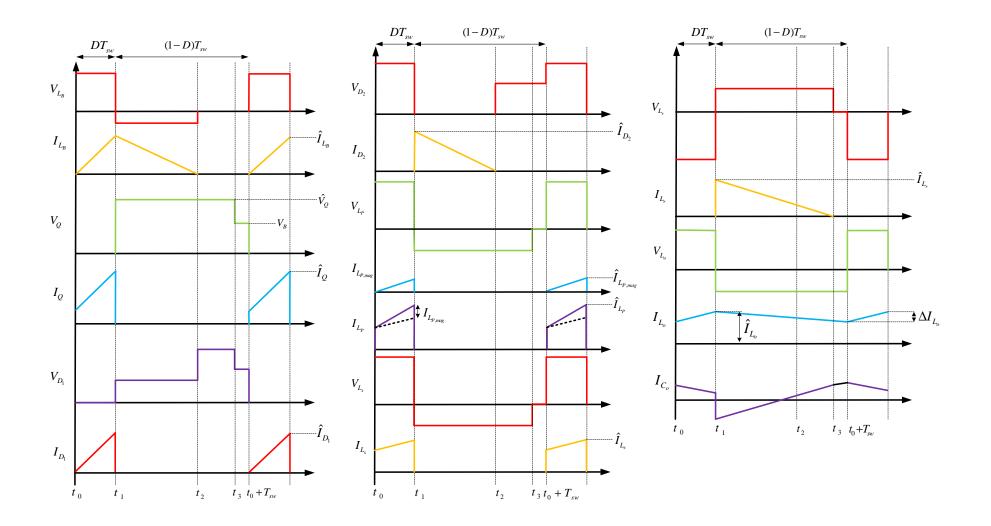

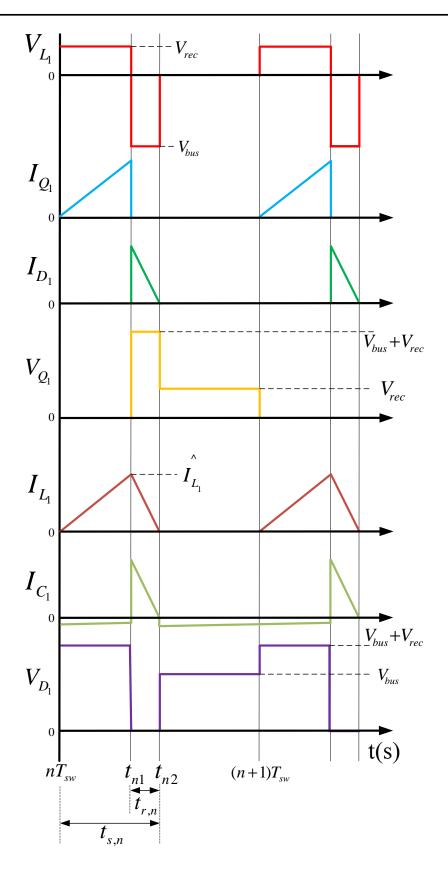

| Figure 2-3 Key waveforms of the S <sup>4</sup> PFC with an IM                                                                           | 64   |

| Figure 2-4 Schematic diagram of the S <sup>4</sup> PFC with an IM during time $t_1$ to $t_2$                                            | .65  |

| Figure 2-5 Schematic diagram of $S^4PFC$ with an IM during time $t_2$ to $t_3$                                                          | . 66 |

| Figure 2-6 Schematic diagram of S <sup>4</sup> PFC with an IM during time $t_3$ to $t_0+T_{sw}$ |

|-------------------------------------------------------------------------------------------------|

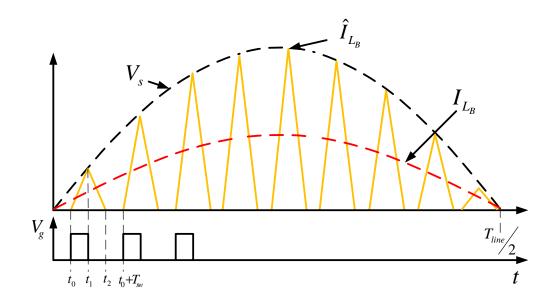

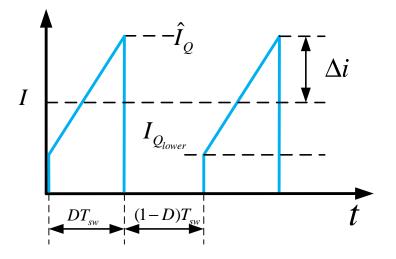

| Figure 2-7 Inductor current waveform during a half line cycle                                   |

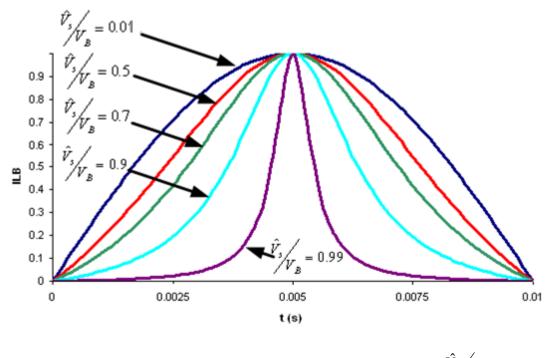

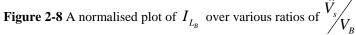

| Figure 2-8 A normalised plot of $I_{L_B}$ over various ratios of $\hat{V}_s / V_B$              |

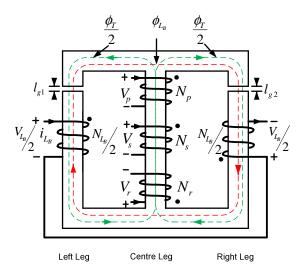

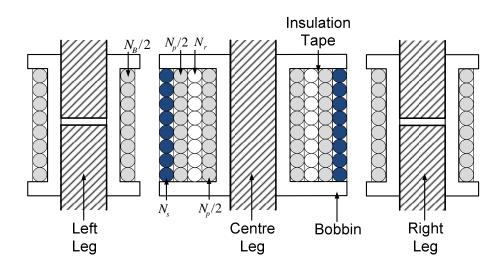

| Figure 2-9 Winding arrangement of integrated magnetic E-core72                                  |

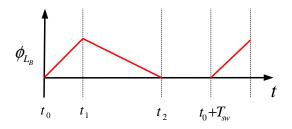

| Figure 2-10 Inductor generated flux, $\phi_{L_B}$ in outer legs                                 |

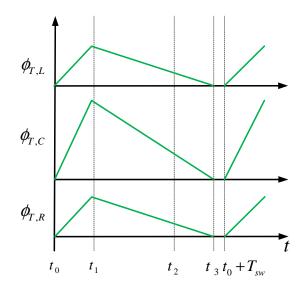

| Figure 2-11 Transformer generated flux, $\phi_T$ , in all three core legs                       |

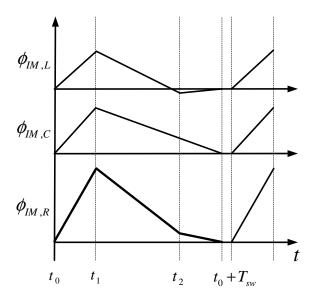

| Figure 2-12 Integrated magnetic component flux, $\phi_{IM}$ , waveforms                         |

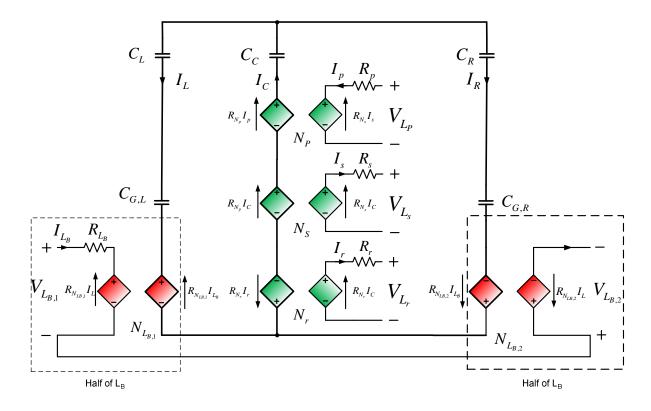

| Figure 2-13 Gyro-Capacitor model of integrated magnetic component                               |

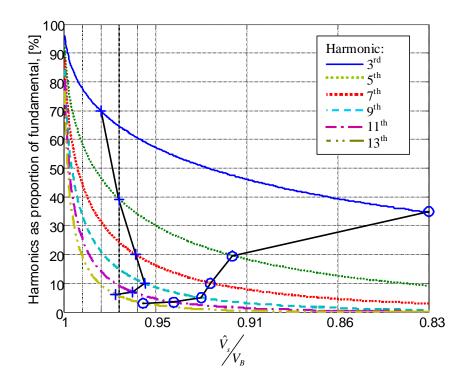

| Figure 2-14 Dominant input current harmonics for a range of voltage ratios                      |

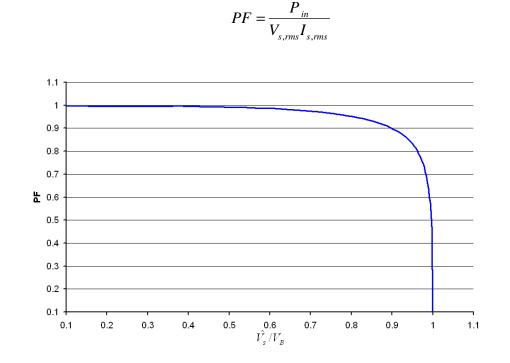

| Figure 2-15 Power factor versus $\hat{V}_s / V_B$                                               |

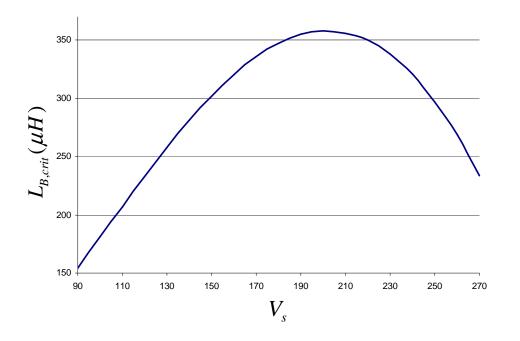

| Figure 2-16 $L_{B,crit}$ over the universal line input voltage range                            |

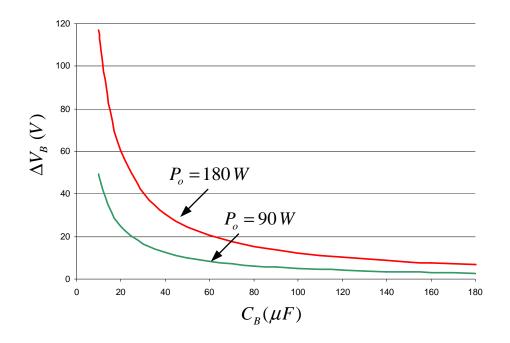

| Figure 2-17 Boost capacitor stage low frequency voltage ripple at $P_0$ = 90 W & 180 W 81       |

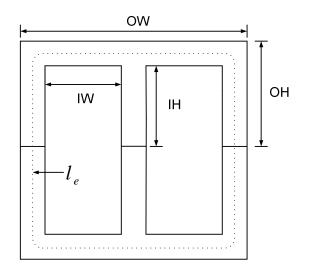

| Figure 2-18 ETD core dimensions, not to scale                                                   |

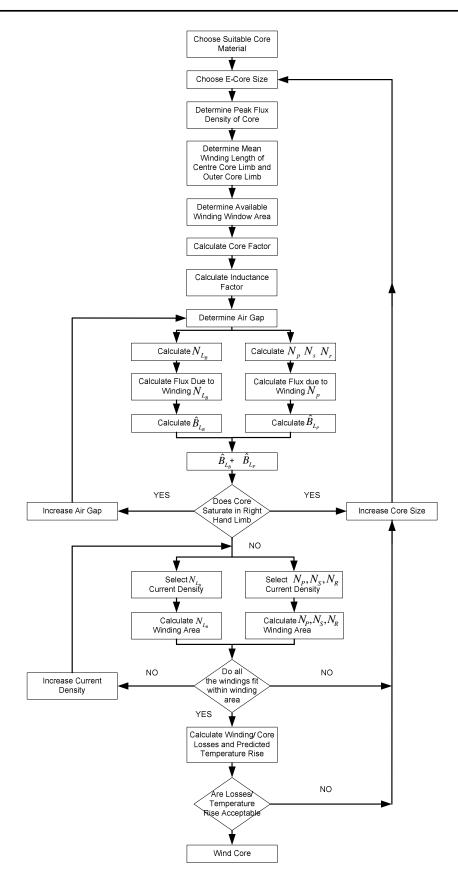

| Figure 2-19 Flow chart for the design of the integrated magnetic component                      |

| Figure 2-20 Cross section of transformer winding arrangement                                    |

| Figure 2-21 Integrated magnetic prototype                                                       |

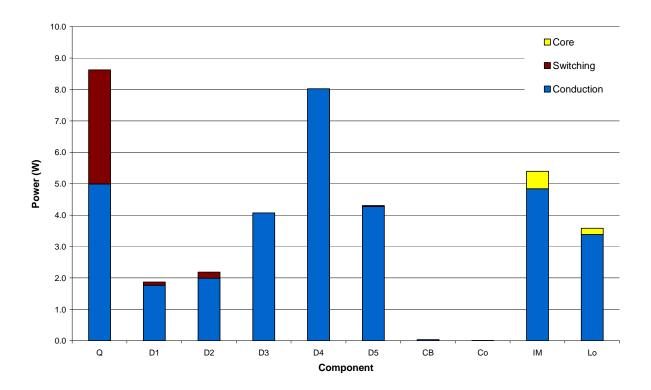

| Figure 2-22 Estimated power losses in S <sup>4</sup> PFC power devices                          |

| Figure 2-23 SABER schematic capture of S <sup>4</sup> PFC with IM                               |

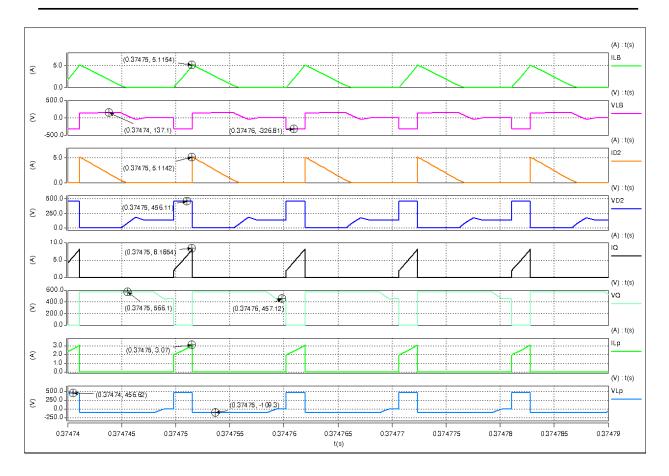

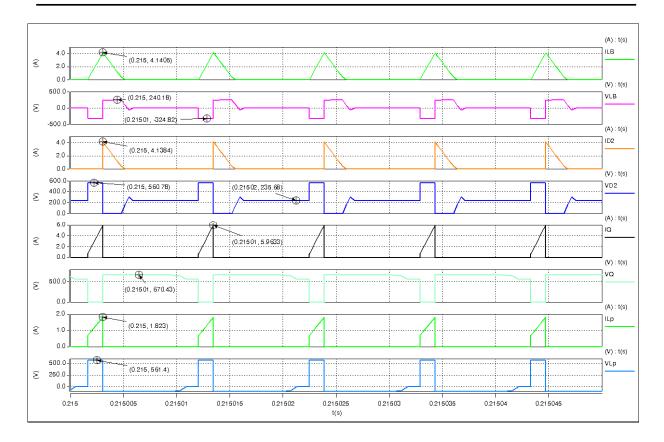

| Figure 2-24 Key SABER simulated waveforms, $V_s$ =230 Vrms, $P_o$ =180 W                        |

| Figure 2-25 Key SABER simulated waveforms, $V_s$ =230 Vrms, $P_o$ =90 W                         |

|                                                                                                 |

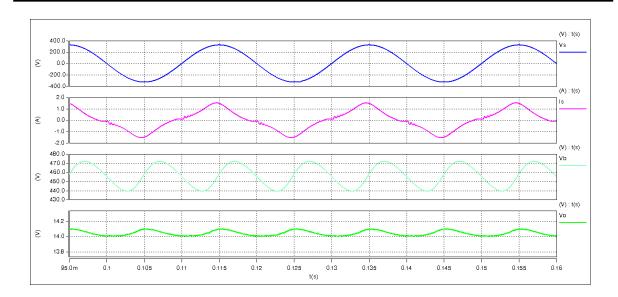

| Figure 2-26 SABER simulated waveforms of $V_s$ , $I_s$ , $V_B$ , and $V_o$ at $P_o=180$ W100    |

| Figure 2-26 SABER simulated waveforms of $V_s$ , $I_s$ , $V_B$ , and $V_o$ at $P_o=180$ W       |

| Figure 2-29 SABER simulation of integrated magnetic flux waveforms                                                               |

|----------------------------------------------------------------------------------------------------------------------------------|

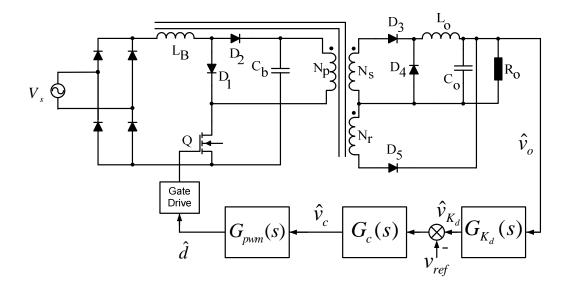

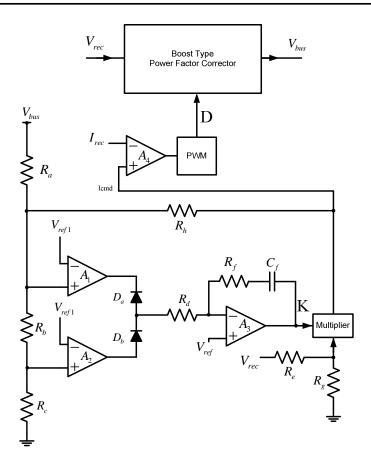

| Figure 3-1 Single-stage single switch power factor corrector with simple control block 105                                       |

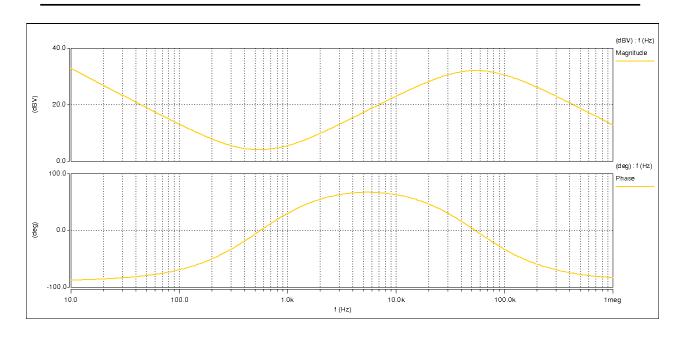

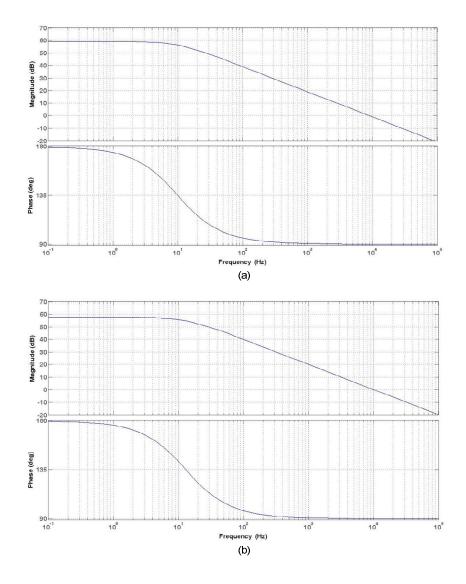

| Figure 3-2 Magnitude and Phase plot of $G_v(s)$ at $V_s = 230$ V and $P_o = 90$ W and 180 W 107                                  |

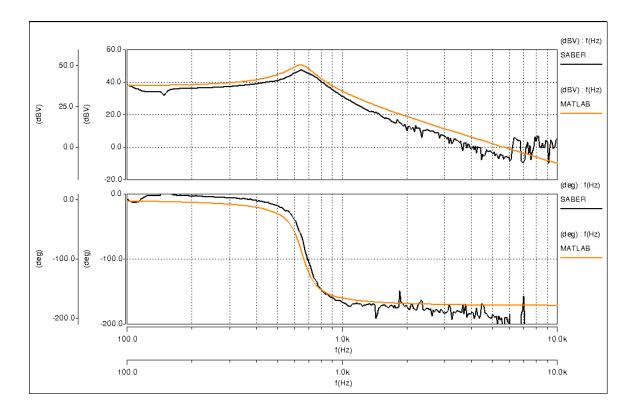

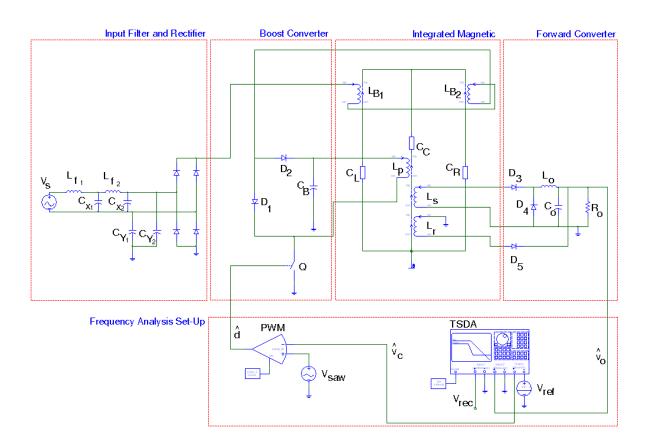

| Figure 3-3 SABER and MATLAB plots of control-to-output of the S <sup>4</sup> PFC 108                                             |

| Figure 3-4 SABER simulator arrangement to determine S <sup>4</sup> PFC $G_{vd}(s)$                                               |

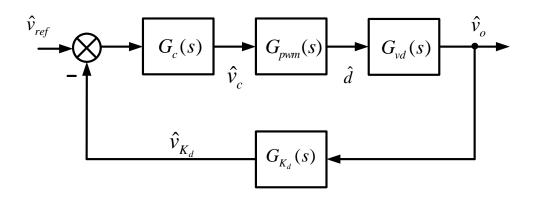

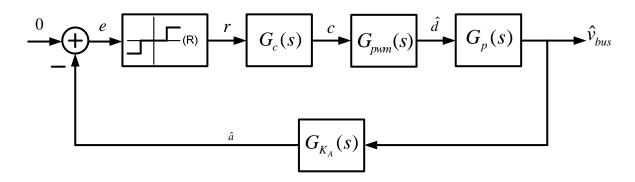

| Figure 3-5 Single loop voltage mode control111                                                                                   |

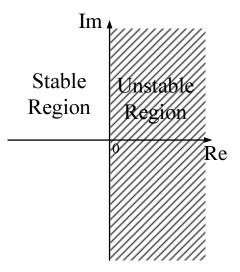

| Figure 3-6 Stability regions in the complex plane for roots of the characteristic equation 111                                   |

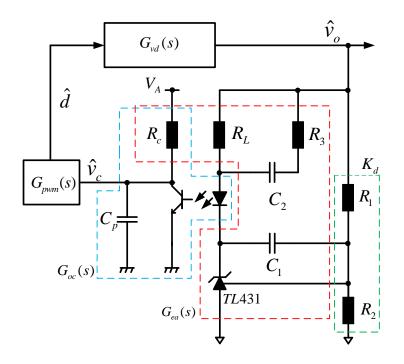

| Figure 3-7 S <sup>4</sup> PFC with a block diagram of the proposed voltage mode control loop                                     |

| Figure 3-8 Practical implementation of isolated feed back and compensation113                                                    |

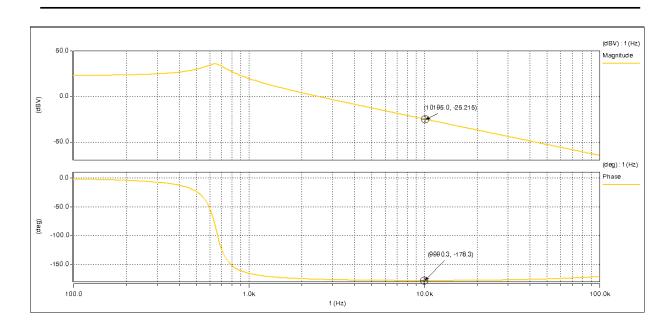

| Figure 3-9 Block diagram of UC2842 control IC 116                                                                                |

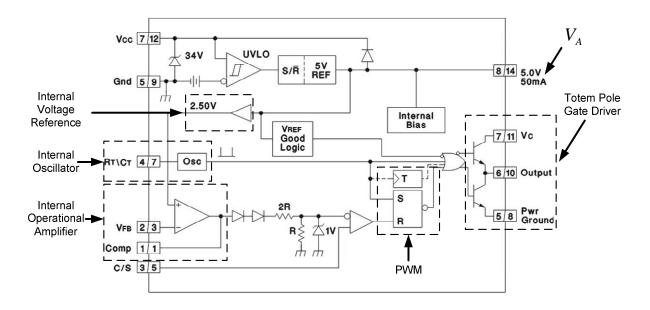

| Figure 3-10 Plot of $G_o(s)$                                                                                                     |

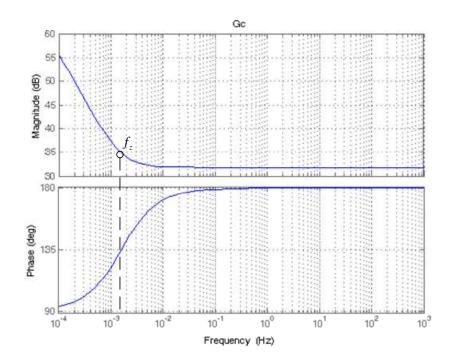

| Figure 3-11 MATLAB plot of $G_c(s)$                                                                                              |

| Figure 3-12 MATLAB plot of $G_{ol}(s)$                                                                                           |

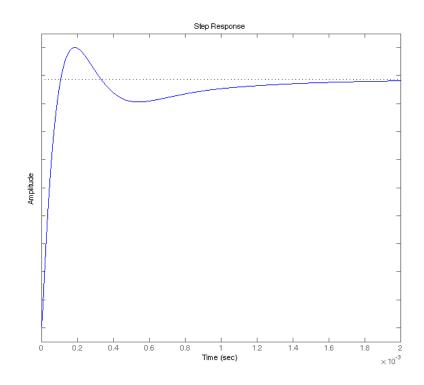

| Figure 3-13 A normalised step response of closed loop system H(s)                                                                |

| Figure 3-14 SABER simulation schematic of control loop for S <sup>4</sup> PFC converter                                          |

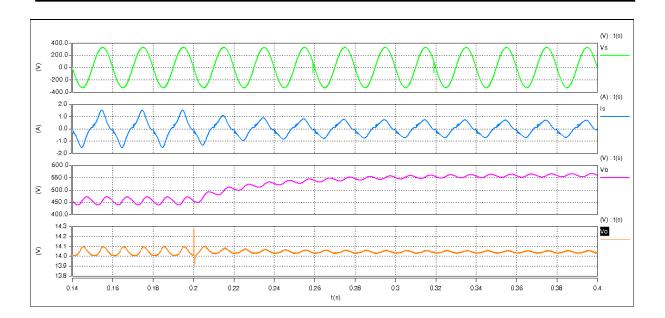

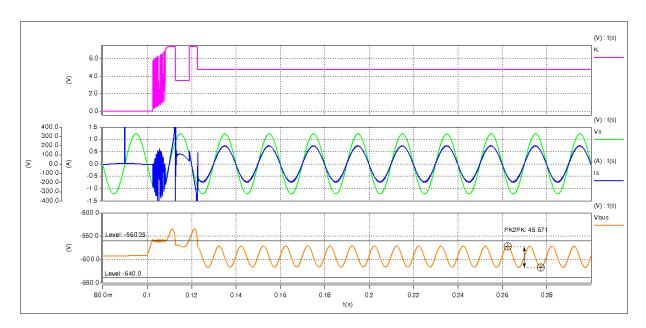

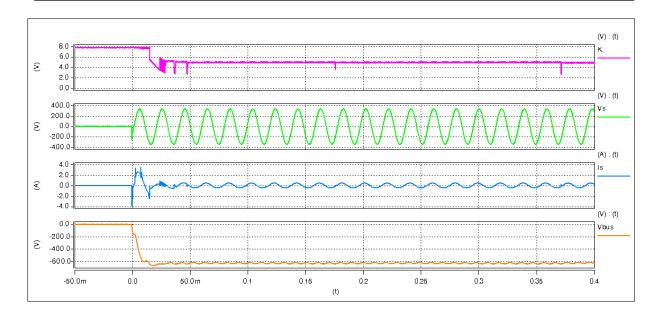

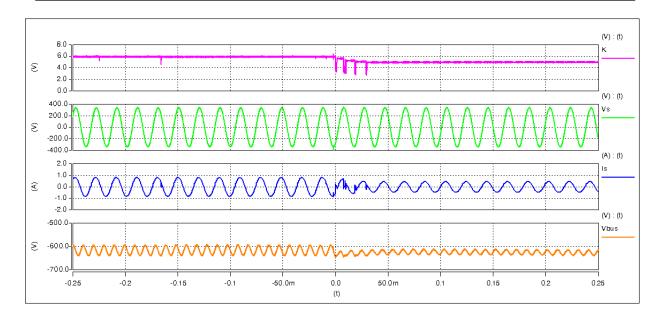

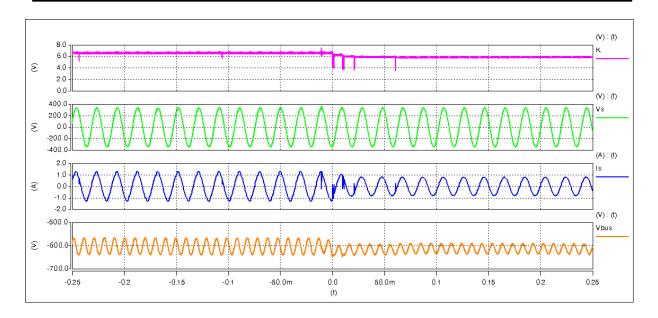

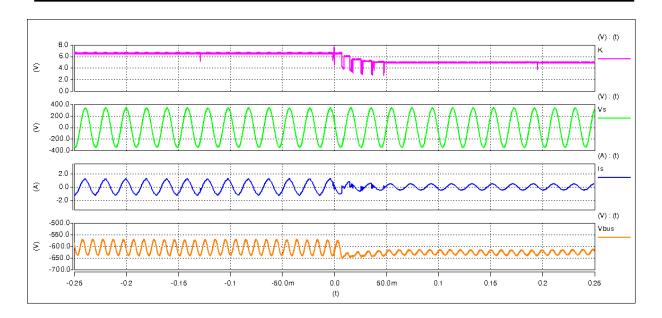

| Figure 3-15 SABER simulation of $V_s$ , $I_s$ , $V_B$ , and $V_o$ in response to a step load change of 180 W - 90 W at t = 0.2 s |

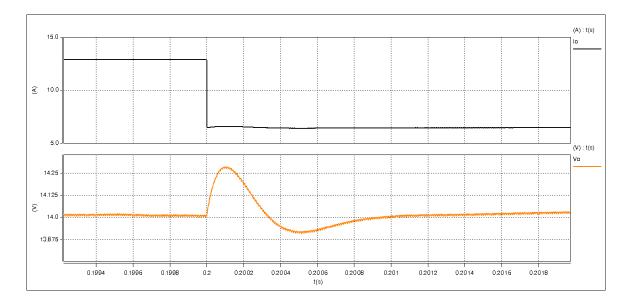

| Figure 3-16 Magnified view of SABER simulation $I_o$ and $V_o$ response to step load of 180 W to 90W                             |

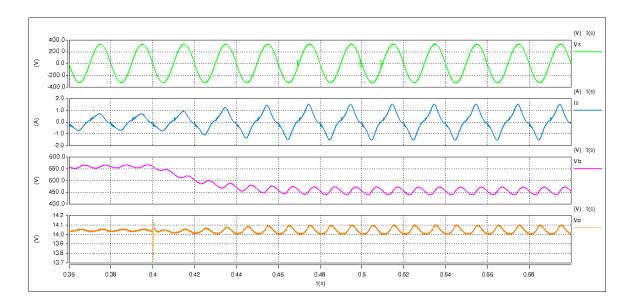

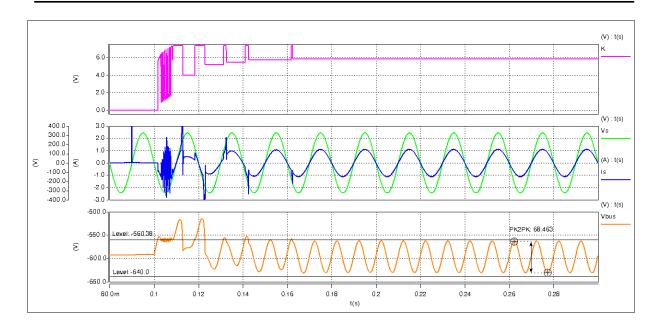

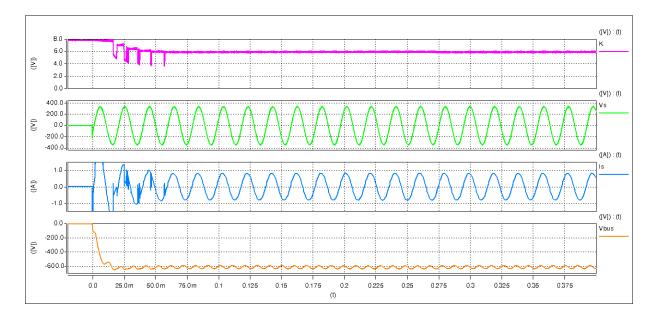

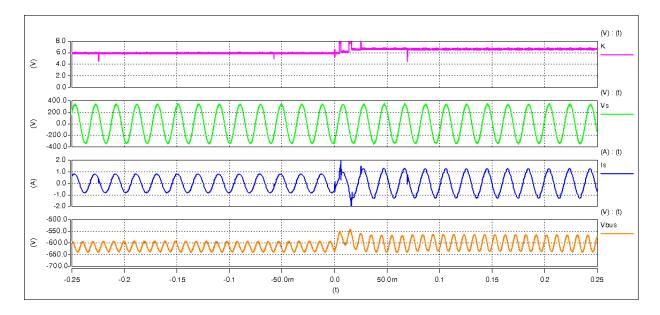

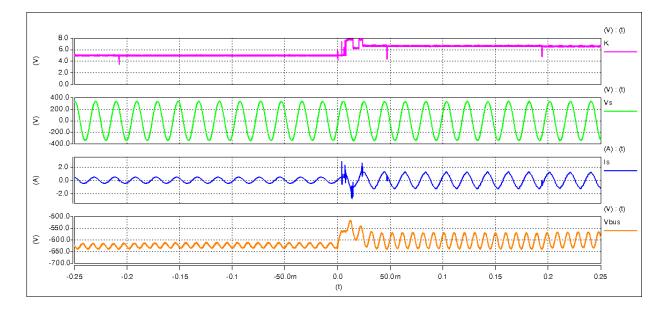

| Figure 3-17 SABER simulation of $V_s$ , $I_s$ , $V_B$ , and $V_o$ in response to a step load of 90 W to 180 W at t = 0.4 s       |

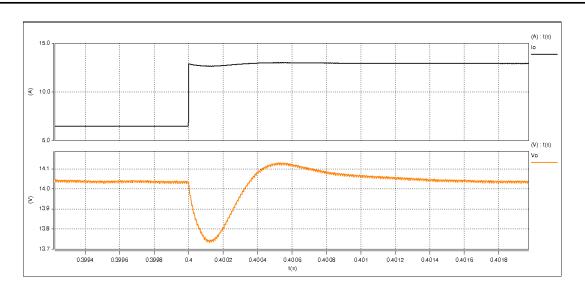

| Figure 3-18 Magnified view of SABER simulation $I_o$ and $V_o$ response to step load 90 W to 180 W                               |

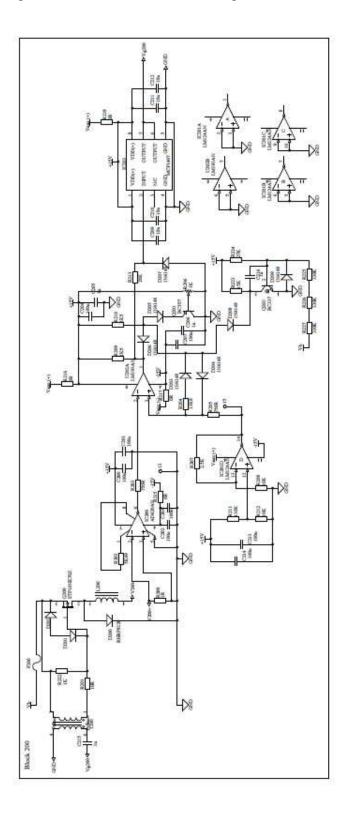

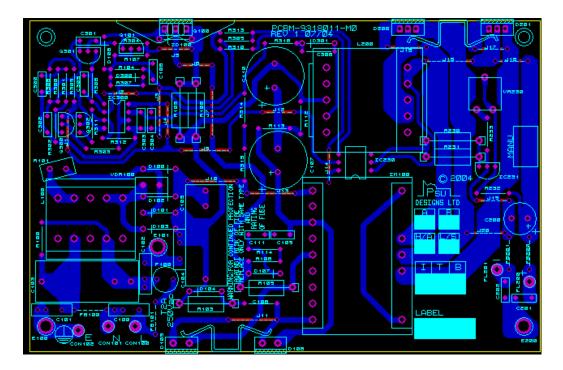

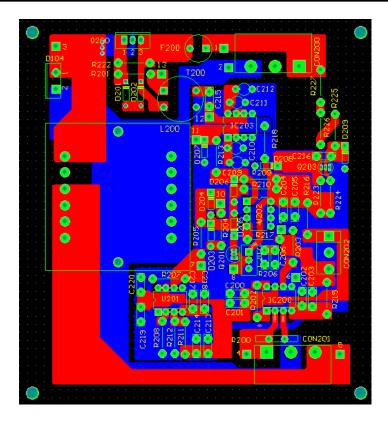

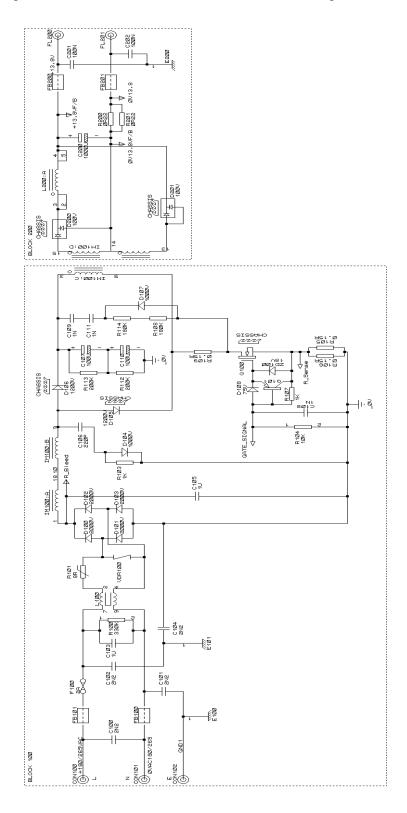

| Figure 4-1 PCB capture of S <sup>4</sup> PFC layout and tracking                                                                 |

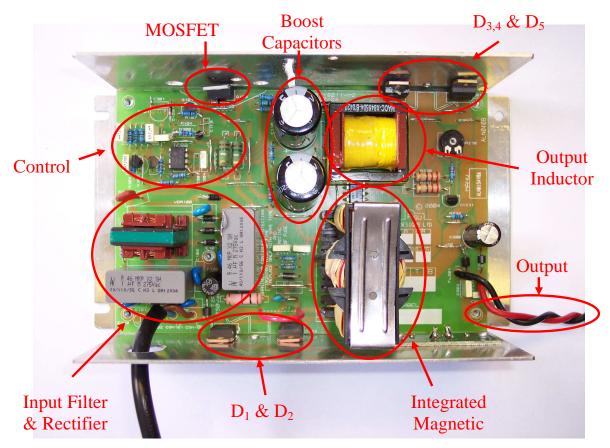

| Figure 4-2 S <sup>4</sup> PFC with integrated magnetic prototype                                                                 |

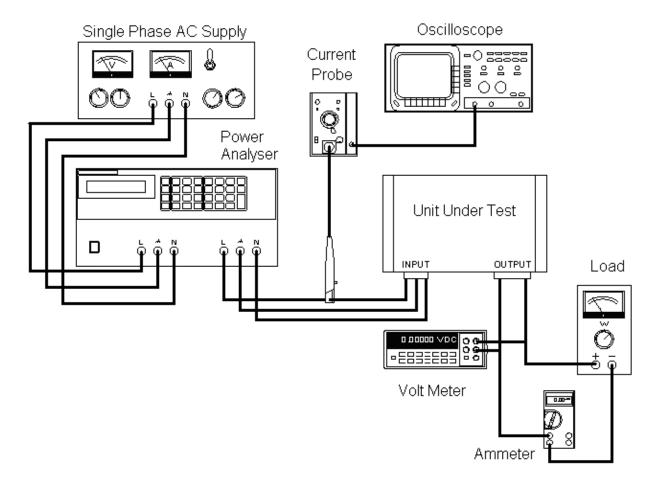

| Figure 4-3 Laboratory setup                                                                                                      |

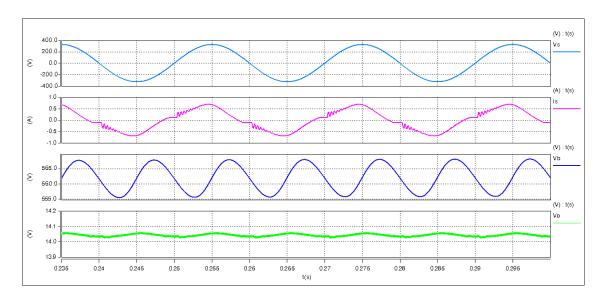

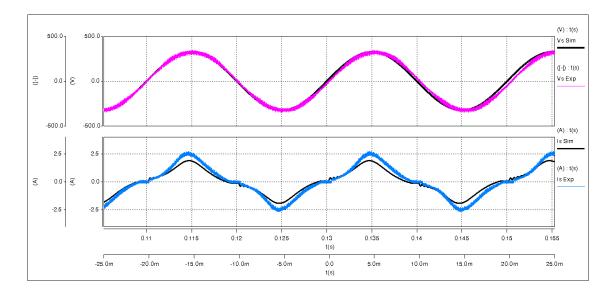

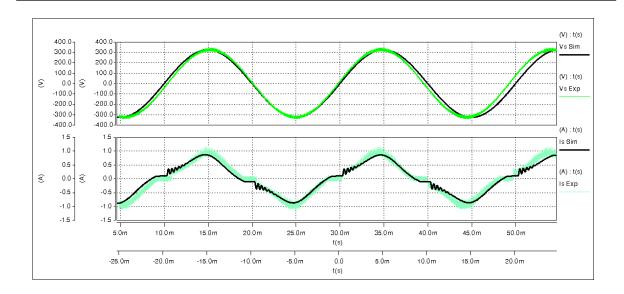

| Figure 4-4 Simulated and experimental waveforms of $I_s$ and $V_s$ where $V_s = 230 \text{ V}_{\text{rms}}$ and $P_0 = 180 \text{ W}$ |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-5 Simulated and experimental waveforms of $I_s$ and $V_s$ where $V_s = 230 \text{ V}_{\text{rms}}$ and $P_0 = 90 \text{ W}$  |

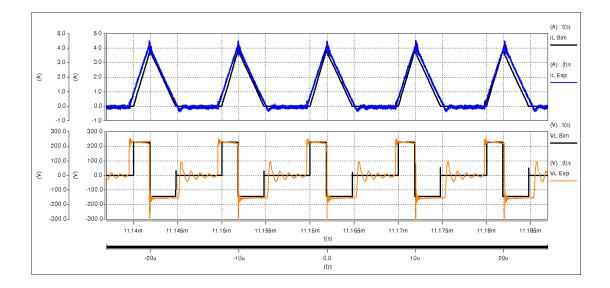

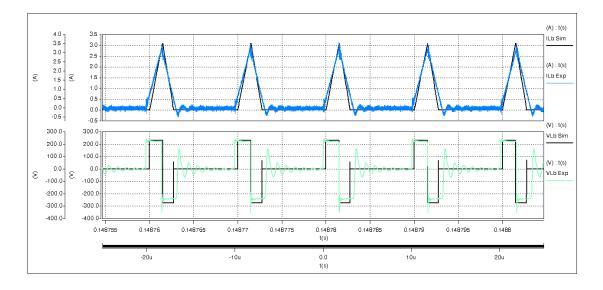

| Figure 4-6 Simulated and experimental waveforms of $I_{L_B}$ and $V_{L_B}$ for $V_s = 230$ V and P <sub>0</sub> =180 W                |

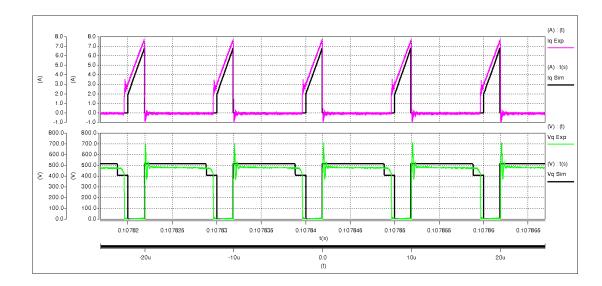

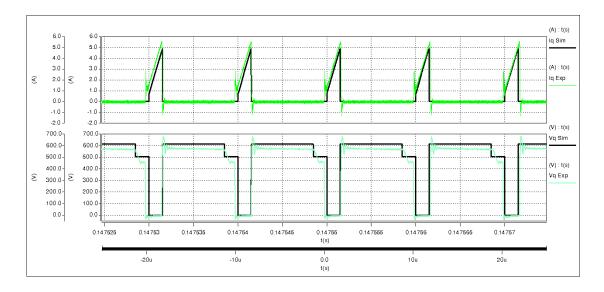

| Figure 4-7 Simulated and experimental waveforms of $I_Q$ and $V_Q$ for $V_s = 230$ V and $P_0 = 180$ W                                |

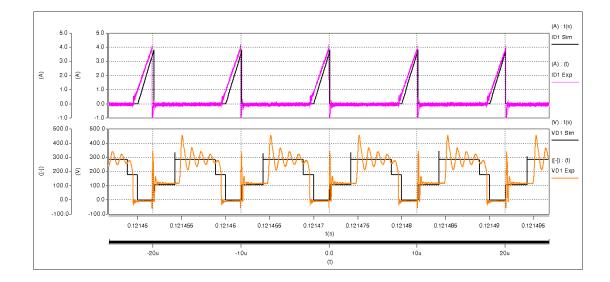

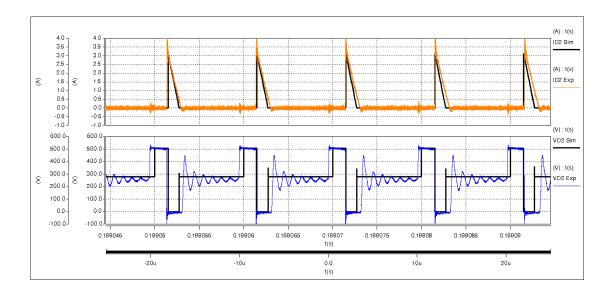

| Figure 4-8 Simulated and experimental waveforms of $I_{D_1}$ and $V_{D_1}$ for $V_s = 230$ V and P <sub>0</sub> =180 W                |

| Figure 4-9 Simulated and experimental waveforms of $I_{L_B}$ and $V_{L_B}$ for $V_s = 230$ V and P <sub>0</sub> =90 W<br>             |

| Figure 4-10 Simulated and experimental waveforms of $I_Q$ and $V_Q$ for $V_s = 230$ V and $P_0 = 90$ W                                |

| Figure 4-11 Simulated and experimental waveforms of $I_{D_2}$ and $V_{D_2}$ for $V_s = 230$ V and P <sub>0</sub> =90 W                |

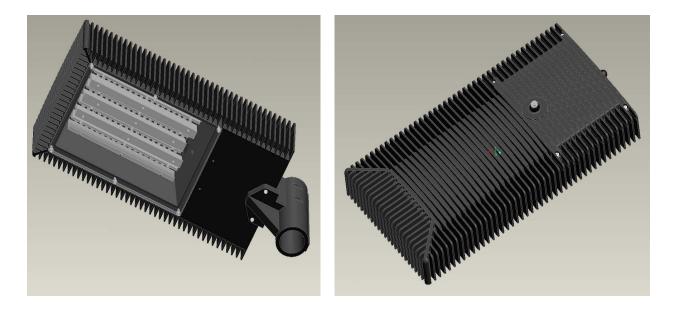

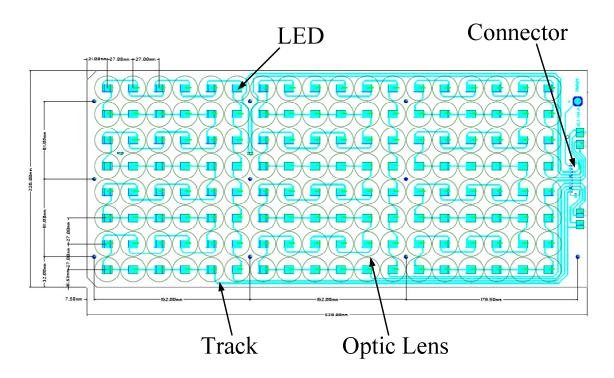

| Figure 5-1 CAD drawing of proposed LED Street Light                                                                                   |

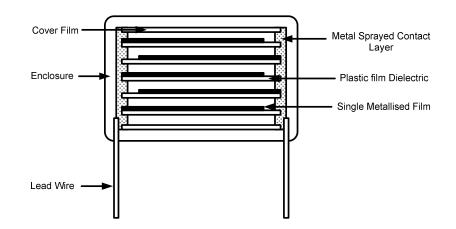

| Figure 5-2 Metallised film capacitor construction                                                                                     |

| Figure 5-3 HP LED power converter block diagram                                                                                       |

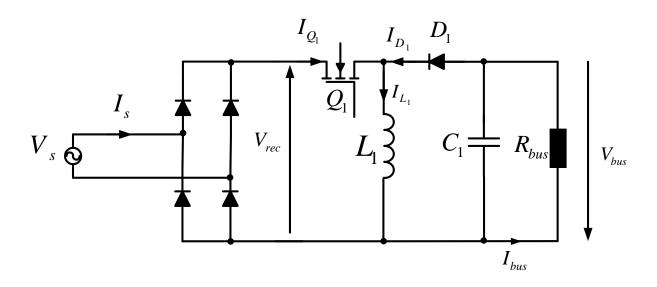

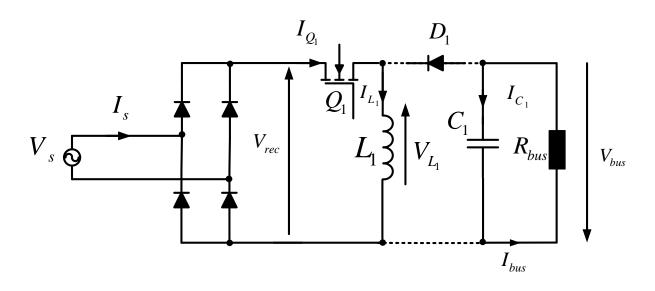

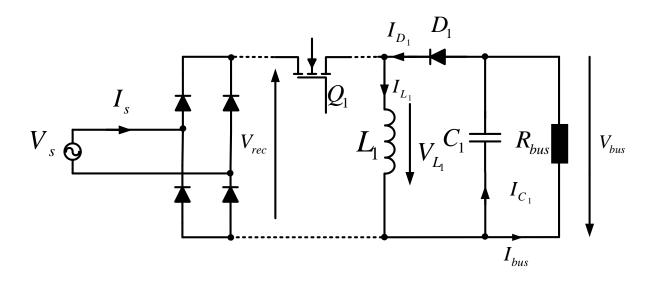

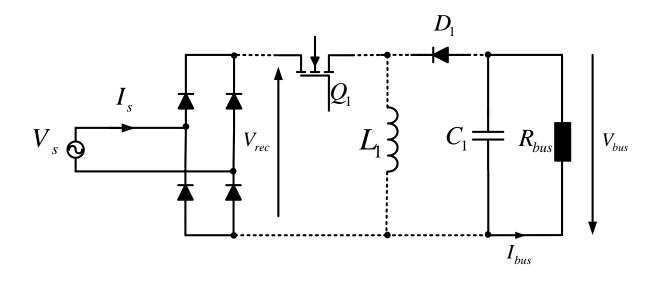

| Figure 5-4 Buck-boost power factor corrector stage                                                                                    |

| Figure 5-5 Buck-boost converter at t <sub>0</sub> to t <sub>1</sub>                                                                   |

| Figure 5-6 Key waveforms of DCM buck-boost converter                                                                                  |

| Figure 5-7 Buck boost converter during t <sub>1</sub> to t <sub>2</sub>                                                               |

| Figure 5-8 Buck boost converter during period $t_{n2}$ to $(n+1)T_{sw}$                                                               |

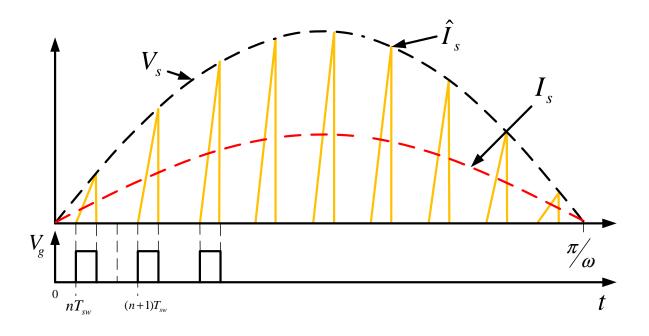

| Figure 5-9 Buck boost input voltage, $V_s$ , and current, $I_s$ , over a half line period                                             |

| Figure 5-10 Boundary conduction of buck boost PFC coverter                                                                            |

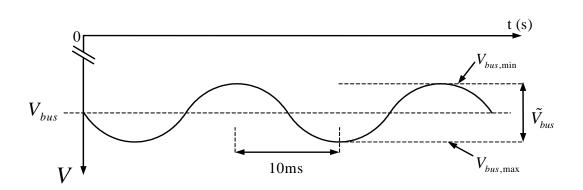

| Figure 5-11 V <sub>bus</sub> waveform                                                                                                 |

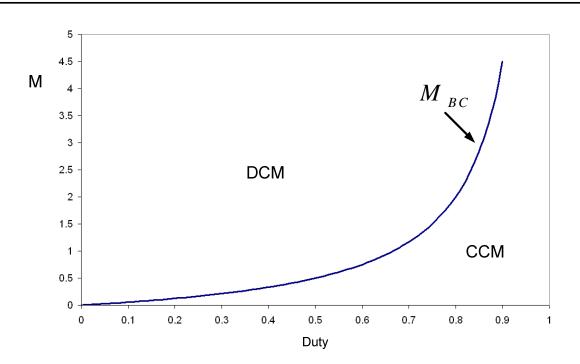

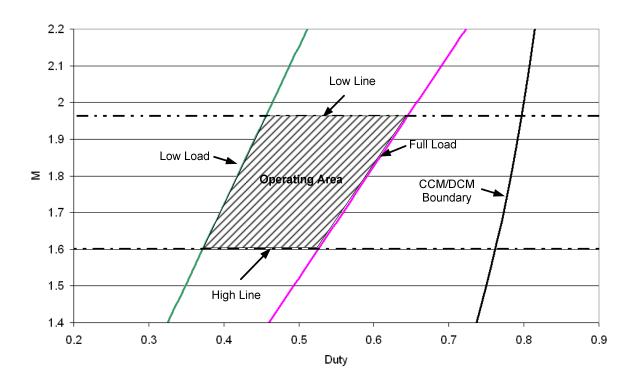

| Figure 5-12 DCM buck boost PFC operating area                                                                                         |

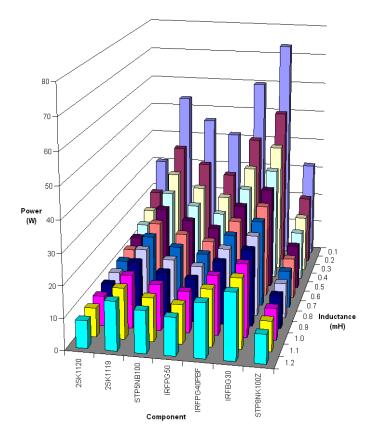

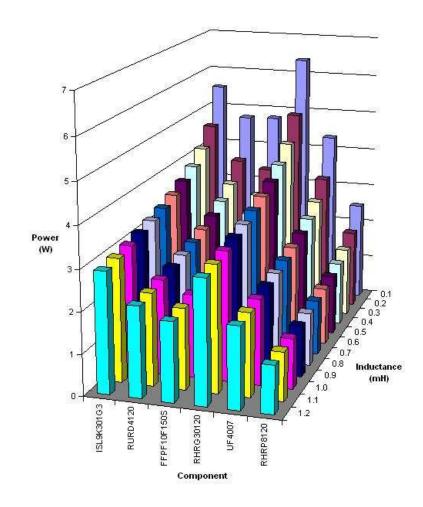

| Figure 5-13 Total losses of MOSFETs versus inductance                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-14 Total diode losses versus inductance                                                                                                                                           |

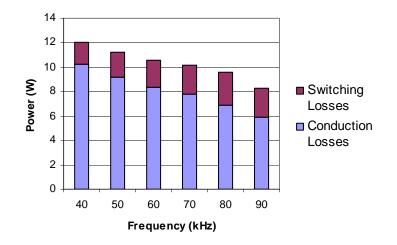

| Figure 5-15 MOSFET STP8NK100Z power losses versus frequency                                                                                                                                |

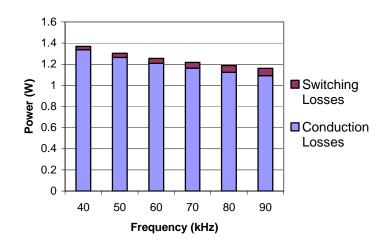

| Figure 5-16 Diode RHRP8120 losses versus frequency                                                                                                                                         |

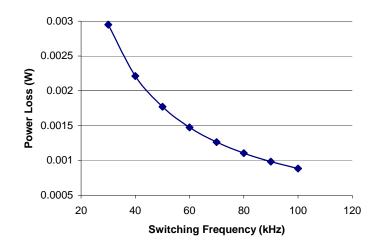

| Figure 5-17 Capacitor losses against converter switching frequency                                                                                                                         |

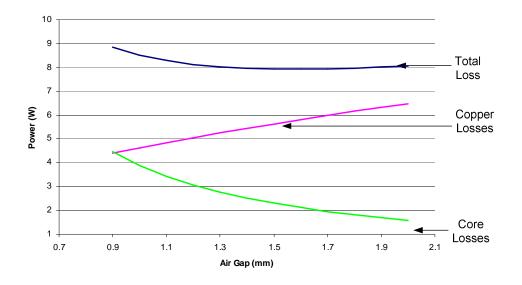

| Figure 5-18 Magnetic losses at various core air gaps                                                                                                                                       |

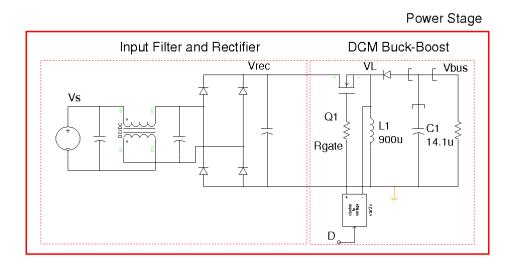

| Figure 5-19 SABER schematic capture of DCM buck boost PFC stage                                                                                                                            |

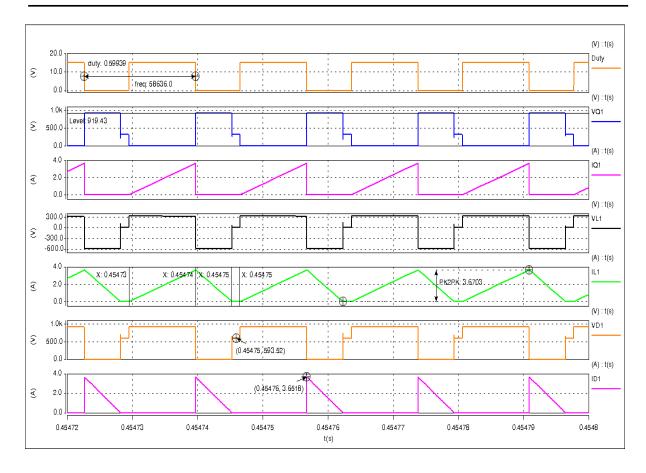

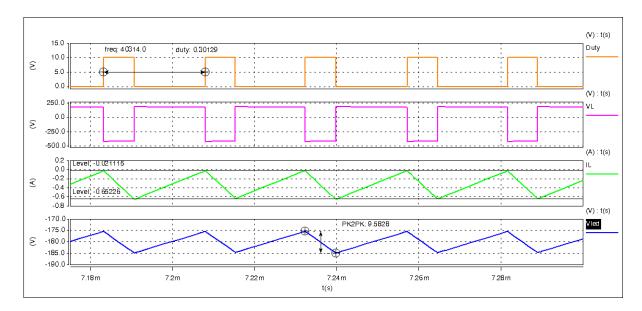

| Figure 5-20 Key steady-state SABER simulated waveforms of the DCM buck boost converter                                                                                                     |

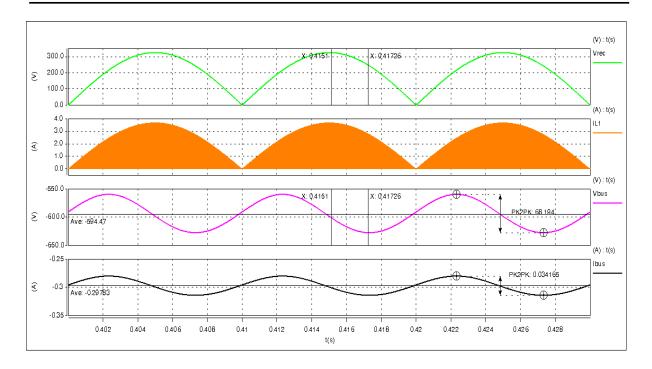

| Figure 5-21 Input current and voltage SABER simulated waveforms of the DCM buck boost converter                                                                                            |

| Figure 5-22 EMC filter for PFC                                                                                                                                                             |

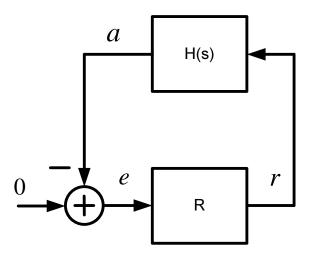

| Figure 6-1 Regulation band control block diagram [86]168                                                                                                                                   |

| Figure 6-2 Modified regulation band control for DCM operation                                                                                                                              |

| Figure 6-3 Buck boost output voltage regulation band limits                                                                                                                                |

| Figure 6-4 Control loop block diagram171                                                                                                                                                   |

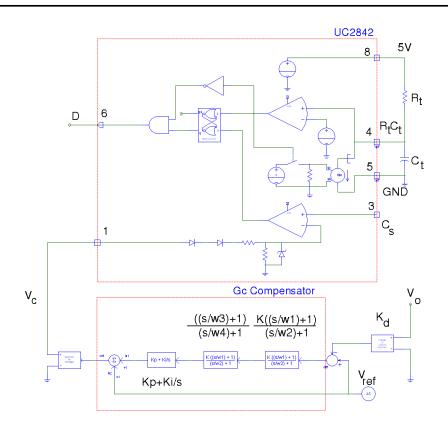

| Figure 6-5 Simplified model of the buck boost and control                                                                                                                                  |

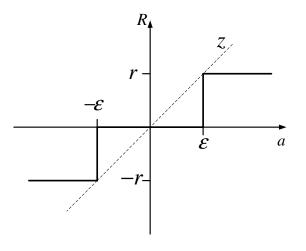

| Figure 6-6 Operation of the relay with dead band174                                                                                                                                        |

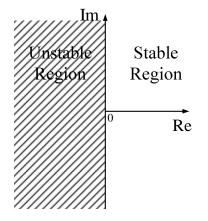

| Figure 6-7 Circle criterion stability requirements                                                                                                                                         |

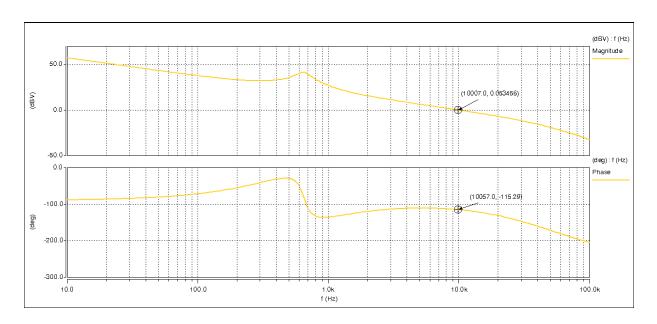

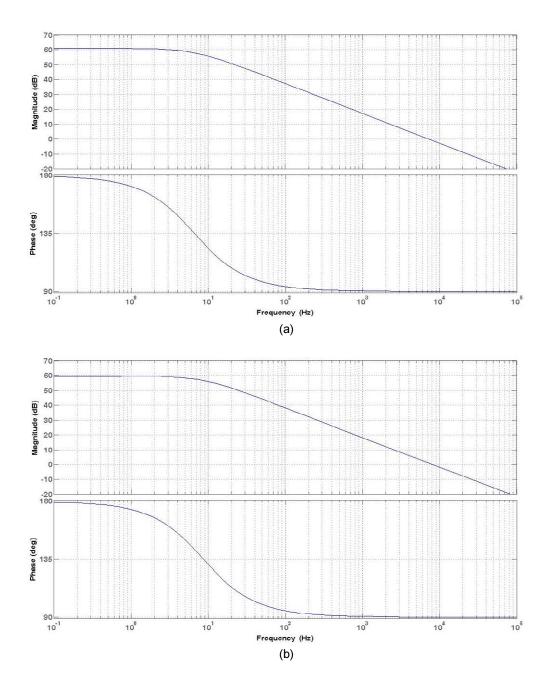

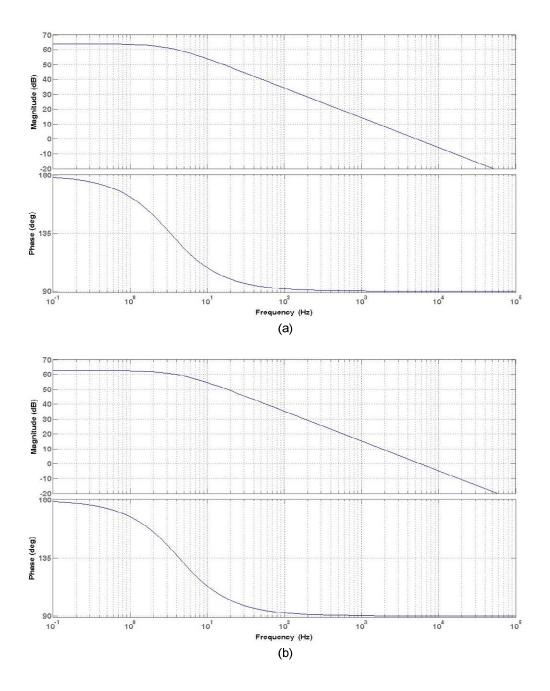

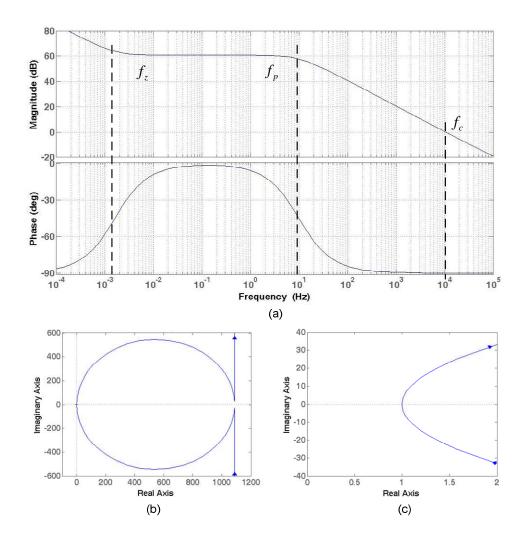

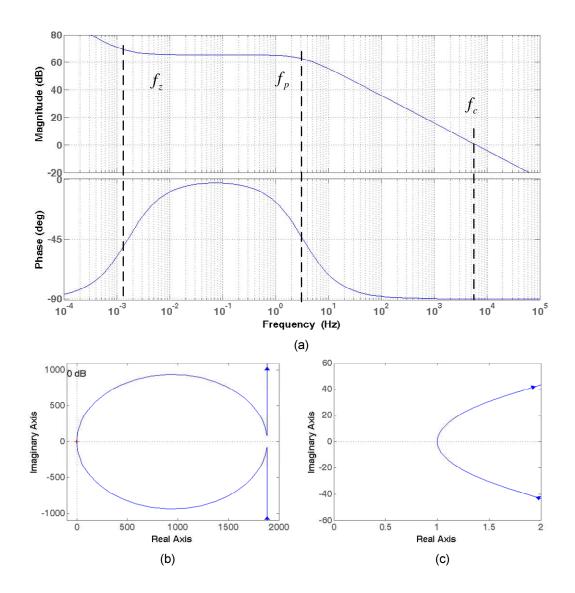

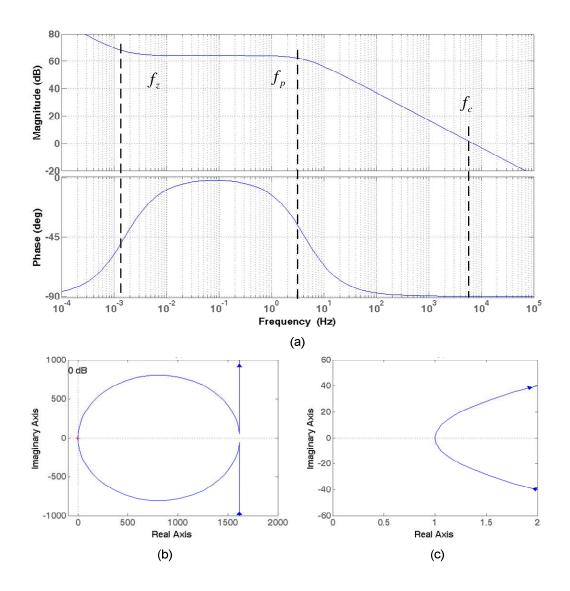

| Figure 6-8 Control-to-output magnitude and phase plots of the buck-boost converter, $V_s=230$ $V_{rms}$ , $P_{out}=180$ W, (a) $V_{bus}=-640$ V, (b) $Vbus=-560$ V                         |

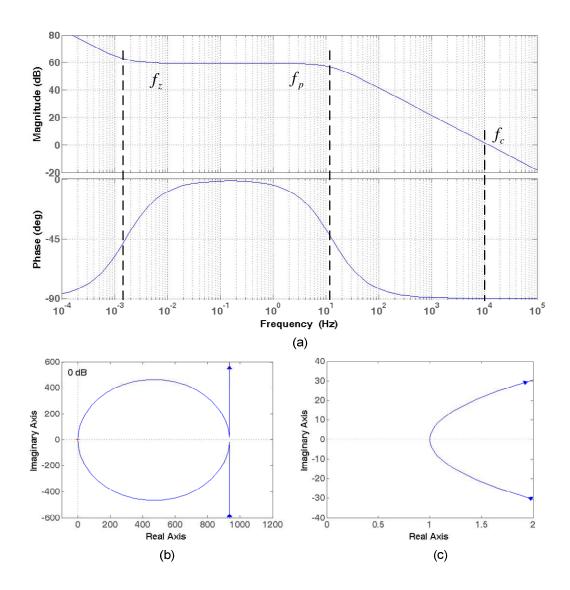

| Figure 6-9 Control-to-output magnitude and phase plots of the buck boost converter, $V_s=230$ $V_{rms}$ , $P_{out}=120$ W, (a) $V_{bus}=-640$ V, (b) $Vbus=-560$ V                         |

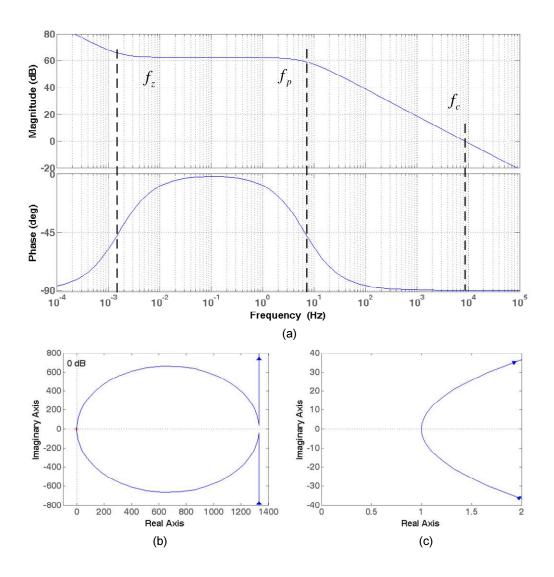

| Figure 6-10 Control-to-output magnitude and phase plots of the buck boost converter, $V_s=230$ $V_{rms}$ , $P_{out}=60$ W, (a) $V_{bus}=-640$ V, (b) $Vbus=-560$ V                         |

| Figure 6-11 Bode plot of $G_c(s)$                                                                                                                                                          |

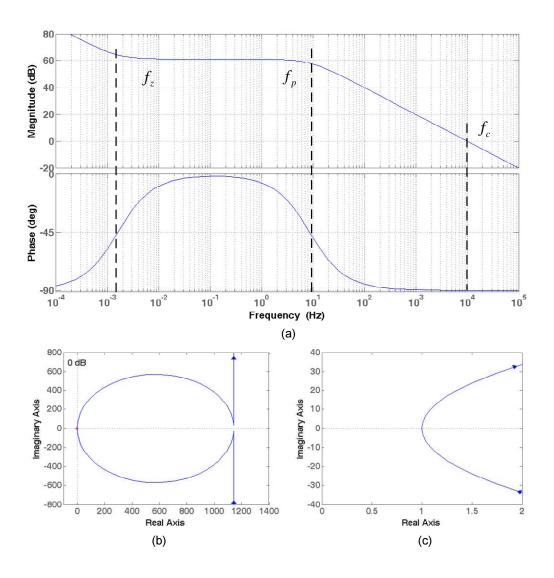

| Figure 6-12 (a) Magnitude and phase of $H(s)$ and R, (b) & (c) plots of $1+zH(j\omega)$ for V <sub>s</sub> = 230 V <sub>rms</sub> , V <sub>bus</sub> = -640 V and P <sub>out</sub> = 180 W |

| Figure 6-13 (a) Magnitude and phase of $H(s)$ and R, (b) & (c) plots of $1 + zH(j\omega)$ for V <sub>s</sub> = 230 V <sub>rms</sub> , V <sub>bus</sub> = -560 V and P <sub>out</sub> = 180 W                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-14 (a) Magnitude and phase of blocks $H(s)$ and R, (b) & (c) plots of $1 + zH(j\omega)$ for $V_s = 230 V_{rms}, V_{bus} = -640 V$ and $P_{out} = 120 W$                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 6-15 (a) Magnitude and phase of $H(s)$ and R, (b) & (c) plots of $1 + zH(j\omega)$ for V <sub>s</sub> = 230 V <sub>rms</sub> , V <sub>bus</sub> = -560 V and P <sub>out</sub> = 120 W                                                                                                                                                                                                                                                                                                                                                    |

| Figure 6-16 (a) Magnitude and phase of $H(s)$ and R, (b) & (c) plots of $1 + zH(j\omega)$ for V <sub>s</sub> = 230 V <sub>rms</sub> , V <sub>bus</sub> = -640 V and P <sub>out</sub> = 60 W                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6-17 (a) Magnitude and phase of blocks $H(s)$ and R, (b) & (c) plots of $1 + zH(j\omega)$ for $V_s = 230 V_{rms} V_{bus} = -560 V$ and $P_{out} = 60 W$                                                                                                                                                                                                                                                                                                                                                                                  |

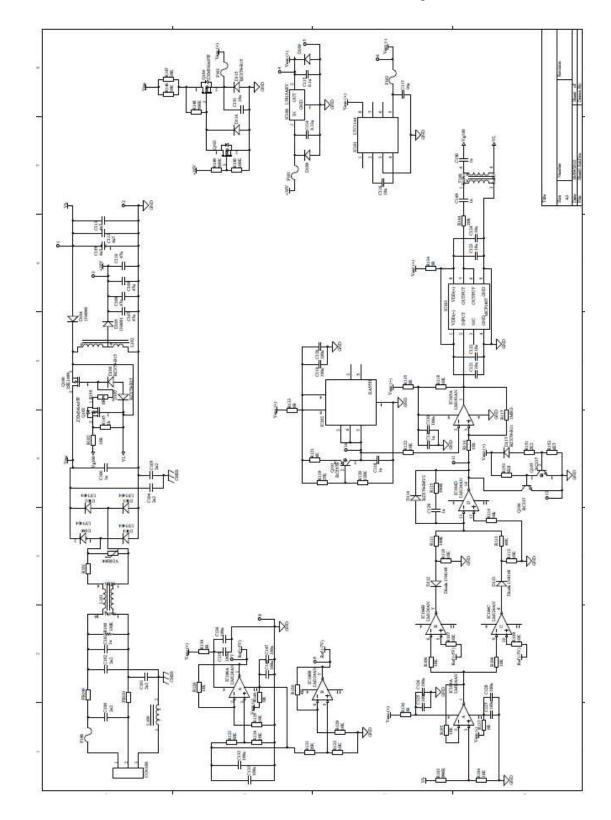

| Figure 6-18 SABER simulation schematic of control loop and PFC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

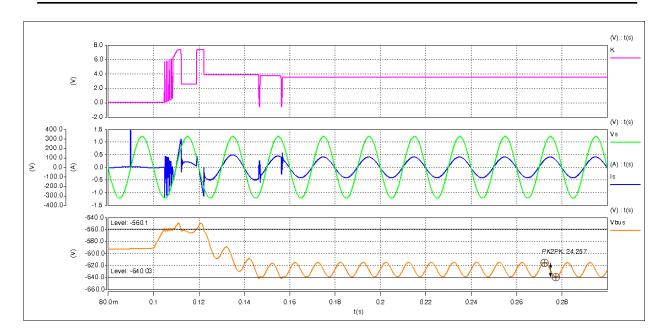

| Figure 6-19 SABER V <sub>bus</sub> response to step load 0 W to 60 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 6-20 SABER V <sub>bus</sub> response to step load 0 W to 120 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6-21 SABER V <sub>bus</sub> response to step load 0 W to 180 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

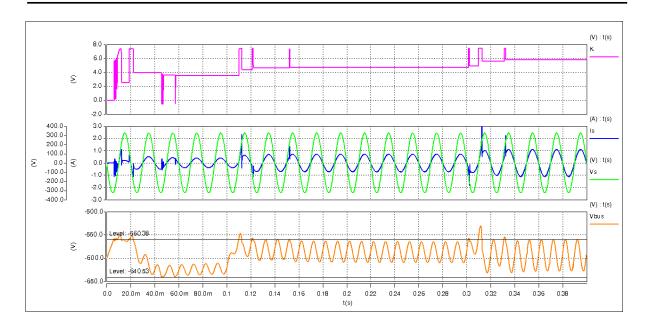

| Figure 6-22 SABER $V_{bus}$ response to step load from 0 W to 60 W to 120 W to 180 W 191                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

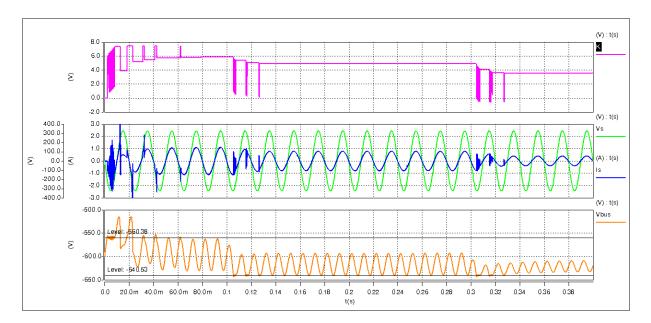

| Figure 6-23 SABER $V_{bus}$ response to step load from 0 W to 180 W to 120 W to 60 W 191                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

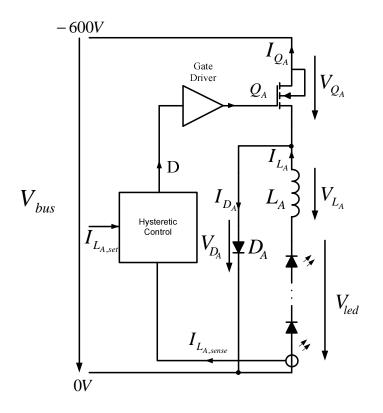

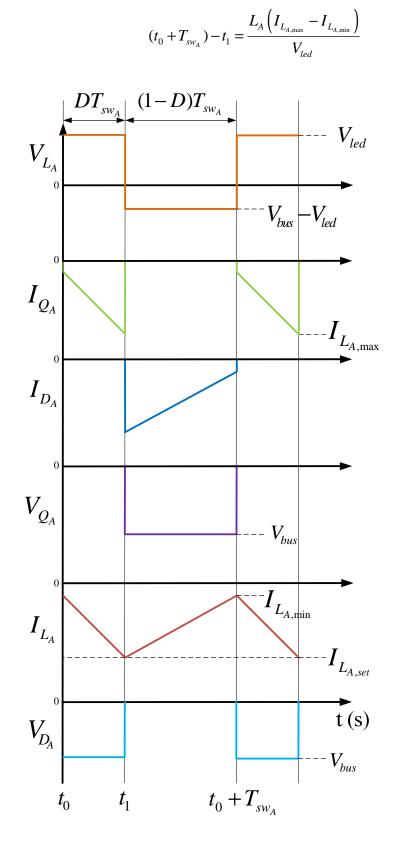

| Figure 6-23 SABER V <sub>bus</sub> response to step load from 0 W to 180 W to 120 W to 60 W 191<br>Figure 7-1 Constant current buck regulator with control                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 7-1 Constant current buck regulator with control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 7-1 Constant current buck regulator with control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

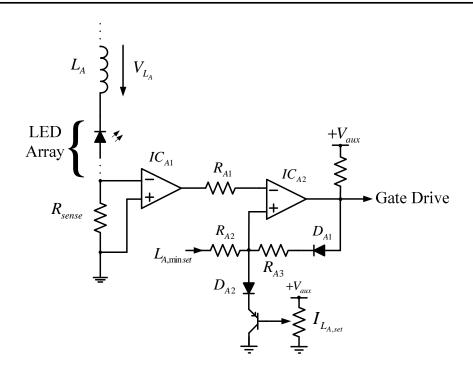

| Figure 7-1 Constant current buck regulator with control    194      Figure 7-2 Key waveforms of buck converter    195      Figure 7-3 Buck Control block diagram    197                                                                                                                                                                                                                                                                                                                                                                         |

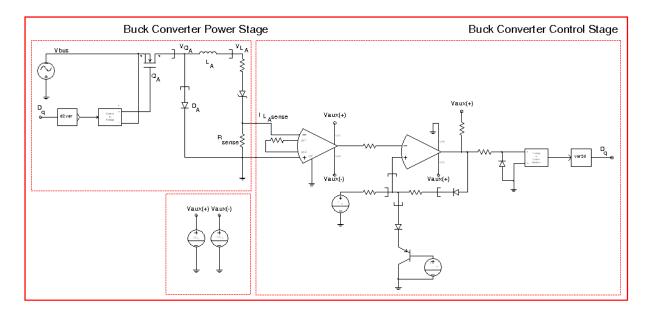

| Figure 7-1 Constant current buck regulator with control194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200                                                                                                                                                                                                                                                                                                                        |

| Figure 7-1 Constant current buck regulator with control194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200Figure 7-5 SABER simulation of key waveforms of constant current HP LED regulator200                                                                                                                                                                                                                                    |

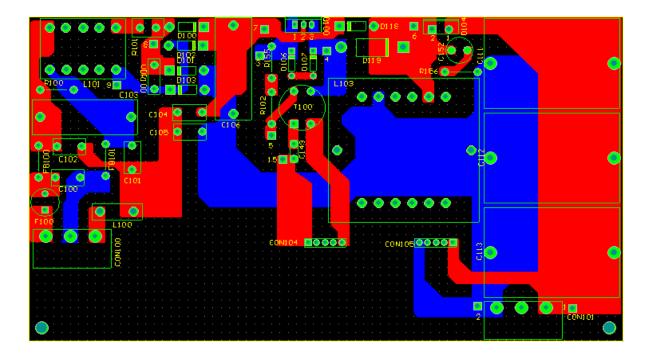

| Figure 7-1 Constant current buck regulator with control194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200Figure 7-5 SABER simulation of key waveforms of constant current HP LED regulator200Figure 7-6 PCB capture of power board layout and tracking201                                                                                                                                                                        |

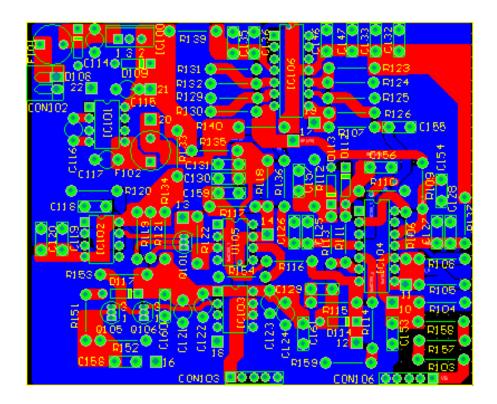

| Figure 7-1 Constant current buck regulator with control.194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200Figure 7-5 SABER simulation of key waveforms of constant current HP LED regulator200Figure 7-6 PCB capture of power board layout and tracking201Figure 7-7 PCB capture of control circuit layout and tracking202                                                                                                       |

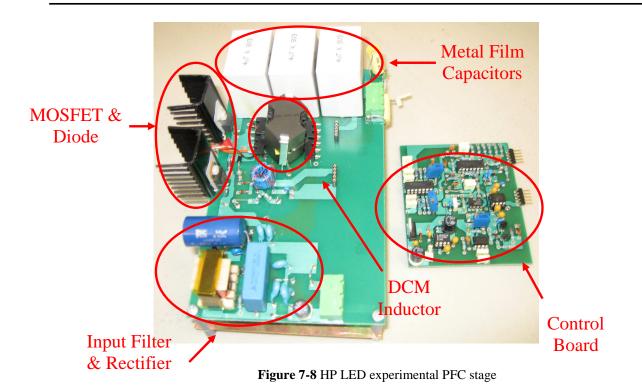

| Figure 7-1 Constant current buck regulator with control.194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200Figure 7-5 SABER simulation of key waveforms of constant current HP LED regulator200Figure 7-6 PCB capture of power board layout and tracking201Figure 7-7 PCB capture of control circuit layout and tracking202Figure 7-8 HP LED experimental PFC stage203                                                            |

| Figure 7-1 Constant current buck regulator with control.194Figure 7-2 Key waveforms of buck converter195Figure 7-3 Buck Control block diagram197Figure 7-4 SABER simulation model of constant current HP LED regulator200Figure 7-5 SABER simulation of key waveforms of constant current HP LED regulator200Figure 7-6 PCB capture of power board layout and tracking201Figure 7-7 PCB capture of control circuit layout and tracking202Figure 7-8 HP LED experimental PFC stage203Figure 7-9 PCB layout of constant current buck regulator204 |

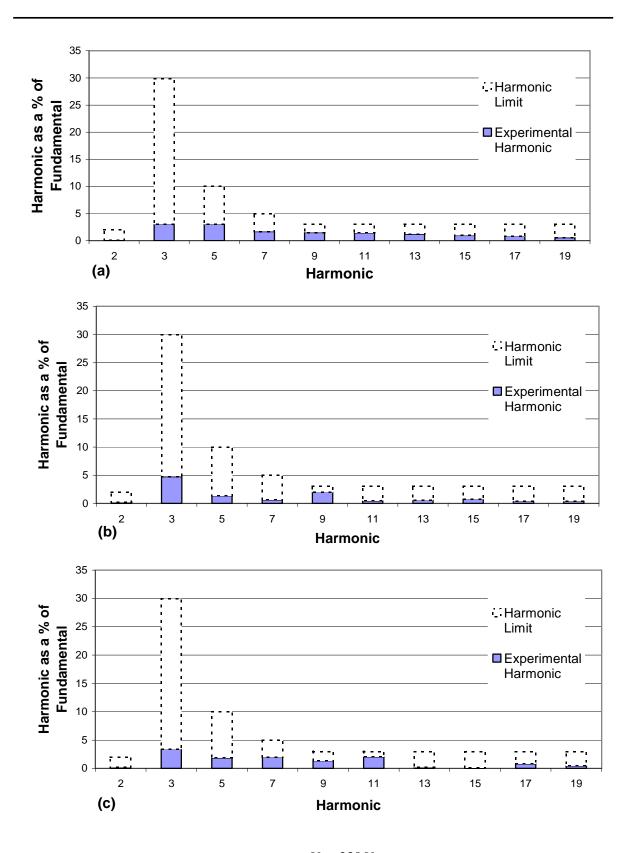

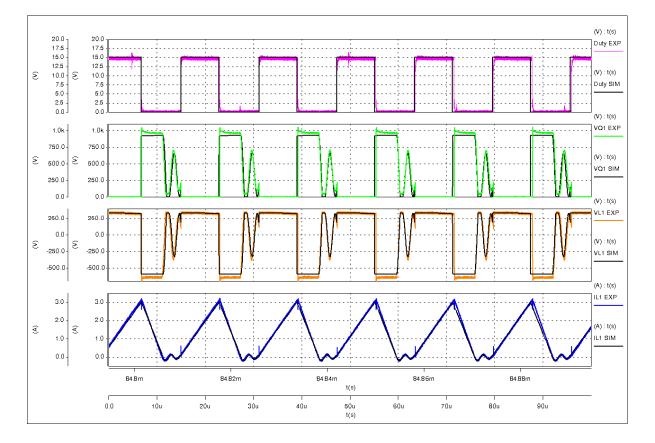

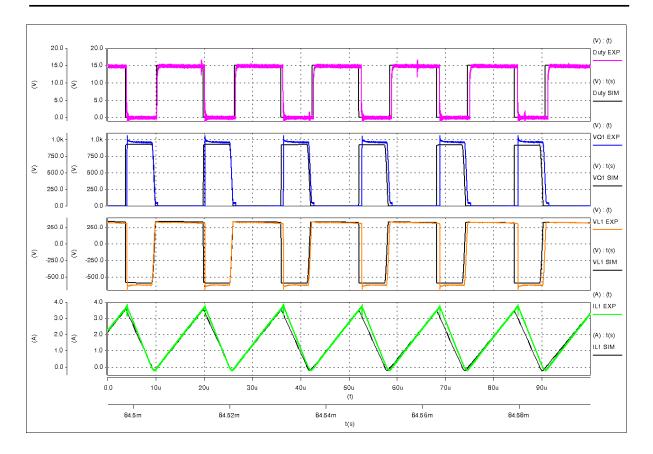

| Figure 7-13 Comparison of simulation and experimental results for $V_s$ =230 $V_{rms}$ at $P_{out}$ =60 W |

|-----------------------------------------------------------------------------------------------------------|

| Figure 7-14 Comparison of simulation and experimental results for $V_s=230V_{rms}$ at $P_{out}=120W$      |

| Figure 7-15 Comparison of simulation and experimental results for $V_s=230V_{rms}$ at $P_{out}=180W$      |

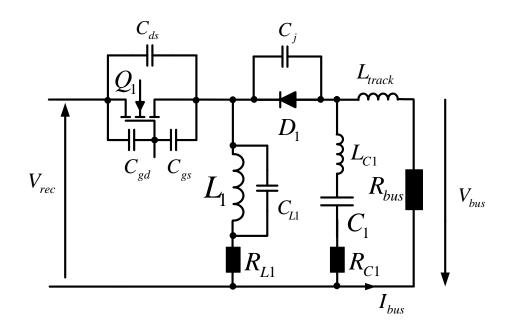

| Figure 7-16 Parasitic components of buck boost                                                            |

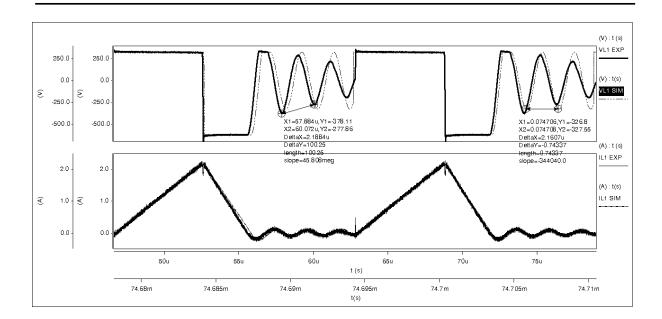

| Figure 7-17 Comparison of simulated and experimental parasitic components                                 |

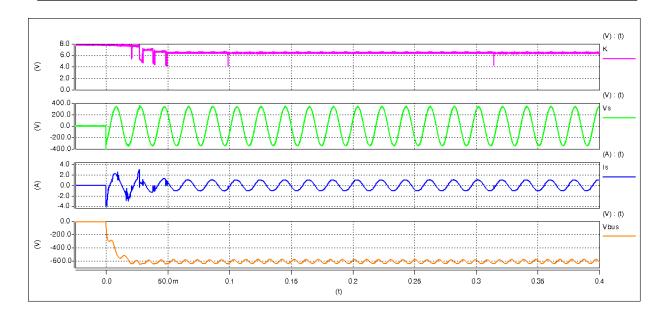

| Figure 7-18 Experimental results of PFC output with a step load of 0 W to 60 W                            |

| Figure 7-19 Experimental results of PFC output with a step load of 0 W to 120 W                           |

| Figure 7-20 Experimental results of PFC output with a step load of 0 W to 180 W                           |

| Figure 7-21 Experimental results of PFC output with a step load of 60 W to 120 W                          |

| Figure 7-22 Experimental results of PFC output with a step load of 120 W to 60 W                          |

| Figure 7-23 Experimental results of PFC output with a step load of 120 W to 180 W                         |

| Figure 7-24 Experimental results of PFC output with a step load of 180 W to 120 W 217                     |

| Figure 7-25 Experimental results of PFC output with a step load of 60 W to 180 W                          |

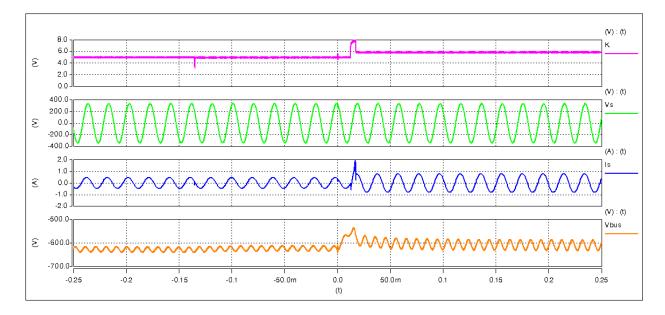

| Figure 7-26 Experimental results of PFC output with a step load of 180 W to 60 W                          |

## **List of Tables**

| Table 1-1 Harmonic limits for; (a) Class C Equipment, (b) Class D Equipment [13]             |     |

|----------------------------------------------------------------------------------------------|-----|

| Table 1-2 Capacitor table comparison                                                         | 56  |

| Table 2-1 S <sup>4</sup> PFC Converter with Integrated Magnetic Specification                | 76  |

| Table 2-2 S <sup>4</sup> PFC key component values                                            |     |

| Table 2-3 Key calculated values of $S^4PFC$ at a $P_{out}$ of 180 W and 90 W                 |     |

| Table 2-4 Integrated magnetic core parameters and operating values at 180 W                  | 89  |

| Table 2-5 Selection of suitable Si MOSFETs for Q                                             | 91  |

| Table 2-6 Selection of suitable Si diodes for D <sub>1</sub>                                 |     |

| Table 2-7 Selection of suitable Si diodes for D <sub>2</sub>                                 |     |

| Table 2-8 Selection of suitable Si diodes for $D_3$ and $D_4$                                | 93  |

| Table 2-9 Selection of suitable Si diodes for D <sub>5</sub>                                 | 93  |

| Table 2-10 Selection of suitable electrolytic capacitors for C <sub>B</sub>                  | 94  |

| Table 2-11 Selection of suitable electrolytic capacitors for Co                              | 94  |

| Table 2-12 A summary of the expected losses detailed in Figure 2-22                          |     |

| Table 2-13 Comparison of key calculated and simulated results                                | 101 |

| Table 3-1 Control parameters for the TDSA component in SABER simulations                     | 110 |

| Table 4-1 S <sup>4</sup> PFC input measurements over various operating conditions            | 128 |

| Table 4-2 Cost analysis of critical components                                               | 134 |

| Table 5-1 HP LED power factor corrector specification                                        | 149 |

| Table 5-2 Selection of suitable Si MOSFETs for Q <sub>1</sub>                                | 150 |

| Table 5-3 Selection of Si ultra fast power diodes                                            | 151 |

| Table 5-4 Section of metallised film capacitors                                              | 151 |

| Table 5-5 Characteristics of the power factor correctors inductor                            | 157 |

| Table 5-6 Estimated power losses of converter components at $P_{out}$ =180 W and $V_{s,min}$ | 158 |

| Table 5-7 Key PFC component parameters at $V_s = 230V_{rms}$ at P <sub>out</sub> =60 W, 120 W and 180 | ) W . 159 |

|-------------------------------------------------------------------------------------------------------|-----------|

| Table 5-8 Comparison of key calculated and simulated                                                  | 162       |

| Table 5-9 PFC converter specification                                                                 | 163       |

| Table 6-1 Summary of control-to-output, $G_p(s)$ , phase and gain bode plots at various               |           |

|                                                                                                       |           |

| Table 6-2 Summary of Figure 6-12 to Figure 6-17                                                       |           |

| Table 7-1 Key calculated values of constant current converter at minimum and maxim                    |           |

| Table 7-2 Characteristics of constant current converter inductor                                      | 198       |

| Table 7-3 Estimated power losses of converter at full load                                            | 199       |

| Table 7-4 Current regulator specifications                                                            | 199       |

| Table 7-5 Measured parameters of PFC                                                                  | 207       |

# Nomenclature

| Symbol                | Description                                        | Unit 2          |

|-----------------------|----------------------------------------------------|-----------------|

| $A_{e}$               | Effective core area                                | $mm^2$          |

| $A_l$                 | Inductance factor                                  | nH<br>2         |

| $A_{_W}$              | Wire cross sectional area                          | $\mathrm{mm}^2$ |

| $A_{(n)}$             | Input current harmonic                             | А               |

| B                     | Flux density                                       | Т               |

| $\hat{B}$             | Peak Flux density                                  | Т               |

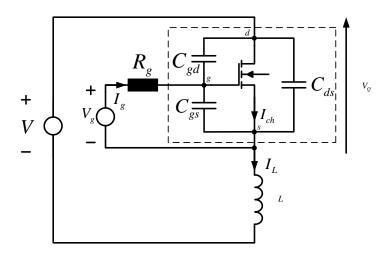

| C<br>C <sub>oss</sub> | Capacitor<br>MOSFET output capacitance             | -<br>F          |

| $C_{iss}$             | MOSFET input capacitance                           | F               |

| $C_{rss}$             | MOSFET reverse transfer                            | F               |

| $C_{gs}$              | capacitance<br>MOSFET gate source capacitance      | F               |

| $C_{_{gd}}$           | MOSFET gate drain capacitance                      | F               |

| $C_{ds}$              | MOSFET drain source capacitance                    | F               |

| D                     | Duty cycle                                         | -               |

| $E_{c}$               | Capacitor energy                                   | J               |

| $f_{line}$            | Line frequency                                     | Hz              |

| $f_{sw}$              | Switching frequency                                | Hz              |

| $f_c$                 | Cross over frequency                               | Hz              |

| $f_p$                 | Pole frequency                                     | Hz              |

| $f_z$                 | Zero frequency                                     | Hz              |

| G                     | Core air gap                                       | mm              |

| $G_c(s)$              | Compensator transfer function                      | -               |

| $G_{c\infty}(s)$      | Compensator gain at high frequency                 | -               |

| $G_{ea}(s)$           | Error amplifier transfer function                  | -               |

| $G_{vs}(s)$           | Boost converter line-to-output transfer function   | -               |

| $G_{v_B}(s)$          | Forward converter line-to-output transfer function | -               |

| $G_{v}(s)$            | S <sup>4</sup> PFC line-to-output transfer         | -               |

| $G_{vd}(s)$           | function<br>CCM forward converter control-to-      | -               |

| $G_{pmw}(s)$          | output transfer function<br>PWM transfer function  | -               |

| $G_{oc}(s)$           | Optocoupler transfer function                      | -               |

| $G_{K_d}(s)$          | Attenuator transfer function                       | -               |

| $G_p(s)$              | Buck boost control-to-output transfer function     | -               |

| $h_{fe}$                                                                                                               | Amplification gain                                                                                                                                                                                                                                                                                                                                                                                               | dB                                                  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| $H_z(s)$                                                                                                               | Open loop transfer function                                                                                                                                                                                                                                                                                                                                                                                      | -                                                   |

|                                                                                                                        | Capacitor current                                                                                                                                                                                                                                                                                                                                                                                                | А                                                   |

| $\hat{I}_{c}$                                                                                                          | Peak capacitor current                                                                                                                                                                                                                                                                                                                                                                                           | А                                                   |

|                                                                                                                        | Diode current                                                                                                                                                                                                                                                                                                                                                                                                    | А                                                   |

| $\hat{I}_{D}$                                                                                                          | Diode current                                                                                                                                                                                                                                                                                                                                                                                                    | А                                                   |

| $I_s$                                                                                                                  | AC line current                                                                                                                                                                                                                                                                                                                                                                                                  | А                                                   |

| $\hat{I}_s$                                                                                                            | Peak AC line current                                                                                                                                                                                                                                                                                                                                                                                             | А                                                   |

| $I_L$                                                                                                                  | Inductor current                                                                                                                                                                                                                                                                                                                                                                                                 | А                                                   |

| $\hat{I}_{L}$                                                                                                          | Peak inductor current                                                                                                                                                                                                                                                                                                                                                                                            | А                                                   |

| I <sub>rec</sub>                                                                                                       | Rectified line current                                                                                                                                                                                                                                                                                                                                                                                           | А                                                   |

| $\hat{I}_{rec}$                                                                                                        | Peak rectified line current                                                                                                                                                                                                                                                                                                                                                                                      | А                                                   |

| $I_Q$                                                                                                                  | MOSFET current                                                                                                                                                                                                                                                                                                                                                                                                   | А                                                   |

| $\hat{I}_Q$                                                                                                            | Peak MOSFET current                                                                                                                                                                                                                                                                                                                                                                                              | А                                                   |

|                                                                                                                        | Output Current                                                                                                                                                                                                                                                                                                                                                                                                   | А                                                   |

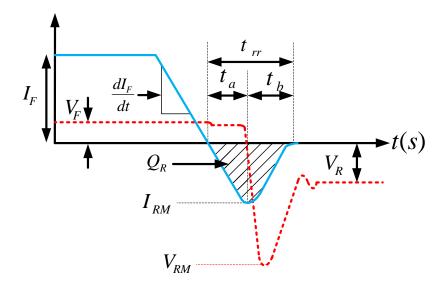

| $\hat{I}_{RM}$                                                                                                         | Peak diode reverse recovery current                                                                                                                                                                                                                                                                                                                                                                              | А                                                   |

| J                                                                                                                      | Current density                                                                                                                                                                                                                                                                                                                                                                                                  | A/mm <sup>2</sup>                                   |

| L                                                                                                                      | Inductor                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                   |

| 1                                                                                                                      | Effective concloneth                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |

| $l_e$                                                                                                                  | Effective core length                                                                                                                                                                                                                                                                                                                                                                                            | mm                                                  |

| $l_w$                                                                                                                  | Total wire length                                                                                                                                                                                                                                                                                                                                                                                                | mm<br>m                                             |

| c                                                                                                                      | · ·                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| $l_w$<br>M                                                                                                             | Total wire length<br>Voltage transfer coefficient                                                                                                                                                                                                                                                                                                                                                                |                                                     |

| l <sub>w</sub><br>M<br>n                                                                                               | Total wire length<br>Voltage transfer coefficient<br>Harmonic number                                                                                                                                                                                                                                                                                                                                             |                                                     |

| $l_w$<br>M<br>n<br>$N_{fb}$                                                                                            | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns                                                                                                                                                                                                                                                                                                        |                                                     |

| $l_w$<br>M<br>n<br>$N_{fb}$<br>$N_L$                                                                                   | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer                                                                                                                                                                                                  |                                                     |

| $l_w$<br>M<br>n<br>$N_{fb}$<br>$N_L$<br>$N_p$                                                                          | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns                                                                                                                                                                                                                                     |                                                     |

| $l_w$ $M$ $n$ $N_{fb}$ $N_L$ $N_p$ $N_s$ $N_r$                                                                         | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns                                                                                                                                                                                         |                                                     |

| $l_w$ $M$ $n$ $N_{fb}$ $N_L$ $N_p$ $N_s$                                                                               | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns                                                             |                                                     |

| $l_w M M n N_{fb} N_{fb} N_L N_p N_s N_r N_{p,s} N_{s,r}$                                                              | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio                                                    | m<br>-<br>-<br>-<br>-<br>-                          |

| $l_{w}$ $M$ $n$ $N_{fb}$ $N_{L}$ $N_{p}$ $N_{s}$ $N_{r}$ $N_{p,s}$ $N_{s,r}$ $P_{in}$                                  | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio<br>Power in                                        | m<br>-<br>-<br>-<br>-<br>-<br>-                     |

| $l_{w}$ $M$ $n$ $N_{fb}$ $N_{L}$ $N_{p}$ $N_{s}$ $N_{r}$ $N_{p,s}$ $N_{s,r}$ $P_{in}$ $P_{in}$                         | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio                                                    | m<br>-<br>-<br>-<br>-<br>-                          |

| $l_{w}$ $M$ $n$ $N_{fb}$ $N_{L}$ $N_{p}$ $N_{s}$ $N_{r}$ $N_{p,s}$ $N_{s,r}$ $P_{in}$ $P_{in}$ $P_{Q,cond}$            | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio<br>Power in<br>Power out<br>MOSFET conduction loss | m<br>-<br>-<br>-<br>-<br>-<br>-<br>W<br>W           |

| $l_{w}$ $M$ $n$ $N_{fb}$ $N_{L}$ $N_{p}$ $N_{s}$ $N_{r}$ $N_{p,s}$ $N_{s,r}$ $P_{in}$ $P_{in}$ $P_{Q,cond}$ $P_{Q,sw}$ | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio<br>Power in<br>Power out<br>MOSFET conduction loss | m<br>-<br>-<br>-<br>-<br>-<br>-<br>W<br>W<br>W<br>W |

| $l_{w}$ $M$ $n$ $N_{fb}$ $N_{L}$ $N_{p}$ $N_{s}$ $N_{r}$ $N_{p,s}$ $N_{s,r}$ $P_{in}$ $P_{in}$ $P_{Q,cond}$            | Total wire length<br>Voltage transfer coefficient<br>Harmonic number<br>Number of turns of feedback turns<br>Number of inductor turns<br>Number of primary transformer turns<br>Number of secondary transformer<br>turns<br>Number of reset transformer turns<br>Primary/ Secondary transformer<br>turns ratio<br>Secondary/ Reset transformer turns<br>ratio<br>Power in<br>Power out<br>MOSFET conduction loss | m<br>-<br>-<br>-<br>-<br>-<br>-<br>W<br>W<br>W<br>W |

| $P_{D,sw}$                 | Diode switching power loss             | W                  |

|----------------------------|----------------------------------------|--------------------|

| $P_D$                      | Total diode power loss                 | W                  |

| P <sub>cu</sub>            | Copper loss                            | W                  |

| P <sub>core</sub>          | Core loss                              | mW/cm <sup>3</sup> |

| $P_s$                      | Real power                             | W                  |

| Q                          | MOSFET                                 | -                  |

| $Q_r$                      | Diode reverse recovery charge          | С                  |

| $Q_{sw}$                   | MOSFET switching gate charge           | С                  |

| $Q_s$                      | Diode on state storage charge          | С                  |

| $Q_o$                      | Q-factor                               | -                  |

| $Q_p$                      | Reactive power                         | VAR                |

| R                          | Resistor                               | -                  |

| $R_{ds_{on}}$              | On-state MOSFET resistance             | Ω                  |

| S                          | Diode snappiness factor                | -                  |

| S <sub>p</sub>             | Apparent power                         | VA 2               |

| S <sub>d</sub><br>T        | Dielectric surface area<br>Transformer | $\mathrm{mm}^2$    |

| $T_{line}$                 | Time period of line frequency          | S                  |

| tine<br>T <sub>sw</sub>    | Time period of switching frequency     | S                  |

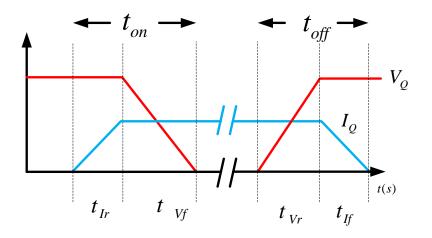

| $T_{on}$                   | MOSFET on time                         | S                  |

| $T_{off}$                  | MOSFET off time                        | S                  |

| $t_{on}$                   | MOSFET turn on time                    | S                  |

| t <sub>off</sub>           | MOSFET turn off time                   | S                  |

| t <sub>rr</sub>            | Diode reverse recovery time            | S                  |

| t <sub>rst</sub>           | Transformer reset time                 | S                  |

| $V_{\scriptscriptstyle B}$ | Boost capacitor voltage                | V                  |

| $\hat{V}_{_{B}}$           | Peak boost capacitor voltage           | V                  |

| $V_{bus}$                  | Bus voltage                            | V                  |

| $	ilde{V}_{bus}$           | Bus voltage high frequency ripple      | V                  |

| $V_L$                      | Inductor voltage                       | V                  |

| $\hat{V_L}$                | Peak inductor voltage                  | V                  |

|                            | AC line voltage                        | V                  |

| $V_s \ \hat{V_s}$          | Peak AC line voltage                   | V                  |

| $V_{rec}$                  | Rectified line voltage                 | V                  |

| $\hat{V}_{rec}$            | Peak rectified line voltage            | V                  |

| $V_Q$                      | MOSFET voltage                         | V                  |

| $\hat{V_Q}$                | Peak MOSFET voltage                    | V                  |

| ¥                          |                                        |                    |

|                   |                                                              | N7              |  |

|-------------------|--------------------------------------------------------------|-----------------|--|

| $V_D$             | Diode Voltage                                                | V               |  |

| $\hat{V_D}$       | Peak diode Voltage                                           | V               |  |

| $V_{g}$           | MOSFET gate voltage                                          | V               |  |

| $\hat{V_g}$       | Peak MOSFET gate voltage                                     |                 |  |

| $V_e$             | Effective core volume                                        | mm <sup>3</sup> |  |

| $V_F$             | Diode forward voltage drop                                   | V               |  |

| $V_o$             | Output voltage                                               | V               |  |

| V <sub>ce</sub>   | Current error amplifier voltage                              | V               |  |

| V <sub>e</sub>    | Error amplifier voltage                                      | V               |  |

| x                 | Arbitrary coefficient                                        | -               |  |

| У                 | Arbitrary coefficient                                        | -               |  |

| Ζ.                | Arbitrary coefficient                                        | -               |  |

| $Z_{o}$           | Output impedance                                             | Ω               |  |

| ε                 | Dielectric constant                                          | _               |  |

| $\eta_{_{PFC}}$   | PFC stage efficiency                                         | %               |  |

| $\eta_{CR}$       | Current regulator efficiency                                 | %               |  |

| ρ                 | Resistivity                                                  | $\Omega cm$     |  |

| $\mu_{_e}$        | Effective permeability                                       | -               |  |