# TRANSACTIONAL DATA STRUCTURES

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Engineering and Physical Sciences

2011

By Kimberley Jarvis Computer Science

# Contents

| A        | Abstract      |                       |                                                 | 11 |  |  |

|----------|---------------|-----------------------|-------------------------------------------------|----|--|--|

| D        | Declaration 1 |                       |                                                 |    |  |  |

| C        | opyri         | $\operatorname{ight}$ |                                                 | 13 |  |  |

| A        | ckno          | wledge                | ements                                          | 14 |  |  |

| 1        | Introduction  |                       |                                                 |    |  |  |

|          | 1.1           | Specu                 | lative execution                                | 15 |  |  |

|          |               | 1.1.1                 | Mutual exclusion                                | 15 |  |  |

|          |               | 1.1.2                 | Speculative execution                           | 16 |  |  |

|          |               | 1.1.3                 | Techniques to support speculative execution     | 16 |  |  |

|          |               | 1.1.4                 | Infrastructure to support speculative execution | 17 |  |  |

|          |               | 1.1.5                 | The problem with locks                          | 18 |  |  |

|          |               | 1.1.6                 | The concurrency problem                         | 19 |  |  |

|          | 1.2           | Memo                  | ry Transactions                                 | 21 |  |  |

|          |               | 1.2.1                 | Transactional Memory systems                    | 21 |  |  |

|          |               | 1.2.2                 | Design priorities                               | 22 |  |  |

|          |               | 1.2.3                 | Design choices                                  | 23 |  |  |

|          |               | 1.2.4                 | The development of Transactional Memory         | 25 |  |  |

|          |               | 1.2.5                 | Software Transactional Memory                   | 25 |  |  |

|          |               | 1.2.6                 | Hardware Transactional Memory                   | 26 |  |  |

|          |               | 1.2.7                 | Ease of programming                             | 28 |  |  |

| <b>2</b> | Cor           | ncurrei               | nt Programming                                  | 30 |  |  |

|          | 2.1           | Concu                 | rrent IO                                        | 31 |  |  |

|          |               | 2.1.1                 | The interaction with external entities          | 31 |  |  |

|   |                   | 2.1.2                                                                                                                           | The database programming model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                                                                                                                                         |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 2.1.3                                                                                                                           | Atomic sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33                                                                                                                                                         |

|   |                   | 2.1.4                                                                                                                           | Previous work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                                                                         |

|   |                   | 2.1.5                                                                                                                           | The Client Server Database Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                                                                         |

|   |                   | 2.1.6                                                                                                                           | Heterogeneous processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                                                                                         |

|   | 2.2               | Parall                                                                                                                          | elism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                                                                         |

|   |                   | 2.2.1                                                                                                                           | Temporal uncertainty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                                                                                                         |

|   |                   | 2.2.2                                                                                                                           | Minimising temporal uncertainty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                                         |

|   |                   | 2.2.3                                                                                                                           | Functional dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                                                                                                                                         |

|   |                   | 2.2.4                                                                                                                           | Mutable shared state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                                                                                                                                                         |

|   |                   | 2.2.5                                                                                                                           | Coordinating concurrent actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                                                                         |

|   |                   | 2.2.6                                                                                                                           | Previous work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44                                                                                                                                                         |

|   |                   | 2.2.7                                                                                                                           | The speculative execution of functional programs $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                                         |

|   |                   | 2.2.8                                                                                                                           | Composable atomic sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                                                         |

|   | 2.3               | Comp                                                                                                                            | atibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                                                                                                                         |

|   |                   | 2.3.1                                                                                                                           | Disruptive changes to existing software                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                                                                                                                         |

|   |                   | 2.3.2                                                                                                                           | Compatibility with existing software                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                                                                                                                         |

|   |                   | 2.3.3                                                                                                                           | Making concurrent programs easier to write                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                         |

|   |                   |                                                                                                                                 | o i i o i o i o i o i o i o i o i o i o                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                            |

| 3 | Mai               |                                                                                                                                 | ng State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52                                                                                                                                                         |

| 3 | <b>Mai</b><br>3.1 | intaini                                                                                                                         | ng State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>52</b><br>53                                                                                                                                            |

| 3 |                   | intaini                                                                                                                         | ng State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

| 3 |                   | i <b>ntaini</b><br>Specul                                                                                                       | ng State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                                                                                         |

| 3 |                   | intaini<br>Specul<br>3.1.1                                                                                                      | ng State<br>lative State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53<br>53                                                                                                                                                   |

| 3 |                   | intaini<br>Specu<br>3.1.1<br>3.1.2                                                                                              | ng State<br>lative State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53<br>53<br>55                                                                                                                                             |

| 3 |                   | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3                                                                                   | ng State      lative State      The memory wall      Immutable memory      Memory bandwidth      The effect of speculation                                                                                                                                                                                                                                                                                                                                                                                        | 53<br>53<br>55<br>56                                                                                                                                       |

| 3 |                   | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                          | ng State      lative State      The memory wall      Immutable memory      Memory bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                       | 53<br>53<br>55<br>56<br>57                                                                                                                                 |

| 3 |                   | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                        | ng State         lative State         The memory wall         Immutable memory         Memory bandwidth         The effect of speculation         Moving the bottleneck                                                                                                                                                                                                                                                                                                                                           | 53<br>53<br>55<br>56<br>57<br>58                                                                                                                           |

| 3 | 3.1               | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                        | ng State         lative State         The memory wall         Immutable memory         Memory bandwidth         The effect of speculation         Moving the bottleneck         Cache coherency                                                                                                                                                                                                                                                                                                                   | 53<br>53<br>55<br>56<br>57<br>58<br>59                                                                                                                     |

| 3 | 3.1               | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut                                               | ng State         lative State         The memory wall         Immutable memory         Memory bandwidth         The effect of speculation         Moving the bottleneck         Cache coherency         table Data Structures                                                                                                                                                                                                                                                                                     | 53<br>53<br>55<br>56<br>57<br>58<br>59<br>61                                                                                                               |

| 3 | 3.1               | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut<br>3.2.1                                      | ng State         lative State         The memory wall         Immutable memory         Memory bandwidth         The effect of speculation         Moving the bottleneck         Cache coherency         table Data Structures         Supporting speculation                                                                                                                                                                                                                                                      | 53<br>55<br>56<br>57<br>58<br>59<br>61<br>61                                                                                                               |

| 3 | 3.1               | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut<br>3.2.1<br>3.2.2<br>3.2.3                    | ng State lative State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>53</li> <li>53</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>61</li> <li>61</li> <li>62</li> </ol>                         |

| 3 | 3.1<br>3.2        | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut<br>3.2.1<br>3.2.2<br>3.2.3                    | ng State lative State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>53</li> <li>53</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>61</li> <li>61</li> <li>62</li> <li>62</li> </ul>             |

| 3 | 3.1<br>3.2        | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut<br>3.2.1<br>3.2.2<br>3.2.3<br>Path (          | ng State lative State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>53</li> <li>53</li> <li>55</li> <li>56</li> <li>57</li> <li>58</li> <li>59</li> <li>61</li> <li>61</li> <li>62</li> <li>62</li> <li>65</li> </ol> |

| 3 | 3.1<br>3.2        | intainin<br>Specul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Immut<br>3.2.1<br>3.2.2<br>3.2.3<br>Path 0<br>3.3.1 | ng State         lative State         The memory wall         Immutable memory         Immutable memory         Memory bandwidth         The effect of speculation         The effect of speculation         Moving the bottleneck         Cache coherency         table Data Structures         Supporting speculation         Immutable Data Structures         Immutable Data Structures         Immutable Data Structures         Immutability and concurrency         Implementing Immutable Data Structures | 53<br>55<br>56<br>57<br>58<br>59<br>61<br>61<br>62<br>62<br>65<br>65                                                                                       |

|   | 3.4 | Binary  | $\gamma$ Trees                                                                                                                                | 78 |

|---|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.4.1   | A flexible Immutable Data Structure design                                                                                                    | 78 |

|   |     | 3.4.2   | The Canonical Binary Tree                                                                                                                     | 79 |

|   |     | 3.4.3   | Previous work                                                                                                                                 | 82 |

|   | 3.5 | Abstra  | act Data Types for Immutable Data                                                                                                             | 35 |

|   |     | 3.5.1   | Priority queue                                                                                                                                | 35 |

|   |     | 3.5.2   | Directed min-tree                                                                                                                             | 90 |

|   |     | 3.5.3   | Deque                                                                                                                                         | 93 |

|   |     | 3.5.4   | Directed deque                                                                                                                                | 94 |

|   |     | 3.5.5   | Map                                                                                                                                           | 98 |

|   |     | 3.5.6   | Interval tree with sentinel                                                                                                                   | )2 |

|   |     | 3.5.7   | Vector $\ldots \ldots \ldots$ | )3 |

|   |     | 3.5.8   | Directed sequence                                                                                                                             | )7 |

|   |     | 3.5.9   | Previous work                                                                                                                                 | )9 |

|   | 3.6 | Balano  | $\operatorname{ring}$                                                                                                                         | 10 |

|   |     | 3.6.1   | Balancing schemes                                                                                                                             | 10 |

|   |     | 3.6.2   | Balancing the Canonical Binary Tree                                                                                                           | 12 |

|   |     | 3.6.3   | Previous work                                                                                                                                 | 18 |

|   |     | 3.6.4   | Utility functions                                                                                                                             | 18 |

|   |     | 3.6.5   | Optimisation                                                                                                                                  | 18 |

|   |     | 3.6.6   | Amortised analysis                                                                                                                            | 20 |

|   | 3.7 | Memo    | ry Management                                                                                                                                 | 22 |

|   |     | 3.7.1   | Memory allocation and reclamation                                                                                                             | 22 |

|   |     | 3.7.2   | Previous work                                                                                                                                 | 23 |

| 4 | Acc | essing  | State 12                                                                                                                                      | 24 |

| - | 4.1 |         | $izable objects \dots \dots$            |    |

|   |     | 4.1.1   | Weak isolation                                                                                                                                |    |

|   |     | 4.1.2   | Strong isolation                                                                                                                              |    |

|   |     | 4.1.3   | Linearizability $\ldots \ldots 12$                        |    |

|   |     | 4.1.4   | Previous work                                                                                                                                 | 28 |

|   |     | 4.1.5   | The semantics of weak isolation                                                                                                               | 28 |

|   |     | 4.1.6   | Isolation pathologies                                                                                                                         | 29 |

|   |     | 4.1.7   | Nested transactions                                                                                                                           | 30 |

|   | 4.2 | Persist | tent Data Structures                                                                                                                          | 33 |

|   |     | 4.2.1   | Accessing past versions                                                                                                                       | 33 |

|   |     |         |                                                                                                                                               |    |

|   |     | 4.2.2   | Persistence                                             |

|---|-----|---------|---------------------------------------------------------|

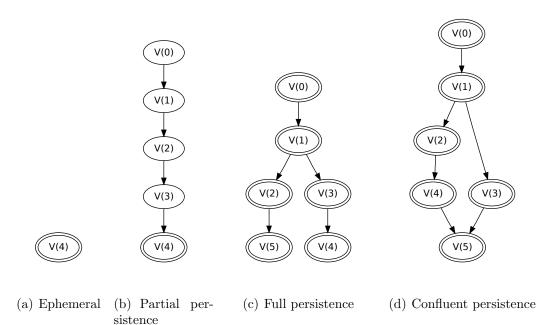

|   |     | 4.2.3   | The classification of persistent data structures 135    |

|   |     | 4.2.4   | Previous work                                           |

|   |     | 4.2.5   | The classification of Transactional Data Structures 138 |

|   | 4.3 | Entang  | glement $\ldots$ $\ldots$ $\ldots$ $140$                |

|   |     | 4.3.1   | Fine grained irregular parallelism                      |

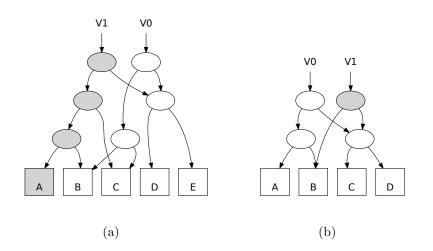

|   |     | 4.3.2   | The composition of Immutable Data Structures 141        |

|   |     | 4.3.3   | Entanglement and Persistence                            |

|   |     | 4.3.4   | Previous work                                           |

|   |     | 4.3.5   | Low overhead checkpointing                              |

|   | 4.4 | Minim   | um Spanning Tree                                        |

|   |     | 4.4.1   | Experiment                                              |

|   |     | 4.4.2   | Results                                                 |

|   |     | 4.4.3   | Method                                                  |

|   |     | 4.4.4   | Serial Graph Colouring Implementation                   |

|   |     | 4.4.5   | Serial No-Colouring Implementation                      |

|   |     | 4.4.6   | The concurrent implementation of Prim's algorithm 153   |

|   |     | 4.4.7   | Concurrent Graph Colouring Implementation 154           |

|   |     | 4.4.8   | Previous work                                           |

|   |     | 4.4.9   | Concurrent No-Colouring Implementation                  |

|   |     | 4.4.10  | The performance of the Concurrent No-Colouring Imple-   |

|   |     |         | mentation                                               |

| 5 | Cor | ncurren | acy Control 159                                         |

|   | 5.1 |         | buted Concurrency Control                               |

|   |     |         | Centralised concurrency control                         |

|   |     | 5.1.2   | Distributed concurrency control                         |

|   |     | 5.1.3   | Transaction management                                  |

|   |     | 5.1.4   | Previous work                                           |

|   |     | 5.1.5   | Time Stamp Ordering 163                                 |

|   |     | 5.1.6   | Programmer productivity                                 |

|   | 5.2 |         | sability $\ldots$ $\ldots$ $\ldots$ $166$               |

|   |     | 5.2.1   | Simultaneous access                                     |

|   |     | 5.2.2   | Implementing concurrency control                        |

|   |     | 5.2.3   | Concurrent semantics                                    |

|   |     | 5.2.4   | Simultaneous semantics                                  |

|   |     |         |                                                         |

|   |     | 5.2.5   | Previous work                                                                 | 70         |

|---|-----|---------|-------------------------------------------------------------------------------|------------|

|   |     | 5.2.6   | Variables                                                                     | 71         |

|   |     | 5.2.7   | Functions and operations                                                      | 72         |

|   |     | 5.2.8   | Validate function                                                             | 76         |

|   |     | 5.2.9   | Meta-data                                                                     | 76         |

|   | 5.3 | Conflu  | ence $\ldots$ $\ldots$ $\ldots$ $\ldots$ $17$                                 | 79         |

|   |     | 5.3.1   | Simultaneous modifications                                                    | 79         |

|   |     | 5.3.2   | Meld Function                                                                 | 79         |

|   |     | 5.3.3   | Previous work                                                                 | 31         |

| 6 | Con | tentio  | n Management 18                                                               | 3          |

|   | 6.1 | Progre  | ess and Contention Management                                                 | 34         |

|   |     | 6.1.1   | Blocking                                                                      | 34         |

|   |     | 6.1.2   | Guaranteed progress                                                           | 35         |

|   |     | 6.1.3   | The Dining Philosophers                                                       | 35         |

|   |     | 6.1.4   | Previous work                                                                 | 38         |

|   | 6.2 | Non-bl  | locking Algorithms                                                            | )0         |

|   |     | 6.2.1   | Ensuring serialisability without blocking                                     | )0         |

|   |     | 6.2.2   | Lock-free serialisability                                                     | )1         |

|   |     | 6.2.3   | Previous work                                                                 | )3         |

|   |     | 6.2.4   | Non-blocking evaluation                                                       | <b>)</b> 4 |

|   | 6.3 | Produ   | cer Consumer Queue                                                            | )8         |

|   |     | 6.3.1   | $Experiment  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | )8         |

|   |     | 6.3.2   | Results                                                                       | )9         |

|   |     | 6.3.3   | Method                                                                        | )4         |

|   |     | 6.3.4   | Implementation                                                                | )4         |

|   |     | 6.3.5   | Workload simulation                                                           | )6         |

|   |     | 6.3.6   | Previous work                                                                 | )7         |

|   |     | 6.3.7   | Mailbox Queue performance                                                     | )8         |

|   |     | 6.3.8   | Messaging Queue performance                                                   | )9         |

|   |     | 6.3.9   | Ease of implementation                                                        | )9         |

|   |     | 6.3.10  | Ease of programming                                                           | 0          |

|   |     | 6.3.11  | Scalability                                                                   | 0          |

|   |     | 6.3.12  | Progress                                                                      | 1          |

|   | 6.4 | Distrib | pution and Scheduling                                                         | 12         |

|   |     | 6.4.1   | Scheduling                                                                    | 12         |

|        | 6.4.2        | Load-balance                                          | 213 |  |

|--------|--------------|-------------------------------------------------------|-----|--|

|        | 6.4.3        | Scheduling parallel work                              | 214 |  |

|        | 6.4.4        | Previous work                                         | 215 |  |

|        | 6.4.5        | Transaction granularity                               | 216 |  |

| 7 Con  | 7 Conclusion |                                                       | 218 |  |

| 7.1    | The fle      | ow of time                                            | 218 |  |

|        | 7.1.1        | The notion of the flow of time as a global phenomenon | 218 |  |

|        | 7.1.2        | The notion of the flow of time as a local phenomenon  | 220 |  |

| 7.2    | Future       | ework                                                 | 223 |  |

| 7.3    | Summ         | ary                                                   | 229 |  |

| Glossa | Glossary     |                                                       |     |  |

| Biblio | graphy       |                                                       | 237 |  |

| Word c | ount 70      | 552                                                   |     |  |

# List of Tables

| 3.1 | Directed min-tree implementation                    |

|-----|-----------------------------------------------------|

| 3.2 | Directed deque implementation                       |

| 3.3 | Map Implementation                                  |

| 3.4 | Directed sequence implementation                    |

| 4.1 | Persistence types for Transactional Data Structures |

| 5.1 | Cap topology and granularity of concurrency         |

| 6.1 | The maximum throughput of a Mailbox Queue           |

# List of Figures

| 1.1  | Observations about scalable concurrent systems $\ . \ . \ . \ . \ .$ | 23  |

|------|----------------------------------------------------------------------|-----|

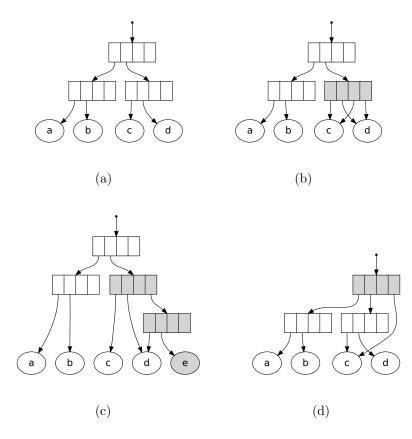

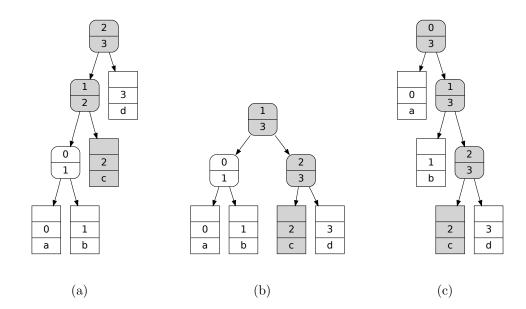

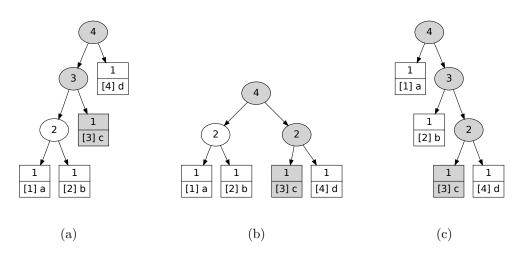

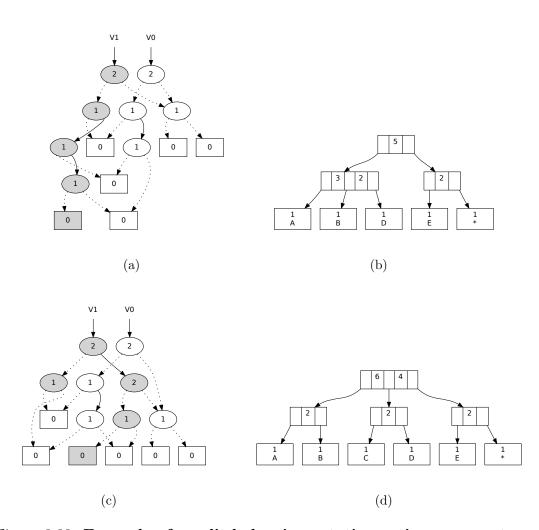

| 3.1  | Insertion and deletion from an immutable deque                       | 63  |

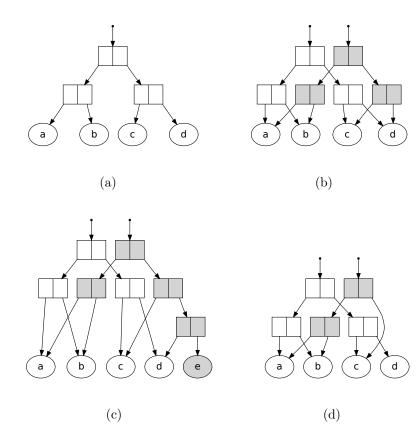

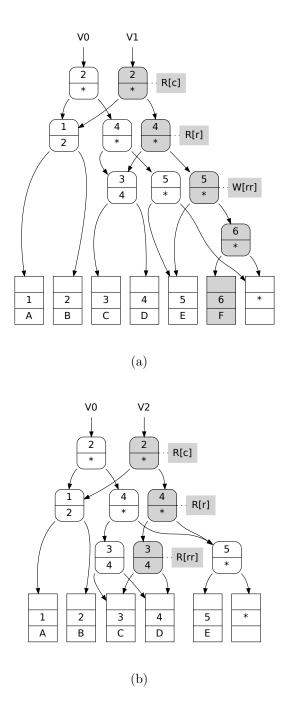

| 3.2  | Full copying technique                                               | 66  |

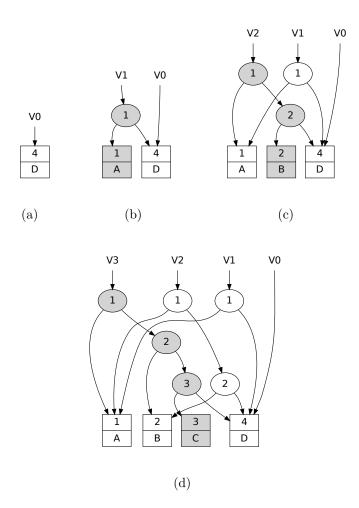

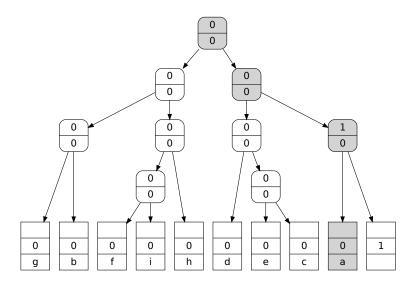

| 3.3  | Path copying technique                                               | 67  |

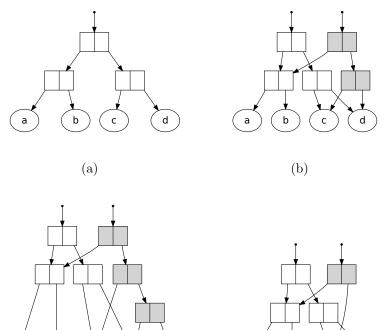

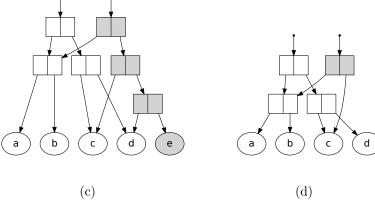

| 3.4  | Fat node technique                                                   | 69  |

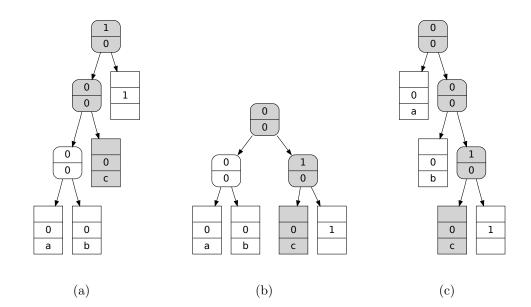

| 3.5  | Node copying technique                                               | 71  |

| 3.6  | Bracket and remove bracket operations                                | 73  |

| 3.7  | Immutable add bracket and remove bracket operations $\ldots$ .       | 75  |

| 3.8  | Immutable insert and delete operations                               | 76  |

| 3.9  | The leaf to root path copying technique                              | 77  |

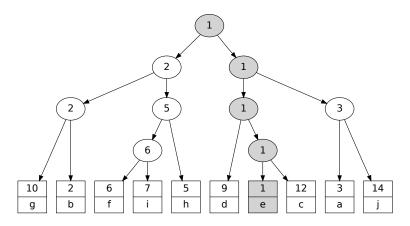

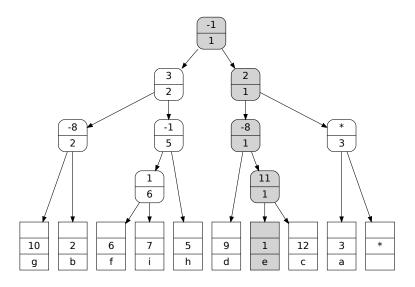

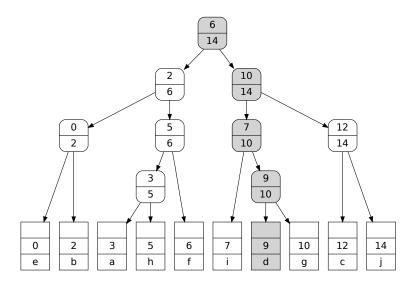

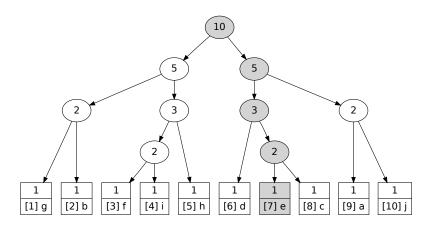

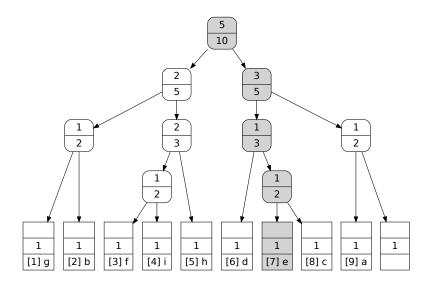

| 3.10 | Example Min-tree                                                     | 86  |

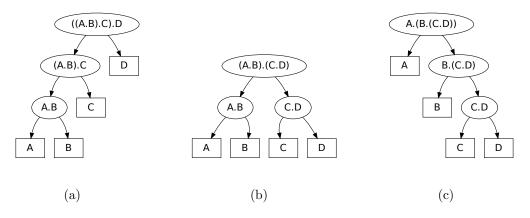

| 3.11 | Associativity property of a min-tree                                 | 86  |

| 3.12 | Insertion and removal of an element in a min-tree                    | 87  |

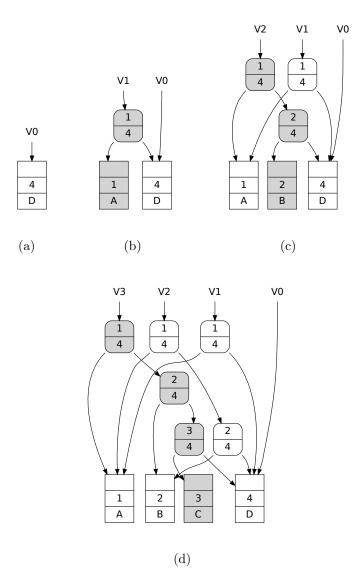

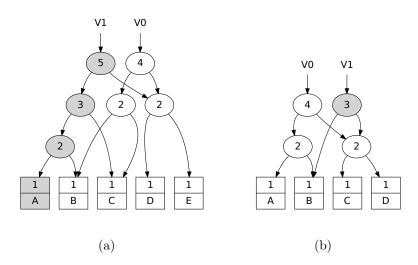

| 3.13 | Animation showing the growth of a min-tree                           | 89  |

| 3.14 | Example Directed min-tree                                            | 90  |

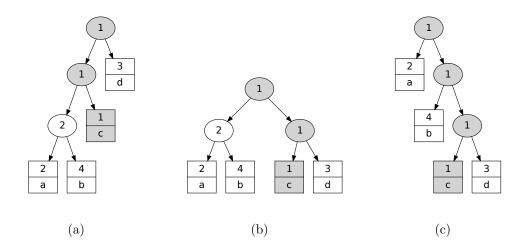

| 3.15 | Example Deque                                                        | 93  |

| 3.16 | Insertion and removal of an element in a deque                       | 94  |

| 3.17 | Animation showing the growth of a deque                              | 95  |

| 3.18 | Example Directed deque                                               | 96  |

| 3.19 | Associativity property of a directed deque                           | 97  |

| 3.20 | Example interval tree                                                | 98  |

| 3.21 | Associativity property of an interval tree                           | 99  |

| 3.22 | Insertion and removal of an element in an interval tree              | 100 |

| 3.23 | Animation showing the growth of an interval tree                     | 101 |

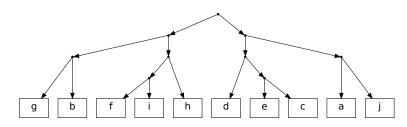

| 3.24 | Example Sequence                                                     | 103 |

| 3.25 | Associativity property of a sequence tree                            | 104 |

| 3.26 | Insertion and removal of an element in a sequence tree $\ldots$      | 105 |

|      |                                                                      |     |

| 3.27 | Animation showing the growth of an immutable sequence tree $\ .$ . | 106 |

|------|--------------------------------------------------------------------|-----|

| 3.28 | Example Directed sequence                                          | 108 |

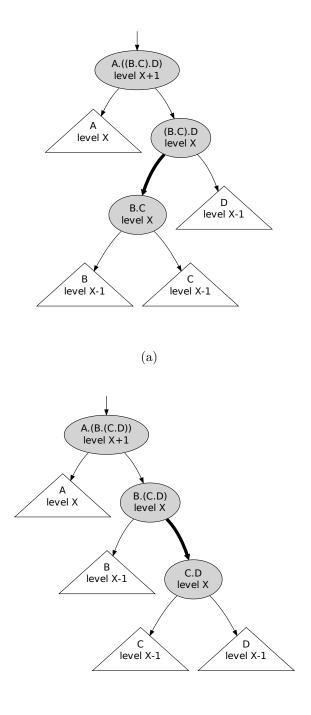

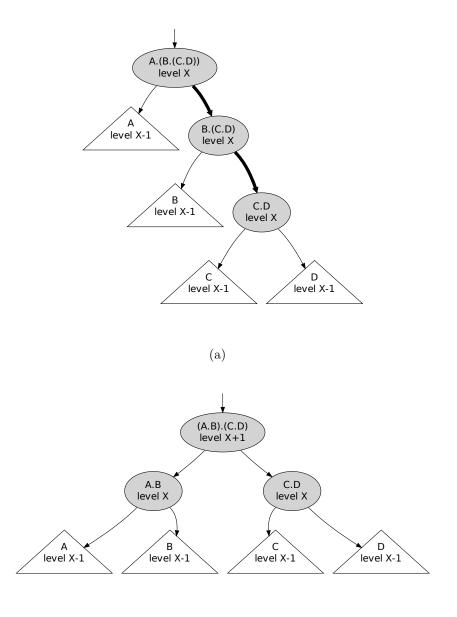

| 3.29 | The associativity property permits balancing                       | 111 |

| 3.30 | A skew balancing rotation                                          | 113 |

| 3.31 | A split rotation                                                   | 114 |

| 3.32 | Example of a skew balancing rotation acting on a vector $\ldots$ . | 115 |

| 3.33 | Example of a split balancing rotation acting on a vector           | 116 |

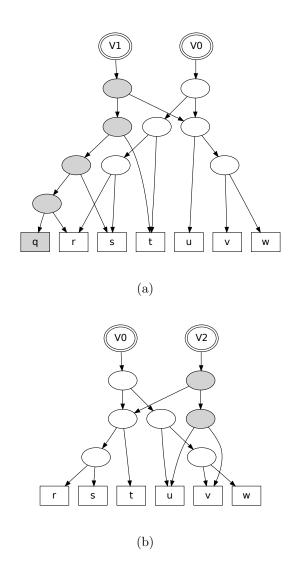

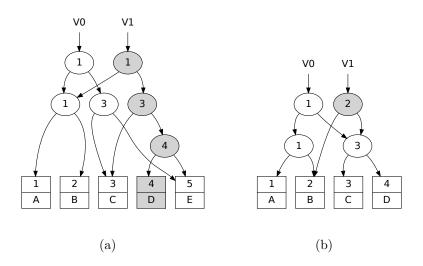

| 4.1  | Version graphs                                                     | 136 |

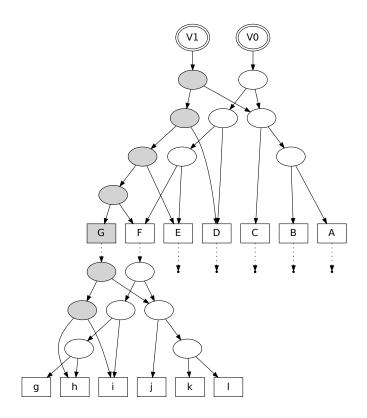

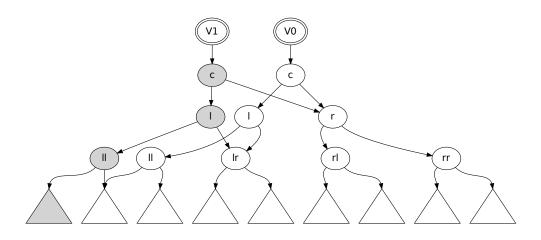

| 4.2  | A pair of entangled queues                                         | 142 |

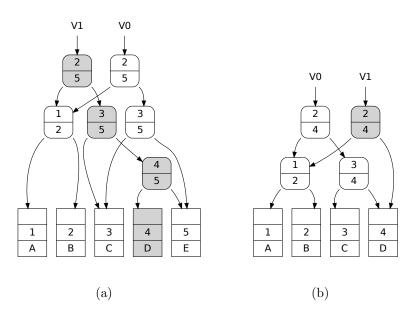

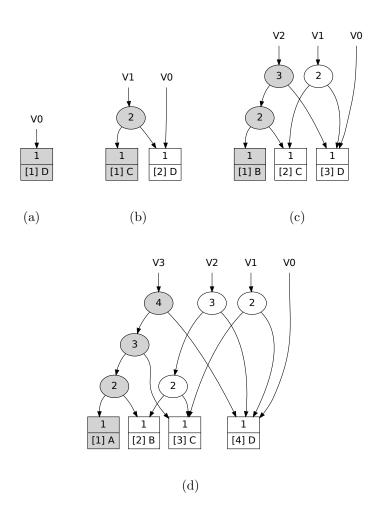

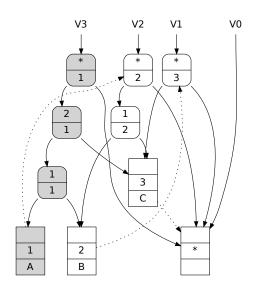

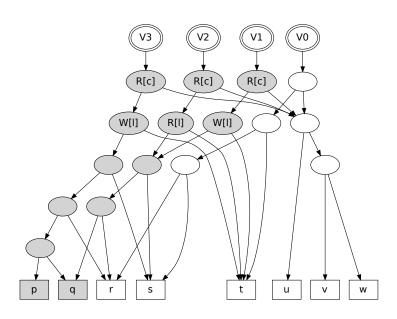

| 4.3  | A persistent Directed min-tree                                     | 144 |

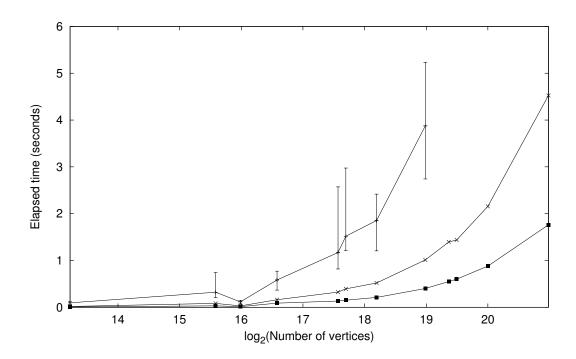

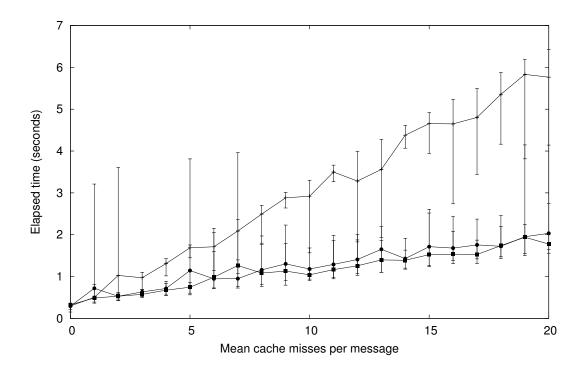

| 4.4  | Comparison of the elapsed time taken to calculate the minimum      | 111 |

|      | spanning tree                                                      | 149 |

| 5.1  | Labelling of variables in the cap of an Immutable Data Structure   | 171 |

| 5.2  | Operations on variables in the cap of a deque                      | 173 |

| 5.3  | Operations on variables in the cap of a map                        | 175 |

| 5.4  | Conflicting and non-conflicting operations on a deque              | 177 |

| 5.5  | Making a deque confluently persistent                              | 180 |

| 6.1  | The dining philosophers                                            | 186 |

| 6.2  | The execution of an access function in the presence of concurrent  |     |

|      | mutations                                                          | 192 |

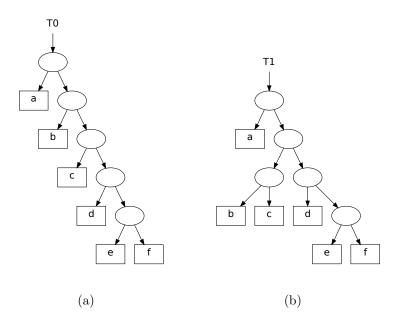

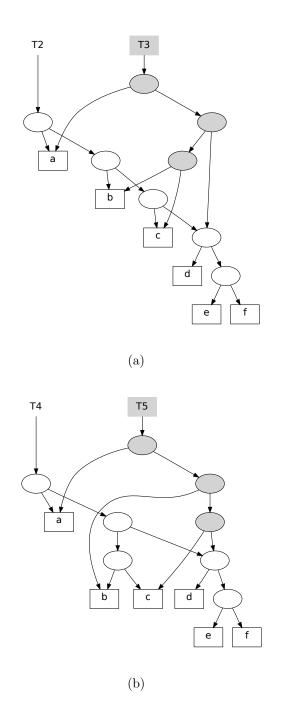

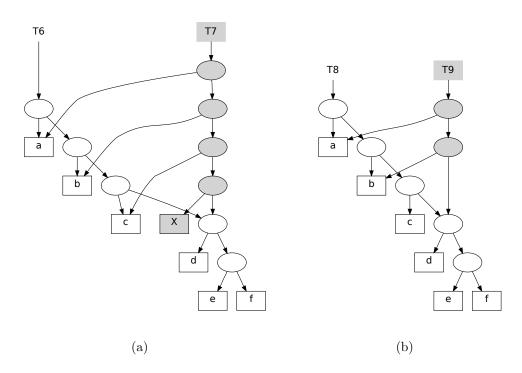

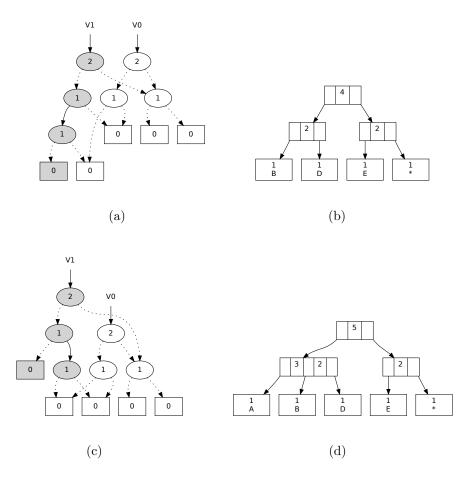

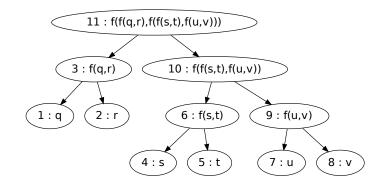

| 6.3  | The abstract syntax tree of an expression                          | 194 |

| 6.4  | An Immutable Data Structure representing the evaluation of an      |     |

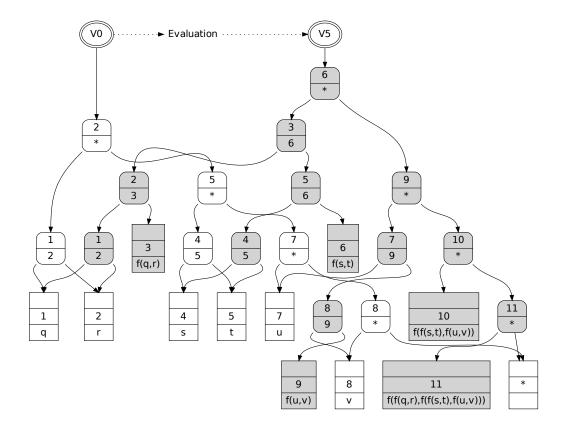

|      | expression                                                         | 196 |

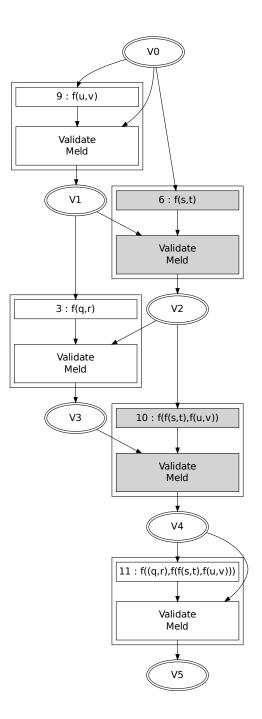

| 6.5  | The non-blocking evaluation of an expression                       | 197 |

| 6.6  | The Producer Consumer Queue                                        | 199 |

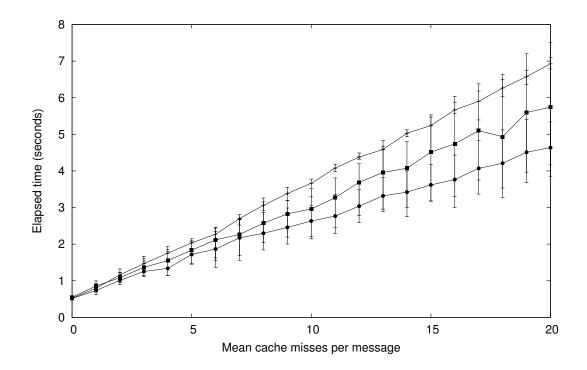

| 6.7  | The maximum throughput of a non-blocking bounded Messaging         |     |

|      | Queue implemented by a confluently persistent Immutable Data       |     |

|      | Structure                                                          | 201 |

| 6.8  | The maximum throughput of a blocking Producer Consumer Queue       |     |

|      | from the Boost library, implemented by the std::deque container .  | 202 |

### Abstract

Concurrent programming is difficult and the effort is rarely rewarded by faster execution. The concurrency problem arises because information cannot pass instantly between processors resulting in temporal uncertainty.

This thesis explores the idea that immutable data and distributed concurrency control can be combined to allow scalable concurrent execution and make concurrent programming easier. A concurrent system that does not impose a global ordering on events lends itself to a scalable distributed implementation. A concurrent programming environment in which the ordering of events affecting an object is enforced locally has intuitive concurrent semantics.

This thesis introduces Transactional Data Structures which are data structures that permit access to past versions, although not all accesses succeed. These data structures form the basis of a concurrent programming solution that supports database type transactions in memory. Transactional Data Structures permit non-blocking concurrent access to familiar abstract data types such as deques, maps, vectors and priority queues. Using these data structures a programmer can write a concurrent program in C without having to reason about locks.

The solution is evaluated by comparing the performance of a concurrent algorithm to calculate the minimum spanning tree of a graph with that of a similar algorithm which uses Transactional Memory and by comparing a non-blocking Producer Consumer Queue with its blocking counterpart.

Kimberley Jarvis Transactional Data Structures Doctor of Philosophy The University of Manchester 11 November 2011

# Declaration

No portion of the work referred to in this thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

# Copyright

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://www.campus.manchester.ac. uk/medialibrary/policies/intellectual-property.pdf), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/ library/aboutus/regulations) and in The University's policy on presentation of Theses

## Acknowledgements

I have been privileged to work with my supervisor Chris Kirkham and my advisor Ian Watson. They have given me an enormous amount of valuable advice and guided me in the preparation of this thesis.

I owe a great debt of gratitude to my colleagues from the Advanced Processor Technologies group at the University of Manchester where I have had the pleasure of working closely with Mohammad Ansari, Behram Kahn, Christos Kotselidis, Mikel Luján, Ian Rogers and Jeremy Singer.

I am grateful to my father James Jarvis for improving the readability of this thesis.

## Chapter 1

### Introduction

#### **1.1** Speculative execution

Programs that deliver scalable speed-up from parallel execution on Chip Multi-Processors are difficult to develop. As the number of processing cores in a Chip Multi-Processor increases so does the potential speed-up from parallel execution but there are few programs that actually achieve scalable speed-up when executing on a Chip Multi-Processor.

This thesis examines the problem of getting the processors of a Chip Multi-Processor to work together on a single program and complete the program in less time than it would take a single processor working alone. The program can be divided into tasks which are simultaneously executed by the processors and these tasks may or may not be interdependent. This thesis focuses on the case where task dependencies are not known until the program is executed.

#### 1.1.1 Mutual exclusion

The most commonly used mechanism to support concurrent execution is mutual exclusion. Mutual exclusion does not permit tasks with possible dependencies to execute in overlapping periods of time. On a Chip Multi-Processor mutual exclusion can be used to permit those sections of a program in which there are known to be no conflicting operations to be executed in parallel and ensure that the critical sections of the program, that may have dependencies, execute serially.

The use of mutual exclusion limits the scalability of a concurrent program and makes it susceptible to progress pathologies such as deadlock. Section 1.1.5 describes why concurrent programming using mutual exclusion is difficult.

This thesis is primarily concerned with the problem of developing scalable concurrent programs for Chip Multi-Processors and it focuses on the case where task dependencies are not known until the program is executed.

Section 1.1.6 describes the scope of the problem addressed by this thesis.

#### 1.1.2 Speculative execution

Speculative execution is a programming technique that can be used as an alternative to mutual exclusion. It facilitates scalable concurrent execution by permitting the simultaneous execution of tasks that may be interdependent. Speculative execution permits tasks to be executed optimistically. A concurrent program can safely speculate that a task is not affected by tasks running on other processors, provided it has a mechanism to re-execute the task should that speculation prove incorrect.

To discover the dependencies between tasks, information must pass between the processors performing them, while the program executes. Processors cannot pass information to each other instantaneously, so each task has a slightly delayed view of the progress that tasks on other processors are making. This delay necessitates speculative execution because if a processor were to wait for a task, on which it is possibly dependent, to complete then there would be little benefit from executing on multiple processors.

This thesis develops programming techniques that support speculative execution on a Chip Multi-Processor.

Section 1.1.3 outlines the techniques presented in this thesis.

This thesis describes software that enables the use of these techniques in an application.

Section 1.1.4 describes the software we develop.

#### **1.1.3** Techniques to support speculative execution

This thesis develops programming techniques that allow applications to access shared state speculatively. These techniques include mechanisms for maintaining shared state and mechanisms for detecting conflicting accesses during program execution.

#### 1.1. SPECULATIVE EXECUTION

This thesis presents a number of data structure representations and algorithms and it describes features which make them suitable for concurrent execution. These features include the use of a sentinel to distinguish between a non-existent and an empty data structure and the use of additional annotations in vertices so that traversals do not need to examine all of the children of a vertex when determining a path through the structure.

A technique for composing data structures which can be used to implement a low-overhead checkpointing and backtracking mechanism is presented. This thesis explores and evaluates the use of the technique by developing a concurrent graph algorithm.

A technique for detecting conflicting concurrent accesses to a data structure is presented. Conflicts are detected by mapping relative positions within the data structure to the variables considered by a concurrency control protocol.

This thesis explores the use of distributed concurrency control to ensure the correctness of concurrent accesses to a data structure. A technique for incorporating a distributed transaction manager into the access functions of a data structure is presented.

A technique for developing non-blocking algorithms that permits the nonblocking execution of data structure access functions is presented. It is implemented by a non-blocking scheduling routine. This thesis explores and evaluates the use of the technique by developing a non-blocking queue.

#### **1.1.4** Infrastructure to support speculative execution

We develop software to demonstrate the programming techniques described in this thesis. This software supports our experiments and allows us to evaluate these techniques. It takes the form of a C++ header library which implements the data structures and a set of routines that implement the mechanisms which permit speculative execution.

A concurrent application that makes use of our techniques accesses shared state through the functions of a data structure. These data structures are implemented by a C++ header library. This library implements common Abstract Data Types (ADTs) in a way that permits the speculative execution of their functions. The library implements a mechanism for maintaining speculative state within a data structure and a mechanism for discovering conflicting accesses at execution time. A concurrent application that makes use of our techniques is divided into tasks that may be executed in parallel on a Chip Multi-Processor. The software includes routines to distribute and schedule concurrent tasks. These routines are written in C++ and implemented using Intel's Threading Building Block product [Int09].

#### 1.1.5 The problem with locks

The correctness of the concurrent execution of critical sections can be ensured by locking. In the simplest scenario, a processor acquires the exclusive ownership of a lock before executing the code within a critical section and relinquishes ownership once the execution of the program code within that critical section is complete. The lock is said to protect the critical section.

Mutual exclusion ensures the serial execution of critical sections regardless of how often dependencies between tasks actually arise. If there is the slightest possibility of a dependency between tasks then they must always be executed serially. As the number of processes is increased, the execution time of the program code within the critical sections dominates and the benefit of parallel execution is diminished. This effect is a consequence of Amdahl's law. [Amd67] [HM08].

The relationship between a lock and the critical section that it protects is abstract. This relationship is not necessarily reflected in the program code or its associated documentation. For example, the code in an existing critical section may not contain information about a newly developed critical section which is protected by the same lock.

Blocking occurs when a delay in the execution of a section of program code delays the execution of other code sections. Mutual exclusion ensures the correctness of the execution of a code section by ensuring that only one processor executes it at any given moment. The progress of processors that attempt to access the code section simultaneously is blocked. A program that blocks is prone to the progress pathology of deadlock which prevents it from completing. For example, a concurrent program in which two critical sections acquire the same locks but in a different order may deadlock.

Sections of program code are said to be composable if they can be combined without examining or altering their implementation. Critical sections are not composable because they have the potential to block the progress of processors that attempt to execute them. Consequently, it is not possible to encapsulate the concerns of mutual exclusion. For example, the order of lock acquisition in an existing critical section must be examined when developing a new critical section protected by the same locks.

Critical sections that are protected by a common lock have shared performance considerations. For example, a low-latency task may be blocked by a long running task protected by the same lock.

Critical sections that are protected by a common lock must be tested to the same level of integrity regardless of the importance of their functionality. For example, a trivial task must be tested to the same level of integrity as an important task protected by the same lock.

#### 1.1.6 The concurrency problem

This thesis addresses the problem of developing scalable concurrent programs for execution on Chip Multi-Processors. We focus exclusively on the execution of tasks from a single program on Chip Multi-Processor hardware that supports parallel execution. We are particularly interested in the case where the dependencies between tasks are unknown until their execution is complete. We regard the concurrency problem as the problem of obtaining speed-up from the parallel execution of tasks from a single program on a Chip Multi-Processor when task dependencies are unknown until their execution is complete.

A Chip Multi-Processor supports parallel execution, which is the simultaneous execution of tasks on different hardware processors. A system may support concurrent execution, which is the execution of tasks that have the *potential* to execute simultaneously. In this thesis we are concerned with internal concurrency which is the potential to execute related tasks, that may interact through memory and which are part of a single program, simultaneously. We do not consider external concurrency which occurs when a program, such as an operating system, needs to perform several possibly unrelated tasks at the same time.

Many applications have the potential to benefit from parallel execution on Chip Multi-Processors but are unable to realise this benefit because their execution is dominated by frequent accesses to shared data. These applications include low-latency trading, travel reservations, on-line inventory, on-line gaming, payment verification and graph traversal algorithms. For these applications the concurrency problem has two related components. Firstly, the development costs associated with ensuring the correctness of concurrent accesses to shared data using mutual exclusion exceed the commercial benefits of parallel execution on a Chip Multi-Processor. Secondly, the scaling restriction imposed by using mutual exclusion precludes significant speed-up from parallel execution on a Chip Multi-Processor.

This thesis focuses on programs written in C++ because applications that may benefit from parallel execution on a Chip Multi-Processor are frequently written in this language. However, the techniques we describe are not restricted to a particular programming language.

Only small regions of many programs may benefit from parallel execution. We focus on techniques which can be applied locally, without disrupting those regions of an application that do not benefit. We seek solutions that can be applied to existing programs. However, the techniques we describe can also be used to develop new programs. The programs we develop to support our evaluation are entirely new.

#### **1.2** Memory Transactions

Transactional Memory is a programming technique that promises to make concurrent programming easier and concurrent programs more scalable. However, Transactional Memory systems rarely deliver on these promises. The design choices made during the development of Transactional Memory systems are motivated by a common set of priorities. These priorities need to be re-evaluated and different design choices considered.

The main contribution of this section is the identification of priorities that motivate Transactional Memory designs. This section focuses on whether Transactional Memory systems really deliver on their promise of making scalable concurrent programs easier to write.

#### **1.2.1** Transactional Memory systems

Transactional Memory is a technique to support speculative execution that can be used as an alternative to mutual exclusion. It facilitates scalable concurrent execution by allowing the simultaneous execution of tasks that may be interdependent.

Section 1.2.4 introduces Transactional Memory.

Software Transactional Memory systems provide a software framework for programmers to construct concurrent programs that can be executed speculatively. However, the overheads of supporting speculative execution entirely in software often exceed the benefits of concurrent execution.

Section 1.2.5 discusses the claim that Software Transactional Memory makes concurrent programming easier.

Hardware Transactional Memory systems support concurrent execution by providing a hardware environment in which concurrent programs can be executed speculatively. The engineering challenges that must be overcome by Hardware Transactional Memory are significant and the commercial barriers to adoption are high.

Section 1.2.6 discusses the claim that Hardware Transactional Memory makes concurrent programming easier.

Transactional Memory can make programming easier by freeing the programmer from having to reason about locks, but concurrent programming using Memory Transactions is not necessarily easier than concurrent programming using mutual exclusion.

Section 1.2.7 discusses the claim that Transactional Memory makes concurrent programming easier.

Research carried out in both the private and public sectors has yet to produce convincing evidence that Transactional Memory systems are making progress towards delivering on their promise of scalability, because the overheads of supporting concurrent execution exceed the benefits of concurrent execution. They also fail to deliver on their promise of improved programmer productivity, because concurrent programming using Memory Transactions is no easier than concurrent programming using mutual exclusion.

#### 1.2.2 Design priorities

Transactional Memory research is founded on the premise that speculative execution is necessary to support scalable concurrent execution on Chip Multi-Processors and it has the goal of making concurrent programming easier. This thesis does not doubt this premise nor question this laudable goal, but it does question the priorities that motivate the design of Transactional Memory systems.

Transactional Memory proposals prioritise some aspects of system design at the expense of others:

- They focus on the speculative execution of programs, at the expense of the interaction with external systems.

- They choose to buffer speculative state, at the expense of increased memory bandwidth.

- They weaken transactional isolation, at the expense of semantic simplicity.

- They centralise the responsibility for transaction management, at the expense of scalability.

- They focus on ease of programming per se, at the expense of total productivity across the software development cycle.

Given the disappointing progress of Transactional Memory systems to date it is reasonable to suggest that some of the priorities should be re-assessed and that designs based on a different set of priorities should be considered.

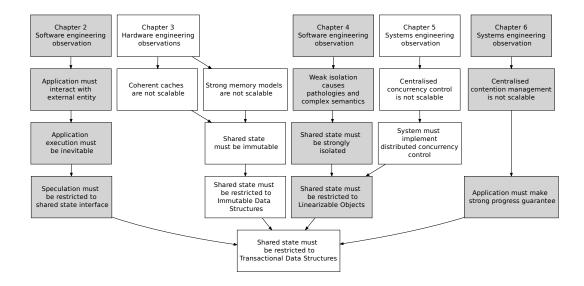

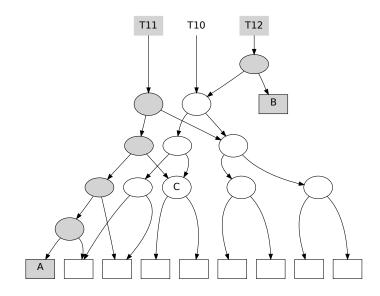

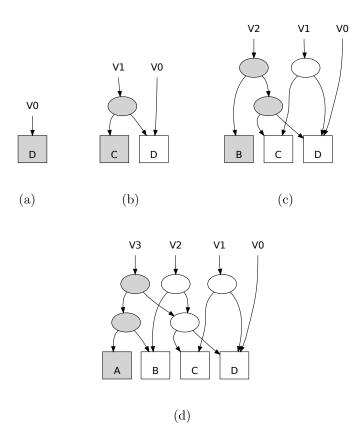

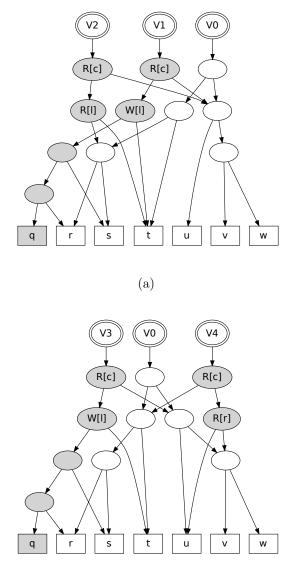

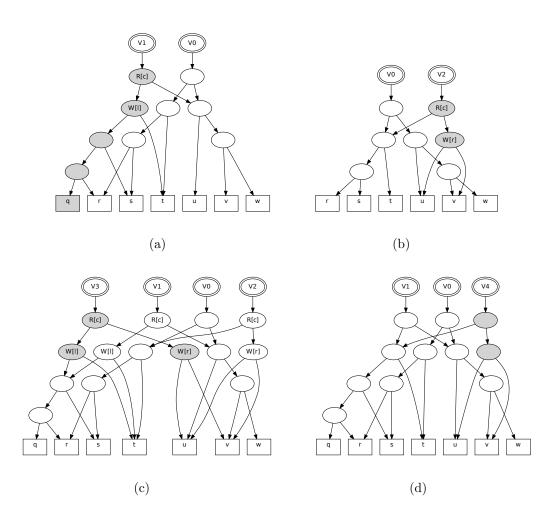

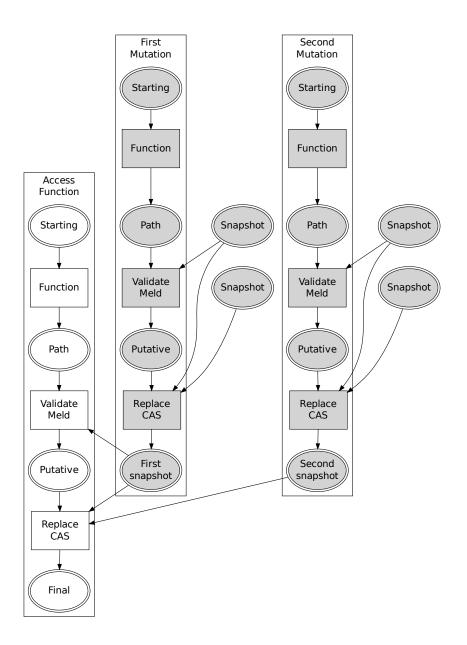

Figure 1.1: Observations about scalable concurrent systems led to the development of the techniques described in this thesis.

#### 1.2.3 Design choices

This thesis is divided into chapters, each of which considers one aspect of the design of a scalable concurrent system. The first section of each chapter examines how the design priorities have influenced the development of Transactional Memory systems. Subsequent sections develop an alternative approach based on a different interpretation of the design priorities.

Figure 1.1 illustrates the organisation of this thesis.

Some aspects of the design of a concurrent system that need to be considered are:

#### How to interact with entities outside the concurrent system?

A useful concurrent application must interact with external entities, but it cannot do so while executing speculatively. This software engineering observation suggests that application execution must be inevitable.

Chapter 2 identifies the interaction with external entities as a primary design concern. It presents a critique of the approach taken by Transactional Memory systems and explores an alternative in which application execution is inevitable and speculative execution is restricted to the interface with shared state.

#### How to maintain shared state and support speculative execution?

Strong memory models and coherent caches are not scalable. These hardware engineering observations suggest that shared state in a concurrent system must be immutable.

Chapter 3 identifies the restrictions on the scalability of hardware as a primary design concern. It examines the approaches to maintaining shared state employed by Transactional Memory systems and develops an alternative in which shared state is immutable.

#### How to provide access to shared state with intuitive concurrent semantics?

Weakly isolated transactional systems have complex concurrent semantics and are prone to pathologies. This software engineering observation suggests that concurrent systems must enforce strong isolation.

Chapter 4 identifies weak isolation as a source of both programming complexity and pathologies. It presents a critique of the approach taken by Transactional Memory systems and develops an alternative in which shared state is maintained in data structures.

#### How to guarantee correct concurrent execution?

Centralised concurrency control is not scalable. This systems engineering observation suggests that concurrency control must not be centralised.

Chapter 5 presents a critique of the centralised approach to concurrency control adopted by many Transactional Memory systems and develops an alternative approach based on distributed concurrency control.

#### How to implement contention management to eliminate progress pathologies?

Centralised contention management is not scalable. This systems engineering observation suggests that a scalable application must make a strong guarantee of progress.

Chapter 6 explores the progress guarantees offered by concurrent systems and suggests that the need for centralised contention management can be alleviated by ensuring that the interface to shared state does not block the progress of the application.

#### **1.2.4** The development of Transactional Memory

Research into Transactional Memory is comprehensively described in a book entitled "Transactional Memory" [HLR10].

The following are some of the significant developments in the history of Transactional Memory:

Lomet proposed the use of transactions within programs [Lom77].

Weihl and Liskov proposed the use of transactions to support concurrent programming [WL83].

Stone, Heidelberger and Turek recognised that Memory Transactions are discontiguous multi-word atomic operations [SSHT93]. Computer hardware typically provides atomic operations that act on a single word or a contiguous doubleword in memory.

Herlihy and Moss proposed Hardware Transactional Memory [HM93]. A Hardware Transactional Memory implements Memory Transactions by using modified hardware to support speculative execution.

Shavit and Touitou proposed the conventional model of Software Transactional Memory [ST95]. A Software Transactional Memory implements Memory Transactions entirely in software by buffering speculative state in core or in a log.

Lie and Asanovic proposed Hybrid Transactional Memory [LA04]. Recent Hardware Transactional Memory systems are typically hybrids involving both compiler and run-time support for Memory Transactions executing on modified hardware.

#### 1.2.5 Software Transactional Memory

Software Transactional Memory systems provide a framework and a run-time system to support the speculative execution of Memory Transactions. Dependencies between tasks are checked at run-time. If conflicting operations are found then the tasks containing them are re-executed resulting in wasted work.

The influential paper "Software Transactional Memory: Why is it only a research toy?" was written by the team responsible for IBM's Software Transactional Memory system [CBM<sup>+</sup>08]. They compared the performance of their

Software Transactional Memory with comparable systems from Intel and Sun [ART08] [DDS06]. They examined the performance of programs from the STAMP benchmark suite [CMCKO08]. This benchmark suite contains programs that are good candidates for concurrent execution. The team does not discuss the interaction with the Network or Operating System because the benchmark programs are monolithic.