# Online Scheduling for Real-Time Multitasking on Reconfigurable Hardware Devices

A Thesis submitted for the degree of Doctor of Philosophy

$\mathbf{B}\mathbf{y}$

Guy Wassi-Leupi

Department of New Media & Technologies,

Faculty of Design, Media & Management,

Buckinghamshire New University

Brunel University, London

July, 2011

#### Abstract

Nowadays the ever increasing algorithmic complexity of embedded applications requires the designers to turn towards heterogeneous and highly integrated systems denoted as SoC (System-on-a-Chip). These architectures may embed CPU-based processors, dedicated datapaths as well as reconfigurable units. However, embedded SoCs are submitted to stringent requirements in terms of speed, size, cost, power consumption, throughput, etc. Therefore, new computing paradigms are required to fulfil the constraints of the applications and the requirements of the architecture.

Reconfigurable Computing is a promising paradigm that provides probably the best trade-off between these requirements and constraints. Dynamically reconfigurable architectures are their key enabling technology. They enable the hardware to adapt to the application at runtime. However, these architectures raise new challenges in SoC design. For example, on one hand, designing a system that takes advantage of dynamic reconfiguration is still very time consuming because of the lack of design methodologies and tools. On the other hand, scheduling hardware tasks differs from classical software tasks scheduling on microprocessor or multiprocessors systems, as it bears a further complicated placement problem.

This thesis deals with the problem of scheduling online real-time hardware tasks on Dynamically Reconfigurable Hardware Devices (DRHWs). The problem is addressed from two angles:

- (i) Investigating novel algorithms for online real-time scheduling/placement on DRHWs.

- (ii) Scheduling/Placement algorithms library for RTOS-driven Design Space Exploration (DSE).

Regarding the first point, the thesis proposes two main runtime-aware scheduling and placement techniques and assesses their suitability for online real-time scenarios. The first technique discusses the impact of synthesizing, at design time, several shapes and/or sizes per hardware task (denoted as multi-shape task), in order to ease the online scheduling process. The second technique combines a looking-ahead scheduling approach with a slots-based reconfigurable areas management that relies on a 1D placement. The results show that in both techniques, the scheduling and placement quality is improved without significantly increasing the algorithm time complexity.

Regarding the second point, in the process of designing SoCs embedding reconfigurable parts, new design paradigms tend to explore and validate as early as possible, at system level, the architectural design space. Therefore, the RTOS (Real-Time Operating System) services that manage the reconfigurable parts of the SoC can be refined. In such a context, gathering numerous hardware tasks scheduling and placement algorithms of various complexity vs performance trade-offs in a kind of library is required. In this thesis, proposed algorithms in addition to some existing ones are purposely implemented in C++ language, in order to insure the compatibility with any C++/SystemC based SoC design methodology.

Key-words: FPGA, Reconfigurable SoC, DES, Modelling, Scheduling, Placement, RTOS.

#### Acknowledgments

This work was carried out in two institutions: at Faculty of Design, Media & Management, Buckinghamshire New University, High Wycombe (UK), and, in the Computer Architecture team at ETIS/CNRS lab, ENSEA, University of Cergy (France).

I would like to take this opportunity to thank Professor Geoff Lawday for giving me the opportunity to undertake this thesis dissertation. I would also like to express my gratitude to him for being always understanding and encouraging even when I felt stressed.

I am sincerely thankful to my supervisors Dr Kevin Maher from Buckinghamshire New University and Dr Amine Benkhelifa from ETIS lab, University of Cergy, for their valuable supervision and support over the years.

I owe a great debt to Professor François Verdier from University of Nice Sophia-Antipolis who advised, encouraged, and inspired my research. I have been blessed with two experts in reconfigurable computing, Amine and François. They have shown generosity and availability towards my research project.

I am grateful to Professor John Boylan and Buckinghamshire New University for supporting me with the funding necessary to carry out my research. I also gratefully thank the ETIS lab for providing me with extra funding along with a suitable research environment.

I would like to thank Professor Chris Hudson, Professor Inbar Fijalkow, Professor Bertrand Granado, Dr Peter Wilkinson, Laura Bray, Howard Bush, William Lishman, Dr Anne Evans, staff at Buckinghamshire New University and staff at ETIS lab, University of Cergy, for their support and advice. I will not forget my fellow research students and my former colleagues from Buckinghamshire New University and the ETIS lab. We have been sharing very fruitful discussions.

Thanks to Paul & Lucy Tanyi, Antoine & Ariane Kamina, Bernard Mankem, Julius Ebokolle, Premkumar Elangovan, Knowledge Mpofu, Indrachapa Bandara and many others that are not personally named here. They all made my life in UK enjoyable and sociable. Thanks to Randolph Boyd for its availability.

My family has been a constant source of understanding, encouragement and love. Thanks to my brothers and sisters, Michel, Alex, Theresine and Anne-Marie for their constant support and love. They always believed in me.

I dedicate this work to my beloved parents Jeanne-d'Arc Beumani and Emmanuel Leupi to my wife Lydie-Flore, to my little princesses Jane-Veronica, Lise-Nahomie and to Françoise-Soul-angel.

I wish Jeanne d'Arc, Françoise and Jeanne witnessed this achievement

I am quite sure, they are all smiling on me up there

## Contents

| 1        | Intr | oducti | ion                                                                 | 1  |  |

|----------|------|--------|---------------------------------------------------------------------|----|--|

|          | 1.1  | Precis | of Embedded Systems and Research Rationale                          | 1  |  |

|          | 1.2  | Raison | n D'être for using Reconfigurable Hardware Devices in Embedded SoCs | 3  |  |

|          |      | 1.2.1  | Dynamic and Online Embedded Applications                            | 4  |  |

|          |      | 1.2.2  | Technology Advances, Market and Costs Constraints                   | 8  |  |

|          | 1.3  | Relate | ed Research Issues                                                  | 11 |  |

|          |      | 1.3.1  | System-On-Chip Design Overview                                      | 11 |  |

|          |      | 1.3.2  | Reconfigurable System-On-Chip Design                                | 13 |  |

|          |      | 1.3.3  | Operating System for Reconfigurable System-On-a-Chip                | 17 |  |

|          | 1.4  | Contri | ibution of the Thesis                                               | 18 |  |

|          |      | 1.4.1  | Algorithms for Online Real-Time Scheduling & Placement              | 18 |  |

|          |      | 1.4.2  | Scheduling & Placement Algorithms for OS-driven Design Space        |    |  |

|          |      |        | Exploration                                                         | 19 |  |

|          | 1.5  | Outlin | ne of the Thesis                                                    | 19 |  |

| <b>2</b> | Dyr  | namica | lly Reconfigurable Architectures $vs$ Implementation Alterna-       |    |  |

|          | tive | ves    |                                                                     |    |  |

|          | 2.1  | Introd | luction                                                             | 22 |  |

|          |      | 2.1.1  | The Switch from Analog to Digital Signal Processing                 | 23 |  |

|          |      | 2.1.2  | The most common DSP Functions                                       | 24 |  |

|          |      | 2.1.3  | Software vs Hardware Platforms                                      | 24 |  |

|          |      |        |                                                                     |    |  |

| 2.2 | Softwa | are Implementation Platforms                               | 25 |

|-----|--------|------------------------------------------------------------|----|

|     | 2.2.1  | General Purpose Processors (GPPs)                          | 25 |

|     | 2.2.2  | Programmable Digital Signal Processors (DSPs)              | 28 |

| 2.3 | Hardw  | vare Implementation Platforms                              | 29 |

|     | 2.3.1  | ASIC Implementation                                        | 30 |

|     | 2.3.2  | Fine and Coarse Grain Reconfigurable Arrays Implementation | 31 |

| 2.4 | ASIP/  | ASSP Implementation                                        | 32 |

| 2.5 | Fine-g | rained Reconfigurable Hardware Devices                     | 33 |

|     | 2.5.1  | Introduction                                               | 33 |

|     | 2.5.2  | FPGA Architectures                                         | 33 |

|     | 2.5.3  | FPGA Technology                                            | 34 |

|     | 2.5.4  | FPGA Structures                                            | 35 |

|     | 2.5.5  | SRAM-based FPGA                                            | 36 |

|     | 2.5.6  | Heterogeneous FPGAs                                        | 41 |

|     | 2.5.7  | FPGA Design Flow                                           | 44 |

|     | 2.5.8  | FPGA Modular Design for Runtime Partial Reconfiguration    | 46 |

|     | 2.5.9  | Coupling with the Host Processor                           | 48 |

|     | 2.5.10 | Types of Reconfiguration                                   | 51 |

|     | 2.5.11 | Configuration Hierarchy                                    | 53 |

| 2.6 | Coarse | e-grained Reconfigurable Arrays                            | 55 |

|     | 2.6.1  | Raison D'être                                              | 55 |

|     | 2.6.2  | Presentation                                               | 55 |

| 2.7 | Platfo | rm-Based Design                                            | 56 |

|     | 2.7.1  | Introduction                                               | 56 |

|     | 2.7.2  | Definition                                                 | 57 |

|     | 2.7.3  | OS for Reconfigurable Platforms                            | 58 |

| 2.8 | Conclu | sion of the Chapter                                        | 62 |

| 3 | Bac | kgrour | nd and Related Work                                               | 64 |

|---|-----|--------|-------------------------------------------------------------------|----|

|   | 3.1 | Introd | $\operatorname{uction}$                                           | 64 |

|   | 3.2 | Real-T | Time Systems                                                      | 65 |

|   |     | 3.2.1  | Hard $vs$ Soft Real-Time                                          | 66 |

|   |     | 3.2.2  | Requirements for Real-Time Computer Systems                       | 66 |

|   | 3.3 | Real-T | Time Scheduling                                                   | 67 |

|   |     | 3.3.1  | Introduction                                                      | 67 |

|   |     | 3.3.2  | Real-Time Tasks                                                   | 67 |

|   |     | 3.3.3  | Different Scheduling Problems                                     | 71 |

|   |     | 3.3.4  | Objective Functions                                               | 74 |

|   |     | 3.3.5  | Offline Scheduling                                                | 75 |

|   | 3.4 | Online | Scheduling                                                        | 76 |

|   |     | 3.4.1  | Introduction                                                      | 76 |

|   |     | 3.4.2  | Different Online Paradigms                                        | 76 |

|   |     | 3.4.3  | Performance Analysis                                              | 78 |

|   |     | 3.4.4  | Schedulability Analysis                                           | 80 |

|   | 3.5 | RT Sc  | heduling for Uniprocessor Systems                                 | 80 |

|   |     | 3.5.1  | Rate Monotonic (RM)                                               | 80 |

|   |     | 3.5.2  | Deadline Monotonic (DM)                                           | 81 |

|   |     | 3.5.3  | Earliest Deadline First (EDF)                                     | 81 |

|   |     | 3.5.4  | Least Laxity First (LLF)                                          | 82 |

|   |     | 3.5.5  | List Scheduling (LS)                                              | 82 |

|   |     | 3.5.6  | Uniprocessor Scheduling Model for Reconfigurable Hardware $\dots$ | 82 |

|   | 3.6 | RT Sc  | heduling for Multiprocessor Systems                               | 87 |

|   |     | 3.6.1  | Multiprocessor Scheduling Problem                                 | 88 |

|   |     | 3.6.2  | Multiprocessor Platforms                                          | 88 |

|   |     | 3.6.3  | Partitioned vs Nonpartitioned Scheduling Strategies               | 89 |

|   |     | 3.6.4  | Multiprocessor Scheduling Model for Reconfigurable Hardware       | 90 |

|   | 3.7 | Online | Real-Time Scheduling on Reconfigurable Hardware Devices           | 93 |

|   |      | 3.7.1            | Online Scheduling $Without	ext{-}Looking	ext{-}Ahead$ and Related Work | 94         |

|---|------|------------------|------------------------------------------------------------------------|------------|

|   |      | 3.7.2            | Online $Looking$ -Ahead Scheduling and Related Work                    | 98         |

|   | 3.8  | Tasks            | Placement and Related Work                                             | 105        |

|   |      | 3.8.1            | Online Placement Issues                                                | 105        |

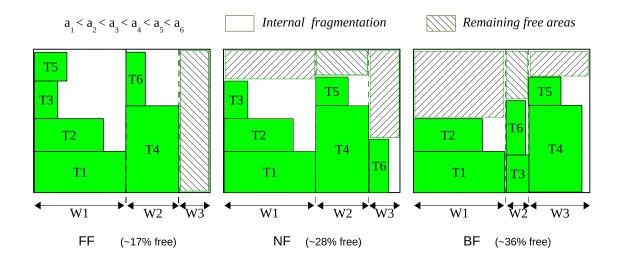

|   |      | 3.8.2            | Free Area Partitioning                                                 | 107        |

|   |      | 3.8.3            | Data Structure to store the State of the Reconfigurable Array          | 110        |

|   |      | 3.8.4            | Fitting Strategies                                                     | 113        |

|   |      | 3.8.5            | Related Work                                                           | 116        |

|   | 3.9  | Fragm            | entation and Related Work                                              | 122        |

|   |      | 3.9.1            | Internal and Intra-task Fragmentations                                 | 124        |

|   |      | 3.9.2            | External Fragmentation                                                 | 125        |

|   |      | 3.9.3            | Related Work                                                           | 125        |

|   | 3.10 | Conclu           | usion of the Chapter                                                   | 134        |

| 4 | Pro  | $\mathbf{posed}$ | Methodology, Models and Metrics                                        | 136        |

|   | 4.1  | Introd           | uction                                                                 | 136        |

|   | 4.2  | Metho            | ${ m dology}$                                                          | 137        |

|   |      | 4.2.1            | Introduction                                                           | 137        |

|   |      | 4.2.2            | Proposed Methodology                                                   | 137        |

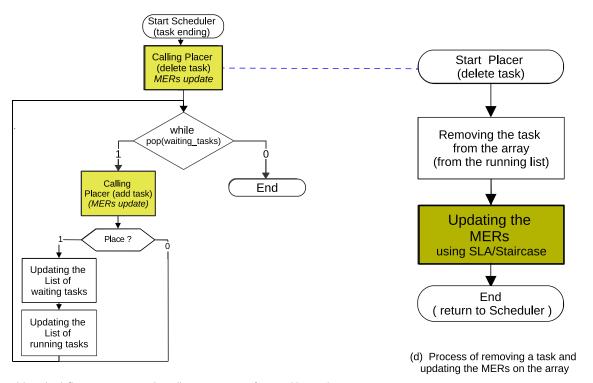

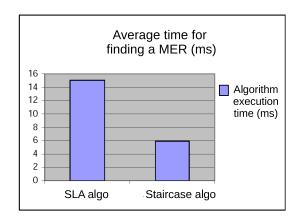

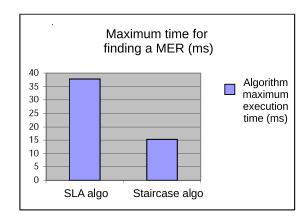

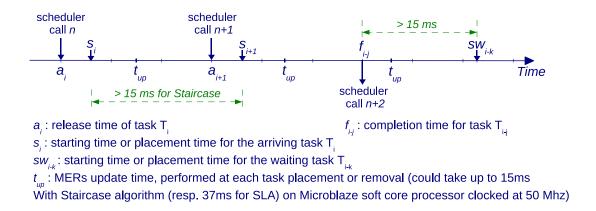

|   |      | 4.2.3            | Running two MERs-based Algorithms on an Embedded Processor .           | 139        |

|   |      | 4.2.4            | Lessons Learnt from Preliminary Results and Conclusion                 | 143        |

|   | 4.3  | Model            | s                                                                      | 146        |

|   |      | 4.3.1            | Real-Time Tasks and Applications Modeling                              | 146        |

|   |      | 4.3.2            | Reconfigurable Devices Area Models                                     | 152        |

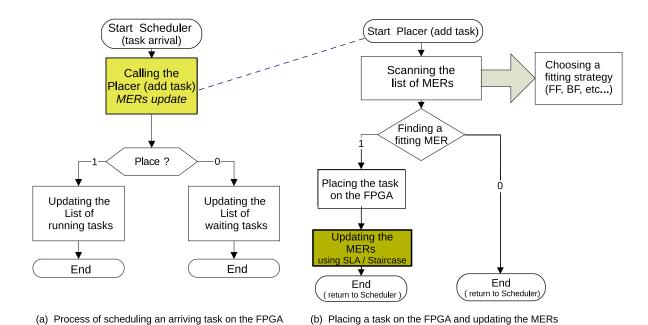

|   |      | 4.3.3            | Scheduler Model                                                        | 155        |

|   |      |                  | Schodal Model                                                          |            |

|   |      | 4.3.4            | Placer Model                                                           | 156        |

|   | 4.4  | 4.3.4<br>Metric  | Placer Model                                                           | 156<br>158 |

|   | 4.4  |                  | Placer Model                                                           |            |

|   |     | 4.4.3            | Application Metrics                                                       | 159        |

|---|-----|------------------|---------------------------------------------------------------------------|------------|

|   |     | 4.4.4            | Scheduling Metrics                                                        | 161        |

|   |     | 4.4.5            | Feasible Schedule                                                         | 164        |

|   | 4.5 | Globa            | l Simulation Model and Compatibility with the OVeRSoC Design              |            |

|   |     | Metho            | odology                                                                   | 164        |

|   |     | 4.5.1            | An UML Overview of the Global Simulation Model                            | 165        |

|   |     | 4.5.2            | The Importance of Using a C++ Based Simulation Model                      | 166        |

|   | 4.6 | Concl            | usion of the Chapter                                                      | 168        |

| 5 | Pro | $\mathbf{posed}$ | Algorithms for Online Real-Time Scheduling & Placement                    | 169        |

|   | 5.1 | Introd           | $oxed{uction}$                                                            | 169        |

|   | 5.2 | Tasks            | Parameters Based Global Scheduling                                        | 170        |

|   |     | 5.2.1            | Temporal parameters based scheduling (Basic, EDF, LLF, etc.) $$           | 173        |

|   |     | 5.2.2            | Geometric parameters based scheduling (BSF, SSF, etc.)                    | 175        |

|   |     | 5.2.3            | Combining Geometric and Temporal parameters for scheduling $$ . $$        | 176        |

|   | 5.3 | Slots-l          | based Scheduling                                                          | 177        |

|   |     | 5.3.1            | n~X~1D variable size slots scheduling                                     | 177        |

|   |     | 5.3.2            | 1D variable slots looking-ahead scheduling                                | 181        |

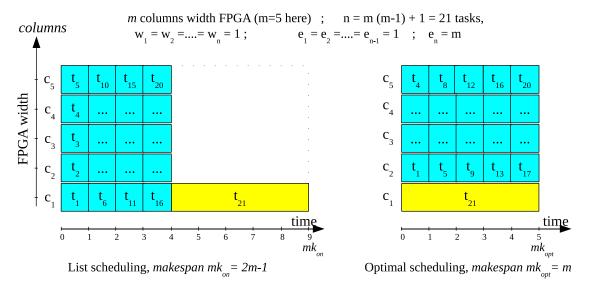

|   |     | 5.3.3            | 1D variable slots scheduling with minimum makespan $\dots$                | 183        |

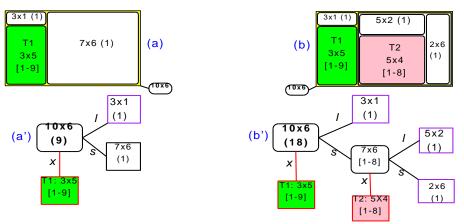

|   | 5.4 | Placer           | ment Strategies for 2D Looking-Ahead Scheduling                           | 187        |

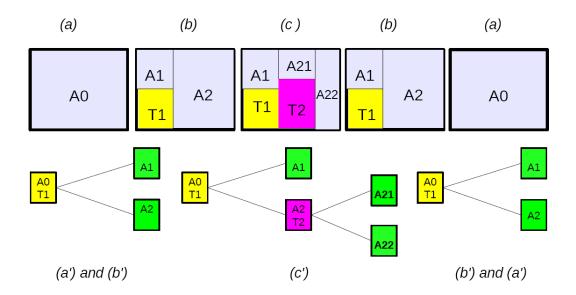

|   |     | 5.4.1            | A Ternary Tree structure for Looking-Ahead Scheduling $\ \ldots \ \ldots$ | 187        |

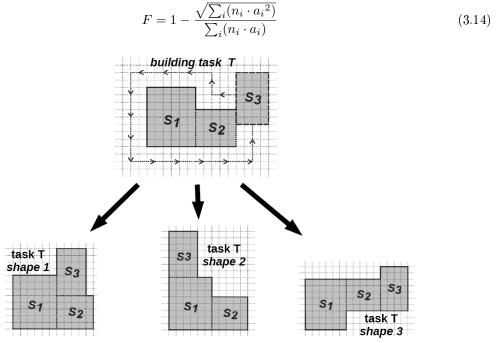

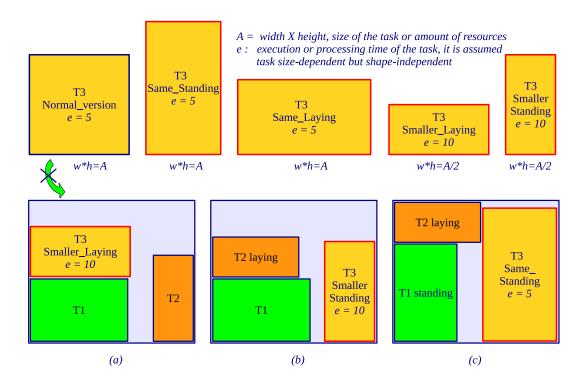

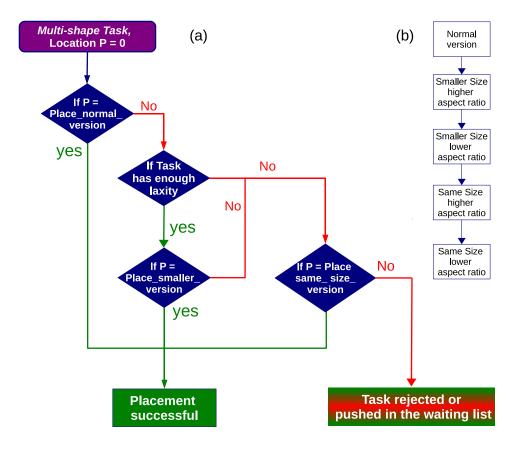

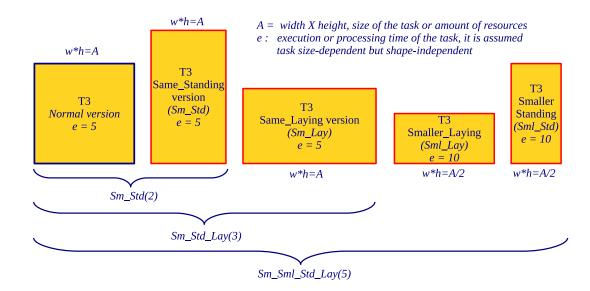

|   | 5.5 | Multi-           | shape based Tasks Scheduling                                              | 191        |

|   |     | 5.5.1            | Raison d'être for multi-shape tasks                                       | 192        |

|   |     | 5.5.2            | The multi-shape basic algorithm                                           | 194        |

|   | 5.6 | Concl            | usion of the Chapter                                                      | 196        |

| 6 | Sim | ıulatio          | n Results of the Algorithms Proposed to Solve Online Rea                  | <b>l</b> - |

|   | Tin | ne Sche          | eduling Issues                                                            | 197        |

|   | 6.1 | Introd           | luction                                                                   | 197        |

|   | 6.2 | Buildi           | ng the Inputs and the Testing Environment                                 | 198        |

|   |      | 6.2.1   | Hardware Tasks Characterization                                        | 198    |

|---|------|---------|------------------------------------------------------------------------|--------|

|   |      | 6.2.2   | Estimating the Size of Tasks                                           | 199    |

|   |      | 6.2.3   | Final Inputs Values for Experiments                                    | 200    |

|   |      | 6.2.4   | The Running Environment                                                | 201    |

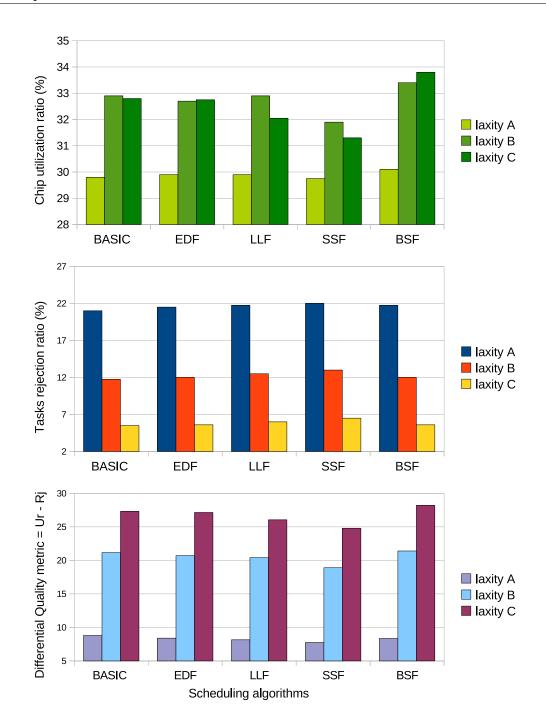

|   | 6.3  | Tasks   | Parameters Based Scheduling                                            | 201    |

|   |      | 6.3.1   | Chip Utilization Ratio and Tasks Rejection Ratio                       | 201    |

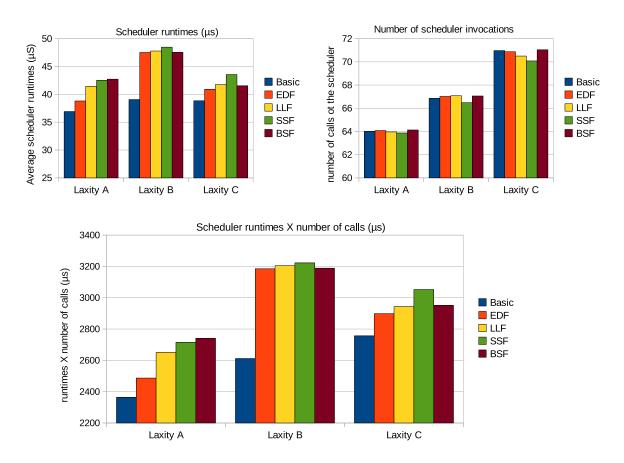

|   |      | 6.3.2   | Runtime Overhead                                                       | 202    |

|   |      | 6.3.3   | Conclusion on parameters based scheduling                              | 205    |

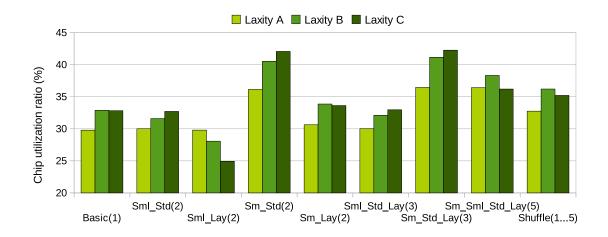

|   | 6.4  | Multi-  | shape Tasks Based Scheduling                                           | 205    |

|   |      | 6.4.1   | Multi-shape Tasks                                                      | 205    |

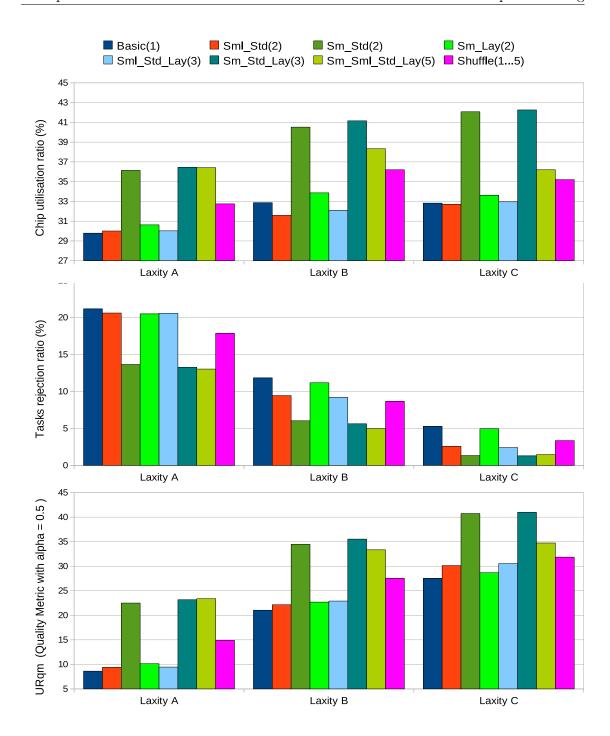

|   |      | 6.4.2   | Chip Utilization Ratio and Tasks Rejection Ratio                       | 208    |

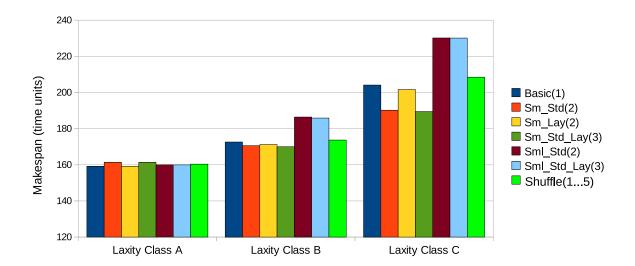

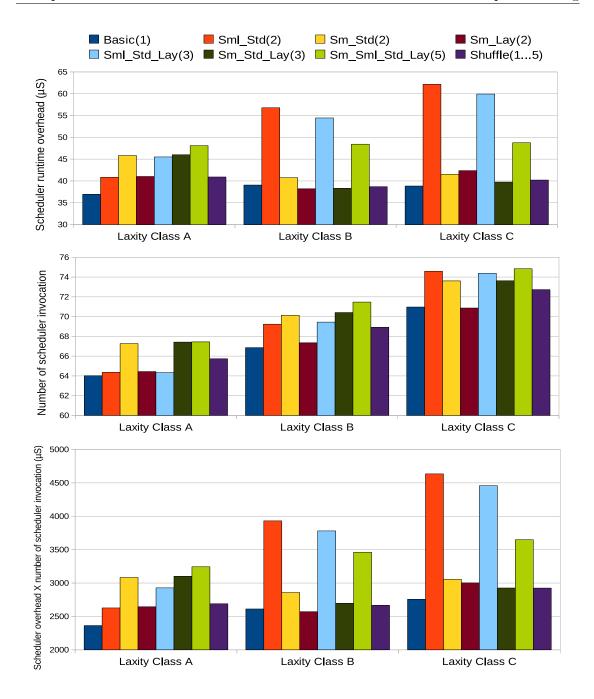

|   |      | 6.4.3   | Makespan and Runtime Overheads                                         | 213    |

|   |      | 6.4.4   | Conclusion on multi-shape scheduling                                   | 218    |

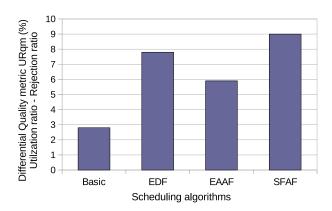

|   | 6.5  | Horizo  | on Looking-Ahead Scheduling Algorithms                                 | 218    |

|   |      | 6.5.1   | Horizon Looking-Ahead Scheduling using a Ternary Tree                  | 219    |

|   |      | 6.5.2   | 1D Variable Slots Looking-Ahead Scheduling                             | 221    |

|   | 6.6  | Conclu  | usion of the Chapter                                                   | 223    |

| 7 | Con  | clusio  | n and Future Work                                                      | 225    |

|   | 7.1  | Discus  | sions                                                                  | 225    |

|   | 7.2  | Key C   | ontributions                                                           | 226    |

|   |      | 7.2.1   | Algorithms for Online Real-time Scheduling/Placement on DPRHW          | m s226 |

|   |      | 7.2.2   | ${\bf Scheduling/Placement~algorithms~library~for~RTOS-driven~design}$ |        |

|   |      |         | space exploration                                                      | 229    |

|   | 7.3  | Hypot   | hesis and Limitations                                                  | 230    |

|   | 7.4  | Future  | e Work                                                                 | 231    |

| A | ppen | dix     |                                                                        | 245    |

|   | 7.5  | Apper   | ndix A: Table classifying related work on scheduling and placement     |        |

|   |      | strates | gies                                                                   | 245    |

| 7.6 | Apper | ndix B : Additional Simulation Results                                        | 248 |

|-----|-------|-------------------------------------------------------------------------------|-----|

| 7.7 | Apper | $\operatorname{dix} C$ : Tables of algorithms and data structures implemented | 256 |

| 7.8 | Apper | ndix D : Size of IPs from the Xilinx core generator $\dots$                   | 260 |

| 7.9 | Apper | ndix E : DA Implementation of a Multi-shape Hardware Task : the               |     |

|     | FIR F | ilter                                                                         | 261 |

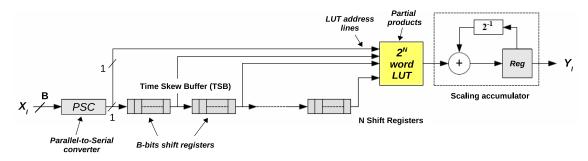

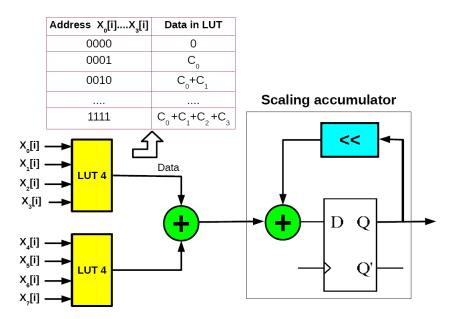

|     | 7.9.1 | Distributed Arithmetic as an enabling technique                               | 262 |

|     | 7.9.2 | Implementing $Y$ using LUT-based DA                                           | 263 |

|     | 7.9.3 | Throughput $vs$ reconfigurable resources trade-off                            | 265 |

## List of Figures

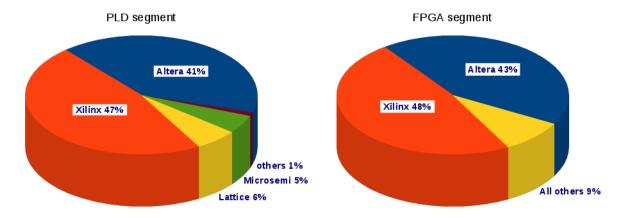

| 1.1 | Programmable device market segment share in 2011 (Xilinx, Company re-                   |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | ports)                                                                                  | 3  |

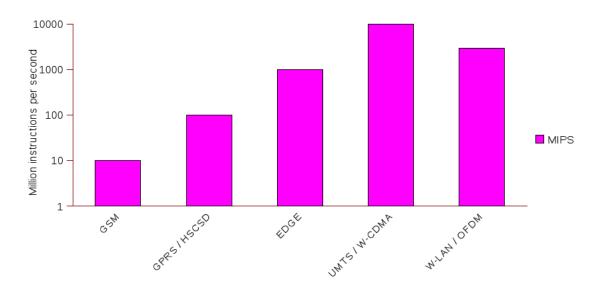

| 1.2 | Processing requirements for wireless access protocols (Schüler and Tan, 2004)           | 5  |

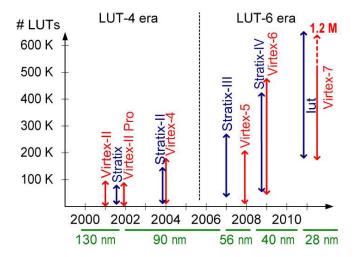

| 1.3 | The increase in logic density in FPGA over one decade and over the corre-               |    |

|     | sponding process technology (Koch and Torresen, 2010)                                   | 10 |

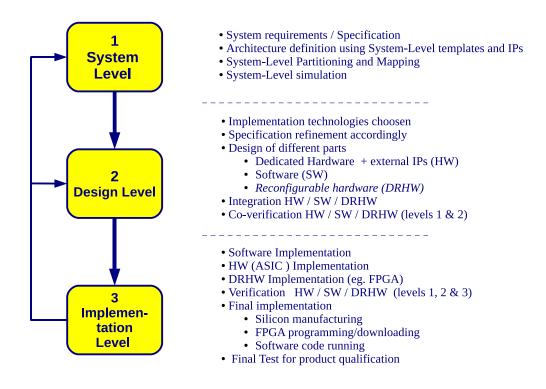

| 1.4 | Main levels in the generic design flow of a SoC                                         | 12 |

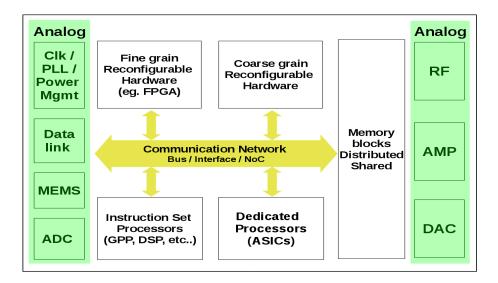

| 1.5 | Generic architecture of a Reconfigurable System-On-Chip                                 | 14 |

| 1.6 | ${\rm Hardware/Software~Co\text{-}Design~shortens~the~design~process(Fujitsu,~2002)~.}$ | 15 |

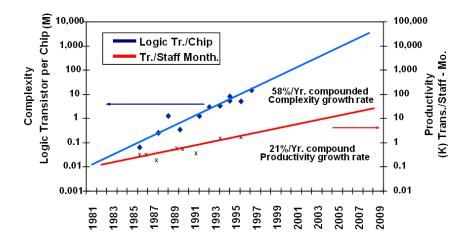

| 1.7 | Productivity gap according to ITRS (The International Technology Roadmap                |    |

|     | for Semiconductors, www.itrs.net)                                                       | 16 |

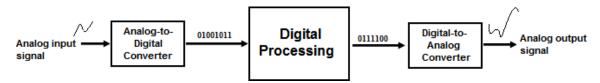

| 2.1 | A simplified representation of a Digital Signal Processing System                       | 23 |

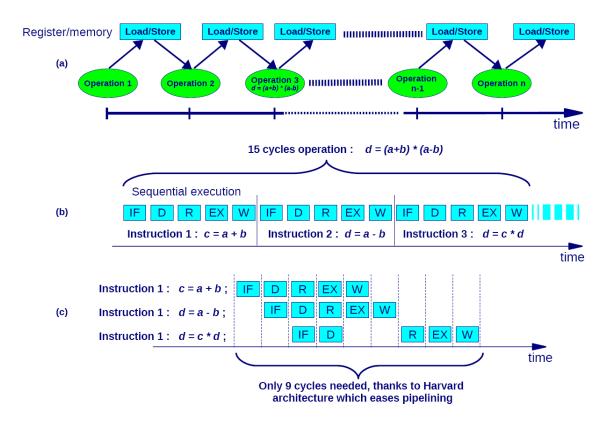

| 2.2 | Sequential execution. (a) a single operation at a time (b) sequential execu-            |    |

|     | tion (c) pipelined execution providing higher throughput.                               | 26 |

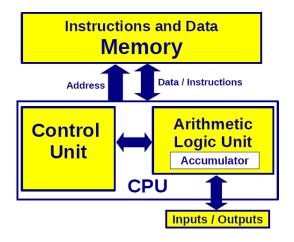

| 2.3 | The Von Neumann architecture                                                            | 26 |

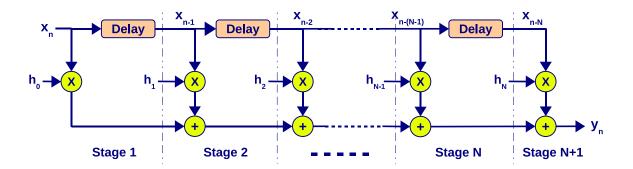

| 2.4 | Dataflow representation of one instruction performing an $N^{th}$ -order $(N+1)$        |    |

|     | taps) FIR filtering                                                                     | 30 |

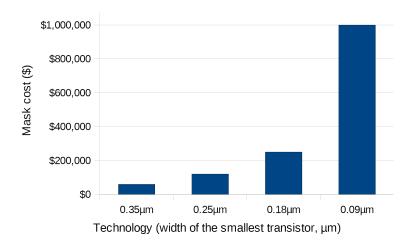

| 2.5 | Mask cost exponentially grows with technology                                           | 32 |

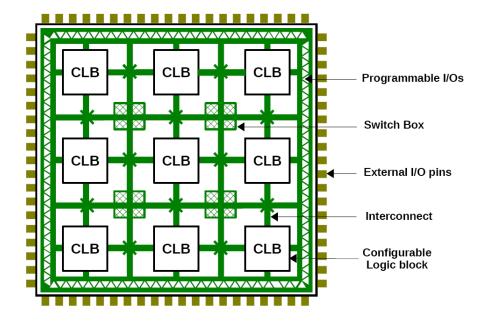

| 2.6 | Simplified structure of an FPGA                                                         | 34 |

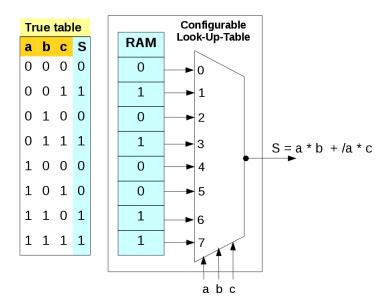

| 2.7 | Truth table of function $S=f$ ( $a,b,c$ ) and its mapping using a 3 inputs              |    |

|     | Look-Up-Table                                                                           | 37 |

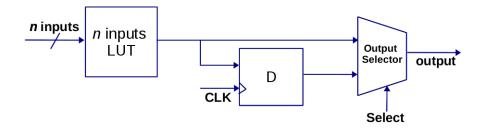

| 2.8 | A logic element or configurable logic block                                             | 38 |

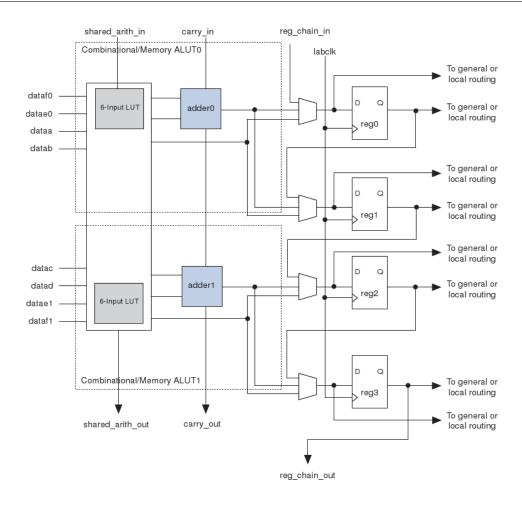

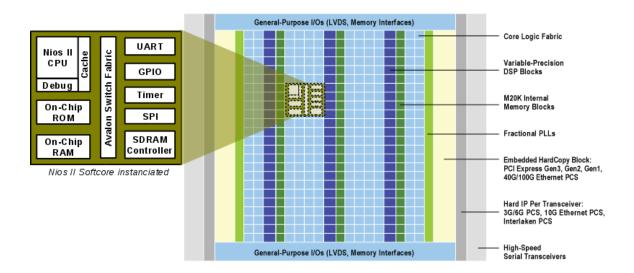

| 2.9  | An Adaptive Logic Module in Altera Stratix V architecture (courtesy Altera).     | 39 |

|------|----------------------------------------------------------------------------------|----|

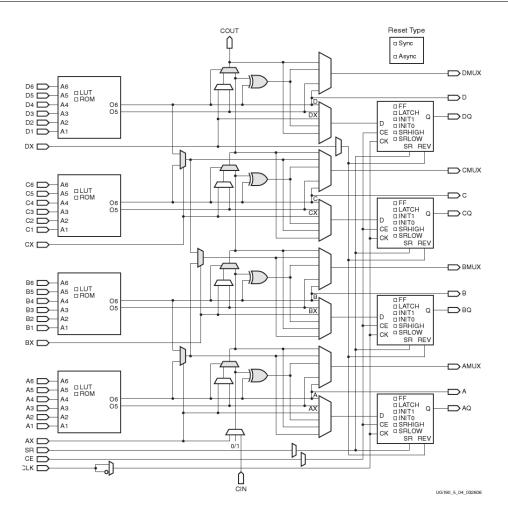

| 2.10 | A Slice (SLICEL) in a Xilinx Virtex 5 FPGA architecture (courtesy Xilinx).       | 40 |

| 2.11 | Altera Stratix-V floor plan (Altera, www.altera.com)                             | 43 |

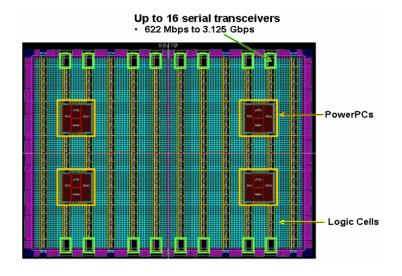

| 2.12 | Xilinx Virtex II Pro FPGA with up to 4 hard core embedded proces-                |    |

|      | sors(Xilinx, www.xilinx.com)                                                     | 43 |

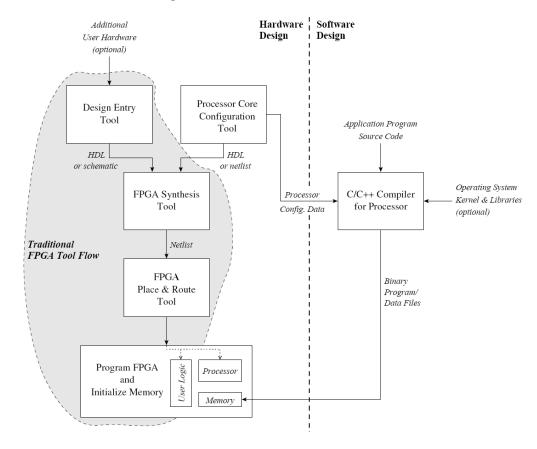

| 2.13 | Design flow for FPGA-based systems embedding a programmable processor.           | 45 |

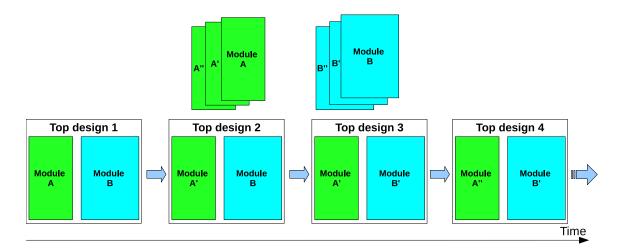

| 2.14 | Modular design enables dynamic module swapping                                   | 47 |

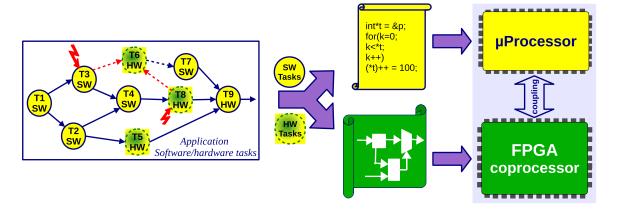

| 2.15 | FPGA as co-processor                                                             | 50 |

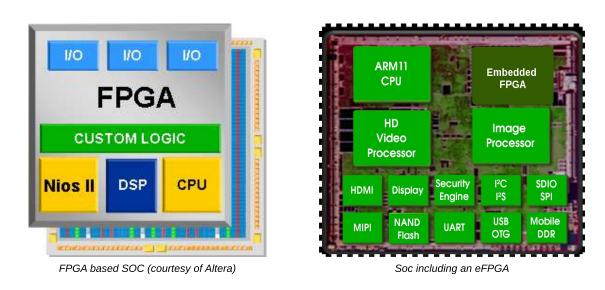

| 2.16 | FPGA based SOPC (left) and embedded FPGA (eFPGA) $\ldots$                        | 50 |

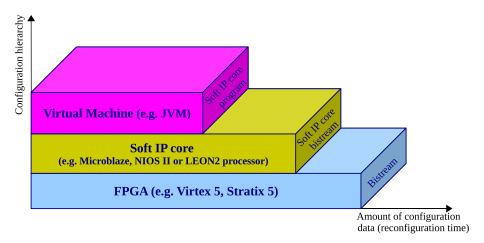

| 2.17 | Configuration hierarchy model                                                    | 53 |

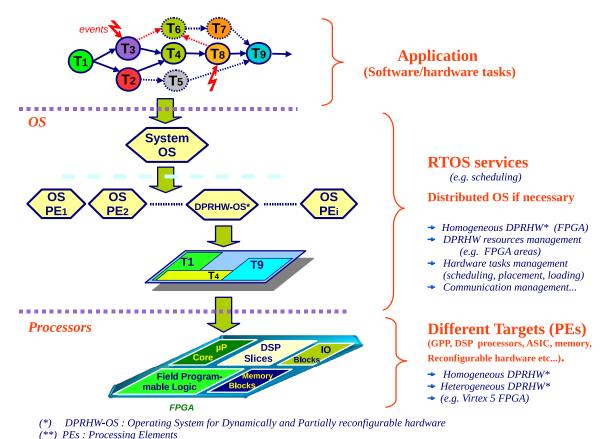

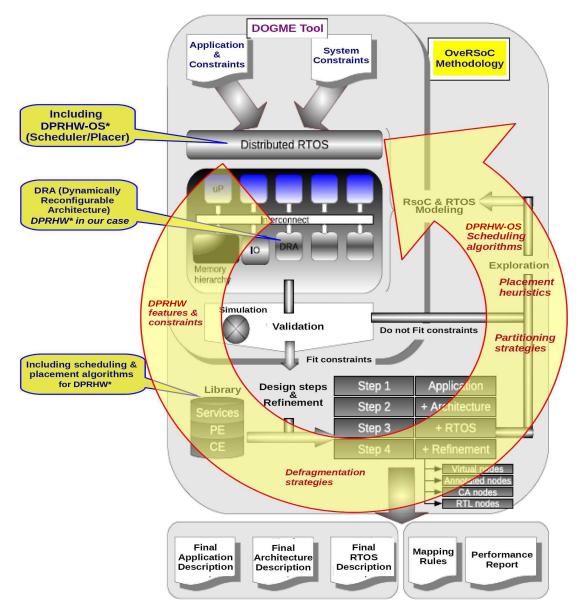

| 2.18 | A view of the OveRSoC methodology with emphasis on DRA (dynamically              |    |

|      | reconfigurable architecture) management                                          | 59 |

| 2.19 | OS services exploration in OveRSoC design methodology (Miramond et al.,          |    |

|      | 2009a) which maps the system level part of the generic design flow of SoC        |    |

|      | (see figure 1.4)                                                                 | 60 |

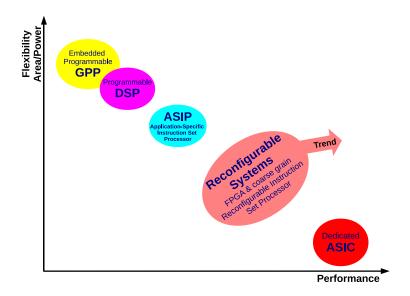

| 2.20 | Flexibility vs Performance of implementation platforms                           | 62 |

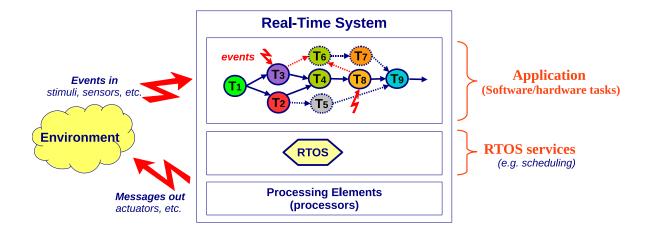

| 3.1  | Model of a Real-Time system                                                      | 65 |

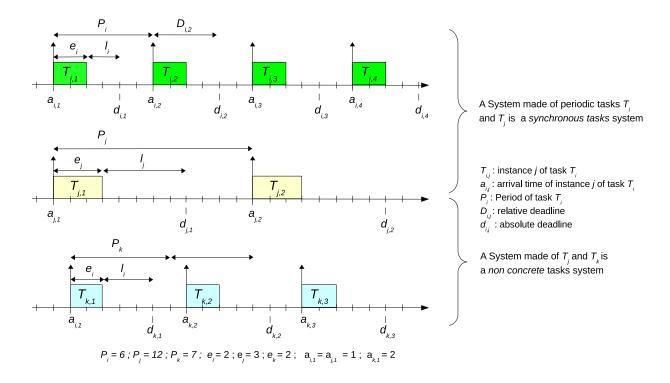

|      | ·                                                                                | 70 |

| 3.2  | Different periodic real-time task according to their release time                |    |

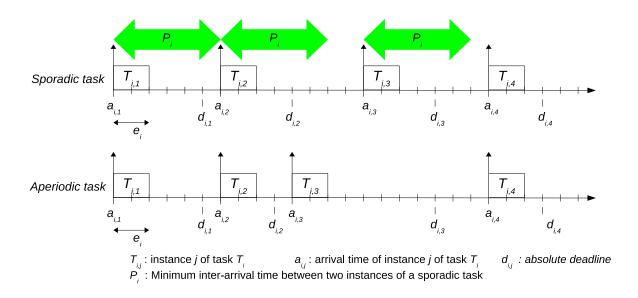

| 3.3  | Aperiodic task and sporadic task                                                 | 71 |

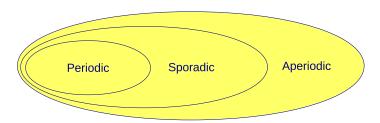

| 3.4  | Periodic, sporadic and aperiodic tasks                                           | 71 |

| 3.5  | Uniprocessor model for reconfigurable hardware devices with time sharing         |    |

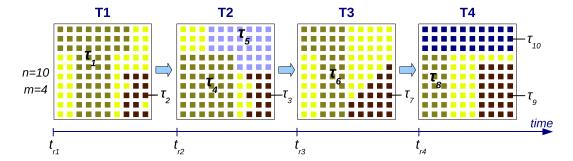

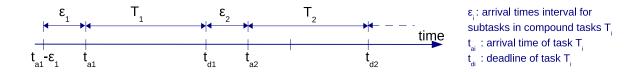

|      | compound tasks                                                                   | 84 |

| 3.6  | Compound tasks timing characteristics                                            | 84 |

| 3.7  | Uniprocessor model for reconfigurable hardware devices with <i>space sharing</i> |    |

|      | compound tasks                                                                   | 86 |

| 3.8  | Equal sizes and unequal sizes partitioning of a DPRHW (dynamically and           |    |

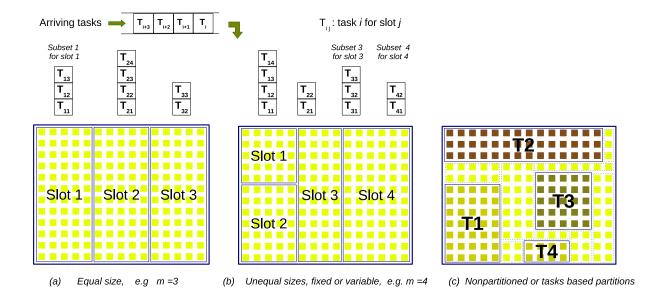

|      | partially reconfigurable hardware device)                                        | 92 |

| 3.9  | Looking-ahead vs without-looking-ahead scheduling approaches                     | 95 |

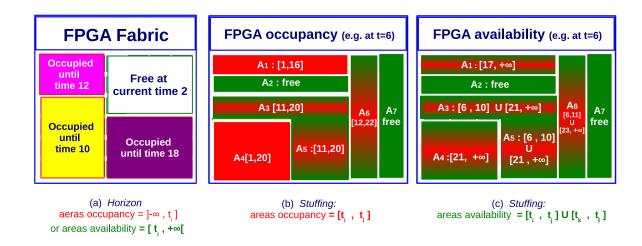

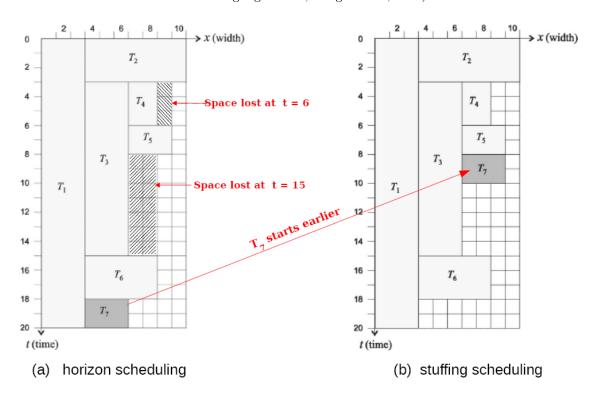

| 3.10 | Managing areas availability or occupancy in looking-ahead scheduling (e.g.      |      |

|------|---------------------------------------------------------------------------------|------|

|      | horizon and stuffing algorithms, Steiger et al., 2004)                          | 100  |

| 3.11 | An example of 1D Horizon and Stuffind scheduling algorithms (Steiger et al., $$ |      |

|      | 2004)                                                                           | 100  |

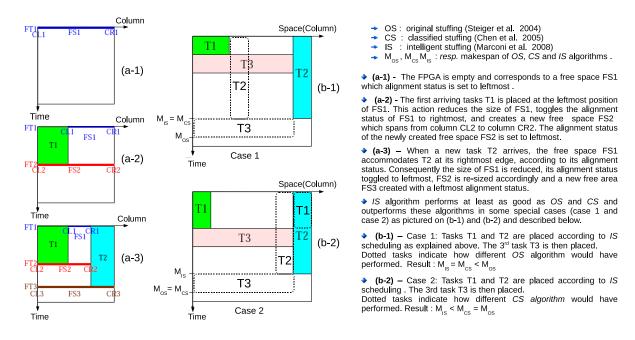

| 3.12 | Intelligent Stuffing (IS) scheduling algorithm using 1D placement (Marconi      |      |

|      | et al., 2008)                                                                   | 103  |

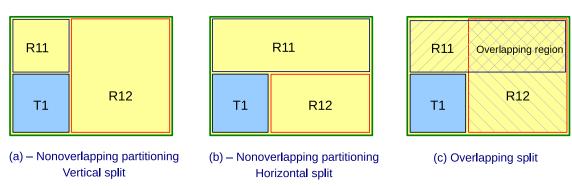

| 3.13 | Nonoverlapping $vs$ overlapping partition; vertical $vs$ horizontal split for   |      |

|      | overlapping partition                                                           | 108  |

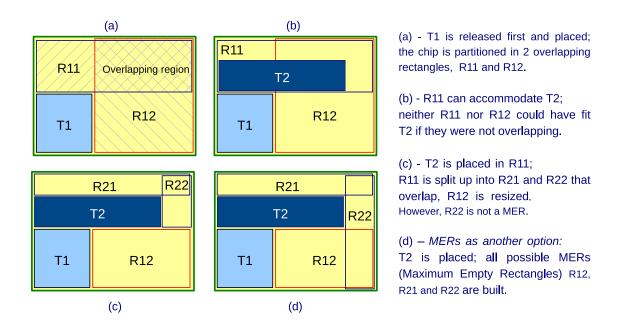

| 3.14 | Placing a task in an overlapping rectangle                                      | 109  |

| 3.15 | Maximum empty rectangles                                                        | 109  |

| 3.16 | A binary tree used as a data structure that records the state of the FPGA       | 11   |

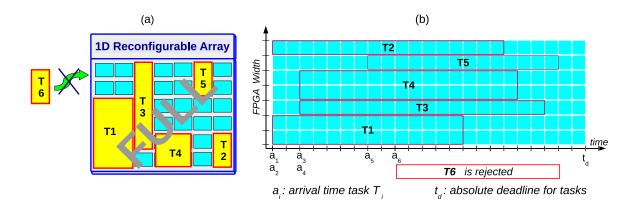

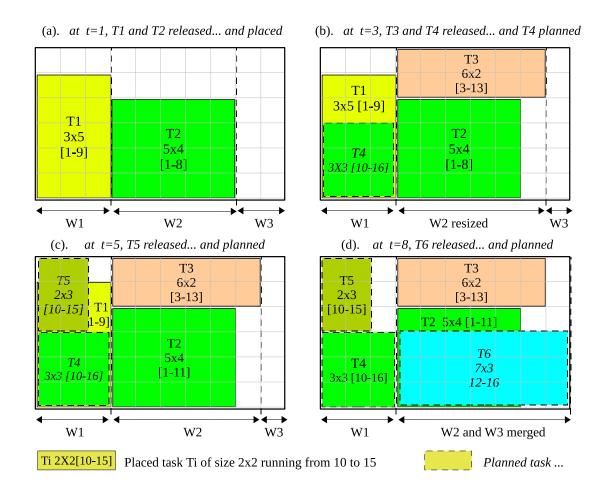

| 3.17 | Scheduling tasks on a 7 X $6$ reconfigurable array using a 1D placement mode    | 1114 |

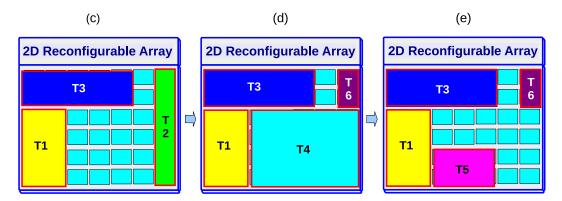

| 3.18 | 2D placement model of tasks on a 7 X 6 reconfigurable array $\ \ldots \ \ldots$ | 115  |

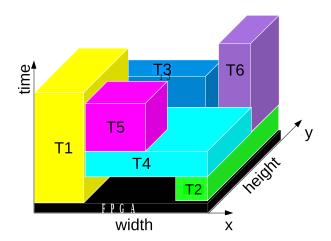

| 3.19 | 3D view of the 2D placement model illustrated in figure $3.18\ldots\ldots$      | 116  |

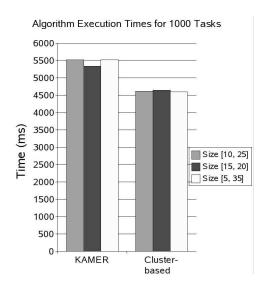

| 3.20 | Algorithms execution time comparison between KAMER algorithm (Bazargar          | 1    |

|      | et al., 2000) and 1D Cluster-based algorithm (Ahmadinia et al., 2004) $$        | 118  |

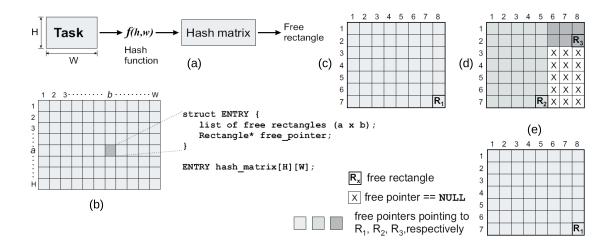

| 3.21 | The hash matrix approach (a), the hash table (b) rectangle insertion/deletion   |      |

|      | in the hash matrix (c), (d) and (e) (Walder et al., 2003) $\dots$               | 120  |

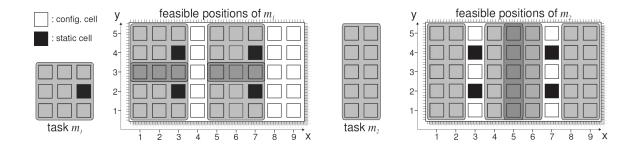

| 3.22 | Placing tasks $m_1$ and $m_2$ on an heterogeneous reconfigurable architecture   |      |

|      | (Koester et al., 2005)                                                          | 121  |

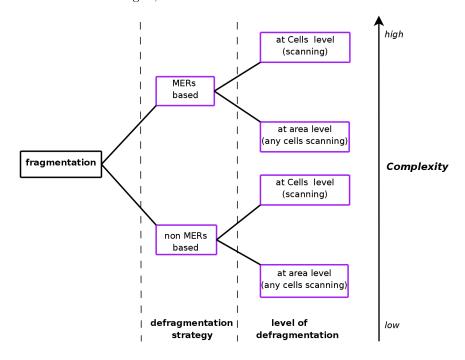

| 3.23 | Defragmentation strategies: complexity grows with performance                   | 123  |

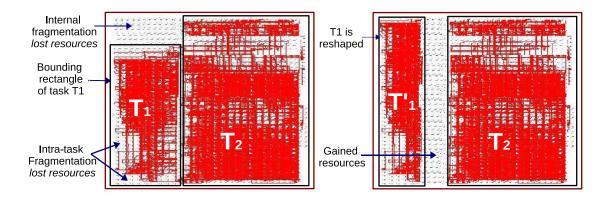

| 3.24 | Intra-task and internal fragmentation                                           | 126  |

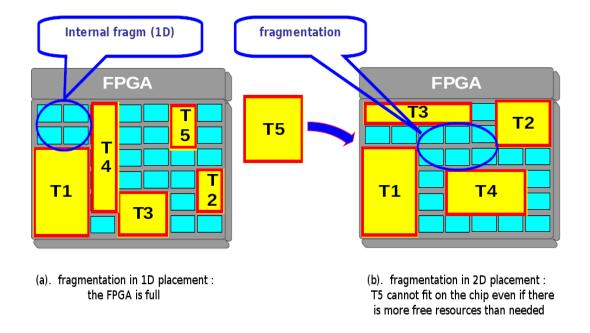

| 3.25 | A fragmented FPGA: the free space available on the chip is sufficient to        |      |

|      | insert the arriving task, but its shape doesn't allow it.                       | 126  |

| 3.26 | Bazargan's adjacency graph: bigger rectangles restoration process (Bazargan     |      |

|      | et al., 2000)                                                                   | 128  |

| 3.27 | Footprint Transform (Walder and Platzner, 2002)                                 | 129  |

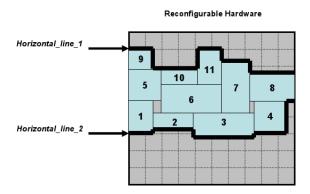

| 3 28 | Using horizontal line to manage free space Ahmadinia et al. (2004)              | 131  |

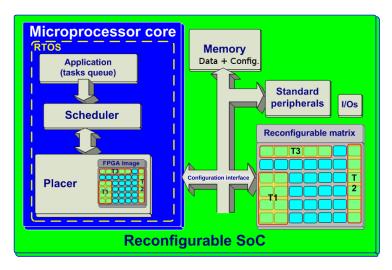

| 4.1  | A simple architecture of a reconfigurable SoC                                     | 138   |

|------|-----------------------------------------------------------------------------------|-------|

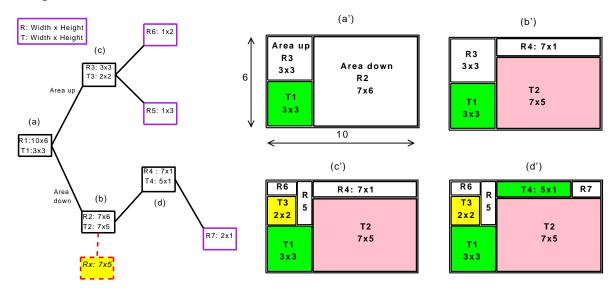

| 4.2  | Scheduling one task on the reconfigurable array using a MERs-based place-         |       |

|      | ment algorithm                                                                    | 141   |

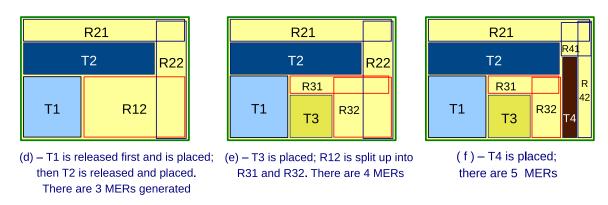

| 4.3  | Scheduling the end of a task using a MERs-based scheduling algorithm              | 141   |

| 4.4  | Time for finding a MER (Maximum Empty Rectangle)                                  | 143   |

| 4.5  | Scheduling timing and overheads (staircase)                                       | 144   |

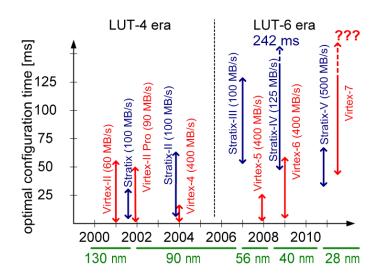

| 4.6  | Evolution (over one decade) of the configuration time of a full FPGA when         |       |

|      | considering the fastest possible configuration speed (Koch and Torresen,          |       |

|      | 2010)                                                                             | 144   |

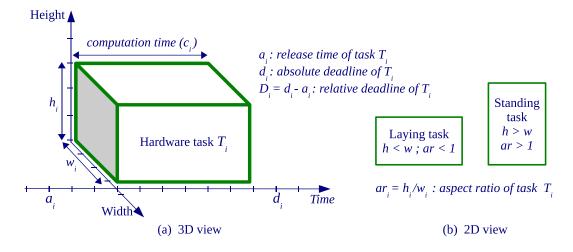

| 4.7  | A hardware task model: 2D view (b) and 3D view (a)                                | 147   |

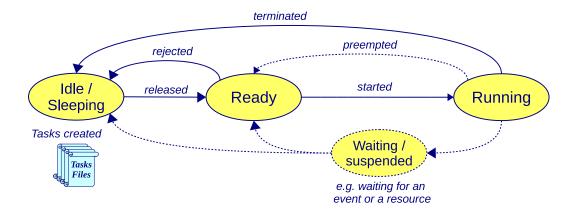

| 4.8  | Different states of a hardware task                                               | 149   |

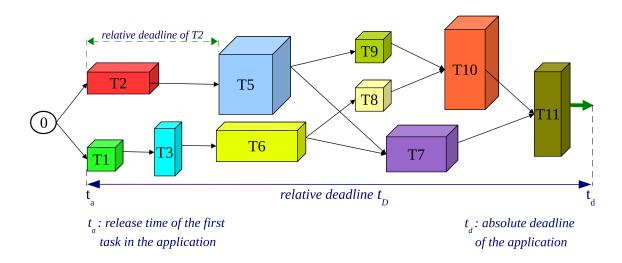

| 4.9  | An application as a set of boxes (taskgraph)                                      | 152   |

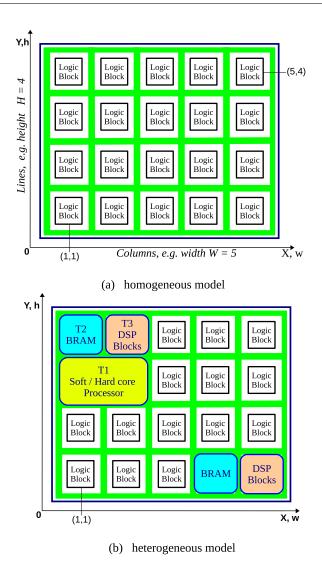

| 4.10 | Simple models of homogeneous and heterogeneous reconfigurable array $\ .$ .       | 154   |

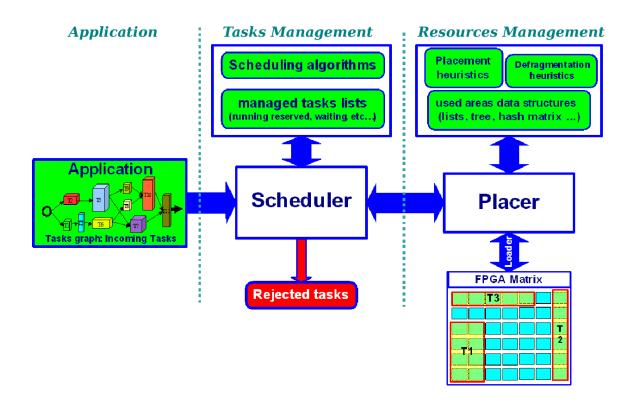

| 4.11 | The global simulation model                                                       | 156   |

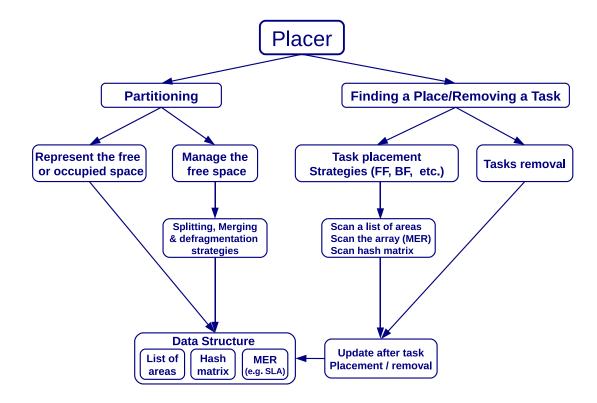

| 4.12 | The placer model and its different functional parts                               | 157   |

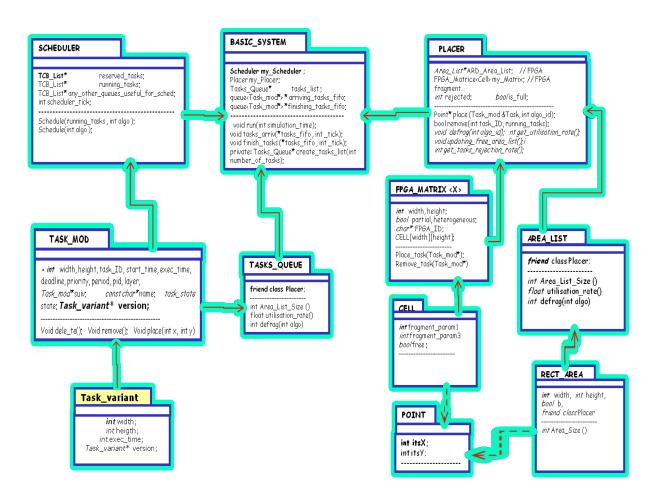

| 4.13 | An UML overview of the global simulation model of the DPRHW-OS for a              |       |

|      | reconfigurable platform                                                           | 166   |

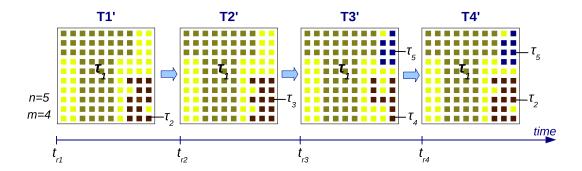

| 5.1  | 1D-like partitioned scheduling                                                    | 178   |

| 5.2  | 1D improved horizon scheduling algorithm, also denoted as $1D\ variable\ size$    |       |

|      | slots horizon (1D-VSSH)                                                           | 182   |

| 5.3  | List scheduling $vs$ optimal scheduling of $n$ tasks on $m$ identical processors; |       |

|      | $e_i$ is the execution time of task $T_i$                                         | 184   |

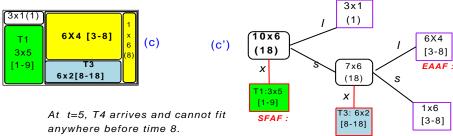

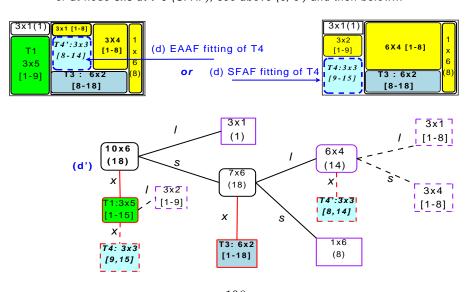

| 5.4  | Ternary tree structure: splitting and updating processes                          | 190   |

| 5.5  | Multi-shape tasks provides more fitting opportunities (e.g. $T_3$ provides 5      |       |

|      | variants)                                                                         | 192   |

| 5.6  | Flow chart of the multi-shape algorithm that selects task version to be placed    | . 194 |

| 6.1  | Summarizing the scheduling problem as defined in this thesis                      | 198   |

| 6.2  | Utilization ratio (top), rejection ratio (middle) and quality metrics (bottom)                                      |     |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

|      | : comparative results for EDF, LLF, SSF and BSF scheduling algorithms.                                              | 203 |

| 6.3  | Scheduling runtime overhead, number of scheduling calls and cumulative                                              |     |

|      | scheduler runtime overheads : comparative results on EDF, LLF, SSF and                                              |     |

|      | BSF scheduling algorithms                                                                                           | 204 |

| 6.4  | Different combinations of multi-shape tasks for variants of multi-shape                                             |     |

|      | scheduling algorithm                                                                                                | 207 |

| 6.5  | Multi-shape scheduling algorithms: simulation results of the utilization ra-                                        |     |

|      | tio, comparison with the Basic scheduling                                                                           | 208 |

| 6.6  | Multi-shape scheduling algorithms: simulation results of the tasks rejection                                        |     |

|      | ratio, comparison with the Basic scheduling                                                                         | 209 |

| 6.7  | Utilization ratio, tasks rejection ratio and differential quality metric $UR_{qm}$                                  |     |

|      | (with $\alpha=0.5$ ) : comparative results for basic scheduling and multi-shape                                     |     |

|      | scheduling algorithms.                                                                                              | 212 |

| 6.8  | The average makespan : comparative results for multi-shape and Basic                                                |     |

|      | scheduling algorithms.                                                                                              | 214 |

| 6.9  | $\label{eq:Multi-shape} \mbox{Multi-shape scheduling algorithms}: \mbox{ the simulation results of the scheduling}$ |     |

|      | runtime overhead, with basic scheduling as reference scheduling                                                     | 215 |

| 6.10 | Differential quality metrics for horizon-EAAF, horizon-SFAF, Basic and                                              |     |

|      | EDF scheduling algorithms                                                                                           | 220 |

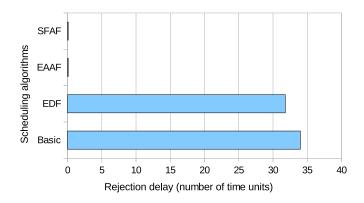

| 6.11 | Rejection delay for horizon-EAAF, horizon-SFAF, Basic and EDF schedul-                                              |     |

|      | ing algorithms.                                                                                                     | 220 |

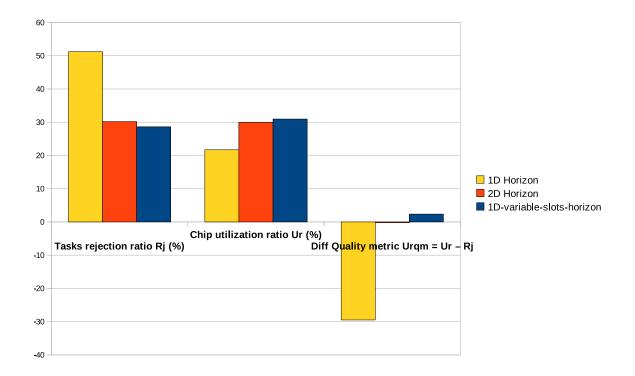

| 6.12 | Tasks rejection ratio, reconfigurable array utilization ratio and differential                                      |     |

|      | quality metric for the proposed $1D\ variable\ slots\ horizon$ scheduling, com-                                     |     |

|      | pared to 1D and 2D horizon scheduling from Steiger et al. (2004) $\ldots$                                           | 223 |

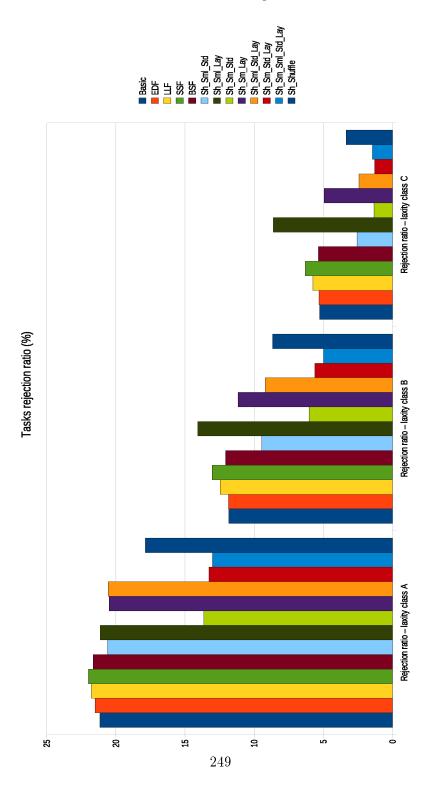

| 7.1  | The tasks rejection ratio for paramaters based scheduling and multi-shape                                           |     |

|      | tasks based scheduling.                                                                                             | 249 |

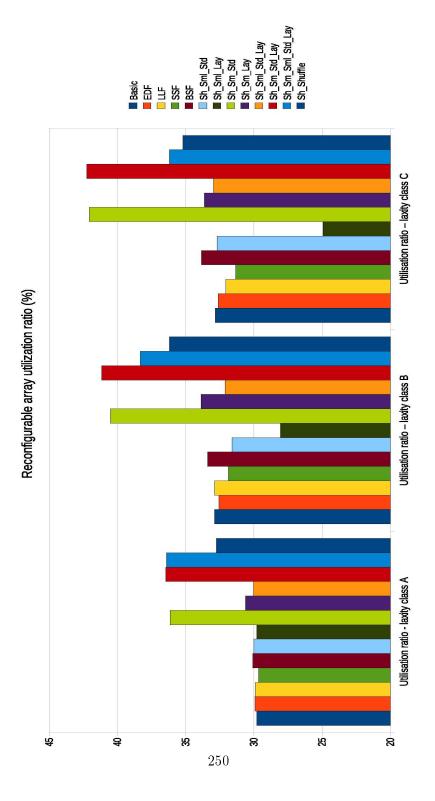

| 7.2 | The reconfigurable array utilization ratio for paramaters based scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | and multi-shape tasks based scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 250 |

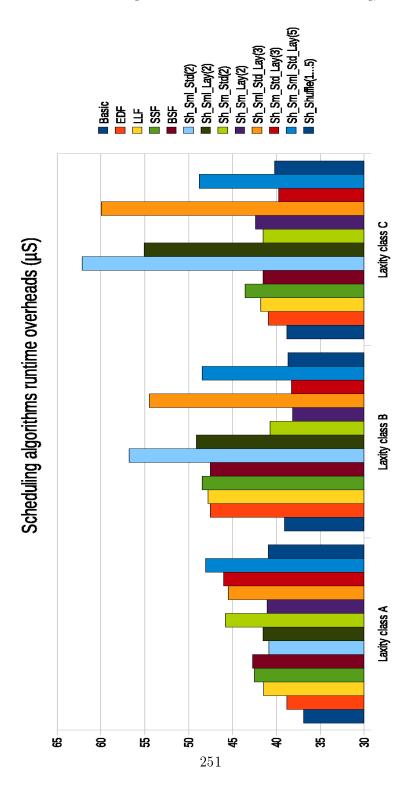

| 7.3 | The runtime overheads of without-looking-ahead scheduling algorithms (parameters) and the scheduling algorithm |     |

|     | maters based scheduling and multi-shape tasks based scheduling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 251 |

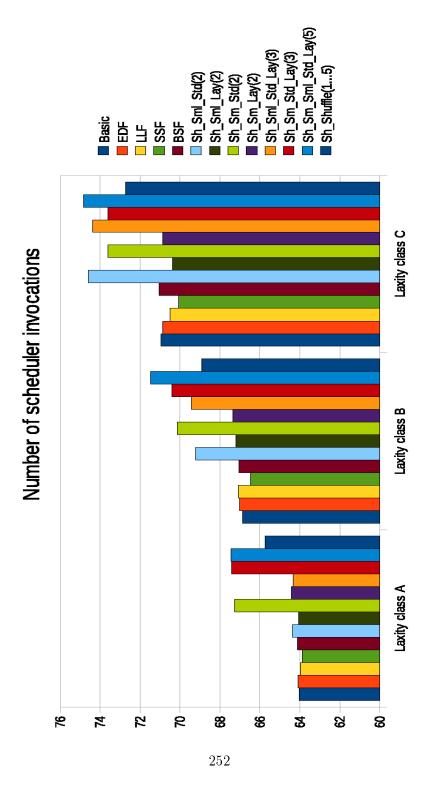

| 7.4 | The number of scheduler invocations for without-looking-ahead schedul-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|     | ing algorithms (paramaters based scheduling and multi-shape tasks based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|     | scheduling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 252 |

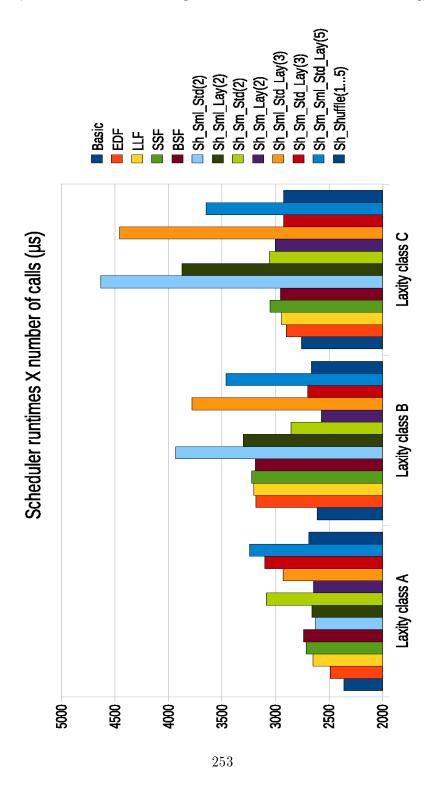

| 7.5 | The cumulative runtime overheads for without-looking-ahead scheduling al-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|     | gorithms (paramaters based scheduling and multi-shape tasks based schedul-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|     | $ing)  \dots $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 253 |

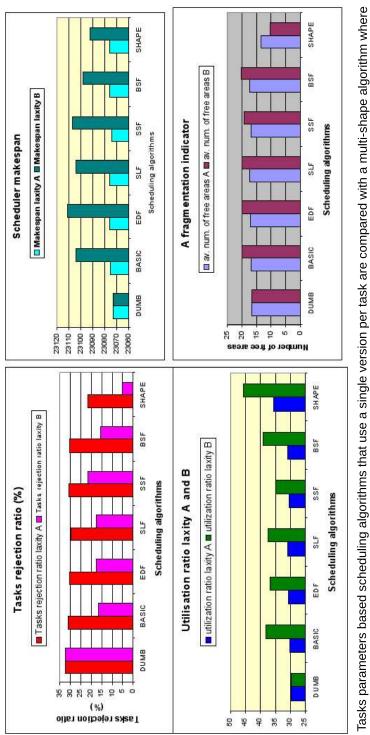

| 7.6 | Tasks parameters based scheduling algorithms $vs$ multi-shape algorithm :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|     | Simulation on a large number of tasks (10 sets of 5000 tasks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 254 |

| 7.7 | Serial Distributed Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 264 |

| 7.8 | Serial-Parallel Distributive Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 264 |

| 7.9 | Example of resources utilization for different DA implementation of a FIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|     | filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 265 |

## List of Tables

| 2.1 | Comparative table of implementation platforms for DSP applications (Adam,                                  |     |

|-----|------------------------------------------------------------------------------------------------------------|-----|

|     | 2002)                                                                                                      | 62  |

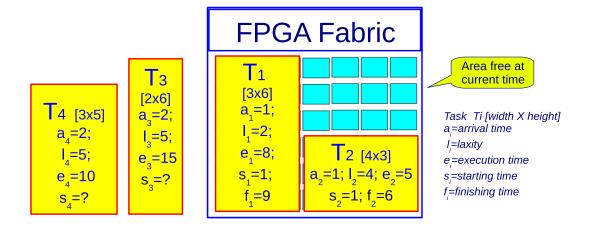

| 3.1 | Tasks to schedule on an FPGA of size 7 X 6                                                                 | 114 |

| 3.2 | $Comparison \ of the \ simulation \ results \ with \ the \ 1D-placement \ approach \ (Koester \ approach)$ | er  |

|     | et al., 2005)                                                                                              | 122 |

| 4.1 | Simulation paremeters for tasks and the reconfigurable array (FPGA) $$                                     | 142 |

| 5.1 | A pseudo code of the tasks parameters-based scheduling algorithm                                           | 171 |

| 5.2 | A pseudo code of the basic scheduling algorithm                                                            | 174 |

| 5.3 | A pseudo code of the 1D variable slots scheduling algorithm                                                | 180 |

| 5.4 | Tasks parameters for 1D $variable\ size\ slots\ looking-ahead\ scheduling$                                 | 181 |

| 5.5 | A pseudo code of the 1D variable slots with minimum makespan algorithm                                     | 186 |

| 5.6 | Example of tasks parameters for $horizon$ - $SFAF$ and $horizon$ - $EAAF$ schedul-                         |     |

|     | ing algorithms                                                                                             | 189 |

| 6.1 | Approximate sizes of most common IPs (hardware tasks)                                                      | 199 |

| 6.2 | Simulation results for looking-ahead scheduling using a ternary tree : com-                                |     |

|     | parison with basic scheduling and EDF scheduling                                                           | 219 |

| 7.1 | Related work on scheduling and placement strategies (homogeneous reconfi-                                  |     |

|     | gurable array model)                                                                                       | 246 |

| 7.2 | Related work on scheduling and placement strategies (heterogeneous reconfi-       |      |

|-----|-----------------------------------------------------------------------------------|------|

|     | gurable array model)                                                              | 247  |

| 7.3 | Scheduling algorithms implemented.                                                | 256  |

| 7.4 | List of placement algorithms implemented                                          | 257  |

| 7.5 | List of placement structures implemented (1): The areas partitioning (ex-         |      |

|     | isting works are cited and those from us are highlighted)                         | 258  |

| 7.6 | List of placement structures implemented (2): Finding fitting areas and           |      |

|     | merging free areas (existing works are cited and those from us are highlighted)   | .259 |

| 7.7 | Few IPs for Virtex2pro FPGAs from the XILINX Core Generator System <sup>1</sup> . | 260  |

#### Nomenclature

$A_{fpqa}$ : Area or total amount of resources on the reconfigurable array (FPGA)

$a_i$ : Release time of a task or job  $T_i$

$Ap_{load}$ : Relative application load or the relative amount of resources required to complete

an  $Ap_k$  on a given reconfigurable array of size  $A_{fpga} = W \cdot H$

$Ap_n$ : Application consisting of n jobs (or set of n tasks or jobs)

ar : Aspect ratio of a hardware task

$c_i$ : Execution or processing time of task  $T_i$

$egin{array}{lll} d_i & : & \mbox{Absolute deadline of task $T_i$} \\ D_i & : & \mbox{Relative deadline of task $T_i$} \\ \end{array}$

$e_i$ : Execution or processing time of task  $T_i$

$ft_{av}$ ,  $rt_{av}$ : Average flow time or response time of a job sequence or tasks set

$ft_i$ ,  $rt_i$ : Response time or flow time of a scheduled task  $T_i$

$ft_{tot}$ ,  $rt_{tot}$ : Total flow time or response time of a job sequence or tasks set

$f_i$  : Finishing time of a task or job  $h_i$  : Height of hardware task  $T_i$

Hp: Hyper-period of a periodic tasks set

$J_i$ : Job number i, with i = 1...n

$l_i$ : Laxity of a task  $T_i$

m : Number of processors or resources available for jobs processing

$M_i$ : Processor number i in a multiprocessor system which consists of m processors

$M_1, M_2, ..., M_m$

mk : Scheduling makespan or length of the scheduling

n: Number of jobs to be processed

$n_a$ : Number of jobs accepted by the scheduling algorithm, among the k jobs in the

application  $\Gamma_k$ , where  $n_a \leq k$ , and  $k = n_a + n_j$

$N_{acc}$ : Number of accepted tasks or jobs

$n_i$ : Number of jobs rejected by the scheduling algorithm, among the k jobs in the

application  $\Gamma_k$ , where  $n_j \leq k$

$N_{rej}$ : Number of rejected tasks or jobs

$P_i$ : Period of a periodic task  $T_i$

$Rd_i$ : Rejection delay of a task  $T_i$

$Res_{Ap}$ : Total amount of resources required to complete all the k jobs  $J_{i=1...k}$  of an

application  $Ap_k$

$Res_{Ti}$ : Total amount of resources required to complete an instance of a hardware

task  $T_i$

$Rj_{\Gamma_k(\%)}$ ,  $Rj_{-}(\%)$ : Tasks rejection ratio

$rt_{av}$ ,  $ft_{av}$ : Average flow time or response time of a job sequence or tasks set