**ANNÉE 2013** Nº d'ordre : 00000

#### **THÈSE / UNIVERSITÉ DE RENNES 1** sous le sceau de l'Université Européenne de Bretagne

pour le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Traitement du signal et télécommunications

**École doctorale Matisse**

présentée par

## **Istas Pratomo**

préparée à l'unité de recherche IETR – UMR6164 École National Supérieure des Sciences Appliquées et de Technologie

Adaptive NoC for Thèse soutenue à Rennes Reconfigurable SoC / NoC Adaptatif pour SoC Reconfigurable

le 08 Novembre 2013

devant le jury composé de :

**Bertrand GRANADO**

Professeur à l'UPMC / Rapporteur

**Dominique HOUZET**

Professeur à Grenoble-INP / Rapporteur

Achmad Affandi

Professeur à ITS de Surabaya / Examinateur

**Christophe Moy**

Professeur à SUPELEC de Rennes / Examinateur

Sébastien PILLEMENT

Professeur à l'Universite de Nantes / Directeur de thèse

To my wife, Eka Prasetiya Noviyanti our daughters, Nadifa Istasabira and Belmine Lumier Pratomo and my parents, Sri Atmini and Slamet Widodo almarhum

## Acknowledge

First and foremost I offer my sincerest gratitude to my supervisor Prof. Sebastien Pillement. This work would not have been possible without his guidance, suggestions, remarks, constructive feedback, comments at various stages and support. He has taught me with patience, both consciously and unconsciously. I appreciate all his contributions of time, ideas and It has been an honor to be his Ph.D. student.

Equally, I wish to thank the head of the Lab Prof. Oliver Sentieys for his kind attitude, generous help and precious suggestions during my PhD thesis. I also want to thank all the members of the jury: Bertrand GRANADO, Dominique HOUZET, Christophe MOY and Achmad AFFANDI who evaluated this work. I wish to thank all the members of the IRISA/CAIRN Lab who make my stay a memorial period. It is a great pride for me completing the PhD thesis in this dynamic Lab.

I am extremely grateful to the Directorate General for Higher Education (DGHE), Ministry of National Education, The Republic of Indonesia for their financial support of this thesis. Finally, I would like to thank my wife, my daughters and my parents for their never ending support and encouragement, that has help me to stay concentrated on my thesis.

Lannion, France May 2013

Abstract: Chips will be designed with billion of transistors and heterogeneous components integrated to provide full functionality of an current application for embedded system. These applications also require highly parallel and flexible communicating architecture through a regular interconnection network. The emerging solution that can fulfill this requirement is Network-on-Chips (NoCs).

Designing an ideal NoC with high throughput, low latency, minimum using resources, minimum power consumption and small area size are very time consuming. Each application required different levels of QoS such as minimum level throughput, delay and jitter. In this thesis, firstly, we proposed an evaluation of the impact of design parameters on performance of NoC. We evaluate the impact of NoC design parameters on the performances of an adaptive NoCs. The objective is to evaluate how big the impact of upgrading the value on performances. The result shows the accuracy of choosing and adjusting the network parameters can avoid performance degradation. It can be considered as the control mechanism in an adaptive NoC to avoid the degradation of QoS NoC.

The use of deep sub-micron technology in embedded system and its variability process cause Single Event Upsets (SEU) and "aging" the circuit. SEU and aging of circuit is the major problem that cause the failure on transmitting the packet in a NoC. Implementing fault-tolerant routing techniques in NoC switching instead of adding virtual channel is the best solution to avoid the fault in NoC. Communication performance of a NoC is depends heavily on the routing algorithm. Adaptive routing algorithms such as fault-tolerant has been proposed for deadlock avoidance and load balancing.

This thesis proposed a novel adaptive fault-tolerant routing algorithm for 2D mesh called *Gradient* and for 3D mesh called *Diagonal*. Both algorithm considers sequences of alternative paths for packets when the main path fails. The proposed algorithm tolerates faults in worst condition traffic in NoCs. The number of hops, the number of alternative paths, latency and throughput in faulty network are determined and compared with other 2D mesh routing algorithms. Finally, we implemented Gradient routing algorithm into FPGA.

All these work were validated and characterized through simulation and implemented into FPGA. The results provide the comparison performance between proposed method with existing related method using some scenarios.

Keywords: adaptive NoC - impact parameter - fault tolerant routing

## Contents

| $\mathbf{C}$ | onten | ${f ts}$                                          | viii |

|--------------|-------|---------------------------------------------------|------|

| Li           | st of | Figures                                           | xii  |

| Li           | st of | Table                                             | xvi  |

| 1            | Intr  | oduction                                          | 1    |

|              | 1.1   | Problem statement (open challenges)               | 6    |

|              |       | 1.1.1 Impact of design parameters on performances | 6    |

|              |       | 1.1.2 Fault-tolerant routing algorithm            | 6    |

|              | 1.2   | Objectives and contributions                      | 7    |

|              |       | 1.2.1 Objectives                                  | 7    |

|              | 1.3   | Organization of the manuscript                    | 9    |

| <b>2</b>     | Stat  | e of the art - Definitions                        | 11   |

|              | 2.1   | From Bus to NoC                                   | 11   |

|              | 2.2   | Network-on-Chips architecture                     | 14   |

|              |       | 2.2.1 Topologies                                  | 15   |

|              |       | 2.2.2 Switching                                   | 18   |

|              |       | 2.2.3 Flow control                                | 20   |

|              |       | 2.2.4 Routing                                     | 20   |

|              | 2.3   | 3-D NoC Technologies                              | 22   |

|              | 2.4   | Performances, parameters and dependencies         | 25   |

|              | 2.5   | Fault-tolerant and deadlock-free techniques       | 27   |

Contents

|   |     | 2.5.1   | Problems of non-fault tolerant routing                          | 27 |

|---|-----|---------|-----------------------------------------------------------------|----|

|   |     | 2.5.2   | Fault tolerant and deadlock freeness                            | 28 |

|   | 2.6 | NoCs    | simulator                                                       | 31 |

|   | 2.7 | NoCs    | prototyping                                                     | 33 |

|   |     | 2.7.1   | NoC design process                                              | 33 |

|   |     | 2.7.2   | Prototyping NoC into FPGA                                       | 34 |

|   | 2.8 | Concl   | asions                                                          | 36 |

| 3 | Imp | oacts o | f NoC Design Parameters on Transmission Performance             | 39 |

|   | 3.1 | Main I  | NoC Parameters                                                  | 39 |

|   |     | 3.1.1   | NoC router parameters                                           | 40 |

|   |     | 3.1.2   | Network parameters                                              | 41 |

|   | 3.2 | Existin | ng work on evaluate of the impact of parameters on performances | 43 |

|   | 3.3 | Impac   | ts of Design Parameters on Performance                          | 44 |

|   | 3.4 | Metho   | dology and Experimental Result                                  | 48 |

|   |     | 3.4.1   | Worst condition scenarios                                       | 49 |

|   |     | 3.4.2   | Network saturation                                              | 50 |

|   |     | 3.4.3   | Impact of adjusting parameters value on performances            | 53 |

|   |     | 3.4.4   | Best parameters type on performances                            | 58 |

|   | 3.5 | Concl   | asions                                                          | 63 |

| 4 | Fau | lt tole | rant routing algorithm for 2D and 3D mesh network               | 67 |

|   | 4.1 | Gradie  | ent: Fault-tolerant Routing Algorithm for 2D Mesh Topology      | 68 |

|   |     | 4.1.1   | Gradient algorithm                                              | 68 |

|   |     | 4.1.2   | Evaluation of minimum hops and alternative path                 | 71 |

|   |     |         | 4.1.2.1 Scenarios                                               | 74 |

|   |     |         | 4.1.2.2 Evaluation result                                       | 75 |

|   | 4.2 | Diago   | nal: Fault-tolerant routing algorithm for 3D mesh topology      | 78 |

|   |     | 4.2.1   | Diagonal algorithm                                              | 82 |

|   |     | 199     | Evaluation of minimum hone                                      | 25 |

| X | Contents |

|---|----------|

| Λ | Contents |

|                  | 4.3               | Concl   | usion of the chapter                               | . 86  |

|------------------|-------------------|---------|----------------------------------------------------|-------|

| 5                | Exp               | erime   | ntal Results                                       | 89    |

|                  | 5.1               | Gradi   | ent: Fault tolerant routing algorithm              | . 89  |

|                  |                   | 5.1.1   | Evaluation based on the faulty position            | . 90  |

|                  |                   | 5.1.2   | Evaluation on increasing faulty node in network    | . 90  |

|                  |                   | 5.1.3   | Evaluation on the scalability of network           | . 91  |

|                  |                   | 5.1.4   | Conclusion                                         | . 92  |

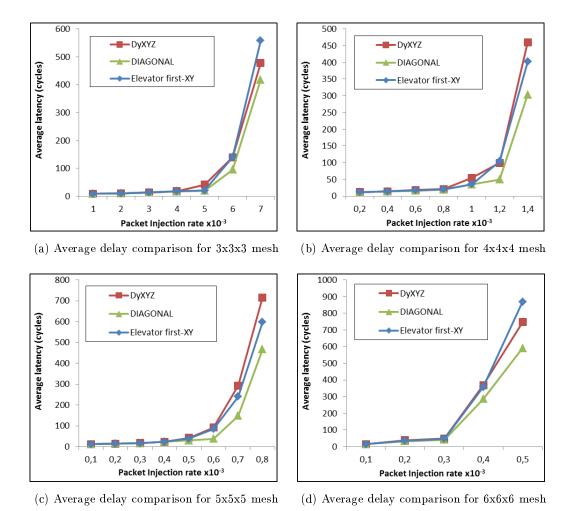

|                  | 5.2               | Diago   | nal: Fault tolerant routing algorithm              | . 93  |

|                  |                   | 5.2.1   | Evaluation on increasing faulty in network         | . 94  |

|                  |                   | 5.2.2   | Evaluation on increasing injection rate in network | . 94  |

|                  |                   | 5.2.3   | Conclusion                                         | . 95  |

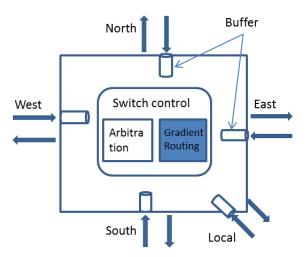

|                  | 5.3               | Imple   | mentation on FPGA                                  | . 96  |

|                  |                   | 5.3.1   | Synthesis result                                   | . 96  |

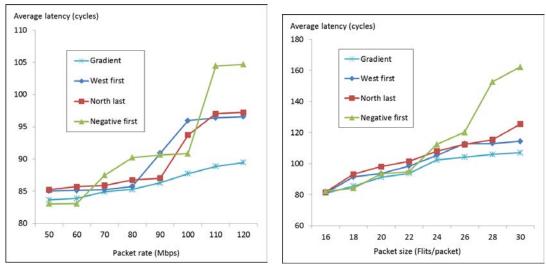

|                  |                   | 5.3.2   | Gradient performances in RTL level                 | . 99  |

|                  | 5.4               | Concl   | usion of the chapter                               | . 101 |

| 6                | Con               | nclusio | ns and perspectives                                | 103   |

|                  | 6.1               | Concl   | $\operatorname{usions}$                            | . 103 |

|                  | 6.2               | Perspe  | ectives                                            | . 105 |

| Bi               | bliog             | graphie | е                                                  | 114   |

| Pe               | erson             | ıal Pul | olication                                          | 115   |

| $\mathbf{A}$     | bbre <sup>.</sup> | viation | 15                                                 | 117   |

| $\mathbf{A}_{1}$ | ppen              | dix     |                                                    | 121   |

| A                | Pat               | h line  | of routing algorithm in 20 case scenario           | 121   |

| $\mathbf{B}$     | Tab               | el con  | nbination of Diagonal algorithm                    | 129   |

Contents

C Decision path comparison of 3D mesh topology for 4 fault scenarios 133

# List of Figures

| 1.1  | General NoC architecture which contains resources (processor, memory,   |    |

|------|-------------------------------------------------------------------------|----|

|      | DSP, etc), switch/router and network interface.                         | 3  |

| 1.2  | Proposed novel routing technique as an approaches towards adaptive NoC  | 5  |

| 2.1  | Direct point to point connection infrastructure for SoC [7]             | 12 |

| 2.2  | Shared bus interconnection infrastructure for SoC                       | 13 |

| 2.3  | Packet switched network communication infrastructure                    | 14 |

| 2.4  | General NoC communication architecture                                  | 16 |

| 2.5  | Regular topologies used in NoC: (a) 2-D mesh, (b) torus, (c) ring and   |    |

|      | (d) binary tree                                                         | 17 |

| 2.6  | General 2-D mesh router architecture                                    | 17 |

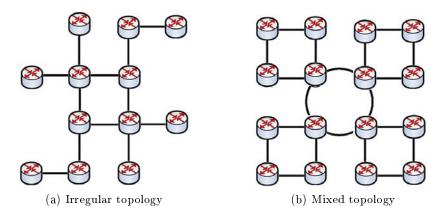

| 2.7  | The example of (a) irregular and (b) mixed topology used in NoC         | 18 |

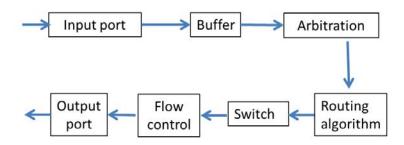

| 2.8  | General switching process                                               | 19 |

| 2.9  | The forbidden turns (dashed line) in turn model routing algorithm: (a)  |    |

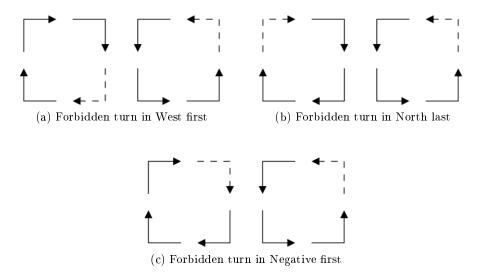

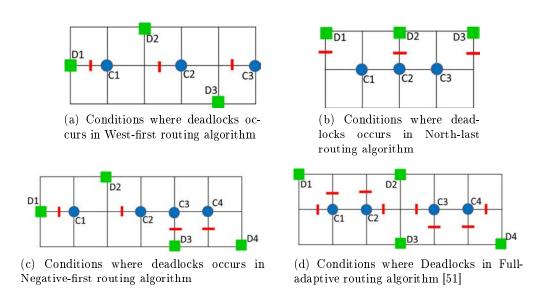

|      | West first, (b) North last and (c) Negative first [52]                  | 22 |

| 2.10 | The concept of 3-D topology to make the distance between node closer    |    |

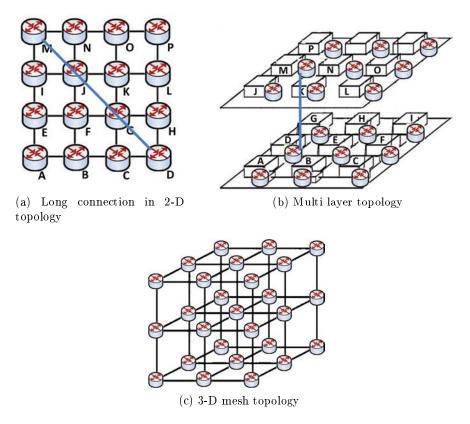

|      | than in 2-D topology                                                    | 24 |

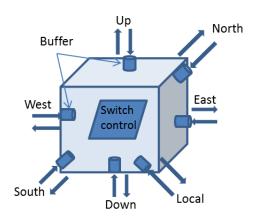

| 2.11 | 3-D mesh router architecture                                            | 25 |

| 2.12 | Conditions where deadlocks occur in (a) West-first, (b) North-last, (c) |    |

|      | Negative-first and (d) Full-adaptive routing algorithm                  | 30 |

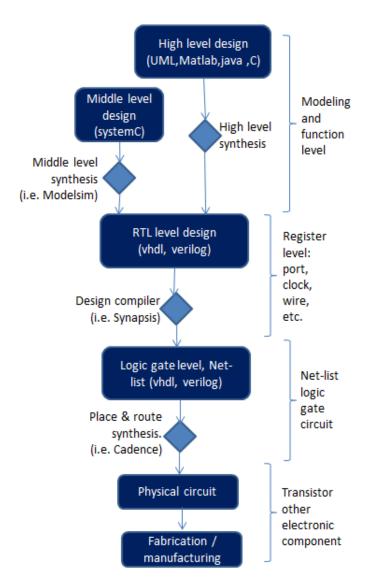

| 2.13 | Abstraction level of NoC design process [5]                             | 35 |

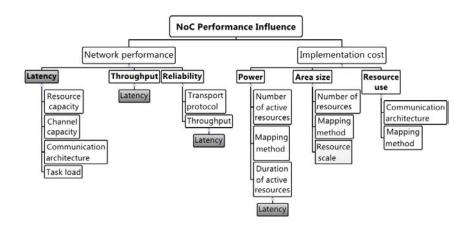

| 3.1  | NoC performances classification, parameter impact and the major influ-  |    |

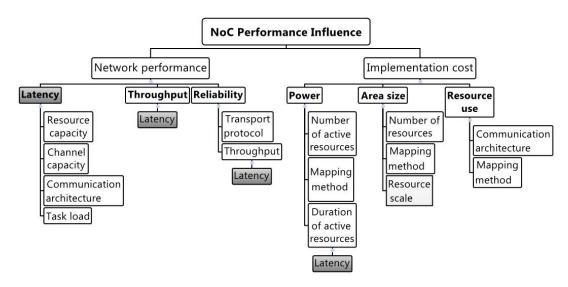

|      | ence of latency to other NoC performances                               | 45 |

| List of Figures | xiii |

|-----------------|------|

|                 |      |

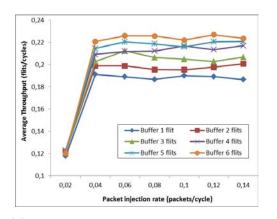

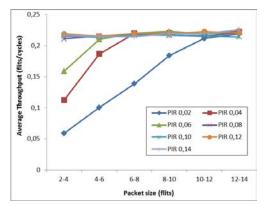

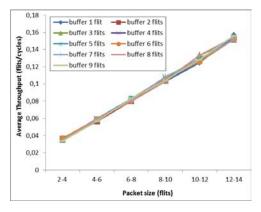

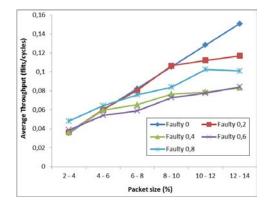

| 3.2  | Evaluation of throughput saturation                                             | 52 |

|------|---------------------------------------------------------------------------------|----|

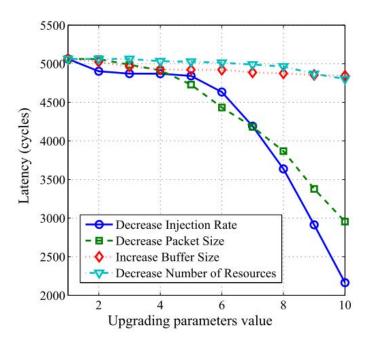

| 3.3  | The impact of upgrading value of injection rate, packet size, buffer size       |    |

|      | and number of resources on upgrading the latency                                | 56 |

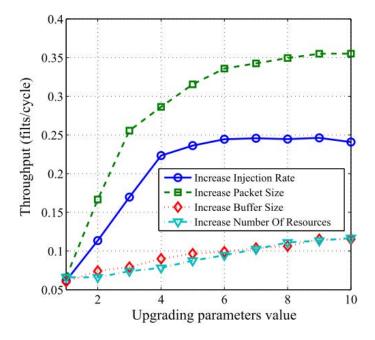

| 3.4  | The impact of upgrading value of injection rate, packet size, buffer size       |    |

|      | and number of resources on upgrading the throughput                             | 56 |

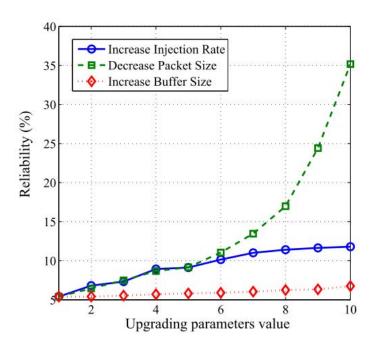

| 3.5  | The impact of upgrading value of injection rate, packet size and buffer         |    |

|      | size on upgrading the reliability                                               | 57 |

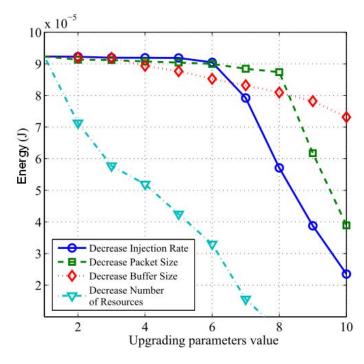

| 3.6  | Energy consumption over different values of injection rate, packet size,        |    |

|      | buffer size and number of resources                                             | 57 |

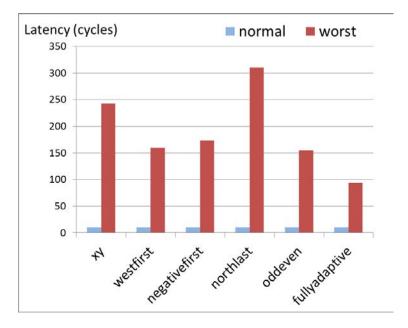

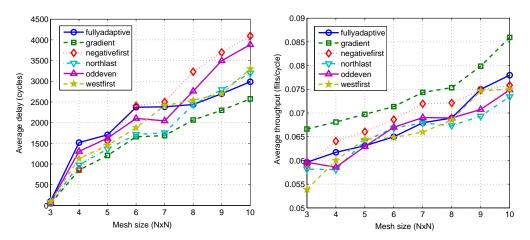

| 3.7  | The impact of the routing algorithm on latency                                  | 59 |

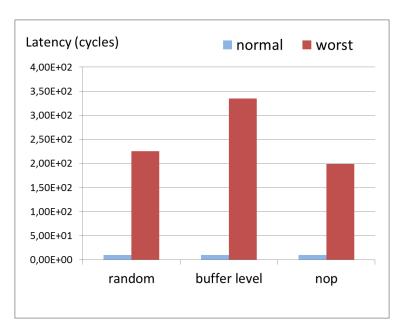

| 3.8  | Selection-path strategy impact on latency                                       | 60 |

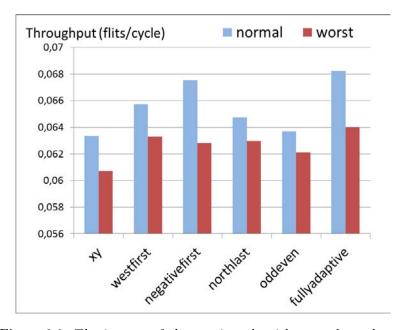

| 3.9  | The impact of the routing algorithm on throughput                               | 60 |

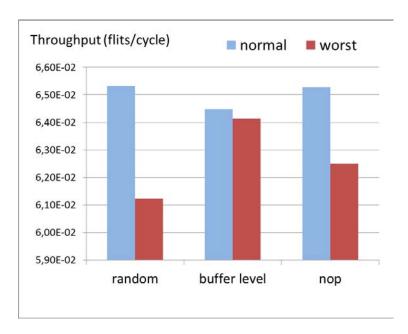

| 3.10 | Selection-path strategy impact on throughput                                    | 61 |

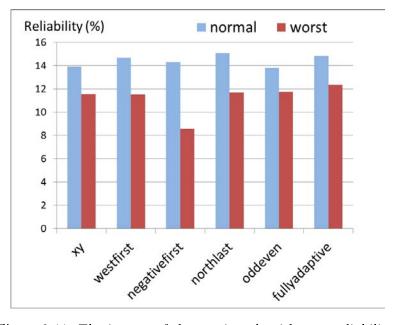

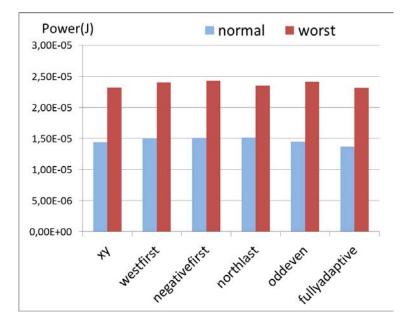

| 3.11 | The impact of the routing algorithm on reliability                              | 61 |

| 3.12 | Selection path strategy impact on reliability                                   | 62 |

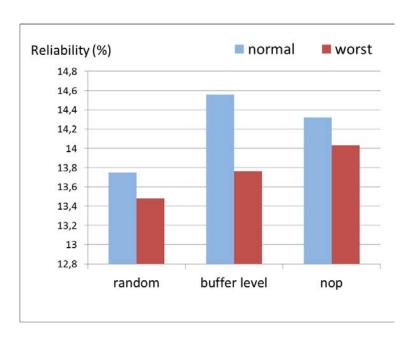

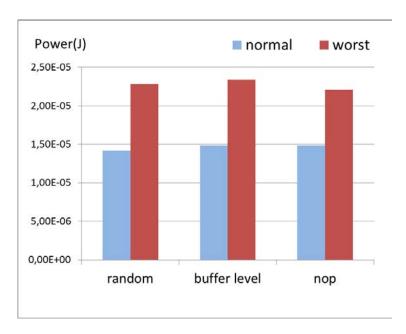

| 3.13 | The impact of the routing algorithm on power consumption                        | 62 |

| 3.14 | Selection path strategy impact on power consumption                             | 63 |

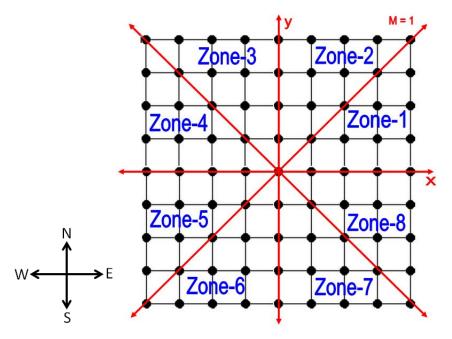

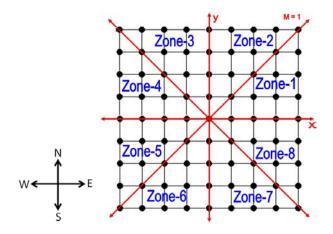

| 4.1  | Gradient concept divide 2D coordinate into eight zones based on gradient        |    |

|      | line                                                                            | 69 |

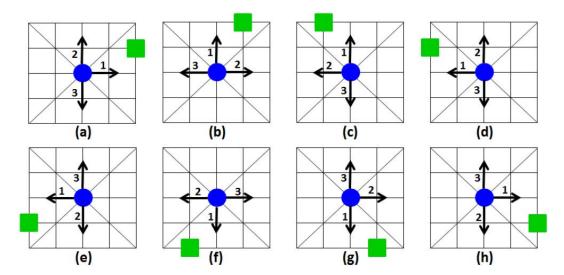

| 4.2  | Sequence decision of <i>Gradient</i> algorithm for a destination in (a) Zone-1, |    |

|      | (b) Zone-2, (c) Zone-3, (d) Zone-4, (e) Zone-5, (f) Zone-6, (g) Zone-7,         |    |

|      | (h) Zone-8                                                                      | 70 |

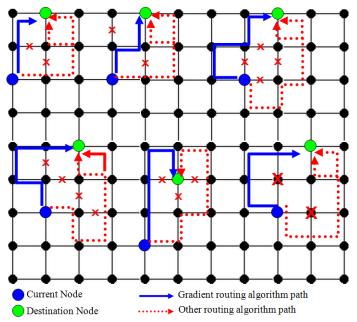

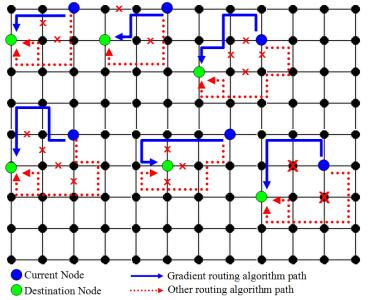

| 4.3  | Alternative path of different routing algorithms in presence of faults in       |    |

|      | the network for different relative position of the destination node             | 72 |

| 4.4  | The abstraction of <i>Gradient</i> routing algorithm                            | 73 |

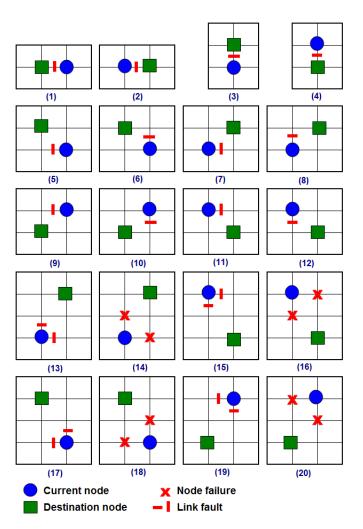

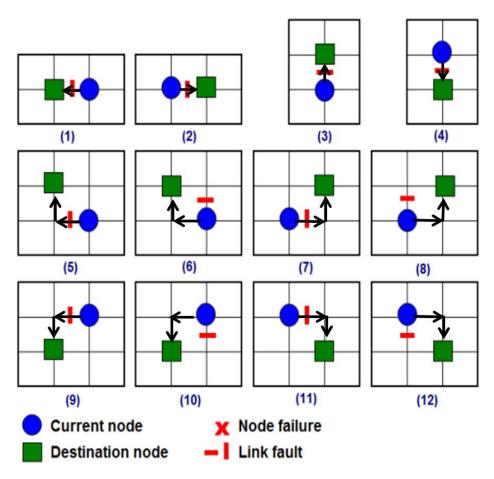

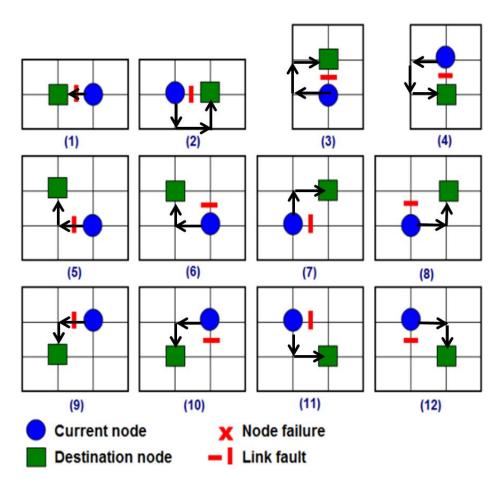

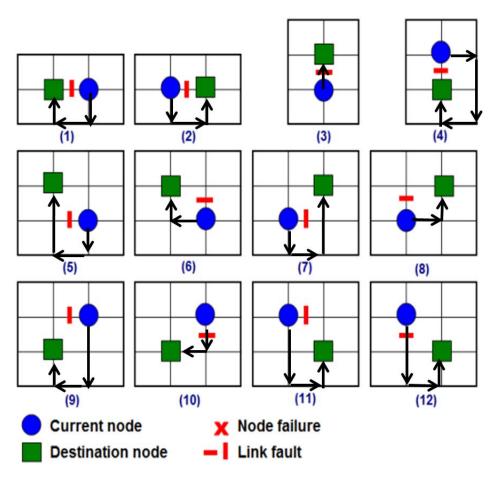

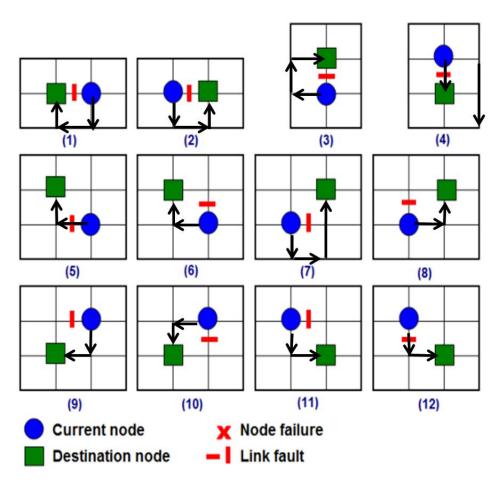

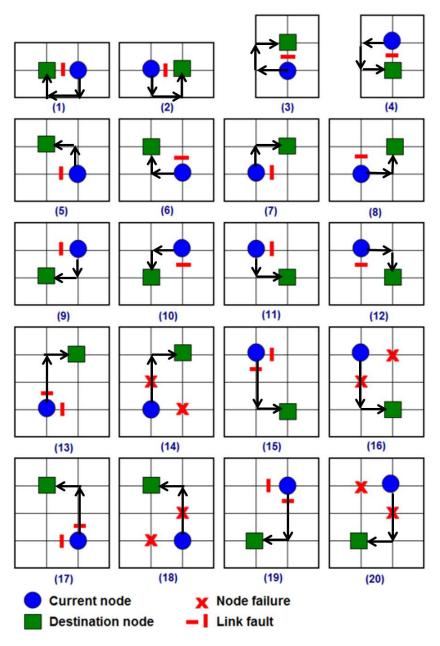

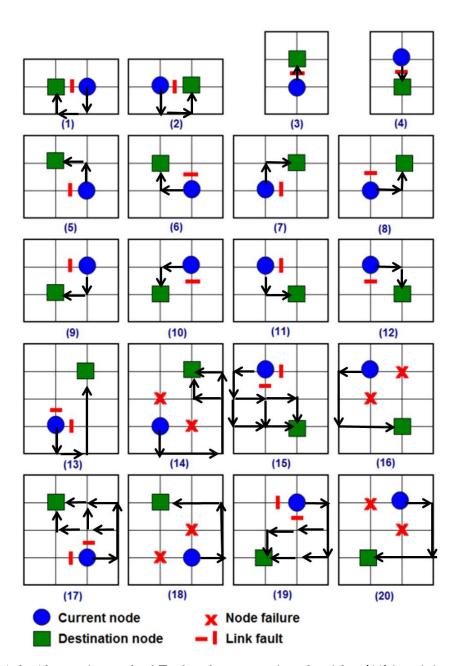

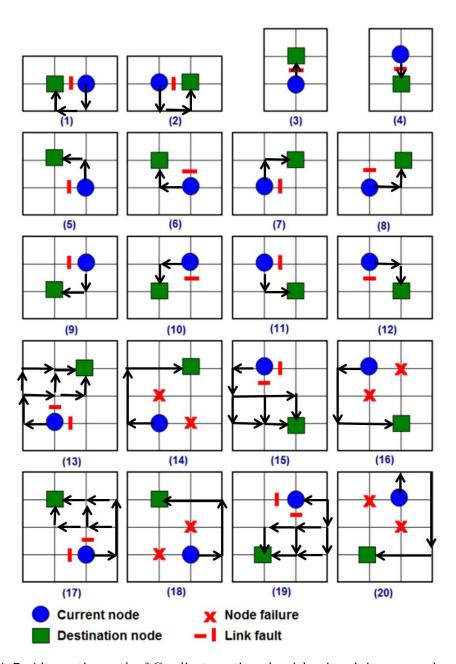

| 4.5  | Twenty conditions of link-faults and node failures to evaluate the min-         |    |

|      | imum hop and number of alternative path for seven different routing             |    |

|      | algorithms                                                                      | 76 |

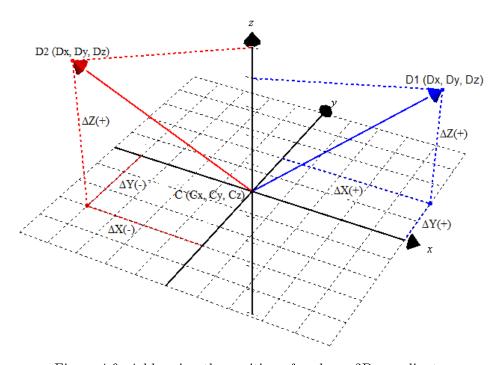

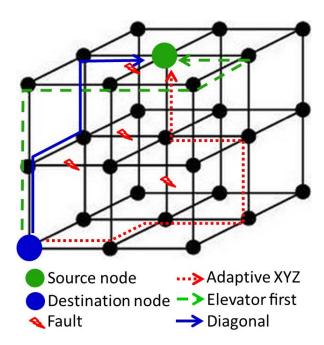

| 4.6  | Addressing the position of node on 3D coordinate                                | 83 |

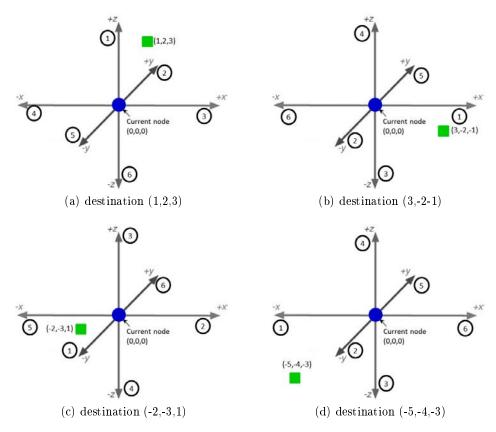

| 4.7 | Sequence decision of <i>Diagonal</i> algorithm for destination coordinate on                                    |     |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

|     | (a) [1,2,3], (b) [3,-2-1], (c) [-2,-3,1] and (d) [-5,-4,-3]                                                     | 84  |

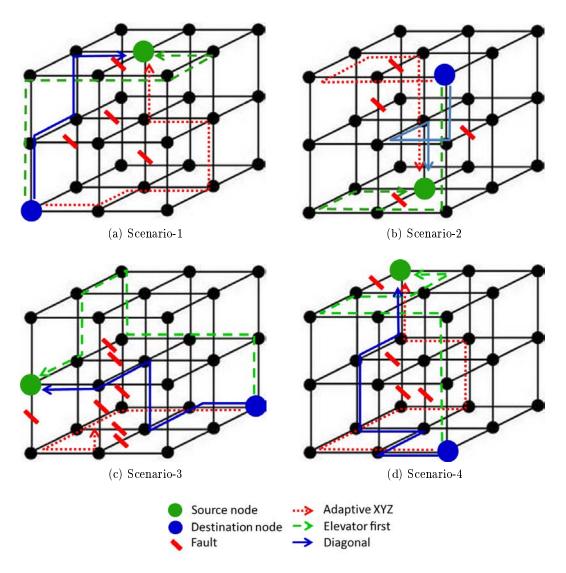

| 4.8 | Comparison between (a) Diagonal routing algorithm and (b) Adaptive<br>XYZ $$                                    |     |

|     | routing algorithm                                                                                               | 85  |

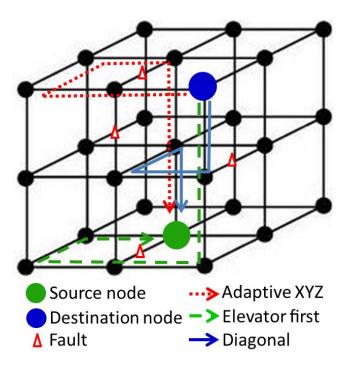

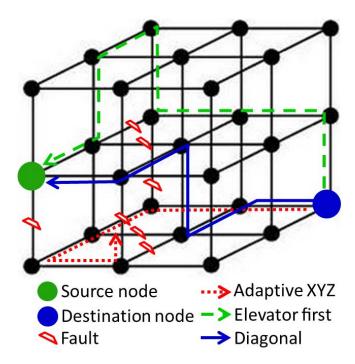

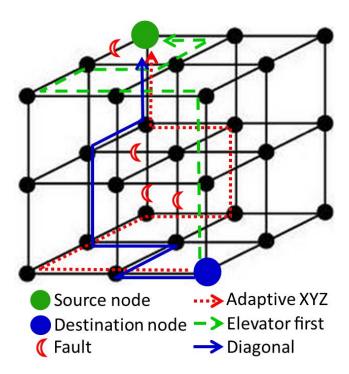

| 4.9 | Routing path comparison between Diagonal, AdaptiveXYZ and Elevator                                              |     |

|     | first [16]                                                                                                      | 87  |

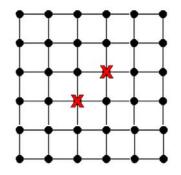

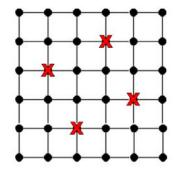

| 5.1 | Two scenarios used in simulation: (a) 6x6 mesh with 2-nodes failure in                                          |     |

|     | the center of network and (b) 6x6 mesh with 4-nodes failure on near                                             |     |

|     | border of network                                                                                               | 91  |

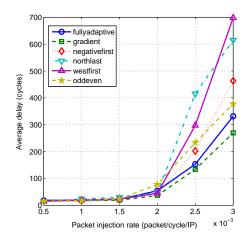

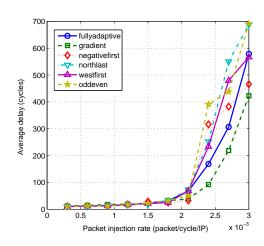

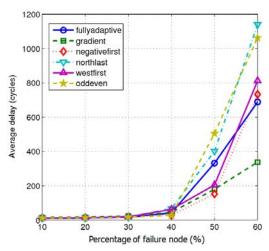

| 5.2 | Average delay comparison on increasing packet injection rate for (a) first                                      |     |

|     | scenario and (b) second scenario                                                                                | 91  |

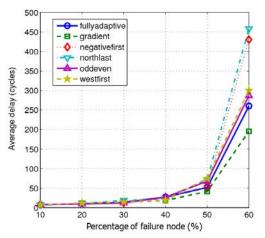

| 5.3 | Average delay comparison on increasing faulty percentage with packet                                            |     |

|     | injection rate of $0.005~\mathrm{packets/cycle/IP}$ for (a) $5\mathrm{x}5~\mathrm{mesh}$ and (b) $6\mathrm{x}6$ |     |

|     | mesh topology                                                                                                   | 92  |

| 5.4 | (a ) Average delay and (b) average throughput on increasing number of                                           |     |

|     | nodes from $3x3$ to $10x10$ with packet injection rate $0,01$ packets/cycle/IP                                  | 93  |

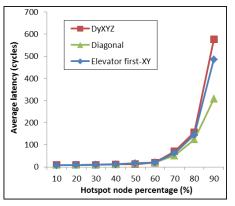

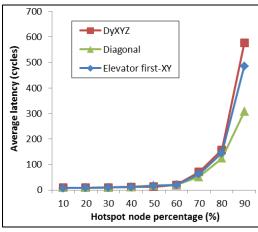

| 5.5 | Average delay comparison on (a) 4x4x4 mesh with packet injection rate                                           |     |

|     | 0,004 and (b) 4x4x4 mesh with PIR 0,0015                                                                        | 94  |

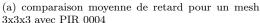

| 5.6 | Average delay comparison on increasing packet injection rate from $0,0005$                                      |     |

|     | to 0,0035 packets/cycle/IP for (a) $3x3x3$ , (b) $4x4x4$ , (c) $5x5x5$ , (d) $6x6x6$                            |     |

|     | mesh                                                                                                            | 95  |

| 5.7 | Implementing Gradient routing logic inside switch control block of HER-                                         |     |

|     | MES NoC router                                                                                                  | 96  |

| 5.8 | Average latency comparison of 2D mesh routing algorithm on increasing                                           |     |

|     | packet rate and packet size                                                                                     | 101 |

| A.1 | Decision path of XY routing algorithm in one fault condition between                                            |     |

|     | current and destination node                                                                                    | 122 |

List of Figures xv

| 2 Decision path of West-first routing algorithm in one fault condition be- |                                    |

|----------------------------------------------------------------------------|------------------------------------|

| tween current and destination node                                         | 123                                |

| Decision path of North-last routing algorithm in one fault condition be-   |                                    |

| tween current and destination node                                         | 124                                |

| Decision path of Negative-first routing algorithm in one fault condition   |                                    |

| between current and destination node                                       | 125                                |

| Decision path of Fully-adaptive routing algorithm in 20 condition between  |                                    |

| current and destination node                                               | 126                                |

| Alternative path of Fault-tolerant routing algorithm [11] in minimum       |                                    |

| number of hops                                                             | 127                                |

| Alternative path of Gradient routing algorithm in minimum number of        |                                    |

| hops                                                                       | 128                                |

| The comparison of decision path of AdaptiveXYZ, Elevator first and         |                                    |

| Diagonal routing algorithm for fault scenario-1                            | 133                                |

| The comparison of decision path of AdaptiveXYZ, Elevator first and         |                                    |

| Diagonal routing algorithm for fault scenario-2                            | 134                                |

| The comparison of decision path of AdaptiveXYZ, Elevator first and         |                                    |

| Diagonal routing algorithm for fault scenario-3                            | 135                                |

| The comparison of decision path of AdaptiveXYZ, Elevator first and         |                                    |

| Diagonal routing algorithm for fault scenario-4                            | 136                                |

|                                                                            | tween current and destination node |

## List of Tables

| 2.1  | Similarities and differences between NoCs and Computer Networks (CN)       | 15 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | Resources in Xilinx Virtex-5 (xc5vsx50t-1ff665) FPGA [77]                  | 34 |

| 3.1  | Impact of NoC parameters to performances                                   | 42 |

| 3.2  | Impact of design parameters on performance of NoC                          | 47 |

| 3.3  | Parameter values for worst network condition for different size of network | 49 |

| 3.4  | Parameters range value used in scenarios to evaluate the saturation per-   |    |

|      | formance                                                                   | 51 |

| 3.5  | Parameters range value used in scenarios to evaluate the saturation per-   |    |

|      | formance                                                                   | 51 |

| 3.6  | Simulation result of latency and starting saturation point                 | 53 |

| 3.7  | The defined and adjusted parameters used in the scenario                   | 54 |

| 3.8  | The adjusting parameters to upgrade the performance                        | 55 |

| 3.9  | The different technique of parameters to evaluate the impact on perfor-    |    |

|      | mance                                                                      | 58 |

| 3.10 | Summarize the most influence parameter to NoC performances                 | 64 |

| 4.1  | Number of hops for each algorithm in the presence of one fault in the      |    |

|      | ${\rm network}  .  .  .  .  .  .  .  .  .  $                               | 77 |

| 4.2  | Comparison of number of minimum hops for the three adaptive routing        |    |

|      | algorithms and optimal calculation by hand                                 | 79 |

| 4.3  | Combination possibilities of (a) distances and (b) directions based        | 83 |

| 4.4  | Number of minimum hops comparison of three adaptive routing algo-          |    |

|      | rithms                                                                     | 86 |

| List of Tables | xvii |

|----------------|------|

|                |      |

| 5.1 | Parameter use in simulation to evaluate Diagonal routing algorithm      | 93  |

|-----|-------------------------------------------------------------------------|-----|

| 5.2 | Router parameter                                                        | 97  |

| 5.3 | Evaluation scenarios                                                    | 98  |

| 5.4 | 4 FPGA resources needed for implementing handshake flow control without |     |

|     | virtual channel nor scheduling                                          | 98  |

| 5.5 | FPGA resources need for implementing Credit Based flow control with 1   |     |

|     | virtual channel and no scheduling                                       | 98  |

| 5.6 | FPGA resources need for implementing credit based flow control with 2   |     |

|     | virtual channel and round robin scheduling                              | 99  |

| 5.7 | FPGA resources need for implementing Credit Based flow control with 2   |     |

|     | virtual channel and priority scheduling                                 | 99  |

| 5.8 | Scenarios for simulation of network performances                        | 100 |

## Chapter 1

### Introduction

Microprocessor is the most important component in all electronic equipment. It allow to runs specific application software at the user interface level, to manage appropriately internal hardware and software interface based on its functionality. Current applications for embedded systems are modeled as a large number of communicating tasks with different characteristics [39]. Single core processor systems cannot handle anymore the requirement of this highly complex applications and the related real time constrains. Thus, communication architecture is required to support the full functionality of these applications. An embedded system will be designed with billions of transistors and heterogeneous components integrated together in a chip called Multiprocessor System on Chip (MPSoC).

The MPSoC paradigm or the embedded system adopts the architecture of the desk-top computers and bus architectures used in PCB by assembling dedicated hardware on a single chip. The current Personal Computer (PC) contains multiple processors, multicore Central Processing Unit (CPU), Digital Signal Processor (DSP), and other application specific-processors (like GPU) to support high computing power, with less power consumption for advanced applications such as multimedia or 3D games. The SoC platform has recently evolved into MPSoC. The interconnection network appeared as the critical bottleneck in MPSoC and the principal important component for high-performance MPSoC. MPSoC has replaced VLSI (very-large-scale integration) or ULSI

(ultra-large-scale integration). MPSoCs are widely used in the equipment systems such as cell phones and portable game devices.

Classically, shared buses and direct point-to-point connections are used for the communications between processing elements on a chip. Both technologies are simple and easy to manage. But, as silicon technology advances further, several problems related to buses and point-to-point links has appeared. With a high numbers of interconnected nodes, bus arbitration can become a bottleneck that can increase the delay. While direct point-to-point, each core needs a lot of pins thus becomes messier in terms of wiring. Buses and point-to-point interconnections are no more possible to support communications between resources on embedded system or System-on-Chip (SoC). To support efficiently these communications it is then required using highly parallel and flexible regular interconnection networks.

Network-on-Chips (NoCs) has been proposed as a solution for communications infrastructure in SoC. NoC architecture provides the communication infrastructure for the resources on a chip. The adaptivity of this communication paradigm provides different Quality of Services (QOS) based on applications need. Moreover, the NoCs can also provide flexible infrastructure to overcome performances degradation due to change in environment or application requirements [36].

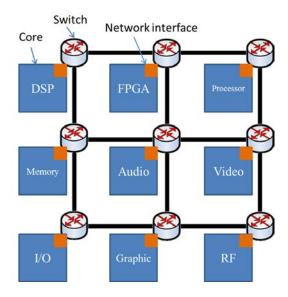

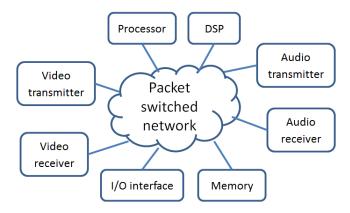

A NoC architecture consists of resources or processing elements such as processor or storage units in the network, and switches or router that are connected using channels so that they are able to communicate with each other by sending messages. A generic NoC infrastructure, as presented in Figure 1.1, is the combination of various hardware elements (e.g., processing element, switches, and links) and protocols communication (e.g., routing, switching policies) that determine the communication architecture. The processing elements can be a processor, DSP, Field Programmable Gate Array (FPGA) block or RAM while the switches are in charge to routes and buffers messages between resources.

A physical layout that describes how the switches or routers in NoC are connected to each other is defined as the topology. In SoC, the key requirement for the network

Figure 1.1: General NoC architecture which contains resources (processor, memory, DSP, etc), switch/router and network interface.

topology is scalability with low power consumption [79]. Mesh topology is the most used topology for NoC due to its relative simplicity and its high scalability [13]. In generic 2D mesh NoC topology, several tiles of routers and resources are connected in a grid-like fashion (Figure 1.1). It is known as a regular structure and short interswitch wires. From this structure, a variety of 3D topologies can be derived. The 3D topology consists of stacking 2D mesh layers connected by I/O or Through-Silicon-Vias (TSVs). It is the solution of the increasing uses of semiconductor and the scalability in embedded system based on the Moore's Law prediction. 3D architecture are designed to avoid suffer from high power dissipation and a large network diameter distance between nodes. It offer better network-on-chips performance compared to the 2D architecture [55] due to the increasing complexity of chips and limited scope of 2D topologies. In this work, we mainly consider the 2D and 3D mesh topology. We designed a fault tolerant routing algorithm for 2D and 3D mesh topologies. Some applications such as video and audio decoding have specific constraints on communication requirements. For these applications, the traffic flow between the pair producer-consumer should need some guarantees on the network performances such as latency or throughput. Latency is the

time needed to send packet from a source to a destination while throughput also known as bit-rate, defines how many bit arrive at destination per second. Traditional packet switching networks which uses packet to communicate with other nodes do not offer guarantees as all packets share the same resources. The quality of service (QoS) refers to a resource reservation mechanism where special packets do not share the resources with other packets. These special packets are called Guaranteed Service (GS) packets while the others are called Best Effort (BE) packets. In worst case scenarios, GS reserve resources to guarantee it services, while BE do not reserve any resources.

Designing a NoC is very time consuming. Different levels of QoS are required to the users based on application constraint. Minimum threshold level of throughput, delay and jitter are needed to fulfill the application requirements. To support a certain QoS for various applications in dynamic condition, an adaptive NoC is mandatory [44]. An adaptive NoC should provide a minimum level of performances to support QoS needed by different application requirements and support flexible communication or dynamic reconfiguration to react and adapt to the changes of working conditions [54]. A designer should consider the QoS requirements of different applications to design an adaptive NoC [27]. A challenge facing designers of SoCs containing NoC is to find NoC instances that balance the cost (e.g. area) and performance (e.g. latency and throughput) [57].

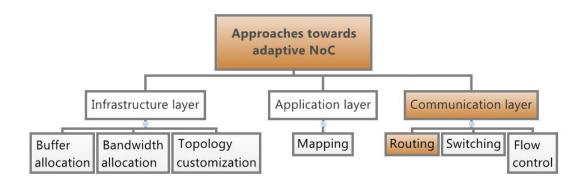

In a NoC based architecture, all nodes are connected and transfers packet through the network via routers. The performances and properties of the adaptive NoCs are dependent on the design of the infrastructure layer, application layer and communication architecture layer as shown on Figure 1.2. In this thesis, routing techniques are designed as a solution towards the dynamic adaptation of NoC. The goal of the routing algorithm is to distribute traffic evenly among the paths supplied by the network topology, so as to avoid hotspots and minimize contention, thus improving network latency and throughput.

An adaptive routing algorithm is proposed for deadlock avoidance and load balancing. The main objective is to reduce the overall latency of communications inside the network. Furthermore they can be used to avoid failures that cause deadlocked packet.

Figure 1.2: Proposed novel routing technique as an approaches towards adaptive NoC

Adaptive fault-tolerant routing [44] is the only solution to reduce the chance of packet entering hot-spots or faulty nodes so that probability of blocking for packets is reduced.

A NoC can be designed in three levels: high level abstraction, medium level and hardware level. A NoC designer can use high-level design to design larger, more complex system and higher performance embedded system using system-level design tools with less effort. The advantages of this method are that it requires less-time to obtain the output performances of the design based on application requirement. Further, NoC designer can also prototype or manufacture their design using high-level synthesis or medium level synthesis. But accuracy of result cannot be guarantee.

Most of existing fault-tolerant routing methods employ virtual channel (VC) in routers to guarantee deadlock-freeness [9]. VCs are known as logical channel which differs from physical wires. It associates multiple queues at each input port in the router so that when a packet is blocked at one port, the other packet can use VC to choose another port. Thus VCs can increase the utilization of physical channel and also the throughput on the network. However, implementation of VCs requires large capacity memory or buffers, which in turn increases area overhead and power consumption, thus making it impractical. Hence, adaptive fault-tolerant routing without VC is desirable for NoCs [74].

A SoC that is composed by several core processors can be built in a single FPGA. FPGA has been chosen by NoC designer to prototypes their design due to the fast and

low cost implementation. In our research, we considered the Xilinx Virtex-5 FPGA to implement our proposed fault-tolerant routing algorithm.

#### 1.1 Problem statement (open challenges)

#### 1.1.1 Impact of design parameters on performances

The introduction of the Quality of Service into a Network-on-Chip requires some kind of end-to-end path reservation in order to guarantee the latency and the throughput of offered packets. The questions addressed for this topic are packet latency, throughput, shared resources and path allocation. The interconnections in NoC have plenty of parameters that affect the performances and the capacity of the interconnection. These parameters can be, for example, the number of data lines, clock frequency, arbitration scheme, the priorities of the blocks, or the maximum time a packet can reserve a shared resource [60]. Almost all NoC parameters such as topology, processing element (PE) number, application type, traffic type, routing algorithm, switching algorithm, packet size, buffer size, flit size and number of virtual channel have influence on throughput, latency and power consumption. For this purpose, a NoC designer should fine several parameters (and their values) impacting the network performances. This way, the adaptation of the network has to fulfill performance requirements.

#### 1.1.2 Fault-tolerant routing algorithm

The use of deep sub-micron technology in an embedded system increase susceptibility to Single Event Upsets (SEU) that can decrease the reliability of NoC. A SEU occurs when a radiation causes a bit-flip in some latches (1 to 0 or vice versa). This undesired modification may cause the dysfunction of the architecture. Another problem that leads to permanent faults in the circuit is the "aging" of circuits. Aging of circuits is caused by physical effect in deep-submicron process and cause permanent errors.

The most important adapted strategies criteria requirement for future circuits is the dependability. The dependability has an impact on computation parts of the embedded

system architecture. If a processor fails, it cannot be used anymore and a different task placement has to be computed. In the same way if the error occurs in the NoC, a rerouting of message in the NoC can be enhanced by adding fault tolerance capabilities, thus they can adapt communication flows to follow fault-free paths.

The important requirements of routing are to avoid deadlock and live-lock. A dead-lock occurs when a flit (an elementary portion of a packet) or a packet waits for a resource that will never be released. The routing can create deadlock if bad decisions are taken. The routing-time of packets is one of the key factors critical to the performance of NoCs. Thus, NoC routing schemes should be enhanced by adding fault tolerance capabilities so that they can adapt the dynamically and flexible communication flows to avoid the performance degradation. This leads us to define a communication infrastructure able to handle faults and manage errors in its resources.

In 2D mesh topology, the classical routing algorithms divide the destination node into several zones, and hence route the packets using one routing criterion. While in 3D mesh NoC, classical routing algorithms divide 3D mesh topology into horizontal and vertical layer which some of them reuse existing 2D mesh routing algorithm for horizontal destination. The algorithms are then not able to handle failures in network if a fault occurs in a router or on a link. It also cannot adapt the route to avoid the use of this resource. Other weaknesses are on how it chooses the sequence of alternative routes when the main routing path fails. Inappropriate selection of alternative path may increase the number of hops of packet to reach its destination, thus degrading the performance of NoC.

#### 1.2 Objectives and contributions

#### 1.2.1 Objectives

The main goals of designing a NoC are to get high throughput, low latency, minimum number of resources, minimum power consumption and small area size. In this thesis we first propose an evaluation of the impact of NoC design parameters on its performance.

It shows that the accuracy of choosing and adjusting the network parameters can avoid performance degradation. The results can be considered as a basis for the control mechanism in an adaptive NoC to avoid the degradation of QoS. For these purposes, first we evaluated the impact of NoC design parameters on the performances of an adaptive NoCs. The objective of this step is to evaluate how big is the impact of upgrading a value of a given parameter on performances. In a second phase we evaluated the impact of different type of parameters on the performances. For this purpose, we identified the most important parameters influencing the performances of the network. We then adjust network parameters under different conditions and hence evaluate their impact on the performance variations. One of the challenges of the study lies in the accuracy in choosing and adjusting the NoC design parameters that can upgrade the performances in minimum QoS condition. The results on latency, throughput and reliability were evaluated using the Noxim simulator and show the impact of the parameters on studied performances.

We designed a novel adaptive fault-tolerant routing algorithm for 2D mesh called *Gradient* and for 3D mesh called *Diagonal*. Both algorithms consider sequences of alternative paths for packets when the main routing path fails. The proposed algorithm can avoid more faults and tolerates multiple failures in worst condition traffic in NoCs. It has minimum hops, lower latency and higher throughput in worst network conditions when compared to conventional routing algorithms. To evaluate the performance of these networks, scenarios with various link-faults and node failures schemes were created and simulated using Noxim simulator. Hence the number of hops from source to destination nodes, the number of alternative paths, latency and throughput in faulty network are determined and compared with other adaptive routing algorithms. Further, we implemented *Gradient* into RTL level then simulate the performances using Modelsim and evaluated the hardware cost thanks to Xilinx ISE tool.

#### 1.3 Organization of the manuscript

This thesis is organized in six chapters. Chapter 2 provides an overview of the evolution of the NoC, the NoC architecture, the impact of parameters to performances, fault tolerant routing algorithm and NoC simulator. State of the art on communication such as bus and direct point-to-point are explained in the NoC evolution. Main topologies, switching technique, flow control technique, scheduling technique and routing technique of NoC are also presented. The problem of non-fault tolerant routing algorithm fault-tolerant routing concept and NoC simulators that are used to evaluate NoC design are also introduced.

In chapter 3, the impact of NoC design parameters on the performances of NoC are defined and evaluated. The detail of NoC performances, parameters, and their dependencies are explained. The methodology on how to evaluate the impact of each parameter on each performance is presented. The last section provides the experimental results including evaluation of network saturation condition and the impact of parameters on the NoC performances.

Chapter 4 presents the proposed Gradient and Diagonal fault-tolerant routing algorithms for respectively 2D mesh and 3D mesh topologies. Scenarios with various linkfaults and node failures schemes are defined to evaluate the number of hops required to reach a destination nodes and the number of alternative paths. In the presence of faults, the comparison with state of the art algorithm results of minimum hops and alternative path are presented.

Chapter 5 presents the experimental results and implementation of proposed fault-tolerant routing algorithm. The comparison of network performance between proposed algorithms with other routing algorithm is also presented. In the last section, the synthesis result of Gradient implementation on FPGA and the evaluation of frequency on the performance are presented. Finally, the last chapter concludes this work and proposes the perspectives.

## Chapter 2

## State of the art - Definitions

This chapter gives an overview of adaptive NoC architectures and their evolutions. The comparisons between bus interconnection, general network and NoC interconnection are presented. The architectures of NoC such as resources, interconnection, topology and protocol communication are explained. The 3-D NoC technology is also presented. Then, the characteristics of NoC parameters and the performances of NoC are defined. Finally, an existing related work of adaptive fault and NoC simulators are presented.

#### 2.1 From Bus to NoC

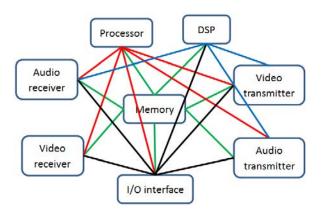

Nowadays, most electronic equipment use system or application that is embedded in a chip. Multi-core in embedded systems has become the basis blocks of computer systems [56]. Direct point-to-point interconnections shown in Figure 2.1 were the first communication infrastructure designed for on-chip systems to communicate between cores. The connection is direct and use dedicated wires without any needs of centralized arbitration. The arbitration decides when incoming data can be served by the router.

In terms of bandwidth availability, latency, and power usage, dedicated point-topoint links are optimal as they are designed especially for this purpose. Also, they are simple to design, verify and easy to model. In small systems of low number of cores, this communication structure is viable. But, as the systems grow and the design

Figure 2.1: Direct point to point connection infrastructure for SoC [7]

cycle time requirements decrease, the number of cores and the number of links will increases exponentially. In large number of cores, it requires a lot of pins for each core, large routing time and area, and becomes very messy in terms of wiring. In terms of performances, the delays and quality of signals become unpredictable, low utilization of routing resources and very low possibility of reuse are experienced in this communication paradigm.

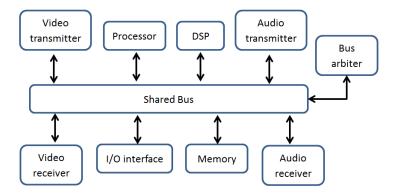

Classically, buses are used for the communication between processing elements on a chip. In a SoC, buses are advantageous because they provide high performance interconnections while they can still be shared by several communication blocks as shown in Figure 2.2. In most SoC applications, a shared bus interconnection is adopted to communicate between each integrated processing unit due to the low-cost and simple control characteristics. But, as the number of units into the system increase, the communication overhead between cores grows and hence quickly become a communication bottleneck. The increasing number of cores in Multi-Processor Systems-On-Chip (MP-SoCs) causes the unfeasible intercommunication between cores using single shared bus or a hierarchy of buses. This is because their poor scalability with system size and their shared bandwidth between all attached cores [5].

Data communication in a general networks have replaced buses in small systems: as the PCI-Express, a network-on-a board, replacing the PCI board-level bus [56]. In data communications, networks can be classified into packet switching and circuit switching From Bus to NoC 13

Figure 2.2: Shared bus interconnection infrastructure for SoC

networks. The packet switching uses packets to be transferred with the destination while the circuit switching defines circuits. Circuit switching use dedicated end-to-end circuit to communicate the data.

In the computer network world, different strategy is used. In packet switching network, the packets contain a header packet and payload of packets. Header packet contains routing information needed to route the packet over the network while on the circuit-switching network, an end-to-end circuit (i.e. a physical path) has to be established before any communication can happen. Thus, the routing method is not needed and this is suitable for streaming and guaranteed service traffic. While packet switching send the packets through undedicated path. Thus, it needs routing method to route the packet to destination.

Packet switching is suitable for Best Effort (BE), a traffic on which there is no guarantee on the performances. The disadvantage of using dedicated end-to-end circuit is that it need an allocator to establish the circuit while in undedicated circuit, the resources can be released automatically. In terms of performance, header packet in packet switching is an overhead while circuit switching have guaranteed throughput and predicted latency. The performances of packet switching are depended on the network condition.

Packet-switched on-chip networks (NoC) as shown on Figure 2.3 were replacing buses and crossbars [37] as communication in many-core chips. This architecture is adopting

Figure 2.3: Packet switched network communication infrastructure

the computer network architecture for communicating by sending and receiving packets between nodes or processing element. NoC also uses switches and routers to forward packet from sender to destination. The routing decisions are distributed if the network protocol is made non-central and the same router may be re-used for all network size. All network wires can be pipelined that's why the local performance will not degrade when scaling the network size. The similarities and the differences between NoCs and general computer network are shown in Table 2.1.

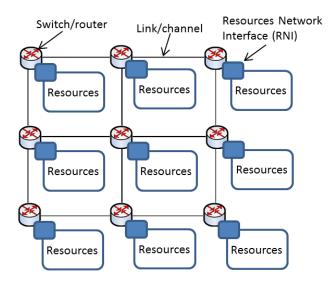

### 2.2 Network-on-Chips architecture

The idea of NoC infrastructure is to separate the communication concerns and the application with the physical layout. Thus the architecture can be scalable and configurable as a network. With this communication infrastructure, a hardware resource can be connected to any other resources as an element in the network. General NOC architecture consists of network elements and resources as presented in Figure 2.4. The network elements consist of switches, channels and Resource-Network-Interfaces (RNI) while the resources are processor, core or embedded systems that are integrated into the network. The network elements provide communication services to the whole set of embedded systems. The resources are connected to switch via RNI, while the switches connect to other switches in network using channels. A channel is a two one-directional

Table 2.1: Similarities and differences between NoCs and Computer Networks (CN)

| Similarities                                                                        | differences                                                                 |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Consist of network element (router/switch, link, PE)                                | NoC designed toward application<br>domain while CN for general<br>purpose   |

| Use packet switching                                                                | NoC topology is fixed by design<br>while CN support plug and play<br>router |

| Flit/packet use header flit that content protocol information such as routing, etc. | Energy is important constraint in NoC thus low power techniques is needed.  |

| Implement communication protocol such as routing, arbitration and flow control.     | NoC can't support heavy communication protocol                              |

point-to-point interconnects.

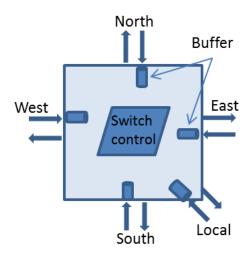

As mentioned, a NoC support hundred or even thousands of resources. The main problem of designing NoC is how to connect them so they can communicate with maximum performances. The physical layout and connections between nodes and channels in the network can be referred as a topology. While communication architecture determine how they communicate each other. The most important element of network is the switch (or router). It routes the data from a sender node to a destination node. A switch contains three major parts: arbitration or scheduling, routing and control flow techniques.

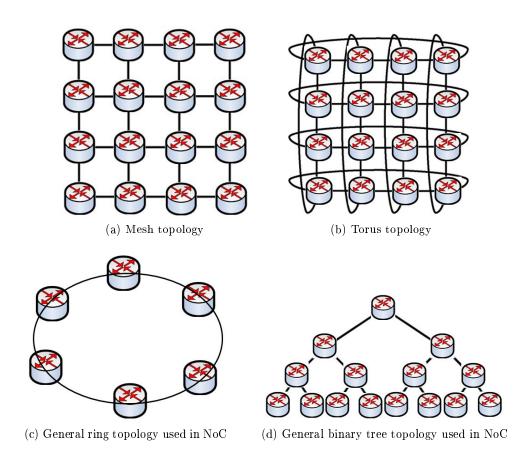

#### 2.2.1 Topologies

The most important parameter of a NoC is the network topology. It gives significant effects on NoC performances due to the fact that it determines the distances between connected node. The two most common topologies for NoCs are mesh and torus as presented in Figure 2.5-a and 2.5-b. These both topologies can be described as k-ary n-cubes, where k is the number of nodes along each dimension while n is the number of dimensions [8]. For 2-D mesh, the value of n is 2 while for 3-D the value of n is 3. For

Figure 2.4: General NoC communication architecture

example, a 4-ary 2-cube is equal to a  $4\times4$  mesh or torus with 16 nodes while a 4-ary 3-cubes is equal to  $4\times4$  mesh or torus with 64 nodes. In torus topology, nodes along the edge of the network are connected thus these nodes have the same port number than the nodes in the center of the network. A torus is also edge-symmetric [68], this property helps the torus network to balance traffic across channels.

Figure 2.6 present general 2-D meshes router architecture. It has four bidirectional ports (i.e. east, west, north and south) to connect with neighbour routers and a local one to connect to its PE. Each input port has a buffer as temporary storage of data before it is served by the router.

In this thesis we consider mainly 2-D mesh topology due to the wide usage of this topology that has been implemented in the SoC domain. Further, this topology has been used by most researchers to design novel routing algorithm in NoC.

In Ring topology (Figure 2.5-c), all the nodes are connected to each-other in a closed loop. Each node is connected to two other nodes on either side, and can communicate with these two adjacent neighbors. The traffic flows in one direction use a token. This topology does not need central point or server to control the connectivity between nodes. Each node has equal access to resources. The main drawback of this topology is that when one node is faulty, the entire network is affected.

Figure 2.5: Regular topologies used in NoC: (a) 2-D mesh, (b) torus, (c) ring and (d) binary tree

Figure 2.6: General 2-D mesh router architecture

Figure 2.7: The example of (a) irregular and (b) mixed topology used in NoC

The tree topology shown in Figure 2.5-d are composed of routers (or switches) forming several hierarchical levels. The source PEs is located at the left side of the NoC while destinations (PEs' inputs) are at the right side. Thus, this topology is classified as unidirectional topology.

Irregular topologies presented in Figure 2.7 are usually designed based on clustering techniques. It's derived from altering the connectivity of a regular topology structure such as removing certain links from a mesh or mixing different topologies [8]. In irregular topology, user may specify different router architectures (i.e. number of input and output port, buffer size, routing, etc.) with other router in network. The goals are to reduce the number of ports, switches or channels that can reduce significantly power and area. With irregular topology, some blocks in network can direct be connected without need of switch, or some router need only two input/output ports instead of complete input/output ports.

#### 2.2.2 Switching

The main component of the interconnection architecture in NoC is the switch. Inside a switch, a data is transferred from an input port to any of its output ports. The data may need to be buffered before going out through the output port. The switch control may consist of arbitration, flow control and routing algorithm that govern where and when the data are forwarded. The arbitration decides when incoming data are served by the

Figure 2.8: General switching process

router, while the flow control decides when the data are sent to the next hop (router). The routing algorithm decides the route on which the data has to be forwarded via a crossbar. The diagram block of general router architecture is presented in Figure 2.8. The time gap between data enters the input port and the time when the data leaves the switch through an output port is called switch-delay [23].

Store-and-Forward (SAF) technique is the first switching technique proposed in NoC. SAF switching techniques convert every packet into flits. The first flit of a packet is the header flit and the last flit is the tail. SAF technique forward the header flits to the next switch if only all body flits of a packet are received. Compared to other switching technique, the SAF switching is not suitable with the requirement of NoCs because it have large latency because all body flits of packet have to be received before forwarding it to the next switch. Moreover, it requires large buffer sizes to accommodate all the flits resulting in a large area needed [23]. The advantage of this technique is no deadlock can occurs.

Wormhole switching technique is similar to SAF switching technique. Both implement packet-based operation with simple control mechanism between routers. In wormhole switching technique, the header flits of packet is forwarded to the next switch before the next flit of packet arrives. Thus, the channel buffer at every router can be as small as a single flit. Moreover, wormhole switching have better latency than SAF because the header flit is processed without waiting the arrival of the next flits or entire packet [23]. The movement of wormhole switching technique looks like a worm. The tail flit follow the same routing path as the header flit. The main drawback of wormhole

switching is the performance degradation due to a chain of packet blocks [23] and risks of deadlocks.

# 2.2.3 Flow control

Flow control is a technique used in network to control the transmission of data to avoid congestion in a busy network. It is designed to avoid the over usage of the queue that causes congestion and collisions in the network. In NoC, flow control governs the allocation of buffers and links in every router. It determines when buffers and links are assigned to messages, the granularity at which they are allocated, and how these resources are shared among the messages using the network [56]. The implementation of complex flow control protocol in NoC router requires complex wiring that increases router micro-architecture area and power consumption.

The main flow control techniques used are handshaking and credit based. Handshaking control flow is used to avoid the overload of the receiver buffer. It governs the process before the communication between two nodes. The sender start sending the packet only if it receive the acknowledge messages from the destination. The acknowledge messages from destination node can be ready or not-ready to receive the packet.

Credit based communication is the extension of the handshake. It transmits data after receiving return signal from neighbor node that has sufficient free space to store the data. Credit based control how use the concept of buffer management [38]. The flits are transmitted when the buffer space in destination router sufficient. The flits in current input-buffer of router become arbitration for the output-port of neighbour and routers. The current buffers decrement the credit count when flit departs from the current router.

# 2.2.4 Routing

In term of networks, routing has been classified in several ways: as source routing or distributed routing, and as deterministic, oblivious or adaptive routing. In source routing, the source node decides the path on which the sending packet will be propagated, while in distributed routing the current node in the networks decides the next hop of the packet. With these schemes, a distributed routing can adapt the route based on network condition while source routing cannot. Routing algorithms are also classified as deterministic, oblivious or adaptive. In a deterministic routing algorithm, all packets take the same path from a source node to the destination [23]. In oblivious routing, the decision of the routing path are fixed or not considering the state of the network condition while in adaptive routing the packets are routed depending on local decisions that considering the state of the network. The main goal of adaptive routing is to avoid congested areas.

Most of routing algorithms in NoC are based on the wormhole switching technique due to its simplicity and its deadlock-free [70]. In this technique, the tail flits follow the same path as header flit. XY routing algorithm [25] is one of the example of a deterministic routing algorithm. It is the most widely used routing strategy for 2-D mesh due to its deterministic, simple, easy and deadlock-free algorithm. In this algorithm a packet first traverses along the X dimension and then along the Y dimension to the destination. XY algorithm is deadlock-free in normal condition but does not support adaptivity. This algorithm is then not able to handle failures in the network. If a fault occurs in a router or on a link, the XY algorithm cannot adapt the route to avoid the use of this resource.

The deterministic routing may cause potential hot-spots if particular router receives more requests than it can serve at a time [56]. Thus it resulting large delay in communication. The solution for this deterministic routing problem is by using Virtual Channel, but this solution comes with a huge hardware overhead.

The main influences factors of routing performances are number of path hop and path distribution. Based on the hops views, routing algorithms can be classified into minimal and non-minimal routing [56]. A minimal routing algorithm use minimal paths pair from source to destination while non-minimal can take both minimal and non-minimal paths. The adaptive routing allows alternative paths between the same pair of

Figure 2.9: The forbidden turns (dashed line) in turn model routing algorithm: (a) West first, (b) North last and (c) Negative first [52]

source and destination nodes. This property provides fault tolerance, because it usually enables the routing algorithm to select a path that avoids faulty network components.

The turn model [25] routing algorithm is an example of adaptive routing. It travel data using a deterministic algorithm, but when the router or the channel fail or is already used for a communication, then the data turn on another direction. Thus, the data reach the destination through an alternative path. The weakness of this algorithm happens when the only path to reach the destination is on the forbidden turn as shown in Figure 2.9. The Odd-Even turn model [12] is designed as a solution of the weakness on previous turn model. This algorithm improves the network performance due to the forbidden turn are more evenly distributed in the network. However, this algorithm doesn't have alternative selection path which is not suitable in faulty network.

# 2.3 3-D NoC Technologies

Performances, power consumption and the size of chip area are the main consideration in designing a NoC. Existing NoC topologies employ routers with a small number of ports (low-radix) to avoid the increasing power and latency [79]. But, with the need of high NoC performances on current application, it pushes the use of more processing

element inside same system that can increase the interconnection requirements between PE. As the network scale, topologies with high-radix (scalable) routers become more feasible than low-radix topologies in terms of both power dissipation and latency caused by large average minimum distance between PE [79].

The conventional 2-D integrated circuit (IC) has limited floor-planning choices, and consequently, it limits the performance enhancements arising out of interconnection architectures [55]. Fat-tree topology has been used to support increasing number of PE and avoid large distances between nodes. But, with a the large number of PE, fat-tree need routers with high number of ports and consequently more wires increasing latency of forwarding packet [49]. A 3-D topology with wafer-to-wafer bonding that consist of multiple stacked connected by Through Silicon Via (TSV) is proposed in [67].

Most of new design topologies interconnection uses vertical integration to face the 3D challenge. This concept is similar with vertical-building like hotel or apartment which is a number of rooms closely connected by using elevator or stairs. This is the idea of 3-D topology to make the distance between nodes closer compared to 2-D topology as illustrated in Figure 2.10. It shows that to the connection between node-D and node-M in 2-D topology is farther (Figure 2.10-a) than 3-D topology (Figure 2.10-b). Using TSV for vertical chip interconnection, leads to shortest distance between two layers, and the bulk capacitance of a wire is also smaller [67].

The main objectives of 3-D NoC technology are scalability and power dissipation. Three-dimensional ICs is capable of achieving better performances, functionalities, and packaging density. The 3-D architecture also offer better interconnection performances compared to the 2-D architecture [55].

The 3-D mesh NoC can be also fully connected (i.e. all routers have access to the upper and lower layers) as presented in Figure 2.10-c. Similar to 2-D router architecture, 3-D mesh router architecture is presented in Figure 2.11, it employs seven port: six bidirectional port connect to neighbor router (above, below, west, east, north, south) and one port to the local PE. The objective of the design of multilayer or 3-D architecture is to enhance the performance, energy efficiency, and thermal behavior of the

Figure 2.10: The concept of 3-D topology to make the distance between node closer than in 2-D topology

Figure 2.11: 3-D mesh router architecture

interconnection.

The author in [79] proposed architecture of 3-D NOC then compare the power consumption with other topologies such as fat-tree, flattened butterfly, mesh and Clos. Some 3-D architectures such as Stacked mesh, Ciliated 3-D mesh and 3-D BFT which use a bus spanning as vertical connection of 2-D mesh structure has been proposed by Feero and Pande in [20]. Other 3-D architecture which consists of multiple network layers connected via crossbar switches called XNoTs is proposed in [46].

The most widely used static routing algorithm for 3-D mesh is XYZ. It is a deterministic, simple, easy and deadlock-free algorithm. As its counterpart in 2D, packet first traverses along the X dimension, then Y dimension, and finally along the Z dimension. XYZ algorithm is deadlock-free in normal condition but does not provide adaptivity in faults condition thus it cannot handle failures in the network. If a fault occurs in a router or on a link, the XYZ algorithm cannot adapt the route to avoid the use of this resource.

# 2.4 Performances, parameters and dependencies

The main goals of NoC design are to get high throughput, low latency, minimum resources requirement, minimum power consumption and small area size. But, the most important consideration on designing a SoC is the trade-off between network perfor-

mances, energy consumption, and silicon area requirements after mapping. Generally, the system performance consists of two parts: computation and communication performance. In NoC, the quality can be measured from its energy consumption, area size and network performance.

Several fixed design NoC architectures such as topology, routing and switching schemes has been proposed to get high performances in certain application, however it may reduce performances in other applications. Thus, NoC designer must consider the impact of each parameter on the result performances.

NoC parameters consist of hardware architecture (i.e router micro-architecture, link architecture and topology), and communication architecture (i.e application, security, traffic, transport protocol, packet size, header size, routing, flow control, switching, flit size, and buffer size). While NoC performances can be classified into latency, throughput and reliability.

Latency is defined as the time spent to transfer one packet from a source node to a destination node [31]. In term of NoC, latency is defined as the time elapsed between the moment the PE source sends the first bit of a data and the moment the PE destination receives the last bit of data. Throughput sometimes known as data rate, represents how many bits arrives at destination node per second. In network, it corresponds to the rate at which packets are delivered by the network and presented in percentage from total network capacity.

Reliability is the reliable communication which provide notifications to the sender of the the delivery of transmitted data [31]. In terms of OSI model, reliability depends on the transport protocol layer. Transport protocol ascertains whether the packet arrived at the destination correctly. Complex transport protocol increases the latency of packet. Error control and flow control is a part of control mechanism in transport protocol. Error control and error detection combined with retransmission further can increases the NoC congestion.

In chapter 3, we propose a method to evaluate the impact of design parameters on the performances of NoC. The result of this work will help NoC system designers in estimating the system performance, associated overheads and defining the best parameters to adapt its system condition.

# 2.5 Fault-tolerant and deadlock-free techniques

An error in the networks can be caused by the faulty in the circuit. There are two type of faulty circuit: permanent faults and temporary fault. Permanent faults can be caused by dielectric breakdown, poor fabrications and irreversible wear-out damage [72] while temporary fault are caused by the operating conditions process such as voltage and temperature fluctuations.

If an error caused by temporary fault, the operation needs to be retried or corrected [63]. But if an error is caused by permanent fault, it needs some form of redundancy in time, space, or information due to retrying an operation will not solve the problem [53]. In that case, sufficient redundancy or spare units are required to continue error-free operation.

The failed element must be remove from the communication system or the faulty chip region must be shuttled down if the permanent fault are caused by poor fabrication yield or lifetime failure [72]. Other solution is by re-routing the packet avoiding faulty area, thus fault-tolerant design is needed. Fault tolerance is the ability of a system to continue operating in the presence of unexpected faults. This property of NoC not only affect fault-tolerance routing strategy, but as simple flow control strategy called Dimensional Bubble Flow Control (DBFC) in [73] has been proposed to avoid fault in network by routing the packet based on its buffer state.

# 2.5.1 Problems of non-fault tolerant routing

A major problem on oblivious routing typically arises when the network starts to block traffic. The only solution is then to wait for a reduction of the traffic amount and to try again. Deadlock, livelock and starvation are potential problems on both oblivious and adaptive routing.

Deadlock occurs in a network when a group of packets are unable to progress because they are waiting on another one to release resources (buffer, link, etc.). If a sequence of packets forms a cycle in the network [14], then the network is deadlocked. In network communication, a deadlock is dangerous because when few resources are occupied by deadlocked packets, other packets will block on these resources thus completely paralyzing the network. Moreover the network would remain in this state until an external intervention occurs. For example, in minimal adaptive routing algorithm that always routes packets along the shortest path. The algorithm is effective when more than one minimal or as short as possible route between sender and receiver exist. The main drawback is when the minimal path is faulty, the packet is blocked due to in fact that it route only on minimal path (i.e. entering a faulty region).

Closely related network pathology is livelock. In livelocks, packets continue on moving inside the network but without making progress toward their destinations. This becomes a concern for example when packets are allowed to take non minimal paths through the network. Livelock occurs when a packet keeps spinning around its destination without ever reaching it. This problem exists in non-minimal routing algorithms. Livelock should be cut out to guarantee packet's throughput. There are a couple of resorts to avoid the livelock.

Other problems of non-fault tolerant routing are contention and starvation. Contentions are defined as delays imposed to a packet in order to wait for a resource to be available. Contentions are not problematic like deadlocks and livelocks because the network recovers from contention without any external intervention. It recovers as soon as previous communication finishes or as soon as another path is found. Starvation can be avoided using a fair routing algorithm or reserving some bandwidth for low-priority packets.

### 2.5.2 Fault tolerant and deadlock freeness

Designing a fault-tolerant routing algorithm is mandatory to achieve design of reliable NoCs. Fault-tolerant routing algorithms can use alternative routes when the main

routing path fails. The main difficulty of these methods is on how to choose the sequence of alternative routes since an inappropriate selection may increase the number of hops of packet to reach its destination, thus degrading the performance of NoCs or causing possible deadlocks or live-locks.

Some switching techniques were designed to avoid the deadlock packet in the network. Wormhole and store-and-forward switching technique were proposed for deadlock freeness, however there are no general result that show the adaptivity and deadlock freeness of these techniques.

Many fault-tolerant routing algorithms have been designed to avoid the faulty resources in network. The first's proposal was based on the adaptation of turn model such as west-first, north-last, negative-first [25], and odd-even [75]. These techniques were proposed to avoid packet deadlock, lower hardware costs compared to more sophisticated algorithm. But they are not deadlock free routing algorithm and have lows performance due to the fact that they have less adaptivity than fully adaptive routing algorithms in avoiding the fault [69].

Turn model routing algorithms divide 2-D coordinates into four destination zones, based on vertical and horizontal lines. Some of them use only one route and are qualified as deterministic. We found three deadlock in the West-first routing algorithm as presented in Figure 2.12-a. Almost all deadlock in West-first routing algorithm occurs when there is a destination node in westbound part of the current node and there is a fault in the west port of current node. For North-last routing algorithm, the deadlock are presented in Figure 2.12-b. It occurs if there is a fault on the south port of the destination node in the northbound of current node. In Negative-first routing algorithm, the deadlock condition are presented in Figure 2.12-c. The deadlock occurs when the fault in the west port of current node for destination node in northwest and southeast from current node. While in Fully-adaptive routing [51] algorithm, the deadlock will occurs only if there are at least two faults between the current node and the destination node as presented in Figure 2.12-d.

The Dyad routing scheme algorithm [29] combines deterministic and adaptive tech-

Figure 2.12: Conditions where deadlocks occur in (a) West-first, (b) North-last, (c) Negative-first and (d) Full-adaptive routing algorithm

niques. Fully adaptive routing algorithm [51] uses always a route which is not congested. The algorithm does not care although the route is not the shortest path between sender and receiver. It may select a non-minimal path allowing uniform distribution of traffic but may result in deadlock. C-routing algorithm in [58] is partially adaptive and prevents live-lock and deadlock without use of virtual channel. It combines XY routing and partially adaptive routing depending on the location of source and destination nodes. All these algorithms were designed for latency optimization and do not take into account faults arising in the network. The RAFT [69] tolerant routing algorithm handles a basic one-faulty-link and can be considered as a fault-tolerant version of DyXY [40]. In [15], the authors proposed a load balancing method to reduce the network congestion using an adaptive scheduler in network interfaces based on the Global Load Balancing (GLB) information metric for arbitration in routers.

A fault-tolerant routing algorithm in [78] propose a method that if there are faulty-router, the algorithm route the packet through a cycle free contour surrounding the faulty router. However this algorithm has more number of hops when it avoids a faulty router to reach the destination. A table-based routing algorithm [21] that can support any NoC topology was also proposed to tolerate faulty links. The main drawback comes

NoCs simulator 31