# DEVELOPMENT OF A MIL-STD-1553B

# TIME DIVISION DATA BUS

TERMINAL

**Geoffrey Anthony Holt**

A project report submitted to the Faculty of Engineering, University of the Witwatersrand, Johannesburg, in partial fulfilment of the requirements for the degree of Master of Science in Engineering.

Johannesburg, 1985

- 1 -

## DECLARATION

I declare that this project report is my own, unaided work. It is being submitted for the Degree of Master of Science in Engineering in the University of the Witwatersrand, Johannesburg. It has not been submitted before for any degree or examination in any other University.

Attole

27 day of DECEMBER 1985

- 2 -

### ABSTRACT

A flexible, general purpose NIL-STD-1553B network terminal is developed to enable evaluation and possible later use of this standard in distributed processing applications. The terminal is capable of operating in any of the defined modes and supports all optional features of the standard.

A survey of components available for interfacing to MIL-STD-1553B is presented. This leads to a choice of the Marconi range of components as being best suited for use in this terminal.

S. Martine .

A specification for the terminal is formulated. The terminal hardware is designed and a general approach to software for the terminal is discussed. An Intel 80186 microprocessor is used to interface a pair of 1553B busses to Multibus, via a dual port memory which provides message buffering.

A prototype version of the terminal has been constructed, and lessons learned in the testing and debugging of this hardware are discussed.

- 3 -

## ACKNOWLEDGEMENTS

The author wishes to acknowledge the following assistance in the execution of this project.

- Mr. G.T. Gray of the Department of Electrical Engineering, University of the Witwatersrand, for supervision of the project.

- Mr. H. Roos of Teklogic, for advice and constructive criticism.

- Tony Kempe, for his advice, help with Forth, and the use of his software utilities.

- Teklogic (Pty) Limited, for the sponsoring of all the components used in the project.

Burn Maran and Stranger

The Council for Scientific and Industrial Research for personal financial assistance.

- 4 -

# CONTENTS

Page

| DECLARATION      | 2  |

|------------------|----|

| ABSTRACT         | 3  |

| ACKNOWLEDGEMENTS | 4  |

| CONTENTS         | 5  |

| LIST OF FIGURES  | 9  |

| LIST OF TABLES   | 10 |

| NOMENCLATURE     | 11 |

|                  |    |

14

IN THE PARTY OF TH

į

Į

| 1     | INTRODUCTION                                | 1.1  |

|-------|---------------------------------------------|------|

| 1.1   | Problem Statement                           | 1.2  |

| 1.2   | Background to Problem                       | 1.3  |

| 1.2.1 | Network Requirements of Distributed Systems | 1.3  |

| 1.2.2 | MIL-STD-1553B Overview                      | 1.6  |

| 1.2.3 | Existing 1553B Systems                      | 1.13 |

| 1.3   | Relevance of Project                        | 1.15 |

| 1.4   | Scope of the Project                        | 1.16 |

| 1.5   | Report Layout                               | 1.16 |

|       |                                             |      |

| 2 | SURVEY  | and  | SELECTION  | OF | MIL-STD-1553B | BUS | 2.3 |

|---|---------|------|------------|----|---------------|-----|-----|

|   | INTERFA | CE ( | COMPONENTS |    |               |     |     |

| 2.1 | Introduction                             | 2.2 |

|-----|------------------------------------------|-----|

| 2.2 | Selection Criteria                       | 2.2 |

| 2.3 | Parts of the Bus Interface               | 2.3 |

| 2.4 | Survey of Components                     | 2.3 |

| 2.5 | Validation of 1553B Interface Components | 2.6 |

| 2.6 | Component Selection                      | 2.7 |

- 5 -

CONTENTS

Contraction of the second second

ł į 1 .

3.1

| -     |                                            |      |

|-------|--------------------------------------------|------|

| 3.1   | Influencing Factors                        | 3.2  |

| 3.2   | Functional Specification                   | 3.3  |

| 3.2.1 | MIL-STD-1553B Interface                    | 3.4  |

| 3.2.2 | Multibus Interface                         | 3.5  |

| 3.2.3 | Generalised Input/Output Interface         | 3.6  |

| 3.2.4 | Embedding of the Terminal in the Subsystem | 3.6  |

| 3.2.5 | System Configurations                      | 3.6  |

| 3.3   | Electrical Specification                   | 3.9  |

| 3.4   | Mechanical Specification                   | 3.9  |

| 3.5   | Compliance with Specification              | 3.10 |

| 3.5.1 | Hardware Design                            | 3.10 |

| 3.5.2 | Prototype                                  | 3.10 |

| 3.5.3 | Final Version                              | 3.13 |

|       |                                            |      |

INAL SPECIFICATION

| 4     | TERMINAL DESIGN OVERVIEW                 | 4.1  |

|-------|------------------------------------------|------|

| 4.1   | Hardwara Design Overview                 | 4.2  |

| 4.1.1 | The Local Processor                      | 4.4  |

| 4.1.2 | Local Memory                             | 4.4  |

| 4.1.3 | Dual Redundant MIL-STD-1553B Interface   | 4.5  |

| 4.1.4 | Generalised I/O Interface                | 4.6  |

| 4.1.5 | Multibus Interface                       | 4.7  |

| 4.1.6 | Dual Port Memory                         | 4.7  |

| 4.1.7 | Local Peripherals                        | 4.8  |

| 4.2   | Software Design Overview                 | 4.9  |

| 4.2.1 | Range of Complexity of Terminal Software | 4.10 |

| 4.2.2 | Proposed Software Structure              | 4.13 |

| 4.2.3 | Implementation of Software Scheme        | 4.16 |

| CON | TR | IN' | PS |

|-----|----|-----|----|

|     |    |     |    |

| Р | a | q | e |

|---|---|---|---|

|   |   |   |   |

| 5     | PRCTOTYPING AND TESTING            | 5.1  |

|-------|------------------------------------|------|

| 5.1   | Prototype Construction             | 5.2  |

| 5.2   | Prototype/Design Differences       | 5.3  |

| 5.2.1 | Generalised I/O Interface          | 5.3  |

| 5.2.2 | Multibus Master Interface          | 5.4  |

| 5.2.3 | Bus Interface Busy Latch           | 5.4  |

| 5.2.4 | Dual Port RAM                      | 5.4  |

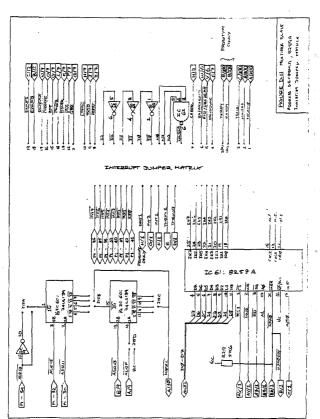

| 5.2.5 | Interrupt Junger Matrix            | 5.5  |

| 5.3   | Debugging and Testing Methods      | 5.5  |

| 5.3.1 | Initial Debugging                  | 5.5  |

| 5.3.2 | Use of Forth as a Development Tool | 5.6  |

| 5.4   | Design Testing and Results         | 5.8  |

| 5.4.1 | Dual Port Memory                   | 5.8  |

| 5.4.2 | 1553B Bus Interface                | 5.10 |

| 6     | RECOMMENDATIONS & CONCLUSIONS | 6.1 |

|-------|-------------------------------|-----|

| 6.1   | Design Review                 | 6.2 |

| 6.1.1 | Possible Design Improvements  | 6.3 |

| 6.2   | Future Work on Terminal       | 6.4 |

| 6.3   | Conclusions                   | 6.5 |

### APPENDICES

1

| A   | MIL-STD-1553B BUS INTERFACE COMPONENTS | A. 2 |

|-----|----------------------------------------|------|

| A.1 | STC Range                              | A.1  |

| A.2 | Marconi/CTI Range                      | A.2  |

| A.3 | Grumman/SMC Bus Interface Unit         | A.4  |

| A.4 | Harris Range                           | A.5  |

| A.5 | ILC Data Device Corporation Hybrid Set | A.6  |

| A.6 | Rockwell-Collins 1553 Interface Device | A.8  |

| $\sim$ |  |  |

|--------|--|--|

ł

Page

| в   | MRTU 53045-SUBSYSTEM INTERFACE AND OPERATION | B.1  |

|-----|----------------------------------------------|------|

| B.1 | Remote Terminal Operation                    | B.1  |

| B.2 | Bus Controller Operation                     | B.9  |

| B.3 | Bus Monitor Operation                        | B.11 |

|     |                                              |      |

| С   | HARDWARE DESIGN                              | C.1  |

| C.1 | Local Processor                              | C.1  |

| C.2 | Local Memory                                 | C.6  |

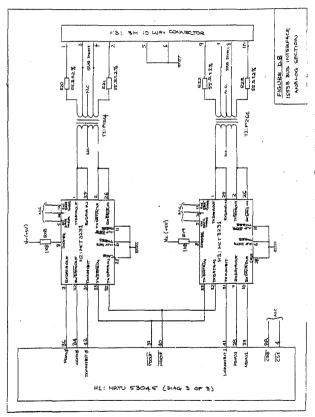

| C.3 | MIL STD-1553B Bus Interface                  | C.7  |

| C.4 | Generalised I/O Interface                    | C.26 |

| C.5 | Multibus Interface                           | C.28 |

| C.6 | Dual Port Memory                             | C.31 |

| C.7 | Local Peripherals                            | C.36 |

| C.8 | Processor Address Space Allocation           | C.39 |

|     |                                              |      |

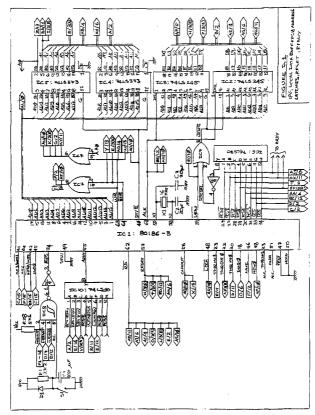

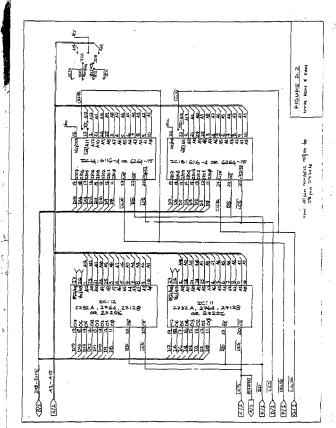

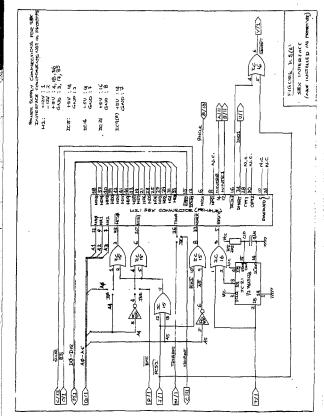

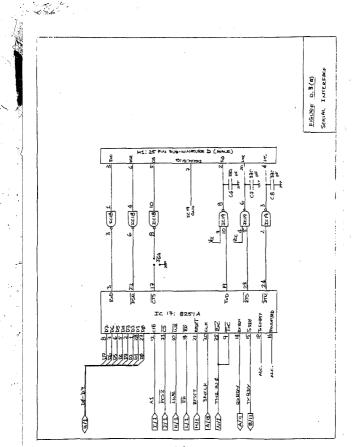

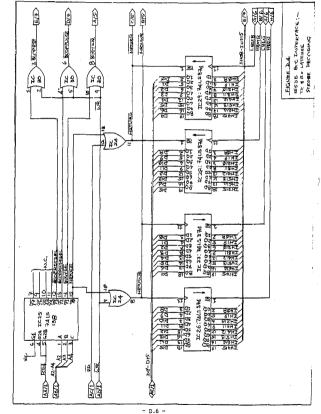

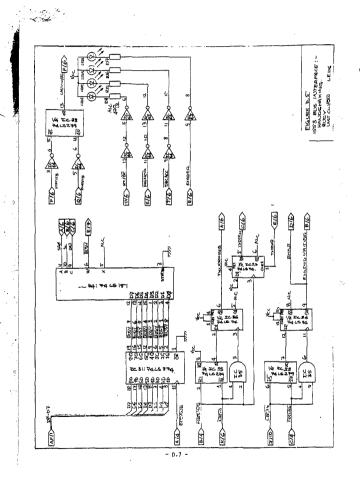

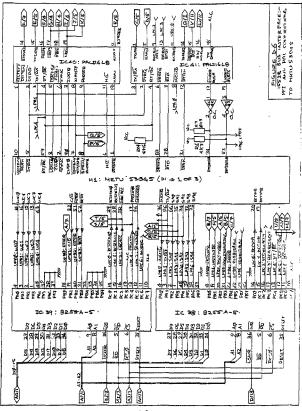

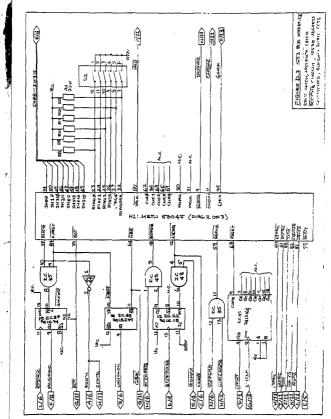

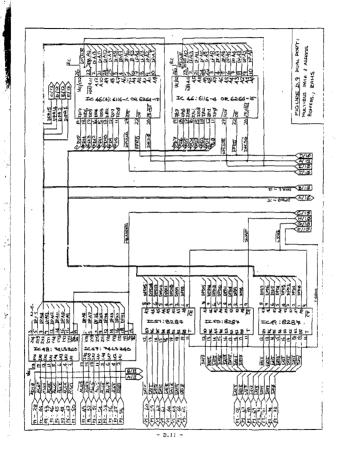

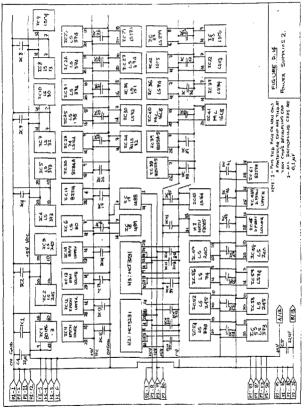

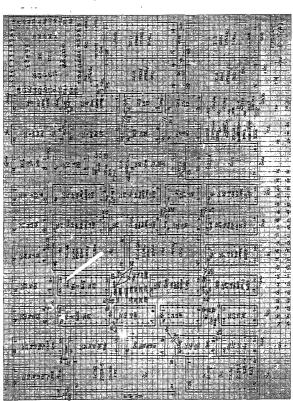

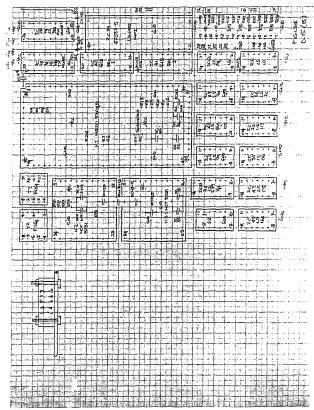

| D   | HARDWARE SCHEMATICS AND CONFIGURATION TABLES | D.1  |

| D.1 | Pin to Pin Schematics                        | D.1  |

| D.2 | Component List                               | D.17 |

| D.3 | Prototype Board Layout                       | D.18 |

| D.4 | Jumper Configuration                         | D.21 |

|     |                                              |      |

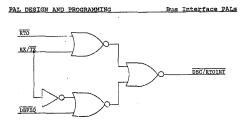

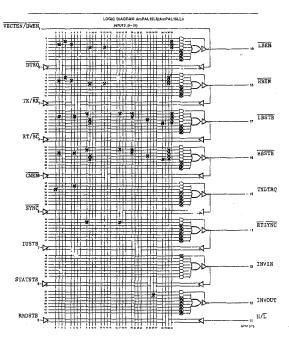

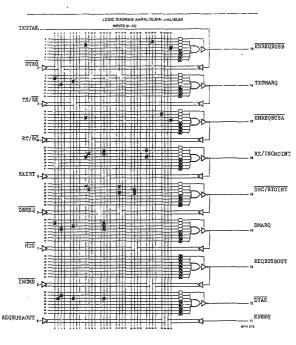

| Е   | PAL DESIGN AND PROGRAMMING                   | E.1  |

| E.1 | Design Procedure                             | E.1  |

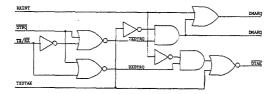

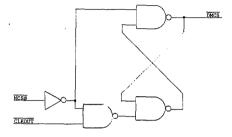

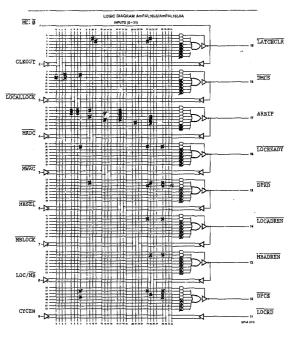

| E.2 | Bus Interface PALS                           | E.3  |

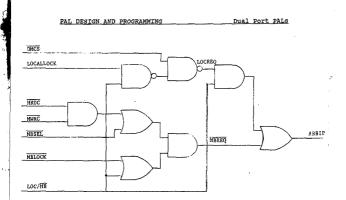

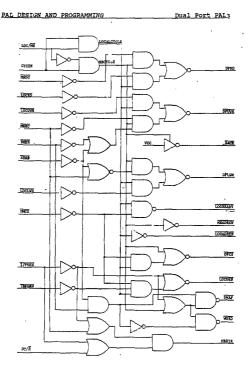

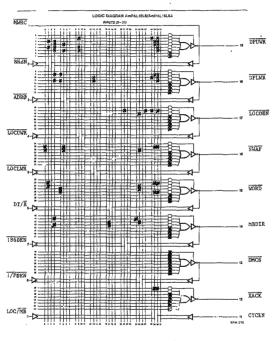

| E.3 | Dual Port Arbitration and Control PALS       | E.17 |

|     |                                              |      |

| F   | TEST SOFTWARE LISTINGS                       | F.1  |

| F.1 | Assembler Hybrid Test                        | F.1  |

| F.2 | Forth Primitives                             | F.9  |

| F.3 | Dual Port Memory Lock Test                   | F.14 |

| F.4 | Forth Bus Interface Drivers                  | F.16 |

| F.5 | Command Interrupt Service Routine            | F.19 |

### REFERENCES

- 8 -

# LIST OF FIGURES

3

学を読みまし、 ない、 たい

0

|        |                                      | Page |

|--------|--------------------------------------|------|

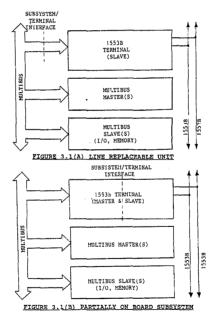

| 3.1(A) | Line Replaceable Unit                | 3.7  |

| 3.1(B) | Partially On Board Subsystem         | 3.7  |

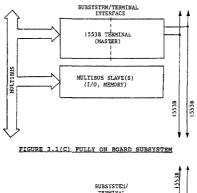

| 3.1(C) | Fully On Board Subsystem             | 3.8  |

| 3.1(D) | Stand Alone                          | 3.8  |

|        |                                      |      |

| 4.1    | Hardware Block Diagram               | 4.3  |

| 4.2(A) | Dual Port Memory Map                 | 4.13 |

| 4.2(B) | Buffer Structure                     | 4.13 |

|        |                                      |      |

| C.1    | The Local 186 Processor              | C.3  |

|        | Template for Bus Interface Schematic | C.24 |

| • •    | MIL-STD-1553B Bus Interface          | C.25 |

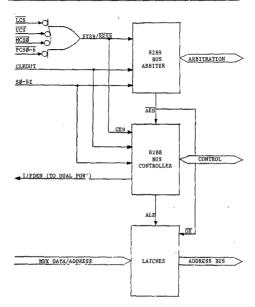

| C.3    | SBX Address Maps                     | G.27 |

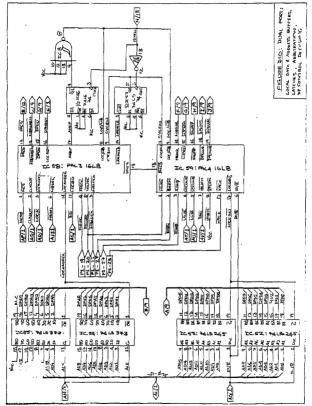

| C.4    | Multibus Master Interface            | C.30 |

| C.5    | Dual Port Memory                     | C.32 |

| C.6    | Interrupt Jumper Matrix              | C.38 |

|        |                                      |      |

|        | Pin-to-Pin Schematics                | D.2  |

| D15    | Prototype Board Layout               | D.19 |

|        |                                      |      |

| E.1    | Handshaking and DMA Request Lines    | E.10 |

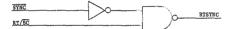

| E.2    | RTSYNC* Line                         | E.11 |

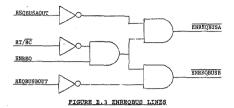

| E.3    | ENREQBUS Lines                       | E.12 |

| E.4    | RX/INCMDINT Line                     | E.13 |

| E.5    | DBC/RTOINT Line                      | E.14 |

| E.6    | PAL 1 Version 0                      | E.15 |

| E.7    | PAL 2 Version 2                      | E.16 |

| E.8    | DMCS* Line                           | E.18 |

|        | ARBIP Line                           | E.20 |

| E.10   | Control Logic                        | E.22 |

| E.11   | PAL 3 Version 1                      | E.25 |

|        | DIT 4 Newsion 1                      | F 26 |

- 9 -

# LIST OF TABLES

|     |                                           | Page |

|-----|-------------------------------------------|------|

| 2.1 | Comparison of Components                  | 2.4  |

| 3.1 | Built In Test Word Bit Assignments        | 3.5  |

| c.1 | Programmable Chip Selects and Wait States | C.40 |

| D.1 | Component List                            | D.17 |

| D.2 | ROM Jumpers                               | D.21 |

| D.3 | RAM Jumpers                               | D.21 |

| D.4 | SBX Jumpers                               | D.22 |

| D.5 | Multibus Slave Decoding Jumper            | D.22 |

| E.1 | LBEN* AND HBEN                            | Ē.5  |

| E.2 | LBSTJ* AND HBSTB*                         | E.7  |

| F 2 | Arbitration Wruth Mable                   | F 10 |

A PARTY

第二三十十年三日本

# NOMENCLATURE

The following conventions have been adopted for the name of signal lines:

All signal lines are written in upper case (eg. CLKOUT). If the signal is active low, the name is followed by an asterisk (eg. IUSTB).

Abreviations used in the text have the following meanings:

And Property of the second sec

| 1553B | MIL-STD-1553B                                    |

|-------|--------------------------------------------------|

| BC    | Bus Controller                                   |

| BIT   | Built-In-Test (word)                             |

| BM    | Bus Monitor                                      |

| CMOS  | Complimentary Metal Oxide Semiconductor (logic)  |

| CPU   | Central Processing Unit                          |

| DMA   | Direct Memory Access                             |

| EPROM | Erasible Programmable Read Only Memory           |

| FIFO  | First In First Out                               |

| IEEE  | Institute of Electrical and Electronic Engineers |

|       | (standardising body)                             |

| I/O   | Input/Output                                     |

| LED   | Light Emitting Diode                             |

| LRU   | Line Replacable Unit                             |

| lsttl | Low power Schottky Transistor-Transistor Logic   |

| MSI   | Medium Scale Integration                         |

| PAL   | Programmable Array Logic                         |

| PIC   | Programmable Interrupt Logic                     |

| PIT   | Programmable Interval Timer                      |

| RAM   | Random Access Memory                             |

| ROM   | Read Only Memory                                 |

| RT    | Remoter Terminal                                 |

| RX    | Receive(r)                                       |

## NOMENCLATURE

| SBX   | iSBX I/O bug (IEEE P959 I/O bus)            |

|-------|---------------------------------------------|

| SSI   | Small Scale Integration                     |

| TTL   | Transistor Transistor Logic                 |

| тх    | Transmit(ter)                               |

| USART | Universal Synchronous Asynchronous Receiver |

|       | Transmitter                                 |

# CHAPTER 1

# INTRODUCTION

The problem that is addressed by this project is stated. This is followed by the relevant background material to the problem leading to a justification of the project. The scope of the project work is defined and finally there is a guide to the layout of this report.

$\nabla$

A CANADA CONTRACTOR

#### Problem Statement

## 1.1 PROBLEM STATEMENT

Teklogic has a need for a fast, reliable and robust network to be used in distributed processing, and remote sensing and actuation applications.

These applications may include avionics, "fly-by-wire", and armament functions in aircraft, and similar operations in other vehicles such as tanks, armoured cars and small naval vessels.

Such a network could also find application in the industrial field of process control where again reliablilty and robustness (but not so much speed) are of prime importance.

A potentially suitable network is defined by MIL-STD-1553B. The function of this project is to provide a flexible, general purpose MIL-STD-1553B data bus terminal for the evaluation and possible later use of this network in distributed processing applications.

The terminal is required to make use of one of the standard components available for interfacing to the bus, rather than attempting a "from soratch" design, while still maintaining flexibility and generality. It must interface to Multibus and if possible not occupy more than one board. A further requirement is that Intel microprocessor products be used where necessary, as support for these is available.

#### Background

## 1.2 BACKGROUND TO PROBLEM

### 1.2.1 Network requirements of Distributed Systems

The required characteristics of the communication channel used by a distributed computer system are influenced by the application of the system.

Typical applications in this case are aircraft systems such as:

- Instrumentation

- Navigation

- Flight safety

- Remote control or "fly-by-wire"

- Weapons control

- Flight recording

These systems may also be used in other types of vehicles, both military and civil.

A second class of application to be considered is industrial process control.

### 1.2.1.1 Speed

A CALL STATE AND A CALL

The speed requirements vary from high speed in data processing (because of the large amounts of data typically involved) to relatively low speeds in the case of process control if the plant time constants involved are long. The speed in any system also obviously depends on the number of units that are connected to the network.

The aircraft or vehicle type application lies between the two. A relatively high speed is required as the time

- 1.3 -

#### Background

constants are fairly short (in the case of remote control) and a system may need to respond rapidly to an event (in the case of flight safety and weapons control). On the other hand there are usually few units in the system.

### 1.2.1.2 Extent

For use in a vehicle, the network need only extend a few tens of metres and support a few units. For use in process control on the other hand, in a large system the extent may be a few kilometres and the number of units a few hundred.

### 1.2.1.3 Integrity

This may of course be ensured at a level above the communication medium at the price of incurring an overhead. It is, however, more desirable that the network have a low error rate, and some method of error detection built into it.

Considering that the electrical environment is potentially noisy, the network should have good noise immunity in order to have a low error rate.

## 1.2.1.4 Robustness

In both classes, the environment in which the network has

- 1.4 -

#### Background

to operate is potentially harsh from an electrical, mechanical and temperature viewpoints. Further, in a military application there is the possibility of ballistic damage.

The network hardware must thus be hardened for use in such an environment to ensure a reasonable robustness. The effect of ballistic damage can be red<sup>2</sup> ed by the inclusion of redundancy at the network level, specifically, redundancy of the actual communication madium (cabling).

### 1.2.1.5 Fault Tolerance

In all distributed applications, it is a general requirement that a failure of one unit connected to the network does not cause the failure of the entire network.

Such a failure must thus neither render the communication medium unuseable nor leave the system without overall control.

### 1.2.1.6 Protocol

The type of protocol required arises partly from the above points.The protocol must support any error detection and redundancy that is available. It must also have a suitable mechanism for fault recovery.

Further, the network should be deterministic, that is; the maximum delay in the delivery of a message to its destination must be calculable. This is again important when critical messages are to be passed.

- 1.5 -

#### Background

## 1.2.2 MIL-STD-1553B Overview

The U.S. Department of Defence sets standards to be used and applied by the military services and their contractors. A military standard is a document that establishes engineering and technical requirements for procedures, practices, and methods that have been adopted as standard. One of these is MIL-STD-1553B "Aircraft Internal Time Division Command/Response Multiplex Data Bus" [3].

### 1.2.2.1 Origins

こうになるない こうかくのうちょう

The steadily increasing complexity of military systems, particularly in avionics, has made it no longer practical to use independent and self-sufficient units to meet all requirements [5]. Thus integration of such systems has been taking place to share information among the units in the system with the following advantages:

- Elimination of unnecessary duplication of information sensing and display.

- Performance gains.

- Reliability gains.

- Cost reduction.

- Space saving.

This integration was however initially carried out with little thought to the interconnection between units; wiring was generally dedicated point-to-point. As the above approach was refined, this wiring method became impractical [4] as:

The weight and space taken up by the wires was becoming excessive.

- 1.6 -

State Barris and the second second

#### Background

- Modifications to the system were difficult.

- Access to all parts of the system for test purposes was difficult.

The solution was to turn to data bus techniques which were also beginning to emerge in commercial applications.

The U.S. military realised the need for data bus techniques and their standardisation as far back as 1968 [5]. At that time other methods failed to meet the high integrity, reliability and flexibility requirements necessary in the military environment. It was therefore necessary to review the characteristics of a data bus. The following factors were considered:

- Modulation and coding techniques.

- Signalling methods and signal detection techniques.

- Transmission media considerations.

Eventually MIL-STD-1553(USAF) was published in August 1973 and found its first full application in the F-16 aircraft. After input from the Army, Navy, and industry, MIL-STD-1553A was released for use by all the armed forces in 1975. As this was applied to more vehicles and systems, certain difficulties were recognised [5]. The standard was revised with more input from suppliers and users, and MIL-STD-1553B was released on 21 September 1978. This final version has now also been adopted in the United Kingdom as DEF\_STAN.00-18 Part 2 and by NATO as STANAG 3838.

### 1.2.2.2 Scope of Standard

The standard establishes requirements for information transfer formats and electrical interface characteristics.

- 1.7 ~

Background

It can be considered as defining a <u>standard</u> for information transfer formats or protocol, while laying down a <u>specification</u> for electrical interface characteristics.

### 1.2.2.3 General Architecture

MIL-STD-1553B defines a serial, time division multiplexed data bus operating at one Mbit/sec data rate. The communication medium is a shielded twisted pair. Provision is made for the use of more than one such cable for redundancy purposes. The length of the bus is limited to about 100m by the propagation delay of the cable and the response times required by the standard.

A command/response or "speal only when spoken to" type of protocol is used under which all transfers are initiated and controlled by a single <u>hus controller</u>. Up to 31 individually addressable <u>remote terminals</u> can be connected to the bus, each of which can interface with up to 30 subsystems if necessary. Further non-transmitting <u>bus</u> <u>monitors</u> can be connected to the bus to "...receive bus traffic and extract selected information to be used at a later time". These are the three possible modes of terminal poperation.

Provision is made to allow terminals to change their mode of operation and for the bus controller to broadcast messages to all remote terminals. Bus controllership can be offered to and accepted by a remote terminal by means of a mode command. The protocol thus has a bus token passing type mechanism built into it.

#### Background

## 1.2.2.4 Information Tomoter Formats

Also referred to as "message formats" in 1553B, these define the protocol that is used. The exchange of messages is precisely described and there are only ten allowable formats.

They can be divided into two groups:

<u>Data Transfers</u>. These are essentially used to "...extract data from and feed data to a functional subsystem...". They may transfer up to 32 data words at a time.

<u>Mode</u> <u>Commands</u>. These are essentially reserved "...to communicate with the multiplex bus related hardware, and to assist in the management of information flow...". There is provision for 32 mode commands, 15 of these are defined, the rest being reserved. The use of any or all defined mode commands is optional.

### 1.2.2.5 Modulation and Coding Technique

The technique used is <u>baseband Manchester II</u> biphase <u>encoding</u> at 1 Mbit/second. This method defines bits by a transition from one voltage level during the first half bit time to the opposite level for the second half bit time. The average voltage is thus zero.

### 1.2.2.6 Word Formats

Each word consists of 16 bits preceded by sync and followed by parity. The sync is three bit-times long, and consists of one and a half bit-times at one level and one and a half bit-times at the other level. The parity (one

- 1.9 -

Background

bit) is odd. Thus a word is 20 bit-times long, that is 20 microseconds.

MIL-STD-1553B defines three types of words:

<u>Command Word</u>. This has a positive followed by a negative sync. It is transmitted only by a bus controller terminal. It initiates transmission and defines the data transfer format that is to be used and contains the address of the remote terminal that is to respond.

Status Word. This word also has a positive followed by a negative sync. It is transmitted by remote terminals at the beginning of their response to a command. The status word identifies the remote terminal and passes certain status information back to the bus controller.

<u>Data Word</u>. This word has a negative followed by a positive sync. It is always transmitted contiguously with a command word, status word, or other data words.

## 1.2.2.7 Electrical Characteristics

This section of the standard specifies the characteristics of the cable (its impedance, shielding, attenuation and termination), terminal input and output characteristics (waveform rise times, noise, common mode rejection, and impedance) and cable stubs.

Terminals may be connected anywhere on the bus in one of two ways: Direct coupled stub connections which should not be longer than one foot (300 mm), and Transformer coupled stubs which may be up to 20 feet (6m)

#### Background

S.

## 1.2.2.8 Error Rate and Error Detection

The maximum word error rate that a terminal may exhibit under specified test conditions is one part in 10\*\*7. Theoretical and experimental results indicate that an undetected bit error rate of 10\*\*-12 can be expected from a practical system using the built-in mechanisms (parity, Manchester, and sync validation).

#### 1.2.2.9 Options in the Standard

There are many parts of the standard which are optional. These are summarised below:

Mode of terminal operation. Terminals may or may not support more than one of the three modes of operation.

<u>Subaddresses</u>. Remote terminals may have provision for any number of subaddresses, between one and thirty, within their subsystems.

<u>Embedding of subsystems</u>. A remote terminal may be embedded in, or separate from but communicating with, the subsystem(s) that it serves.

Broadcast. Terminals may or may not support the use of broadcast commands.

<u>Mode commands</u>. These are all optional as to whether or not they are supported by a terminal. Non-implemented mode commands should simply be ignored.

<u>Built-in-test word</u>. One of the mode commands is for a remote terminal to transmit a built-in-test word. This

- 1.11 -

#### Packground

word is intended to supplement the available bits in the status word when a terminal is sufficiently complex to warrant its use. There is no specification defining what the bits will be used for, except that they shall not be used to transfer subsystem information, and their definition is left up to the designer.

<u>stub coupling</u>. The terminal may use a transformer coupled stub or direct coupled stub or have provision for both.

Redundant busses. The terminal may support extra bus cables to be used as redundant standbys.

### 1.2.2.10 MIL-STD-1553B and the OSI/RM

MIL-STD-1553B has not been related to the OSI reference model in any of the references used in this project. This is probably due to the fact that 1553B was defined before the work on the reference model was completed. This is a brief attempt to show what parts of the model are defined by 1553B.

Lavel 1. the Physical Control Level comprises the physical, mechanical, functional and procedural characteristics required to connect, maintain, and disconnect the physical circuits between equipments [9]. This layer is defined by the MIL-STD-1553B standard with the exception of the mechanical characteristics as no specific connector configuration is laid down.

Level 2, the Link Control Level is concerned with reliable interchange of data connected by level 1 facilities and includes address differentiation, message identification, error detection and response, and flow control. All these features are built into the standard, but since some of

#### Background

them are partially optional (built-in-test word and vector word), they will vary from terminal to terminal.

Lavels 3 upward are concerned with more complex networking operations and support transmission across more than one network. MIL-STD-1553B does not extend to any of these lavers.

### 1.2.2.11 Signal Suitability

The appendix to the MIL-STD-1553B document, which gives some design guidelines suggests, that signals of bandwidth 400 Hz or less are the most suitable for inclusion on the bus, while signals in the range 400 Hz to 3 kHz may be accommodated if the loading on the bus is low enough. High bandwidth signals (eg. video) must obviously be excluded [3].

Signals that have a low rate but possess a high urgency (event type messages) are also considered to be generally unsuitable because of bus latency.

## 1.2.3 Existing 1553B Systems

The existing applications of the standard are mainly in avionics. This is mainly because all new U.S. military aircraft requiring a data bus are obliged to use 1553B. The specific application examples found in the references are all aircraft systems, but mention is made of ground and naval systems that are operating, as well as 3.3 on the space shuttle [5]. Although the suitability of the bus to industrial applications is often mentioned [11,17,4], there is no reference to specific cases of such systems.

#### Background

From the examples it is clear that in the past at least, a 1553B terminal was soldow designed in isolation. Generally an entire multiplex system was designed and then the terminals were designed to meet specific requirements in the system. This would often resulted in several different types of terminals in the system, each possessing differing capabilities.

Finally there are some variations of the standard that have been suggested and in some cases are in prototype form:

Transmission method. Fibre optic [5] and current mode transmission [17]. Although non-standard, these could be useful in certain applications and could form the basis of new standards with only the relevant sections altered.

<u>Bus length</u>. This could be extended by increasing the no response time out [11]. This does not violate the standard, as only a minimum no response time out is specified, but the minimum is invariably used in aircraft applications.

Bus speed. There is a design supporting a 2.5 MHz bit rate [17]. This is obviously non-standard.

<u>Use of reserved parts of standard</u>. The reserved mode codes and reserved bits in the status word could be used to convey application specific subsystem information, thus increasing efficiency [15]. Again this is in obvious violation of the standard.

~ 1.14 -

#### Relevance of Project

## 1.3 RELEVANCE OF PROJECT

From the background study, it is clear that MIL-STD-1553B is potentially well suited for the type of distributed processing applications cutlined in section 1.2.1. In order to evaluate, and possibly later use the standard in such applications, a 1553R terminal design is required.

In contrast to the usual approach, in which the system is designed around 15538 and the function of each terminal is fixed, the specific requirements of this terminal will change from one application to the next, or from one function within an application to the next.

In the case that the standard is put into use in a system, it will save considerable design time to have a configurable terminal that can be used in every connection to the bus. It will also make the system far more maintainable, particularly if the terminal can be made to be an easily replaceable module (hence the requirement that it occupy only one board).

The terminal must thus be as flexible and general as possible. All optional portions of the standard should be implemented and where there is a choice, both possibilities should be accommodated. If the terminal could support some of the non-standard variations this might be an advantage, but such variations would have to be used with great discretion. If the terminal could use the status bits and mode codes that are currently reserved it would be able to support possible future versions of the standard which might define functions for the these status bits and mode codes.

The requirements that the terminal use Intel products and interface to Multibus are limiting but practical in terms

- 1.15 -

#### Relevance of Project

of the support which is available, and equipment which is in general use by Teklogic.

Finally this project is intended to add to the local knowledge and expertise in MIL-STD-1553B.

### 1.4 SCOPE OF THE PROJECT

The scope of this project is the specification, hardware design and verification of a suitable NIL-STD-1553B data bus terminal to meet the stated requirements of the problem.

This also involves a survey of commercially available 1553B bus interface components (since a "from scratch" bus interface design has been ruled out), formulation of an overall approach to the design of the terminal (including a software scheme), and the construction of a prototype terminal with which to verify the design.

### 1.5 REPORT LAYOUT

The remainder of this report is arranged as follows:

The available bus interface components are surveyed in chapter 2. With this information it is possible to draw up the functional specification in chapter 3. The overall design of the terminal is presented down to block diagram lavel in chapter 4. Chapter 5 deals with the prototype hardware construction and testing. Finally chapter 6 contains conclusions and suggestions for further work.

Appendix A is survey of 1553B bus interface components. The interface to, and operation of, the components that were selected is summarised in appendix B. Appendix C

- 1.16 -

#### Report Layout

describes the detailed implementation of the hardware blocks defined in chapter 4. Appendix D contains the full circuit schematic diagrams, component list, configuration information and board layout of the prototype. The method, and details, of the design of the FAL components used is in appendix E, and listings of software used to test the prototype are in appendix F.

## **CHAPTER 2**

## SURVEY AND SELECTION OF MIL-STD-1553B BUS INTERFACE COMPONENTS

The criteria for the choice of bus interface components are discussed. The components that are available are then surveyed. A selection of bus interface components is then made and justified.

Introduction

# 2.1 INTRODUCTION

Before a realistic functional specification for the MIL-STD-1553B terminal can be defined, it is necessary to review the capabilities of the various components that are available to interface to 1553B. The level to which the standard is implemented, the options that are supported, and the restrictions that are imposed by the components that are finally selected, will affect what the terminal is functionally capable of doing. The selection is thus made before the functional specification is presented.

## 2.2 SELECTION CRITERIA

いくため、大学をないたからないとうとう

The criteria on which a selection is made are as follows:

Minipisation of external hardware and software remired to complete the full protocol. The more that is done in this regard by the bus interface components themselves, the less the burden on hardware external to the components (thus saving board space) and software (thus freeing processor time for other functions).

Simplicity of interfacing to the components. For example: Do the components have an 8 or 16 bit bus? Are commands specified by a pattern of input lines or simply by writing to a control block in memory? Is there a DNA type interface or must transfers be handled externally? Again the more simple this interface, the less board space will be occupied.

<u>Ability to implement optional features of 1553B</u>. The components must allow the support (either directly or with external hardware and software) of as many of the options in the standard as possible. Of most importance is that

- 2.2 -

#### Selection Criteria

bus control and bus monitor modes are possible besides the usual remote terminal mode.

<u>Flexibility in terms of reserved parts of 1553B</u>. Will the Components allow the use of the reserved mode codes and status bits or not?

Small size. Again, a board space consideration.

The components to be chosen must thus be the ones which best fulfil the requirements of "generalness" and size, while not being so elementary that it will be necessary to design a great deal of hardware and incur a large software overhead to implement the full protocol.

## 2.3 PARTS OF THE BUS INTERFACE

The bus interface can be separated into three main parts:

- The isolation/coupling transformers.

- The analog driver/receiver section.

- The digital section.

It is to the last of these that most of the above criteria apply. Hence the following survey covers mainly the components for the digital section.

## 2.4 SURVEY OF COMPONENTS

The components surveyed fall roughly into two groups:

Full implementation components. These are usually in the form of a chip set or hybrid. They tend to implement the whole standard, and nothing but the standard.

- 2.3 -

<u>More general components</u>. These are generally single chips performing some of the low level operations necessary in a 1553B terminal (eg. Manchester encoding/decoding and recognition of sync type, address, broadcast and mode code) but not enforcing any particular response or action by the terminal.

Appendix A is a detailed survey of features of components from the main MIL-STD-1553B manufacturers. Of these the most common appear to be the first four namely Marconi, STC (Snith), Harris, and Grumman/SMC [ll,15]. The features of the main components of these manufacturers are summarised in table 2.1

| FEATURE      | GRUMMAN   | HARRIS | SMITH    | MARCONI  |

|--------------|-----------|--------|----------|----------|

| Subsystem    | 16 bit    | serial | 16 bit   | 8 bit    |

| data I/F     | [parallel | 1      | paralle1 | parallel |

| Data         | DMA async | sync   | sync     | DMA sync |

| transfer     | handshake | 1      | 1        | 1        |

| control      | 1         |        |          |          |

| Use of       | )yas      | yes    | no       | ) no     |

| reserved     | 1         | Í.     | 1        | 1        |

| features     | 1         | 1      | i i      | i        |

| allowed      | 1         |        |          | 1        |

| Buffering of | double    | none   | one      | double   |

| data         | Í.        | i.     | message  | i        |

| 1            | 1         | Í.     | length   | 1        |

| 1            |           | I      | IFIFO    | 1        |

#### TABLE 2.1 COMPARISON OF COMPONENTS

Survey

State State

Survey

| FEATURE                               | GRUMMAN    | HARRIS     | SMITH      | MARCONI     |

|---------------------------------------|------------|------------|------------|-------------|

| Error checks                          | Manchester | Manchester | Manchester | Manchester  |

|                                       | parity     | parity     | parity     | parity      |

|                                       | word count | sync       | sync       | sync        |

|                                       | response   | I.         | bit count  | bit count   |

|                                       | sync       | 1          | word count | word count  |

|                                       | >16 bits   | 1          | 1          | loop test   |

|                                       | 1          | I          | l –        | RT address  |

|                                       | l .        | ł          | 1          | parity      |

|                                       | 1          | I          | 1          | no response |

|                                       | 1          | 1          | I          | tx timeout  |

|                                       | 1          | 1          | 1          | subsystem   |

|                                       | 1          | I          | L          | handshake   |

| provision for                         | no         | 2,5 Mb/sec | no         | no          |

| other bit                             | 1          | ł          | l          | ł           |

| rates                                 | L          | I          | L          | L           |

| Bus                                   | i yes      | yes, not   | no         | yes         |

| controller                            | 1          | directly   | 1          | I           |

| and monitor                           | 1          | available  | ļ.         | 1           |

| capability                            | L          | L          |            | l           |

| Redundancy                            | no         | no         | yes, with  | yes, in     |

| capability                            | l          | 1          | addition   | hybrid or   |

|                                       | l          | 1          | of second  | with second |

| · · · · · · · · · · · · · · · · · · · | I          | L          | enc/dec    | receiver    |

| Packaging                             | 40 pin     | 40 pin     | 3 chip set | 4 chip set  |

|                                       | chip       | chip       | 48, 40 and | 40, 40, 48  |

|                                       | 1          | 1          | 53 pins or | and 40 pins |

| ·                                     |            |            | hybrid     | or hybrid   |

| Mode codes                            | 7 only     | none       | all        | all         |

| handled                               | I i        |            |            | 1           |

| irectly                               |            |            |            | L           |

## TABLE 2.1 Continued

- 2.5 -

FEATURE SMITH MARCONI GRUMMAN HARRIS Remote is/w loaded must be |hardwired |hardwired [terminal can be |externally|with |with address |read back |implemen- |parity bit |parity bit | ited Technology INMOS Junction |CMOS liso-CMOS lisolated | I CMOS

#### TABLE 2.1 Continued

Survey

### 2.5 VALIDATION OF 1553B INTERFACE COMPONENTS

All NIL-STD-1553B components to be used by the U.S. armed forces have to pass a validation test at the Air Force's Systems Engineering Avionics Facility (SEAFAC) [1]. The tests cover six basic area:

- Misinterpretations and deviations from the standard.

- Bu., configuration.

- Test conditions at manufacturer's facility.

- Basic design flaws.

- Periodic and non-periodic error conditions.

- Terminal response to induced errors.

This gives rise to an argument against the use of software to implement the full 1553B protocol. It is argued that during slight software modifications to suit a particular application, the 1553B protocol may be corrupted, thus requiring re-approval by SEAFAC for every implementation.

This problem, which is not an important consideration in this design, could partly explain the fact that the two British designs from Marconi and Smith Industries have

- 2.6 -

1553B INTERFACE COMPONENTS Validation of Components

secured a large portion of the mainly American market [11].

#### 26 COMPONENT SELECTION

The interface components chosen are:

- Marconi MRTU 53045 Remote Terminal Bus Control Thick Film Hybrid.

- Two Marconi MCT 3231 Driver/Receivers.

- Two Pascall P1264 coupling transformers for use with MCT 3231s.

The reasons for the choice of the MRTU 53045 are follows:

- The MRTU 53045 is a very compact version of the Marconi chip set.

- It supports bus controller and bus monitor modes as well as the usual remote terminal mode.

- The full 1553B protocol is implemented and no external hardware or softwire is required for this purpose.

- The subsystem interface is relatively simple. For bus control in particular it is very easy to use. Almost all internal conditions can be monitored or used to interrupt the subsystem.

- The no response time out can be stretched.

- The device has been used before in South Africa and thus there is some local experience of the device.

- The design has been tried and proven overseas. (This applies to the chip set as such, the hybrid implementation did prove to have some flaws.)

2.7 -

#### 1553B INTERFACE COMPONENTS

#### Component Selection

1782

- The documentation is fairly complete, but a little difficult to read due to awkward layout.

- The component was readily available.

The main disadvantanges of this component are:

- Inflexibility from the point of view of reserved features of the standard.

- Built-in-test word is predefined and fixed.

- It is very expensive.

のないない

The choice of the MCT 3231 analog section and the F1264 transformer is due purely to the fact that they are directly compatible, both with the MRTU 53045 and with each other.

- 2.8 -

# CHAPTER 3

## TERMINAL SPECIFICATION

The factors influencing the specification are reviewed. The detailed specification is then presented. Finally the level to which the design, prototype, and final versions are expected to comply with the specification are discussed.

#### Influencing Factors

## 3.1 INFLUENCING FACTORS

The main factors determining and influencing the specification have been covered in the previous two chupters and are reviewed here.

#### They are:

Constant and the second second

- The requirements and

- the constraints as given in the original problem statement.

- The capabilities of the bus interface components that have been chosen.

#### The requirements are:

- The terminal must implement the HIL-STD-1553B data bus standard.

- It must be general, supporting as many of the optional portions of the standard as possible.

- It must be flexible, allowing its use in a variety of applications.

- It must be able to interface to Multibus so as to enable its use with existing equipment.

### The constraints are:

- The terminal must make use of existing components to interface to the bus and not attempt a "from scratch" design.

- The terminal should not occupy more than one Multibus card.

- Microprocessor products to be used are restricted to the Intel range.

- 3.2 -

#### Influencing Factors

The bus interface components selected influenced the final concise specification of the terminal. This does not imply that the components were selected without regard for the specification and then the specification built around the components. Rather the selection was the result of some iterations of terminal specification and reveiw of component capabilities. Parts of the final specification however, came about directly as a result of the components ultimately chosen. For this reason the selection of the components is covered before the specification is presented.

The features of the components that affect the specification are:

- The MRTU 53045 supports the full protocol with all mode codes in remote terminal mode.

- The MRTU 53045 may easily be configured for bus control and bus monitor modes.

- The MRTU 53045 does not allow the use of reserved features of the standard.

- The contents of built-in-test word is defined and fixed.

- The MRTU 53045 supports dual redundant busses.

- The Pascall P1264 transformer will support both direct and transformer coupled stubs.

## 3.2 FUNCTIONAL SPECIFICATION

The terminal may be viewed as a 'black box' which has, as means of communicating with the outside world, a dual redundant MII-STD-1553B bus interface, a Multibus interface, and a generalised J/O interface.

TERMINAL SPECIFICATION Functional Specification

#### 3.2.1 MIL-STD-1553B Interface

The MIL-STD-1553B interface is dual redundant, that is connections are possible to two busses which are regarded as a dual redundant pair as defined in the standard.

The terminal is capable of operating in all three defined modes namely; remote terminal (RT) mode, bus controller (BC) mode and bus monitor (BM) mode. It is capable of changing from one mode to another during operation as allowed by the standard. It may also change modes in special circumstances (such as failure of the bus controller to initiate any communication for longer than a certain time) not normally allowed by MIL-STD-1553B. It is capable of powering up into any one of these modes.

Tm all three modes the terminal operates in full accordance with the entire standard. In addition all optional features of the standard are implemented. This means that in bus monitor mode, all defined information transfer formats may be intiated and that any command may be sent. In remote terminal mode this means that all mode codes are implemented, and that the terminal may respond to broadcast commands if desired.

When the mode command to transmit built-in-test (BIT) word is received by the terminal in RT mode, the terminal will respond with its status followed by a BIT word where the bits have the significance as given in table 3.1. The full explanation as to the meaning and use of the various bits is given in the MEDL 1553 LSI Chip Set - Remote terminal specification [18].

- 3.4 -

Functional Specification

#### TABLE 3.1 BUILT IN TEST WORD BIT ASSIGNMENTS

|         |                                  | _  |

|---------|----------------------------------|----|

| BIT NO. | ASSIGNMENT                       | _1 |

| 0 lsb   | Transmitter timeout flag         | I  |

| 1       | Subsystem handshake failure      |    |

| 2       | Loop test failure                | 1  |

| 3       | Mode T/R bit wrong               | ļ  |

| 4       | Illegal mode command             | 1  |

| 5       | Word count low                   | 1  |

| 6       | Word count high                  | 1  |

| 7       | Broadcast transmit data received | I  |

| 8       | Bus 0 shutdown                   | I  |

| 9       | Bus 1 shutdown                   | Į  |

| 16      | Bus 2 shutdown                   | I  |

| 11      | Bus 3 shutdown                   | 1  |

| 12      | Transmitter timeout on bus 0     | I  |

| 13      | Transmitter timeout on bus 1     | 1  |

| 14      | Transmitter timeout on bus 2     | 1  |

| 15 msb  | I Transmitter timeout on bus 3   | _1 |

## 3.2.2 Multibus interface

A AND A A

The terminal has an interface functionally conforming to the IEEE 796 bus or Multibus specification (24). The interface has two parts; a slave interface and a master interface.

The slave interface appears as a block in the Multibus memory address space. The size of this block is sufficient to queue messages to and from the network in the event of the maximum of 30 subaddresses being used in a remote terminal subsystem. The memory is dual ported and may be transparently accessed by the terminal internally. Both Multibus and the terminal are able to "lock" a series of transactions to this memory to prevent the other

- 3.5 -

### Functional Specification

gaining access. The base address of this memory in the Multibus address space is hardware configurable.

The master interface allows the terminal access to the Multibus in the same way as any other master. The block in the memory address space occupied by the slave interface specified above is not necessarily accessible to the terminal via its master interface.

### 3.2.3 Generalised Input/Output Interface

This interface is functionally compatible with the IEEE P959 or Intel iSEX I/O bus [24]. It is provided to enable the terminal to communicate with a variety of Input/Output (I/O) devices having this interface, without the need to use Multibus. For prototyping, this interface will be useful to monitor the internal state of the terminal.

### 3.2.4 Embedding of the terminal in the subsystem

The terminal has the capability of supporting the software for a small subsystem or part of a larger subsystem onboard. Any I/O required by this subsystem could be accessible either via the Multibus interface or the generalised I/O interface. Such a configuration is equivalent to the subsystem with embedded remote terminal as defined in MIL-STD-1553B.

## 3.2.5 System Configurations

In this context the system refers to the combination of terminal and subsystem. The network will have several such systems connected to it.

- 3.6 -

ģ

R

いないという

à.

3

#### Functional Specification

The system may thus be configured in four main ways (some other combinations are obviously possible) as illustrated in figure 3.1. The position of the terminal/subsystem functional interface is shown in each case.

- 3.7 -

### Functional Specification

In Figure 3.1(A) the terminol can be regarded as a line replaceable unit (LRU) which can be replaced by an "off the shelf" unit in the event of a failure, without regard for the specific subsystem it must serve. It is

~ 3.8 -

「「「「「「「「」」」」

THE REAL PROPERTY IN

### Functional Specification

anticipated that the terminal will be used mainly in this configuration.

The configuration in figure 3.1(B) could be used in medium sized systems where one extarnal processor on Multibus is just insufficient for the application. A small amount of the load could be shifted to the terminal's local processor.

The figure 3.1(C) and (D) configurations will be useful in the case of a small subsystem load. The stand alone mode also has the advantage that it frees the terminal from Multibus.

## 3.3 ELECTRICAL SPECIFICATION

The Multibus and SBX interfaces conform electrically with the relevant sections of the respective standards.

The MIL-STD-1553B interfaces conform to the specification in all respects for both direct and stub coupling.

The components all conform to the military temperature ratings or are directly replaceable with components which do.

The terminal requires power supplies at +5 volts +12 volts and -12 volts.

### 3.4 MECHANICAL SPECIFICATION

The terminal occupies a single Multibus board.

The Multibus and SBX interfaces once again conform fully

### Mechanical Specification

with the mechanical portions of their specifications.

There is no specific portion in MIL-STD-1553B determining how the twisted pair stubs are to be connected, except that the connection must be as close as nossible to the coupling transformer. This is adhered to and suitable connectors are used. Separate pins are provided for the direct and transformer coupled stub options on each of the two busses.

## 3.5 COMPLIANCE WITH SPECIFICATION

### 3.5.1 Hardware Design

The hardware design of the terminal presented in the following chapters complies fully with the functional and electrical specifications presented above, as far as is possible in the hardware design phase.

Some aspects of the functional specification which relate to software, such as the ability of the onboard processor to be able to support an application as well as control the bus interface components during time critical operations, could not be guaranteed at the time of this design. It was also not possible to predict with certainty that the hardware would fit onto the single Multibus card.

## 3.5.2 Prototype

The prototype, seeks to verify the the most important aspects of the hardware design and test its ability to implement the functional specification.

- 3.10 -

Compliance

The prototype adheres to the constraint of board space imposed by the single Multibus card. In some cases availability and cost of components were limitations. For these reasons, "ome parts of the hardware (that in any case are fairly standard designs) were not implemented in the prototype, and certain sections were substituted by other simulified or less general designs.

### 3.5.3 Final Version

The experience of the prototype shows how much of the original hardware design can be implemented on a single card with all the design flaws eliminated. It also shows what parts of the functional specification cannot be met.

The final product of this design, if it were to be carried through to that stage, would thus best be a result of at least another iteration of functional specification and prototype (using a printed circuit board this time).

## CHAPTER 4

## TERMINAL DESIGN OVERVIEW

An over fiew of the design to meet the functional and electrical specifications is presented. It is divided into hardware and software aspects of the design. The hardware is presented as a block diagram design. The functions and requirements of each block are discussed. The proposel software design is then overviewed.

- 4.1 -

#### Hardware

## 4.1 HARDWARE DESIGN OVERVIEW

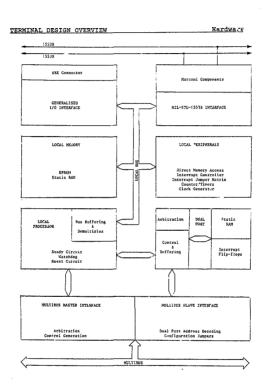

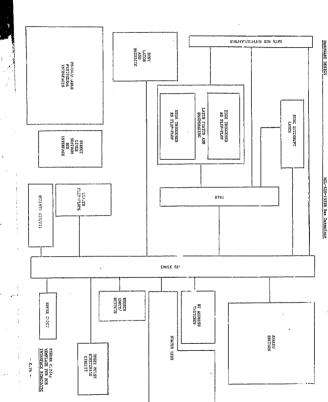

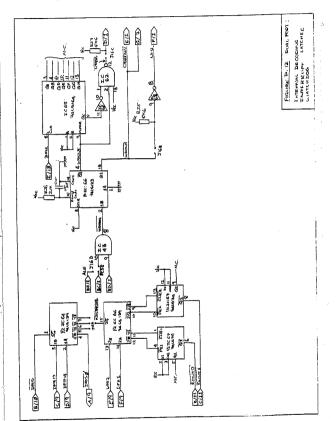

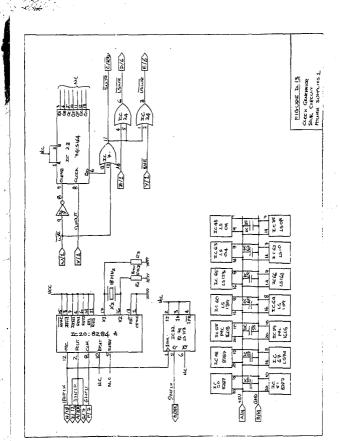

The hardware required to meet the design specifications can be broken down into 7 main blocks as shown in figure 4.1:

The <u>three interfaces</u> required by the functional specification:

- Dual redundant MIL-STD-1553B interface.

- Multibus interface.

- Generalised I/O interface.

The <u>medium for message buffering</u> and communication between the terminal and Multibus:

- Dual port memory.

The <u>on board microprocessor system</u> required to control these resources:

- Local processor.

- Local memory.

- Local peripherals.

Figure 4.1 also shows the principal parts internal to each block and the interconnections between each block.

The following paragraphs cover the purpose, requirements and functional design of each block. The actual implementation of each block in hardware is covered in the appendix C while pin-to-pin connection diagrams and consiguration information are given in appendix D.

- 4.2 -

ş

A DESCRIPTION OF A DESC

.....

3.9

-----

#### FIGURE 4.1 HARDWARE BLOCK DIAGRAM

- 4.3 -

#### Hardware

### 4.1.1 The Local Processor

This will be responsible for controlling the MRTU 53045 chip set hybrid, as well as possibly forming part of the subsystem. The response time demanded by the hybrid in certain cases is fairly short. The processor should be able to respond to an interrupt and run the necessary code in time to satisfy this requirement (see section 4.2.3). The processor chosen must therefore be suitably powerful both in terms of spoed and instruction set.

Since the data quantities handled by 1553B are intrinsically 16 bit, it makes sense to use at least a 16 bit processor.

A watchdog circuit is provided to restart the processor in the event of it "hanging". This may be either a hardware watchdog, which will only detect that the processor has stopped running, or a software watchdog that, together with suitably written software, will also detect that the processor is hung in a software loop.

### 4.1.2 Local Memory

The processor will require some ROM for initialisation after power up and to implement the terminal function. If it is required to implement a part or all of the subsystem as well, considerably more program memory may be required (ace section 4.3). The ROM memory must thus be expandable up to at least 32k. ERROMS are used at this stage.

Some local RAM is provided. It is anticipated that this will be used simply as scratch pad memory since all the data to be handled by the terminal will be stored in the dual port memory. However in some situations, notably in

- 4.4 -

Hardware

prototyping, this memory could be useful as program storage for code which has been downloaded. Since it is necessary for all components that are used to be available in MIL versions, dynamic RAM cannot be used. At least 16k of static RAM is therefore required.

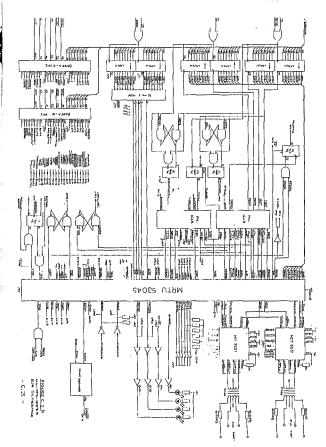

### 4.1.3 Dual Redundant MIL-STD-1553B Interface

This block represents the major portion of the work in the design, particularly as very few guide lines were available. Some simple examples are given in the <u>Subsystem Interface For MEDL LSI 1553B Remote Terminals</u>, [20 pp 28-30].

This provides the interface as specified to two 1553B busses (allowing both direct and transformer coupling on each) on one side, and clean interface to the local microprocessor system on the other.

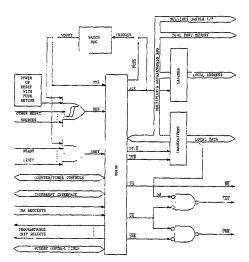

It consists of the Marconi bus interface components and the required circuitry to interface these to the local bus, and to provide suitable signals for interrupting the local processor. The interface to, and operation of, the Marconi 53045 chip set hybrid is summarised in Appendix B.

The 8 bit hybrid data bus must be interfaced to the 16 bit processor data bus with a suitable buffering to ease the response times required of the processor. Handshaking must be supplied for these data transfers. A method of writing to and latching the control input lines is required, as well as a means of reading the status output lines. Those output lines which indicate events (rather than states), must either be latched to provide status information, or modified (if necessary) to provide interrupts.

Contraction of the local division of the loc

Hardware

Since the terminal has to be flexible and the exact function of some of the lines on the MRTU 53045 is not clear, the interface is more complex than is strictly necessary. For instance, several output lines have been made suitable for both monitoring as status, and causing interrupts as it is not known at this stage which will be more useful. After the prototype has been fully tested in all modes it may be possible to simplify the supporting circuitry.

The hybrid has, by means of the current word count (CWC) status lines and certain strobe lines, the ability to implement a DMA type interface. While this could be useful for a simple application, it is not a viable method of transforing data in this case for the following reason:

The use of this feature of the hybrid will necessitate either the use of a triple port memory (since both Multibus and the local processor also need access to the data), or the design of handshaking and isolation to enable the hybrid to gain control of the local bus. The first method is obviously impracticable, while the second will be expensive on board area and will tie up the local bus for approximatly two microseconds for each transfer. Transfer of data can be achieved more efficiently by using a normal DNA channel.

### 4.1.4 Generalised I/O Interface

This interfaces the local bus to the SBA I/O bus. In order to support all possible modules that may be attached, two interrupt lines and one DMA channel are required. It is hardware configurable for different modules.

~ 4.6 -

#### Hardware

## 4.1.5 Multibus Interface

This consists of a master and a slave interface. The master interface allows the local processor access to the Multibus while the slave interface allows Multibus access to the dual port memory.

These could be totally independent of each other, however it is convenient (from a space point of view) to combine certain lines which are common to both. In particular this could be done with the data and address busses. The local busses could be interfaced to the Multibus busses via the dual port busses, the dual dot is isolation and byte swap compo-

The slave interface also provides hardware selection and decoding of the Multibus dual port address.

The multibus interrupt lines are available for use either to or from the terminal, the master interface does not support bus vectored interrupts.

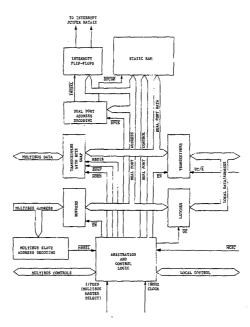

## 4.1.6 Dual Port Memory

This block is composed of three sections; the memory itself, interrupt flip-flops, and the arbitration logic and bus buffering. These are linked by the dual port data, address, and control busses.

The memory has to be large enough to queue messages to and from the network in the event that the full house of 30 subaddresses are used in a remote terminal (see section 4.2). The memory must thus be expandable to 32k. The memory must be static RAM for the same reason as the local memory.

- 4.7 -

Hardware

The interrupt flip-flops are provided as a means for the local processor to generate interrupt for another processor on Multibus. These flip-flops are necessary because Multibus does not allow the use of edge triggered interrupts. They are used to cause an interrupting condition which must be reset by the service routine of the interrupted processor. The latches are set and cleared from within the dual port address space.

The arbitration logic manages the bus buffer and RAM control lines to effectively couple either the local processor bus, or Multibus, to the RAM, based on which has asserted a select line. The arbitration logic also allows each bus to lock itself to the memory by means of a lock line. The arbitration logic further provides for the coupling of the local data and/or address busees and the corresponding Multibus buses via the dual port address bus whon the local processor is accessing Multibus, if the scheme outined in 4.1.5 above is implemented.

### 4.1.7 Local Peripherals

Based on the above discussion, certain peripheral devices ars required.

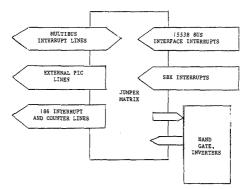

One direct memory access chunnel is needed to service the 1553B bus interface and another for the SBX interface.

At least one interrupt controller device is required to service the 1553B interface, the SBX interface and Multibus interrupts. Not all of the possible sources of interrupt will be required for a given application. Particularly this is true of the 1553B interface, where many signals have been designated as inter rupt sources in

- 4.8 -

Hardware

the prototype design, in case they are needed. A second interrupt controller however may be required if the minimum number of lines that may need service in any application exceeds the number provided by one controller.

An interrupt jumper matrix is provided to enable selective strapping of optional interrupts to the controller(s).

An event counter is useful in the case of a terminal which is to be used in bus monitor mode. Conditions occuring on the bus (such as parity errors) can be counted by connecting the parity error interrupt line to the event counter. Thus the input to this device must also go to the above interrupt jumper matrix.

An interval timer is required to provide a regular interrupt (tick) to the processor if a multitasking executive is to be used (see section 4.2).

Sundry clock signals are generated for use by various devices.

## 4.2 SOFTWARE DESIGN OVERVIEW

1

The software design presented here is not implemented in this project. The scope of the project covers only test software to verify the operation of the prototype hardware, and to check the ablility of the local processor to respond to the network within the time constraints imposed by the protocol.

This section is provided to show the motivation for some of the features that have been included in the hardware, and to suggest an approach for software for the terminal to be written at a later date. This approach will

- 4.9 -

Software

accommodate both simple and complex applicat.ons in its structure.

The various strategies for program control of the hardware itself (mainly the MRTU 53045 hybrid) are covered in the appendix C under the lardware design as, in some sections, the hardware design is a result of hardware/software interface considerations.

#### 4.2.1 Range of Complexity of Terminal Software

The terminal software could range in complexity from a very simple remote terminal application to a bus controller/remote terminal which supports the full protocol and many subaddresses.

An example of a simple application is a remote terminal that interfaces an instrument on a plant to a 1553B network. If the output of the instrument is a single 16 bit value, then only a single type of message transfer format needs to be accommodated, namely a transmit command to transmit a single word. The bus controller should not send any other type of command to the RT. In this case the transmit/receive bit, subaddress and word count may be ignored by the RT. It does not need to respond to broadcasts or support the subsystem busy bit, the service request bit, the transmit vector word mode command, or the synchronise mode command. All that is required of the terminal software, in this case is, that it continuously reads the output of the instrument, check the MRTU 53043 hybrid for a word request and if true, supplies the value. Note that this is an example of the subsystem residing locally on the terminal board.

An example of a complex application is the case of a

- 4.10 -

Software

remote terminal which supports the use "" the full 30 subaddresses and is capable of accepting bus controllership. All information transfer formats, all status bits, and all mode commands are supported in both RT and BC mode. In RT mode, messages to and from the network must be buffered and queued. In addition part or all of the subsystem software resides locally.

Both extremes of application are accommodated in the following proposed software structure.

## 4.2.2 Proposed Software Structure

The software is separated into tasks. The bus interface or terminal software is considered as one task, while the subsystem is considered as consisting of at least one task but possibly several tasks (corresponding to different subaddresses). The bus interface task communicates with the subsystem tasks via a suitable data structure in the dual port memory.

The bus interface task always runs on the terminal's local processor, while the subsystem tasks may run locally or on other processors on Multibus. If one or more tasks besides the bus interface task reside locally, some form of multitasking executive must be provided.

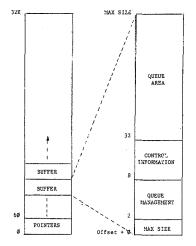

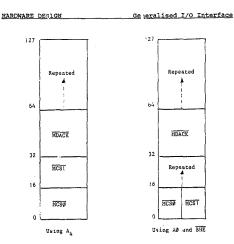

### 4.2.2.1 Uual Port Memory Data Structure

Each of 30 potential subsystem tasks (one for each subaddress) is allocated a pair of buffers in the dual port memory, one for input from and the other for output to the network.

- 4.11 -

Software

The base of the dual port memory contains a table of pointers (offsets relative to the base of the dual port memory) to the input and output buffers to be used for each subaddress. This allows more than one subaddress to be assigned to the same task by placing the same buffer addresses in the pointers for each subaddress.

Figure 4.2(a) is a diagram of the dual port memory using this scheme.

The buffers are managed as queues of optional size and also provide for the passing of control information. Figure 4.2(b) is a diagram of a possible buffer structure. The max queue size indicates the size of the queue area. The following these locations manage the queue. The next 12 locations could be used for passing control information (such as subsystem busy, subsystem status, service request synchronising word and vector word) or semaphores indicuting the validity of data.

A dual port memory of 32k will allow an application to use a full house of subaddresses each having separate input and sutput buffers capable of holding seven full length (32 word) messages as follows:

Buffer pointers: 2 x 30 = 60 words Each buffer: 32 + 7 x 32 = 256 words Total size of data structure: 60 + 30 x 2 x 236 = 15420 words = 30840 bytes Dual port memory of 32k = 2\*\*15 = 32766 bytes

- 4.12 -

FIGURE 4.2(B) BUFFER STRUCTURE

- 4.13 -

Software

## 4.2.2.2 Bus Interface Task

This task may be composed of up to three routines corresponding to the three possible modes; remote terminal, bus controller, and bus monitor. Control is passed from one routine to another (if present) when the terminal changes mode under the conditions specified in the standard.

The <u>RT routine</u> is application independent. It is responsible for:

- Setting up DMA transfers of the correct length to and from the correct location in the dual port memory in response to transmit and receive commands.

- Monitoring the service request subsystem status and busy bits of each subaddress and providing the logical OR of these bits to the hybrid.

- Providing the vector word in response to a transmit vector word mode command.

- Synchronising the subsystem in response to a synchronise mode command with or without an associated data word.

- Correctly setting the dynamic bus control acceptance bit and passing control to the BC routine if r dynamic bus control mode command is received a: the terminal is able to assume bus control.

The <u>BC</u> routine will be application dependent. No specific functions are regulared of a terminal in BC mode by the standard. This routine may pass control to either the RT or BM routines after successfully passing bus control to another terminal on the network.

- 4.14 -

Software

The <u>BM routine</u> is also application independent. No specific functions are required of a terminal in BM mode, but the terminal is restricted in that it cannot transmit and in that all information gathered is for off line use. The BM routine may pass control to the BC routine in the event that the bus has been sensed to be silent for longer than a specified period.

### 4.2.2.3 The Subsystem Tasks

These are obviously application dependent. They have access to the data structure in the dual port memory. Suitable primitives could be provided to allow these tasks to engueue and dequeue messages, and to set and read control information from the buffers.

### 4.2.2.4 The Multitasking Executive

The requirements of this executive need further consideration, but a fairly simple scheme would probably suffice. Provision is made for a tick or regular interrupt in hardware on which to run the executive.

Since Intel components are being used, a possible choice for an executive could have been the RMX operating system. Rowever, besides being far too complicated, this executive is unsuitable due to the length of time that it disables all interrupts.

A further point about interrupts is that there are certain conditions which will require immediate response from the local processor, such as the receipt of a command by the hybrid when in RT mode. These interrupts must be made high priority and must never be disabled. It will not be

- 4.15 -

Software

State State

necessary for the service routines of these interrupts to modify the state of any of the tasks, so they will not affect the operation of the executive if they occur while it is rescheduling tasks.

#### 4.2.3 Implementation of Software Scheme

Certain aspects of this software design will have to be tested on the prototype board in order check the viability of the scheme.

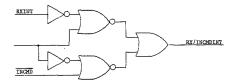

In particular the amount of processing that can be done between an interrupt indicating the reception of a command in RT mode and the hybrid requiring a DNA transfer, is important. During this time the processor must determine what type of command it is and, if it is a transmit or receive command, initialise a DMA channel. The DMA initialization involves using the subaddress and transmit/receive bit to get the buffer pointer from the table in the base of the dual port RAM, and using this pointer to obtain a queue input or output pointer (depending on the command received) which is the address to or from which the DMA must be programmed to occur. The word count must also be programmed into the DMA channel.