THE VALIDATION OF EMBEDDED SOFTWARE

Thomas Davidtz

A dissertation submitted to the Faculty of Engineering, University of the Witwatersrand, Johannesburg, in fulfilment of the requirements for the degree of Master of Science in Engineering.

Johannesburg 1986

Page i

DECLARATION

I declare that this dissertation is my own, unsided work. It is being submitted for the degree of Master of Science in Engineering at the University of the Witwatersrand and has not been submitted before for any degree or examination at any other University.

THOMAS DAVIDTZ

TNELFTH day of AUGUST 19 86

Page ii

ŝ

and the second of the second

# ABSTRACT

The use of embedded computers in Railway Signalling systems and other highly-critical monitoring and control applications has led to a demand for an effective method of validation of the software within such systems. An important aspect of validation is proving a computer programme to be consistent with its specification.

This dissertation proposes a pragmatic method of proving a machine-code programme to be consistent with its high-level programme specification. A disassembly of the machine-code programme is obtained and automatically analysed in terms of control-flow and data~flow. Βv using information from the datadeclaration portion of the specification. the disassemblv listing is translated to а level corresponding to that of the high-level specification. Consistency between the translated programme and the original high-level specification is proved by direct comparison.

The dissertation suggests the validity of the above approach and shows by example, how such an approach may be implemented.

Page iii

# ACKNOWLEDGEMENTS

I wish to acknowledge my debt to:

The SOUTH AFRICAN TRANSPORT SERVICES for sponsoring the research.

Mr Louis Potgieter, Senior District Engineer, SOUTH AFRICAN TRANSPORT SERVICES, for his advice, guidance and enthusiasm.

Professor M.G. Rodd, University of the Witwatersrand, for his advice and support throughout the duration of the research project.

Page iv

# CONTENTS

1. O ....

# Page

| DECLARATION      |   | 5   | 1 |

|------------------|---|-----|---|

| ABSTRACT         |   | i   | i |

| ACKNOWLEDGEMENTS |   | iii | i |

| CONTENTS         |   | i١  | ŧ |

| LIST OF FIGURES  | v | iii | Ĺ |

# CHAPTER 1 INTRODUCTION

| 1.1   | Background               | 1  |

|-------|--------------------------|----|

| 1.2   | Statement of the Problem | 2  |

| 1.3   | Direction of Research    | 5  |

| 1.4   | Scope of Research        | 8  |

| 1.4.1 | Programme                | 8  |

| 1.4.2 | Specification            | 9  |

| 1.4.3 | Automation               | 10 |

| 1.4.4 | Stated goal              | 11 |

| 1.5   | Overview of Dissertation | 11 |

# CHAPTER 2 LITERATURE SURVEY

| 2.1 | Survey of publicat | ions | 14 |

|-----|--------------------|------|----|

| 2.2 | State-of-the-art   |      | 24 |

## CHAPTER 3 DISASSEMBLY

| 3.1   | Test Set-Up                                  | 29 |

|-------|----------------------------------------------|----|

| 3.1.1 | Guinea-pig microprocessor system             | 29 |

| 3.1.2 | Tracing the microprocessor's operations      | 30 |

| 3.1.3 | Stimulus of the device                       | 30 |

|       | Operation of the block instruments           | 30 |

|       | Hardware monitoring and failure strategies - | 30 |

|       | Message reception and analysis               | 31 |

3.2 Trace Specification -----32 3.2.1 Trace specification document -----34 Trigger occurrence -----34 Trigger on opcode ----- 35 3.3 Production of the Disassembly Listing ----- 35 3.3.1 Obtaining the traces \_\_\_\_\_ 35 Providing the stimulus ----- 35 Tracing the test runs \_\_\_\_\_ 36 3.3.2 Manipulation of the traces ----- 36 Uploading the traces to a minicomputer ---- 36 Editing and sorting the traces ----- 36 3.4 Result of Disassembly \_\_\_\_\_ 38

# CHAPTER 4 CONTROL-FLOW ANALYSIS

| 4.1   | Constructs in P-notation                     | 40 |

|-------|----------------------------------------------|----|

| 4.1.1 | Sequence                                     | 40 |

| 4.1.2 | Selection                                    | 40 |

| 4.1.3 | Iteration                                    | 40 |

| 4,2   | Construct Recognition and Labelling          | 41 |

| 4.2.1 | Input and storage of disassembly listing     | 41 |

| 4.2.2 | Processor-specific information               | 42 |

| 4.2.3 | First pass: if-then-else and                 |    |

|       | loop recognition                             | 42 |

| 4.2.4 | Second pass: case recognition                | 44 |

| 4.2.5 | Overlapping and unrecogniseable constructs - | 47 |

| 4.3   | Results of Control-Flow Analysis             | 48 |

#### CHAPTER 5 DATA-FLOW ANALYSIS

19

| 5.1   | Data Types in P-notation                  | 50 |

|-------|-------------------------------------------|----|

| 5.1.1 | Formulation of a data table               | 53 |

| 5.2   | Effect of Data-Type on Data Manipulations | 55 |

| 5.3   | Analysis of Data Manipulations            | 56 |

| 5.3.1 | General strategy                          | 56 |

Page v

5.3.2 Immediate manipulation

58

5.3.3 Register storage

59

Bit-wise analyser

62

Arithmetic expression generator

68

5.3.4 Conditional branches

71

5.4 Results of Data-Flow Analysis

75

Page vi

# CHAPTER 6 PROGRAMME TRANSLATION

| 6.1   | Structure Translation            | 77 |

|-------|----------------------------------|----|

| 6.1.1 | Formatting of constructs         | 77 |

| 6.2   | Data-Flow Transistion            | 79 |

| 6.3   | Results of Programme Translation | 83 |

# CHAPTER 7 FINAL RESULT AND CONCLUSIONS

A.2

| 7.1                 | Techniques Developed                 | 85 |

|---------------------|--------------------------------------|----|

| 7.1.1               | Features                             | 85 |

| 7.1.2               | Limitations                          | 85 |

|                     | Limitations of control-flow analysis | 86 |

|                     | Limitations of data-flow analysis    | 87 |

|                     | General limitations                  | 87 |

| 7.1.3               | Recommended refinements              | 88 |

|                     | Control-flow analysis refinements    | 88 |

|                     | Data-flow analysis refinements       | 89 |

|                     | General refinements                  | 89 |

| 7.2                 | Conclusions                          | 90 |

|                     |                                      |    |

|                     |                                      |    |

| REFERI              | ENCES                                | 92 |

|                     |                                      |    |

| APPENDIX A TEM L 30 |                                      |    |

|                     |                                      |    |

|                     | Tu 4 m - 4 m - 4 d                   |    |

A-2

Overview of Operation -----

# Page vii

V B

بال ما

61

4

| A.3   | System Operation                             | A-2 |

|-------|----------------------------------------------|-----|

| A.3.1 | Operation of the block instrument - input -  | A-3 |

| A.3.2 | Encoding                                     | A-3 |

| A.3.3 | Data transmission                            | A-4 |

| A.3.4 | Data receipt                                 | A-4 |

| A.3.5 | Operation of the block instrument - output - | A-5 |

| A.4   | Safety Features                              | A-5 |

APPENDIX B P-NOTATION SYNTAX

ġ

0

# APPENDIX C CONTROL-FLOW ANALYSIS ALGORITHMS

| C.1 | Algorithm for Case Identification | C-1 |

|-----|-----------------------------------|-----|

| C.2 | Algorithm for If-Then-Else and    |     |

|     | Loop Identification               | C-2 |

Page viii

LIST OF FIGURES

3000

I

| Figu | gure .                                                        |     |

|------|---------------------------------------------------------------|-----|

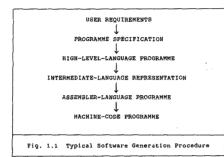

| 1.1  | Typical software generation procedure                         | - 7 |

| 3.1  | Test set-up                                                   | 33  |

| 3.2  | Portion of trace specification document                       | 34  |

| 3.3  | Sample trace file                                             | 37  |

| 3.4  | Sample disassembly listing                                    | 37  |

| 4.1  | Generalised implementations of P-notation standard constructs | 43  |

| 4.2  | Printout after pass one of the                                |     |

|      | analyser                                                      | 44  |

| 4.3  | An implementation of the P-notation                           |     |

|      | case construct                                                | 45  |

| 4.4  | Printout after pass two of the analyser                       | 46  |

| 4.5  | Overlapping construct detection                               | 48  |

|      |                                                               |     |

| 5.1  | Data object positioning within a record                       | 52  |

| 5.2  | Absolute address declaration                                  | 53  |

| 5.3  | Standard format of data-table                                 | 54  |

| 5.4  | Immediate memory-location manipulation                        | 58  |

| 5.5  | CLR statement type-determination                              | 59  |

| 5.6  | Whole-byte representation of                                  |     |

|      | bit-wise operation                                            | 60  |

| 5.7  | Correct representation of Bit-complement                      | 60  |

| 5.8  | Character-string initialisation                               | 63  |

| 5.9  | Character-string modification after<br>bit-mask operation     |     |

|      |                                                               | 63  |

| 5,10 | Character-string modification after                           |     |

|      | register-load operation                                       | 64  |

|      | Expressions generated for bit-wise operation -                | 65  |

| 5.12 | Character-strings for store-operation                         |     |

|      | with operand 0001H                                            | 65  |

| 5.13 | Expressions generated for bit-copy operation -                | 65  |

6

# Page ix

| 5,14 | Data type-violation detoction             | 65  |

|------|-------------------------------------------|-----|

| 5.15 | Recognition of Boolean-bit                |     |

|      | complement operation                      | 66  |

| 5.16 | Bit-copy within byte                      | 67  |

| 5.17 | Bit-copy between bytes                    | 67  |

| 5,18 | Analysis of manipulation using carry bit  | 68  |

| 5.19 | Character-string initialisation           |     |

|      | according to register-name                | 69  |

| 5.20 | Character-string modification after       |     |

|      | register-addition                         | 69  |

| 5.21 | Character-string modification after       |     |

|      | register-loading                          | 70  |

| 5.22 | Addition-operation representation         | 70  |

| 5.23 | Insertion of parentheses                  | 71  |

| 5.24 | Insertion of redundant parentheses        | 71  |

| 5.25 | Textual representations of                |     |

|      | conditional branch instructions           | 73  |

| 5,26 | Initialisation of character-strings       |     |

|      | before conditional branch instruction     | 73  |

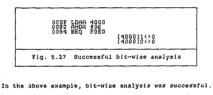

|      | Successful bit-wise analysis              | 74  |

| 5.28 | Unsuccessful bit-wise analysis            | 74  |

| 5.29 | Premature termination of analysis         | 74  |

|      |                                           |     |

| 6.1  | Control-flow translation                  | 79  |

| 6.2  | Control- Sw translation including         |     |

|      | case const uct                            | 79  |

| 6.3  | Translation of if-then-else construct     | 80  |

| 6.4  | Translation of repeat-until construct     | 61  |

| 6.5  | Register-name appearing in test-predicate | 81  |

| 6.6  | Translation of case construct             | 82  |

|      |                                           |     |

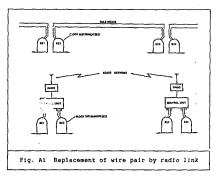

| A1   | Replacement of wire-pair by radia link    | A-2 |

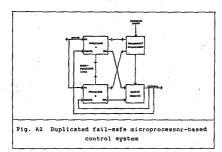

| A2   | Duplicated fail-safe microprocloudrybased |     |

|      | control system                            | A-3 |

0 \_0 \_ KS \_ KS \_ KS \_

#### CHAPTER 1 INTRODUCTION

## 1.1 Background

In railway signalling, an "interlocking system" is a control system which ensures the safe operation of trains. Until very recently, all interlocking systems were fail-safe, relay-based control systems. These relay-based interlocking systems have evolved to a point where they display extremely high degrees of reliability. However, many of the relays used in relay-based interlocking systems are specialised items which are expensive to manufacture and require routine maintenance.

The interlocking function is essentially the logical manipulation of an input state to produce an output state and is thus ideally suited to implementation by a computer-based system. With the cost of computer computer-based hardware continually decreasing. interlocking systems are becoming an in reasingly attractive alternative to relav-based interlocking systems. Several electronic, computer-based interlocking systems are already in use in various countries as pilot schemes for evaluation.

The South African Transport Scrvices, who are responsible for the national railway system, has had two computer-based, electronic interlocking systems commissioned for evaluation. In addition to evaluation of the individual interlocking systems, the South African Transport Services wishes to keep abreast of technology in the field of electronic interlocking systems.

In order to be a viable alternative to relay-based

$\mathcal{C}$

interlocking systems, elactronic interlocking systems must at least match the safety standards of relay-based interlocking systems. This high degree of safety required is normally achieved by hardware redundancy. Software output-comparison and voting are used to isolate faulty components or, in the event of multiple failure, to shut-down the entire system. Software also often dees routine hardware-monitoring to check the integrity of hardware components such as RAM and PROM memories. Thus the integrity of the software is of prime importance.

$h^{i}$

Therefore, before a compute,-based interlocking system can be put into use, engineers in the railway organisat:on must satisfy themselves as to the integrity of the embedded software. Also, if changes are the be made to the software after commissioning, engineers making the changes must be able to show that their changes have not decreased the safety of the railway system controlled by the computer-based interlocking system.

Thus a need for a mothod of validating software embedded in electronic interlocking systems was required by the South African Transport Services. The research described in this dissertation was sponsored by the South African Transport Services in order to develop such a validation method.

## 1.2 Statement of the Problem

"The computer's messed it up again!" "It's not the computer, it's those people who work it!"

These days, most people have at some time or other encountered a computer malfunction or computer-operator

error. These errors manifest themselves in the form of exorbitant water accounts, incorrect bank balances, delayed aircraft schedules and the like. These errors are the errors which arise in "business computers". When these computers are incorrectly programmed or operated, or when they malfunction, the harm they do is to stir-up human emotions varying from irritation to frenzied anger.

There is another class of computers whose consequences of failure from malfunction or incorrect programming are far more dire. These are the "life-critical embedded systems" - the computers that steer aircraft, route trains, monitor nuclear reactors and perform a host of other life-critical functions. These computers simply must not fail. They must do exactly what their users intend them to do, even if they have been programmed to do otherwise! Therein lies the dilemma.

In the world of real-time process-control, a computer is empolyed to do a specific job and nothing else. Two grey areas immediately become apparent. How does one exactly specify the job the computer is to do and how does one precisely translate that job specification into a computer-executable programme? The extent to which these duties can be correctly performed determines the extent to which a computer will do what it is required to do.

With any method of specification and translation, one aims to ensure that the specification exactly represents the requirements and that the programme, translated from the specification, exactly represents the specification. This is the crux of software validation.

Whatever the form of the programme and however it was generated, it must be shown to meet its requirements, whatever form they too, may take. This is the ultimate goal of validation. In the real world, however, infinite variations of programming style and technique render this task impossible.

Where validation of programmes is essential, programmes must be written in a way which will facilitate their validation. The use of haphazard control-flow and "sneakv", elusive data manipulations renders validator's task extremely difficult and eliminates the possibility of automatic analysis of programmes. An automated or semi-automated validation technique requires that programmes be written using only allowable constructs and forms of data-manipulation. This places restrictions on programmers, but in the words of C.A.R. Hoare, "...and simplicity is the unavoidable price we must pay for reliability!" (Hoare [1975] p. 533).

Software is generated for many very different applications. Each different application requires programmes to be written to suit that application.

Therefore, programmes are written in a variety of languages and using a variety of data-manipulation techniques, from low-level bit-manipulation to highlevel mathematical computation. Therefore, no single validation technique can be expected to be universally applicable. For a particular application, a validation technique must be found which is most suited to the type of software and to the software generation process used in that application.

Software written for the control of real-time processes, such as those performed by an electronic

interlocking system, must cater for such things as bitmanipulation and critical timing. In this field, software is often produced as hand-written assemblylanguage code or compiled from languages allowing lowlevel manipulation. In railway signalling, fail-safety is of prime importance and so validation of any software for an electronic interlocking system is essential. However, no convincing techniques for validation of low-level programmes exist. The techniques normally used are those borrowed from other areas of application - techniques which were developed with different validation goals in mind.

A survey was conducted of available publications on the subject of software validation, verification and testing (Chapter 2). Almost all publications referred to static code-parsing and dynamic testing of programmes written in high-level languages. Where authors and researchers referred to validation throughout the life-cycle of software, this too, was only up to the point of high-level language generation.

No references were found to the validation of assembler language or machine-code programmes with respect to a higher-level language or specification. No references were found even to the analysis of assembler language or machine-code programmes in environments where no high-level language or specification exists.

It was therefore decided to conduct research simed at developing a method of validating embedded software with respect to a higher-level language or specification.

1.3 Direction of Research

The aim of software validation is to demonstrate the

consistancy between a computer programme and the user requirements. In the generation of software, the extremes of the generation process are marked by user requirements at one end and machine-code at the other. The translation of the user requirements into machinecode is far from standardised, although some common stepping-stomes are in use.

From the requirements, some form of programme specification is usually drawn-up. This is typically a formal statement of what the programme must schieve. It may or may not include information on how the programme is to achieve its goal - the important aspect of the specification is the exact definition of the goal. In a contractual context, the programme specification is often the dotted line between a user and a supplier of software.

The specification, if it is not already in the form of a high-order-language, is translated into a log derlanguage and then processed by a compiler to the machine-code. A typical software generation produce is shown in figure 1.1 overleaf.

In the generation of software for railway signalling and other critical fail-safe applications, the levels of high-level-language and intermediate-language are often omitted. The specification is translated by hand to assembler level and then processed by an assembler to produce machine-code. This is done to gain the advantage of bit-manipulation at the assembler level and sometimes too, for reasons of code length.

In order to validate a programme generated by the procedure shown in figure 1.1, a method is proposed whereby the generation procedure is reversed. The proposed procedure begins at the level of the machinecode programme. This programme is then translated backwards through the various levels shown in figure 1.1 until it is at the level of the user requirements.

The proposed validation procedure would thus have generated a set of user requirements derived from the machine-code programme itself. If the user requirements thus obtained can be shown to be consistent with the original user requirements used in the generation phase of the programme, then the programme would have been shown to correctly implement the original user requirements.

Unfortunately, user requirements are not usually formally stated. They normally take the form of

informal human language statements about what is required. The level of the programme specification is normally where formality is first encountered.

Since user requirements are normally informally stated, validation of the programme specification with respect to the requirements is a matter of manual interpretation, involving checks for completeness, consistency and unambiguity.

The research described in this dissertation was directed towards validating machine-code with respect to its high-level specification. Since the high-level specification can be formally stated, automation of the validation process is possible. One of the major aims of this research was to show how this process could be automated.

#### 1.4 Scope of Research

Programmes and specifications take on many forms. In attempting to develop a validation method involving a programme and its specification, the first question must be: what type of programme and what type of specification?

# 1.4.1 Programme

A high-order-language programme suffers many manipulations and changes of appearance before it can instruct a central processing unit. It is compiled or interpreted; library functions and routines are called and linked; lower level representations such as P-code or assembler are generated and only finally is a string of executable instructions produced. To assume that a high order language is an exact representation of the instructions which will be given to a central processor is to ignore the fallibility of these manipulators and their operators.

The validation philosophy proposed in 1.2 involves analysis and upward-translation of machine-code to prove its consistency with a high-level specification. Input to the proposed validation procedure is thus machine-code. This has the additional advantage that embedded software which was written without reference to a specification can be subjected to the same analysis and upward-translation processes. This will greatly assist understanding of such software when necessary, for example when a modification is to be made to the software.

It is also intuitively correct that the level at which a machine executes instructions should be the end of the generation phase and beginning of the validation phase of those instructions.

#### 1.4.2 Specification

Nany methods of software specification are in use, for example SPECK (Quirk (1983)), PSL/PSA (Teichroew and Hershey (1977)), SADT (Ross and Schoman (1977)) and ESPRESO (Ludewig (1881)). In the railway signalling department of the South African Transport Services, the software specification method in use is P-notation (Young (1980)).

9

P-notation is of a lower level than most other specification languages or methods, being roughly at the level of a high-level-language such as Pascal. This level of specification language was chosen by the

signalling department because it is used to specify programmes which are then coded directly from it as hand-written assembler.

P-notation, as presented by Young, was found by programmers in the signalling department to be inadequate in certain areas, particularly those of data-type specification and Boolean variable handling. Thus, as it is used in the signalling department, P-notation is a modified version of Young's original P-notation. A description of P-notation, as it is used in the signalling department is contained in Appendix B.

It was not within the scope of this research to assess the effectiveness of modified P-notation for application in the signalling department, nor to compare it with other specification languages in use. Since it is already in use in the department and found to be effective by programmers, modified P-notation was selected as the specification language for use in this research.

# 1.4.3 Automation

Programmes are often long. Humans make mistakes. In fact, the longer programmes are, the more likely are human validators to make mistakes.

Whatever guise a validation method may take, it is likely to possess the attributes of rigour and repetitiveness. This will render it tedious and time-consuming for human execution. Automation should thus be a major consideration in the development of any validation method or procedure. Errors which would inevitably arise in manual validation exercises would

0

also be avoided.

One of the majo, quels of this research was thus to automate the projected validation procedure wherever possible, or at least to demonstrate that it could be automated.

## 1.4.4 Stated goal

The goal of this research was to devise a mathod of showing a machine-code programme, as executed by a microprocessor, to be consistent with its specification in P-notation. Maximum automation of this process was of prime importance.

# 1.5 Overview of Dissertation

The need for an effective method of validation of software for fail-safe, real-time process control systems was the motivation for the research presented in this dissertation.

A software validation method has been proposed which is a reverse of the typical software generation process.

The proposed method is based on the hypothesis that each stage of the generation process can be validated by translation of its product to the level of the product of the previous stage and validating by comparison. For example, a high-level-language programme can be upward-translated to the level of its -specification and compared with the specification. This would validate the specification-to-high-levellanguage-programme translation stage of the generation process.

Since user requirements are normally informally presented, the reverse translation, or validation of a programme specification against these requirements, is also an informal process. However, since a programme specification can be formally presented in a specification language, software generation processes from that level right down to machine-code can be formally validated by the proposed method of reversetranslation.

The research presented in this dissertation was aimed specifically at software for the electronic interlocking systems used in railway signalling, where assembler language programmes are often generated directly from their high-level specification. These assembler language programmes are then projessed by an assembler to produce machine-code. It was to be shown that these two processes could be validated by the proposed method of reverse-translation. Automation of this validation method was also to be investigated.

A description is given of a guinea-pig microprocessor system, the process of tracing its operation and manipulation of the resultant traces to form 3 complete disassembly listing of the system's embedded software.

Nethods of automatic control-flow and data-flow analysis of the disassembly listing are described and their operation is demonstrated by using sample portions of code. These analyses are done in preparation for translation of the disassembly listing into P-notation.

Final formatting of the programme to P-notation format is then described. This essentially involves controlflow formatting and variable-name insertion.

Finally, an analysis of the overall effectiveness of the proposed validation method in terms of the goal of the research is given. Conclusions drawn as a result of the research are presented.

## CHAPTER 2 LITERATURE SURVEY

A survey was conducted of available publications on the subject of software validation, verification and testing. Nost publications present generalised approaches to software and are, as such, not specifically relevant to the reliability of software within embedded systems. However, it is precisely this shortcoming which renders these publications relevant to the history of validation.

# 2.1 Survey of publications

By 1975 the poor reliability and high cost of large software systems was becoming a serious problem. Formal proof of programme correctness was thought to be infeasible or at least many years away and manual testing and code inspection of large systems were, in them.eives, unreliable and costly.

Some automated analysis tools and software evaluation systems were in use at the time and Ramamoorthy and Ho (1975) described these as the most effective means of improving the reliability and reducing the cost of large software systems. Automated tools were capable of checking the presence of certain software attributes such as syntactic correctness, proper control structuring and module interfacing.

"Software evaluation systems" were defined as composite systems of automated cols for the purposes of system design analysis, debugging, testing and partial validation, that being the process of demonstrating the validity of a programme to an acceptable degree of reliability and performance.

#### Fage 15

Ramamoorthy and Ho also described the software evaluation systems in use at the time as only partially fulfilling their requirements in that they analysed the source code, but generally ignored the design and specifications.

Miller [1977] proposed a method of path-based testing and showed how a test coverage measure could be used as a measure of "how far the testing process has gone".

Testing a programme by running it on sets of test data had, until 1975, not been regarded as an effective validation method, since sets of test data were generated on an ad hoc basis by analysis of the internal structure of a programme only. Goodenough and Gerhart [1975] proposed a more rigorous method of test data selection. They proposed a "condition table" method of deriving test predicates. Test predicates describe what aspects of a programme are to be tested. Derivation was done by reference to the general requirement a programme was to satisfy, the programme's specification and the general characteristics of the implementation method used.

Admitting that exhaustive testing WAS rendered such time-considerations as impossible bv human mortality, Goodenough and Gerhart hypothesised that the input domain of a programme could be partitioned into a finite number of equivalence classes such that a representative test for each class would, by induction, test the entire class. They did, however, point out that the fundamental problem of testing was the inference from the success of one set of test dats that others would also succeed and that a problem with equivalence class testing was to show that the input domain partitioning was, in fact, appropriate. They suggested that their rigorous test case generation

method led to a better approximation of exhaustive testing and, used in conjunction with programme correctness proofs, significantly decreased the likelihood of programme failure.

While Goodenough and Gerhart were testing programmes by running them on sets of test data, Allen and Cocke (1976) were proving the integrity of data-relationships within a programme without execution of the programme. Their algorithmic approach used a control-flow graph representation of the programme and information about the data items used, to determine the data-flow relationships within the programme.

King [1976] was not convinced. He considered programme testing and programme proving as extreme alternatives and introduced the concept of symbolic execution, which he regarded as a practical approach between these two extremes. He developed SFFIGY, an interactive symbolic execution system for language statements in PL/I-style syntax. In EFFIGY, a user could define arbitrary identifiers to be symbolic programme inputs in place of specific integer constants and analyse programme behaviour by inspection of the resultant expressions generated by symbolic execution.

è.

A further practical implementation of the concept of symbolic execution was provided by Clarke (1976]. She presented an interactive system for automatic test data generation to execute a specified path of an ANSI-Fortran programme and subsequent symbolic execution of that path. Her system also provided the facility for detection of nonexecutable programme paths.

Based on King's EFFIGY, the SELECT symbolic execution system devised by Boyer, Elspas and Levitt, and Clarke's ANSI-Fortran symbolic executor, Howden [1977]

developed the DISSECT symbolic testing system. The major advantage offered by the DISSECT system over previous systems was the command-file facility whereby a user could initially set up a series of executions to be performed, some conditional on others if desired, for any specified paths and with any combination of symbolic and real input values. As with Clarke's system, DISSECT was ANSI-Fortran specific.

In a case study of the effectiveness of various analysis and testing techniques, Howden [1978] applied the techniques six sample to programmes containing "naturally" occuring errors. He found that the use of symbolic testing resulted in an increase in reliability of 10-20 percent over testing on actual The increase was, however, reduced to 3-4 data. percent if "actual data" testing was augmented with other programme analysis and testing techniques such as special values and interface analysis. He showed that in most cases, one particular analysis or testing technique was more effective than the others in pinpointing a particular type of error and his overriding conclusion was that no single programme analysis technique or programme testing strategy should be used to the exclusion of all others.

In the midst of the massive drive to automate the validation process, work was still being carried out on the development of more reliable manual validation techniques for use in environments where limited resources were available. The coupling effect, whereby most global errors such as failure to satisfy a particular specification are seen as being coupled to simple errors such as missing control paths, was exploited by De Millo, Lipton and Sayward (1978]. They based a series of "hints on manual test data selection" on the hypothesis that test data which distinguishes

all programmes differing from a correct one by only simple errors is so sensitive that it also implicitly distinguishes more complex errors. Branstad, Cherniavsky and Adrion [1980] also proposed a streamlining and improvement of manual validation techniques throughout the development life cycle by testing, code reading and inspection, and independent reviews.

While referring to the various validation tools available at the time, Meyers [1979] too, proposed rigorous manual validation techniques and testing with carefully chosen test cases as being the most effective. His choice of test cases was based mainly on boundary-value analysis and caus-effect graphing.

ø,

The selection of test data had, for the most part, always been based on the internal control structure of a programme. Howden (1980a) proposed a "black box" approach to programme testing in which the internal structure of a programme was ignored during test data selection. Tests were constructed from the functional properties of the programme that were specified in the programme's requirements. The technique was known as functional testing, as opposed to structural testing.

Howden described the disadvantage of the black box approach as the fact that it ignored important functional properties of a programme which were part of its design or implementation and which were not described in the requirements. A case study involving a collection of scientific programmes led to the predictable conclusion that structural and functional testing were complementary rather than competing techniques.

Testing was still accepted as being more effective than formal programme proof in the demonstration of

programme correctness. Formal representation of specifications was viewed as so problematical as to be of little practical value. Formal proofs could not be used with the informal specification methods in use at the time. Kopetz described the specification methods in use as "verbal specification of software systems outside the areas of logic or numerical mathematics" (Kopetz (1979)).

Deutsch [1979] was sceptical about both testing and proving of programmes as effective means of increasing their reliability. Reduction of the complexity of programmes, he believed, would increase productivity, clarity, maintainability and modifiability.

Various papers were produced on the theory of test data selection for revealing particular types of error. Weyuker and Ostrand [1960] found Goodenough and Gerhart's [1975] theory of test data selection difficult to apply in the real world and proposed certain modifications to the theory whereby they set semicorrectness-proving a their goal. Proving semicorrectness meant demonstrating the absence of certain errors rather than the ideal proof of correctness, which meant demonstrating the absence of all errors.

White and Cohen [1980] developed a method of testing specifically to pinpoint control-flow errors and the conditions under which their method was reliable were carefully specified. Gustafson [1984] proposed testing for errors whose necessary input conditions were more likely to occur and for errors whose consequences were serious. His test case selection was based on what he called the "cost of errors".

ŝ

A consolidation of software analysis and testing techniques as developed up to 1980 was provided by

Howden [1980b] when he applied various existing testing and analysis methods to a package of Fortran He divided the methods used into two subroutines. distinct categories: static analysis methods and dynamic testing methods. Static analysis methods referred to methods which were performed without actual execution of the code. Dynamic methods consisted essentially of testing and were performed automatically, except for the selection of test data. Test data was selected with a view to both structural and functional testing as previously described (Howden [1980al). Static analysis methods consisted of automatic methods such as path flow analysis and statement analysis and manual methods which mostly involved checking consistency between subroutine headers and programme or requirements content. Кe concluded that the methods used could discover "a large majority" of errors in programmes of the type used. He found that testing (static and dynamic) and analysis methods were equally useful, each responsible for the discovery of about half the errors found. He indicated the need for extensible static analysis systems which allowed for the addition of further static analysis also stressed the importance of the rules. Нe development of a method to identify and test general and detailed design functions.

Carré [1980] described the principle methods of validating programmes as flow analysis (control-flow and data-flow analysis) and semantic analysis. He described a systematic manual method of control-flow analysis involving a methodical labelling technique to show such control flow anomalies as black holes and unused labels.

٩.4

In data-flow analysis, Carre's detection of undefined variables and unused definitions was based on

algorithmic processing of sets of binary vectors representing variable-definitions within the programme. His method of semantic analysis was twofold. Assertions, derived from programme specifications, were inserted into the programme and manually processed using the programme logic and computation statements. A systematic technique was presented to prove that the truth of an assertion at any point followed from the truth of assertions at previous points in the The other aspect of semantic analysis was programme. symbolic execution. He was later to automate and present these techniques as a "validation package" (SPADE, 1985).

Because of the real need to validate large software systems, various validation packages or validation environments were developed after 1980. They mostly used existing techniques such as static code-parsing and dynamic testing, each implementing the techniques an automated slightly dífferentlv in package. Important amonost these were the STRUM system [Patterson, 1981] which concentrated on programmes for microcomputers and a system presented by Benson [1981] which introduced the concept of instrumentation of a programme with "executable assertions". Executable assertions are formal assertions made about the state of the programme variables at various points in the programme. The assertions are presented in such a way that the programme statements can be applied to them to show that execution of the programme would not violate any of the assertions.

The practice of translating a high-level source language into an intermediate language more suited to validation techniques had been instituted as sarly as 1975 (Ramamoorthy and Ho [1975]). No further development of the technique took place until it was

again used in the IVTS system [Taylor, 1983].

The IVTS system (Integrated Varification and Testing Sytem) was designed specifically for use on HAL/S, a used mostly in aerospace applications. language Although IVTS used standard established validation techniques, its advantages over other integrated validation systems were a very sophisticated user interface, making application of any of the techniques simple for unqualified personnel, and the incorporation of an automatic "report writer" for documentation The major advantage of the use of an enhancement. intermediate language is that it renders the tools used non-source-language-specific. All source languages are translated to the same intermediate level and are thus able to be processed by the same tools. This feature was exploited by Carré in his validation package [SPADE, 1985].

Software fault tree analysis, the hypothesising of a occurring and particular fault subsequent "backtracking" through the software to discover all possible causes of the fault, was introduced by Taylor [1982] and used in a practical impl-mentation by Leveson and Harvey [1983]. Taylor presented a proposed method of automating the procedure, but to date not much interest has been shown in the analysis method. The lack of interest has been due to difficulty in handling loops and the size of trees generated for most hypothesised faults. The method can be, and sometimes used for analysis of some highly-critical is, individual possible faults, but has little general application.

In the early ninteen-eighties, there was an increasing awareness that validation of programme code with respect to its requirements was only one facet of

validation in general. It was realised that design errors discovered as late as the coding stage were expensive to correct. Thus, validators began to realise that validation techniques had to be applied throughout the life-cycle of the software (Rzevski [1961] and Howden [1962]).

Validation techniques applied to software requirements and specifications were those related to checking consistency, completeness and correctness. Howden [1982] proposed the selection of test cases throughout the software life-cycle, including the requirements and specifications definition phases.

An in-depth survey and evaluation of the existing techniques of validation, verification and testing of computer software was conducted by Adrion, Branstad and Cherniavsky [1982]. To say the least, their conclusions were controversial. Because most validation and testing techniques were applicable to the testing of actual programmes and had little other relevance through the life-cycle of the software. they concluded that traditional, manual validation methods were most effective. Such methods included walk-throughs. reviews and inspections. Traditional manual methods could be used without massive capital expenditure and had uniform applicability throughout the software lifecycle, although they required a serious commitment and disciplined application. They also concluded that most existing automated validation techniques lacked a sound theoretical basis.

Thus it was that, where validation was of critical importance in the development of real systems, validation techniques used were still essentially manually orientated, involving massive human effort (eq. Short [1983]).

In a recent publication, Gerber (1985) described the techniques which were used to validate a large, realprocess control programme. Modules time were individually validated by test cases and automatic integration and module-interface (inter-module data flow) analysis were performed. Functional analysis was manually performed by cross-referencing of the documentation. Timing analysis, too, was manually performed by doing a series of time-related calculations based on the programme code and showing that the programme would always operate within its specified timing constraints.

# 2.2 State-of-the-art

The previous section has given a general history of developments in the field of software validation since 1975, by reference to, and resumes of, significant publications. During the period from the mid- to lateninteen-seventies, the emphasis was on developing the ability to analyse and test high-level language programmes which performed arithmetic and logic functions. Much mental effort and practical trial went into this development and a sound basis for further development was created. Noteworthy were papers by Ramamcorthy and Ho [1975], Goodenough and Gerhart [1975], King [1976], and Howden [1978], The original motivation for the development of this analytical and testing ability was a so-called "software crisis" brought about by the low reliability and consequent high cost of software. The objective was to improve software reliability to a level where the cost of its generation and implementation were acceptable.

Within the context of the above motivation, it can be argued that early work in the field of software

analysis and testing was extremely successful.

Sumi-correctness (correctness up to an acceptable level of reliability) of programmes was achieved both by validation techniques and by design-for-validation techniques. Even to this day, programmers writing computational programmes can use established validation techniques to improve the quality and reliability of the software they produce.

After the late nineteen-seventies, however, a branch of computer usage which had been slowly developing for some years, very quickly became an important aspect of computing technology and usage. The microprocessor was to be used in real-time process control applications involving the risk of the loss of many human lives, such as in nuclear-reactor monitoring and transportsystem control. Validation needs changed; the science of validation did not.

The goal of validation changed from "partial validation for increased reliability" to "complete validation for complete reliablity". Not only did the goal change applications of software also changed. Real-time applications involve aspects that were not previously considered in validation philosophies such as stringent timing constraints and the cyclical nature of real-time programmes. Emphasis changed from arithmetic/ programmes high-level-language t٥ computational programmes involving many and varied I/O routines and bit-manipulation, often written in low-level languages.

A summary of techniques available and in use for the validation and verification of real-time software was provided by Quirk [1985]. His book contains a comprehensive bibliography of relevant publications.

A significant contribution to the assessment of the state-of-the-art of software validation and verification was made by the third Verification Workshop (VERkshop III [1985]), held in California.

The principal goal of VERkshop III was to review verification technology and, in particular, to identify what was being used in practice and what specific areas required additional research. The attendees included researchers who were active in the development of verification systems, theorem proving, formal language semantics and applying current verification techniques to production problems.

Although four years had passed since the previous Verification Workshop (VERkshop II), there was a consensus of opinion that only incremental progress had been made in the area of programme verification. It was agreed, however, that using existing methods and technology, significant progress had been made in the development of integrated verification systems, although the systems were still usable only by highly skilled individuals and were not in a position to be used on a production basis.

A stagnation in the abilities of validation techniques has been brought about by the application of analysis techniques to software which has different validation requirements from those ich motivated the design of the analysis techniques. All divelopments in validation since 1980 have essentially been refinements of the original techniques developed by validation joneers such as Ramamoorthy and Ho [1975] and King [1976]. The fundamentals of validation as a science must be re-addressed in order to develop new, more applicable validation techniques to meet new validation demands.

Thus it felt appropriate to undertake an was exploratory project to show the validity of the validation procedure proposed in the previous chapter. The proposed validation procedure would meet the validation demands of a computer-based railway signalling system and many other applications of computer-based control systems.

10

### CHAPTER 3 DISASSEMBLY

The validation procedure proposed in chapter one of this dissertation consists of analysing a machine-code programme executed by a microprocessor and translating the programme up to the level of its high-level specification. The translated programme is then compared with its original specification.

In this approach, no assumptions are made about the correctness of assembly-language listings supplied by a manufacturer or programmer. The machine-code programme is obtained directly from the microprocessor itself. Actual operations executed by the microprocessor, as a result of instructions fetched from PROM, are used to reconstruct the machine-code programme. Validation is thus ensured from the lowest possible level - that of the effect of the software on the microprocessor chip.

The operations of a microprocessor are traced by a logic analyser whilst external stimulus is given to the microprocessor system to force the software to traverse every one of its possible paths. All traces thus obtained are combined and edited to form a complete diseasembly listing of the programme. This diseasembly listing is then subjected to subsequent analysis and translation procedures.

The method of obtaining a disassembly listing of a machine-code programme was demonstrated by practical trial. The test set-up used and experimental procedure followed are described in this chapter.

### 3.1 Test Set-Up

### 3.1.1 Guinea-pig microprocessor system

A method of producing a disassembly listing from a microprocessor-based system has been proposed. To test the proposed method, a guinea-pig microprocessor-based system was required. One such system, the "TEM L 30 Block Instrument Controller" (TEM L 30 Block Instrument Control Unit, A Technical Description (1983]), was available in the Signalling Department of the South African Transport Services, where the research was undertaken. This system was selected so as to provide a test-bed which was a true representation of the application area being addressed in this current research investigation.

In railway signalling, a "block instrument," is an electro-mechanical device which is used to solve durant of forward or reverse polarity down a pair of wires to another block instrument. It also indicates the presence and polarity of any current it receives from any other block instrument. A more detailed description of a signalling block instrument can be found in Appendix A.

The "TEN L 30 Block Instrument Controller" is a microprocessor-based control-unit designed to facilitate the operation of block instruments over radio links, instead of over wire-pairs. The task performed by the TEM L 30 controller is the bidirectional, fail-safe transmission of information, between two block instruments, over a radio link. A more detailed description of the TEM L 30 controller can be found in Appendix A.

### 3.1.2 Tracing the microprocessor operations

Tracing was done with the State-6 Analyser option of an HP64000 measurement system (HP64000 Logic Development System, System Overview [1962]). The system offers instant disassembly, mass storage of traces on its associated disc, sophisticated triggering and storage specification facilities, printing of traces for documentation purposes and uploading of traces to a minicomputer for manipulation.

### 3.1.3 Stimulus of the device

The TEM L 30 was required to traverse every possible path of its programme while its operations were traced by a logic analyser. In order to ensure that all possible paths had been traversed, the contents of the programme-PROM were listed. A check was made to ensure that there were no programmed PROM locations which did not appear in any of the logic analyser traces.

Certain paths of the TEM L 30 software are not traversed during normal power-up, quiescent operation or power-down. They are the paths associated with the operation of one or both of the block instruments causing message-transmission, hardware-monitoring with associated failure strategies and message-reception with subsequent output to the block instruments. In order to cause the TEM L 30 controller to traverse these paths of its programme, it was necessary to provide external stimulus to the TEM L 30.

# Operation of the block instruments

Block instrument simulation was realised by means of

two block instrument simulators supplied with the controller for testing purposes. The simulators r'mply provide the ability to source current of "sither polarity to the controller by manual pushbutton operation.

### Hardware-monitoring and failure strategies

The actual monitoring of the condition of the hardware is a routine operation when the controller is in a powered-up state. It was, however, necessary to simulate hardware failures to force the software along the paths of its failure-strategies. Such hardware failures were easily simulated by false feeds, component removal, supply voltage adjustment, etc.

#### Message reception and analysis

A radio simulator was provided with the controller for testing purposes. The simulator simply injects noise into a physical connection between the modem cards of two TBM L 30 controllers. This creates the effect of the operation of the modems over a radio link. Another controller could, therefore, have been used to send a valid message via the radio simulator to the controller under test.

The normal, operative interaction of the two controllers, however, forms a small part of their message-handling routines. To force the TEM L 30 controller to traverse all possible programme-paths related to message-analysis, it was necessary to transmit to the controller under test messages with incorrect parity, faulty Manchester II coding, less than three messages in agreement, etc. The easy

manipulation of messages to be sent was thus an important criterion. A programmable microprocessorbased data acquisition and transmission system was used for this purpose. This microprocessor-based system was developed by engineers of the South African Transport Services and is known as a Remote Data Unit (RDU).

The modem card of a second controller was used to interface, via the simulated radio link, to the controller under test. Control of the modem card, interactive message-compilation and messagetransmission were realised with the RDU.

Programmes were written on the RDU to perform the various message-generation tasks and were executed by the RDU as compiled Basic programmes.

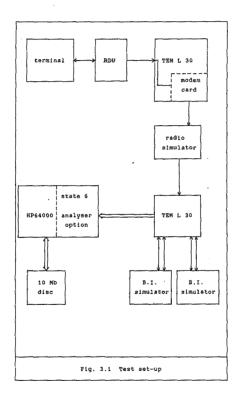

The complete test set-up which was used to obtain the traces is shown in fig. 3.1 overleaf.

#### 3.2 Trace-Specification

Before any of the traces were executed, a tracespecification document was produced. This document showed the address trigger point to be set up on the HP64000, the section of code to be stored and the stimulus to be applied to the TEM L 30 for each trace The trace-specification to be executed and recorded. document was produced by reference to the TEM L 30 manufacturer's software listing, circuit diagrams and description of operation. Any errors or omissions in these manufacturer's documents would have become apparent when actual execution of the traces was attempted. A sample portion of the complete trace specification document is shown in figure 3.2.

30

33

10.00

Con Signation

• (

-

|       |          |        |        | ·2-1-4-12      | 0.1.6.99010.2009000.0010.0110.1019.02000.10.00911 |

|-------|----------|--------|--------|----------------|---------------------------------------------------|

| Tree. | Trig and | Addit! | Sat.   |                | Stimulus to test rig                              |

|       |          | Hen    | Sie.   | Gagur.         |                                                   |

| 142   | C928     | Coas   | 2704   | ( š            | i Sand valle enscope to 124.30                    |

| 140   | 2943     | 6970   | 6070   |                | Gene wealage with any no failure                  |

| 169   | 5949     | 6064   | 000    |                | trate 144 - H2 feilurs in fixed part              |

| 170   | 2991     | COEL   | 6800   | ·····          | ref, iren 149                                     |

|       | C760     | 6942   | CHER   |                | trate 142 - HS fatture in warjable part - LP23    |

|       | 6290     | 6910   | TYAS   |                |                                                   |

|       |          |        |        |                | trace idd - H2 fellune in veriable part - LPGL    |

| 173   | C100     | CICA   | 0009   | l              | ref, 1769 172                                     |

| 174   | CPOL     | 6023   | COID   | £              | raf. ireda 172                                    |

| 175   | C104     | CICA   | 5636   |                | ( eef, tradu 172                                  |

| 176   | C+07     | 6004   | CEID   |                | (a), 17463 173                                    |

| 155   | 2005     | 1.53%  | 6007   | 1              | ret. trans 167                                    |

| 171   | CHEA     | COTT   | 000    |                | raf, 17464 147                                    |

|       | C367     | Crac . | 6007   | ] <del>;</del> | ref. treta 147                                    |

|       |          |        |        |                |                                                   |

| 150   | C977     | COCI   | 6800   |                | ref, trans 147<br>ref, trans 147 - to 1923        |

| 202   | CPFA     | 0342   | CA7F   | 1              |                                                   |

| 101   | CIFE     | CHE    | 6609   | 1              | Send measure with loanersai parity                |

| 192   | CAN      | COLL   | COND   |                | Sang measure with incorrect parity                |

| 104   | CADO     | CASZ   | 6440   | ·              |                                                   |

| ***** | CANF     | Calo   | 6836   |                | Sent mess, to Loga then to Logi                   |

|       |          | 6004   | 1 2010 |                | Sand meas, to LP23 then to LP01                   |

|       |          | 6435   | 1000   |                |                                                   |

| 147   |          |        |        |                | Send another measure during decode - LP42 -       |

| ted   | CASE     | COCI   | CDEO   | 1              | Sena enether message during decode - LP01         |

| 164   | CA4F     | CA-LO  | DC3C   |                | Send Let 2 meas, with different polarily          |

| 114   | CAST     | 4032   | C010   | 1              | raf, ireca 10P                                    |

| 101   | CAFA     | 60.00  | 1000   | ·····          | ral, 17653 167 - UP31                             |

| 142   | Ca26     | 1 6661 | Coio"  |                | 1 Fef. 1/484 147 - LP61                           |

|       |          | 1.6457 | 1 2415 |                | ref. ireda 167 - 16 1723                          |

| 192   | CH//     |        |        |                |                                                   |

# Fig. 3.2 Portion of trace specification document

3.2.1 Trace-Specification Document

### Trigger-occurrence

It will be seen that the trace-specification document (figure 3.2) contains a column headed "occur.". This specifies the occurrence of the trigger-point address on which the analyser must trigger: first or second. Triggering on the second occurrence was specified in order to trace through a section of code ended by a branch instruction back to a point within that section. This was preferable to triggering on the branch instruction itself, since it showed that the code was actually taking that particular branch of the decision.

Percent

#### Trigger-on-opcode

What is not apparent from the trace-specification document (figure 3.2) is that triggering was not initiated on the occurrence of a particular address alone. The TEM L 30 does regular inter-processor PROM comparisons and so a particular address may appear on the address bus for the purpose of a data-read from the PROM. Triggering was desired only in the case of the correct address being present <u>and</u> an opcode being fetched. This was specified for all triggering conditions.

### 3.3 Production of the Disassembly Listing

Production of the disassembly listing consisted of two phases.

Firstly, each of the test runs specified on the trace specification document was executed. All the trace listings obtained were stored as files on the HP64000 measurement system's local disc.

Secondly, all files thus obtained were uploaded to an HP1000 minicomputer, where they were edited and sorted by absolute address to form the complete disassembly listing.

# 3.3.1 Obtaining the Traces

## Providing the stimulus

The stimulus to be applied to the TEM L 30 controller to obtain each trace was determined from the tracespecification document. Some stimuli consisted of

initial conditions to be set up (eg. removal of a fuse), while others were actions to be taken during operation of the device (eg. operation of one block instrument during servicing of the other).

# Tracing the test runs

Triggering and storage conditions for each test run were set-up on the measurement system. Once the trigger had been enabled and the measurement system was waiting to trigger, the TEM L 30 controller was powered-up as specified in the trace-specification document. On completion of storage, the trace obtained was stored on the measurement system's disc.

### 3.3.2 Manipulation of the Traces

Uploading the files to a minicomputer

All the traces which were stored as files on the measurement system's disc were uploaded to an HP1000 minicomputer for editing, sorting and analysis.

Since all files were to be concatenated for sorting and analysis, the large virtual-RAM capacity of the minicomputer was required for this purpose.

#### Editing and sorting the traces

Pascal programmes were written and run on the HP1000 minicomputer to edit and sort the traces into a complete disassembly listing. A sample trace-file is shown in figure 3.3.

. 6

Trace List Label: ADDRESS Base: ADDRESS 64620 State Analyzer Man, 10 Jun 1985, 11:38 State 6, 60 channel, 6800/02 interface 6800/6802 Maa ADDR\_MAP HUDR\_MAP SNE CC2A UDA 2002 20 operand fatch 20 operand fatch 10 mmry read SNE cc24 10 mmry read 10 mmry -002 -001 trigger +002 +003 +005 +005 +005 +005 opprand fotch ANF9 5TAB 5TAB 200 PUL09 PUL09 PUL09 RTSC1 2F 002 operand fatch operand fetch 114567890 stack read stack read stack read Fig. 3.3 Sample trace file AC16 LDAB F003 AC17 EGRB 4F003 AC18 STAB F003 AC19 STAA X AC19 STAA X AC14 CHPA 4F008 AC18 SGT AC20 AC1C LDAA F001 AC1D DRAA F009 AC1F BRA 1024 AC18 F004 F001 AC1F BRA 1024 AC20 LDAA F001 AC20 LDAA F001 AC21 COMA AC22 ANDA F009 AC23 STAA F009 AC24 LDAA F009 AC24 LDAA F000 AC25 LDAA \$F000 AC26 CMPA F001 AC26 BLT AC2A AC29 LSRB AC29 LSRB AC29 LSRB AC29 LSRB AC29 LSRB AC2A LDAA F002 AC2B ANDA \$F00B AC2C ABA AC2D SYAA F002 AC2E BRA AC01 Fig. 3.4 Sample disassembly listing

ware water in the state to be assessed in the

'n

These trace-files were first individually edited to remove the unnecessary text at the head, triggering information and data-reads and writes. All the resultant edited trace-files were then concatenated to form a single file. All duplicated statements were removed and the file was sorted by absolute programma address to form a complete disassembly listing. A sample fr the resultant listing is shown in figure 3.4.

#### 3.4 Result of elsassembly

A method of deriving a complete disassembly listing of a programme executed by a microprocessor has been described.

The method essentially involves tracing the operations of the microprocessor with a logic analyser while the microprocessor system is externally stimulated to execute every path of the machine-code programme. Resultant traces are manipulated to form the complete disassembly listing.

The actual disassembly of machine-code instructions is performed by the logic analyser. If required, the integrity of the disassembler can be demonstrated by re-assembling the resultant disassembly listing and comparing the result with the original machine-code.

The analysis and translation techniques described in further chapters are aimed at demonstrating the consistency between a machine-code programme and its Pnotation specification. Since the machine-code programme of the TEM L 30 was not written from a Pnotation specification, the programme will not be subjected to such analysis and translation.

Assembler listings of the same format as the TEM L 30 disassembly listing which were written from *P*-notation specifications will be used to demonstrate these techniques. It will, however, be shown how the techniques developed can greatly assist the readability and understandability of a disassembly listing such as that obtained from the TEM L 30.

Further chapts is describe how a disassembly listing can be analysed and translated to the level of its Pnotation specification. This process begins with control-flow analysis, described in the following chapter.

### CHAPTER 4 CONTROL-FLOW ANALYSIS

The previous chapter described a method of deriving a complete disassembly listing of a machine-code programme. In order to translate the listing thus obtained into P-notation, it was necessary to analyse the listing in terms of control and data-flow. A method of analysing the control-flow of a disassembly listing in terms of standard P-notation constructs is presented in this chapter.

# 4.1 Constructs in P-notation

P-notation supports constructs in the three broad categories of sequence, selection and iteration.

#### 4.1.1 Sequence

Sequence refers to the top-down sequential execution of programme statements. If a statement does not explicitly transfer control to some other part of the programme, then the statement below it is the one which will be executed next.

### 4.1.2 Selection

P-notation supports two types of selection construct: the case statement and the if statement. Definitions of these statements can be found in Appendix B.

# 4.1.3 Iteration

P-notation supports three iterative constructs: the

repeat statement, the while statement and the for statement. Definitions of these statements can be found in Appendix B.

# 4.2 Construct Recognition and Labelling

4.2.1 Input and storage of disassembly listing

The control-flow analysis programme provides the facility for the input of any user-specified file containing a disassembly listing of the form obtained from the TEM L 30 (Chapter 3). The listing is stored in a record structure in RAM. Fields of each record contain absolute programme address, opcode, and where applicable, operand.

# 4.2.2 Processor-specific information

A data file containing information specific to the Notorola 6802 microprocessor is referenced by the analysis programme. The data file contains information about whether a particular opcode is a conditional branch statement an unconditional branch statement or neither. For each statement read from the disassembly listing file, branch information is read from the data file and added to the record of that particular statement.

Together with the absolute addresses in the disassembly listing, the branch information from the data file is sufficient to facilitate automatic control-flow analysis of the disassembly listing.

### 4.2.3 First pass: if-then-else and loop recognition

Recognised constructs are numbered sequentially in order of recognition. An internal labelling system is used in labelling recognised constructs. The various elements of a construct are labelled with a characterstring indicating their significance.

So if recognised construct number # is an if\*-then-else construct, the statement beginning the if portion is labelled if\_\_#, the statement beginning the else portion is labelled else# and the end of the construct is labelled comp#. In the simplified case of an ifthen construct, the else# is omitted.

If recognised construct number # is a while do loop construct, then the beginning and end of the loop are labelled whil# and endw# respectively. In the case of a repeat until loop, the beginning and end of the loop are labelled rept# and unti# respectively.

Distinguishing between a for loop and a while do loop is difficult and in any case not always possible. For loops are .ecognised as while do loops. Standard coding of for loops for the purpose of recognition could be added as a refinement of the loop recognition process.

If a branch and 'm destination are not recogniseable in the context of any standard construct, then they are labelled unkn# and endu# respectively.

Using the abbreviations UCB for unconditional branch and CB for conditional branch, generalised implementations of the P-notation standard constructs are given in figure 4.1 overleaf.

Page 43 3 СВ ٠r £ ۱, if portion if-then-else ī исв ٤ }----۶r 1 ł else portion. נ'ז נ'ז<--ſ -1 ι, i CB . 5 if-then ٤ 3 if portion 1 5 1 3 (1) (1) (1) repeat until body of loop test for completion СВ --> [] 3 £ 1 prepare test 1 ٤ 1----CВ while do t 2 ٤ ٦ Т UCB ---- [ [1] [1]

> Fig. 4.1 Generalised implementations of P-notation standard constructs

hady of loop

The algorithm used to recognise the above constructs and label the relevant statements accordingly is shown in Appendix C. The algorithm was implemented as a Pascal programme for automatic construct recognition. A sample printout after the first pass of the analyser is shown in figure 4.2 below.

| if   | CIAE LDAA 00,X<br>1 CIBO DEC CIBC<br>CIBS LDAA 135C<br>CIBS LDX #CO<br>CIBS LDX #CO<br>CIBS LDX #CO |

|------|-----------------------------------------------------------------------------------------------------|

|      | C185 LDX #C0                                                                                        |

| proc | 2 CIBG JSR 04,X<br>CIBA BRA CIDI<br>CIBC CPX #0010<br>2 CIBF BNE CIOS                               |

| if   | CIBC CPX #0000<br>2 CIBF BNE C106<br>CICI CLR 0003                                                  |

| comp | C1C4 LD88 #01                                                                                       |

|      | CICB LDAA #01<br>CICA STAA 0003<br>CICC STAA 1002<br>1 CIDI NOP                                     |

| comp | 1 CIDI NOP                                                                                          |

### 4.2.4 Second pass: case recognition

$\vec{\xi} = \vec{\xi}_{35^{+}}$

If recognised construct number '#' is a case construct, then the statement beginning the construct will by labelled case#. The statement beginning each of the separate cases within the construct will be labelled of\_#.

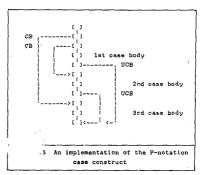

An implementation of the P-notation case construct could take the form shown in figure 4.3 overleaf.

### Page 44

Branching need not have occurred in the order shown. The first conditional branch could have branched to the second case body and the second conditional branch to the third case body, or any other order.

Whatever the order of branching, the whole construct would have been analysed in the first pass of the analyser as a series of overlapping if-then-else constructs. This fact is exploited in the recognition of case constructs by the second pass of the analyser.

The analyser does a second pass of the listing, searching for statements which were marked in the first pass as multiple comp statements. All such statements could form the end of case constructs. The algorithm shown in Appendi/ C is used to determine whether a particular multiple comp statement does in fact form

Page 45

the end of a case construct. The algorithm also marks the relevant statements accordingly if a case construct is recognised.

The number of a recognised case construct is the number of the lowest numbered overlapping if-then-else construct forming part of the case construct.

The algorithm shown in Appendix C was implemented as a Pascal programme. This programme was used to perform automatic case construct recognition.

Figure 4.4 shows a printout after pass two of the analyser. The portion of code which was analysed is seen to contain an if-then construct (construct number 2) nested within the first case of a case construct (construct number 1).

| 0<br>1<br>0<br>0<br>0<br>0 | omp1 C1E3   | LORGA GO ANALASSA CONSTRUCTION OF CONSTRUCT OF CONSTRUCT OF CONSTRUCT OF CONSTRUCT OF CONSTRUCTION OF CONSTRUCTION OF CONSTRUCT OF CONS |              |