# FAULT TOLERANCE IN COMPUTER SYSTEMS

# FAULT TOLERANCE IN COMPUTER SYSTEMS

Michael John Bury

A dissertation submitted to the Faculty of Engineering, University of the Witwatersrand, Johannesburg, for the degree of Master of Science in Engineering.

Johannesburg, 1986.

# DECLARATION

I declare that this dissertation is my own, unaided work. It is being submitted for the Degree of Master of Science in Engineering in the University of the Witwatersrand, Johannesburg. It has not been submitted before for any degree or examination in any other University.

BURY

19 th day of August 1986.

# ABSTRACT

In many computer applications, it is necessary to ensure that the probability of failure is as low as possible. The degree of reliability required of the system is determined by its application. High reliability is particularly important in systems where computer failure could lead to loss of life, or to injury, or to financial loss.

Much research has endeavoured to develop techniques for reducing the probability of computer failure. In this dissertation, such techniques are described and discussed.

The dissertation proceeds to describe the development of an experimental fault-tolerant computer system which is sufficiently flexible to allow the examination of several techniques for achieving high reliability. Particular issues arising from the application of the techniques of triple-modular redundancy and software-implemented fault-tolerance to the system are discussed.

# ACKNOWLEDGEMENTS

The author wishes to express his thanks to:

The National Institute for Aeronautics and Systems Technology of the Council for Scientific and Industrial Research, for sponsoring the project.

Professor Mike Rodd, who supervised the project, and provided extensive moral support is addition to considerable practical advice.

Mr. Hein Smit, who was instrumental in setting up the project to the satisfaction of the CSIR, and gave encouragement and assistance whenever it was needed.

Mr. Carel Combrinck and Mr. Johan Prinsloo, of NIAST, who also provided willing essistance at all times.

PAGE

| DECLARATION                                                                                                     | i   |

|-----------------------------------------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                                                        | ii  |

| ACKNOWLEDGEMENTS                                                                                                | iii |

| CONTENTS                                                                                                        | iv  |

| LIST OF FIGURES                                                                                                 | ix  |

| LIST OF TABLES                                                                                                  | ×   |

| and the second secon |     |

| 1 INTRODUCTION                                                                                                  | 1   |

|                                                                                                                 |     |

| 1.1 Introduction                                                                                                | 1   |

| 1.2 Minimization of Computer-related Dangerous Situations                                                       | 1   |

| 1.2.1 Fault Avoidance                                                                                           | 1   |

| 1.2.2 Fail-Safety                                                                                               | . 2 |

| 1.2.3 Fault Tolerance                                                                                           | 2.  |

| 1.3 Investigations into Fault-Tolerance                                                                         | 3   |

| 1.3.1 Replication                                                                                               | 4   |

| 1.3.2 Back-up                                                                                                   | 4   |

| 1.4 Research Project Objectives                                                                                 | 6   |

| 1.5 Overview of the Dissertation                                                                                | 7   |

| 1.6 Summary                                                                                                     | 8   |

| •                                                                                                               |     |

| 2 FAULT TOLERANCE - AN OVERVIEW                                                                                 | 10  |

|                                                                                                                 |     |

| 2.1 Introduction                                                                                                | 10  |

| 2.1.1 Mctivation for the Use of Fault Tolerance Techniques                                                      | 10  |

| 2.1.2 Criteria to be Satisfied by Fault-tolerant Systems                                                        | 11  |

| 2.1.3 Basic Terms and Concepts                                                                                  | 12  |

| 2.1.4 Causes of Faults                                                                                          | 13  |

| 2.1.5 Classification of Faults                                                                                  | 17  |

ìv

| 2.2   | Techniques of Fault-Tolerance                                                                                    | 17       |

|-------|------------------------------------------------------------------------------------------------------------------|----------|

| 2.2.1 | An Outline of Fault-Tolerance                                                                                    | 18       |

| 2.2.2 | Information Redundancy                                                                                           | 21       |

| 2.2.3 | Herdware Redundancy                                                                                              | 22       |

| 2.2.4 | Software Redundancy                                                                                              | 29       |

| 2.2.5 | Time Redundancy                                                                                                  | 31       |

| 2.3   | Evaluation of Appropriate Fault-tolerance Technique                                                              | a 32     |

| 2.3.1 | Qualitative Techniques                                                                                           | 32       |

| 2.3.2 | Quantitative Evaluation                                                                                          | 33       |

| 2.4   | Summary                                                                                                          | 34       |

|       |                                                                                                                  |          |

| 3     | SOFTWARE DEVELOPMENT TECHNIQUES                                                                                  | 35       |

|       | and the second | s        |

| 3.1   | Introduction                                                                                                     | 35       |

| 3.2   | Structured Design                                                                                                | 35       |

| 3.2.1 | Design Methodologies                                                                                             | · 35     |

| 3.2.2 | Besign Principles - Overview                                                                                     | 36       |

| 3.3   | Structured Programming                                                                                           | 37       |

| 3.3.1 | Structure Theorem and Conventions                                                                                | 39       |

| 3,3.2 | Specification Extraction                                                                                         | 40       |

| 3.3.3 | Tree Structure Diagrams                                                                                          | <b>1</b> |

| 3.3.4 | Pseudo Codo                                                                                                      | 43       |

| 3.4   | Data Flow                                                                                                        | 44       |

| 3.4.1 | Introduction                                                                                                     | 44       |

| 3.4.2 | The Use of Data Flow Techniques                                                                                  | 44       |

| 3.5   | Top-Bown Design                                                                                                  | 45       |

| 3.6   | Verification and Validation                                                                                      | 47       |

| 3.6.1 | Definitions                                                                                                      | 47       |

| 3.6.2 | Verification and Validation Criteria                                                                             | 47       |

| 3.6,3 | Verification and Validation Techniques                                                                           | 49       |

| 3.7   | Debugging                                                                                                        | 49       |

| 3.8   | Summary                                                                                                          | 60       |

|       |                                                                                                                  |          |

| 4     | SYSTEM DESCRIPTION                       | 52   |

|-------|------------------------------------------|------|

| 4.1   | Introduction                             | 52   |

| 4.2   | Detailed System Description              | 55   |

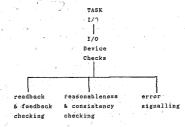

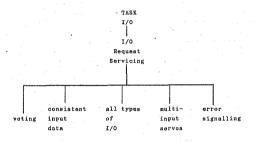

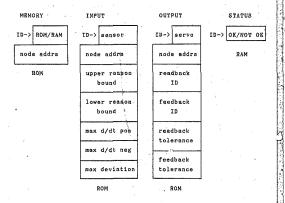

| 4.2.1 | Task I/O Voting                          | 65   |

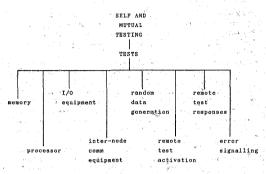

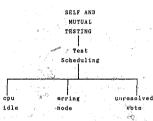

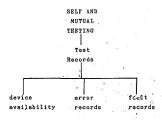

| 4.2.2 | Self and Mutual Testing                  | 58   |

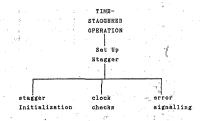

| 4.2.3 | Time Staggered Operation                 | 63   |

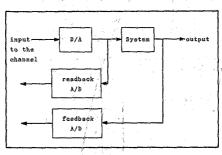

| 4,2.4 | Device Operation Validation              | 66   |

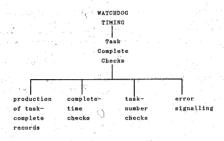

| 4.2.5 | Watchdog Timing                          | 70   |

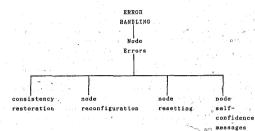

| 4.2.6 | Fault Handling                           | 72   |

| 4.3   | Summary                                  | 74   |

|       | ) A (                                    |      |

| 6     | SYSTEM DESIGN                            | 75   |

| 5.1   | Introduction                             | 75   |

| 5.2   | Hardware Characteristics                 | 75   |

| 5.3   | Software Requirements                    | 76   |

| 5.3.1 | Task I/O Handling                        | 76   |

| 5.3.2 | Self and Mutual Testing                  | 77   |

| 5.8.3 | Time-staggered Operation                 | 78   |

| 5.3.4 | Watchdog Timing                          | 7.8  |

| 5.3.5 | Error Handling                           | 79   |

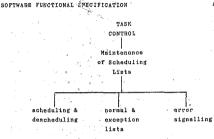

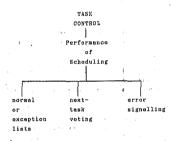

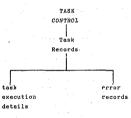

| 5.3.6 | Task Control                             | 79   |

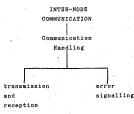

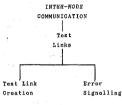

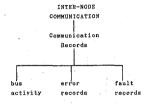

| 5.3.7 | Inter-node Communication                 | 79   |

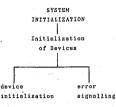

| 5.3.8 | System Initialization                    | . 80 |

| 5.4   | Functional Spec'fication of the Software | 80   |

| 5,4.1 | Task Input and Oumput                    | 81   |

| 5.4.2 | Self and Mutur ing                       | 82   |

| 5.4.3 | Time-stagg cion                          | 84   |

| 5.4.4 | Watchdog Tim.                            | 84   |

| 5.4.5 | Brror Handling                           | 84   |

| 5.4.6 | Task Control                             | 85   |

| 5.4.7 | Inter-node Communication                 | 86   |

| 5.4.8 | System Initialization                    | 86   |

vi

|       | 2                                     | PAGE |

|-------|---------------------------------------|------|

|       |                                       |      |

| 6.5   | Software Outline                      | 87   |

| 5.5.1 | Introduction                          | 87   |

| 5.5.2 | Operating System Routines             | 87   |

| 5.5.3 | General Routines                      | 88   |

| 5.6   | Summery                               | 89   |

|       | · · · · · · · · · · · · · · · · · · · |      |

| 6     | SYSTEM INTEGRATION                    | 91   |

|       |                                       |      |

| 6,1 3 | Introduction                          | 91   |

| 6.2 1 | Requirements for the Supervisor Node  | 91   |

| 6.2.1 | Inter-node Communication              | 91   |

| 6.2.2 | System Monitoring and Control         | 92   |

| 6.3 1 | Description of the Supervisor Node    | 92   |

| 6.3.1 | Communication Handling                | 93   |

| 6.3,2 | System Monitoring and Control         | 96   |

| 6.4 8 | System Testing                        | 99   |

| 6.5 8 | Summary                               | 100  |

|       | · · · · ·                             |      |

| 7 (   | CONCLUSION                            | 102  |

|       | 20-3<br>-                             |      |

| 7,1 5 | Summery                               | 102  |

| 7,1.1 | Fault Tolerance                       | 102  |

| 7.1.2 | Software Day lopment Techniques       | 102  |

| 7.1.3 | System Description                    | 103  |

| 7.1.4 | System Design                         | 104  |

| 7.1.5 | System Integration                    | 104  |

| 7.2 1 | Discussion                            | 104  |

| 7.2.1 | Fault Tolerance                       | 104  |

| 7.2.2 | Software Development Techniques       | 105  |

| 7.2.3 | Evaluation of the Experimental System | 106  |

| 7.3 C | Conclusion                            | 108  |

|       |                                       |      |

1. a. Chr.

PAGE

| REFERENCE | 88    |                                            | 109 |

|-----------|-------|--------------------------------------------|-----|

|           |       |                                            |     |

| BIBLIOGR  | A P H | Ŷ                                          | 113 |

|           |       | (                                          |     |

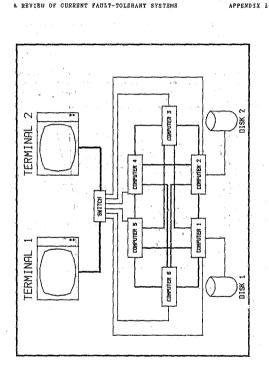

| APPENDIX  | 1     | A Review of Current Fault-tolerant Systems | 118 |

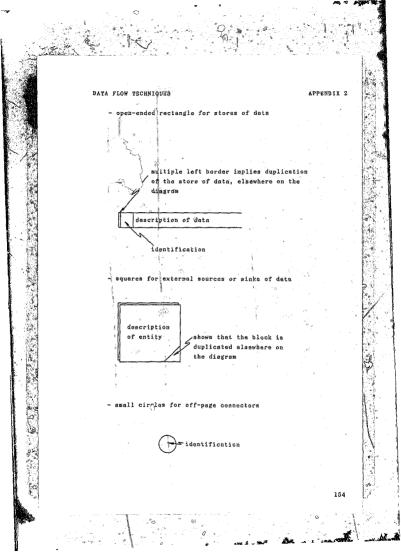

| ÁPPENDIX  | 2     | Data Flow Techniques                       | 153 |

| APPENDIX  | 3     | Software Debugging Techniques              | 160 |

| APPENDIX  | 4     | Self-testing: Theory and Practice          | 162 |

| APPENDIX  | 5     | Hardware Details                           | 171 |

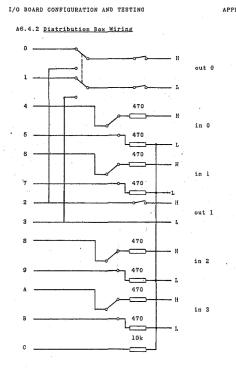

| APPENDIX  | 6     | I/O Board Configuration and Testing        | 189 |

| APPENDIX  | 7     | Software Requirements                      | 204 |

| APPENDIX  | 8     | Software Functional Specification          | 215 |

| APPENDIX  | 9     | Software Module Descriprions               | 259 |

| APPENDIX  | 10    | Reduced 1553 User Interface Definition     | 282 |

24

4

# LIST OF FIGURES

PAGE

| 1.  | The Hot Backup Configuration             |        | 1.1   | 5    |

|-----|------------------------------------------|--------|-------|------|

| 2.  | The Pair-and-a-Spare Configuration       |        | 1     | ି ଜ  |

| 3.  | Time Constants of Systems                |        |       | 12   |

| 4.  | Causes of Faults                         |        |       | . 14 |

| 6.  | Conventional Software Development        |        | V - 2 |      |

|     | and the Origins of Faults                |        |       | 15   |

| 6.  | Hardware Voting                          |        | a .   | 24   |

| 7.  | Software Voting                          |        |       | 24   |

| 8.  | Voter Triplication                       |        |       | 25   |

| 9.  | The Dual-Redundant Configuration         |        |       | 27   |

| 10. | The Quad-Modular Redundant Configuration | ь<br>1 | P.    | 28   |

| 11, | Functional Redundancy Checking           |        |       | 29   |

| 12. | A Narkov Nodel                           |        | 1.1   | 34   |

| 13. | A Decision Tree                          |        |       | 4 ï  |

| 14. | A Decision Diagram                       |        |       | 42   |

| 15. | A Tree Structure Diagram                 |        |       | 43   |

| 16. | Traditional Top-down Development         |        |       | 45   |

| 17, | Revised Top-down Development             |        |       | 46   |

| 18. | Satisfactory Softwore Specification      |        |       | 48   |

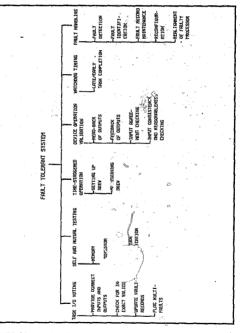

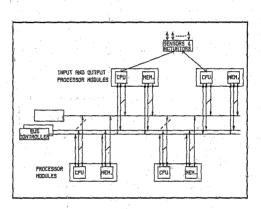

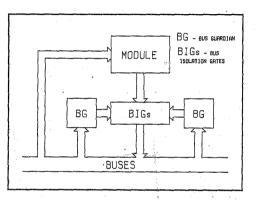

| 19. | System Description                       |        |       | 54   |

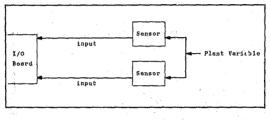

| 20, | Task I/O Voting                          |        |       | 57   |

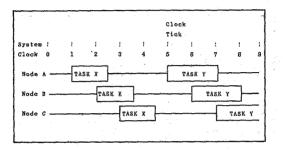

| 21. | Staggared Execution of Tasks             |        | 8     | 65   |

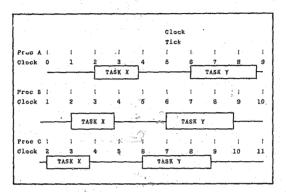

| 22. | Staggered Clocks                         |        |       | 66   |

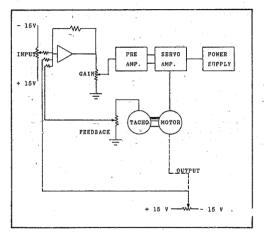

| 23. | An Output Channe!                        |        |       | 67   |

| 24. | An Input Channel                         |        |       | -69  |

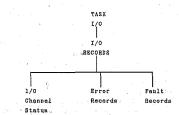

| 26. | Task Complete Records                    |        |       | 71   |

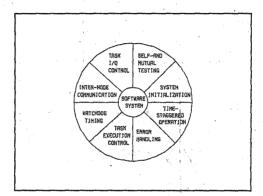

| 26. | The Software System                      |        |       | 81   |

|     |                                          |        |       |      |

# LIST OF TABLES

1. Node Errors and Faults 2. General System Errors and Faults

PAGE 98

99

# Chapter 1 - INTRODUCTION

# 1.1 Introduction

Since the early use a computers in which they were installed primarily to produce answers to numerical problems, they have become integrated more and more into our everyday environment. We can now find them in a variety of forms, strapped to our wrists, installed in our cars, and suspended hundreds of kilometers above us.

With computers taking such an active part in our lives, their failure can often cause dangerous situations, where death, injury or financial loss cán result. Consider, for excepte, a nuclear power plant, controlled by a process system using a series of digital computers. The failure of a computer can clearly be very serious, and it is naturally desirable to prevent such situations from arising. This has led to much work in designing computer systems which are as reliable as possible.

# 1.2 Minimization of Computer-related Dangerous Situations

Three main philosophies have emerged for the minimization of computer-related danger. These may be summarized as:

- Fault avoidance

- Fail-safety

- Fault tolerance

#### 1.2.1 Fault Avoidance

An obvious way of preventing computers from causing harm to the plant, or to the environment which they control, is to make sure that they never fail! The philosophy which attempts to accomplish this goal is known as "fault avoidance".

Fault avoidance requires that the physical components of a computer system, and their assembly methods, are as perfect as pos-

1

water in the in the

#### INTRODUCTION

2

martin a the martin the

sible. The cost of obtaining near-perfect components is often excessive, and maintenance staff must be continuously available because the system ceases to operate upon first failure. So, fault-avoidance techniques are clearly expensive and imperfect [1], and may consequently not result in adequate reliability.

# 1.2.2 Fail-Safety

In view of the problems relating to the design of perfect systems, the emphasis in research has focused on ensuring that computer failures do not lead to harm if and when they occur. This leads to another philosophy, namely that of "fail-sefety".

To achieve fail-safety, it is necessary that when a computer system ceases to operate, it does so in such a manner that it can have no harmful effect on the environment over which it has influence. A particularly good example of the application of failsafety techniques can be found in the area of railway signalling. If the system which manipulates the signals of a railway system fails, then all affected signals are set to STOP, so that trains in the area come to a halt, and hence avoid collision or derailment.

# 1.2.3 Fault Tolerance

There are situations, however, where the removal of the computer from a system cannot be accomplished without undesirable side-effects.

In many industrial processes, loss of control spells ruin of the product, with the additional possibility of permanent damage to equipment. In such a circumstance, a fail-safe end to control does little to prevent considerable financial loss.

An even worse case may be considered: the failure of a fly-bywire aircraft control system (one in which control signals to the aircraft take the form of electrical signals rather than mechanical links) could lead to the loss of the aircraft and

# INTRODUCTION

3

- marine a come we will be

#### Chapter 1

crew. Mechanical back-up systems may be used in certain cases, but experimental aircraft are being developed which depend entirely upon the fast and accurate capabilities of a computer to maintain controllability [2].

In the case of remote equipment, such as weather monitoring stations and satellites, it is not possible to effect early repair should the computer system fail. Unless self-repair and/or graceful degradation facilities are built into the system, use of the system is totally lost when a fault occurs. Once again, therefore, fail-safety is inadequate.

There is consequently a need for computer systems which operate even when there are faults in the system. This leads to the concept of "fault-tolerance", which has been defined as "the ability of a system to operate correctly in the presence of faults" [3], and is the central topic of this dissertation.

# 1.3 Investigations into Fault-Tolerance

Over the past decade, such research effort has been dedicated to the development of fault-tolerant computer systems, and this has resulted in a large number of techniques being proposed as suitable for particular applications.

By definition, a fault-tolerant system must be designed assuming that some components will fail. The key ingredient in all faulttolerance techniques is therefore redundancy - of information, resources and/or time. The type and extent of the redundancy esployed in the system depends on the technique used, as well as on the intended application. The techniques of fault-tolerance fall into two loosely defined categories:

- replication

- back-up

# INTRODUCTION

## Chapter 1

# 1.3.1 Replication

From the literature, "replication" is evidently the most popular technique being used today. Many identical or similar units are used, and all fault-frea units are active, that is to say, they contribute to the operation of the system as a whole. When a unit's failure is detected, the system attempts to reconfigure with one unit less. Hence, execution time might lengthen, but all essential services are maintained.

# 1.3.2 Back-up

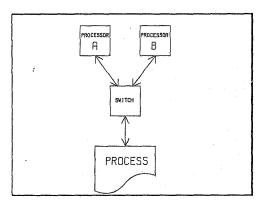

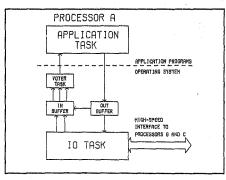

"Back-up" is the second widely used technique (See fig. 1). In this approach, only "nat's operational, while one or more units are available ø approach. If the spare units are powered in the idle state, the "protent is referred to as "hot" backup. Sometimes, unpowered where are used, in an attempt to lower the spare failure rate. The units are connected to the process through a switching mechanism that keeps only one active at a time. The active processor performs comprehensive self-checking, and is switched out when faulty.

at a Dr. with he

INTRODUCTION

# FIGURE 1 - The Hot Back-Up Configuration [4]

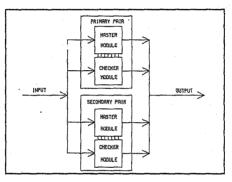

An extended version of hot back-up, known as "pair-and-a-spare" may also be implemented (Sea fig. 2). In this, the active and back-up units each consist of two modules, thus forming a tightly-coupled unit capable of reliable self-checking.

INPUT PRIMARY PAIR NOULE CHECKER NOULE NOULE NOULE NOULE NOULE NOULE NOULE NOULE NOULE

INTRODUCTION

FIGURE 2 - The Pair-and-a-Spare Configuration [5]

# 1.4 Research Project Objectives

This project had two major objectives. Firstly, it simed to generate insight into the field of full-tolerance, and secondly to produce a flexible experimental system which could be used for studying various fault-tolerance techniques.

It was fait that at this staga in the development of faulttolerant systems, little practical experience exists, creating a need for the project. However, the effort investigating faulttolerance was not simply ... facilitate the production of the experimental system; it was also desirable to gain expertise in the field of fault-tolerance, with a view to applying the knowledge in future projects.

It was therefore necessary to broaden the theoretical side of the project beyond that necessary for the production of the

to the me

#### INTRODUCTION

experimental system. To this end, various aspects of the topic required further attention, such as;

- investigations into the theory of fault-tolerance

- study of important current systems, both commercially available, and undergoing development

It should be pointed out that the composition of much of the experimental system developed was defined by available equipment and tools. These constraints are discussed in the appropriate place in the dissertation.

Development of the experimental system consisted of:

- selection of a representative fault-tolerance technique for demonstration of the system

- investigations into software engineering techniques

- production of a suite of software modules for use in the Various system configurations

- integration of the software and hardware components of the system

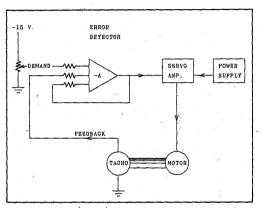

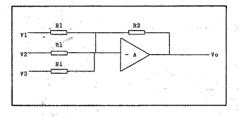

- application to a real-time, but simple serve-control system so as to provide a live demonstration

1.5 Overview of the Dissertation

The remainder of this dissertation covers the following areas:

Chapter 2 - Fault-Tolerance - a discussion of techniques for achieving fault-tolerance and for evaluating fault-tolerant systems

at a total line

#### INTRODUCTION

Chapter 3 - Software Development Techniques - Structured design, structured programming, data flow techniques, top-down design, verification, validation, and debugging

Chapter 4 - System Description - System requirements, functional specification of the system

Chapter 5 - System Design - Hardware characteristics, software requirements, functional specification of the software, and software characteristics

Chapter 6 - System Integration - Development of the software required for system control and testing, and implementation of the system

Chaptor 7 - Conclusion - A brief summary of the results of the research followed by a discussion of the more important findings and conclusions as well as uncolved issues

# 1.6 Summary

Because of the wide use of computers in critical applications, it has become necessary for attention to be given to the problem of computer faults. The main computer-fault handling techniques are

- Fault avoidanco,

- Fail-safety, and

- Fault tolerance.

Research effort into the technique of fault telerence has led to many fault telerence methods, which can be leesely divided into the categories of

e Mar -

- Replication, and

- Back-up.

# INTRODUCTION

The goals of the current project were to gain insight into the field of feult-tolerance, and to produce a flexible experimental system for use in the study of feult-tolerance techniques.

To provide a sound basis for the development of an experimental system, an extensive study into fault tolerance was undertaken, and this is covered in the next few chapters.

# Chapter 2 - FAULT TOLERANCE - AN OVERVIEW

# 2.1 Introduction

The benefits of employing fault-tolerance to computer system design are many, but in essence, lead to reduced system lifetime costs. In this chapter, various aspects of fault-tolerance are explored, and ti most critical areas are highlighted. Many current fault-tolerant systems are referred to, and are described in detail in appendix l.

#### 2.1.1 Motivation for the use of Fault-tolerance Techniques

A number of factors have led to the development of faulttolerance techniques, the most important being:

Reliability. Since maintenance and general downtime costs have risen to become a large proportion of total system lifetime cost, it is obviously desirable that systems should be designed to fail as coldom as possible.

Data integrity. Because computers are used in highly critical areas, it is essential that data corruption is highly improbable.

Availability. From a users point of view, it is necessary that computer down-time is minimised, especially when the service provided by the system involves human interaction.

Graceful Degradation. Remote computer equipment must function for as long as possible without repair. In the "treme situation of, say, an unmonned spacecraft, no repairs at all are possible; any failure should not lead to a total system failure, but merely a drop in performance.

It should be no ed that these are the most obvious points of improvement brought about through the use of fault-tolerance techniques; other facilities which may be provided by the application of the philosophy include:

10

é . Ó. .

#### FAULT TOLERANCE - AN OVERVIEW

11

é.Ar

On-line maintenance (the ability to perform repairs without switching the system off). A fault-tolerant system would regard the removal of a single unit as a unit failure, and continue in its normal fault-handling menner.

Fail-safe operation (the prevention of dangerous effects caused by failure of the computer). The failure of a unit can be automatically prevented from affecting the environment, by the fault-handling mechanism.

# 2.1.2 Criteria to be Satisfied by Fault-Tolerant Systems

The reliability requirements which must be imposed on a system naturally depend on the intended application [6]. For example, the primary function of information storage systems is the safe storage of data, so such systems can tolerate short losses of service, but not data loss or corruption. On the other hand, telephone exchanges require high availability, so that users do not have to wait for intelerably long periods oefore the required service is provided, but it doesn't necessarily matter if a few wrong connections are made. In the extreme case, life-critical systems can tolerate no failures at all.

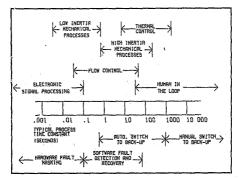

The computer must be capable of a recovery time (the time it takes the system to function acceptably, after a fault) which is appropriate to the time-constant of the application (a measure of the speed of the system) (See fig. 3).

#### FAULT TOLERANCE - AN OVERVIEW

FIGURE 3 - Time Constants of Systems [4]

# 2.1.3 Basic Terms and Concepts

Many differing interpretations are placed on a number of terms and concepts used in the field of fault-tolerance. In order to svoid misinterpretation of terms used in this dissertation, the more important terms and concepts are defined below:

Fault - any state of a computer's hardware or software which could cause the computer to operate incorrectly, or not at all

- Common-mode fault - a fault which affects all parts of the system simultaneously (for example, electromagnetic interference)

- Error - incorrect operation of the computer, leading to incorrect data or to invalid actions by the computer

12

#### FAULT TOLERANCE - AN OVERVIEW

- Reliability - the probability that the computer will operate correctly during a given time period

- Fault masking - the prevention of error propagation into other parts of the system

- Fault tolerance - the ability of a system to operate correctly in the presence of faults. The concept embodies:

- fault detection - the discovery of a fault

- fault recovery - removal of the effects of the fault and isolation of the faulty system component (i.e. ensuring that the component cannot exert any influence on the operation of the system as a whole)

#### 2.1.4 Causes of Faults

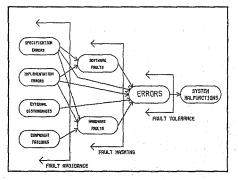

In order to combat the occurrence of faults, it is necessary to know the way in which they arise (See fig. 4). It is often possible to perform "preventative design" (this entails the conf struction of the system in such a way that susceptibility to faults is minimized), which will cut down on the number of faults that must be catered for by the fault-tolersnce mechanism.

Chapter 2

#### FAULT TOLERANCE - AN OVERVIEW

14

FIGURE 4 - Causes of Faults [7]

In essence, the origins of faults can be grouped into four categories:

- specification faults

- implementation faults

~ component failures

- external disturbances

The way in which these fault origins relate to the conventional software development cycle is shown in figure 5.

Chapter 2 COMPONENT FRILING PELFICATION EXTERNIAL ECT/1007101 CEPTONES' N IS DESCOL DESCOL COUNTRY AND A 40153 R. TORT C PISTER

FIGURE 5 - Conventional Software Development and the Origins of Faults [8]

> est. 01

FAULT TOLERANCE - AN OVERVIEW

15

#### FAULT TOLERANCE - AN OVERVIEW

Specification faults.

The first possible cause of specification faults is that of hardware and software design specification mistakes, which occur when the hardware or software has been specified in a way that does not meet with the requirements of the system. Secondly, architectural mistakes mean that the system has been designed in such n- way that it is not able to perform all operations required of it. Finally, algorithm mistakes arise when an algorithm implemented in the system is incorrect.

# Implementation faults.

Following on from the design specifications, the system is susceptible to implementation faults. These can be the result of, firstly, poor design, which implies that the design of the hardware does not meet all the requirements of the specification. Otherwise, such faults can originate in poor component selection, where unsuitable components have been chosen. Furthermore, poor construction of the hardware can lead to weak points in the system, or software coding faults can lead software which does not always perform according to the software specifications.

Component failures,

Component failure can arise from manufacturing errors, where a component has been incorrectly constructed, or from component flaws or component aring.

# External disturbances.

Radiation is the one of the most prevalent external disturbances. External electromagnetic fields can alter the operation of the system so that it fails. Physical damage to the system can also occur from an external source, or unexpectedly severe environmental conditions can cause the system to fail. Finally, inappropriate man/machine interaction via control or maintenance

E . Bar

# FAULT TOLERANCE - AN OVERVIEW

17

Chapter 2

panels, where the operator has made a mistake or is not qualified to control the system, can lead to system failure.

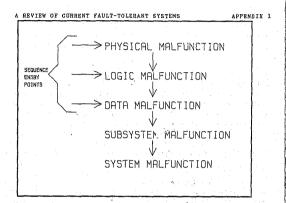

# 2.1.5 Classification of Faults

Faults are classified using one or more of the following parameters:

- Cause - one of the possibilities mentioned in section 2.1.4, which caused the fault

- Nature - whether the fault is in the hardware or the software

- Duration - whether the fault is permanent, transient or pseudo-transient (e.g. pattern dependent)

- Extent - the amount of the system which is affected by the fault

Value - whether the errors are detorminate or indetorminate (i.e. whether the errors are always the same, or random)

Knowledge of these details enables effective counter-measures to be taken.

# 2.2 Techniques of Fault-Tolerance

As mentioned previously, redundancy forms the basis of a faulttolerant system, and this redundancy may take the form of information redundancy, hardware redundancy, software redundancy and/or time redundancy. Each of these topics will be covered in the following sections.

#### FAULT TOLERANCE - AN OVERVIEW

# 2.2.1 An Outline of Fault-Tolerance

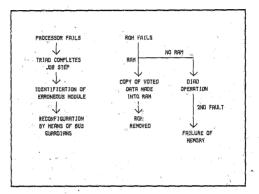

The sequence of handling a fault begins with the detection of an error. The system then attempts to diagnose the fault which caused the error, and prevent the damage from spreading (confinement). Thereafter, it is necessary to reconfigure the system to a valid state, bypassing the faulty components, and to continue operation - as fully as possible. Finally, if possible, repair to the faulty component(a) should be made, thereby ultimately restoring full capabilities to the system. In the sections which follow, the various stages involved are discussed in depth.

Error Detection.

Faults and subsequent errors typically manifest themselves as invalid dats. To detect errors and faults, therefore, it is necessary to detect invalid data. To determine the validity of data, two types of test are possible:

Voting

Bounds of reason

Voting. Several answers to a calculation are obtained typically using one of two methods:

- repeated celculations - Each calculation (for which the result is to be validated), is performed two or more times. The answers obtained in each repetition (which may be performed by different processors), are compared, and any inconsistency reveals that an error has occurred. If executed on only one processor, then this technique detects the occurrence of faults and non-determinate faults only, since a permanent, determinate fault would manifest itself in the same way in each calculation, misleading the system into believing that the result is valid. Also, if the calculations are to be run in separate processors, care must be taken to ensure that the executions are staggered to

18

No the State of the second second

#### FAULT TOLERANCE - AN OVERVIEW

time so that common-mode faults do not produce the same errors in all processors.

- duplicated calculations - Each calculation (for which the result is to be validated), is performed in two or more different ways (possibly by different computers). Any discrepancy in the results indicates the occurrence of an error. All types of fault are covered by this method, but extra effort is required in development of the algorithms, and extra program storage space is needed for the different versions of the calculation.

There are two possible ways in which the answers to these calculations may be compared:

- hardware - Dedicated circuits are used to compare the results of computations. This method is fast, but requires the addition of components, increasing the cost and the risk of failure - because of the extra components! Furthermore, in order for hardware voting to be used, all values of data must be simultaneously available. This leads to the possibility of a commonmode fault affecting all versions of the data in the same way, causing the voter to pass the incorrect value

- software - Voting is accomplished using a software module

Considerable effort is also required in both hardware and software voting to make the voting mechanism itself faulttolerant,

Bounds of reason. In this tochnique, the value of a data element is checked against pre-dofined limits, beyond which it is determined to be invalid. The test may be applied to any data element for which bounds of reason can be defined. The limits are usually characteristics of the application, or possible constraints imposed by the data-typing provided by the programming language.

S. Martin Cont.

#### FAULT TOLERANCE - AN OVERVIEW

#### Chapter 2

#### Fault diagnosis.

Faults that are to be tolerated by the system must be well defined at an early stage, so that they can be specifically catered for in the design. Such faults must be automatically detected and localized by the system, using the characteristics of errors which have occurred, or can be made to occur, using disgnoatic programs.

#### Damage Confinement.

In order to limit the effects of a fault, it must be possible to reset the system to a valid (correct) state after the occurrence of a fault, so that the system does not continue producing more and more errors.

# Reconfiguration.

The system must automatically bypass defective components and yet keep all system functions, which are not dependent on the lost component, available to the user, with: a possible reduction in processing speed.

#### Recovery.

Data which was found to be erroneous must be corrected. Otherwise, recovery will be in the form of resetting to a previous valid state (when possible), or to a predicted future state. An important goal in the recovery process is that every restart must be accomplished with a minimum recovery time, in order to minimize down-time losses.

## Fault Treatment and Continued service.

The system should remain in a degraded state for as short a time as possible. If possible, the fault should be repaired or the faulty unit replaced so that fault-tolerant operation is resumed.

minter a the marked

#### FAULT TOLERANCE ~ AN OVERVIEW

The following sections discuss the techniques used to put these principles into practice.

# 2.2.2 Information Redundancy

Information redundancy is the use of more information about the data than is actually needed by the application.

A widely used technique for implementing information redundancy is by the use of "data encoding". Numerous information-redundant codes have been developed to provide for detection and, in certain cases, correction of errors. A code constructed in such a way that any single error transforms a valid code into an invalid code is called a single-error detecting code. A simple form of such error detection is the single-bit parity check. Another type is "M-out-of-N" coding, where code words are N bits long, and always contain M "l"s.

A number of "checksum" error-detection codes exist. The checksum is calculated by summing the binary data that is to be moved from one point to another. When the data reaches its destination, the checksum is recalculated, and if the new value and the one calculated previously do not agree, then an error is indicated. These codes are useful in the transfer of blocks of data.

Possibly the most common extension of parity checking is the Hamming error-correcting code. Hassning codes can detect double errors, and correct single errors. Once a single binary error has been detected, it is easily corrected by complementation of the data bit in the identified position.

Fault-tolerant systems often incorporate information redundancy into the fault-tolerance mechanism, especially in the memory sections of the system. In some cases, however, the primary faulttolerance mechanisms of the system are so effective that they make the reliability improvement brought about by the use of information redundancy negligible.

water a dely me with the second

# FAULT TOLERANCE - AN OVERVIEW

#### 2.2.3 Hardware Redundancy

Hardware redundancy is the use of more physical equipment than is required by the application.

Hardware redundancy methods may be grouped into two categories;

- replication

- back-up

The addition of spare resources to either category results in what is often called an "hybrid" system.

# Replication.

In the technique known as "replication", more than one resource is available to perform tasks required of the system. Memory, processing, and/or input and output units may be replicated, depending on the requirements of the application. All units in the system contribute to the operation of the system as a whole, and may be run out of close synchronization (where every instruction is executed at the same time in all processors) to avoid the effects of common-mode faults. An example of such a system is the Fault-tolerant Array Signal Processor [9], which uses a form of replication to perform space-based signal processing (See appendix 1 for more details).

Three important forms of replication are:

- dual redundant systems

- triple-modular redundant systems

- gracefully-degrading systems

Martin Otto

# FAULT TOLERANCE - AN OVERVIEW

Chapter 2

Dual Redundant Systems. One of the simplest redundant systems is the dual system, in which the same tanks are executed on two different units, and the outputs compared. If the outputs do not agree, then an error is signalled. The system is incapable of deciding which of the two units has produced the error unless further testing is undertaken. This means that the system must be shut down when an error ocurs.

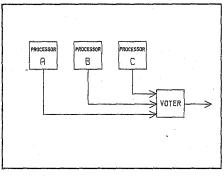

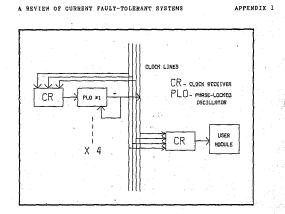

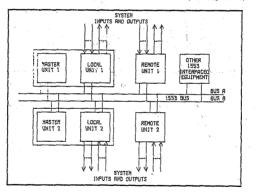

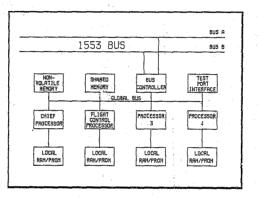

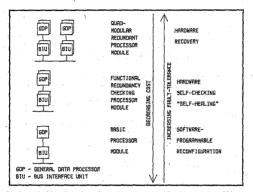

Triple-modular Redundant Systems. These systems use three units, all performing the same calculations, and are capable of masking all single errors, as well as indicating which unit was responsible for the error. Furthermore, the systems are capable of detecting simultaneous errors in all units, because the vote will fail. The Triplex 32 system [4] utilizes TMR (Triple Modular Redundancy) to accomplish fault-tolerant process control, while the Software Implemented Fault Tolerance [10] system applies TMR to aircraft control (See appendix 1 for detailed descriptions).

After a faulty unit has been pinpointed, its outputs are ignored, while the good units continue operation as a dual system. When the faulty unit has been repaired, it is set to a state consistent with the other units, and the system returns to its original degree of fault-tolerance.

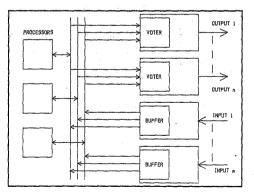

Voting may be accomplished in either hardware (See fig. 6), or in software (See fig. 7).

23

ad a dra

# FAULT TOLERANCE - AN OVERVIEW

FIGURE 5 - Hardware Voting [4]

FIGURE 7 - Software Voting [4]

24

# FAULT TOLERANCE - AN OVERVIEW

Bear &

25

With voting, there is some loss of performance while data is passed through the voting machanism. It is possible with hardware voting, however, to utilize parallel processing so that modules in the system are performing the next operation while the votor is finishing the previous one. A more serious, drawback of hardware voting is that the votor components are unprotected, and expose the system to a single-point failure. One solution is to triplicate the voters (See fig. 8). The problem of common-made faults is not overcome, however, because data must still be available to each voter at the same time. The major advantage of hardware voting is its speed, especially in fouris alpoint at the which often require large numbers of inputs and outputs.

FIGURE 8 - Voter Triplication [5]

If more than three units are used in the system, then N-modular redundancy is being employed, where N is the number of units, Such replication may be used when inadequate reliability is provided by the triple-modular technique. There are usually en

## FAULT TOLERANCE - AN OVERVIEW

odd number of units, so that a majority vote can always be chtained.

Gracefully-degrading Systems. When the multiple units in a system all perform different functions, then a gracefully-degrading system can be formed. Effective load sharing across system resources, and efficient communication between the units are necessary. When a unit fails, its load is shared among the others units. Hence, execution time increases, but all system functions are maintained. In addition to utilizing the technique of faple modular redundancy, the "Software Implemented Fault-ti\_srance" (SIFT) system also has the ability to degrade gracefully, because of replicated resources. Other systems which are capable of graceful degradation are the Basic Fault-tolerant System [11] and the Tandem transaction processing system [12] (See appendix 1).

#### Back-up.

The fundamental idea behind the principle of back-up systems is that one unit is operational, while one or more units wait in reserve. When the active unit has failed, a replacement pakes over.

Two important back-up configurations are:

- dual-redundancy with switch-over

#### - pair-and-a-spare

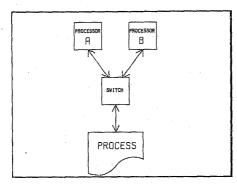

Dual-redundancy with Switch-over. This technique is often  $a_{p-}$ plied in process control. A dual-redundant control system is comstructed using two process controllers or commercial computers, with additional hardware and software to detect and recover from faults. The pair is connected to the process through a switching mechanism that keeps one active and the other in reserve (See fig. 9).

marte a Colle marte

# FAULT TOLERANCE - AN OVERVIEW

Chapter 2

odd number of units, so that a majority vote can always be obtained.

Gracefully-degrading Systems. When the multiple units in a system all perform different functions, then a gracefully-degrading system can be formed. Effective load sharing across system resources, and efficient communication between the units are necessary. When a unit fails, its load is shared among the other units. Hence, execution time increases, but all system functions are maintained. In addition to utilizing the technique of triple modular redundancy, the "Software Implemented Fault-tolerance" (SIFT) system also has the ability to degrade gracefully, because of replicated resources. Other systems which are capable of graceful degradation are the Basic Fault-tolerant System [11] and the Tandem transaction processing system [12] (See appendix 1).

#### Back-up.

The fundamental idea behind the principle of back-up systems is that one unit is operational, while one or more units, wait in reserve. When the active unit has feiled, a replacement takes over.

Two important back-up configurations are:

- dual-redundancy with switch-over

#### ~ pair-and-a-spare

Dual-redundancy with Switch-over. This technique is often applied in process control. A dual-redundant control system is constructed using two process controllers or commercial computers, with additional hardware and software to detect and recover from faults. The pair is connected to the process through a switching mechanism that keeps one active and the other in reserve (See fig. 9).

26

ante a Cara un

FIGURE 9 - The Dual-Redundant Configuration [4]

The active computer executes both a control program for the application, and a diagnostic program that continually checks for errors in the processing unit, memory and I/O circuits. When an error is detected, the switching mechanism transfors control to the reserve computer, which will have been passively monitoring the process. The Agusta 129 helicopter flight control system is an example of such back-up, as is the Resilient transaction processing system. These are covered in some detail in appendix 1.

For fast processes, several problems make this method unsuitable. The first problem is that orrors may occur before the diagnostic program can detect that something is wrong. Secondly, the switching time at computer change-over may be too long, causing an unacceptable discontinuity in the control values. Finally, the switching mechanism could fail, causing complete loss of con-

attended a Office marker + Edite

## FAULT TOLERANCE - AN OVERVIEW

trol. When such fast processes are to be controllød, techniques that provide fault-masking must be used.

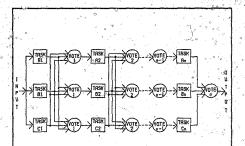

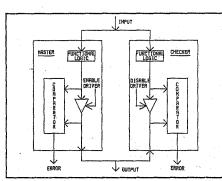

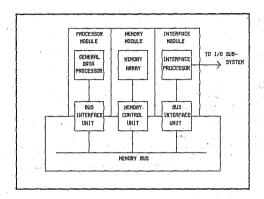

Pair-and-a-spare. In the pair-and-a-spare configuration, four identical modules are organized as primary and shadow pairs of master and checker modules (See fig. 10).

FIGURE 10 - The Quad-Modular Redundant Configuration (5)

Only the primary's master module is capable of activating the computer outputs. While the primary's master transmits data, its checker module compares external data and that presented to its disabled output drivers (See fig. 11). This technique is called "functional redundancy checking". If the primary's checker module detects an error, it initiates a procedure that disables the primary pair, and enables the shadow pair to take over the primary role. Systems which apply this technique are the Stratus transaction processing system and the Intel 432 general-purpose system (See appendix 1 for more details).

28

strate a the works

#### FAULT TOLERANCE - AN OVERVIEW

FIGURE 11 - Functional redundancy Checking [5]

Hybrid.

The essence of the hybrid system is the availability of spare units to replace those that are faulty. Spares can be provided for any system in which the faulty unit can be identified. The purpose of providing spares is to ensure that the system is returned to its original fault-tolerant state with the minimum of delay. The failed unit can then be removed for repair.

# 2.2.4 Software Redundancy

Software redundancy is the use of more software than is required by the application.

Software redundancy can range from the addition of small routines to perform validity checks on the data, to full replication of

to the mark of the

#### FAULT TOLERANCE - AN OVERVIEW

all software (i.e. more than one complete software system), written by different programming teams.

There are many possible approaches to implementing redundancy in software, differing mainly in complexity. Validity checks are the simplest; in this approach, the values of key variables in calculations are monitored to pick up any deviation from the range of values that the variables may have.

Redundant software may be used to perform periodic testing of hardware, by applying algorithms to pre-defined data with known results. If erroneous results are produced by the hardware, then that particular piece of equipment is signalled as faulty.

Full replication of software may be used as a maging to avoid error propagation, using voting. Identical copies of the software may be run concurrently in different processors (thereby including hardware redundancy as well), and the results compared. Newever, global faults such as electromagnetic interference may cause the same error to occur in all sets of the software. For this reason, the execution of the software may be staggered slightly in time, so that the same error is not induced in all copies of the program.

An expensive, but potentially reliable way of replicating software is to have different design teams each produce the programs knowing only the functional requirements of the system. This may even be taken so far as to have the teams use different programming languages. In this way, it is unlikely that the same code will be produced, and it will also be unlikely that the same programming mistakes will be made. Hence both common-mode errors and software errors have a greater probability of detection when such a system is in use.

Software may be used to perform the voting involved in hardware redundant systems. Each computer receives the same inputs, computes a result, and sends it to the other computers, receiving their answers in return. The majority voted

30

. A.

#### FAULT TOLERANCE - AN OVERVIEW

result is the used for output. This approach is known as SIFT [10], and will be discussed later.

Another software-redundant fault-tolorance technique, called "check-pointing", is used in some loosely-coupled systems, in which duplicated processors run the software at approximately the same time, but not with step-by-step synchronization. Software in these systems can periodically suspend normal program execution while ack system compares its state with the state(s) of its companion(s) to determine if an error has occurred since the last check-point. If no error is detected, then the system saves its current state, and operation resumes. If an error is detected, then each system is "rolled back" to the previous (recorded) error-free state, and processing continues from that point. If the same error is detected at the next check-point, the failure is diagnosed as permanent.

## 2.2.5 Time Redundancy

Time redundancy is simply the use of more time than is needed to perform only the functions required by the application. All the fault-tolerance techniques already discussed involve the use of time redundancy:

information-redundant systems must always perform checks to see if the data has to be corrected. Even if these checks are performed in hardware, some delay occurs. If correction is needed, then further delay is required

hardware-'.sdundant systems also perform correctness tests when they reach the voting stages of the each process, so that time redundancy is also evident here

- software-redundant systems can require many times the normal execution time if the entire software system is replicated. If only small diagnostic routines are used, then only a small increase in execution time will be necessary

#### FAULT TOLERANCE - AN OVERVIEW

Time redundancy can be used to aid in the determination of the nature of a fault; by repeating a calculation, it is possible to distinguish between permanent and trensient faults.

# 2.3 Evaluation of Appropriate Fault-tolerance Techniques

Bvaluation of systems is necessary to determine their suitability for a -particular application. It is clear that a wide range of techniques are available for incorporation into the design of a specific fault tolerant computer system. It is naturally important to weigh up the various attributes of each approach and the trade-offs in a particular application. Generally, it is apparent that, as in all engineering, both qualitative and quantitative factors must be considered.

## 2.3.1 Qualitative Techniques

Qualitative comparisons describe trade-off issues and specific benefits of one technique or design over another. These are factors that can not be given numerical values, and can include:

- verifiability - the ability to determine that a system design performs the functions required of it

tostability - the ability to determine that a system is operating as it was designed to operate. Additional features are usually incorporated to make the system (estable)

- flexibility - the ability of a system to be used in many different application environments

Additional points which are considered in system evaluation are:

- faults that are covered by the system

- applications supported by the system

32

E - Alter Ser 6

#### FAULT TOLERANCE - AN OVERVIEW

- technology - the expansion of, and requirements for the system depend on the technology used

2.3.2 Quantitative Evaluation

Quantitative evaluation techniques derive values for [7]:

- \_fault coverage - the probability of detecting and handling all faults

- reliability - the probability of survival in the time span (to , t), given that the system was operational at to

- availability - the probability that the system is available at time t

Numerous quantitative measures are taken into consideration in the above evaluations, including [13]:

- mean time to first failure

- mean time between failure

- mean down time

- availability

- computation reliability

- computation availability

- average computation to first failure

- average computation between failures

Also important in the evaluation of a technique are:

performance - including throughput and response times

cost - including purchasing price, meintenance cost and application engineering cost

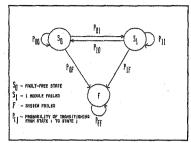

Two widely used quantitative system evaluation techniques are [7]

- combinatorial modelling

- Markov modelling (See fig. 12)

33

Ca Chan we we

#### FAULT TOLERANCE - AN OVERVIEW

FIGURE 12 - A Markov Model [7]

2.4 Summary

The concept of fault-tolerance arises from the need to cater for the occurrence of faults in computer systems. Different applications require different aspects of the system to be made secure against the effect of faults.

The core principle, around which the sequence of fault-handling events is built, is that of redundancy. This redundancy may take the form of information redundancy, hardware redundancy, software redundancy and/or time redundancy.

In order to compare the relative monits of different faulttolerant systems, a number of evaluation measures, both qualitative and quantitative, have been developed.

It is evident that a major portion of many fault-tolerant systems is the software which provides fault-tolerance functions. It is clearly necessary that this software be as reliable as possible, so that it does not diminish the raliability of the system as a whole. The next chapter gives a brief coverage of the techniques of good software design, or software engineering.

34

Sec. Ale

# Chapter 3 - SOFTWARE DEVELOPMENT TECHNIQUES

# 3.1 Introduction

A major aspect in the production of any fault-telerant computer system is clearly the development of reliable, well defined software. In view of this, relevant software development techniques are examined in this chapter.

The application of conventional development practices to software design has been shown [14] to lead to a 20x - 80x rule for the division of resources between definition and coding (20%) and testing and maintenance (80%). The lack of appropriate software design and development tools may lead to unstructured, poorly documented, and error-prone programs which are difficult to understand and expensive to maintain [14]. The increasing complexity and extent of applications of computers has reinforced the need for improved software development techniques.

However, with the application of modern software engineering practices, reductions in software costs, increases in programmers' productivity and reductions in error frequency of between 25% and 75% have been observed. Experiments indicate that the application of more systematic management, design and development techniques may lead to a 40% - 20% - 40% rule for the division of resources between definition/design, coding, and testing/maintenance respectively [14].

# 3.2 Structured Design

#### 3.2.1 Design Methodologies

As applied to programming, design methodology consists of [15]

- establishing the definition of the problem

- specifying the data objects the software must manipulate

# SOFTWARE DEVELOPMENT TECHNIQUES

- specifying the operations that correspond to the manipulation of the data objects

- specifying the programs which must operate on the defined data objects

In order to control the complexity of the development sequence, it is necessary that specifications are initially represented in an abstract form, leading to the adoption of formal specification systems.

#### 3.2.2 Design Principles - Overview

The four major design principles are [15], [14]:

Specification - identification of a 32 the function, that the design must provide. Specifications formally define the functions and properties that a designed system must have. Formalized specifications are derived from the external requirements of the system.

Complexity decomposition - a structured organization of intellectually manageable steps or components of the design. The structure of an entity is given when the relationships between its components have been identified. The most widely accepted notion of modern programming techniques is the introduction of good structure into program and data design.

Guided design. A constrained and controlled process of construction of the design. The construction model consists of three rules which govern the development process:

- A program cannot be functionally specified until all its requirements are known

- The program's algorithm connot be derived until the functional specifications are known

#### SOFTWARE DEVELOPMENT TECHNIQUES

$\sim$  The environment for programs and objects form conditions which in turn may generate requirements through data type specifications to be satisfied by a lower level development step

Proof of correctness. Ideally, a proof should be possible for every program design and every data representation to ensure the design is consistent with its specifications. At present however, it is accepted that this goal is not practically sttainable. Two types of proof are needed

- Proof of the program text

- Proof of the data representation

Proof is considerably aided by good documentation structure and the use of formalized specifications throughout the design sequence [15].

## 3.3 Structured Programming

It is clear that the essist systems to maintain are those built up from manageably small modules, each of which in, as far as possible, independent of the others. This allows them to be taken out of the system, changed, and put back in the system without affecting the rest of the aystem.

In such a system, each module has its own job, which it performs only when given orders from above; it. communicates only with its invoking module and with its invoked modules, to which it will, in turn, issue orders.

#### Coupling.

A good design therefore has the least possible coupling between modules. Three types of coupling have been defined [16]:

# SOFTWARE DEVELOPMENT TECHNIQUES

Data coupling. Data is passed as part of the invocation of the module and as part of returning control to the invoker. The coupling is improved if as few data exchanges as possible are used. This coupling has been found to be the best type.

Control coupling. In this form of coupling, status reports are passed ...between the invoking module and the called module, causing changes in the control pattern. This type of exchange should be kept to a minimum, for ease of understanding ~? program flow, and hence essier maintenance.

External/content/pathological coupling. This coupling arises when the execution of a module depends extensively on another module. Such coupling should be avoided, because of the confusion it can create in understanding of the program.

# Cohesion,

A highly cohesive module, whose parts all contribute to a single function, is not likely to need much coupling to other modules. Six types of cohesion have been identified. From the worst to the best, they are [16]

Coincidental cohesion. The elements of the module cannot be seen as achieving any definable function.

Logical cohesion. Several similar functions are combined into one module.

Temporal cohesion. A variety of functions, which are executed at the same time, are combined into one module.

Procedural cohesion. Each chunk or procedure of a flowchart has been built into the same module.

Communicational cohesion. All functions in the module operate on the same data stream.

#### SOFTWARE DEVELOPMENT TECHNIQUES-

Functional cohesion. The module carries out one identifiable function.

Structured programming involves coding programs using a limited number of control structures to form highly cohesive units of code that are easily readable, and therefore more easily tested, maintained and modified than donventional programs.

Many tools which aid in program development are available. The prime tools are:

- The structure principle

- Specification extraction

- Tree structure diagrams

- Pseudo-code

# 3.3.1 Structure Theorem and Conventions [17]

The structure theorem states that any proper program (a program with one entry and one exit) is equivalent to a program that contains as control structures only

- sequences of two or more operations

- conditional branches to one of two operations (IF condition x THEN action a FLSE action b)

- repetition of an operation while a condition is true (DO WHILE condition x)

A large and complex program may be developed by the  $a_D^{(1)}$ propriate nesting of these three basic structures within each other. The logic flow of such a program always proceeds from the beginning to the end without arbitrary branching.

#### SOFTWARE DEVELOPMENT TECHNIQUES

Two useful extensions to the three structures are

- DO UNTIL condition x

- DO CASE condition x

Several conventions are included as a supporting part of structured programming. For example, strict attention is paid to the indentation of the control structures on the printed page, so that logical relationships in the coding correspond to the physical position on the listing. Code is segmented into reasonable amounts (normally one segment or function per page). Segmentation continues down through the entire coding process.

The use of structured programming should provide many benefits, including fewer errors in the programming process, programs that are nearly self-documenting, and code that can be more easily read, modified and maintained.

# 3.3.2 Specification Extraction

A critical area in the design process is the establishment of the correct specification for the system. All design stems from this specification, so any arrors or omissions will be propagated from it, into the final system. Two tools aid in the correct specification of the system:

- decision trees

- decision diagrams

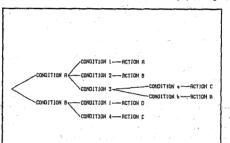

Decision Trees. [16]

Decision trees are used as a tool to extract the correct decision logic from ambiguous specifications.

# SOFTWARE DEVELOPMENT TECHNIQUES

41

**UX** 2

The technique is to identify conditions, actions, "unless", "however," "but",..... structures, greater than/less than ambiguities, and/or ambiguities, and undefined adjectives. This satablishes areas which must be cleared up by the intonded usor of the system. Once clarification has been completed, a revised specification narrative is produced, and a decision tree is dream up (See fir, 13).

FIGURE 13 - A Decision Tree [16]

Decision Diagrams. [16]

Decision diagrems (See fig. 14) are exhaustive tables of all possibilities for every condition. They are used to . specify exactly the action which must be taken for each combination of conditions.

SOFTWARE DEVELOPMENT TECHNIQUES

42

C1-condition 1

Y

Y

Y

N

N

N

Cthere may be more than two

C2-condition 2

Y

Y

N

N

Y

N

N

distinct values for each

C3-condition 3

Y

Y

N

N

Y

N

N

Condition

A1-metion 1

X

X

X

X

Caction not taken

A2-action 2

X

X

X

Z

action taken

Fin. .4 - A Decision Diagram [16]

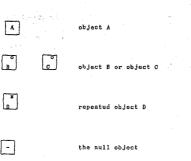

3.3.4 Tree Structure Disgrams [18]

A useful graphic representation of a structured system is the tree structure diagram. A graphic representation allows easier visualization of the system, enabling the designer to more readily see improvements to the structure. Using this system, nodes on the diagram are shown as rectangles, such as those which follow:

.

object A

B C

object B or object C

**\***

-

repeated object D

the null object

## SOFTWARE DEVELOPMENT TECHNIQUES

| Cl-condition 1 | Y | Y. | Y | Y | N | N | N | N- | Cthere may be more than two |

|----------------|---|----|---|---|---|---|---|----|-----------------------------|

| C2-condition 2 | Y | Y  | N | N | Y | ¥ | N | N  | distinct values for each    |

| C3-condition 3 | Y | N  | y | N | Y | N | Y | N  | condition                   |

| Al-action 1    | x |    | x |   |   | x | x | -  | 2-action not taken          |

| A2-action 2    |   | X  | Γ | X | X |   | Г | x  | 2- action taken             |

FIGURE 14 - A Decision Diagram [16]

3.3.4 Tree Structure Diagrams [18]

A useful graphic representation of a structured system is the tree structure diagram. A graphic representation allows easier visualization of the system, enabling the designer to more readily see improvements to the structure. Using this system, nodes on the diagram are shown as rectangles, such as those which follow:

### SOFTWARE DEVELOPMENT TECHNIQUES

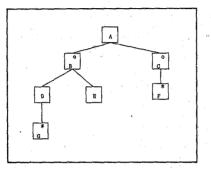

Nodes are connected in a tree structure which indicates the relationship between nodes. An example is shown in figure 15.

FIGURE 15 - A Tree Structure Diagram [18]

## 3.3.5 Pseudo-code

The primery purpose of pseudo-code is to enable an individual to express his thoughts in a form that uses native language prose, but expresses the control flow of the program in an unambiguous meanner. Pseudo-code acts as a form of program documentation which is easy to maintain and not excessively timeconsuming to produce.

"Structured words", such as IF, DO UNTIL etc., and indentation rules, are used to show control dependency. Natural language phrases are used to express thoughts [17].

#### SOFTWARE DEVELOPMENT TECHNIQUES

3.4 Data Flow

# 3.4.1 Introduction

Data flow is the technique of connecting the functions of a system only by flows of the data within the system. Functions connected by data flow are not dependent on adjacent functions [19]. An independent job step can execute as long as its input data is available and it can dispose of its output data. This ensures that the program is easy to maintein.

(See appendix 2 for a more detailed description)

# 3.4.2 The use of Date Flow Techniques

The basic tool for utilizing data flow is the data flow diagram. A standard set of symbols is used to represent the flow of data through the elements of a system. The set includes;

- functions - processes which operate on the data

- flows of data

- stores of data

- external sources or sinks of data

- off-page connectors

Data dictionaries are used to provide standard descriptions of elements in the system.

To get from a data flew diagram to an hierarchical structure, one starts with the rewest form of input and traces it through the data flew until the point is reached where it can no longer be said to be input. Likewise, the output is traced back into the system until it can no longer be thought of as output. The middle piece of the system forms the transformation section.

# SOFTWARE DEVELOPMENT TECHNIQUES

Tree structure diagrams are used to represent the hierarchical system.

# 3.5 Top Down Design

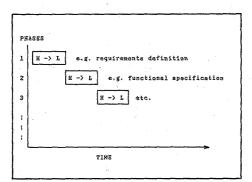

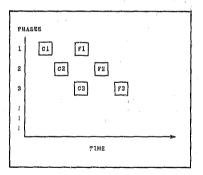

Traditionally, top-down development involved the ordering of development, in each design phase, from the highest level to the lowest level, as shown in figure 16.

FIGURE 16 - Traditional Top-Down Development [20]

### SOFTWARE DEVELOPMENT TECHNIQUES

Recently, a modified approach to top-down system development has been proposed [20]. The new upproach essentially combines topdown and bottom-up development.

Using the new approach, top-down design is defined as the technique of producing a crude skeleton vermion of a system, then adding and testing more cample.ity, piece by piece (See fig. 17) [21]. \_

Course and fine versions of the system are developed in turn. This allows phases to run in parallel, since design teams do not usually concern themselves with phases in the development other than the one in which they specialize.

FIGURE 17 - Revised Top-Down Development (20)

With revised top-down development, the highest level of a system is coded and tested first. Since this unit will normally invoke lower level units, dummy code must be substituted temporarily for

#### SOFTWARE DEVELOPMENT TECHNIQUES

them. Once the higher levels have been completed, work proceeds down the hierarchy until all coding is done.

The major advantage in top-down development is that it avoids the problem of interfacing many small modules. Also, it allows users to see reduced versions of the system so that they can offer comments at an early stage.

The quality of a system produced in this manner should be increased through earlier detection and elimination of design problems and coding errors [17].

## 3.6 Verification and Validation

The main objectives of the verification and validation processes are the identification and solving of software problems and highrisk insues as early in the software life cycle as possible.

# 3.6.1 Definitions

Verification - "The process of determining whether or not the products of a given phase of the software development cycle fulful the requirements established in the previous phase" [22].

Validation ~ "The process of evaluating software at the end of the software development process to ensure compliance with software requirements" [22].

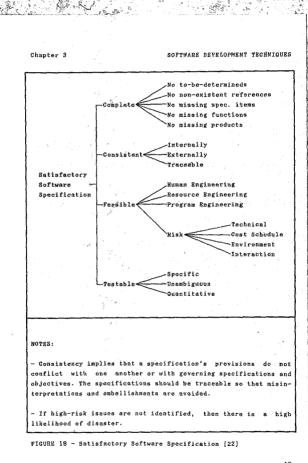

#### 3.6.2 Verification and Validation Criteria

The criteria are shown in figure 18, overleaf

## SOFTWARE DEVELOPMENT TECHNIQUES

### 3.6.3 Verification and Validation Techniques [22]

Although manual techniques for verification and validation prevail, there is increasing development of automatic tools which improve the speed, reliability and consistency of the checking processes.

Manual techniques. These techniques may take the form of

- reading by someone other than the originator

- manual cross-referencing

- interviews with the originator of the specification

- checklists

Chapter 3

- manual modelling in defined environments

- mathematical proofs

Automatic techniques. These may take the form of

- automated cross-referencing.

- automated modelling

- prototypes

# 3.7 Debugging [23]

It is almost certain that, even after the most rigourous software development process, bugs will be found in the completed system.

#### SOFTWARE DEVELOPMENT TECHNIQUES

The debugging process consists, in essence, of the following:

- describing the error

- (\*) gathering data about the program's behaviour

- hypothesizing about the cause of the error, and taking steps to remedy it

- testing the hypothesis