This is a repository copy of Evaluation of gate drive circuit effect in cascode GaN-based application.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/172265/

Version: Published Version

#### Article:

Tan, Q.Y. orcid.org/0000-0002-9272-983X and Narayanan, E.M.S. orcid.org/0000-0001-6832-1300 (2021) Evaluation of gate drive circuit effect in cascode GaN-based application. Bulletin of the Polish Academy of Sciences: Technical Sciences. ISSN 0239-7528

10.24425/bpasts.2021.136742

© 2021 Polish Academy of Sciences. Article available under the terms of the CC-BY-NC-ND licence (https://creativecommons.org/licenses/by-nc-nd/4.0/).

#### Reuse

This article is distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) licence. This licence only allows you to download this work and share it with others as long as you credit the authors, but you can't change the article in any way or use it commercially. More information and the full terms of the licence here: https://creativecommons.org/licenses/

#### **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES DOI: 10.24425/bpasts.2021.136742

#### THIS IS AN EARLY ACCESS ARTICLE.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication.

# **Evaluation of gate drive circuit effect** in Cascode GaN-based applications

Q.Y. TAN\* and E.M.S. NARAYANAN

Department of Electronic and Electrical Engineering, The University of Sheffield, S1 3JD, UK

**Abstract.** This work evaluates the influence of gate drive circuitry to cascode GaN device's switching waveforms. This is done by comparing three PCBs using three double-pulse-test (DPT) with different gate driving loop design. Among important parasitic elements, source-side inductance shows a significant impact to gate-source voltage waveform. A simulation model based on experimental measurement of the cascode GaNFET used in this work is modified by author. The simulation model is implemented in a synchronous buck converter topology and hereby to assess the impact of gate driving loop of cascode GaN device in both continuous conduction mode (CCM) and critical conduction mode (CRM). Apart from simulation, a synchronous buck converter prototype is presented for experimental evaluation, which shows a 99.15% efficiency at 5A under soft-switching operation (CRM) with a 59ns dead-time.

Key words: cascode GaNFETs; parasitics; buck-conerter; gate drive design.

#### 1. INTRODUCTION

Si-based devices have been a cornerstone in power electronics field and implemented in a wide range of applications in order to assist signal processing or energy conversion [1]. Si-based devices have dominated power electronics for several decades. However, an increasing demand for energy conversion has been observed in global power electronics market. The development and adoption of wide bandgap (WBG) power semiconductors are projected to result in a breakthrough in power electronics field.

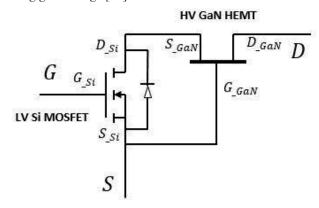

Recently, significant efforts have been made by researchers in wide bandgap (WBG) power devices owing to their superior characteristics and properties over that of current dominant Si devices, such as higher breakdown field, higher mobility and higher power density [2]-[5]. GaN-based device has been assumed as a very promising candidate in the low-medium voltage range applications [6]-[12], owing to GaN device presents excellent performance in accordance with its theoretical characteristics and corresponding technological process among all potential candidates [13]. Currently, there are two types of GaN power devices available in the commercial market, namely, enhancement-mode GaNFETs and cascode GaNFETs. The traditional e-mode GaNFETs have relatively low gate threshold voltage  $(V_{th})$  and narrow gate driving voltage safety margin, which poses a significant difficulties in terms of gate drive circuitry design. Different from e-mode GaNFET, cascode GaNFET is constructed by two discrete devices, a LV Si MOSFET and a HV GaN HEMT as illustrated in Fig. 1.

Thanks to the implementation of LV Si MOSFET within cascode GaN device package, the gate threshold voltage is much higher than that of e-mode GaN device. Moreover, cascode GaNFETs can withstand a maximum 10V over-driving gate voltage [14].

Fig.1. Cascode GaN device configuration

There are multiple cascode GaN-based converters/inverters that have been introduced by Transphorm [15]. In the meantime, significant research related to parasitic effect in GaN-based design have been studied in [16]–[21]. All of these presented research works are mainly focusing on the evaluation of the effect of common source inductance and parasitic inductance in power loop for GaNFET-based design. It is worth pointing out that cascode GaNFETs exhibit higher input capacitance in comparison with e-mode GaNFET, due to the existence of an unavoidable high-frequency gate-source

<sup>\*</sup>e-mail: qtan5@sheffield.ac.uk

Q.Y. Tan and E.M.S. Narayanan

voltage ringing. In this work, TPH3205WSB in TO-247 package from Transphorm is used for evaluation.

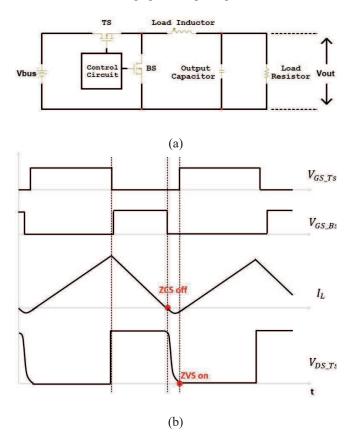

This paper evaluates the effect of gate drive circuit design to cascode GaN devices and accordingly proposes a simple approach to improve system efficiency for cascode GaNbased design. A SPICE-based simulation model is made in accordance with the experimental measurement of cascode GaNFET (TPH3205WSB), which is used further to access the effect of different gate driving loop design to the overall efficiency of cascode GaN-based buck converter. Moreover, a synchronous buck converter prototype with proposed gate drive design is made and tested with hard switching (CCM) and soft-switching (CRM) for the aim of evaluation. The hard switching operation, also known as continuous conduction mode (CCM), where the energy in the load inductor continuously flows through the converter during normal operation. The power transfer can be simply divided into two steps. When top switch is ON, the inductor stores energy; when top switch is OFF, the energy stored in load inductor will be transferred to output load. The critical conduction mode (CRM) is selected for soft switching demonstration. Due to the CRM can easily achieve zero voltage switching turn-on for top switch and zero current switching turn-off for bottom switch with synchronous buck converter topology used in this work. Fig. 2 shows the buck converter scheme and the CRM soft switching operation principle used in this work.

Fig. 2. (a) Buck converter scheme; (b) CRM operation principle

### 2. Gate drive circuit consideration for cascode GaN devices

#### A. Finds in experimental measurement

In order to find out the impact of gate drive circuit to the switching performance of cascode GaN device. A series of double pulse test (DPT) were conducted to collect experimental result, which consists of a (TPH3205WSB) and a SiC diode (FFSH3065B-F085). Three PCBs with different gate drive circuitry design were made for the comparison purpose. Table.1 shows the two critical parasitic inductance extracted via Ansys Q3D from gate drive loop in three PCBs. The PCB Version 1 exhibit highest gate turn-on inductance and source-side inductance among three PCBs. The PCB Version 2 is made with higher gate turn-on inductance and smaller source-side inductance in comparison to PCB Version 1 for investigation purpose. The PCB Version 3, which has least gate turn-on inductance and source-side inductance. Methods to lower PCB Version 3 inductance in gate driving loop is: (a) ground plane is used to minimize the physical trace length between GND pin of the gate driver IC and the source pin of the device; (b) remove all vias around gate driving loop/switching node; (c) place gate turn-on path and return path as close as possible.

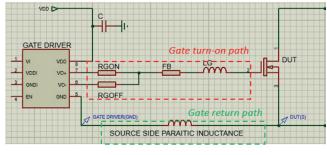

The gate turn-on inductance indicates the total parasitic inductance in gate turn-on path, whereas source-side inductance is the sum of the parasitic inductance in gate return path. Fig. 3 shows the location of these two important parasitic inductance and the way to measure the voltage ringing caused by source-side inductance.

Table 1. Parasitic inductacnce extraction within gate drive loop

| Parameter                  | PCB Version<br>1 (Original<br>board) | PCB Version<br>2 | PCB Version<br>3 |  |

|----------------------------|--------------------------------------|------------------|------------------|--|

| Gate turn-on inductance/nH | 5.6012                               | 9.4462           | 4.4326           |  |

| Source-side inductance/nH  | 10.376                               | 4.2235           | 1.092            |  |

Fig. 3. Key parasitic inductance in gate driving loop and source-side ringing measurement

#### Evaluation of gate drive circuit effect in Cascode GaN-based applications

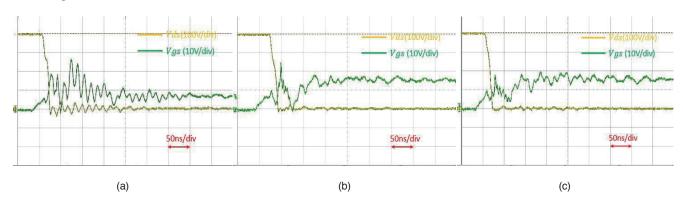

Fig. 4 shows the gate-source voltage and drain-source voltage measurement from oscilloscope. All data as concluded in Table 2. In accordance with the measurement result, the PCB Version 1 shows a significant gate-source voltage oscillation as large as 28.4V in turn-on event, which is 8.4V higher than specified  $V_{as\ max}$  (20V) [22]. Even the high gate-source voltage spikes disappear within 6ns, the drain-source voltage waveform still affected by this high gate-source voltage oscillation as depicted in Fig. 4(a). Compared to PCB Version 1, the Version 2 exhibits 3.845nH higher gate turn-on inductance while 6.1525nH lower source side inductance. However, the Version 2 board shows a 15.4V reduction in gate-source voltage during turn-on process. Furthermore, the source-side high frequency ringing has reduced from 510ns in PCB Version 1 to 360ns in PCB Version 2. In contrast, the turn-on inductance is not the only one determinant of gatesource voltage. The PCB Version 3 is made for further

investigation, which has minimum turn-on inductance (4.4326nH) and source-side inductance (1.092nH) among these three boards. As shown in Table 3, PCB Version 3 attain a 15.5 V reduction in source-side ringing and a 320ns shorter source-side ringing duration in comparison to those of PCB Version 1.

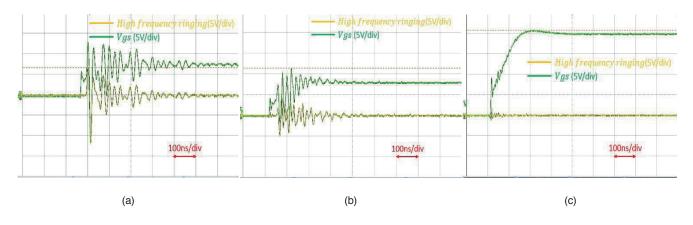

In accordance with the gate-source voltage and source-side voltage measurement as shown in Fig. 5. The gate-source voltage waveform is very similar to the source-side voltage waveform in term of duration time and frequency. As a result, the source-side inductance shows a more significant influence on the gate-source voltage in comparison with that of gate turn-on inductance. In an extreme case, such as PCB Version 1, such high frequency gate voltage ringing caused by source-side inductance can affect the drain-source waveform as illustrated in Fig. 4(a)

Fig. 4. Gate-source voltage and drain-source voltage measurement @400V/5A turn-on of (a) PCB Version 1; (b) PCB Version 2; (c) PCB Version 3

Fig. 5. Gate-source voltage and source-side voltage measurement @ Vds=100V of (a) PCB Version 1; (b) PCB Version 2; (c) PCB Version 3

Table 2. Detailed three PCBs experimental measurement result

|                          | PCB Version 1 (0 | Original board) | PCB V   | ersion 2 | PCB V   | ersion 3 |

|--------------------------|------------------|-----------------|---------|----------|---------|----------|

| Parameter / unit         |                  |                 |         |          |         |          |

|                          | Turn-on          | Turn-off        | Turn-on | Turn-off | Turn-on | Turn-off |

| Vgs <sub>pk-pk</sub> / V | 28.4             | 10.3            | 13      | 10       | 10.3    | 10       |

#### Q.Y. Tan and E.M.S. Narayanan

| Vgs <sub>Max</sub> / V                              | 26.3 | 7.8 | 12.2 | 8.1 | 9.6 | 8.1 |

|-----------------------------------------------------|------|-----|------|-----|-----|-----|

| Vds <sub>pk-pk</sub> / V                            | 438  | 403 | 413  | 406 | 409 | 400 |

| Vds <sub>Max</sub> / V                              | 400  | 400 | 397  | 400 | 402 | 399 |

| Source-side ringing @ Vds=100V / V                  | 18.3 |     | 9.9  |     | 2.8 |     |

| Time duration of source-side ringing @ Vds=100V/ ns |      | 0   | 3    | 360 | 19  | 90  |

# **B.** Simulation model of TPH3205WSB cascode GaNFET Transphorm provides the original SPICE model of cascode GaNFET TPH3205WSB, and this model has been modified by author based on experimental measurement result. The detailed

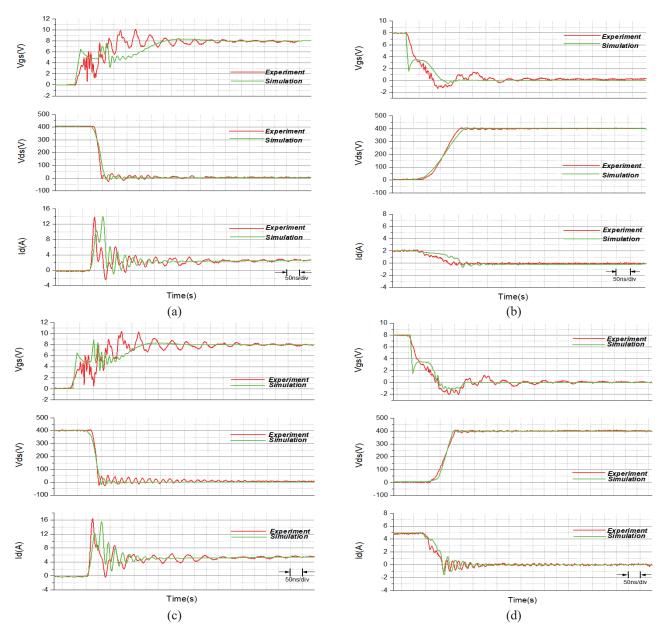

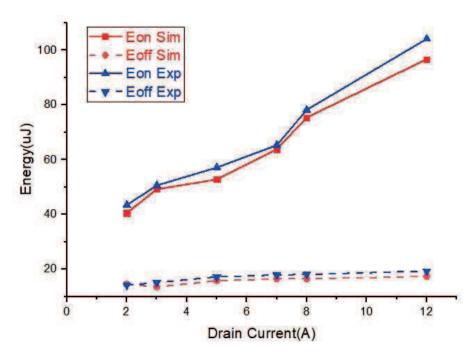

comparison between simulation model and experimental measurement as illustrated in Fig. 6. According to Fig. 7, when the device operating at 5A or lower current, the simulation model shows 3.9% and 5.8% difference from practical turn-on and turn-off switching loss respectively.

Fig. 6. PCB Version 3 switching waveform comparison between simulation model and experimental measurement of (a) turn-on @400V/2A; (b) turn-off @ 400V/2A; (c) turn-on @ 400V/5A; (d) turn-off @ 400V/5A

#### Evaluation of gate drive circuit effect in Cascode GaN-based applications

Fig. 7. PCB Version 3 switching loss comparison between simulation model and practical measurement

## 3. Implementation of optimized gate drive circuitry in buck converter

As drawn in Fig. 6 and Fig. 7, the simulation model only has very little difference from practical measurement. Therefore, a synchronous buck converter topology has been chosen in order to find out the advancement of PCB Version III with optimized source-side inductance.

#### A. Power loop parasitic inductance extraction.

Apart from parasitic inductance shown in Table 1, the inductance in power loop also play an important role in overall performance. In PCB Version 3, the value of power loop parasitic inductance is also extracted via Ansys Q3D as indicated in Fig. 8, which is formed by the power communication path from freewheeling diode to the coaxial current shunt.

All parasitic elements in PCB traces and components are included in the buck converter simulation in order to ensure the accuracy of the result. The list of key components and parameters used in simulation as shown in Table 3.

Fig. 8. Power loop parasitic inductance extraction of PCB Version 3

Table 3. Parameters/components used in SPICE-based simulation

| Component/parameter |                         | Value                        | Unit |

|---------------------|-------------------------|------------------------------|------|

|                     | name                    |                              |      |

| Loa                 | nd inductor             | 500                          | uН   |

| Turr                | n-on resistor           | 10                           | Ω    |

| Turn                | -off resistor           | 2                            | Ω    |

| Gate<br>driving     | Gate turn-on inductance | 5.6(Ver I)/4.43(Ver III)     | nН   |

| loop                | Source-side inductance  | 10.376(Ver I)/1.092(Ver III) | nН   |

| Power 1             | oop inductance          | 5.2                          | nН   |

| Bus voltage         |                         | 400                          | V    |

| Out                 | put voltage             | 200                          | V    |

| Switching frequency |                         | 100                          | kHz  |

#### Q.Y. Tan and E.M.S. Narayanan

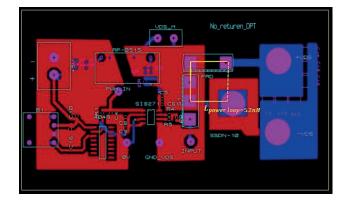

Cadence Orcad is a SPICE-based simulation software, which is selected to compare buck converter performance respect to different gate driving loop design. A synchronous buck converter is built in Cadence Orcad, consisting of two identical cascode GaN power devices, which are implemented as top and bottom switch in the design. All parameters filled into simulation are the same as PCB V1 and V3 for comparison purpose. Both hard-switching (CCM) and softswitching (CRM) operation are conducted in the simulation in order to determine the possible maximum efficiency of the converter with proposed gate drive circuitry. Meanwhile, a synchronous buck converter prototype with optimized gate driving loop and similar power loop parasitic inductance has made for experimental verification. Fig. 9 shows the synchronous buck converter prototype made in this work. An integrated gate driver (Si8230) with high CMTI and ultra-low propagation time from Silicon Laboratories is implemented in hardware. Regarding to CRM operation, the dead time between two switches is set to 59ns by connecting a  $5.9k\Omega$ resistor from the DT pin of the gate driver to its ground.

Fig. 9. Side-view of synchronous buck converter prototype and load inductor

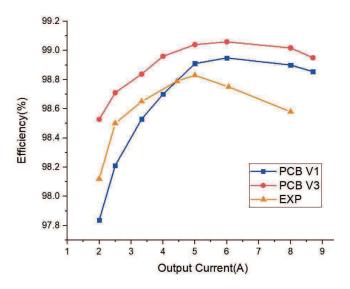

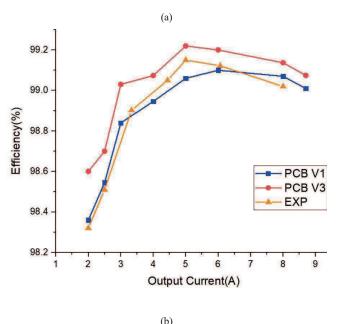

Fig. 10 shows the efficiency comparison between simulation result and prototype experimental result in CCM and CRM operation. The main difference between PCB V1 and PCB V3 is the gate drive circuitry design. PCB V3 has significant lower source-side parasitic inductance in gate return path in comparison to that of PCB V1 as shown in Table 1. Therefore, an obvious improvement in efficiency can be observed under both hard and soft switching modes in synchronous buck converter according to the simulation result. It is necessary to mention that the simulation model is less accurate at high current operation (>5A), due to simulation environment is set under constant room temperature. A hardware prototype with proposed gate drive design is made, which only exhibits 1nH parasitic inductance in gate return path. As drawn in Fig. 9, the prototype can attain a maximum efficiency of 98.79% at 4.4A under hard switching operation (CCM) and 99.15% efficiency at 5A under soft switching operation (CRM).

Fig. 10. Efficiency comparison between PCB V1&V3 simulation result and experimental measurement in (a) hard-switching (CCM); (b) soft-switching (CRM)

#### 4. Conclusion

This paper analyses the impact of gate driving loop to cascode GaNFET switching performance. As proved in this work, a careful gate drive circuit design with minimum source-side inductance can greatly reduce such voltage oscillation. Therefore, for any cascode GaN-based design, additional care for source-side inductance should be taken due to gate return path is more critical in comparison with gate turn-on path. Although this is not covered in this work, it is worth to point out that higher input capacitance (Ciss) of cascode GaN device in comparison with e-mode GaNFET leading to a slower switching transient and lower maximum operation frequency.

#### Evaluation of gate drive circuit effect in Cascode GaN-based applications

The purpose of such high input capacitance is to protect the unwanted gate-source voltage ringing caused by source-side inductance in gate driving loop. As analyzed in this work, when gate return path is optimised, cascode GaN devices no longer require that high input capacitance to ensure the stability of gate-source voltage. Hence, further development of cascode GaNFETs can be done by implementation of LV Si MOSFET with lower input capacitance. This can boost the switching speed of cascode GaNFETs, and hereby making use of the advantages that GaN brings.

A SPICE model is modified based on experimental measurement. Accordingly, a series of simulations using the modified model are conducted in order to find the influence of different gate drive circuit design. An improved operation of cascode GaNFET-based applications can be achieved with proposed gate drive circuitry design. Namely, an optimized gate return path is more important in comparison with gate turn-on path when cascode GaNFETs are used in the design. A synchronous buck converter prototype is made in this work, which attains a 99.15% efficiency at output current of 5A under soft switching mode.

#### **REFERENCES**

- Power Electronics UK and CSA CATAPULT, "Opportunities and Challenges of Wide Band Gap Power Devices," pp. 1–8, 2020.

- [2] E. A. Jones, F. F. Wang, and D. Costinett, "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 707–719, 2016.

- [3] H. Jain, S. Rajawat, and P. Agrawal, "Comparision of wide band gap semiconductors for power electronics applications," 2008 Int. Conf. Recent Adv. Microw. Theory Appl. Microw. 2008, pp. 878–881, 2008

- [4] S. Chowdhury, Z. Stum, Z. Da Li, K. Ueno, and T. P. Chow, "Comparison of 600V Si, SiC and GaN power devices," *Mater. Sci. Forum*, vol. 778–780, no. October 2015, pp. 971–974, 2014.

- [5] A. Taube, M. Sochacki, J. Szmidt, E. Kamińska, and A. Piotrowska, "Modelling and Simulation of Normally-Off AlGaN/GaN MOS-HEMTs," *Int. J. Electron. Telecommun.*, vol. 60, no. 3, pp. 253–258, 2014.

- [6] B. N. Pushpakaran, A. S. Subburaj, and S. B. Bayne, "Commercial GaN-Based Power Electronic Systems: A Review," *J. Electron. Mater.*, vol. 49, no. 11, pp. 6247–6262, 2020.

- [7] C. T. Ma and Z. H. Gu, "Review of GaN HEMT applications in power converters over 500 W," *Electron.*, vol. 8, no. 12, 2019.

- [8] H. Jain, S. Rajawat, and P. Agrawal, Comparision of wide band gap semiconductors for power electronics applications. 2008.

- [9] H. Umeda et al., "High power 3-phase to 3-phase matrix converter using dual-gate GaN bidirectional switches," Conf. Proc. - IEEE Appl. Power Electron. Conf. Expo. - APEC, vol. 2018-March, pp. 894–897, 2018.

- [10] K. Nowaszewski and A. Sikorski, "Predictive current control of three-phase matrix converter with GaN HEMT bidirectional switches," *Bull. Polish Acad. Sci. Tech. Sci.*, vol. 68, no. 4, pp. 1077–1085, 2020.

- [11] S. Y. Tang, "Study on characteristics of enhancement-mode gallium-nitride high-electron-mobility transistor for the design of gate drivers," *Electron.*, vol. 9, no. 10, pp. 1–11, 2020.

- J. Rąbkowski, K. Król, M. Zdanowski, and M. Sochacki, "GaNbased soft-switched active power buffer operating at ZCS problems of start-up and shut-down," *Bull. Polish Acad. Sci. Tech. Sci.*, vol. 68, no. 4, pp. 785–792, 2020.

S. Davis, "The Great Semi Debate: SiC or GaN?," 2019.

- [13] S. Davis, "The Great Semi Debate: SiC or GaN?," 2019.

[Online]. Available:

https://www.powerelectronics.com/technologies/power-management/article/21864289/the-great-semi-debate-sic-or-gan.

[Accessed: 20-Nov-2020].

- [14] Transphorm Inc., "Cascode vs. e-mode." [Online]. Available: https://www.transphormusa.com/en/gan-revolution/#casecode-vs-e-mode.

- [15] Transphrom Inc., "Design Resources." [Online]. Available: https://www.transphormusa.com/en/design-resources/#evaluation-kits. [Accessed: 20-Nov-2020].

- [16] Z. Liu, "Characterization and Application of Wide-Band- Gap Devices for High Frequency Power Conversion," 2017.

- [17] F. C. Lee and R. Burgos, "Characterization and Failure Mode Analysis of Cascode GaN HEMT Characterization and Failure Mode Analysis of Cascode GaN HEMT," 2014.

- [18] Z. Liu, X. Huang, F. C. Lee, and Q. Li, "Package parasitic inductance extraction and simulation model development for the high-voltage cascode GaN HEMT," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1977–1985, 2014.

- [19] K. Umetani, K. Yagyu, and E. Hiraki, "A design guideline of parasitic inductance for preventing oscillatory false triggering of fast switching GaN-FET," *IEEJ Trans. Electr. Electron. Eng.*, vol. 11, pp. S84–S90, 2016.

- [20] T. Ibuchi and T. Funaki, "A study on parasitic inductance reduction design in GaN-based power converter for highfrequency switching operation," 2017 Int. Symp. Electromagn. Compat. - EMC Eur. 2017, EMC Eur. 2017, pp. 0–4, 2017.

- [21] B. Sun, Z. Zhang, and M. A. E. Andersen, "Research of low inductance loop design in GaN HEMT application," *Proc. IECON 2018 - 44th Annu. Conf. IEEE Ind. Electron. Soc.*, pp. 1466–1470, 2018.

- [22] Transphorm Inc., "TPH3205WSB 650V GaN FET in TO -247 (source tab)," vol. 247, pp. 1–13, 2017.