# FAULT DIAGNOSIS AND CONDITION MONITORING OF POWER ELECTRONIC COMPONENTS USING SPREAD SPECTRUM TIME DOMAIN REFLECTOMETRY (SSTDR) AND THE CONCEPT OF DYNAMIC SAFE OPERATING AREA (SOA)

A DISSERTATION IN Electrical Engineering and Mathematics

Presented to the Faculty of the University of Missouri-Kansas City in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

by SOUROV ROY

M.S., Electrical Engineering, University of Missouri-Kansas City, 2020

> Kansas City, Missouri 2021

© 2021

SOUROV ROY

ALL RIGHTS RESERVED

FAULT DIAGNOSIS AND CONDITION MONITORING OF POWER ELECTRONIC COMPONENTS USING SPREAD SPECTRUM TIME DOMAIN REFLECTOMETRY (SSTDR) AND THE CONCEPT OF DYNAMIC SAFE OPERATING AREA (SOA)

Sourov Roy, Candidate for the Doctor of Philosophy Degree

University of Missouri-Kansas City, 2021

#### **ABSTRACT**

Fault diagnosis and condition monitoring (CM) of power electronic components with a goal of improving system reliability and availability have been one of the major focus areas in the power electronics field in the last decades. Power semiconductor devices such as metal oxide semiconductor field-effect transistor (MOSFET) and insulated-gate bipolar transistor (IGBT) are considered to be the most fragile element of the power electronic systems and their reliability degrades with time due to mechanical and thermo-electrical stresses, which ultimately leads to a complete failure of the overall power conversion systems. Therefore, it is important to know the present state of health (SOH) of the power devices and the remaining useful life (RUL) of a power converter in order to perform preventive scheduled maintenance, which will eventually lead to increased system availability and reduced cost. In conventional practice, device aging and lifetime prediction techniques rely on the estimation of the meantime to failure (MTTF), a value that represents the expected lifespan of a device. MTTF predicts expected lifespan, but cannot adequately predict failures attributed to unusual circumstances or continuous overstress and premature degradation. This inability is due in large part to the fact that it considers the device safe operating area (SOA) or voltage and current ride-through capability to be independent of SOH. However, we experimentally proved that SOA of any semiconductor device goes down with the increased level of aging, and therefore, the probability of occurrence of over-voltage/current situation increases. As a result, the MTTF of the device as well as the overall converter reliability reduces with aging. That said, device degradation can be estimated by accomplishing an accurate online degradation monitoring tool that will determine the dynamic SOA. The correlation between aging and dynamic SOA gives us the useful remaining life of the device or the availability of a circuit. For this monitoring tool, spread spectrum time domain reflectometry (SSTDR) has been proposed and was successfully implemented in live power converters. In SSTDR, a highfrequency sine-modulated pseudo-noise sequence (SMPNS) is sent through the system, and reflections from age-related impedance discontinuities return to the test end where they are analyzed. In the past, SSTDR has been successfully used for device degradation detection in power converters while running at static conditions. However, the rapid variation in impedance throughout the entire live converter circuit caused by the fast-switching operation makes CM more challenging while using SSTDR. The algorithms and techniques developed in this project have overcome this challenge and demonstrated that the SSTDR test data are consistent with the aging of the power devices and do not affect the switching performance of the modulation process even the test signal is applied across the gate-source interface of the power MOSFET. This implies that the SSTDR technique can be integrated with the gate driver module, thereby creating a new platform for an intelligent gate-driver architecture (IGDA) that enables realtime health monitoring of power devices while performing features offered by a commercially available driver.

Another application of SSTDR in power electronic systems is the ground fault prediction and detection technique for PV arrays. Protecting PV arrays from ground faults that lead to fire hazards and power loss is imperative to maintaining safe and effective solar power operations. Unlike many standard detection methods, SSTDR does not depend on fault current, therefore, can be implemented for testing ground faults at night or low illumination. However, wide variation in impedance throughout different materials and interconnections makes fault location more challenging than fault detection. This barrier was surmounted by the SSTDR-based fault detection algorithm developed in this project. The proposed algorithm was accounted for any variation in the number of strings, fault resistance, and the number of faults. In addition to its general utility for fault detection, the proposed algorithm can identify the location of multiple faults using only a single measurement point, thereby working as a preventative measure to protect the entire system at a reduced cost.

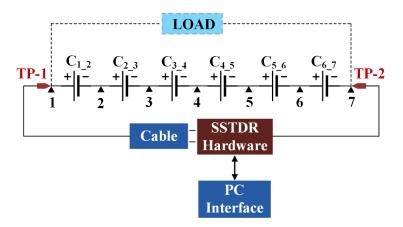

Within the scope of the research work on SSTDR-based fault diagnosis and CM of power electronic components, a cell-level SOH measurement tool has been proposed that utilizes SSTDR to detect the location and aging of individual degraded cells in a large seriesparallel connected Li-ion battery pack. This information of cell level SOH along with the respective cell location is critical to calculating the SOH of a battery pack and its remaining useful lifetime since the initial SOH of Li-ion cells varies under different manufacturing processes and operating conditions, causing them to perform inconsistently and thereby affect the performance of the entire battery pack in real-life applications. Unfortunately, today's BMS considers the SOH of the entire battery pack/cell string as a single SOH and therefore, cannot monitor the SOH at the cell level. A healthy battery string has a specific impedance between the two terminals, and any aged cell in that string will change the impedance value. Since

SSTDR can characterize the impedance change in its propagation path along with its location, it can successfully locate the degraded cell in a large battery pack and thereby, can prevent premature failure and catastrophic danger by performing scheduled maintenance.

#### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies have examined a dissertation titled "Fault Diagnosis and Condition Monitoring of Power Electronic Components Using Spread Spectrum Time Domain Reflectometry (SSTDR) and the Concept of Dynamic Safe Operating Area (SOA)" presented by Sourov Roy, candidate for the Doctor of Philosophy degree, and certify that in their opinion it is worthy of acceptance.

## **Supervisory Committee**

Faisal Khan, Ph.D., Committee Chair Department of Computer Science and Electrical Engineering

> Yong Zeng, Ph.D., Co-discipline Advisor Department of Mathematics and Statistics

Ghulam Chaudhry, Ph.D.

Department of Computer Science and Electrical Engineering

Masud Chowdhury, Ph.D.

Department of Computer Science and Electrical Engineering

Ahmed Hassan, Ph.D. Department of Computer Science and Electrical Engineering

> Kamel Rekab, Ph.D. Department of Mathematics and Statistics

# **CONTENTS**

| ABSTRA  | ACT                                                                    | iii    |

|---------|------------------------------------------------------------------------|--------|

| LIST OF | FILLUSTRATIONS                                                         | xii    |

| LIST OF | F TABLES                                                               | xviii  |

| ACKNO   | WLEDGEMENTS                                                            | xix    |

|         |                                                                        |        |

| Chapter |                                                                        |        |

| 1 INT   | RODUCTION                                                              | 1      |

| 2 BAG   | CKGROUND STUDY AND LITERATURE REVIEW                                   | 10     |

| 2.1     | Degradation Assessment and Precursor Identification of Power Semicondu | ictor  |

| Device  | e in Live Power Converters                                             | 10     |

| 2.1.    | 1 Degradation Mechanism and Effect of Aging on Measurable Parameter    | ers 11 |

| 2.1.2   | 2 Existing Aging Measurement Techniques and Their Limitations          | 13     |

| 2.2     | PV Ground Fault Detection                                              | 16     |

| 2.2.    | 1 Reasons for PV Ground Faults                                         | 17     |

| 2.2.2   | 2 Standard Ground Fault Protection Devices and Their Limitations       | 17     |

| 2.2.    | 3 Existing Ground Fault Detection Techniques and Their Limitations     | 19     |

| 2.3     | Detection of Degraded Cell in a Li-ion Battery Pack                    | 21     |

| 2.3.    | Origin of Cell-level Degradation in a Li-ion Battery Pack              | 22     |

| 2.3.2   | 2 Limitations of Existing Li-ion SOH Estimation Methods                | 22     |

| 3 FUN   | NDAMENTALS OF SPREAD SPECTRUM TIME DOMAIN REFLECTO                     | METRY  |

| (SSTDR  | ): A NEW METHOD FOR TESTING ELECTRONICS LIVE                           | 24     |

| 3.1     | Basic Concepts of Reflectometry                                        | 24     |

| 3.2     | SSTDP Operation                                                        | 25     |

|   | 3.3  | Inf     | fluence of the Failure Precursor Parameters on SSTDR Due to Device Aging 2      | 9 |

|---|------|---------|---------------------------------------------------------------------------------|---|

|   | 3.4  | Αg      | ging Detection from the Gate-Source Interface: A Platform for Intelligent Gate- |   |

|   | Driv | er Aı   | rchitecture                                                                     | 2 |

|   | 3.   | 4.1     | Tentative Implementation Plan of the Intelligent Gate Driver Module 3-          | 4 |

| 4 | A    | CCE     | LERATED AGING TEST BENCH: DESIGN AND IMPLEMENTATION 3                           | 8 |

|   | 4.1  | Ac      | etive Power Cycling Test Bench for Power MOSFETs                                | 8 |

|   | 4.2  | Ac      | eccelerated Battery Cycling Test Bench for Li-ion Cells                         | 3 |

| 5 | C    | OND     | ITION MONITORING OF POWER SWITCHING DEVICES IN LIVE POWER                       | ) |

| E | LEC' | TRO     | NIC CONVERTERS USING SSTDR4                                                     | 6 |

|   | 5.1  | Ca      | se Study-1: Condition Monitoring of a Single-Phase H-bridge Grid-Tied PV        |   |

|   | Inve | erter A | Applying SSTDR Signal Across AC output Node                                     | 7 |

|   | 5.   | 1.1     | Equivalent Path Impedances                                                      | 7 |

|   | 5.   | 1.2     | Experimental Set-up and Results                                                 | 0 |

|   |      | 5.1.2   | Histogram/Amplitude Distribution                                                | 2 |

|   | 5.2  | Ca      | se Study-2: Condition Monitoring of Power Converters using SSTDR Embedded       | Į |

|   | PWI  | M Se    | quence                                                                          | 4 |

|   | 5.   | 2.1     | Degradation Detection of Power Devices in a Live DC-DC Converter 5-             | 4 |

|   |      | 5.2.1   | .1 Condition Monitoring of a Single Switch Buck Converter 5.                    | 5 |

|   |      | 5.2.1   | .2 Condition Monitoring of a Synchronous Buck Converter: Aging Detection        | l |

|   |      | of M    | Tultiple Switching Devices from a Single Measurement Point                      | 7 |

|   | 5.   | 2.2     | Degradation Detection of Power Devices in a Live Three-Phase Inverter 6         | 2 |

|   |      | 5.2.2   | A Modification in the Switching Scheme: Better Accuracy and Flexibility         |   |

|   |      | in Co   | ondition Monitoring of a Live Three-Phase Inverter                              | 2 |

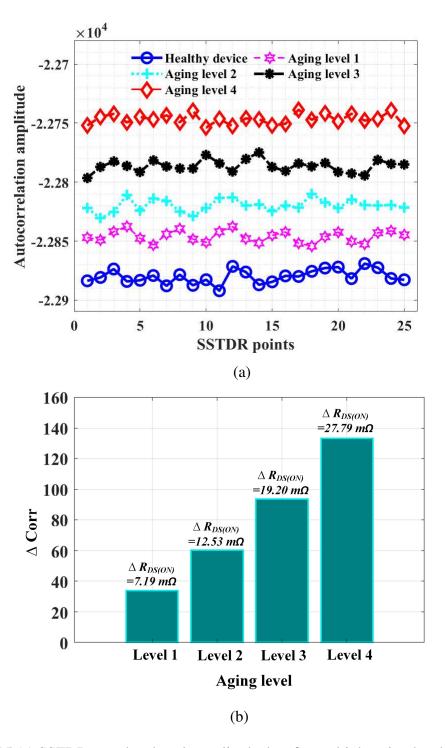

|          | 5.    | .2.2.2   | Quantifying Degradation Levels in a Power Device of a Live Three-Ph     | ase |

|----------|-------|----------|-------------------------------------------------------------------------|-----|

|          | In    | nverter  |                                                                         | 68  |

|          | 5.    | .2.2.3   | Aging Detection of Multiple Power Devices in a Live 3-Phase Inverter    |     |

|          | us    | sing a S | ingle Access/ Measurement Point                                         | 71  |

| 5.       | 3     | Discus   | sion                                                                    | 74  |

| 5.       | 4     | Conclu   | sion                                                                    | 75  |

| 6        | AN    | IRRAD    | DIANCE-INDEPENDENT, ROBUST GROUND-FAULT DETECTION                       |     |

| SCF      | ŀЕМ   | E FOR    | PV ARRAYS BASED ON SSTDR                                                | 77  |

| 6.       | 1     | Ground   | d Fault Detection Algorithm                                             | 77  |

|          | 6.1.  | 1 Ba     | seline Creation                                                         | 80  |

|          | 6.1.  | 2 Sy     | stem Noise Estimation                                                   | 81  |

|          | 6.1.  | 3 Fa     | ult Detectionult                                                        | 82  |

| 6.       | 2     | Impact   | of Different Parameters on Ground Fault Detection Algorithm             | 84  |

|          | 6.2.  | 1 Im     | pact of Carrier Frequency                                               | 85  |

|          | 6.2.2 | 2 Im     | pact of Fault Resistance                                                | 87  |

|          | 6.2.  | 3 Im     | apact of Parallel Connected Strings                                     | 90  |

|          | 6.2.  | 4 Im     | pact of Solar Irradiance                                                | 92  |

|          | 6.2.: |          | ouble Ground Fault                                                      | 94  |

| 6.       | 3     | Conclu   | sion                                                                    | 95  |

| 7        | DET   |          | ON OF DEGRADED/AGED CELL IN A LI-ION BATTERY PACK USI                   |     |

|          |       |          |                                                                         |     |

| 7.       |       |          | mental Set-up for Locating Aged Cell in a Series Connected Battery Pack |     |

| 7.<br>7. |       | _        | on Detection of Individual Aged Cells Using SSTDR                       |     |

| , .      | _     | Locali   | in Detection of marriada rigod comb Comig DOIDIC                        | )   |

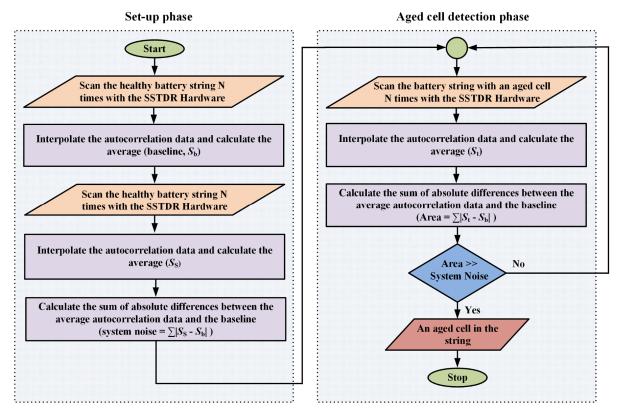

| 7.2.1 Proposed Algorithm                                                     | 98    |

|------------------------------------------------------------------------------|-------|

| 7.3 Conclusion                                                               | . 103 |

| 8 DYNAMIC SAFE OPERATING AREA (SOA) OF POWER SEMICONDUCTOR                   |       |

| DEVICES                                                                      | . 104 |

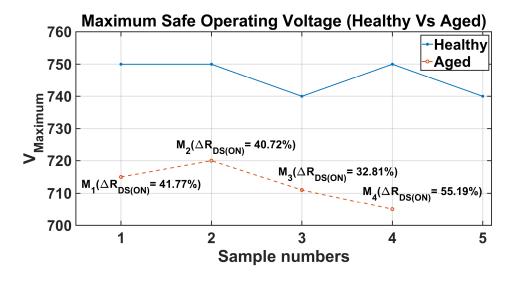

| 8.1 A Case Study Showing How Reduced SOA Can Reduce Availability             | . 105 |

| 8.2 The Relationship Between Aging and Dynamic SOA                           | . 106 |

| 8.2.1 Why Aging Reduces Maximum Safe Operating Voltage                       | . 106 |

| 8.2.2 Why Aging Reduces Maximum Safe Operating Current                       | . 107 |

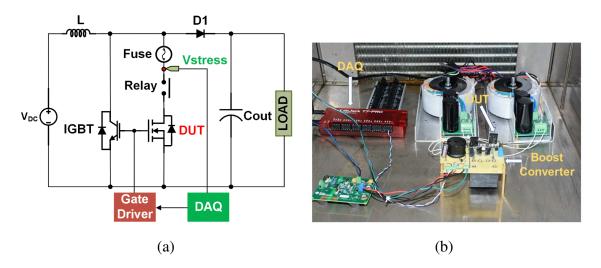

| 8.2.3 Experimental Set-up and Results: Characterizing Maximum Safe Operating | 3     |

| Voltage as a Function of Aging                                               | . 108 |

| 8.3 Conclusion                                                               | . 111 |

| 9 CONCLUSION AND FUTURE RESEARCH                                             | . 112 |

| REFERENCES                                                                   | .117  |

| VITA                                                                         | 133   |

# **ILLUSTRATIONS**

| Figure Page                                                                                                 |

|-------------------------------------------------------------------------------------------------------------|

| Figure 1.1 Block diagram of the proposed steps involved in the work strategy in determining                 |

| remaining lifetime estimation of power semiconductors                                                       |

| Figure 2.1 Survey of different components responsible for converter failure [86] 10                         |

| Figure 2.2 (a) Formation of cracks and voids in a power MOSFET due to aging and (b) wire                    |

| bonding failure [7].                                                                                        |

| Figure 2.3 Typical grounding diagram of PV arrays. The GFDI fuse (system ground) is                         |

| usually installed inside the PV inverter in a grounded PV array, and system grounding is                    |

| absent in an ungrounded PV array [53]                                                                       |

| Figure 3.1 Schematic diagram of a transmission line of length $L$ and characteristic impedance              |

| equal to $Z_0$ . A generator circuit is connected at one end $(d=-L)$ , and other end $(d=-0)$ is           |

| connected to load Z <sub>L</sub> 24                                                                         |

| Figure 3.2 Schematic diagram of the SSTDR mechanism [36]                                                    |

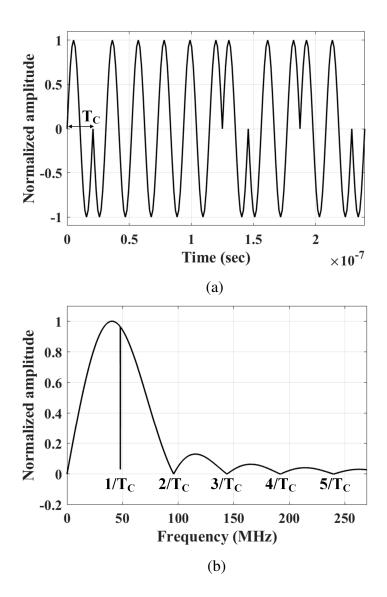

| Figure 3.3 Incident signal of SSTDR with carrier/center frequency equal to 48 MHz: (a)                      |

| time-domain representation (a portion of one entire SSTDR sequence is shown here),                          |

| and (b) frequency-domain (FFT) representation (only the upper side band is shown                            |

| here)                                                                                                       |

| Figure 3.4 Photograph of the FPGA-based SSTDR hardware (an R&D product from                                 |

| Livewire Innovation)                                                                                        |

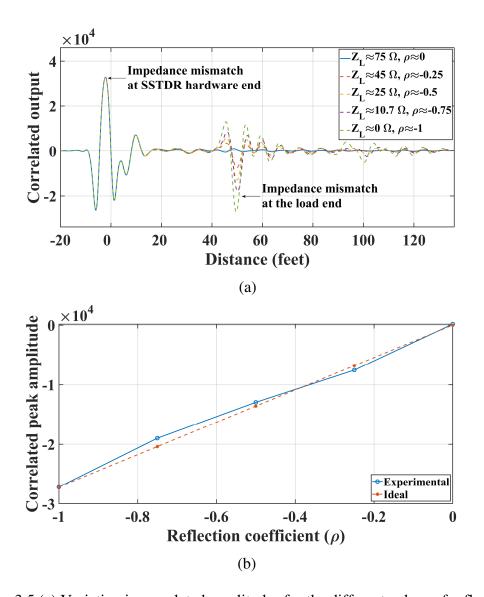

| Figure 3.5 (a) Variation in correlated amplitudes for the different values of reflection                    |

| coefficients ( $\rho \le 0$ ) and load impedances ( $Z_L \le Z_0$ ) (for 50 feet long, 75 $\Omega$ co-axial |

| cable), and (b) variation in the corresponding correlated peak amplitudes for the            |

|----------------------------------------------------------------------------------------------|

| different values of reflection coefficients ( $\rho \le 0$ ).                                |

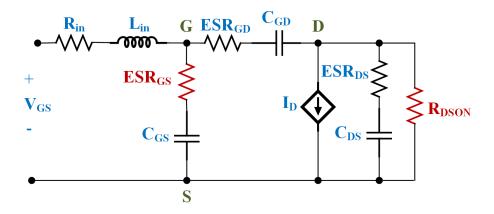

| Figure 3.6 Simplified equivalent circuit of a power MOSFET [112]                             |

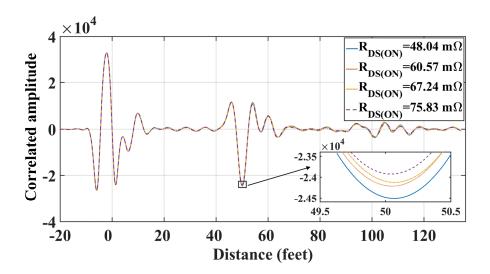

| Figure 3.7 Correlated amplitude variation for different aging levels (corresponding to       |

| different values of $R_{\rm DS(ON)}$ ) of a power MOSFET in a buck converter                 |

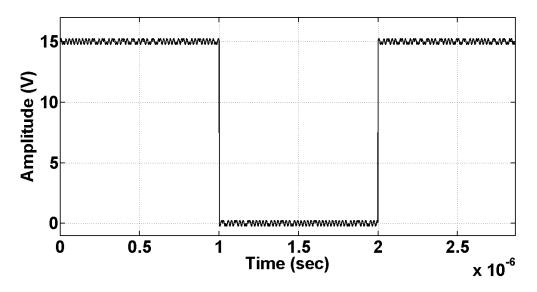

| Figure 3.8 A 100 mV (p-p), 48 MHz SSTDR incident signal superimposed on a 15 V, 500          |

| kHz PWM sequence (with a 50% duty cycle)                                                     |

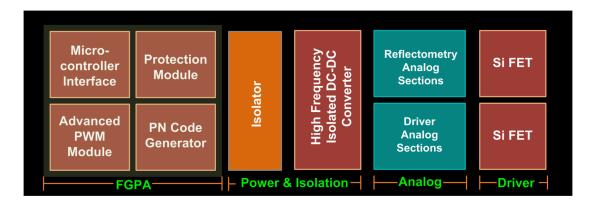

| Figure 3.9 Tentative layout of the proposed intelligent gate driver module                   |

| Figure 3.10 A simplified block diagram of the SSTDR-ASIC integration pathway, coined as      |

| "Livewire IC" [120]                                                                          |

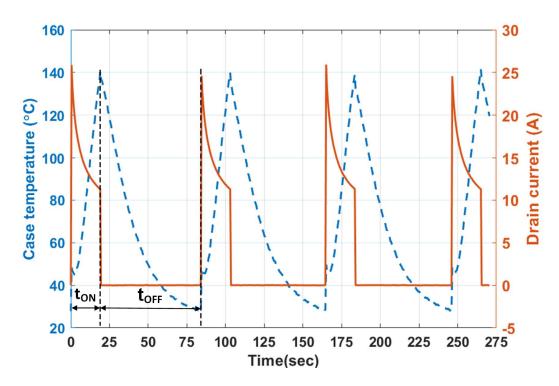

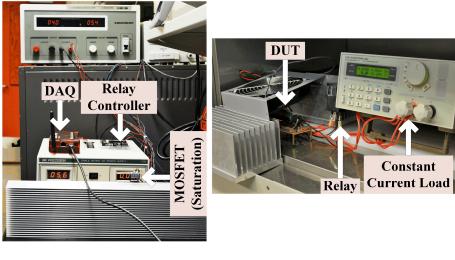

| Figure 4.1 Case temperature and drain current swing of the DUT during power cycling test o   |

| phase-24                                                                                     |

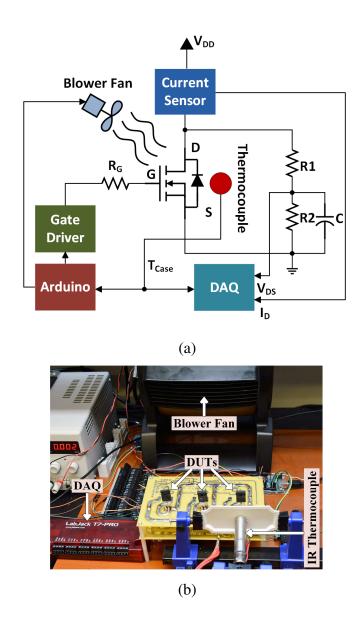

| Figure 4.2 (a) Schematic and (b) photograph of the experimental set-up for accelerated aging |

| test4                                                                                        |

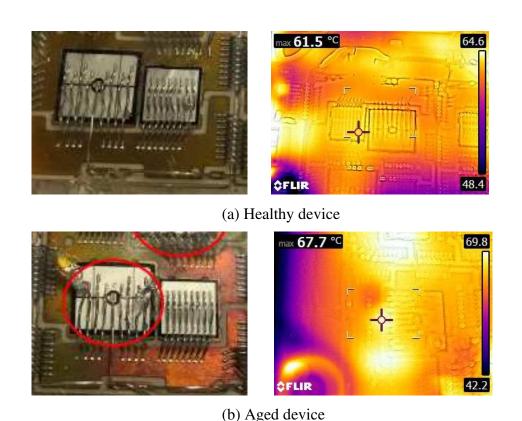

| Figure 4.3 Thermal image captured during the aging process                                   |

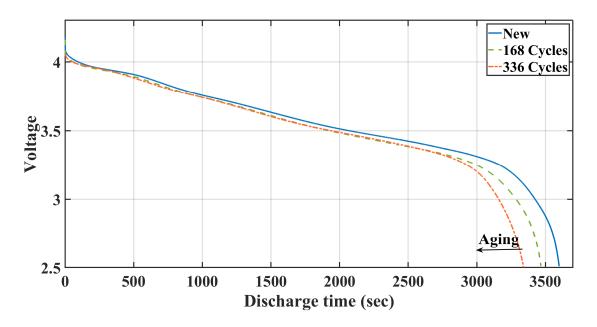

| Figure 4.4 Battery aging station, (a) schematic and (b) photograph 4-                        |

| Figure 4.5 Discharge profile of a Li-ion cell after different charging-discharging cycles 4  |

| Figure 5.1 SSTDR test diagram for detecting device degradation in a single-phase H-bridge    |

| grid-tied PV inverter4                                                                       |

| Figure 5.2 Switching scheme used in the single-phase H-bridge grid-tied PV inverter under    |

| test A <sup>1</sup>                                                                          |

| Figure 5.3 Various equivalent SSTDR impedance paths inside the PV inverter. Here, $Z_{cap}$ =       |

|-----------------------------------------------------------------------------------------------------|

| impedance of the DC bus capacitor, $R_{DS}$ = ON-state channel resistance of the MOSFET,            |

| and $Z_p$ = lumped impedance due to the parasitic capacitances of the MOSFET                        |

| Figure 5.4 Experimental test set-up for condition monitoring of H-bridge grid-tied PV               |

| inverter under test. 50                                                                             |

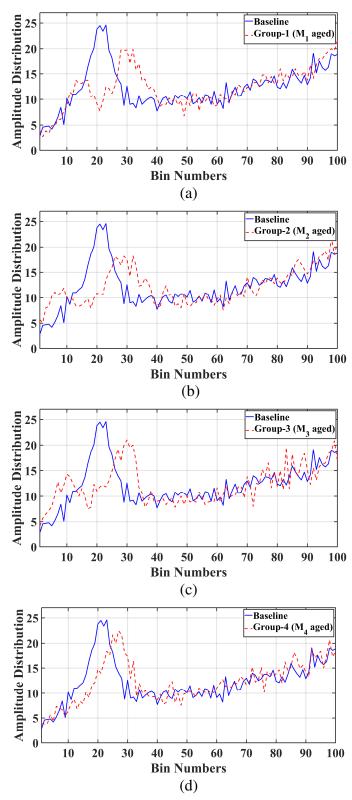

| Figure 5.5 Amplitude distribution-comparison between baseline and an aged MOSFET at (a)             |

| $M_1$ position: aged $M_1$ (Group 1), (b) $M_2$ position: aged $M_2$ (Group 2), (c) $M_3$ position: |

| aged $M_3$ (Group 3), and (d) $M_4$ position: aged $M_4$ (Group 4)                                  |

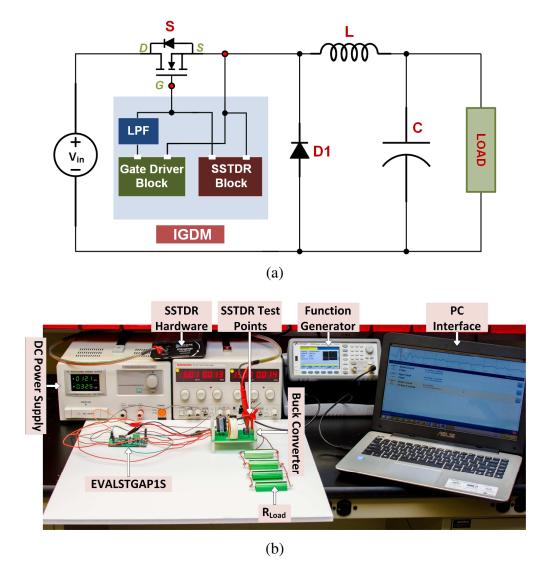

| Figure 5.6 Experimental set-up for condition monitoring of a single switch buck converter:          |

| (a) schematic, and (b) photograph.                                                                  |

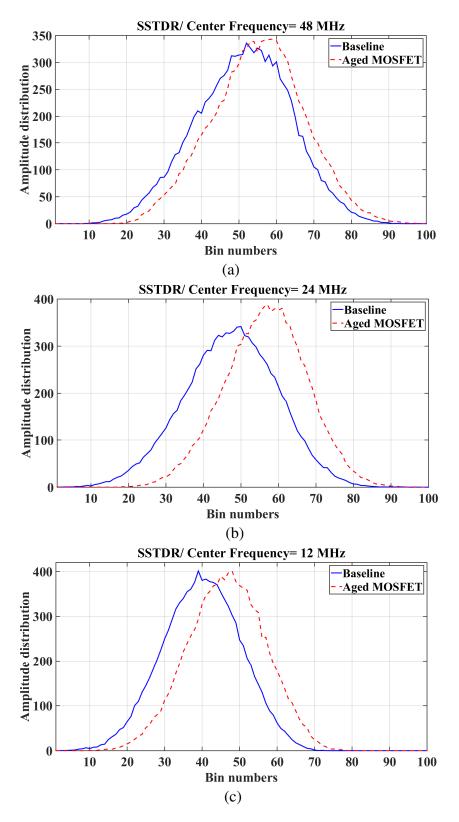

| Figure 5.7 Amplitude distribution comparisons for single switch buck converter for SSTDR            |

| frequencies: (a) 48 MHz, (b) 24 MHz, and (c) 12 MHz                                                 |

| Figure 5.8 Experimental set-up for condition monitoring of a synchronous buck converter:            |

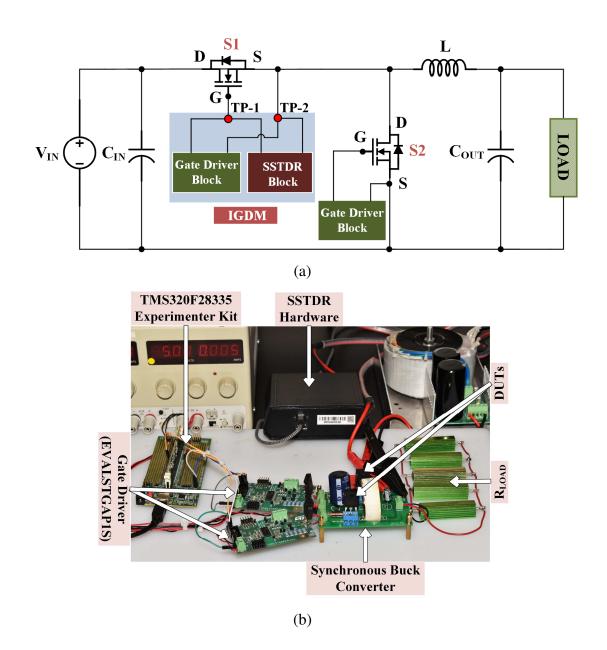

| (a) schematic, and (b) photograph. Here, IGDM= intelligent gate driver module 59                    |

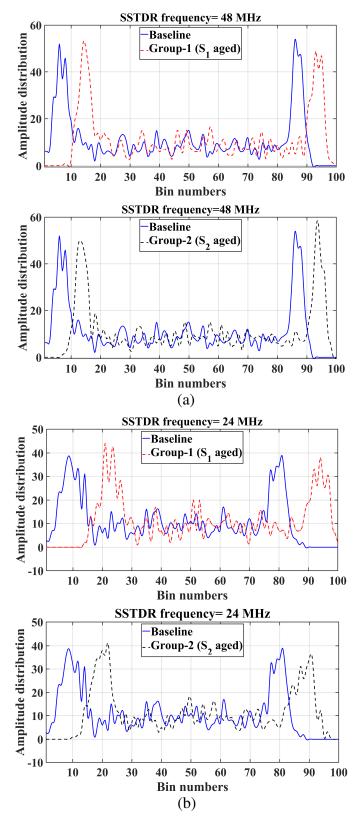

| Figure 5.9 Comparison of amplitude distributions for synchronous buck converter: (a)                |

| SSTDR frequency= 48 MHz, and (b) SSTDR frequency= 24 MHz                                            |

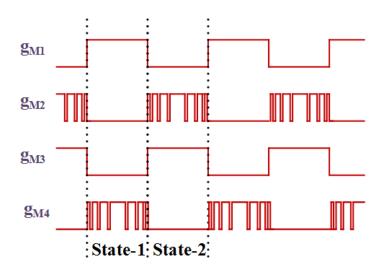

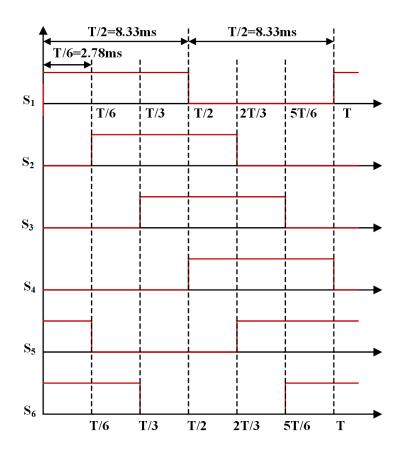

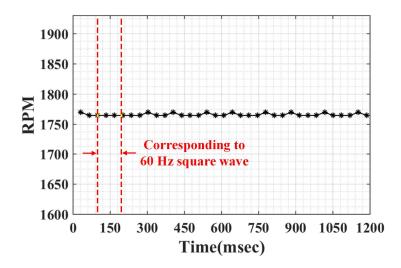

| Figure 5.10 A 60 Hz square wave mode switching scheme of a three-phase inverter 65                  |

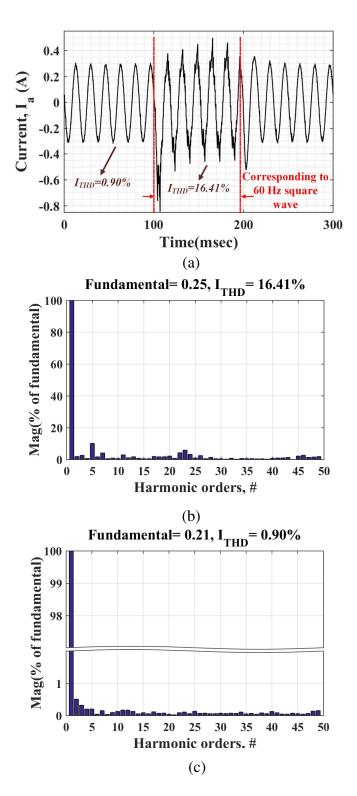

| Figure 5.11 (a) a-phase current waveform of the three-phase induction motor at two different        |

| switching modes of the inverter, (b) corresponding $I_{THD}$ at 60 Hz square wave mode, and         |

| (c) corresponding <i>I</i> <sub>THD</sub> at 30 kHz SPWM mode60                                     |

| Figure 5.12 RPM of the 3-phase induction motor at two different switching modes of the              |

| inverter6                                                                                           |

| Figure 5.13 Prototype of a three-phase inverter running an induction motor                          |

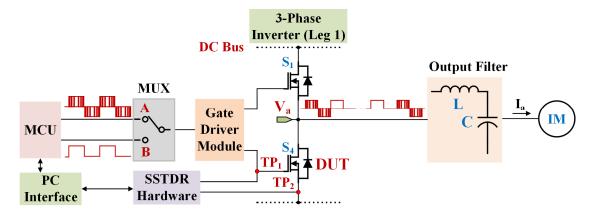

| Figure 5.14 Block diagram of the proposed synchronization scheme where SSTDR signal is          |

|-------------------------------------------------------------------------------------------------|

| synchronized with 60 Hz square wave gate signal at Leg 1 of the inverter                        |

| Figure 5.15 (a) SSTDR correlated peak amplitude data for multiple aging levels of $S_4$ -       |

| MOSFET, and (b) changes in the average SSTDR correlated peak amplitude data for                 |

| multiple aging levels of $S_4$ -MOSFET. Here, initial $R_{\rm DS(ON)}$ of the healthy MOSFET is |

| 48.04  mΩ. 70                                                                                   |

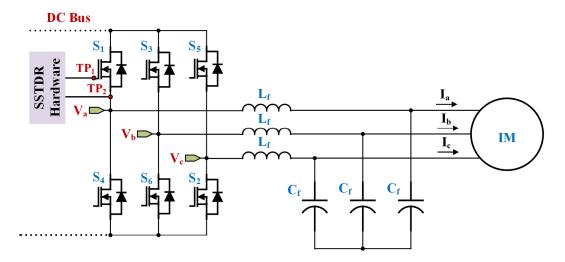

| Figure 5.16 Schematic of the three-phase inverter prototype connected with an induction         |

| motor. Here, SSTDR test signal is synchronized with 60 Hz square wave gate signal of            |

| <i>S</i> <sub>1</sub> MOSFET71                                                                  |

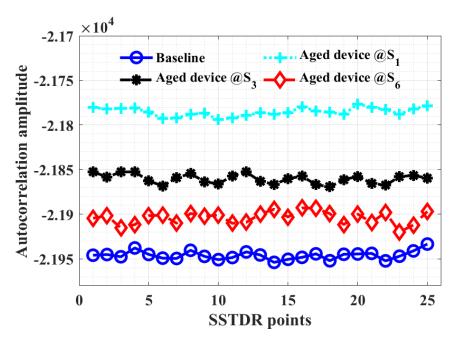

| Figure 5.17 SSTDR correlated amplitude data for baseline and aged MOSFET at three               |

| different locations                                                                             |

| Figure 5.18 Average SSTDR correlated amplitude data for healthy and aged MOSFET                 |

| located at all six locations                                                                    |

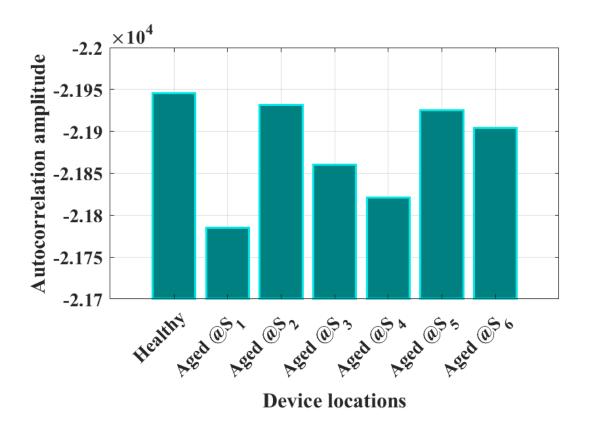

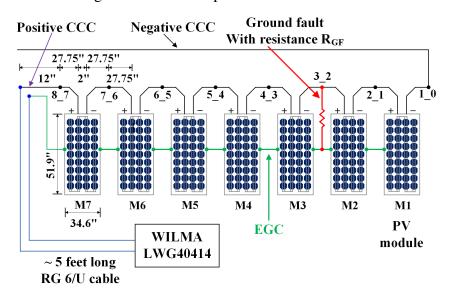

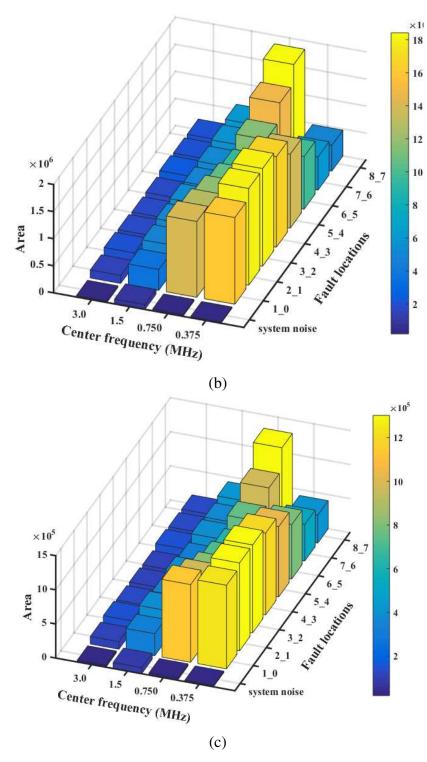

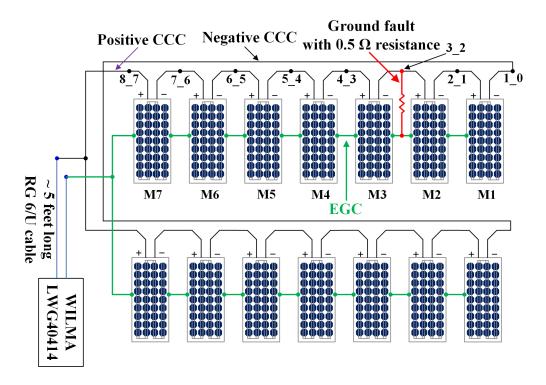

| Figure 6.1 Test set-up used at DETL of SNL                                                      |

| Figure 6.2 Schematic diagram of the test setup (physical dimensions are not drawn according     |

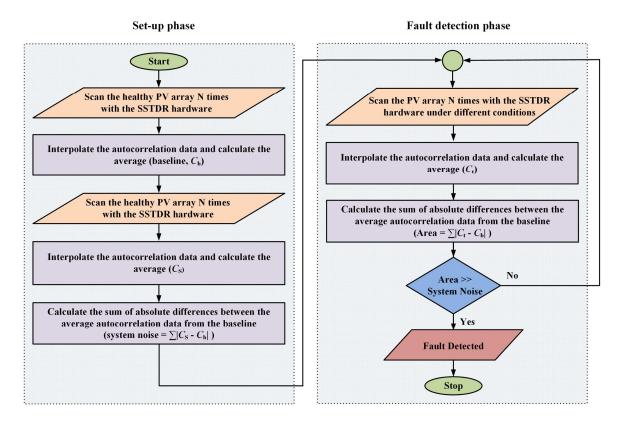

| to scale)                                                                                       |

| Figure 6.3 Flowchart of the ground-fault detection algorithm                                    |

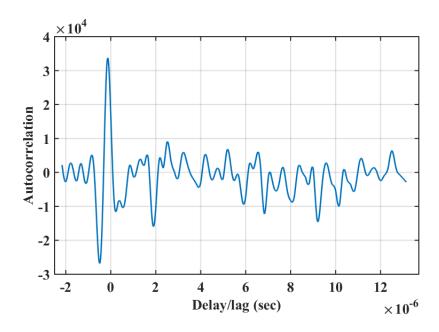

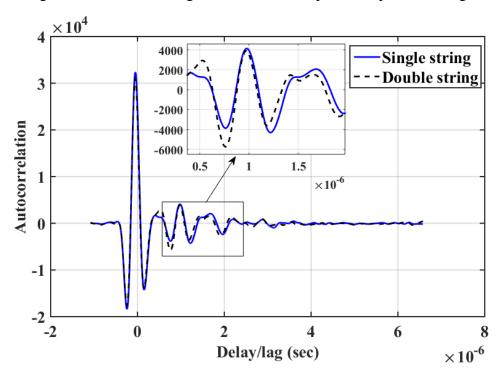

| Figure 6.4 Baseline autocorrelation plot for ground-fault detection with center frequency 750   |

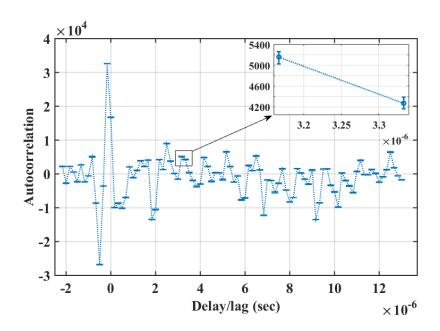

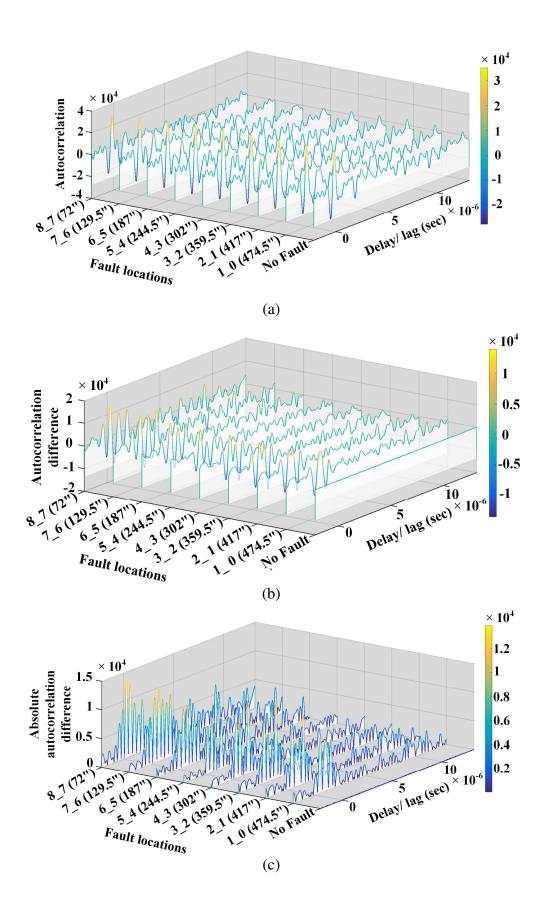

| kHz80                                                                                           |

| Figure 6.5 Error plot of autocorrelation data for center frequency of 750 kHz                   |

| Figure 6.6 (a) Average autocorrelation plot using the same PV string without any ground         |

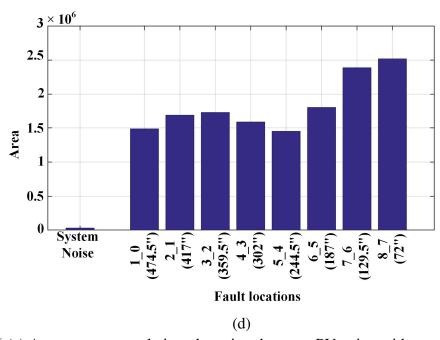

| fault and ground fault at different locations. (b) differences between average                  |

| autocorrelation data and the baseline, (c) absolute values of the differences, (d) sum of                |

|----------------------------------------------------------------------------------------------------------|

| absolute values of the differences                                                                       |

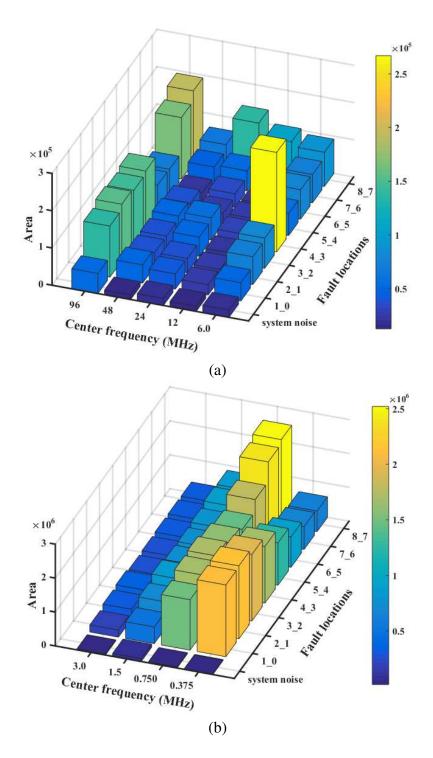

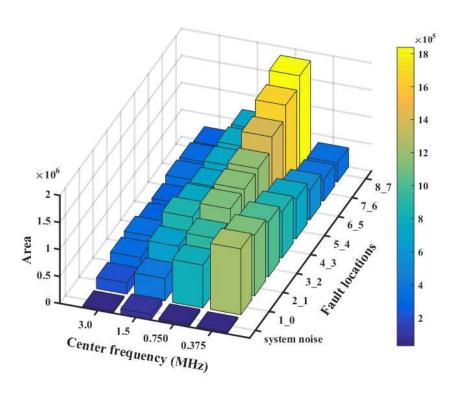

| Figure 6.7 Area under absolute autocorrelation difference plots for healthy PV string (system            |

| noise) and ground faults at different locations in the PV string using $0.5\text{-}\Omega$ resistor with |

| different center frequencies: (a) center frequencies from 96 to 6 MHz and (b) center                     |

| frequencies from 3 to 0.375 MHz                                                                          |

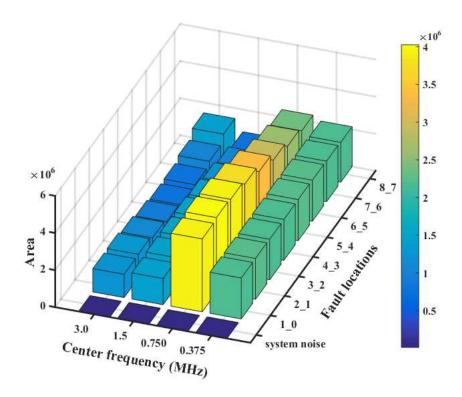

| Figure 6.8 Area plots for center frequencies 3.0, 1.5, 0.75, 0.375 MHz and fault resistances:            |

| (a) 0.5-Ω, (b) 5-Ω, (c) 10-Ω                                                                             |

| Figure 6.9 Schematic diagram of the test setup for two parallel strings                                  |

| Figure 6.10 Comparison of baseline autocorrelation plots for single string and double string.            |

| 91                                                                                                       |

| Figure 6.11 Area plot for PV array consists of two parallel strings with and without ground              |

| faults92                                                                                                 |

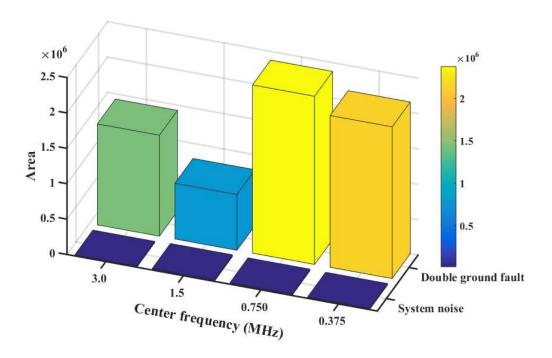

| Figure 6.12 Area plot for PV string inside laboratory with and without ground fault 93                   |

| Figure 6.13 Area plot for PV string with and without double ground fault for different center            |

| frequencies94                                                                                            |

| Figure 7.1 SSTDR hardware connected with a series-connected battery string of 6 (six) Li-                |

| ion cells97                                                                                              |

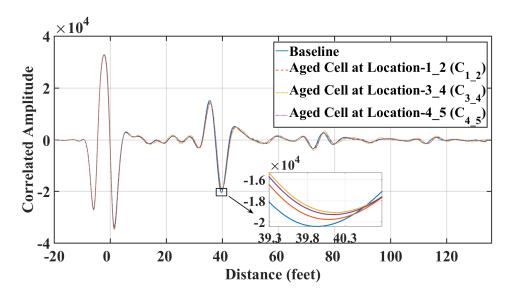

| Figure 7.2 Variation in correlated amplitudes for healthy battery string and battery string with         |

| an aged cell at different locations (for a 40 feet long cable connected to the string) 98                |

| Figure 7.3 Flowchart of the proposed algorithm for aged cell detection in a large battery pack           |

| using SSTDR                                                                                              |

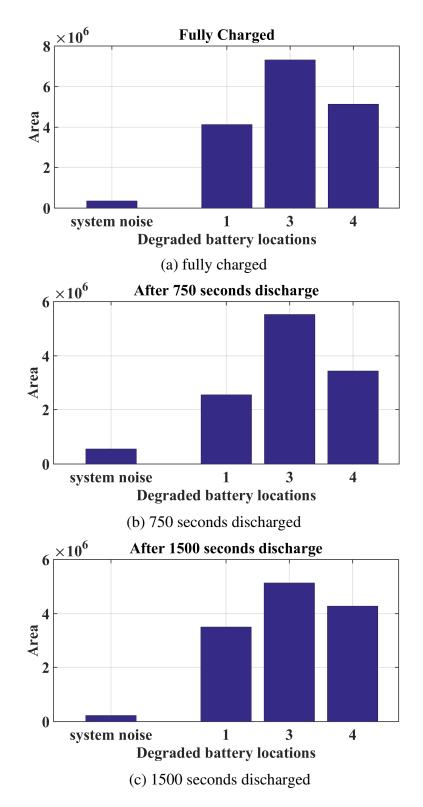

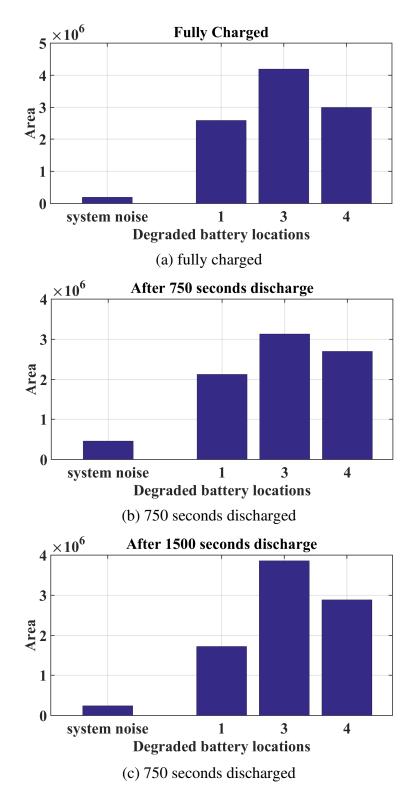

| Figure 7.4 Area plots for the battery string with aged cell at different locations along with |

|-----------------------------------------------------------------------------------------------|

| system noise for 48 MHz center frequency under different SOC conditions 101                   |

| Figure 7.5 Area plots for the battery string with aged cell at different locations along with |

| system noise for 24 MHz center frequency under different SOC conditions 102                   |

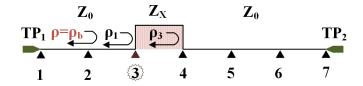

| Figure 7.6 Impedance discontinues in SSTDR propagation path for aged cell at location 3_4.    |

|                                                                                               |

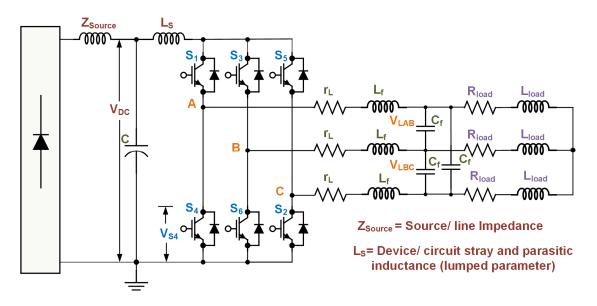

| Figure 8.1 Schematic of a grid-connected three-phase voltage source inverter                  |

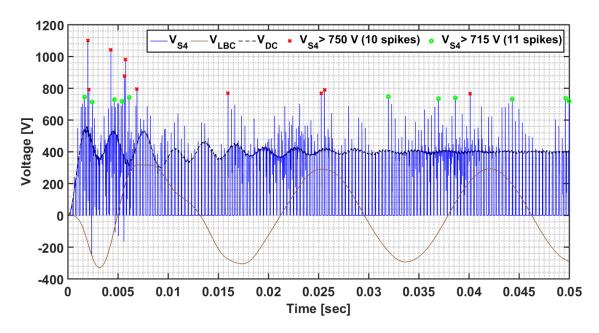

| Figure 8.2 Simulation waveforms showing accidental overvoltage situations across switch $S_4$ |

| of the three-phase inverter. 106                                                              |

| Figure 8.3 Bond wire lift off and corresponding current crowding. Test data generated by      |

| experiment. The red circle shows damaged bond wires                                           |

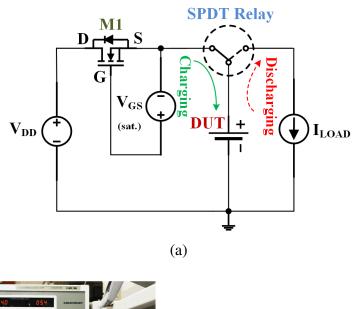

| Figure 8.4 (a) Schematic diagram and (b) photograph of the experimental set-up for            |

| maximum safe operating voltage determination                                                  |

| Figure 8.5 Experimental results showing reduced maximum safe operating voltage of an aged     |

| MOSFET, $V_{\text{maximum}}$ = maximum safe operating voltage                                 |

# **TABLES**

| Table                                                                                             | Page       |

|---------------------------------------------------------------------------------------------------|------------|

| Table 1 Summary of the accelerated aging parameters                                               | 42         |

| Table 2 Battery parameters (Samsung INR 18650-25R)                                                | 45         |

| Table 3 Switching states of the PV inverter                                                       | 49         |

| Table 4 SSTDR test results for different frequencies                                              | 56         |

| Table 5 Specification of a PV module used in the test setup (at 1000 W/m <sup>2</sup> , 25°C cell |            |

| temperature)                                                                                      | 79         |

| Table 6 Specification of a PV module used in the laboratory environment (at 1000 W/               | $m^2$ , 25 |

| cell temperature)                                                                                 | 93         |

| Table 7 Summary of the accelerated aging parameters                                               | 110        |

#### **ACKNOWLEDGEMENTS**

This research work was partially supported by the National Science Foundation (NSF) grant# 1947410, University of Missouri System FastTrack grant, and School of Graduate Studies research grant program, University of Missouri-Kansas City (UMKC).

Firstly, I would like to express my sincere gratitude to my advisor, Dr. Faisal Khan who has been extremely supportive since the days I started working at the Missouri Center for Advanced Power (MCAP). His expertise was invaluable in formulating the research questions and methodology. His insightful feedback pushed me to sharpen my thinking and brought my work to a higher level. He always encouraged me whenever I felt depressed because of not getting a successful outcome, even though I was working hard. On top of that, Dr. Khan inspired me to take the lead of my own research projects that improved my independent research skills and developed persistence in me to learn new skills in a very short period of time. He is one of the smartest people I came to know, and I could not have imagined having a better advisor and mentor for my Ph.D. study. I hope that I could be as lively, enthusiastic, and energetic as Dr. Khan.

Apart from my Ph.D. supervisor, I would not forget to express the gratitude to the rest of my Ph.D. committee members Dr. Yong Zeng, Dr. Masud Chowdhury, Dr. Ahmed Hassan, Dr. Ghulam Chaudhry, and Dr. Kamel Rekab for their advice, support, and guidance throughout my degree. I would also like to thank the outside reader of my Ph.D. committee, Dr. Mohammed Alam for his advice and suggestions in my research in the field of fault diagnosis of photovoltaic systems. Special thanks should be given to Dr. Anthony Caruso for his extensive personal and professional guidance. He also provided me with the great

opportunity to work in collaboration with talented, passionate, and diverse individuals of the Missouri Institute of Defense and Energy (MIDE) that allowed me to have unique learning experiences, especially in terms of time and project management.

I would also like to thank my fellow lab mates Abu Hanif, Wasek Azad, and Swagat Das for the fun-time we spent together, for the sleepless nights that enabled us to complete tasks before deadlines, for stimulating the discussions, and for happy distractions to rest my mind outside of my research.

Last but not the least, I am grateful to my parents and siblings for remembering me in their prayers for my ultimate success. My hard-working parents have sacrificed their lives for me and provided unconditional love and care. Nobody has been more important to me in the pursuit of my Ph.D. than the members of my family- my wife Mitaly Biswas and my little son Liam Roy. Mitaly was always with me in all difficult times I have come across. Whatever I write in the acknowledgments will never do justice to the sacrifices she has made for me to make my research work a priority in our lives and achieve my objective without any obstacle in the way.

# DEDICATION

To my parents, my elder brother, and my wife, without them I would have been nothing.

•

## CHAPTER 1

#### 1 INTRODUCTION

Power semiconductor switching devices such as metal oxide silicon field-effect transistor (MOSFET) and insulated-gate bipolar transistor (IGBT) are indispensable elements in any power conversion system, especially where heavy but critical power is required. Unfortunately, these power semiconductor devices are failure-prone and when they fail, results can be catastrophic. Therefore, it is of paramount importance to predict the device failures before they happen which will reduce the maintenance cost and can potentially save human lives. The mean time to failure (MTTF) represents the expected lifespan of the device although it cannot adequately predict unusual circumstances or continuous overstress and premature degradation which makes the power switch fail before its MTTF. In practice, the MTTF of the device as well as the overall converter reliability decreases when a device undergoes aging [1]. For a long time, we knew about this fact, but we have not yet pinpointed the reason(s). According to our study and experimental validation in our laboratory, the safe operating area (SOA) of any semiconductor device goes down with the increased level of aging, and this observation explains why the reliability or MTTF of an entire circuit exponentially drops with aging. SOA is a well-known device parameter that indicates the device's ride-throughcapability against over-voltage and over-current situations [2]. In all calculations, MTTF predicts the constant value of SOA of power switching devices, and the overall reliability of the circuit simply becomes the probability of an abnormal condition to occur and the probability of other device failures. However, SOA of any semiconductor device is agedependent rather than static as considered in reported literature to-date, and this age-dependent SOA is the underlying reason for device failure especially when the device is subjected to

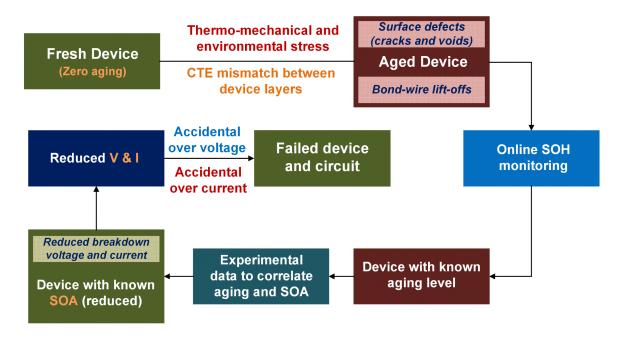

accidental over-voltage/current [3]. Based on the outcome of this breakthrough research, the following chronological order/steps are involved in the process of finding out the remaining useful life (RUL) of a power semiconductor device:

- a) Accidental over-voltage and current can damage both a healthy and aged device although the probabilities would be different. A healthy (new) device may override multiple overstressed situations, but an aged device is less likely to override those anomalies. This is the underlying reason for the increased failure rate of a circuit once the devices are aged.

- b) In all calculations, we assume the SOA of a device to be constant. According to our recent test results, SOA changes with aging, i.e. SOA goes down with higher aging.

- c) Remaining life of a switch is a function of SOA.

- d) Therefore, the remaining life goes down with higher aging.

- e) For high-power devices such as MOSFETs and IGBTs, aging is caused by bond wire detachment, cracks in the bond wire interface, voids in the wafer and other packaging issues. By knowing the device health using online condition monitoring (CM), it is possible to accurately estimate aging.

- f) Therefore, by accomplishing (e), we can estimate aging. By knowing aging, we can determine dynamic SOA. *The correlation between aging and dynamic SOA gives us the useful* remaining life of the device or the availability of a circuit.

- Fig. 1.1 demonstrates the above-mentioned steps chronologically. Finding the remaining life of a power converter is the ultimate objective to ensure the uninterrupted operation of a power electronic system. Therefore, online state-of-health (SOH) monitoring/CM of semiconductor devices need to be performed to measure the level of aging, which can be used to identify the dynamic SOA, and thus, to predict the MTTF of the overall circuit. SOH

Figure 1.1 Block diagram of the proposed steps involved in the work strategy in determining remaining lifetime estimation of power semiconductors.

estimation or CM of power switches is a fairly well-established area, although better accuracy is still needed [4]–[7]. Variations in electrical parameters (i.e. ON-state channel resistance  $(R_{\rm DS(ON)})$ , collector-emitter voltage in saturation  $(V_{\rm CE(SAT)})$ , gate-source threshold voltage  $(V_{\rm GS(TH)})$ , gate leakage current  $(I_{\rm GSLK})$ , transconductance or saturation current, or switching turn ON  $(T_{\rm ON})$  and turn OFF  $(T_{\rm OFF})$  times, etc.) carry the degradation information in most of the chip-and package-related failures such as gate structure degradation, wire-bond lift offs, solder fatigues and so on [7]–[17]. The research to date is primarily focused on characterizing the device degradation using both direct and indirect methods of measuring the above-mentioned aging precursors. Traditional CM methods for power converters are based on failure precursor measurement of power devices [20]–[28], system identification [29], [30], data-driven or model analysis [31], [32], and so on [12], [33]. Among them, precursor measurement-based CM methods require additional noise-immune, high-resolution sensors and digital controllers,

which may not be cost-effective. Other methods require either an advanced signal processing algorithm or a large number of training data which increases the computational burden.

To overcome the limitations of real-time power converter health monitoring techniques, reflectometry-based method has recently been proven to become a good candidate because this technique does not depend on the direct measurement of the traditional on-site parameters and sensors to detect device aging levels, and therefore reduces the measurement error. Different reflectometry-based methods have long been used for detection and locating faults in transmission lines, and a comparative study summarizing different reflectometry methods for fault detection in electrical wiring has been discussed in [34]. Among the known reflectometry techniques, spread spectrum time-domain reflectometry (SSTDR) provides several advantages such as low-cost fault detection in powered/live cables, very high noise immunity, embedded solutions, etc. over the other reflectometry-based techniques [34]–[39]. The incident signal of SSTDR is a high-frequency sine modulated pseudo-noise sequence (SMPNS), and the corresponding reflections may identify faults and characterize the level of aging by determining the changes in the impedance in its propagation path. Each type of device degradation leads to various impedance changes inside a power device such as  $R_{\rm DS(ON)}$ , gatesource capacitor impedance (Z<sub>eq,GS</sub>), and so on, therefore, this unique feature makes SSTDR an excellent candidate for estimating any device's SOH. Recently, the SSTDR-based technique has been proposed in [40]-[44] for estimating the level of aging associated with power semiconductor switches. However, these techniques could only estimate the device SOH while it was in full conduction mode. Therefore, these methods are only effective while the device is isolated from the circuit and subjected to a dedicated characterization setup with no modulation applied at the gate. That being said, the fast impedance variations in the SSTDR signal

propagation path due to high-frequency PWM switching of a live semiconductor device makes interpretation of the SSTDR reflection extremely difficult. The algorithm proposed in this paper demonstrates that SSTDR data can be implemented to overcome such limitations resulting in faithful aging detection in power semiconductor switches during the converter operation.

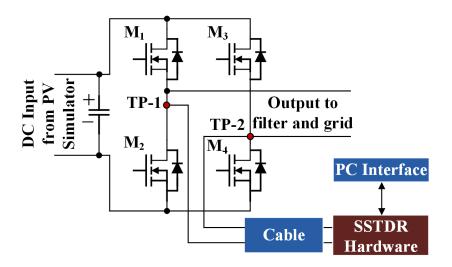

In this research, we performed several case studies regarding real-time SOH estimation or CM of power devices in live converter circuits. First, an H-bridge single-phase grid-tied PV inverter was considered where the SSTDR incident signal has been applied across its ac output terminal nodes [45]. Using the experimental results, we were able to successfully characterize the degradation level in multiple MOSFETs from this single measurement point. Later, the SSTDR test signal (SMPNS) was applied across the gate-source interface of a power semiconductor device in buck converters [46], [47] and a three-phase dc-ac inverter [48]–[50], respectively. Due to the simple implementation of the SSTDR test signal into the gate-source interface, the SSTDR scheme can potentially be embedded into commercial gate drivers offering built-in-self-test capability which will eliminate the need for a separate CM module leading to significant system-level savings. This CM hardware embedded gate driver module can be termed as Intelligent Gate Driver Module (IGDM). This IGDM will make the CM possible for high voltage converters because the gate terminal always remains at a lower potential than that of the collector/emitter side and the driver module needs to be connected to the low voltage gate-side anyway. Last but not the least, connecting SSTDR hardware to the low voltage gate terminal will help in designing it for significantly lower ratings which will considerably reduce the cost of the overall CM hardware.

As of today, there is no similar technology that can combine the level of aging (determined by SSTDR) and the corresponding change in SOA yielding the true SOA of a device without destroying it. Estimating the remaining life will allow for scheduled maintenance of any high-power converter thus enabling reduced maintenance cost. Known availability will help to select the proper converter for any specific application, and the estimation of dynamic SOA will allow the operator to choose whether the converter could be operated at full power level.

In addition to CM of live semiconductor power devices, SSTDR can be used for detecting and locating ground faults in photovoltaics (PV) array [51], [52]. PV arrays in solar PV systems are vulnerable to various types of fault occurrences and among them, ground faults are considered to be the most common fault and are reported to be one of the major reasons behind catastrophic failures resulting in electrical fires and shock hazard [53]. According to the U.S. National Electrical Code-690 (NEC-690), PV array must be protected against ground fault detection and interruption (GFDI) fuses [54]–[57]. However, even with the use of this standard protection device in a PV system, faults occurring in a PV array may remain undetected, especially when the fault current falls within the blind spot range because of the low irradiance and high fault impedances [53], [58], [59]. Apart from ground-fault detection devices, several ground fault detection techniques have been proposed in recent years [60]-[73], and most of them require several on-site parameters such as voltage, current, irradiance level, temperature, etc., for accurate fault detection. Dependency on the measurement of these parameters may result in false detection since a change in weather condition, partial shading, etc. often affects these parameters and thus the *I–V* characteristics/MPPT of the PV panel [53], [74]–[81]. In contrast, SSTDR can become an excellent candidate for PV array fault detection,

especially for testing ground faults at night or low illumination, because this method does not use traditional on-site parameters and sensors to detect faults. A healthy PV array has a specific impedance between node pairs, and any ground fault changes these impedance values which can be characterized by SSTDR. However, the wide variation in impedance throughout the entire PV system, which is caused by the use of different materials and interconnections makes PV fault detection more challenging while using SSTDR. In this research, an algorithm centered around SSTDR has been developed that can overcome this challenge and can detect the ground fault in PV arrays with any variation in the number of PV strings, the number of faults (single or double), and values of fault impedances [52].

This manuscript also presents a cell-level SOH measurement technique based on SSTDR that can identify the location and amount of aging of a degraded cell in a large Li-ion battery pack [82]. Li-ion batteries have become the most popular sources of energy storage for today's electric vehicles and renewable energy systems due to their higher energy density, lower self-discharge rate, reduced size, and weight compared to other rechargeable batteries [83]. Depending on the application, a large number of Li-ion cells (tens or hundreds) are connected in series-parallel combinations in a single pack to meet the high-power and voltage demand [84]. However, like other battery chemistries, Li-ion batteries suffer from performance degradation over time with the increased number of charging and discharging cycles, elevated temperatures and so on. Because of the inconsistency in the manufacturing process or non-uniform operating conditions, the initial SOH of one or more cells can be different that affects the performance of the entire battery pack in real-life applications [85]. Therefore, cell level SOH along with the respective cell location is a crucial metric for the battery management system (BMS) to predict the remaining useful lifetime of the entire battery pack and avoid

unwanted failures and catastrophic hazards in battery systems. Unfortunately, today's BMS cannot monitor the SOH at the cell level. To confront this issue, we propose to use SSTDR as a signature to quantify the SOH of the aged cell along with its location information in a large battery pack using its unique ability to characterize the age-related impedance variation in any device. The proposed method can determine the SOH of both the individual cells and the overall battery pack using a single measurement point that helps to monitor the remaining life in a lithium-ion battery pack and facilitate timely and cost-effective maintenance.

In Chapter 2, a literature review on the origin of degradation in power semiconductor devices is given at the beginning which is followed by a literature review on the origin of degradation in Li-ion cell in large battery pack along with the causes of ground fault occurrence in PV array system. Chapter 2 also discusses the limitations of existing aging measurement techniques of live power devices in power converters and Li-ion battery packs, and ground fault detection techniques in PV arrays. The fundamentals of the proposed SSTDR-based methods to detect faults and aging in power electronic components have been introduced in Chapter 3. To perform CM of power devices in live power converters in a laboratory environment, reference failure tests and reliability data such as test data for devices under tests (DUTs) of known aging levels are necessary [31]. However, these devices are meant to last for millions of cycles under normal and ideal operating conditions. To accelerate the fatigue process, accelerated aging tests are widely recognized, and had been demonstrated by many research groups. Chapter 4 discusses the test set-up for accelerated aging of power MOSFETs developed in the laboratory. An industry-standard accelerated battery cycling test was also performed to induce degradation in Li-ion cells and this process has been illustrated in chapter 4 as well. Chapter 5 summarizes the CM technique of a single-phase H-bridge grid-tied PV

inverter applying SSTDR test signal across the ac output node. Chapter 5 also describes the CM technique of DC-DC converters and a 3-phase power inverter applying SSTDR embedded PWM signal across the gate-source interface. SSTDR-based CM technique in a live H-bridge PV inverter and DC-DC converters was performed at the cost of a large amount of SSTDR data acquisition for the purpose of error reduction where the error is caused by the rapid variation in impedance throughout the entire live converter circuit due to the fast-switching operation. An advanced statistical algorithm has been incorporated in order to analyze the large number of SSTDR test data which has been discussed in detail in Chapter 5. In contrast, such limitations of data-intensive computing can be overcome by a little modification in the switching scheme inside a three-phase inverter, and this dissertation has presented this concept in detail in Chapter 5 as well. PV ground fault detection and location technique based on SSTDR has been presented in Chapter 6. A cell-level SOH estimation technique based on SSTDR capable of identifying aged cells in a large lithium-ion battery pack has been described in detail in Chapter 7. Chapter 8 demonstrated how the SOA of a power semiconductor device is impacted by aging and corresponding experimental results have been documented. In addition, a case study showing the relationship between dynamic SOA and the probability of occurring a failure for a specific circuit is investigated in Chapter 8. Finally, Chapter 9 summarizes the work presented in this dissertation. Future directions of the research on fault diagnosis and CM of power electronic components are also provided in the final chapter (Chapter 9).

# **CHAPTER 2**

# 2 BACKGROUND STUDY AND LITERATURE REVIEW

# 2.1 Degradation Assessment and Precursor Identification of Power Semiconductor Device in Live Power Converters

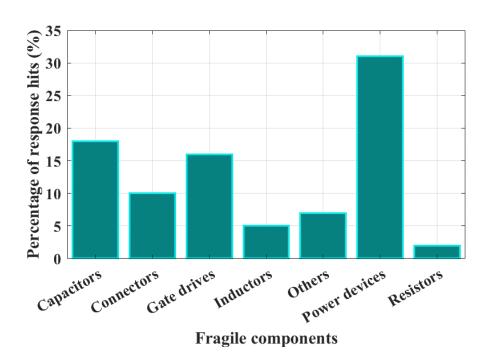

A power converter is an integral part of most consumer and industrial products needing electric power. Various segments such as upcoming all-electric aircraft industry, existing motor drive market, space mission, electric automotive, health sector, renewable energy market, high voltage direct current (HVDC) substation and many others require the use of power converters. Power converters are built from one or more power semiconductor devices (typically MOSFET or IGBT), capacitors, inductors, and low power controller circuits. Among various components of a power converter, the power semiconductor device has been reported to be the most failure-prone element. In an industry-based survey conducted in [86] (shown in

Figure 2.1 Survey of different components responsible for converter failure [86].

Fig. 2.1), about one-third of the responders answered that the power semiconductor device is the most fragile component in the power electronic system. Reliability of these critical components degrades with time due to mechanical and thermo-electrical stresses during regular operation, therefore downgrading the performance or even complete failure of the overall power conversion systems. The statistics found in [87] show that degradation in power devices accounts for 55% of the power converter failures. Therefore, the reliability and performance of the power converters greatly depend on these power semiconductor devices. By conducting condition monitoring (CM), it is possible to assess the degradation of power semiconductor switches, which eventually can predict failures before they happen. This failure prediction can prevent unwanted system shutdown due to the failures and can estimate the remaining life of live power converters.

# 2.1.1 Degradation Mechanism and Effect of Aging on Measurable Parameters

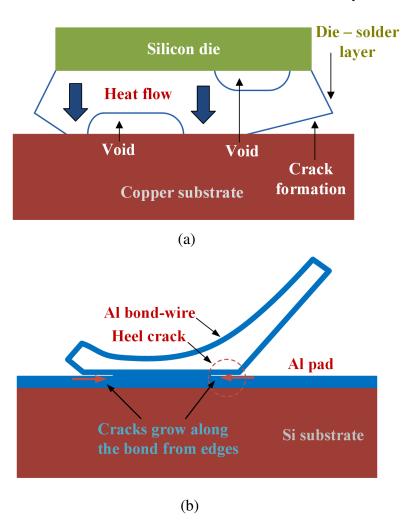

Two types of failure mechanisms typically exist in power semiconductor switches. They are (1) chip-related failure and (2) package-related failure. Chip related failures are caused by electrical overstresses (EOS), electrostatic discharge (ESD), latch-up and triggering of parasitic, hot carrier injection, electromigration, aluminum bond pad reconstructions, and so on [7], [8]. Chip-related aging involves gate-oxide degradation, which cumulatively shifts the gate-source threshold voltage ( $V_{GS(TH)}$ ), gate leakage current ( $I_{GSLK}$ ), transconductance or saturation current, or switching turn ON and turn OFF times, etc. [9]–[12]. In addition, trapped charges in the gate oxide layer and Si/SiO<sub>2</sub> interface due to gate oxide degradation cause positive  $V_{GS(TH)}$  shift and decrease electron mobility, leading to the increase in the device ON-state channel resistance ( $R_{DS(ON)}$ ) [88]. Moreover, aluminum bond pad reconstruction and metallization cause chip degradation, which eventually increases the  $R_{DS(ON)}$ . The increase in

$V_{\rm GS(TH)}$  also increases the equivalent series resistance ( $ESR_{\rm GS}$ ) leading to an increase in the gate-source capacitor impedance ( $Z_{\rm eq,GS}$ ) [13], [14]. Although chip related degradation causes ultimate device failure, package related failure mechanisms are most frequently observed in power devices [7]. The main driving forces acting on package related degradation are the mismatches in the coefficient of thermal expansion (CTE) between different materials in the chips and packages. These mismatches lead to mechanical stress throughout the packaged device under temperature swing through regular power and thermal cycling. As shown in Fig. 2.2, owing to this CTE mismatch, cracks, and voids in the die-attach layer between Si and Cu

Figure 2.2 (a) Formation of cracks and voids in a power MOSFET due to aging and (b) wire bonding failure [7].

die, and the bond wire and chip interface are formed, resulting in the bond wire lift-off and soldier fatigue [7], [8], [89], [90]. Reduced number of bond-wires, cracks, and voids will impede the heat dissipation throughout the device, and thus thermal impedance ( $Z_{th}$ ), as well as junction temperature ( $T_j$ ), will increase which can be determined by the increase in the device on-state channel resistance ( $R_{DS(ON)}$ ) and on-state collector-emitter voltage ( $V_{CE(ON)}$ ) [7], [8], [15]–[17], [89].

# 2.1.2 Existing Aging Measurement Techniques and Their Limitations

According to recent literature studies, measuring the failure precursors of the power devices, analyzing the model of the degradation process and using system identification are explored to continuously monitor the condition of the power converters. In [20], [21], [24]– [26],  $V_{\text{CE(ON)}}$  and/or  $R_{\text{DS(ON)}}$  measurements have been carried out to perform device health monitoring. Although these precursors ( $V_{CE(ON)}$  and  $R_{DS(ON)}$ ) can be measured using specially designed sensors, changes in these quantities are significantly small relative to their OFF-state counterparts, and these sensors often need electrical isolation to block the high DC-link voltage. Therefore, the direct measurement of these parameters is not practical and costeffective for many high voltage applications and could result in low-resolution measurements. It is of paramount interest to detect and track the variation of  $V_{\text{CE(ON)}}$  and/or  $R_{\text{DS(ON)}}$  without introducing additional sensors or circuitry. Thermal resistance and junction temperature-based CM technique [22], [28] can detect solder fatigue inside the packaging of a power module, however, direct measurement of junction temperature is impractical and can only be applied during the idle state of the converter. Switching transients such as turn-ON and turn-OFF timebased health monitoring methods proposed in [23] and [27] respectively, can characterize device failure mechanisms along with gate driver circuit degradation. However, the direct

measurement of switching transients, often in the range of tens of nanoseconds, requires a very high bandwidth and noise immune transient detection circuit with a high-resolution sensor. Recently, other CM methods for gate degradation detection based on Miler Plateau gate voltage [33] and gate leakage current ( $I_{GSLK}$ ) measurement [12] have been proposed. Like the direct measurement of switching transients, a high-resolution detection circuit with high bandwidth is needed for the above-mentioned gate-signal-based CM methods [12], [33], which is very difficult to implement due to the compromise needed between the measurement resolution and signal bandwidth. Moreover, the instrumentation amplifier must withstand a large common-mode voltage and is required to offer a very high common-mode rejection ratio (CMRR) even at a very high switching frequency. Although switching transient and gatesignal-based CM methods can be integrated into the gate-drivers to make them intelligent, the above-mentioned drawbacks along with their ability to only detect gate degradation inhibit their wide range of applications. All of these methods need external sensors to collect aging precursor data that require the use of additional probes, complex hardware as well as digital controllers, which may not be cost-effective. Therefore, CM techniques without using internal sensors are indeed highly desirable. System-identification-based CM technique can be implemented without any additional sensors other than those required for the operation of the converter and with minimal additional digital hardware [29], [30]. However, this technique requires an advanced signal processing algorithm which increases the computation burden. Moreover, derivation of precursor information from external measurements requires establishing an accurate relationship between the device condition and the measurable system performance, otherwise, the variable operating condition of a converter system may produce false results. The data-driven or model-based CM approach proposed in [31], [32], is based on the comparisons of estimated and measured variables that require a large number of training data, and they also have a poor estimation of specific variables in different operating conditions.

In order to overcome these limitations of real-time power converter health monitoring techniques, spread spectrum time domain reflectometry (SSTDR) based aging detection techniques have been proposed in [40]–[44] because of its low voltage characteristics, very high signal to noise ratio, and the ability to perform in both the low-frequency and highfrequency environment. Previous SSTDR based CM methods were only able to detect device degradation while the converter operates in an idle state (constant input at the gate), therefore the technique cannot be implemented in live power converter applications (PWM switching). Moreover, these methods required SSTDR test signals to be applied across the drain-source terminals of a power MOSFET or collector-emitter terminals of an IGBT with the help of external SSTDR hardware, which could be unsuitable in high voltage circuits. As described in Chapter 4, all these limitations can be overcome by adopting either of the two schemes: (i) incorporating advanced statistical analysis in SSTDR data interpretation, and (b) synchronizing the SSTDR test signal (SMPNS) with the PWM gate signal (across the gatesource interface) as well as modifying the switching scheme with better flexibility. Most importantly, CM from the gate-source interface allows us to monitor the high voltage converter easier and safer than it was in the past. This feature also helps in designing the SSTDR hardware for significantly lower ratings since the gate terminal is always at a lower potential compared to the drain/collector. Last but not least, due to the ability to synchronize the SMPNS code with the PWM gate signal, the proposed technique can be integrated with the gate driver module, thus making it intelligent. No similar technology involving gate driver with built-in

SOH/CM module presently exists and chapter 3 described the detailed features of this proposed intelligent gate-driver architecture.

#### 2.2 PV Ground Fault Detection

According to the International Energy Agency (IEA), the world's total renewable energy-based power capacity is expected to increase by 50% between 2019 and 2024. This is an increase of 1,200 GWs, equivalent to the current total power capacity of the United States. Of that global total power capacity, 60% is expected to come from solar/photovoltaic (PV) energy, the fastest-growing source of renewable energy in nearly every country around the world [91]. PV energy's popularity stems from the lower costs for installation and operation of PV systems and its ability to replace conventional finite energies that are harmful due to carbon emissions into our ever-warming atmosphere. Despite the attractiveness of the PV technology, PV systems can experience faults that often go unnoticed and can cause catastrophic failure in the power system. These faults decrease electrical power output as well as degrade module properties [92]. Based on their locations, three types of failures in PV systems are studied in power electronics: faults on PV arrays [53], [77], [78], [93], failures in power conditioning systems [94], [95], and disturbances in the utility interconnections (such as islanding, and so on) [96], [97]. However, recent fire events initiated by the catastrophic failures in PV arrays have been drawing the attention of researchers toward this area [98], [99]. Among all possible major faults that happen in the PV arrays such as ground faults, line-to-line faults, arc faults, hot-spot formation, and open circuit faults, ground faults are considered to be the most common faults in PV systems and are reported to be one of the major reasons behind catastrophic failures resulting in electrical fires and shock hazard [53], [58], [59].

#### 2.2.1 Reasons for PV Ground Faults

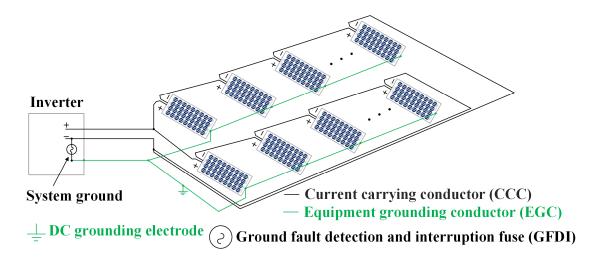

The ground fault is the undesirable condition of current flowing through the unintentional low resistance path between a current-carrying conductor (CCC) and an equipment grounding conductor (EGC)/earth. In addition to CCCs, a PV array has several non-current-carrying conductors (NCCCs) such as module frames, mounting racks, metal enclosures, distribution panels, the chassis of end-use appliances, and power converters [55]. No current flows through these paths under normal operating conditions, but a nonzero current exists in any path during faults. All these NCCCs are connected through the EGC, and the use of EGC is mandated by National Electrical Code (NEC) 690.43 regardless of the nominal voltage of the PV system in order to protect people and other living animals from being electrocuted [54]–[56]. There are several potential reasons for ground faults such as (a) cable insulation damage during the installation due to aging, chewing done by rodents, water leakage, and corrosion, etc., (b) ground fault within the PV modules caused by degraded sealant, oxygen and water vapor penetration into the module, and (c) accidental short circuit inside the PV combiner box, often at the time of installation [55], [56], [74].

#### 2.2.2 Standard Ground Fault Protection Devices and Their Limitations

PV array installations can be divided into two categories: grounded and ungrounded [55], [56]. In grounded systems, at least, one of the CCCs needs to be connected to the EGC using a ground-fault detection and interrupter (GFDI) fuse in order to detect the presence of any accidental circulating current path, and this is termed as system grounding. PV systems with system grounding are known as grounded, and this category is prevalent in the U.S.; an example of this grounding-type is illustrated in Fig. 2.3. However, there are alternative ground-fault protection schemes, which are more common outside the U.S. including residual current

Figure 2.3 Typical grounding diagram of PV arrays. The GFDI fuse (system ground) is usually installed inside the PV inverter in a grounded PV array, and system grounding is absent in an ungrounded PV array [53].

monitoring devices (RCD) and dc insulation resistance (Riso) measurements [51], [53]. These ground-fault protection systems often are used on ungrounded (floating) PV systems that do not have a connection between a CCC and ground.

In general, ground fault detection devices are based on passive fuses, isolation impedance measurements, or differential current measurement methods, and these ground-fault protection devices suffer from several limitations [53], [57]. For instance, a ground fault may remain undetected when the fault current falls within the blind spot range because of the low irradiance and high fault impedances [53], [57]–[59]. This phenomenon is known as the blind spot of the detection device, i.e., when the fault current magnitude is less than the tripping/melting current of this device preset. Recent fire events on April 5, 2009, in Bakersfield, CA, USA, and April 16, 2011, in Mount Holly, NC, USA, resulted from undetected ground faults within the blind spot range [98], [99]. In both of these fire events, a double ground fault occurred. The first ground fault occurred between the negative CCC and

EGC and resulted in current flow through the GFDI fuse, although the current magnitude was below the rated current of the installed fuse, and this fault remained undetected for an indefinite amount of time. The second ground fault within the same array resulted in a flow of 952A of current through the EGC and ignited fire before the fault current was cleared by the overcurrent protection fuse. Leakage current in the system may lead to the blind spot of the detection device. Sufficient leakage current may flow through the system if it is designed poorly, especially during the presence of high relative humidity [100]. This leakage current may flow in the opposite direction of the ground fault current resulting in the reduced magnitude of the current through the GFDI and IMD devices which may remain undetected [58], [98]. Additionally, RCDs may be affected by external electrical noise resulting in nuisance tripping of the system [101].

#### 2.2.3 Existing Ground Fault Detection Techniques and Their Limitations

Apart from ground-fault detection devices, several ground fault detection and mitigation techniques have been proposed in recent years that are based on comparisons of estimated and measured variables, pattern recognition using signal processing, machine learning analysis, and so on. Platon *et al.* proposed an online fault detection method based on the differences between measured and estimated ac power output from a modeled PV system [60]. A "fractional-order color relation classification" based fault detection method has been introduced in [61] where a fractional-order dynamic error (FODE) is calculated to measure the power degradation caused by the fault. In [62], a "descriptive and inferential statistic" has been conducted on the population of the energy generated from the PV inverters equipped with each PV subarray to identify the faulty part of the plant. A wireless sensor-based fault detection technique, which detects fault by comparing expected values with measured values of

operating voltages and currents of PV panels, is introduced in [63], [64]. A fault diagnosis technique for the PV panel is presented in [65], where several intrinsic parameters are estimated based on modified particle swarm optimization (MPSO) by sampling the dynamic panel voltage and current. The fault in the panel can be detected if there is any change in the estimated parameters from their initial values. Saleh et al. presented a fault detection method, based on the magnitudes and wave-shape characteristics of voltage signals of the PV modules, which needs two voltage transducers in each string [66]. All of these methods are computationintensive and need external sensors to collect the data. Moreover, machine-learning techniques based on prerecorded and on-site data have been proposed in [67], [68] and require a large amount of training data along with external sensors. Again, both the machine-learning-based and comparison-based fault detection techniques need accurate PV models to estimate circuit parameters. However, the models designed for specific environmental conditions are not capable of simulating the characteristics of the PV performance under different environmental conditions, and thus, may result in false detection in these cases [67]-[71]. Therefore, these models have to be configured properly to get the correct estimated values. Yi and Etemadi [72] presented a pattern-recognition-based fault detection method that utilizes fuzzy inference systems (FIS) to detect the faults with the help of extracted necessary signal features from a multiresolution signal decomposition (MSD) technique. Though this method uses fewer sensors compared to the machine learning methods, it needs a series of filters that make the system more expensive. The authors of [73] utilized the difference in voltages between the healthy module in the faulty string and the module in the healthy string to locate the faulty module. This computation-intensive method needs to update the software programs of the existing commercial converters with additional voltage sensors. Wang et al. proposed a highimpedance ground-fault (HIGF) detection scheme of PV arrays using the common-mode (CM) current spectrums of the CM model of the full-bridge inverter [69]. This model-based fault detection technique needs to be updated for different configurations of PV arrays and experiences difficulties in determining the stray and parasitic parameters.

Most of these existing ground fault detection techniques require several on-site parameters such as voltage, current, generated power, irradiance level, temperature, humidity, etc., for accurate fault detection. Changes in any of these parameters may affect the I–V characteristics/MPPT of the PV panel making the fault detection techniques more challenging especially for those methods that rely on the I–V characteristics of the PV module [53], [74]–[81]. Therefore, a method that does not use traditional on-site parameters and sensors to detect faults is highly desirable to overcome these limitations in PV array fault detection techniques. SSTDR based fault detection method could be an excellent candidate to overcome such limitations since it only relies on the fault-related impedance variations rather than the traditional on-site parameters and sensors.

#### 2.3 Detection of Degraded Cell in a Li-ion Battery Pack

Electric vehicles (EVs) and hybrid EVs (HEVs) as well as the battery energy storage of renewable energy generations (such as wind and solar PV plants) use a large number of Liion cells connected in series and parallel to meet their stringent power and energy requirements [84]. The Li-ion battery packs usually constitute the single largest cost (81% of the total powertrain cost) of the entire vehicle [102], and thus prolonging the battery life is crucial to saving the maintenance costs.

#### 2.3.1 Origin of Cell-level Degradation in a Li-ion Battery Pack

Like other battery chemistries, Li-ion batteries suffer from performance degradation over time. Because of the inconsistency in the manufacturing process or non-uniform operating conditions, the initial SOH of one or more cells is different [85]. Uneven SOH at the cell level leads to the existence of different resistance paths and temperature gradients that will create an uneven current distribution in the system. These factors can accelerate further degradation in the cells in a cascading manner, and eventually, the entire battery pack loses capacity, becomes unreliable, and even may lead to catastrophic failure [85], [103]. Therefore, the location information of individual cells along with their aging level in a large Li-ion battery pack is indispensable since it can help us to estimate the SOH of the entire battery pack and thus predicting its remaining useful lifetime (RUL).

#### 2.3.2 Limitations of Existing Li-ion SOH Estimation Methods

The capacity and internal impedance are considered to be the two main precursors of the SOH of a battery [84], [104]. An aged battery experiences loss in capacity and an increase in internal impedance. For instance, the automotive manufacturers consider the end of life (EOL) of a lithium-ion battery if the capacity degrades by 10%-20% of its nominal capacity, or if the internal impedance increases by 160 % of its initial value at the same SOC and operating temperature [104]. A considerable number of methods on battery SOH monitoring and prognosis based on characterizing these two precursors have been reported that measure the traditional parameters such as load current, terminal voltage, surface temperature and so on. These methods can be roughly divided into five groups: namely offline open-loop direct methods [105], state-observer methods [106], signal processing methods [107], model-based [108] and data-driven based regression methods [109]. Open-loop direct methods suffer from

poor accuracy since the load profile and environmental conditions rarely follow the aging test dataset from which the SOH estimation model is derived. Again, state-observer methods require a huge computational task that makes them unsuitable for on-board SOH estimation. Similarly, signal processing techniques are not suitable for online SOH monitoring in real application since they require batteries must be charged or discharged with a constant current. Lastly, the model-based and data-driven based regression methods estimate the battery SOH using statistical learning methods that require the historical data, and the SOH prediction accuracy greatly suffers from the quantity and quality of the selected training dataset. However, none of these battery health monitoring and prognosis methods can monitor the SOH at the cell level and thus identify the location of the degraded cell in a large battery pack.

#### CHAPTER 3

# 3 FUNDAMENTALS OF SPREAD SPECTRUM TIME DOMAIN REFLECTOMETRY (SSTDR): A NEW METHOD FOR TESTING ELECTRONICS LIVE

#### 3.1 Basic Concepts of Reflectometry

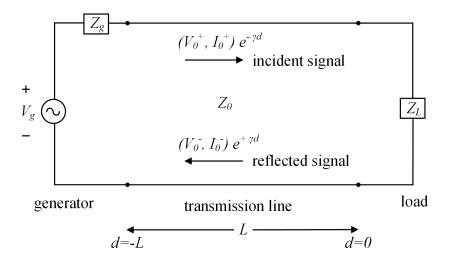

Reflectometry is a well-known technique in electromagnetics, and it has been successfully used for detecting and locating faults in transmission lines and aircraft wirings [34]–[39]. Reflectometry is based on the reflection of an electrical signal at any impedance discontinuity in a transmission line. As illustrated in Fig. 3.1, any incident signal  $(V_0^+, I_0^+)$  is sent down the line and a portion of the signal  $(V_0^-, I_0^-)$  is reflected back if it finds any impedance mismatch from the characteristic impedance  $(Z_0)$  of the line. Characteristic impedance,  $Z_0$ , is defined as the ratio between the voltage and current of the incident or the reflected wave as follows:

Figure 3.1 Schematic diagram of a transmission line of length L and characteristic impedance equal to  $Z_0$ . A generator circuit is connected at one end (d=-L), and other end (d=-0) is connected to load  $Z_L$ .

$$Z_0 = \sqrt{\frac{R' + jwL'}{G' + jwC'}} = \frac{V_0^+}{I_0^+} = \frac{V_0^-}{I_0^-}$$

(3.1)

Here, R' ( $\Omega/m$ ), L' (H/m), G' (S/m), and C' (F/m) are per unit length resistance, inductance, conductance, and capacitance of the transmission line, respectively. The ratio between the reflected and incident voltage signals is known as the reflection coefficient ( $\rho$ ), which is a measurement of how much signal is reflected back [defined in (3.2)]:

$$\rho = \frac{V_0^-}{V_0^+} = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{3.2}$$

Here,  $Z_0$  is the characteristic impedance and  $Z_L$  is the impedance at the point of impedance discontinuity (impedance of the load/device under test, fault, etc.).

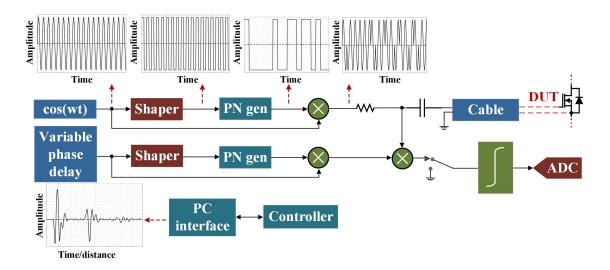

#### 3.2 SSTDR Operation