# Design of an Integrated CMOS Transceiver with Wireless Power and Data Telemetry with Application to Implantable Flexible Neural Probes

Jordan Thimot

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2021

© 2021

Jordan Thimot

All rights reserved

#### ABSTRACT

### Design of an Integrated CMOS Transceiver with Wireless Power and Data Telemetry with Application to Implantable Flexible Neural Probes Jordan Thimot

Recent developments in implantable medical devices (IMDs) have created a need for communication systems integrated directly into the implant with feedback data for various sensing systems. The need for modern communication techniques, power delivery systems, and usable interfaces for smart implants present an interesting challenge for engineers trying to provide doctors and medical professionals with the best resources available for medical research.

This dissertation will cover the design of an integrated CMOS transceiver and near-field inductive link used for an IMD and the accompanying CMOS front end for the application space of neural recording in the brain of lab mice. The design process of the CMOS IC, along with thinning techniques, the nearfield inductive link, and the design of an external reading system will be discussed in detail. The various wireless power and data telemetry techniques applicable for IMDs and their strengths and weaknesses will also be described. Software techniques and implementation for real-time analysis of a high data rate communication system from the designed IMD will be covered. Finally, transceiver verification will be given for both power and data telemetry under various scenarios, with front end verification performed via controlled lab bench experiments using input sinusoidal wave forms.

## Contents

| $\mathbf{Li}$  | st of | Figur  | es                                               | iv   |

|----------------|-------|--------|--------------------------------------------------|------|

| Li             | st of | Table  | S                                                | viii |

| A              | ckno  | wledgr | nents                                            | ix   |

| 1 Introduction |       |        | ion                                              | 1    |

|                | 1.1   | Wirele | ess Near-Field Power Systems                     | 3    |

|                |       | 1.1.1  | WPT in Biological Systems                        | 7    |

|                | 1.2   | Wirele | ess Communications Links                         | 8    |

|                |       | 1.2.1  | Encoding Techniques                              | 9    |

|                |       | 1.2.2  | Load Shift Keying                                | 9    |

|                |       | 1.2.3  | Intersymbol Interference and Signal Equalization | 12   |

|                | 1.3   | Impla  | ntable CMOS Devices                              | 17   |

| <b>2</b>       | Des   | ign of | Implantable ASIC                                 | 21   |

|          | 2.1                                   | Desigr                                       | n Specifications and Goals                 | 21 |  |  |

|----------|---------------------------------------|----------------------------------------------|--------------------------------------------|----|--|--|

|          | 2.2                                   | P. Near-field Four Coil Design               |                                            |    |  |  |

|          |                                       | 2.2.1                                        | Power Systems Circuitry                    | 26 |  |  |

|          | 2.3                                   | Data I                                       | Modulation Circuitry                       | 29 |  |  |

|          |                                       | 2.3.1                                        | Clock Recovery                             | 30 |  |  |

|          |                                       | 2.3.2                                        | Data Modulation and Demodulation Circuitry | 32 |  |  |

|          | 2.4                                   | Neura                                        | l Interface Circuitry and Post Processing  | 34 |  |  |

|          |                                       | 2.4.1                                        | SAR ADC                                    | 34 |  |  |

|          |                                       | 2.4.2                                        | Neural Amplification System                | 37 |  |  |

|          |                                       | 2.4.3                                        | Chip Thinning                              | 41 |  |  |

| 3        | Des                                   | Design of External Reader System 4           |                                            |    |  |  |

|          | 3.1                                   | PCB (                                        | Coil Design                                | 46 |  |  |

|          | 3.2                                   | Data 1                                       | Acquisition System                         | 50 |  |  |

|          |                                       | 3.2.1                                        | External Transmitter Board                 | 50 |  |  |

|          |                                       | 3.2.2                                        | LSK Reconstruction Board                   | 53 |  |  |

|          | 3.3                                   | 3.3 Data Reconstruction                      |                                            |    |  |  |

|          |                                       | 3.3.1                                        | Modifed CMA Algorithm                      | 57 |  |  |

|          |                                       | 3.3.2                                        | FPGA Interface                             | 60 |  |  |

| 4        | Measurement and Simulation Results 64 |                                              |                                            |    |  |  |

|          | 4.1                                   | Power                                        | and Data Telemetry Results                 | 64 |  |  |

|          |                                       | 4.1.1                                        | Power Harvesting                           | 65 |  |  |

|          |                                       | 4.1.2                                        | Data Telemetry Results                     | 68 |  |  |

|          | 4.2                                   | Application Results: Neural Amplifier System |                                            |    |  |  |

|          | 4.3                                   | Post I                                       | Fabrication Thinning and Surgical Results  | 76 |  |  |

| <b>5</b> | Cor                                   | nclusio                                      | ns                                         | 92 |  |  |

| Refere | References |                                   |    |

|--------|------------|-----------------------------------|----|

|        | 5.2.2      | Neural Recording Systems          | 96 |

|        | 5.2.1      | Wireless Transceiver              | 95 |

| 5.2    | Propo      | sed Changes for Future Iterations | 95 |

| 5.1    | Summ       | ary of Contributions              | 92 |

# List of Figures

| 1.1  | Standard WPT Model for Wireless Systems                                      | 5  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Near-field E and H penetration in a human head model                         | 7  |

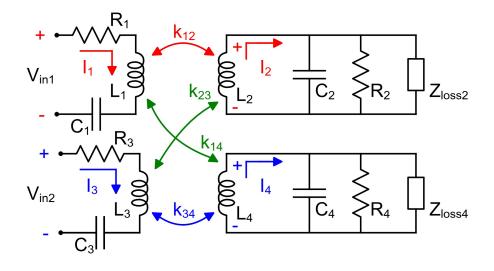

| 1.3  | 4-Coil Model for simultaneous power and data transfer                        | 10 |

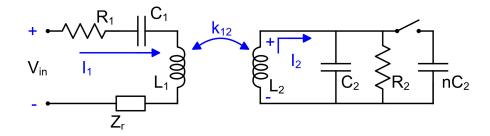

| 1.4  | 2-Coil Model including Reflective impedance for LSK Encoding $\ . \ . \ .$   | 11 |

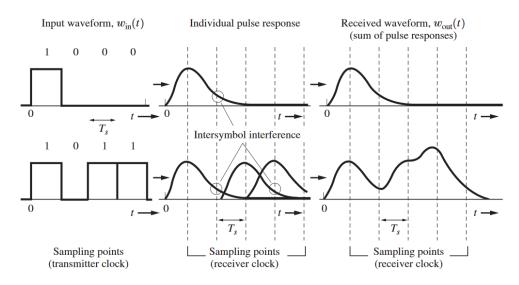

| 1.5  | Example of ISI on received bianry pulses in a communication system $\ . \ .$ | 13 |

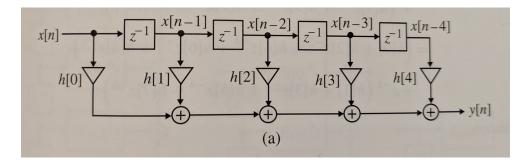

| 1.6  | Direct form linear FIR filter with 4-taps                                    | 14 |

| 1.7  | Structure of a Linear Equalizer                                              | 14 |

| 1.8  | 16-QAM Constellation with a variable Modulus (a) and 8-PSK with Con-         |    |

|      | stant Modulus (b)                                                            | 15 |

| 1.9  | Theoretical BER vs $E_b/N_0$ for common constellations                       | 16 |

| 1.10 | Ideeal Eye Diagram for PSK                                                   | 17 |

| 1.11 | Commercial Neuropixel System                                                 | 19 |

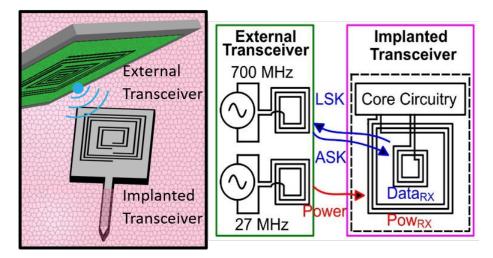

| 1.12 | Proposed System Application                                                  | 20 |

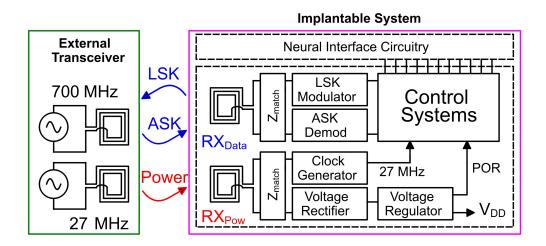

| 2.1  | Implant IC System Block                                                      | 22 |

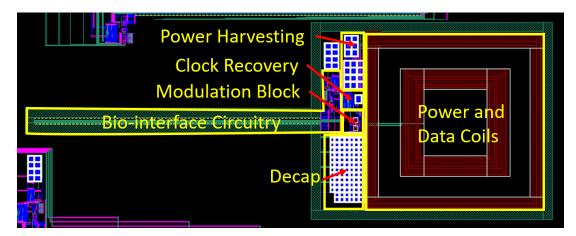

| 2.2  | Physical Layout of Implantable ASIC                                         | 23 |

|------|-----------------------------------------------------------------------------|----|

| 2.3  | IC side vs PCB side RF transmission                                         | 24 |

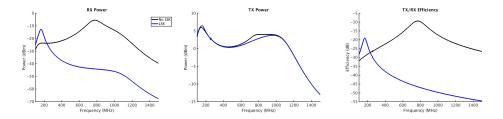

| 2.4  | RX Power, TX Power, and TX/RX Efficiency with LSK modulation                | 25 |

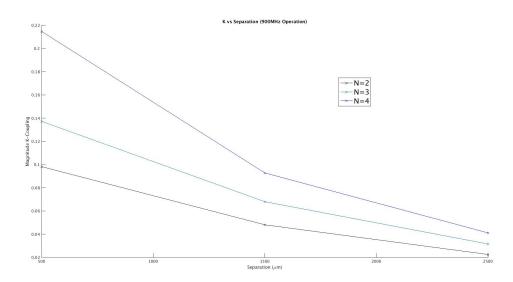

| 2.5  | Coupling coefficient for power coils vs transceiver radius                  | 26 |

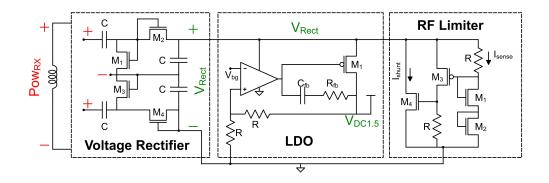

| 2.6  | System Block for Rectification, Regulation, and RF Protection Circuitry     | 28 |

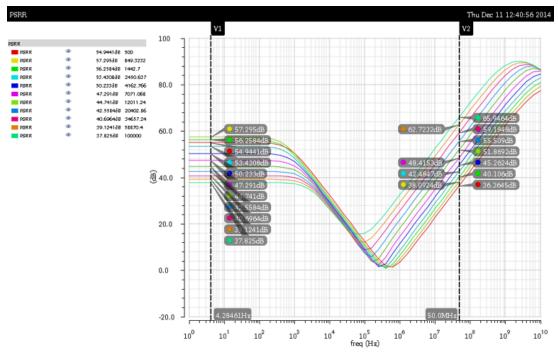

| 2.7  | PSRR of LDO block                                                           | 28 |

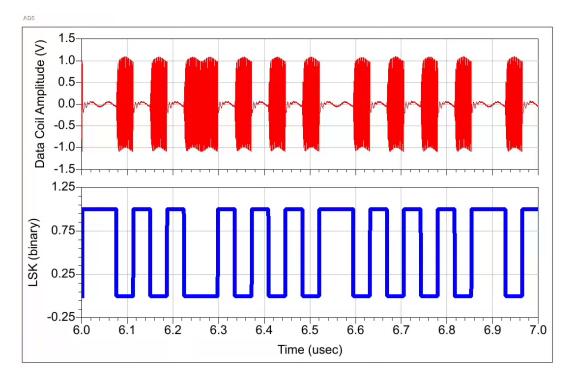

| 2.8  | LSK Waveform on the Chip's Data Receiver                                    | 31 |

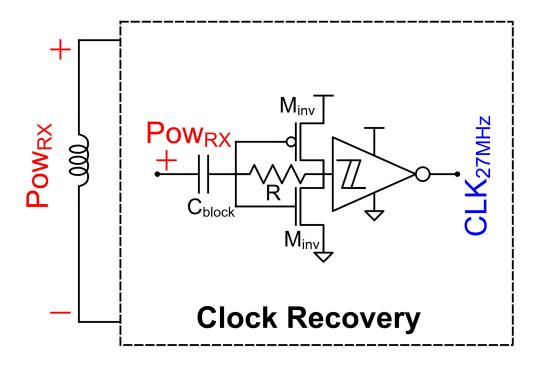

| 2.9  | Clock Generator Circuitry                                                   | 32 |

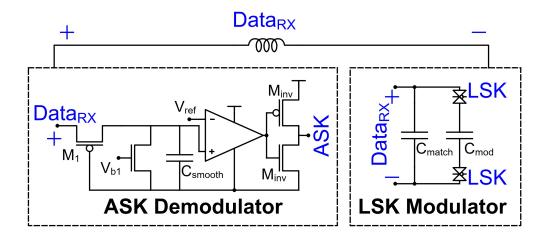

| 2.10 | ASK Demodulation and LSK Modulation Circuitry                               | 33 |

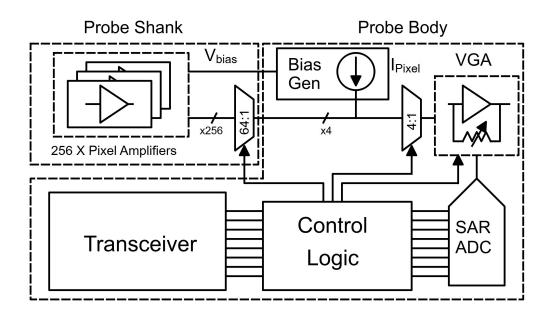

| 2.11 | Neural Interface Circuitry and ADC System Block                             | 35 |

| 2.12 | SAR ADC System Block Diagram with a<br>synchronous controller $\ . \ . \ .$ | 36 |

| 2.13 | Monotonic Switching Controller                                              | 37 |

| 2.14 | 2 Stages of Neural Amplifier System                                         | 38 |

| 2.15 | Tunable 3rd Stage of Amplifier System                                       | 39 |

| 2.16 | Operation Amplifier Circuit Topologies                                      | 40 |

| 2.17 | Gain Performance of Amplifier Chain                                         | 41 |

| 2.18 | IC post thinning and shank formation                                        | 43 |

| 2.19 | IC Shank Formation Procedure                                                | 44 |

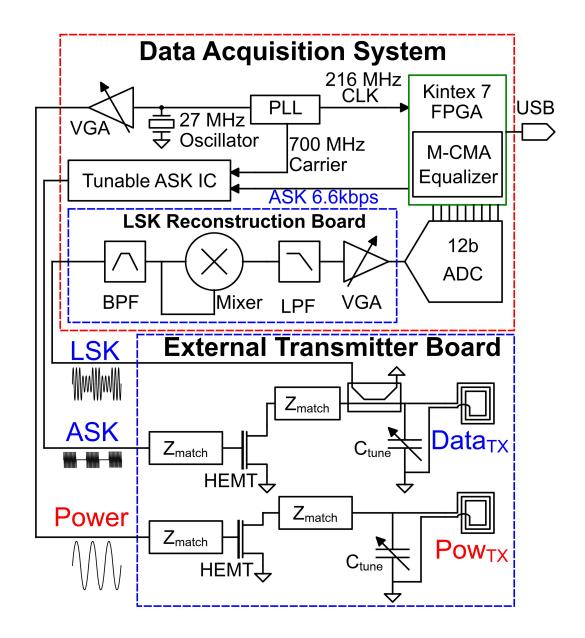

| 3.1  | System Block of full Reader System                                          | 47 |

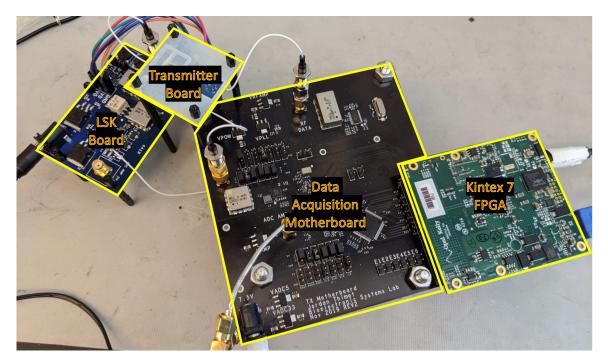

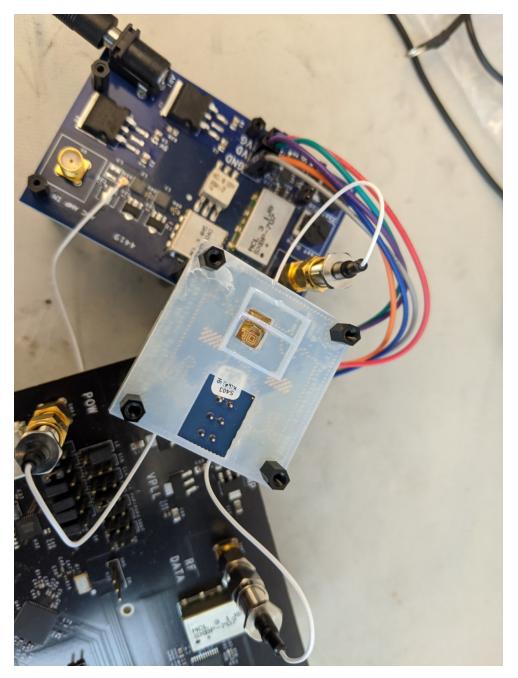

| 3.2  | Full Physical Reader System                                                 | 48 |

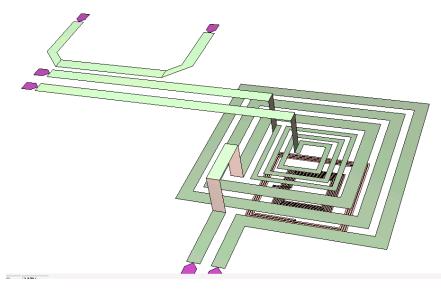

| 3.3  | Physical Layout of 4-coil System                                            | 48 |

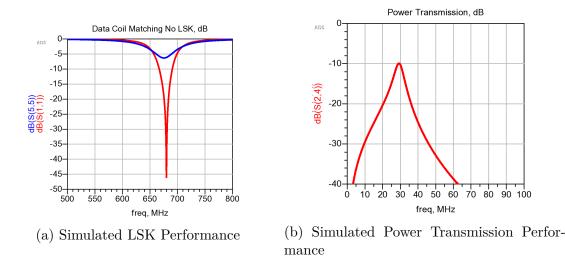

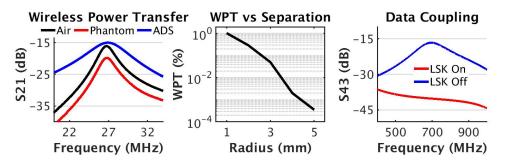

| 3.4  | Power and Data Transmission ADS Simulations                                 | 50 |

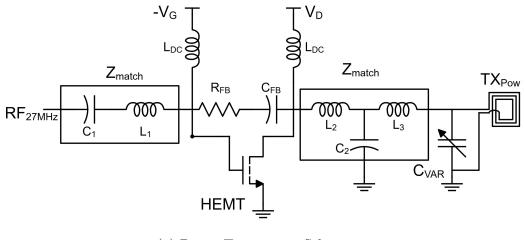

| 3.5  | Power and Data TX Board Circuitry                                           | 52 |

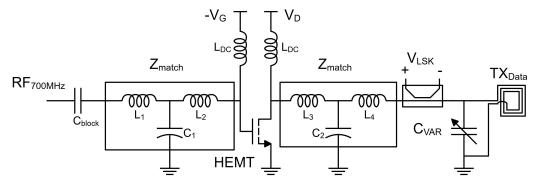

| 3.6  | Transmitter PCB with Reader Transmitter Coils                               | 53 |

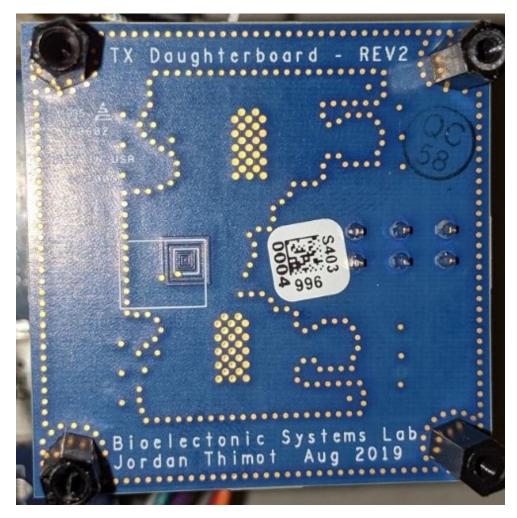

| 3.7  | TX Board Amplifier S-parameter performance                                  | 54 |

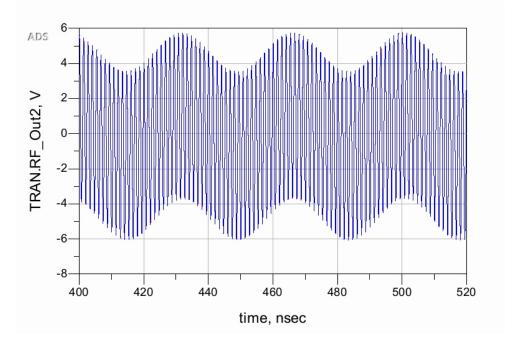

| 3.8  | Simulated expected waveform across data TX with normal implant operation    | 54 |

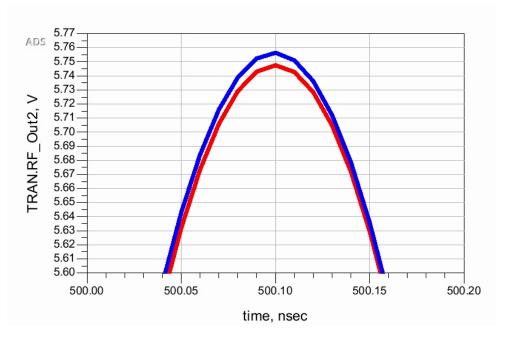

| 3.9  | 10mV Amplitude difference on carrier with LSK at different binary states                                 | 55 |

|------|----------------------------------------------------------------------------------------------------------|----|

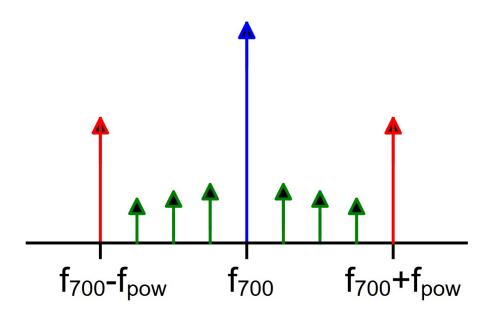

| 3.10 | FFT content of signal at data receiver                                                                   | 56 |

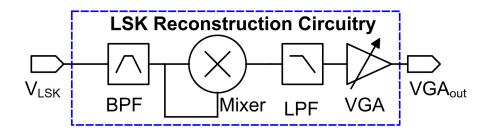

| 3.11 | LSK Recovery Circuitry Blocks                                                                            | 56 |

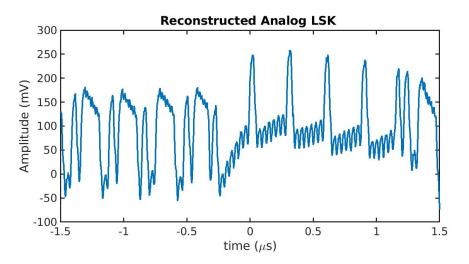

| 3.12 | Signal Waveform at output of LSK Reconstruction Board                                                    | 57 |

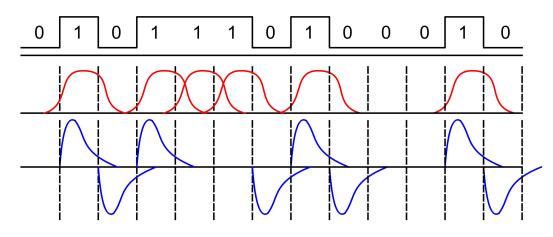

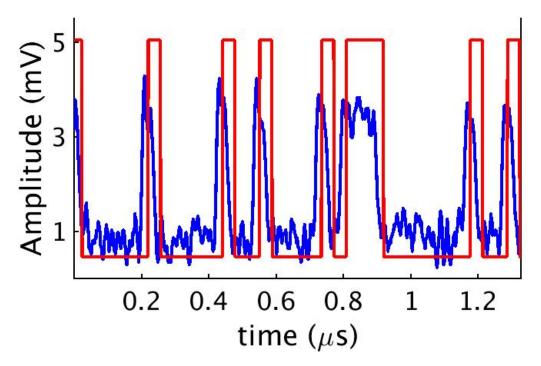

| 3.13 | ISI for implant (blue), standard NRZ ISI (red)                                                           | 59 |

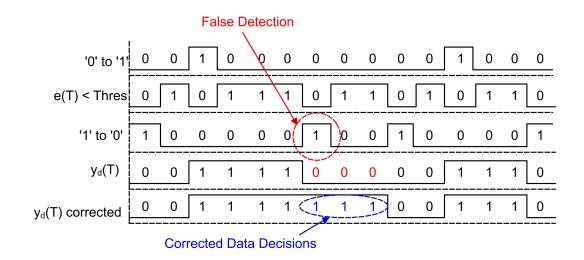

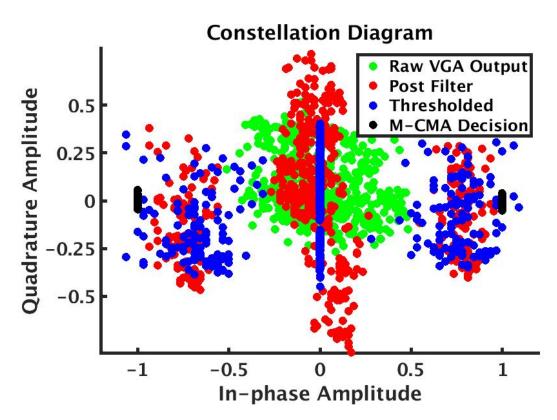

| 3.14 | Error Correction for M-CMA final decision                                                                | 60 |

| 3.15 | Expected Data Sequencing for input word '1111'                                                           | 61 |

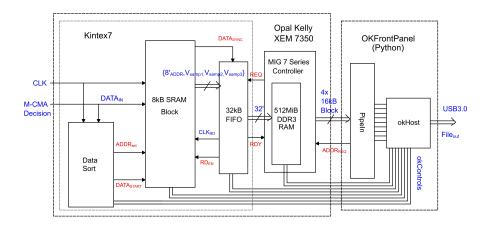

| 3.16 | FPGA design for real-time data sorting                                                                   | 63 |

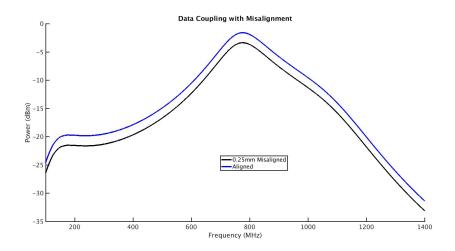

| 4.1  | Power Loss vs misalignment                                                                               | 66 |

| 4.2  | Methodology for Power Measurements                                                                       | 67 |

| 4.3  | Power delivery with 0.25mm alignment offset                                                              | 68 |

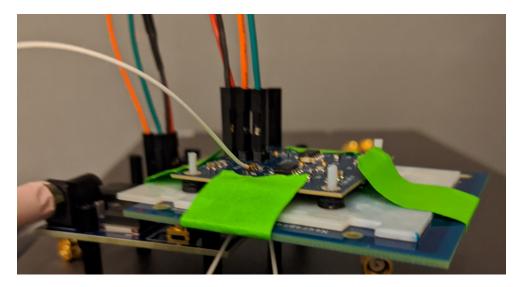

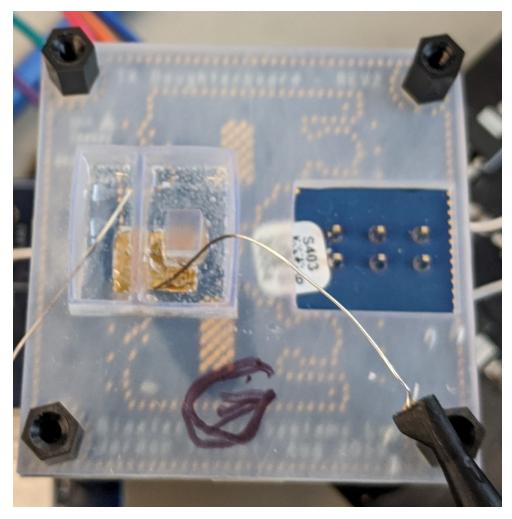

| 4.4  | 3D Printed Well for TX/RX Alignment                                                                      | 69 |

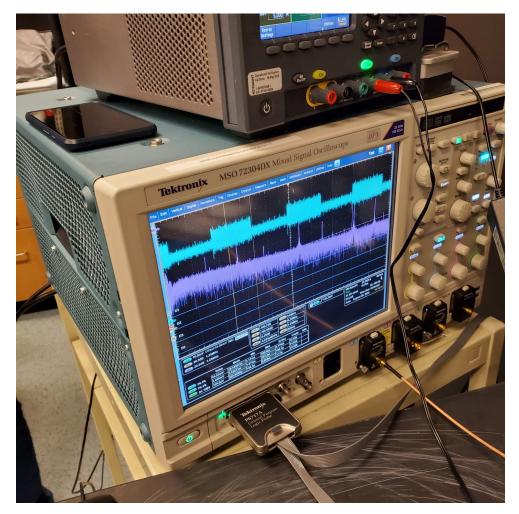

| 4.5  | Raw waveform post mixing and amplification (blue), with expected binary                                  |    |

|      | decision (red) $\ldots$ | 70 |

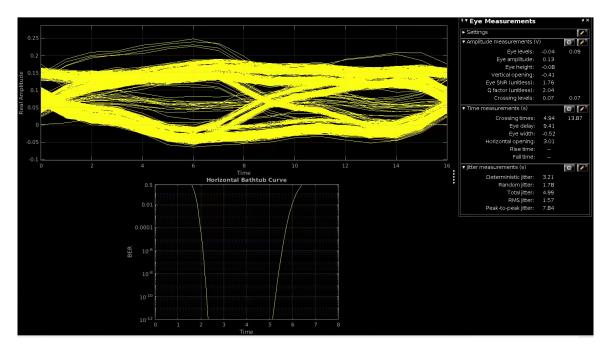

| 4.6  | Eye Diagram of Raw LSK Signal pre-equalization                                                           | 71 |

| 4.7  | Eye Diagram mid M-CMA Equalization                                                                       | 72 |

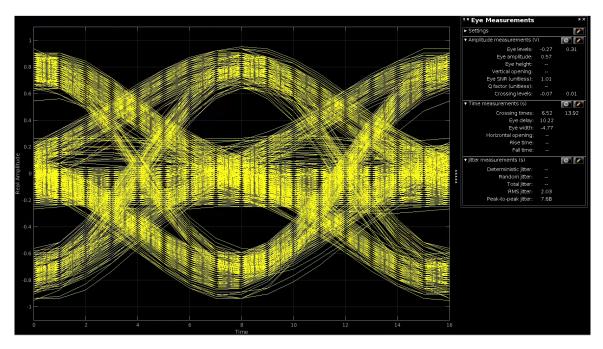

| 4.8  | Eye Diagram post M-CMA Equalization                                                                      | 73 |

| 4.9  | Constellation diagram at various stages of MCMA processing                                               | 74 |

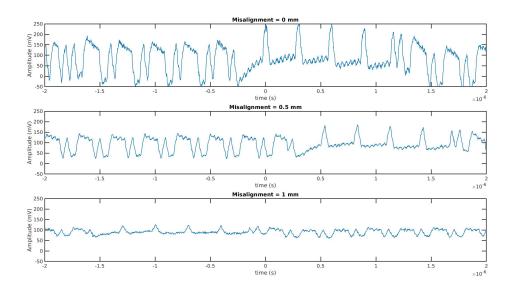

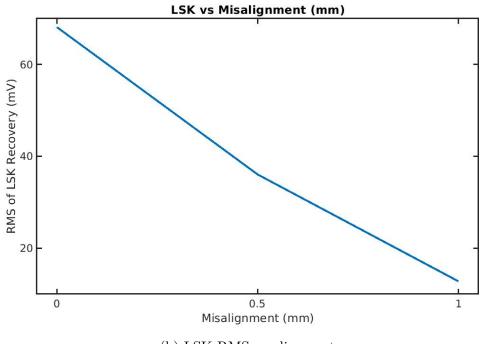

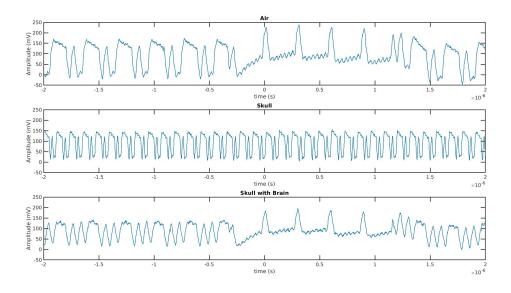

| 4.10 | Alignment effects on LSK                                                                                 | 79 |

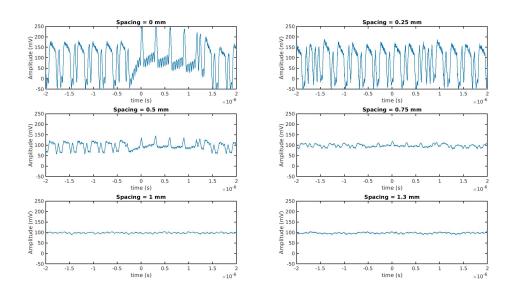

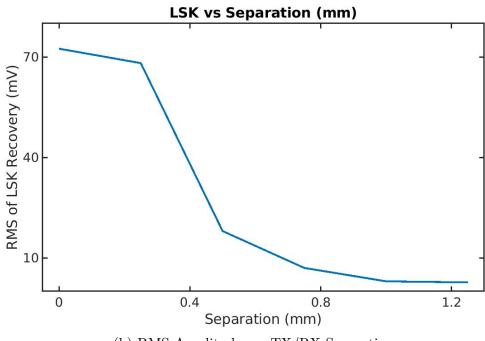

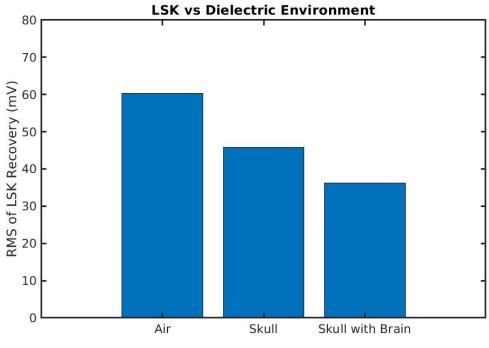

| 4.11 | $\mathrm{TX}/\mathrm{RX}$ separation effects on LSK                                                      | 80 |

| 4.12 | LSK for different dielectric media                                                                       | 81 |

| 4.13 | In-vitro measurement methodology                                                                         | 82 |

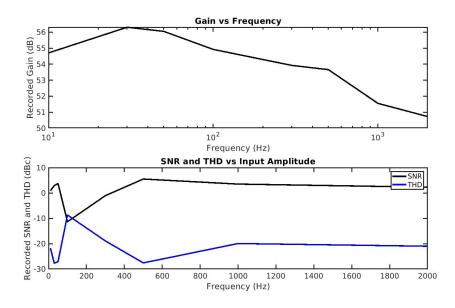

| 4.14 | Measured SNR, THD, and Gain for Amplification System                                                     | 83 |

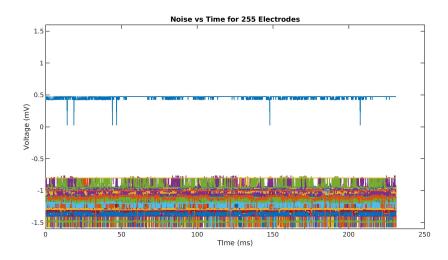

| 4.15 | Input referred noise waveforms for all 255 electrodes                                                    | 83 |

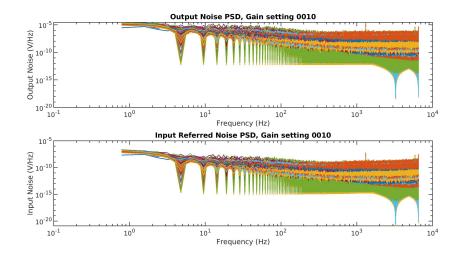

| 4.16 | Input referred PSDs for all 255 electrodes                                                               | 84 |

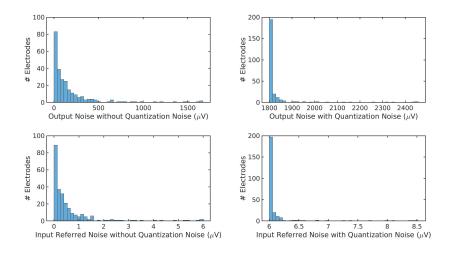

| 4.17 | Noise histograms for all 255 electrodes                                                                  | 84 |

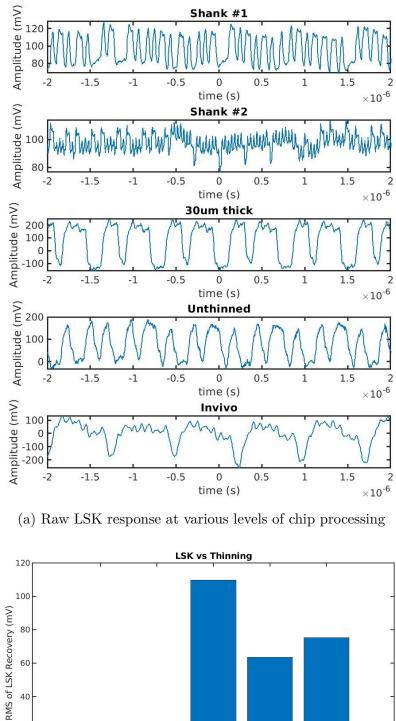

| 4.18 | Thinning and Processing effects on LSK                         | 85 |

|------|----------------------------------------------------------------|----|

| 4.19 | Fully processed implant                                        | 86 |

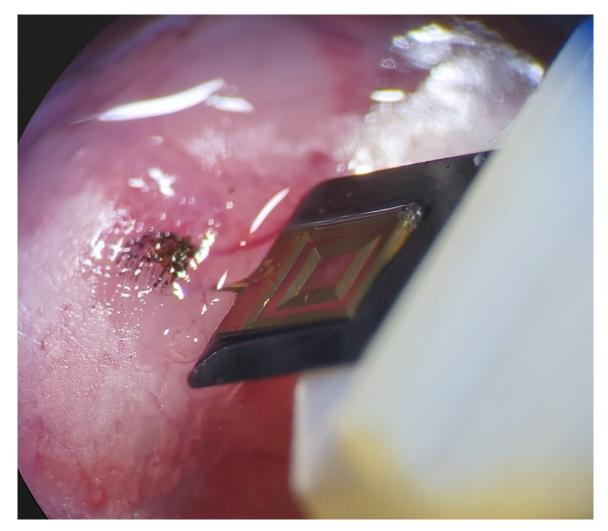

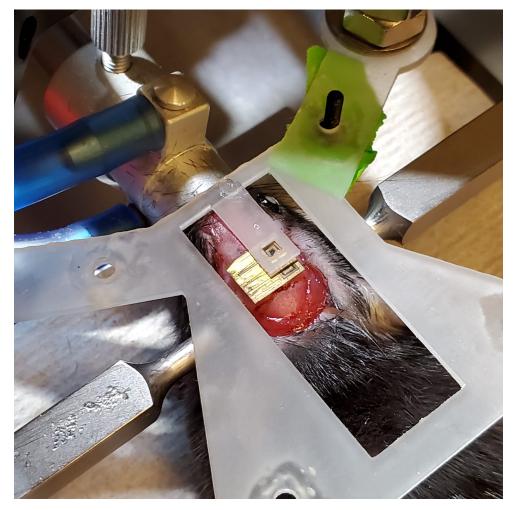

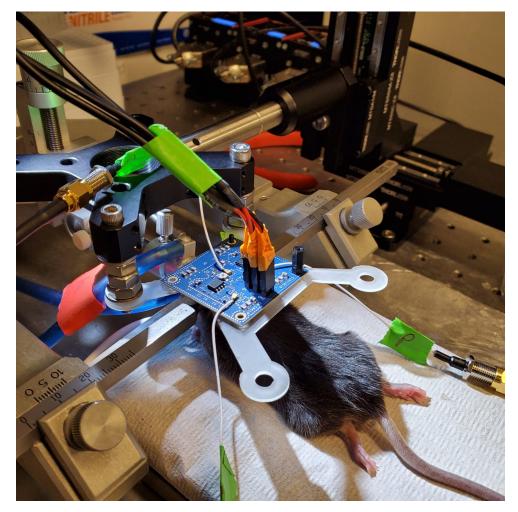

| 4.20 | Implanted transceiver with guide shank mid insertion           | 87 |

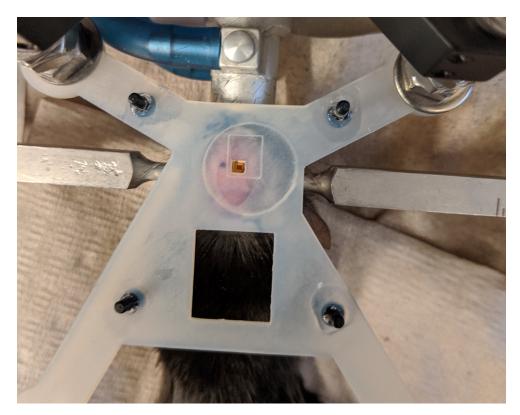

| 4.21 | Interposer system for aligning inserted probe to reader system | 88 |

| 4.22 | Surgical Insertion Process                                     | 88 |

| 4.23 | Thinned Die on surface of Mouse Brain                          | 89 |

| 4.24 | Transceiver Alignment Invivo                                   | 90 |

| 4.25 | In-vivo LSK functionality                                      | 91 |

## List of Tables

| 3.1 | 4 Coil Link Physical Parameters              | 49 |

|-----|----------------------------------------------|----|

| 5.1 | Comparison to other implantable transceivers | 94 |

| 5.2 | Comparison to Shank Systems                  | 94 |

## Acknowledgments

Over my 7 years at Columbia working and studying as a member of the Bioelectronic Systems Lab, I have met many incredible, intelligent, and hardworking people who have supported me during even the most trialing of times. I would like to thank my advisor, Ken Shepard, for introducing me to the world of biomedical implants and for providing his support and guidance on this journey.

I would like to thank all my colleagues for any and all help over my time here. In particular I would like to thank my colleagues Adrian Bradd, Jake Rabinowitz, Jeff Elloian, Esha John, Chen Shi, Girish Ramakrishnan, Scott Trocchia, Steven Warren, Siddharth Shekar, Daniel Fleischer, Yihan Zhang, Maria Vomero, Kukjoo Kim, John Barth, and Fengqi Zhang for their wide knowledge and assistance during my work and more importantly for their friendship and support. I would like to especially thank both Kevin Tien and Jeffrey Sherman for imparting in me just a fraction of their knowledge about electrical engineering as a whole. I have learned more from those two in casual conversations than can be quantified and they were always available and willing to help when a problem was presented. Outside the lab, I would like to thank Daniel de Godoy Peixoto, Syed Athar, Christopher Jayne, and Chris Barr for their friendship. I would like to thank my parents and siblings for their support. Finally, I want to thank my future wife Emily for her unending support and love. Without her, completing this thesis would have been an impossibility. Thank you.

## Chapter 1

## Introduction

Inductively coupled links have become commonplace in supplying both power and data to implantable medical devices (IMDs). Previous wireless IMDs have typically used off-chip receiver (Rx) antennas and circuitry for telemetry and voltage rectification, increasing the required volume of the implant considerably and creating a rigid interface between implant and tissue that triggers stronger immune response [1–4]. In our case, we seek to push down the scale and form-factor of RF transceivers and wireless powering to create millimeter-scale antennas for these links and do so on-chip, while achieving Mbps data rates and mW-scale power levels at mm-scale implantable depths. Other approaches for scaled power transfer such as ultrasound [5], which have advantages in implantation depth, do not allow high-data-rate telemetry because of MHz-scale carrier frequencies.

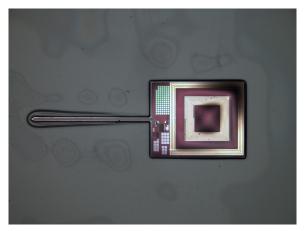

Our wireless implant has the Rx antennas integrated on-chip and, by thinning the

substrates to 15µm, allows the implant transceiver to displace an overall volume of less than 0.08 mm3 with the Rx coils covering an area of only 4 mm2. Once thinned, the integrated transceiver has the form factor of tissue paper allowing it to conform to tissue surface. Removal of the lossy silicon substrates also improves wireless power transfer (WPT) efficiency.

The requirements for mW-scale power and Mbps-scale data rates necessitates the use of backscatter techniques (passive modulation of Rx resonance frequency) for data uplink (IMD to outside). Other high-data-rate telemetry techniques such as the use of ultra-wide-band (UWB) transmitters or non-passive frequency modulation, require larger antennas and power amplifiers to drive the antennas to achieve acceptable biterror-rates (BERs) [6]. The use of millimeter-scale integrated coils produces smaller transmission radii and lower power transfer efficiency (PTE) than what would be achievable with larger, lower-loss antennae. Backscatter data transfer at high-datarates with this antenna scale through lossy media, even at mm-scale implantation depths, also presents intersymbol-interference (ISI) challenges, which we overcome with extensive equalization of the channel.

This thesis will be divided into 5 chapters including this introduction. The remainder of chapter 1 provides an background information to the three main topics covered by the application space of this work. Specifically the three section to be covered will be a discussion on the history of wireless power systems, with an emphasis on how system design changes in biological media, a discussion of wireless data communications techniques, with emphasis of reconstruction in an unknown wireless channel, an introduction to the intended application space of the transceiver system, neural interface systems for recording in the brain of mice. Chapter 2 will cover the design of the ASIC itself, specifically covering the circuit design of critical blocks and designed performance metrics. Also covered will be the thinning and post-processing that is performed on the chip to become flexible and reduce implant volume. Chapter 3 will cover the design of the external reader system. Heavily emphasis in this section will be devoted to data reconstruction of the back-scattered data signal, as a custom and rigorous equalization technique needed to be implemented to maintain connection across the wireless channel. Chapter 4 will cover the simulated and measured results of the implant systems that are covered in chapters 2 and 3. Finally, chapter 5 will conclude the work with a summary of the results and discussions of future work that can be done on comparable systems.

#### 1.1 Wireless Near-Field Power Systems

Through the history of development of IMDs, the need for transmission of wireless energy to power the implant, typically referred to as wireless power transfer (WPT), has become a main staple in most implants [7]. Wireless power has been a topic of interest even outside of the biomedical field since Nikola Tesla's experiments for worldwide wireless power distribution in the late 19th to early 20th century [8]. The type of operation for wireless power networks can be broken down into three distinct regions: the reactive near-field region, the radiating near-field or Fresnel region, and the far-field or Fraunhofer region [9]. Far-field transmission is suitable for a variety of uses, typically either low-power sensor networks where efficiency is not a concern and the entire network could be safely illuminated with radiation to supply low amounts of power to all receivers in the field, or in military or space applications, where both the efficiency and cost hits are necessary for the application space. For most applications, where both higher power transfer and power transfer efficiency (PTE) become the driving force in the design, the transmission radius must be reduced into the nearfield or Fresnel region. While this limits the physical radius of operation of systems, it greatly improves both operating efficiency of the system and safety, as the distance between receiver and transmitter is typically on the order of a wavelength or less, and radiated power outside that zone is considerably lower and thus well outside specific absorption rate (SAR) limits as indicated by the IEEE [10]. By definition the three wireless regions are defined by:

$$\begin{aligned} Near - Field : & R < 0.62 \sqrt{D^3/\lambda} \\ Fresnel : & 0.62 \sqrt{D^3/\lambda} < R < 2D^2/\lambda \end{aligned} \tag{1.1}$$

$$Fraunhofer : & R > 2D^2/\lambda \end{aligned}$$

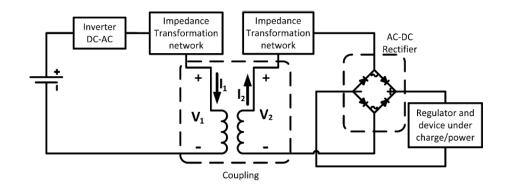

Where R is the distance from the antenna, D is the largest dimension of the antenna, and  $\lambda$  is the wavelength of the electromagnetic wave [9]. Depending upon application, research into WPT based technologies are split into far-field radiation systems [11–14] and near-field systems [15–18]. In the near-field the magnetic field dominates inductive coupling between close proximity antennas, which greatly increases the coupling, mutual inductance, and wireless power transfer between a matched coil pair. This has made near-field magnetic coupling the go to method for wireless power transfer for high efficiency systems. A general model for a near-field WPT system for DC delivery in an implantable system is depicted in figure 1.1. A inductor coil pair is matched to impedance transformation networks such that the ratio of the radiation resistance for each coil is maximized. This occurs when the input matching network's impedance is designed to be the complex conjugate of each inductor's impedance at the desired resonance frequency. Examples of wireless power systems utilizing the near-field magnetic field strength for high efficiency WPT are commonly seen in the biomedical application space [19–24].

For a printed circuit board loop antenna, the self-inductance of a single loop antenna coil can be calculated by the equation:

$$L_{self}(R,w) = \mu R[ln(\frac{16R}{w}) - 2]$$

(1.2)

Figure 1.1: Standard WPT Model for Wireless Systems

Where R is the radius of the loop,  $\mu$  is the magnetic permeability of the surrounding medium, and w is the diameter of the wire, assuming a circular cross section [25]. For an N turn loop, the self-inductance is scaled by a factor of N. When two coils are placed within close proximity, the mutual inductance for the coil pair in the near field can be calculated by the Neumann formula to be:

$$M = \frac{\mu}{4\pi} \oint \oint \frac{dI_1 \cdot dI_2}{R} \tag{1.3}$$

Which involves the double line integral of both the magnetic fields generated by the current in  $L_1$  and the field generated by the current in  $L_2$  [26]. Solving this integral two circular inductors, the mutual inductance between 2 coils in a link can written as functions of the effective spiral radii and number of turns of each spiral, and the separation radius:

$$M_{12}(R_1, n_1, R_2, n_2, d_{12}) = \frac{\pi \mu_o n_1 R_1^2 n_2 R_2^2}{2\sqrt{(R_1^2 + d_{12}^2)^3}}$$

(1.4)

Giving mutual inductance dependence and therefore coil coupling on coil separation as  $\frac{1}{d^2}$ . The coupling coefficient, k, can be written as a function of the coil inductances and mutual inductance, and the quality factor, Q, of an inductor can be expressed as a function of the coil inductance and internal resistance:

$$k_{12} = \frac{M_{12}}{\sqrt{L_1 L_2}} \tag{1.5}$$

$$Q = \frac{\omega L}{R} \tag{1.6}$$

Algebraically combining equations for k, Q and solving the 2-port RLC equivalent for the near-field wireless power transfer, we can determine the theoretical peak efficiency of the link without load to be:

$$\eta_{max} = \frac{k_{12}^2 Q_1 Q_2}{(1 + \sqrt{1 + k_{12}^2 Q_1 Q_2})^2} \tag{1.7}$$

Now considering loads, At resonance for a near-field coil pair, the power delivered to a load attached to the receiver can be calculated to be:

$$P_{load} = \frac{V_{in}^2 \omega^2 M^2 R_L}{(R_1 (R_2 + R_L)^2 + \omega^2 M^2)^2}$$

(1.8)

Where  $R_1$ ,  $R_2$ ,  $R_L$ ,  $V_{in}$ , and  $\omega$  are the parasitic coil resistances, the resistance of the load being driven at the output of the receiver coil, the input voltage to the transmitter coil, and the frequency of operation respectively. From this equation, we see that the output power is a direct function of the input power at the TX, and will increase with mutual inductance as a function of the driven load. The power transmission efficiency for a driven load can be then written as:

$$\eta_{load} = \frac{\omega^2 M^2 R_L}{R_1 (R_2 + R_L)^2 + \omega^2 M^2 (R_2 + R_L)}$$

(1.9)

In general this means the PTE of a wireless link increases as the series resistance of the transmitter and receiver coils are minimized. Using these equations, the WPT can be maximized by designing inductors  $L_1$ , and  $L_2$  to have low parasitic resistance, high self and mutual inductance, and high quality factors [27, 28].

#### 1.1.1 WPT in Biological Systems

For implantable systems, the use of near-field inductive links has become the standard technique for wireless power transfer [29–33]. Biological systems are unique transmission mediums and may, in general, be described as a fairly dense, lossy, dielectric that presents difficult challenges to maintain functionality without harming the biological system in which the system is implanted. In order to properly simulate expected electromagnetic losses in in-vivo systems, living tissue may be modeled as a planar set of layered homogenous boundaries with the appropriate permittivities and conductivities [7].

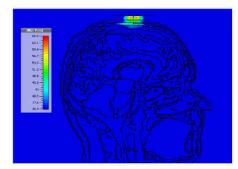

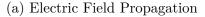

The dielectric properties of tissue result in high power absorption, particularly in terms of the electric field, making far-field communications extremely difficult, and requiring near-field inductive links [32, 34]. Luckily for magnetic coupling, the magnetic permeability in a majority of tissues is close to 1, causing the magnetic permeability to approach  $\mu_o$ , the permeability in free space, favoring inductive links for both data and power transmission in implants even more [35]. Simulations highlighting this stark difference in energy radiation between electric and magnetic fields were performed by [32] can be seen in figure 1.2.

(b) Magnetic Field Propagation

Figure 1.2: Near-field E and H penetration in a human head model

Temperature considerations are also critical for WPT in tissues, as the tissue

absorbs a significant amount of energy in radiated electromagnetic fields which is quantified as the specific absorption rate (SAR). Mathematically SAR can be expressed as:

$$SAR = \frac{\sigma}{2\rho} \mid E \mid^2 \tag{1.10}$$

Which shows a quadratic relationship of SAR to the generated electric field [36]. In general the magnetic field in tissues are approximately equal to the equivalent field in air, since the magnetic permeability of tissues in general is close to one. Therefore energy focused into electromagnetic fields in tissue will primarily be delivered by the magnetic component, why the loss and heating components will be dominated by the electric field. Any tissue heating, particularly in brain tissue, causes damage to living cells, which places extra emphasis on power transfer efficiency to maximized as much as possible in a biological environment for implants.

#### **1.2** Wireless Communications Links

For near-field data communications, emphasis on wireless power transfer is not as important as for near-field power links, with a large emphasis placed on signal bandwidth for increased data rate. From an antenna standpoint, wider bandwidths actually occur from a lower quality factor, meaning antenna layout needs to be adjusted to increase coupling and bandwidth at the cost of power delivery and efficiency. This section will cover the encoding techniques commonly used in implant technologies and in wireless communications in general, and will cover the primary data recovery technique on the receiver side for noisy channels, equalization.

#### **1.2.1** Encoding Techniques

For wireless data transmission, a carrier signal is modulated in order to encode data onto a higher frequency system. In the near-field, the primary mode of energy coupling is still the magnetic field as was the case for WPT. The oldest standard in near-field coupling is the radio-frequency ID tag (RFID) which was invented in the 1940s [37], where data is measured by reflected power from a receiver coil in the presence of a transmitter. RFID was limited to 1-directional communications however, so various bi-directional near-field communications (NFC) systems were developed. The most common modulation techniques used for near-field magnetic systems include amplitude modulation methods such amplitude-shift-keying (ASK) and on-off keying (OOK), load-shift-keying (LSK), and cyclic on-off-keying (COOK). In each of these amplitude modulation methods, the magnitude of magnetic coupling occurring in the transmitting antenna is increased or decreased which can be demodulated on the receiver side using circuitry.

Frequency modulation encoding techniques include frequency-shift-keying (FSK), phase-shift-keying (PSK), passive-phase-shift-keying (PSSK), and for extremely high data rate communications, impulse radio-ultra wideband (IR-UWB) encoding is used. Frequency modulation techniques modify the phase relationship of a carrier frequency, while maintaining relatively even magnitude over time, and the binary decisions sent by the transmitter can be recovered from the frequency shifts using demodulation circuitry on the receiver, typically in the form of in-phase and quadrature (IQ) demodulation circuitry [38–42].

#### 1.2.2 Load Shift Keying

For this work, the primary encoding technique employed is LSK. For a fully wireless link where both power and data are supplied, a 4-coil link (figure 1.3) is often created,

Figure 1.3: 4-Coil Model for simultaneous power and data transfer.

with one 2-coil pair (coils 1 and 2) employed for the wireless power link, and the other 2-coil pair (coils 3 and 4) employed for the data communications link. By tuning the power coil pairs to have a sufficiently different resonance frequency than the data coils, the cross coupling terms,  $k_{14}$  and  $k_{23}$  can be ignored. Typically modeled into the lumped loss impedance calculated for the wireless power transfer equations is the reflective impedance contribution from other coils in the link, Zr. This reflective impedance comes from the backscattered return path from the transmitter coil to the receiver coil and by definition can be modeled as, where the data coils are now coils 1 and 2:

$$Z_r = \frac{(\omega M_{12})^2}{Z_2} \tag{1.11}$$

Which has proportionality to the square of the mutual inductance. This means that the backscattered amplitude of an LSK signal falls off as a function of the separation radius cubed! For near-field links, which typically only operate at separation distances of 1 to 2.5 times the largest geometric feature on a transmitting inductor [43], this means the effective communication radius on an LSK link will likely fall below the outer diameter of the transmitting coil.

Adding the reflective impedance in the 4-port circuit depicted in 1.3, circuit analysis, and working under the assumption the coupling coefficients between the power coils and the data coils are not considered to be significant since the power coils are tuned for a different resonance, the effective 2-port network for the LSK coil pair can be changed into the form of figure 1.4. Algebraically, we can determine the impedance on the receiver side,  $Z_2$  to be:

Figure 1.4: 2-Coil Model including Reflective impedance for LSK Encoding

$$Z_2 = j\omega L_2 + (R_2 || C_2) \tag{1.12}$$

Using voltage division, the voltage across the transmitting inductor,  $V_{L1}$ ), is :

$$V_{L1} = \left(\frac{j\omega L_1}{R_1 + Z_r + j(\omega L_1 - \frac{1}{\omega C_1})}\right) V_{in}$$

(1.13)

Mathematically at resonance the conditions:

$$j(\omega L_1 - \frac{1}{\omega C_1}) = 0 = j(\omega L_2 - \frac{\omega C_2 R_2^2}{1 + \omega^2 C_2 R_2^2})$$

(1.14)

are satisfied. Using these resonance conditions and equations for Z2, Zr, yields an expression at resonance for the ratio of the input voltage to the transmitter voltage in terms of the coupling coefficient and quality factors of the coils:

$$\frac{V_{in}}{V_{L1}(\omega = \omega_o)} = -j(\frac{1}{Q_1} + \frac{k^2}{Q_2})$$

(1.15)

When the LSK enabled, the switch is closed so the effective parallel capacitance increases from  $C_2$  to  $C'_2 = C_2 + nC_2$ . Adding this parallel capacitance to the network and rederiving the voltage ratio yields:

$$\frac{V_{in}}{V_{L1}(\omega = \omega_o)} = -j(\frac{1}{Q_1} + \frac{k^2}{Q_2}) + k^2n$$

(1.16)

Meaning the resonance shift in the receiver from load-shift-keying causes an increase in the real impedance as seen by the transmitter, which causes an extremely small dip in the output power of the transmitter power amplifier when the LSK switch is opened or closed.

#### **1.2.3** Intersymbol Interference and Signal Equalization

As in all wireless communications systems, infinite bandwidth would be required to fully received a perfect binary waveform across a wireless medium. In physical systems, bandwidth is finite, meaning sent binary levels will be both decayed and spread out in the time domain to the point that one symbol's time response will bleed into the next and possibly multiple consecutive symbols. This bleeding effect is referred to as intersymbol interference (ISI). Figure 1.5 depicts typical ISI in a binary communication system [44].

Mathematically the original binary input waveform transmitted,  $\omega_{in}(t)$ , can be written as:

$$\omega_{in}(t) = \sum_{n} a_n h(t - nT_s) \tag{1.17}$$

Where  $a_n$  Refers to the valid amplitude levels for different transmitted data, h(t)is the unit impulse response, and  $\delta(t - nT_s)$  is a unit dirac delta function with a

Figure 1.5: Example of ISI on received bianry pulses in a communication system

time width of  $1/T_s$ . For a binary phase-shift-key sequence the valid values of  $a_n$  are 1 and -1. This binary waveform gets corrupted during transmission by the channel's unknown transfer function  $h_e(t)$  yielding the output corrupted waveform mathematically as:

$$\omega_{out}(t) = \sum_{n} a_n h_e(t - nT_s) \tag{1.18}$$

The corruption of this signal is identified as the ISI, and must be removed in order to create an accurate wireless data link. One of the primary methods of removing ISI from a signal is equalization. One form, linear channel equalization, involves the use of a linear filter, called the equalization filter, which narrows the band of a distorted digital waveform thus reducing the effects of ISI. This linear filter has a set number of taps, each with different weights corresponding to the equivalent coefficients of the filter's transfer function. A normal linear filter FIR topology is depicted in figure 1.6 [45].

Since the actual wireless channel can be unknown, and can change from causes such as interference or the multi-path problem, it becomes important for the equalizer

Figure 1.6: Direct form linear FIR filter with 4-taps

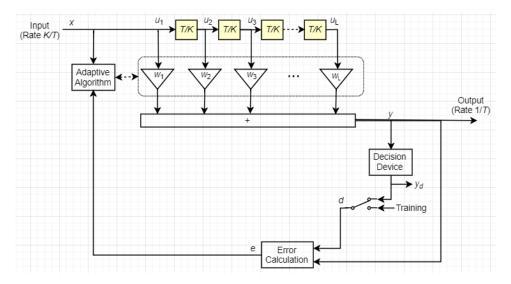

to be able to adapt to the channel through the use on an adaptive filter. By adapting the weights of the linear FIR filter using a feedback algorithm by defining an error function, the linear filter is transformed into a linear equalizer. The structure of a linear equalizer with adaptive feedback takes the structure depicted in figure 1.7 [46]. A linear equalizer is specified to have N taps, with M taps per symbol decision

Figure 1.7: Structure of a Linear Equalizer

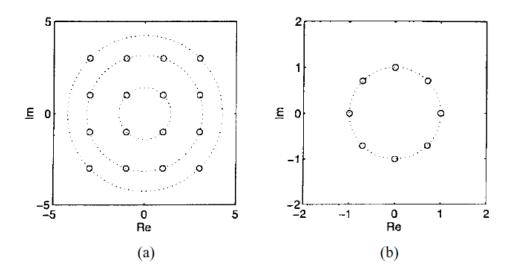

To determine the error of the equalization channel, desired amplitude and phase responses for respective binary values are predetermined in Hilbert space with a time width corresponding to a single symbol. Error is considered to be minimized, when the value of the hilbert-space magnitudes matches the input waveform after going through the equalization filter. Those desired points can be plotted on a quadrature graph called the channels desired constellation. Two of the most commonly used hilbert-space data constellations are depicted in figure 1.8 [47].

Figure 1.8: 16-QAM Constellation with a variable Modulus (a) and 8-PSK with Constant Modulus (b)

The method at which the filter weights is tuned generally referred to as the used equalization algorithm. The most common adaptive equalization algorithms are the Least Means Square (LMS), Recursive Least Squares (RLS), and the Constant Modulus Algorithm (CMA). For the LMS and RLS adaptive algorithms, the filter weights for all taps start with a normalized value of one and by recursive application of a training sequence, where the desired output is already known to the equalizer. For the CMA algorithm, no training sequence is necessary, since the filter goal is to create a constant magnitude with only phase changes for every symbol decision. Since a training sequence is not necessary, the CMA algorithm is the only application error function that is compatible with the implant transceiver [46–48].

The ultimate quality measure in optical communication links is the bit error ratio (BER). However, a direct experimental BER determination can be done only as long as the link is out of service (if not a hard-decision forward error correction (FEC) is able to report errors), because a known data sequence has to be transmitted, and it

consumes a significant amount of time if the BER is small.

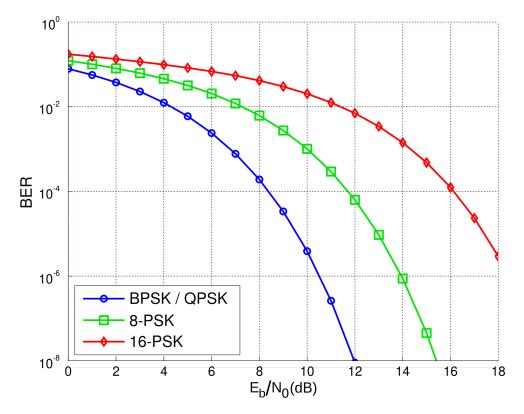

The BER of a signal is a direct function of the ratio of the energy-per-bit transmitted in the signal to the noise level of the received signal, known as  $E_b/N_o$ . For different designed hilbert-space constellations, the theoretical BER as a function of  $E_b/N_o$  is depicted in figure 1.9.

Figure 1.9: Theoretical BER vs  $E_b/N_0$  for common constellations

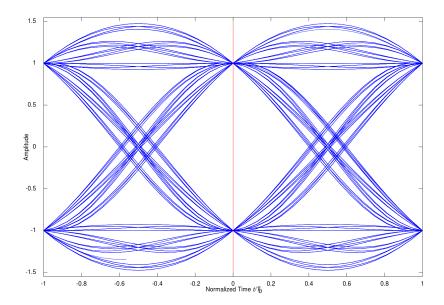

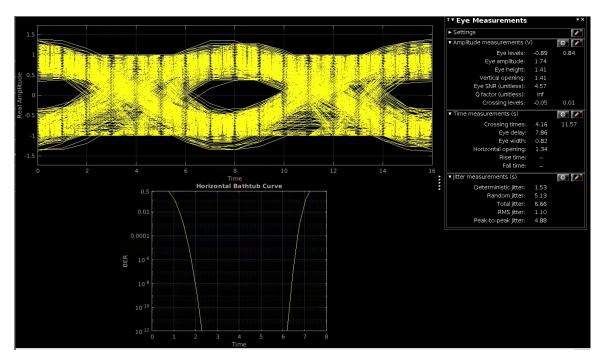

Plotting at the graph of the hilbert-space function of binary-encoded constellation data over the sample period T, a pattern forms known as the eye diagram (figure 1.10). Based on both the height and width of this eye, a graph known as a bathtub curve can be generated, the spacing of which can be used to estimate the BER of an equalized signal depending upon both the amplitude and phase of the sample point in the periodic time in hilbert space. By choosing the center of the eye both in phase jitter, and in noise amplitude, BER of a wireless link can be minimized [49–51].

Figure 1.10: Ideeal Eye Diagram for PSK

### 1.3 Implantable CMOS Devices

Along with the development and advancement of microelectronics, modern IMDs have been developed to assist in treatment of a plethora of diseases for both monitoring and treatment of patients. Because of size constraints and power limitations, a variety of different power systems have been developed, typically employed using small shortterm batteries that require regular charging to maintain functionality of the implant or a physical tether outside of the body that supplies both energy and data to and from the implantable system. Specifically in this thesis, the primary discussion of IMDs will pertain to neural interface systems. As opposed to larger IMD systems such as cochlear implants, pace makers, or heart monitors where a large foreign object can be easily stitched in-between tissue layers without causing a strong immune response, neural interface systems must take a much smaller form factor so as not to displace a large amount of tissue and disrupt neural behavior. The exact volume limit that an IMD is aiming for is therefore extremely dependent upon the organism in which it is being implanted. For our application, we have designed a transceiver system that is compatible with neural recording systems for laboratory mice. Since the mouse brain's dimensions are on the order of a couple centimeters as opposed to a primate brain which is on the order of 10s of centimeters, the volumetric displacement must be limited to far less than  $1mm^3$ . In addition, a shank-based approach with a several millimeter long and approximately 100 micron wide electrode interface will allow for deep brain recording in the targeted region of the mouse brain.

Most current neural recording systems utilize passive silicon shanks in which only electrodes and wires exist on the shank itself with all the electronics external. Recent advances in nanofabrication techniques have allowed these systems to scale to up to 256 recording sites per shank. More recently, active CMOS probes have been developed that incorporate the electronics on the shank itself, allowing even higher channel counts [52–54]. These CMOS neural probes, however, require a physical tether to a power source and data acquisition system requiring wiring through the skull and skin of the animal and mechanical fixation of the probe to the skull, resulting in additional damage and inflammation as the brain moves relative to the probe. A picture of the state-of-the-art neuropixel system [55] highlights how large and bulky these tethers can be.

To remove the requirement of a bulky tether, the design addition of an integrated transceiver on the ASIC itself is proposed. This transceiver will be fully wireless and is designed to be completely implanted in the brain of the mouse itself for recording, mechanically floating with the brain. Figure 1.12, depicts the intended final application space of this thesis, a small wireless implant system-on-chip, with a shank inserted deeply into the tissue of a mouse brain with both power delivery and data telemetry supplied by an external reader system that communicates with the chip via near-field RF communications. In addition, in order to lessen the immune response of the brain tissue, the chip will be thinned While other systems have used wireless

Figure 1.11: Commercial Neuropixel System

power and data telemetry for biomedical implants, these efforts have all used multiple components, specifically large off-chip antennas, increasing the required volume of the implant considerably [1–3]. Since the system proposed decreases the entire package volume considerably, the dedicated area for a front end neural interface is limited compared to commercial systems, and this trade-off will be seen in the number of total sites that can be integrated on a single system, the speed and accuracy of integrated data converters, and the overall range of tunable controls for an amplification system.

Compared to other wireless implants, neural systems require a much higher data bandwidth than cochlear or cardiac devices, as the neural signal content covers both a much higher bandwidth, and the density of sites to be recorded from is significantly higher. To address this, while still providing a fully wireless system, the proposed system will utilize the highest data rate possible communications scheme while still maintaining a very small volumetric form factor. The primary consequence of higher data rates means significantly higher operational bandwidth than what might be seen

Figure 1.12: Proposed System Application

in current medical devices. While a wireless band is already dedicated for medical implant communications (known currently as the MedRadio bands) in the low 400MHz range, the data bandwidth of these bands is limited to 300kHz [56–58]. Neural signals cannot be properly captured at this small a data bandwidth, as the primary frequency content of high frequency potentials can be as high as 10-20kHz. As such, current neural recording systems require data bandwidths of 10-30kS/s per site! With only a 300kHz data band to work with, that would limit the total number of concurrent sampled sites to approximately 10, and that's assuming a multi-bit sample can be sent in a single cycle. To achieve higher data rates, therefore, the use of both a higher and non-standard frequency carrier is required, in addition to the use of a custom data protocol that will maximize data communication rate.

### Chapter 2

## **Design of Implantable ASIC**

### 2.1 Design Specifications and Goals

In the design of this ASIC implant, there are three distinct sub-blocks each with their own set of requirements to meet the desired goals of the implant system. These three blocks are the physical antennas for both power and data telemetry, the datamodulation and demodulation systems, power harvesting circuitry, including clockand-data recovery, and the biological interface circuitry including front end amplifiers and on-chip ADC. In parallel, each of these sub-blocks was also designed to operate after being thinned post-fabrication from the foundry.

A system block of the implantable IC is depicted in figure 2.1. The overarching ASIC design goals were to be able to be fully wirelessly power-able while remaining under the Specific Absorption Rate (SAR) limit specified by the IEEE guidelines for limited exposure for medical implants and for the transceiver to provide a high enough data-rate to be able to concurrently sample all sites in the neural amplification system at a high enough sample rate to capture the relevant data bandwidths for neural signals.

Figure 2.1: Implant IC System Block

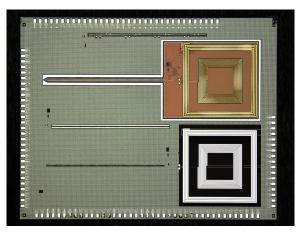

The final IC layout with each major block labeled is depicted in figure 2.2. The shank with bio-interface circuitry measures 3.25mm by  $70\mu m$  wide, with  $60\mu m$  of metal exclude for post-processing of the shank. The antenna blocks with power and data coils measures 2mm by 2mm with all remaining circuitry encompassed in a 0.5mm by 2mm block. A majority of the remaining circuitry's area is taken up by arrays of decoupling capacitors to maintain as steady a DC voltage to power the ASIC as possible. The simulated power required to fully power the implant is 2.7mW for the transceiver circuitry, and 1.5mW for the neural interface system and ADC. Including insertion loss, this requires 10.4mW of total WPT from reader to implant to achieve full wireless functionality.

Figure 2.2: Physical Layout of Implantable ASIC

### 2.2 Near-field Four Coil Design

For the on-chip antennas, the first design decision was which type of wireless link to employ, with the most common link types for implant systems described in detail in Chapter 1. Also, the antennas were designed considering both the specific-absorptionrate (SAR) limits as specified for localized fields by the IEEE standards. In order to meet these absorption rates, assuming the overall PTE would be on the order of 1-3%and at least 50% of the energy received by the power coils could be harvested, a total power budget of 1W was given at the reader transmitter, leaving 10mW of expected received power in the implant power coil, resulting a total of 5mW remaining for all the circuitry in both the transceiver and the neural amplifier system.

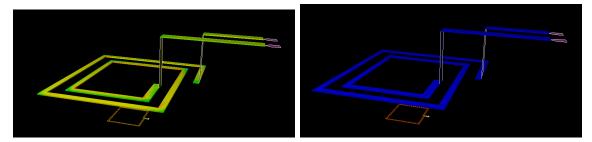

The downsides of using integrated inductors for transmission comes with the problem of electrical smallness. As you can see from plots of the current distributions given in figure 2.3, the transmission efficiency of IC side radiation is significantly lower than for large coils that can be fabricated on the PCB side of the system. By definition, a radiating antenna becomes electrically small when the area of the entire antenna fits inside a sphere of radius  $a = \lambda/(2\pi)$  [59–63]. The effects of this electrical smallness can be observed in figure 2.3, where the energy radiated by the TX and absorbed by the RX is great when the PCB side is transmitting and the implant side is absorbing (2.3a), and the energy absorbed by the RX is very small when the implant side is the radiator (2.3b).

For power transmission, the implant is simply a passive receiver, so the concept of electrical smallness is not a problem since it will never actually transmit power at 27MHz, the power transfer efficiency just takes a hit since the coils cannot be perfectly matched. For data transmission, however, this presents a challenge which greatly limits the effective range for data transmission. Also, since we are only able to use passive modulation to save power in the implant design, the data coil's backscattered matching is what is measured for the data uplink, meaning we are taking the hit for RF losses from the TX/RX separation twice. To change the backscattered matching we shift the load impedance that is attached in parallel to the inductive coil which modifies the resonance frequency of the data receiver coil. Since we are shifting the load of the coil, we call this type of modulation load shift keying (LSK). An example design from ADS where the resonance frequency of a receiver is shifting from being in tune with the RX at close to 800 MHz (curves in black) to being completely out of tune at < 200 MHz (curves in blue) is depicted in figure 2.4. Without LSK enabled, the amount of power supplied by the TX side is actually effectively modulated to two separate binary states on the receiver side in terms of output power.

(a) EM Current Distribution with PCB side (b) EM Current Distribution with IC side transmission transmission

Figure 2.3: IC side vs PCB side RF transmission

Figure 2.4: RX Power, TX Power, and TX/RX Efficiency with LSK modulation

For physical inductor size of the on-chip coils, the coil outer diameter was limited by the size limit of the implant while still being usable in the brain of a small mouse. Total implant volume was targeted to be less than  $0.1mm^3$ , which for assumed  $20\mu m$ thickness, allowing for a total chip surface area of  $5mm^2$ . Budgeting 80% of surface area for the near-field inductors, yielded an outer radius of 2mm by 2mm for the power coil. For the near-field link being designed, we show in figure 2.5 that the amount of coupling between TX and RX increases with turn count as a function of  $N_2$  where N is the number of turns in a loop inductor. Increasing the number of turns, however, also has the downside of increasing the resistive losses as a function of N, which at some point will both create too much heat loss and diminish the radiation efficiency of the coil. For our system, the optimal turn count was iteratively determined to be 5 for the power coil and 7 for the data coil.

For the cross sectional area of the antennas, the goal was to maximize the quality factor of the coils. The Q of the inductors is directly proportional to the coil inductance, and inversely proportional to the resistance per unit length of the coil. Therefore a maximal Q-factor will occur when the width, and height of the inductor is maximized, while the separation between loops is minimized, which increases L and decreases R. Unfortunately in integrated coils, the height is a set-value by the chosen technology (4 $\mu$ m in 180nm SOI), and the minimum separation between metal shapes increases as wire width increases. For example, fabrication limitations limited metal trace widths to 50 $\mu$ m, as long as spacing between traces exceeded 30 $\mu$ m. If trace

Figure 2.5: Coupling coefficient for power coils vs transceiver radius

widths were limited to  $20\mu m$ , spacing could be reduced to  $10\mu m$ , adding a series of non-allowed ratios between draw-length, trace width, and trace spacing for iterative simulation using an electromagnetic method of moments solver.

Taking these manufacturability limitations in mind, iterative analysis for the peak possible Q in the power coil showed peak PTE with an optimal trace width greater than  $50\mu m$  with separation less than  $30\mu m$ , so the DRC limits were chosen as the power coil inductor parameters. For the data coil, the design process differed slightly, as the goal was not to maximize power transfer efficiency, but voltage coupling between the coils. Theory shows that a peak in coupling occurs at so by decreasing trace thickness and spacing to maximize draw length and Q-factor, with less importance placed on reducing resistive losses, the goal was able to reach a self-resonance frequency in the desired band of 600MHz - 800MHz.

## 2.2.1 Power Systems Circuitry

With inductor parameters, and thus usable scattering parameters for an importable cadence model available, the next step was to design power harvesting circuitry to

convert the . For implantable devices, both passive and active rectifier circuit topologies have been created, with strengths and weakness of both designs [64–68]. For this implant, a passive voltage rectifier based on a voltage quadrupler circuit was implemented. The voltage qaudrupler topology used is depicted in figure 2.6 in the left most block. For this design the transistors  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  are all simply acting as diode connected FETs which only allow current to flow in one direction at the cost of a turn on voltage. When the AC input across the voltage quadrupler exceeds the diode-connected-FET threshold voltage, the system acts as a charge pump in both the positive and negative AC phases, effectively rectifying two times the positive AC input voltage at the output of  $M_2$  and two times the negative AC voltage amplitude at the output of  $M_4$ . Setting the negative voltage to be the ground reference of the chip, and adjusting the magnitude of the input power signal to create 900mV on both the positive and negative phases, we yield a 1.8V DC voltage at the rectifier output. In order to reduce the 27MHz ripple on this rectified voltage, the value of the differential capacitors at the output of the passive rectifier are made large enough to limit DC ripple to less than 150mV, allowing 150mV of overhead for the regulator of the chip to create a steady 1.5V DC rail which is the suggested operating voltage for optimal performance of the 180nm SOI technology. The efficiency of this passive rectifier was simulated to be between 60to65%, or an overall insertion loss from antenna to available power of approximately -4dB.

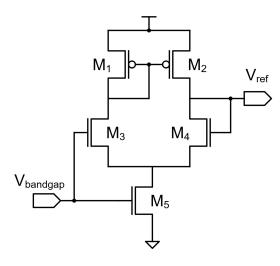

To create the regulated 1.5V rail for the remaining chip circuitry, a low dropout regulator (LDO) was implemented with circuit topology depicted in the center of figure 2.6. A telescopic op-amp is driven by a bandgap reference set to 750mV in a non-converting gain configuration with a gain of 2. A large PFET,  $M_1$  is placed at the output of this op-amp which acts as a current source for the regulated DC output. As long as the current average drawn by the chip never exceeds the RMS current in the power receiver coil, the LDO will be able to properly regulate. A function of the

Figure 2.6: System Block for Rectification, Regulation, and RF Protection Circuitry power supply rejection ratio, PSRR, of the designed LDO is depicted in figure 2.7. Monte Carlo simulations for the PSRR show a minimum of 36dB at 50MHz, which is twice the expected operating bandwidth of all signals on chip outside of the data receiver carrier frequency.

Figure 2.7: PSRR of LDO block

The final block in the power systems circuitry is the RF Limiter. The FETs used in all subsystems outside of the rectifier and regulator blocks have a strict operating voltage limit of 1.65V before permanent damage is done to the transistors. The

bandgap reference in the LDO block, which is powered by the rectifier output, will exceed 0.8V in the rectifier output exceeds 1.95V, which will create a regulated LDO output that exceeds safe operating voltages for the internal circuitry. To protect the system from this, an RF limiter circuit was added in parallel to the voltage rectifier output as depicted in the rightmost circuit block of figure 2.6. In this block, a voltage sensing circuit composed of the series stack of a resistor,  $M_1$ , and  $M_2$  generate a current called  $I_{sense}$ . When  $I_{sense}$  is small,  $M_3$  is in cutoff and does not draw current, causing the voltage at the source to drop to zero, leaving  $M_4$  also in cutoff. As the voltage output of the rectifier approaches 1.9V, the current  $I_{sense}$  increases, creating a cascading effect of turning on  $M_3$ , which turns on  $M_4$  creating a current shunt at the output of the voltage rectifier. This causes any excess RF energy being converted into DC power to be shunted to the implants ground reference. The RF limiter will only function up an input power level of 21.mW, however, by the time this limit is reached, the transistors in the rectification system will have already exceeded safe operating voltages and have already ceased to function. The RF limiter's primary function is to protect against unexpected rises in the transmitted power from the reader that might occur when programming the output power of the external transceiver.

# 2.3 Data Modulation Circuitry

In order to limit power usage and stay under SAR limits, the data modulation topologies for both uplink and downlink were chosen to be as low power as possible and passive in terms of modulation technique. For downlink, ASK modulation was chosen and for uplink, passive backscattering LSK modulation was chosen.

When powered on, the implant starts in a "blinking configuration" state. Since LSK transmission effectively shunts the received carrier signal to the no-amplitude condition to modulate a zero, only data uplink or downlink can occur at any given time. While in the blinking state, the implant alternates between transmitting the chip's current configuration settings for eight downlink cycles and listening for an ASK response. While listening, the LSK modulation circuitry is disabled. The external data Tx tracks this blinking state and sends the configuration word in the listening phase. If one of 16 valid words (which act as input configuration gain for the biological interface circuitry) is received, the implant enters the data transmit state where it continuously sends digitized data. At this point the ASK demodulation circuitry is disabled to both save power, and to prevent the chip's configuration from changing during sampling. In order to reset the system and transmit a new input code, the system must be fully powered off by either disabling the power transmission signal, or by moving the implant out of both power and data range. Since the power transmission operation range is approximately 3-5 times longer in radius than the data link, the suggested method is to turn off the power signal. This will also have the bonus effect of preventing a false programming condition, that will be highlighted when discussing the modulation circuitry in detail. The waveform with the LSK enable and disabled on the chip-side is depicted in figure 2.8.

## 2.3.1 Clock Recovery

For higher power wireless systems, a local oscillator is typically used to create an on-chip clock signal. While the advantages of this include on-chip tunability of the clock signal, it comes at the heavy cost of requiring some type of phase-locked-loop (PLL) or delay-locked-loop (DLL) which can sync to the external system, adding high complexity and power requirements to the system [66, 69–71]. In this passive system, the power budget is limited to only 2.7mW for all of the transceiver circuitry, not allowing this circuitry overhead for an on-chip oscillation system.

The clock recovery circuitry used on the chip is depicted in figure 2.9. The positive

Figure 2.8: LSK Waveform on the Chip's Data Receiver

terminal of the power coil is connected to the input of the block which is AC coupled using a blocking MIM capacitor. This captures only the AC signal of the power coil, and ignores the DC value that has been set to the power coil in steady-state operation. This is then fed into an inverter that has a feedback resistance, which at no AC-input will cause both the input and output of the inverter to be set to Vdd/2, which for this technology is approximately 750 mV. The inverter then simply acts as a highly non-linear amplifier, amplifying the AC input from sinusoidal into a square wave with a switching time window close to the inverter time constant  $\tau_{inv}$  which is approximately 50*ps* for the 180*nm* SOI process. To reduce glitching, this square waveform is fanned out to Schmitt triggers which distribute the recovered 27*MHz* clock to the control blocks of the chip. To prevent uneven loading on the positive and negative terminals of the power inductor, an unpowered replica of the MIM capacitor and inverter with resistive feedback is place on the negative terminal with closely matched wire lengths.

Figure 2.9: Clock Generator Circuitry

#### 2.3.2 Data Modulation and Demodulation Circuitry

For data recovery, since the external reader is creating the power signal with a COTS PLL, the IC's clock frequency can be assumed to match the sent power signal, thus effectively phase-locking the on-chip clock to the external reader clock without the use of an on-chip PLL. For the passive LSK backscattering modulation, the circuit topology used can be seen in figure 2.10. For this block, the differential AC signal on the data receiver coil,  $RX_D$  is matched using a small MIM Capacitor,  $C_{match}$ , giving the parallel LC circuit a resonance frequency of:

$$\omega_o = \sqrt{L_{RX_{Data}} C_{match}} \tag{2.1}$$

Depending upon process corner, and the remaining bulk capacitance after thinning the silicon, this value is designed to range from 650 - 750MHz. A second larger detuning capacitor,  $C_{mod}$  can be added in parallel to  $C_{mod}$ . The desired modulated data decision LSK is used to open and close pass gates, effectively changing the resonance frequency to:

$$\omega'_{o} = \sqrt{L_{RX_{Data}}(C_{match} + C_{mod})} \tag{2.2}$$

Where the value of  $C_{mod}$  is large enough to reduce the resonance frequency to far below 150Mhz, which effectively shunts the received 700Mhz carrier signal to 0V. The circuit topology for the ASK demodulation and LSK modulation systems are depicted in 2.10.

Figure 2.10: ASK Demodulation and LSK Modulation Circuitry

For the LSK circuitry,  $C_{match}$  and  $C_{mod}$  are implemented via 400 fF and 10,000 fFMIM capacitors, and the pass gates are implemented with  $10\mu m$  width complementary gates. For the ASK circuitry (depicted on the left in figure 2.10), an envelope detector is implemented using the triode connected PFET  $M_1$  and MoM capacitor  $C_{smooth}$ . This envelope level is compared to a bias voltage  $V_{ref}$  which will trigger an ASK value of 1 when the LSK level drops below the reference threshold. Since the time constant of this envelope detector is quite long, a shunting NFET biased by  $V_{b1}$  is placed in parallel to the envelope voltage that will attempt to pull down the envelope voltage quickly, allowing for a very fast reaction to a shift in data carrier amplitude during ASK transmission. This shunting FET also serves a secondary purpose after programming, as the bias voltage is increase to always transmit a value '0' in the ASK, preventing accidental reprogramming during data uplink. Since the ASK detection occurs when the envelope drops below a threshold, it is also important that the data carrier frequency be switched on before the power carrier is turned on to prevent a false programming of '1111'. Since this state is the most likely accidental programming state, the '1111' state is also designed to be the minimum gain setting and most stable setting for the neural amplifier system.

The impedance load caused by the LSK circuitry and ASK demodulation system at 700*MHz* can be modeled by a parallel RC circuit with C = 430 fF and  $R = 4.3k\Omega$ with the LSK disabled, and C = 10.6pF and  $R = 106k\Omega$  with the LSK enabled. To maintain equal loading the positive and negative terminals, an unpowered replica of the ASK Demodulator is placed on the negative terminal of the data coil.

# 2.4 Neural Interface Circuitry and Post Processing

The neural interface system is implemented with a multi-stage amplifier with time multiplexing and an 8 bit successive approximation register (SAR) ADC. A system level circuit block for the neural system is depicted in figure 2.11.

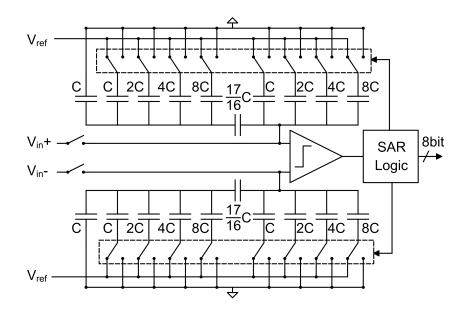

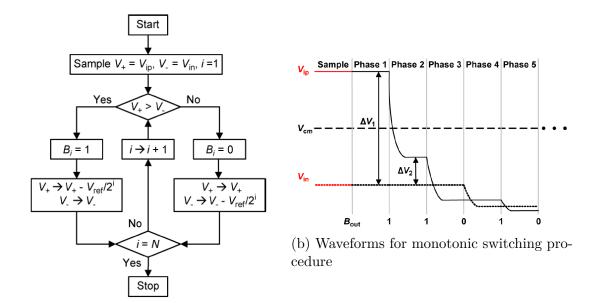

### 2.4.1 SAR ADC

To digitize analog input signals on the shank, an 8-bit successive-approximationregister (SAR) ADC was designed. The SAR-ADC has an asynchronous controller, providing all 8-bits in parallel in a single clock cycle. In order for the SAR data rate to match the 27MHz clock frequency, the SAR's clock was divided down by 8 for a

Figure 2.11: Neural Interface Circuitry and ADC System Block

designed sample rate of 3.375MS/s. The ADC runs continuously, with the previous 8-bit decision from the last clock cycle stored in a register block that is forwarded to the LSK modulator. The capacitor array for the ADC was designed using MIM capacitors, with a unit capacitance of 33fF. In order to greatly decrease the overall capacitance of the capacitor array, a split-capacitor array was implemented with separate capacitor arrays for the upper and lower nibbles. The system block level schematic for the design SAR ADC is depicted in figure 2.12. The total capacitance in the array that needs to be driven is 2.11pF, which without the split-capacitor array would be 16.83pF, meaning the use of 2 4-bit nibbles in the split capacitor array reduce the required capacitance in the SAR by 87.4%. The asynchronous block arrives at the full 8-bit binary decision in under 50ns, meaning the SAR could properly function at up to 20MS/s if required.

The comparator for the ADC was implemented using a standard strong-arm topology and the input switches were implemented using large CMOS pass gates, which are capable of driving the input well before the 3.375MHz switching time. The reference

Figure 2.12: SAR ADC System Block Diagram with asynchronous controller

voltage was generated using a bandgap reference and was designed to give a reference voltage of 800mV, giving the whole switching procedure a difference dynamic range of 1.6V. The capacitor array is reset to VDD/2 which is 750mV before each sample period. This means that the SAR can operate accurately for input voltages ranging from 350mV to 1150mV. The switching logic was designed to follow the asynchronous monotonic switching algorithm as highlighted by Liu, et al. [72]. The flow chart and waveforms for the logic block for the monotonic switching procedure is highlighted in figure 2.13. As the decision logic moves from MSB to LSB, the effective DC average for  $V_{in}$  approaches 350mV. The strong-arm comparator is driven with a PFET based differential input, meaning the strength of the comparison becomes stronger as the required voltage precision increases in the lower LSBs. Virtuoso simulations for the comparator block show functionality for differences as small as 540nV.

(a) Logic flow chart for Monotonic SAR

Figure 2.13: Monotonic Switching Controller

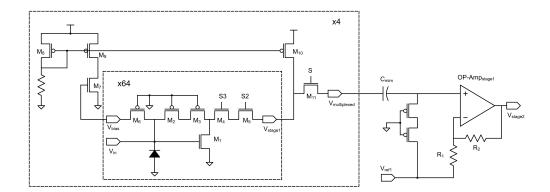

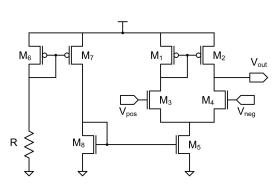

## 2.4.2 Neural Amplification System

The neural amplification system can be summarized as a time-multiplexed 3-stage amplifier chain, with the load on the third stage being the 2.1pF differential capacitor array from the SAR ADC. The first stage of the amplifier has 256 copies, with an amplifier present under each site along the shank. Of these 256 electrode sites, 255 correspond to active amplifier inputs, with the 256th connected to the chip's ground as a reference. Circuit schematics for the first two stages of the amplifier chain are depicted in fig 2.14.

In the shank, there are 4 blocks of 64 amplifier stages, each connected to their own large bias generators that both supply current for the amplifier, and supply bias voltages for the gate input at the elctrode interface. Each electrode site (referred to as pixels) has a common source amplifier implemented directly under the  $20\mu m$  by  $20\mu m$ top metal square on the shank with the glass-cut opening to the surface sized at  $14\mu m$ by  $14\mu m$ . To protect the gate of this amplifier from any ESD effects, an ESD diode

Figure 2.14: 2 Stages of Neural Amplifier System

is placed in parallel to the gate input to the chip's ground. While this is not the full recommended ESD protection circuitry for 180nm SOI, which also requires a second reverse biased ESD diode to the voltage rail, it is sufficient to prevent massive yield problems in the pixel amplifiers. To select a given pixel on the shank, digital inputs  $S_2$  and  $S_3$  are used to turn on transistors  $M_4$  and  $M_5$ . The DC bias voltage at  $V_{on}$  is set by the current mirror formed  $M_7$ ,  $M_8$ ,  $M_9$ , and R.  $M_6$  acts as a large resistance to provide an AC block and a DC feed through path for the current mirror. There are 4 copies of the current mirror on the base on the shank, and each one sets the DC value of 64 sites. Transistors  $M_2$  and  $M_3$  function as deep triode devices to maintain the DC value at the drain of  $M_1$  when a site is not being sampled, which greatly decreases the power-on time when a given pixel is selected. At a given time, 4 pixels are selected and powered, 1 from each quadrant. A single pixel is output to the next stage of the amplifier,  $Op - Amp_{stage1}$ , with the selected quadrant chose by sending a digital '1' to S to close  $M_{11}$ . Each powered quadrant draws approximately  $50\mu W$ , meaning the total shank power drawn is limited to  $200\mu W$ . The mean simulated gain for the common source stage when a pixel is selected is 20dB for a bandwidth of 10Hz to 1MHz. Since the circuit is sampled at 12.9KHz, this bandwidth is aliased down into the 10-6.5kHz band. The circuit topology for the amplifier  $Op - Amp_{stage1}$ is depicted in 2.16b. It is a simple telescopic five transistor amplifier with a current

mirror that provides a gain of 23dB in closed loop for the resistance values  $R_1$  and  $R_2$  over the necessary bandwidth necessary bandwidth.

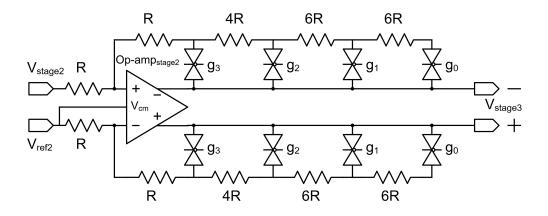

Figure 2.15: Tunable 3rd Stage of Amplifier System

The final stage of the neural amplification system is depicted in figure 2.15. This amplifier stage singled ended to differential and is tunable by opening and closing the pass gates  $g_3$  through  $g_0$  which are set by the ASK configuration on start-up. The unit resistance value of R for this design was  $25k\Omega$ , making valid tunable gains from this stage to be 0dB, 14dB, 21dB, and 24dB respectively. The input code  $g_3g_2g_1g_0$ is a one-hot design, and the gain value will take the value of the left most binary '1' input code. This means the programmed gain codes are 0dB for gain codes 8 through 15, 14dB for codes 4 though 7, 21dB for codes 2 and 3, 24dB for code 1, and code 0 is invalid, leaving the amplifier in open-loop. The circuit topology for  $op - amp_{stage2}$ is depicted in figure 2.16c. This topology also uses a 5 transistor telescopic base, but also uses common mode feedback to set the common-mode voltage to 750mV at both the input and output. The output common mode is of heightened importance since it will be driving the DC average sent to the SAR ADC at every clock cycle.

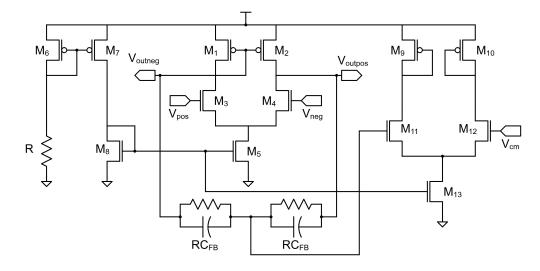

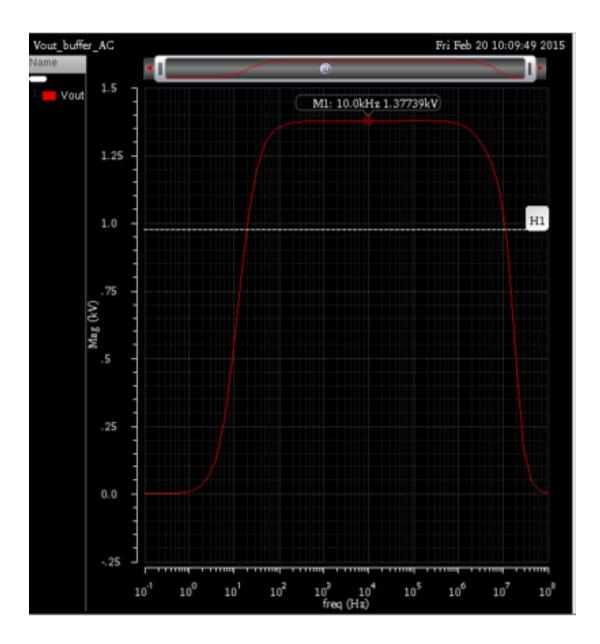

The DC-steady state gain for the full amplifier chain is depicted for a bandwidth of 10Hz to 1MHz, and shows a peak voltage gain of 1377 or 62.7dB. The integrated input referred noise of the amplifier without multiplexed switching was found to be  $4.2\mu V$

(b) Stage 1 Op-amp Circuitry

(a) Topology for Reference Generator Amplifiers

(c) Stage 2 Op-amp Circuitry

Figure 2.16: Operation Amplifier Circuit Topologies

over the 10Hz-1MHz bandwidth. The sampling frequency of the multiplexing will fold noise contributions between 6.5kHz and 1MHz into the amplifier output, and this will be reflected in a higher recorded noise value. The recommended time-multiplexing ratio to limit noise folding for neural recording systems was recommended to be 20 by Raducanu et. al [73], however our system oversamples at a rate of 64:1, leading to poor noise performance in measurement.

Figure 2.17: Gain Performance of Amplifier Chain

# 2.4.3 Chip Thinning

Thinning of passive implantable medical devices has been documented with shank cross sections on the order of 10s of  $\mu ms$  [74–76]. In our system, we perform thinning

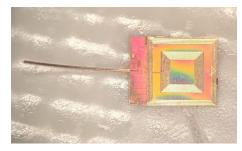

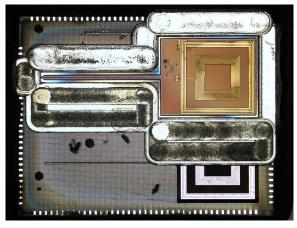

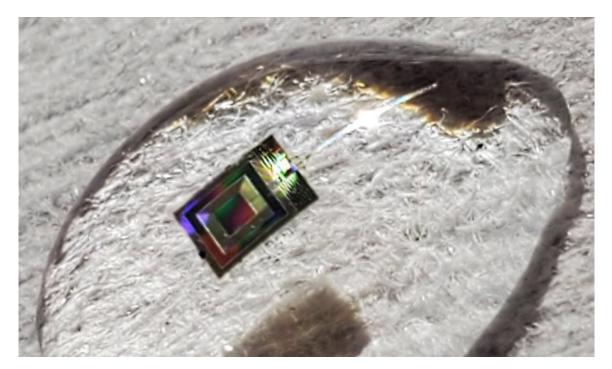

on after silicon electrodes after receipt from the foundry, when the probe is postprocessed to thin the chip. The chip is implemented on SOI such that removal of the p-type silicon substrate has minimal effects on the bodies of the active transistors, since a blocking silicon dioxide box layer isolates the active silicon base connection from the substrate. While this comes at the cost of the circuits being vulnerable to the floating body effect, it causes chip performance and transceiver operation to be indistinguishable pre and post thinning. The passivation, dielectric of the back-end stack, and silicon substrate are trenched by successive dry etching, separating the probe from the rest of the die. The final shank is 3.2mm-long and 130µm-wide with a tapered tip. The thickness of the whole device is approximately  $20\mu m$ , yielded an overall implant volume of  $0.08mm^3$ . The trenching process can be seen in figure 2.19. First mask layers are used to etch down the metal exclude areas surrounding the perimeter of the die (2.19a), the sounding portions of the chip are then mechanically grinded down (2.19b), and finally the bulk silicon is thinned from behind until the now trenched chip is cleaved from the remaining portions of the die (2.19c). An implant post-thinning is depicted in figure 2.18a and a fully processed shank is depicted in figure 2.18b. At this thinned, the shank is flexible as is apparent in the visible curvature of the thinned die and the thinned shank. To combat this and prevent the shank from rolling to the point of damage, the chip is temporarily glued to a stiff silicon guide shank.

As can be seen in the picture, the die is now flexible, to the point that the shank is naturally curving upward. At this thickness, the probe is extremely brittle, requiring attachment to a thicker guide shank system.

(a) Post Thinning

(b) Post Shank Formation

Figure 2.18: IC post thinning and shank formation

(a) IC surface post chemical etch of trench

(b) IC post mechanical grinding

(c) IC fully detached from substrate

Figure 2.19: IC Shank Formation Procedure

# Chapter 3

# Design of External Reader System

The external reader system can be divided into three major sections: 1) The physical PCB trace transmitter design using electromagnetic simulations 2) The boards designed to create the power transmission signal and reconstruct and transmit the data signals 3) The verilog based reconstruction and equalization instantiation via FPGA

The system block diagram for these three systems are depicted in figure 3.1, and the physical boards can be seen in figure 3.2. The necessity for these systems come from the ISI challenges introduced by the high-data-rate backscattering through lossy media present for uplink data recovery using an integrated coil. The thickest metal layer available on the implant is limited to  $4\mu m$  in  $0.18\mu m$  SOI, giving the integrated coils low quality (Q) factors from small trace cross sectional area. Low Q decreases greatly radiation efficiency, causing the received power signal to have extremely poor PTE and the data LSK signal to be >60dB lower than the transmitted 700MHz carrier. To overcome this, equalization techniques must be employed to process the LSK data and achieve acceptable BERs, and highly tunable power amplifiers must be implemented on the transmitter boards to achieve reliable powering.

# 3.1 PCB Coil Design