Copyright by Haishan Zhu 2018 The Dissertation Committee for Haishan Zhu certifies that this is the approved version of the following dissertation:

# QoS-Aware Mechanisms for Improving Cost-Efficiency of Datacenters

Committee:

Mattan Erez, Supervisor

Jichuan Chang

Keshav Pingali

Gustavo de Veciana

Mohit Tiwari

# QoS-Aware Mechanisms for Improving Cost-Efficiency of Datacenters

by

Haishan Zhu

## DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

May 2018

Dedicated to my wife, Cathy Chen and my parents, Zhiliang Zhu and Meifang Cui

## Acknowledgments

First and foremost I want to thank my adviser Mattan Erez. This dissertation would not have been possible without his mentorship throughout my PhD career. He provided the much needed rigorous and incisive technical critiques on each and every piece of my work. His wide research interests and fruitful work have also inspired me to keep expanding my knowledge and sharpening my skills. Perhaps more importantly, Mattan gave me the precious intellectual freedom to pursue projects that I am interested in, to take inevitable detours in research work, and to learn from those experiences. When I encountered challenges and obstacles in numerous occasions, Mattan has always provided me with patient guidance and selfless support. I am deeply grateful to have him as my adviser and I am certain that I will continue to be inspired by his teaching even beyond research work.

I am also privileged to have collaborated with many outstanding computer architects at Google Platform Team. I would like to especially thank Jichuan Chang, David Lo, Liqun Cheng, Rama Govindaraju, and Parthasarathy Ranganathan for working with me for two consecutive summers on challenging and impactful projects. Thanks to their knowledge, experience, and resourcefulness, I was able to grow out of an inexperienced graduate student and gain insights in the state-of-art datacenter architectures. My collaboration with them also played a fundamental role to the constitution of this dissertation.

I would like to give special thanks to my mentors and professors at Michigan: Jason Clemons, Todd Austin, Mark Brehob, Peter Chen, and Thomas Wenisch. While I only spent two years there, I learned a lot about computer architecture from either taking their classes or working on research projects with them. Their diligent teaching and research work led me to continue to explore this field in graduate school.

I am glad to get to know many other graduate students during my PhD. I want to thank Yuhao Zhu, Jingwen Leng, Jungrae Kim, and Minsoo Rhu for selflessly sharing their experience and knowledge with me and inspiring me to keep improving my work. I was also fortunate to receive much academic and career advice from Ikhwan Lee, Milad Hashemi, Min Kyu Jeong, Doe Hyun Yoon, and Dan Zhang. I also thank all the other members of our research group: Jinsuk Chung, Mike Sullivan, Song Zhang, Dong Wan Kim, Seong-Lyong Gong, Tianhao Zheng, Derong Liu, Kyushick Lee, Nick Kelly, Esha Choukse, Benjamin Cho, Sangkug Lym, Yongkee Kwon, Chun-Kai Chang, Majid Jalili, and Wenqi Yin. And I am grateful for the friendship with many others: Hao Xin, Rohit Pandey, Andrea Lottarini, Junwhan Ahn, Grant Ayers, Yuhuan Du, Zhuoran Zhao, Siavash Kamali, Ben Lin, Stephen Pruett, Ali Fakhrzadehgan, and Matt Halpern. It has been much fun discussing work, drinking coffee, having pizza, and occasionally slacking off together.

Last but not the least, I can never overstate how much I appreciate my family. I am grateful to have my incredible wife Cathy Chen with me through all the adventures and endeavors during graduate school. Her love and caring made it easy for me to keep my eyes on the target. I deeply thank my parents, Zhiliang Zhu and Meifang Cui, for their unconditional love and support while I pursue my goals thousands of miles away from them. My love for my family is what gives meaning to working on this dissertation and pushing through all the obstacles.

Haishan Zhu February 2018, Austin, TX

# QoS-Aware Mechanisms for Improving Cost-Efficiency of Datacenters

Publication No. \_\_\_\_\_

Haishan Zhu, Ph.D. The University of Texas at Austin, 2018

Supervisor: Mattan Erez

Warehouse Scale Computers (WSCs) promise high cost-efficiency by amortizing power, cooling, and management overheads. WSCs today host a large variety of jobs with two broad performance requirements categories: latencycritical (LC) and best-effort (BE). Ideally, to fully utilize all hardware resources, WSC operators can simply fill all the nodes with computing jobs. Unfortunately, because colocated jobs contend for shared resources, systems with high loads often experience performance degradation, which negatively impacts the Quality of Service (QoS) for LC jobs. In fact, service providers usually over-provision resources to avoid any interference with LC jobs, leading to significant resource inefficiencies. In this dissertation, I explore opportunities across different system-abstraction layers to improve the cost-efficiency of dataceters by increasing resource utilization of WSCs with little or no impact on the performance of LC jobs. The dissertation has three main components. First, I explore opportunities to improve the throughput of multicore systems by reducing the performance variation of LC jobs. The main insight is that by reshaping the latency distribution curve, performance headroom of LC jobs can be effectively converted to improved BE throughput. I develop, implement, and evaluate a runtime system that achieves this goal with existing hardware. I leverage the cache partitioning, per-core frequency scaling, and thread masking of server processors. Evaluation results show the proposed solution enables 30% higher system throughput compared to solutions proposed in prior works while maintaining at least as good QoS for LC jobs.

Second, I study resource contention in near-future heterogeneous memory architectures (HMA). This study is motivated by recent developments in non-volatile memory (NVM) technologies, which enable higher storage density at the cost of same performance. To understand the performance and QoS impact of HMAs, I design and implement a performance emulator in the Linux kernel that runs unmodified workloads with high accuracy, low overhead, and complete transparency. I further propose and evaluate multiple data and resource management QoS mechanisms, such as locality-aware page admission, occupancy management, and write buffer jailing.

Third, I focus on accelerated machine learning (ML) systems. By profiling the performance of production workloads and accelerators, I show that accelerated ML tasks are highly sensitive to main memory interference due to fine-grained interaction between CPU and accelerator tasks. As a result, memory resource contention can significantly decreases the performance and efficiency gains of accelerators. I propose a runtime system that leverages existing hardware capabilities and show 17% higher system efficiency compared to previous approaches. This study further exposes opportunities for future processor architectures.

# Table of Contents

| Ackno   | wledg  | ments                                                 | $\mathbf{v}$ |

|---------|--------|-------------------------------------------------------|--------------|

| Abstra  | ict    |                                                       | viii         |

| List of | Table  | 25                                                    | xiv          |

| List of | Figur  | res                                                   | xv           |

| Chapte  | er 1.  | Introduction                                          | 1            |

| 1.1     | Warel  | house Scale Computers and Workloads                   | 2            |

| 1.2     | WSC    | Workload Management                                   | 3            |

| 1.3     | Perfor | rmance Interference and Utilization Bottleneck        | 5            |

| 1.4     | WSC    | Workload Statistical Behavior                         | 6            |

| 1.5     | Thesis | s Statement                                           | 7            |

| 1.6     | Contr  | ibutions                                              | 7            |

| 1.7     | Disser | tation Organization                                   | 10           |

| Chapte  | er 2.  | Improving QoS and Utilization<br>on Multicore Sysmtes | 11           |

| 2.1     | Backg  | ground                                                | 12           |

|         | 2.1.1  | Target Workloads and Metrics                          | 12           |

|         | 2.1.2  | Contention Control Mechanisms                         | 13           |

| 2.2     | Dirige | ent Principles                                        | 14           |

| 2.3     | Dirige | ent Design and Implementation                         | 17           |

|         | 2.3.1  | Offline Execution Profiler                            | 18           |

|         | 2.3.2  | Execution Time Predictor                              | 19           |

|         | 2.3.3  | Performance Controller                                | 22           |

| 2.4     | Evalu  | ation                                                 | 27           |

|         | 2.4.1  | Workloads and Evaluation Infrastructure               | 28           |

|       | 2.4.2  | Predictor Accuracy                                                         | 32 |

|-------|--------|----------------------------------------------------------------------------|----|

|       | 2.4.3  | Coarse Time Scale QoS Control                                              | 33 |

|       | 2.4.4  | Dirigent Performance                                                       | 34 |

|       | 2.4.5  | LC Throughput and BE Performance Tradeoffs $\ . \ . \ .$                   | 42 |

| 2.5   | Relate | ed Work                                                                    | 43 |

| 2.6   | Summ   | nary                                                                       | 45 |

| Chapt | er 3.  | Mitigating Performance and QoS Impact of NVM<br>on Datacenter Applications | 48 |

| 3.1   | Backg  | ground                                                                     | 49 |

|       | 3.1.1  | Target Workloads                                                           | 49 |

|       | 3.1.2  | Workload Characteristics                                                   | 49 |

| 3.2   | Targe  | t Architecture                                                             | 51 |

|       | 3.2.1  | Baseline Page Placement and Migration                                      | 52 |

|       | 3.2.2  | DRAM Admission Control                                                     | 55 |

|       | 3.2.3  | DRAM Occupancy Control                                                     | 58 |

|       | 3.2.4  | Write Bandwidth Metering                                                   | 59 |

| 3.3   | ONSi   | m                                                                          | 60 |

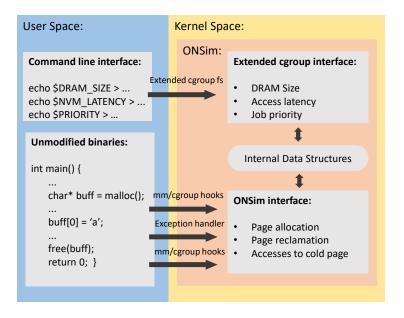

|       | 3.3.1  | Simulator Architecture                                                     | 62 |

|       | 3.3.2  | Performance and Architecture Modeling                                      | 65 |

|       | 3.3.3  | ONSim Accuracy and Overheads                                               | 66 |

| 3.4   | Evalu  | ation                                                                      | 71 |

|       | 3.4.1  | Methodology                                                                | 71 |

|       | 3.4.2  | Standalone Execution                                                       | 74 |

|       | 3.4.3  | Colocation Scenarios                                                       | 77 |

| 3.5   | Relate | ed Work                                                                    | 83 |

|       | 3.5.1  | Heterogeneous Memory Architectures                                         | 83 |

|       | 3.5.2  | Cache Replacement Policies                                                 | 85 |

|       | 3.5.3  | HMA Performance Simulation                                                 | 85 |

| 3.6   | Summ   | nary                                                                       | 87 |

| Chapte  | er 4.  | Enforcing QoS for Accelerated Machine Systems                                                   | Learning  | 88           |

|---------|--------|-------------------------------------------------------------------------------------------------|-----------|--------------|

| 4.1     | Backg  | round                                                                                           |           | 89           |

|         | 4.1.1  | Target Accelerator Use Case                                                                     |           | 89           |

|         | 4.1.2  | Accelerator-CPU Interaction                                                                     |           | 90           |

|         | 4.1.3  | Managing Interference at WSC Scale                                                              |           | 94           |

| 4.2     | Accel  | erated Machine Learning Workloads                                                               |           | 95           |

|         | 4.2.1  | Platforms and Workloads $\ . \ . \ . \ . \ . \ .$ .                                             |           | 95           |

|         | 4.2.2  | Interference Sensitivity                                                                        |           | 96           |

| 4.3     | Kelp I | Design and Implementation                                                                       |           | 98           |

|         | 4.3.1  | NUMA Subdomain Performance Isolation $~$                                                        |           | 99           |

|         | 4.3.2  | Shared Memory Backpressure                                                                      |           | 100          |

|         | 4.3.3  | Improving System Throughput                                                                     |           | 103          |

|         | 4.3.4  | Kelp Workflow and Implementation $\ . \ . \ .$ .                                                |           | 104          |

| 4.4     | Evalu  | ation $\ldots$ | • • • • • | 106          |

|         | 4.4.1  | Methodology $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                               |           | 106          |

|         | 4.4.2  | Benchmark Case Studies                                                                          | ••••      | 109          |

|         | 4.4.3  | Overall Results                                                                                 | ••••      | 115          |

| 4.5     | CPU    | Design Challenges and Opportunities                                                             | ••••      | 116          |

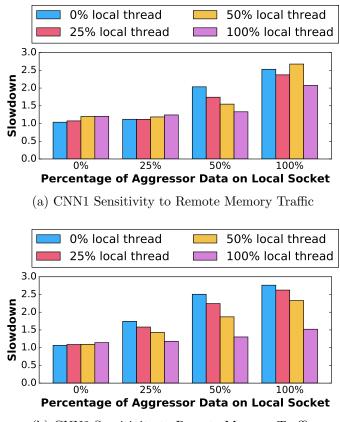

|         | 4.5.1  | Remote Memory Interference $\ldots \ldots \ldots \ldots$                                        | ••••      | 117          |

|         | 4.5.2  | QoS-Aware Prefetching                                                                           | ••••      | 118          |

|         | 4.5.3  | Global Memory BW Backpressure $\ . \ . \ . \ .$                                                 | ••••      | 120          |

|         | 4.5.4  | Fine-Grained Memory Isolation                                                                   | ••••      | 120          |

| 4.6     | Relate | ed Work                                                                                         | ••••      | 122          |

|         | 4.6.1  | Wide Adoption of Accelerators $\ldots \ldots \ldots$                                            | ••••      | 122          |

|         | 4.6.2  | Accelerator QoS and Utilization $\ldots \ldots \ldots$                                          | ••••      | 123          |

|         | 4.6.3  | System Performance Isolation                                                                    | ••••      | 124          |

| 4.7     | Summ   | nary                                                                                            |           | 126          |

| Chapte  | er 5.  | Conclusion                                                                                      | 1         | L <b>2</b> 8 |

| Bibliog | raphy  | 7                                                                                               | 1         | 132          |

| Vita    |        |                                                                                                 | 1         | 64           |

# List of Tables

| 2.1 | LC and BE Benchmarks                                        | 27 |

|-----|-------------------------------------------------------------|----|

| 3.1 | Default workload generator configuration                    | 71 |

| 3.2 | Default simulation parameters                               | 71 |

| 3.3 | Best-Effort Tasks Used in This Study                        | 73 |

| 4.1 | Accelerated ML platforms and production workloads. Detailed |    |

4.1 Accelerated ML platforms and production workloads. Detailed measurements are not publishable due to confidentiality concerns. 95

# List of Figures

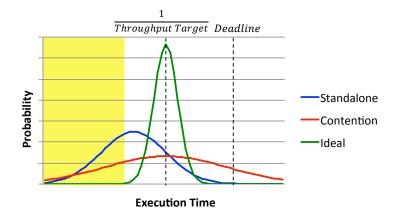

| 2.1  | Example LC completion time probability density functions when<br>run alone, under contention, and in an ideal scenario; the shaded<br>region points to underutilized resources when run alone                                                                                                                            | 16 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Reservation-based scheduler efficiency with two different task types: type A with high execution time variance and type B with low variance.                                                                                                                                                                             | 17 |

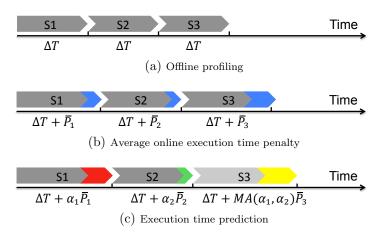

| 2.3  | Execution time predictor example.                                                                                                                                                                                                                                                                                        | 19 |

| 2.4  | Overview of LC Workloads.                                                                                                                                                                                                                                                                                                | 30 |

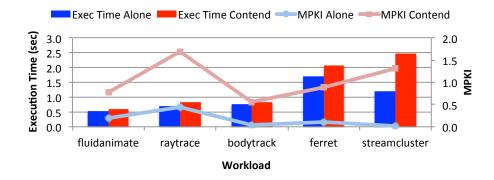

| 2.5  | Overview of BE Workloads.                                                                                                                                                                                                                                                                                                | 31 |

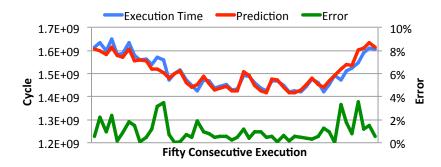

| 2.6  | Prediction Trace for <i>Raytrace</i> with <i>RS</i>                                                                                                                                                                                                                                                                      | 31 |

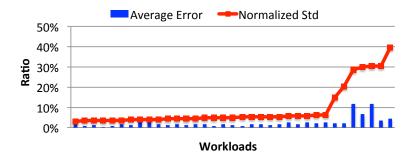

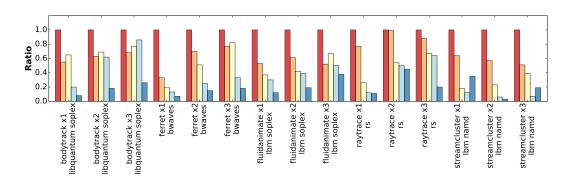

| 2.7  | Prediction Accuracy for all LC-BE mixes                                                                                                                                                                                                                                                                                  | 33 |

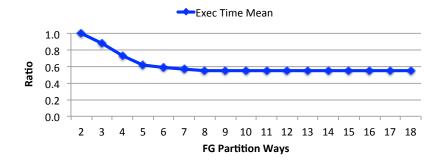

| 2.8  | Exhaustive Search on Partition Size                                                                                                                                                                                                                                                                                      | 34 |

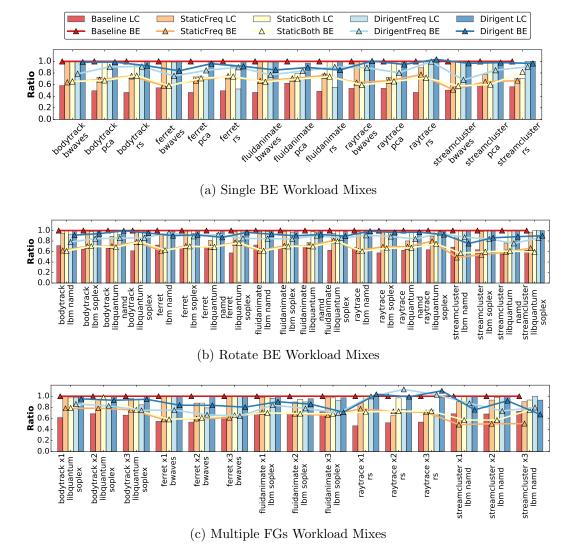

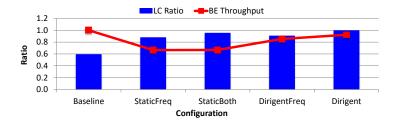

| 2.9  | Comparison of LC and BE Performance                                                                                                                                                                                                                                                                                      | 36 |

| 2.10 | Summary of All Single LC Workload Mixes                                                                                                                                                                                                                                                                                  | 37 |

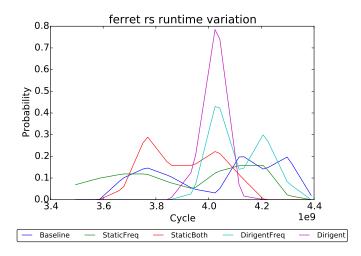

| 2.11 | Execution Time Probability Density Function Curve.                                                                                                                                                                                                                                                                       | 39 |

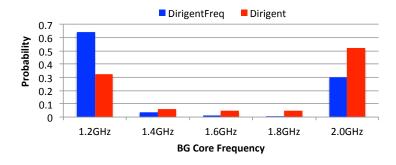

| 2.12 | BE Core Frequency Distribution                                                                                                                                                                                                                                                                                           | 39 |

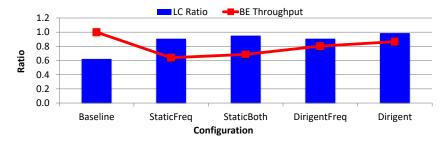

| 2.13 | Summary of All Multiple LC Workload Mixes                                                                                                                                                                                                                                                                                | 41 |

| 2.14 | Normalized Standard Variation of Multiple LC Workload Mixes.                                                                                                                                                                                                                                                             | 41 |

| 2.15 | Tradeoff Between LC throughput and BE performance $\ . \ . \ .$ .                                                                                                                                                                                                                                                        | 42 |

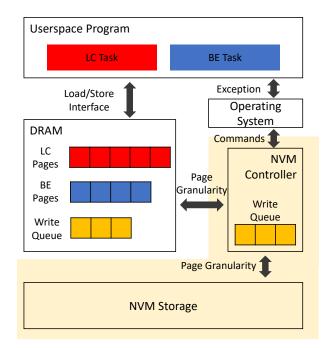

| 3.1  | Baseline system architecture                                                                                                                                                                                                                                                                                             | 51 |

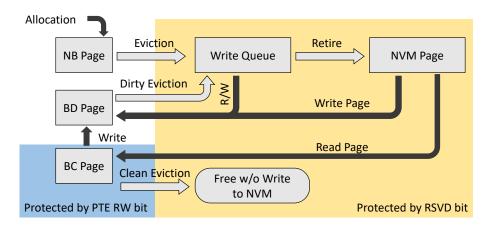

| 3.2  | Baseline page management policy                                                                                                                                                                                                                                                                                          | 53 |

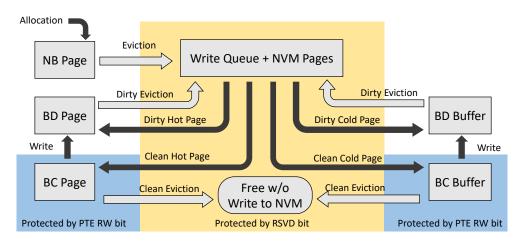

| 3.3  | Page management policy with NVM buffer                                                                                                                                                                                                                                                                                   | 56 |

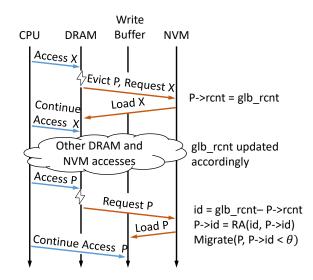

| 3.4  | Page admission with Idle Distance. The idle distance id of page<br>P is the number of NVM read requests between its most recent<br>access (tracked by glb_rcnt) and when it was evicted last time<br>(tracked by per page rcnt). Our implementation updates id<br>using running average (RA) to filter out system noises | 57 |

| 3.5  | Miss Rate Fraction example                                                                                                                                                                                                                                                                                               | 58 |

| 0.0  |                                                                                                                                                                                                                                                                                                                          | 00 |

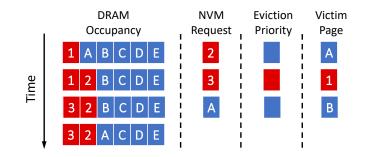

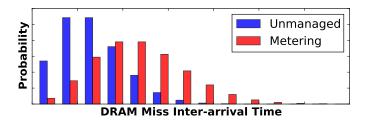

| 3.6  | Write Bandwidth Metering smoothes out write bursts to reduce interference with LC tasks.                                                                                                                                                                                        | 60  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.7  | Simulator architecture                                                                                                                                                                                                                                                          | 62  |

| 3.8  | ONSim PTE extension bits.                                                                                                                                                                                                                                                       | 64  |

| 3.9  | ONSim Performance Overhead.                                                                                                                                                                                                                                                     | 69  |

| 3.10 | ONSim NVM-latency accuracy.                                                                                                                                                                                                                                                     | 70  |

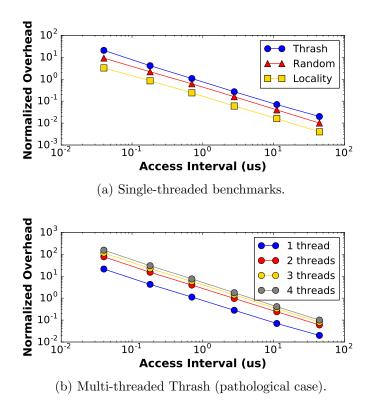

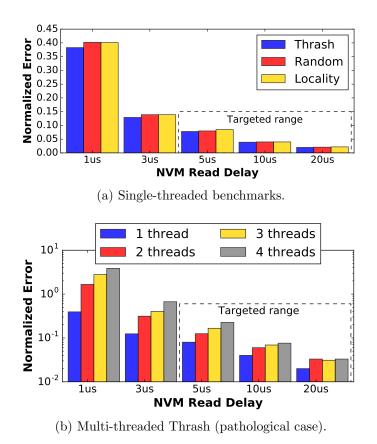

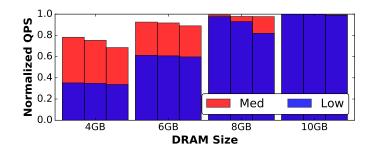

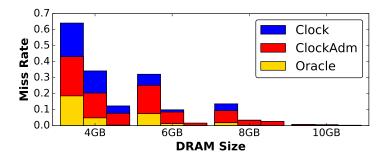

| 3.11 | Performance sensitivity to DRAM size. QPS is normalized to all-DRAM configuration. Bars with in each group represent $5/10/20$ µs NVM latency. Results show larger performance improvements when bottleneck shifts from write bandwidth to read latency.                        | 75  |

| 3.12 | DRAM Caching Efficiency Sweep Analysis. Each group of bars show results of low, medium, and high locality from left to right.                                                                                                                                                   | 75  |

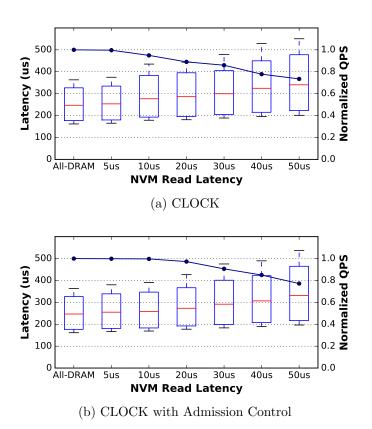

| 3.13 | NVM latency sweep. Curve is normalized QPS; the whiskers are 5%-ile and 95%-ile latency; box bounds are 10%-ile and 90%-ile latency; line is average latency.                                                                                                                   | 78  |

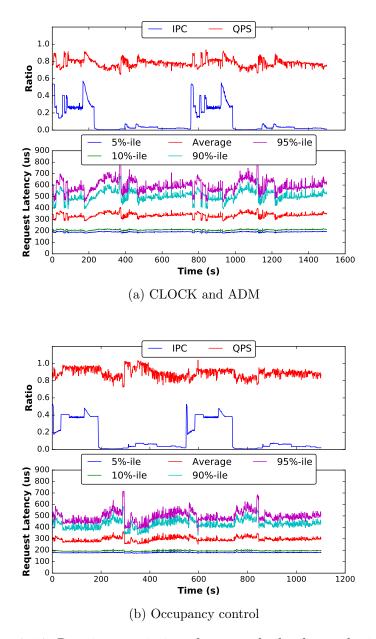

| 3.14 | Runtime statistics of memcached colocated with BT                                                                                                                                                                                                                               | 79  |

| 3.14 | Runtime statistics of memcached colocated with BT (cont.).                                                                                                                                                                                                                      | 80  |

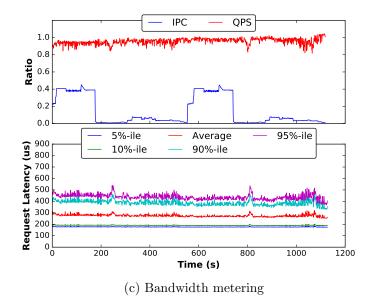

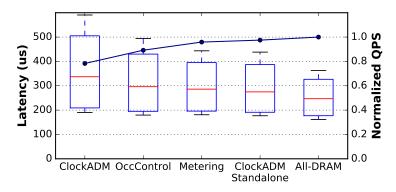

| 3.15 | Latency distribution colocated memcached                                                                                                                                                                                                                                        | 80  |

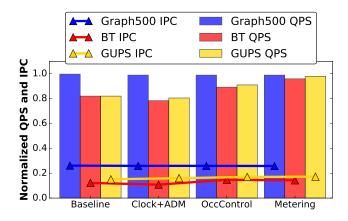

| 3.16 | Performance results of task colocation                                                                                                                                                                                                                                          | 83  |

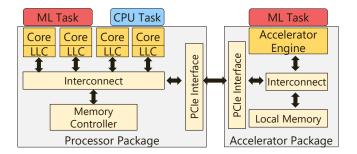

| 4.1  | Architecture of an accelerated platform.                                                                                                                                                                                                                                        | 90  |

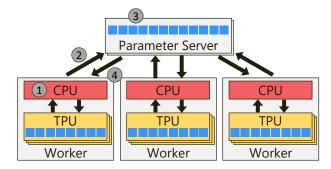

| 4.2  | Example workflow of distributed TensorFlow training with parameter servers.                                                                                                                                                                                                     | 91  |

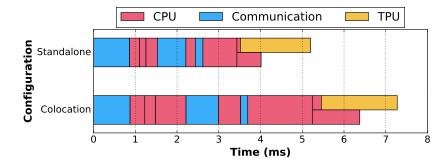

| 4.3  | RNN inference server execution timeline on a TPU platform.<br>Execution time for CPU-intensive phases increases by 51% un-<br>der heavy contention. The interleaving among different phases<br>in the execution timeline is on the order of sub-milliseconds to<br>millisecond. | 93  |

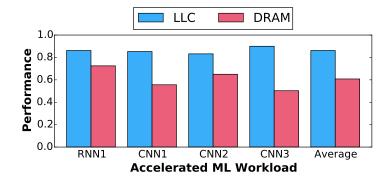

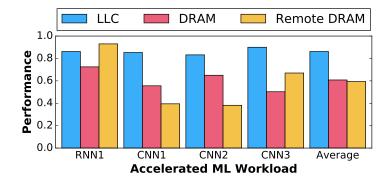

| 4.4  | Workload sensitivity to shared resource interference. Perfor-<br>mance is normalized to no interference                                                                                                                                                                         | 97  |

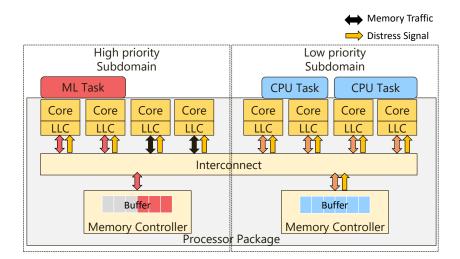

| 4.5  | NUMA subdomain and memory backpressure                                                                                                                                                                                                                                          | 99  |

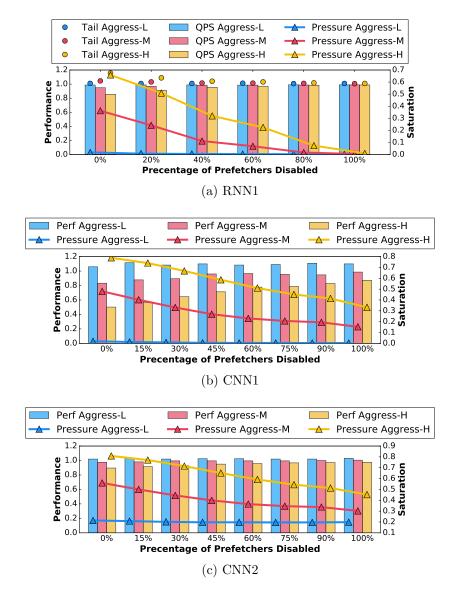

| 4.6  | Performance impact of shared memory backpressure and effec-<br>tiveness of backpressure management with prefetchers toggling.<br>Three levels of aggressiveness of the antagonists (L, M, and H)                                                                                | 102 |

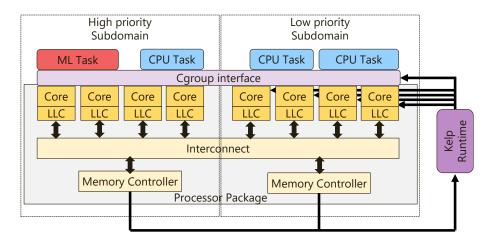

| 4.7  | Kelp architecture.                                                                                                                                                                                                                                                              | 105 |

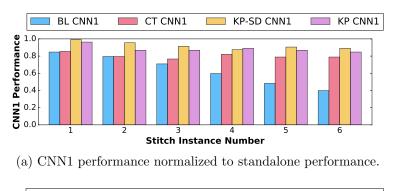

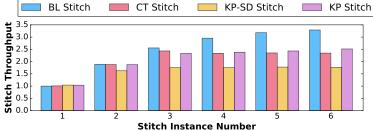

| 4.8  | Memory pressure sweep $\text{CNN1} + \text{Stitch.} \dots \dots \dots \dots$                                                                                                                     | 110 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

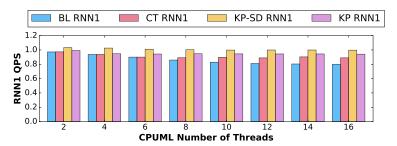

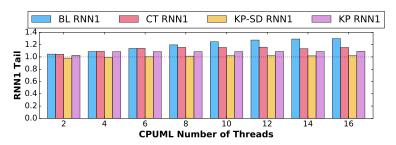

| 4.9  | Memory pressure sweep RNN1 + CPUML                                                                                                                                                               | 112 |

| 4.10 | Parameters for three performance isolation configurations for $CNN1 + Stitch. \dots \dots$ | 113 |

| 4.11 | Parameters for three performance isolation configurations for $RNN1 + CPUML$ .                                                                                                                   | 114 |

| 4.12 | ML and CPU task performance results                                                                                                                                                              | 115 |

| 4.13 | Performance tradeoff comparison between CT, KP-SD, and KP.                                                                                                                                       | 116 |

| 4.14 | Workload sensitivity to remote memory interference compared to LLC and local DRAM.                                                                                                               | 117 |

| 4.15 | Cloud TPU Platform Remote Memory Sweep                                                                                                                                                           | 119 |

# Chapter 1

## Introduction

Billions of dollars are invested every year in building warehouse scale computers (WSCs). By amortizing power, cooling, and management overheads, WSCs promise significantly higher cost-efficiencies compared to private datacenters, and attract applications with a large range of performance characteristics and requirements. One important category of WSC workloads includes a combination of latency-critical and latency-noncritical tasks. Ideally, noncritical tasks are used to "backfill" compute resources to fully utilize the WSC. Unfortunately, this is often difficult to achieve while still maintaining the performance goals of the latency-critical tasks because their performance degrades from resource interference. In fact, hardware is often intentionally over-provisioned to ensure quality-of-service (QoS) goals for latency-critical tasks, and the resulting under-utilization translates into huge wastes of system capacity and capital investment. As a result, performance interference bottlenecks system utilization and causes significant loss in cost-efficiencies of datacenters. This dissertation focuses on mitigating the fundamental conflicts between stringent QoS requirements for latency-critical tasks and inflated infrastructure Total Cost of Ownership  $(TCO)^1$ .

## 1.1 Warehouse Scale Computers and Workloads

Warehouse Scale Computers (WSCs) power the Internet as we know it today [15]. With the increasing adoption and deployment of machine learning services, WSC operators continue to evolve their infrastructure and workloads to maintain competitive service cost-efficiency.

From the hardware infrastructure perspective, a WSC usually consists of thousands of computing nodes that are interconnected through a network subsystem. While WSC operators update hardware over time, the infrastructure is relatively homogeneous in that there are relatively few configurations in a given WSC (instead of hundreds of configurations in the consumer electronics market). The small number of configurations significantly reduces overhead in managing the system and allows the WSC operator to easily test and deploy new services across the WSC.

From the workload perspective, WSC applications typically rely on distributed storage systems to process huge amounts of data. The scale of these services dictates that applications have to leverage parallelisms over multiple

<sup>&</sup>lt;sup>1</sup>Content in this chapter is published in the following article: Haishan Zhu and Mattan Erez. 2016. Dirigent: Enforcing QoS for Latency-Critical Tasks on Shared Multicore Systems. In Proceedings of the Twenty-First International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '16). ACM, New York, NY, USA. Authorship contributions: conception and design of study: Haishan Zhu and Mattan Erez; data acquisition and analysis: Haishan Zhu and Mattan Erez; drafting manuscript: Haishan Zhu and Mattan Erez; critical manuscript revision: Mattan Erez.

levels of system abstraction (computation, storage, and network). Another interesting characteristic of the workload is the increasing variety of applications that run on WSCs [97]. A wide range of services and applications are attracted to WSCs because of immediate availability of large-scale computation resources and competitive cost-efficiency. For example, with constant advances in data analytic techniques (e.g., machine learning), more entities that handle large amounts of data depend on WSCs to extract information and build services.

Finally, the recent advancement in machine learning applications leads to increasingly wide adoption of accelerators in WSC environments. GPUs have been widely used for ML training and inference [5, 94, 33, 59]. Other solutions that are application specific (e.g., FPGAs [143] and ASICs [95]) can achieve even higher efficiency and performance and have also been deployed in production. Accelerated nodes can further scale-out to accommodate larger ML models. As the heavy computation is carried out by the accelerators, CPUs in these systems are often responsible for various supporting tasks to sustain the high accelerator performance. This new computation paradigm brings new challenges in resource management and CPU design.

## 1.2 WSC Workload Management

Workloads in the datacenter can be broadly classified into two categories: The first includes tasks that are best-effort (BE), for which throughput is the primary concern and that can be freely scheduled in the background when resources are available. The second category includes latency-critical (LC) user-facing tasks, which often have a short execution time with strict completion time targets to achieve certain quality-of-service (QoS) goals. This LC category can be further divided into three application types:

- Applications like key-value stores usually have extremely short delay targets (a few milliseconds) in order to achieve good user experience.

[16, 78, 119] Caching services that built on top of these applications often rely on sharding of data to improve system capacity and throughput, which can cause high sensitivity to tail latency on each node for large fan-out services [40].

- 2. Offloaded tasks from mobile devices is an emerging class of workloads. Such tasks are computationally intensive and have relatively long execution times (e.g., hundreds of milliseconds) [114, 72, 182]. Examples of this class of workloads include online video processing, online stream data analysis, and recognition tasks.

- 3. Accelerated machine learning workloads, which include both training and inference. These tasks have high priority because accelerators are often capable of higher computational throughput and efficiency compared to CPUs, and customers are usually charged more for using these resources [66, 8]. Note that while training applications typically have long execution time, latency is still critical for ML model design iterations and service time to market.

LC tasks on their own cannot be used to fully utilize a node. It is often undesirable to collocate LC tasks because of aspects relating to how data is sharded across cloud servers and sizes of application state [15, 119, 40]. WSC applications often scale out to thousands of nodes, each of which works on a portion of the total dataset to exploit data-level parallelism. Ideally, best-effort tasks are used to "backfill" compute resources to fully utilize all available resources in the WSC, thus providing optimal cost-efficiency for both the datacenter operators and WSC clients. Unfortunately, this is often difficult to achieve while still maintaining the performance goals of the latency-critical tasks because their performance degrades from resource interference, as we discuss in more detail next.

#### **1.3** Performance Interference and Utilization Bottleneck

"Backfilling" BE tasks to better utilize nodes is not always possible because of the detrimental impact it has on LC performance. Specifically, collocating BE and LC tasks can cause performance degradation because of the contention between LC and BE tasks for limited shared resources, such as CPU time, cache and main memory occupancy, and I/O bandwidth. Due to the scale-out design of WSC applications, the response time of each request is ultimately determined by the delay of the slowest node. As a result, even a small increase in the probability of a QoS violation at the node level can be significantly amplified at the service level [40]. One of the most common techniques to minimize QoS violations it to over-provision hardware resource to guarantee quality-of-service (QoS) for latency-critical tasks. The resulting under-utilization translates into wasting system capacity and capital investment. As a result, performance interference bottlenecks system utilization and causes significant loss in the cost-efficiency of datacenters.

#### 1.4 WSC Workload Statistical Behavior

WSC workloads exhibit various statistical behaviors in terms of workload intensity and resource requirements. As a result, it is often difficult for programmers and WSC operators to accurately estimate and allocate resources for production workloads. Resource allocation is often conservative to guarantee the performance of high-priority latency critical tasks, leading to low utilization and loss of efficiency.

There are two main factors that contribute to the statistical behavior of WSC workloads. First, user behavior is non-deterministic, which causes the workload to vary over time. Specifically, user behavior varies on two time scales. On the coarse time scale, user behavior varies in a diurnal pattern [119], in addition to spikes events and holidays. On the fine time scale, user behavior also oscillates over hours and even seconds [167]. Second, WSC application behavior is non-deterministic. For example, master-slave database architectures are commonly used in data hosting. The slaves are mostly responsible for backing up data from the master and exhibit low load. However, in cases when the master fails, a slave will be promoted and its load will increase rapidly [138]. Other factors that contribute to the variability of WSC workloads include system daemons, queueing at various layers, and maintenance activity [40, 122]. The statistical behavior of WSC workloads places unique challenges and opportunities in WSC resource provisioning. In this dissertation, I exploit this observation to improve utilization of hardware resources.

#### 1.5 Thesis Statement

Internet service providers need to further improve cost-efficiency of Warehouse Scale Computing beyond simple resource aggregation. However, increasing hardware utilization without managing resource interference can cause performance and quality-of-service degradation for latency-critical tasks. As a result, system operators often over-provision hardware resources, causing significant loss of total cost of ownership. My thesis is that the resource utilization, hence cost efficiency, of a datacenter can be drastically improved with a set of cross-layer techniques, which leverage the statistical behavior of latency-critical tasks and maximize total system throughput without compromising the quality-of-service for latency-critical tasks.

### **1.6** Contributions

In this dissertation, I study the performance and QoS issues caused by task colocation in the WSC environment. I choose three representative workload and system architecture combinations and tailor solutions based on application requirements and architecture performance isolation capabilities. These studies show that significant opportunities exist in increasing WSC resource utilization without sacrificing QoS for latency-critical tasks. I propose a set of runtime solutions to take advantage of these opportunities by measuring workload performance characteristics and leveraging low-level hardware capabilities. I evaluate these solutions on existing hardware when the capabilities are available and use simulators when they are not. The main contributions of this dissertation are summarized as follows:

- 1. To improve cost-efficiency of multicore systems that target emerging of-floaded workloads, I propose to leverage the statistical behavior of LC workloads to improve total system throughput. This is achieved by iso-lating tasks to limit performance interference and guarantee QoS for LC tasks, while converting latency headroom of the LC tasks to improve total system throughput. I demonstrate the benefits of this approach with Dirigent, a lightweight resource management runtime system that reduces the execution time variation of LC tasks to improve the throughput of BE tasks. Dirigent coordinates all contending processes with the knowledge of expected completion times and deadlines. Dirigent is thus able to improve background-task performance by enabling foreground tasks to yield resources when they are expected to finish faster than their required latency.

- 2. To improve the cost-efficiency of the memory subsystem, I identify an opportunity to replace a significant portion of DRAM with slower but cheaper Non-Volatile Memory (NVM). To quantify the performance im-

pact of such a Heterogeneous Memory Architecture (HMA), I develop and build ONSim, an OS-level NVM simulator. ONSim integrates within the Linux kernel and virtualize multiple PTE bits to dynamically collect and act on runtime memory access information. ONSim is transparent to userspace applications. ONSim enables users to easily modify HMA parameters, page migration policies, and various resource-allocation priorities without changing the underlying functional kernel code. I perform rigorous evaluation on the capability of ONSim, and show that it has both low overhead and high fidelity for its target workloads.

- 3. I study the performance of memcached, a popular key-value store application, on systems with heterogeneous memory using ONSim. I analyzed the performance of memcached in both standalone and colocated execution. I then propose three techniques to reduce NVM performance impact by exploiting the performance characteristics of the target workloads, such as the strong locality in memory accesses, low write-to-read ratio, and load variation over time. I evaluate these techniques with ONSim and show that these techniques can maintain high performance and QoS for the popular and important key-value store application on HMA systems.

- 4. To improve the cost-efficiency of accelerated systems for machine learning (ML) applications, I first profile a set of production ML workloads on various accelerated systems. Through a detailed sensitivity study, I

show that the performance of these workloads can be significantly impacted by host memory bandwidth pressure, which prevents colocation of low priority tasks and leads to wasted resources. To tackle this problem, I propose Kelp, a lightweight runtime system that leverages existing hardware features to mitigate performance interference. Evaluation results show that Kelp is effective in isolating accelerator performance from memory bandwidth interference while sustaining high system throughput. This study also shows that high-performance accelerators pose new system architecture challenges, and motivates the need for fast and lowoverhead fine-grained memory performance isolation mechanisms

### 1.7 Dissertation Organization

The rest of my dissertation is organized as follows. Chapter 2 discusses mechanisms that improve cost-efficiency of multicore systems by leveraging latency headroom to achieve better system performance. Chapter 3 details the design and evaluation of ONSim, which simulates HMA systems with high fidelity and low overhead. I also describe the work on performance and QoS of HMA systems in this chapter. Chapter 4 presents the study on performance interference in accelerated ML systems and discusses mechanisms to mitigate it on real systems. Finally, Chapter 5 discusses future work and concludes this dissertation.

## Chapter 2

# Improving QoS and Utilization on Multicore Sysmets

Latency-critical applications suffer from both average performance degradation and reduced completion time predictability when collocated with batch tasks. Such variation forces the system to overprovision resources to ensure Quality of Service (QoS) for latency-critical tasks, degrading overall system throughput. We explore the causes of this variation and exploit the opportunities of mitigating variation directly to simultaneously improve both QoS and utilization. We develop, implement, and evaluate Dirigent, a lightweight performance-management runtime system that accurately controls the QoS of latency-critical applications at fine time scales, leveraging existing architecture mechanisms. We evaluate Dirigent on a real machine and show that it is significantly more effective than configurations representative of prior schemes<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Content in this chapter is published in the following article: Haishan Zhu and Mattan Erez. 2016. Dirigent: Enforcing QoS for Latency-Critical Tasks on Shared Multicore Systems. In Proceedings of the Twenty-First International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '16). ACM, New York, NY, USA. Authorship contributions: conception and design of study: Haishan Zhu and Mattan Erez; data acquisition and analysis: Haishan Zhu and Mattan Erez; drafting manuscript: Haishan Zhu and Mattan Erez; critical manuscript revision: Mattan Erez.

#### 2.1 Background

#### 2.1.1 Target Workloads and Metrics

Based on prior publications, we classify cloud workloads into three categories [15, 109, 72, 27, 31, 114]. The first includes tasks that are not userfacing, for which throughput is the primary concern, and that can be freely scheduled in the background when resources are available. The second class includes short latency-critical user-facing tasks, such as responding to web search requests and content caching. This class of workloads is characterized by short deadlines in the order of tens of milliseconds. The third is an emerging class of workloads that correspond to offloading of work from user devices to the cloud. Examples include recognition tasks. Such tasks are user facing and latency critical, yet are also computationally intensive and have relatively long execution times. compared to some other user-facing cloud These tasks can take hundreds of milliseconds or more to finish and therefore can benefit from being offloaded to the cloud [114, 72, 27].

Both the second and third classes are typically user-generated tasks, of which those arising from sophisticated data and sensor processing applications often belong to the third class. Both classes pose challenges for efficient cloud resource usage. In particular, their performance is expressed both in terms of throughput (number of tasks processed per unit time) and in terms of strict latency constraints where only a small fraction of tasks can violate the constraints without severe penalties. Two common and useful measures corresponding to these performance goals are *average execution time* for throughput and 95-percentile execution time (or other percentile goals) for latency constraints. Note that in evaluating Dirigent in this paper, we use workloads comprised of tasks from the first and the third categories.

#### 2.1.2 Contention Control Mechanisms

Dirigent relies on existing mechanisms to manage interference and provide good QoS for the LC jobs. Dirigent uses per-core DVFS and cache partitioning, which we summarize below. We also discuss additional hardware mechanisms that have recently been proposed.

Per-Core dynamic voltage and frequency scaling (DVFS) is a common mechanism for controlling performance and improving processor energy efficiency [130, 104, 86]. Per-core frequency management enables performance adjustments at fine time scales [147, 78], and it can also be used as a throttling mechanism to manage contention and resource usage [74, 80].

Cache partitioning is another well-studied mechanism that provides performance isolation of processes that are collocated and that is used to limit variation and contention [145, 115, 100, 150, 30, 35, 81]. Prior work established the effectiveness of cache partitioning as a QoS mechanism and it has recently been implemented in commercial processors. However, because of the large capacity of the last level cache, changes to cache partitions take significant time to have an impact on execution, an effect termed *cache inertia* [100]. Thus, cache partitioning is effective at relatively long time scales.

While we do not currently use these mechanisms in Dirigent as they

are not yet available in commercial processors, there is also a large body of work on QoS mechanisms for managing memory bandwidth and latency resources. Yun et al. studied the performance benefits of memory bandwidth reservation for latency-sensitive applications [173]. Mutlu et al. show different levels of QoS goals and performance benefits that can be achieved by making memory scheduling QoS aware [133, 134, 105, 135]. Usui et al. presented QoS aware memory scheduler that handles different priority levels in heterogeneous systems [164]. In other related work, Ebrahimi et al. proposed source throttling, which is a hardware-based mechanism controls the rate at which cores generate requests to shared memory system [51]. Jeong et al. studied the rowbuffer locality interference in multicore processors [92]. Zhou et al. proposed an architecture that allows fine-grain micro-architecture resource partitioning among threads [180]. Ma et al. designed a mechanism to control queueing delay of requests in different architecture structures [121]. While other contention sources exist in warehouse scale datacenters, there is a large body of related work that show how intelligent task schedulers can identify and avoid such resource conflicts [96, 110, 112, 46, 47].

## 2.2 Dirigent Principles

An important insight that Dirigent leverages is that minimizing variation can simultaneously meet the performance targets of latency-critical tasks and improve system utilization. Large variations in the completion time of LC tasks cause inefficiencies in the shared system because they lead to overprovisioned resources for LC tasks and system underutilization for latency targets to be met. To understand these inefficiencies, consider an LC task that can meet its throughput and latency targets when running alone, but suffers from large variation in execution time when under contention.

Figure 2.1 shows an example of the execution time probability density function of such a program, where the blue curve represents standalone execution, the red curve shows the behavior under contention, and an ideal curve is shown in green. In standalone execution, LC tasks often complete significantly ahead of the deadline and the throughput achieved (average execution time) is higher than required. As a result hardware is not fully utilized because there is large performance headroom in most LC executions that could be used for other tasks (shown as the highlighted region). However, when a BE task is introduced, too many deadlines are missed despite the average throughput target being maintained.

Previous work focused on keeping core occupancy high while meeting latency goals [126, 119, 176]. However, by explicitly addressing task-to-task variation at fine time scales within a single task, the ideal (green curve) can be achieved. In this ideal case, both throughput and latency targets are met precisely and core and frequency resources are maximally utilized. Dirigent achieves this ideal curve through unique fine time scale monitoring and control mechanisms.

Furthermore, high variation reduces resource utilization because of task scheduling policies designed for meeting LC task latency constraints. Consider

Figure 2.1: Example LC completion time probability density functions when run alone, under contention, and in an ideal scenario; the shaded region points to underutilized resources when run alone.

a common reservation-based scheduling policy that ensures on-time completion of LC tasks by reserving sufficient resources to guarantee a 95% latency target [10]. :Figd:fig:scheduler shows how this scheduler operates on two different sets of tasks: tasks of type A, which have high execution time variance, and type B which have low variance. With high variance, the scheduler reserves too much time for the first task (shown in green) because allocation is forced to expand due to the long tail of execution time probability distribution curve, leading to poor system utilization. This does not happen with the lowvariance tasks. Significant prior work on scheduling has shown that scheduling tasks with deadlines can be done more aggressively and with higher system resource utilization when variance is low [154].

Dirigent controls fine-grained scheduling and frequency to maximize utilization while meeting QoS goals. In this way overall utility per unit energy

Figure 2.2: Reservation-based scheduler efficiency with two different task types: type A with high execution time variance and type B with low variance.

is maximized. This is in contrast to a line of prior work that reduces the impact of variation by rapidly adjusting processor clock frequency [118, 78, 165, 99, 117, 25]. Matching frequency to LC compute needs reduces processor energy consumption, but falls short of maximizing efficiency because the processor itself consumes just 25% - 35% of total system power [127, 118, 54].

## 2.3 Dirigent Design and Implementation

Dirigent is composed of three main components: profiler, predictor, and controller. The profiler examines and records the execution of an LC applications offline and in isolation. The profiling information is then used online to predict the expected execution time of the LC application. The controller then partitions resources and throttles tasks to minimize the execution time variation of LC tasks while providing as much resources as possible to BE tasks, thus achieving the goal of simultaneously meeting latency-critical requirements and allowing high processor utilization. The rest of this section discusses in detail the design and initial implementation of Dirigent. Again, we point out that Dirigent is unique in the fine time scales on which it operates. We implement Dirigent in C++ and evaluate it using a 6-core Intel Xeon E5 2618L-v3 processor, which supports per-core frequency settings and cache partitioning [81].

#### 2.3.1 Offline Execution Profiler

Dirigent profiles the execution of an LC application when running alone offline. The profiler records progress information that is then used to make accurate online predictions of completion time under contention while a task is still executing. The Dirigent profiler periodically samples the execution progress of the LC task being profiled by measuring and recording a series of (*time, progress*) pairs when the LC is running alone without any contention (see Figure 2.3a). The LC program in the example of Figure 2.3a has 3 profiled segments and takes  $3\Delta T$  time units to execute, where  $\Delta T$  is the sampling period. We measure *progress* by counting the number of retired instructions using the processor's model-specific performance counter monitors [86], but more abstract metrics can also be used. Note that progress can significantly differ between segments even though the sampling frequency is constant. This is because progress depends on the instruction mix, data access pattern, data set size, and other factors.

Dirigent requires minimal profiling. In our current implementation, the profiler requires no extra hardware as both execution time and instruction count are readily available in most architectures today. Dirigent uses performance counters and sleep method for periodic sampling with negligible

Figure 2.3: Execution time predictor example.

impact on the running application. Although performance overhead is not a great concern in offline profiling, this low overhead ensures the accuracy of these measurements. Furthermore, note that while our current implementation of Dirigent relies on offline profiling, it is possible to perform online profiling instead, which requires the system to run the LC task a few times while all other tasks are paused to record a stable profiling record.

#### 2.3.2 Execution Time Predictor

To predict LC completion time and control resources, Dirigent periodically samples progress during contended online execution. Dirigent predicts LC completion time by tracking actual progress, comparing this progress to the profiled data, and computing a *time penalty* experienced by the LC process, which is then projected forward to completion as explained below. We pin the Dirigent runtime thread to a core that runs a BE task and again use the **sleep** method to periodically interrupt the BE task and execute the Dirigent runtime task.

The time penalty of a specific segment is computed assuming a fixed rate of progress within each segment. The penalty is the difference between the expected time to make the amount of progress within the profiled segment at the rate of progress experienced in the online segment vs. the profiled time for this segment. This is summarized in Equation 2.1 where  $P_i$  is the penalty for the  $i^{th}$  segment and  $\Delta T_i$  is the duration of that segment. Note that  $\Delta T_i$ can be slightly different than  $\Delta T$  in the real implementation because of factors such as errors in timers. We account for that difference in Dirigent to ensure the accuracy of the prediction. Also, we introduce the symbol  $\alpha_i$  shown in Equation 2.1 as shorthand for the ratio of measured vs. expected progress rates for the  $i^{th}$  segment.

$$P_{i} = \frac{Profiled\_progress_{i}}{Measured\_progress_{i}} \Delta T_{i} - \Delta T_{i} = (\alpha_{i} - 1) \Delta T_{i}$$

(2.1)

Frequent samples increase the execution time prediction accuracy and the opportunities for performance management, but each prediction and control segment has overhead. We measured this overhead using a subset of our workload mixes. Results show the runtime overhead is minimal and each Dirigent invocation requires on average less than  $100\mu s$  (including predictor and throttler). We therefore chose a sampling period  $\Delta T = 5ms$  to balance the overhead and effectiveness of online prediction and control. This sampling period provides 100 or more segments in all the LC applications we test with only negligible runtime overhead.

To increase prediction accuracy, Dirigent maintains an exponential moving average (with weight 0.2) of the penalty within each segment across multiple executions of the LC task, which we denote  $\overline{P_i} = 0.2P_i + 0.8\overline{P_i}$ . Figure 2.3b shows the average penalty in blue. Note that just like progress, the average penalty can differ significantly across segments. The moving average smooths occasional outlier executions. At a given point in time during a single LC task's execution, Dirigent's predictor uses the penalties observed so far for each segment, the total elapsed time from the start of the process, and the average penalties of the segments yet to execute to compute the expected execution time of the task. The formula is shown in Equation 2.2, where k is the segment corresponding to current time T, N are the total number of segments in the profiled execution, and  $MA\left(\left\{\alpha_i\right\}_{i=1}^k\right)$  denotes an exponential moving average over the rate factors measured so far in the current execution. This moving average is used as the expected penalty scaling factor for the remainder of the current execution.

$$T_{est,k} = T + \sum_{i=k+1}^{N} \left( MA\left( \{\alpha_i\}_{i=1}^k \right) \overline{P_i} + \Delta T_i \right)$$

(2.2)

Figure 2.3c illustrates how the prediction calculation of Equation 2.2 is performed. When the example program finishes executing the second segment, the penalty scaling factor  $\alpha_2$  is much smaller than the factor  $\alpha_1$  of the first segment. This difference arises from factors such as OS noise, phase changes of the BE applications, and context switches. The moving average across executions and of executions within the segment smooths out the difference of the scaling, which is then used as the predictive factor for the remaining segment.

In our experiments with Dirigent, we arbitrarily chose a weight of 0.2 for the exponential moving averages and a 5ms sampling interval. As we show in Section 2.4.2, the predictor is highly accurate with these parameters and is able to predict the expected execution time to within 2%, typically, across multiple applications and different levels of contention. We tested the sensitivity of Dirigent to weight factors in the range of 0.1 - 0.3 and conclude that Dirigent is robust. We also evaluate Dirigent's sensitivity to sampling periods. We conclude that even 40 samples per execution of the LC task tested provide for accurate completion-time predictions. However, the low performance overhead (< 100µs per invocation) enables high sampling frequency for accurate prediction and tight QoS control for LC tasks that widely differ in execution time.

### 2.3.3 Performance Controller

Dirigent monitors the performance of LC applications online and uses the predictor to determine whether these applications are progressing faster or slower than necessary to meet their latency goals. Recall that Dirigent does not strive to minimize the execution time of LC tasks, but rather to minimize their execution time variation while meeting their latency targets. As a result, resources for the LC tasks are not over-provisioned. If a LC task is expected to complete before its target time, it is deprioritized and BE tasks can achieve higher throughput. On the other hand, if a LC task is lagging, Dirigent prioritizes resources toward that LC task and away from BE tasks.

In our current implementation of Dirigent, we allocate resource by controlling the frequency at which each core operates, by partitioning the last-level cache (LLC), and by pausing BE tasks when necessary. We chose these mechanisms from the possible ones described in Section 2.1.2 because they are both effective and available in current systems. We use frequency and task-pausing to control LC progress at fine time scales and cache partitioning at a coarser ones; with large caches, *cache inertia* means significant time passes before the impact of adjusting partitions takes effect [100].

Fine time scale control: The goal of the fine time scale controller is to quickly respond to changes in contention and LC task progress to ensure deadlines are met and minimize performance variance. The controller observes the execution time predictions and decides whether LC tasks can yield resources or whether BE tasks must be throttled and to what extent. A simplified version of the fine time scale controller policy for a single LC task is designed as follows.

At each decision point, the controller determines if the LC task is ahead or behind. If ahead, the controller will check the following three options in order. First, if any best-effort jobs are paused, the control decision is to continue them. Second, if no tasks are paused but some are throttled, the decision is to speed up any throttled BE processes by one speed grade (using existing per-core DVFS mechanisms). Third, if all BE tasks are already running at their maximum frequency, the decision is to throttle the LC task frequency. Similarly, if the LC task is behind schedule, the decision is to speed up to maximum frequency. If it is already at maximum frequency, the decision is to immediately throttle the frequency of the BE tasks. If the BE tasks are already at the minimum frequency, the most intrusive active BE is paused; we define intrusiveness as the number of LLC load misses a task generates, which we obtain from existing performance counters. The throttler controls each core using the CPUFreq Governor of Linux [18].

While the Dirigent runtime is very lightweight, the impact of control decisions is not instantaneous. We therefore only make control decisions every some small number of prediction segments (5 in our experiments, arbitrarily). Furthermore, we only take control actions if the expected LC execution time is more than 2% ahead the target deadline and only pause BE tasks if the LC task is expected to complete more than 10% behind its deadline. We chose 2% because it corresponds to the typical error of the predictor and is thus a good safety margin that prevents prematurely slowing down or interfering with a LC task. We chose a larger threshold for pausing because its overhead is greater (again, the value of 10% was arbitrarily chosen within a reasonable value range; sensitivity studies reveal that Dirigent is not sensitive to this

choice).

The decision making process is slightly more complicated when there are multiple collocated LC processes along with BE tasks. Each LC task may exhibit different levels of performance degradation even when the interference level is the same for all of them. Furthermore, any action taken on BE tasks will impact all collocated LC tasks. As a result, when all LC tasks show the same performance tendency, we use the same policy described before for a single LC process. Otherwise, BE tasks are throttled based on the performance of the slowest concurrent LC task, and any other LC tasks that are expected to finish sooner than the deadline are throttled down individually.

**Coarse time scale control:** Dirigent uses cache partitioning for coarsegrain control over the expected execution time of LC tasks, specifically the Cache Allocation Technology recently introduced by Intel [81], which can be used to specify which cache ways may be used by each processor. Because of cache inertia the system's response time to partition changes is fairly slow when compared to the typical short durations of LC tasks. We therefore use statistics collected over multiple executions of a LC task to guide adjustments to cache partitioning. Specifically, our current implementation of Dirigent tracks three measures: (1) the correlation between a LC tasks' execution time and the LLC misses it generates (over multiple executions); (2) a history of the absolute number of LLC misses over executions; and (3) a history of the Dirigent decisions states over time. In our current implementation, we use the history of 10 last executions to compute the measures above. We construct three heuristics to determine whether LC tasks benefit from greater isolation and more dedicated cache ways or whether BE tasks are allowed to utilize a greater portion of the LLC.

First, if there is strong correlation between the execution time of LC tasks and their LLC misses, it indicates that growing the LC partition is likely to improve LC performance. Therefore, if correlation is strong *and* LC tasks have recently missed deadlines, we increase isolation and add one LLC way to the LC partition (removing it from the list of ways utilized by BE tasks). We somewhat arbitrarily chose a correlation coefficient of 0.75 as the threshold determining strong correlation.

Second, Dirigent observes the LLC hit-rate history and if growing the LC partition does not lower LC tasks LLC misses, Dirigent shrinks the LC partition. This heuristic coupled with the coarse time scale and averaging performed prevents the LC partitions from continuously growing due to anomalous executions.

It is also possible for the correlation between misses and performance to not be strong yet for partitioning to still help: when LC performance is bottlenecked by high memory latency caused by contention from BE tasks. Because Dirigent's fine time scale controller throttles BE tasks when they heavily contend for resources, correlation would not detect the need for stricter partitioning of LC and BE tasks. Therefore, our *third heuristic* grows the LC partition when the controller history indicates that BE tasks are heavily throttled and their utilization of core resources is low. The second heuristic then differentiates between scenarios where BE tasks should be throttled from those where partitioning is more beneficial by shrinking the LC partition back if hit-rate does not improve. We show the effectiveness of our method in Section 2.4.3.

### 2.4 Evaluation

We evaluate Dirigent on a real machine with a range of workloads representative of a wide range of LC and BE behaviors. We first introduce the evaluation infrastructure and workloads. We then discuss a set of experiments that demonstrate the accuracy of Dirigent's completion-time predictor, the effectiveness of the coarse time scale partitioning heuristic, Dirigent's performance benefits compared to a baseline configuration and configurations that roughly correspond to prior work, and the new tradeoff between BE task throughput and LC deadline target that Dirigent enables.

#### 2.4.1 Workloads and Evaluation Infrastructure

System: We evaluate Dirigent on a 6-core Intel Xeon E5-2618L v3 server processor. The nominal per-core maximum frequency is 2GHz and 9 frequency steps are available for throttling (1.2 - 2.0 GHz, though Dirigent uses just 5equi-spaced frequencies). Turbo Boost is enabled in all experiments. The processor has a 15MB L3 LLC and supports Intel's Cache Allocation Technology, which enables us to partition the cache between LC and BE tasks to provide

| Type         | Name          | Description                             |

|--------------|---------------|-----------------------------------------|

| LC           | bodytrack     | Body tracking of a person               |

|              | ferret        | Content similarity search               |

|              | fluidanimate  | Fluid dynamic for animation             |

|              | raytrace      | Real-time raytracing                    |

|              | streamcluster | Online clustering of an input stream    |

| Single<br>BE | bwaves        | Simulation of blast waves in 3D         |

|              | PCA           | Principal Component Analysis            |

|              | RS            | Range Search                            |

| Rotate<br>BE | namd          | Biomolecular system simulation          |

|              | soplex        | Linear program solver                   |

|              | libquantum    | Simulation of quantum computer          |

|              | lbm           | Simulation of fluids with free surfaces |

Table 2.1: LC and BE Benchmarks

additional isolation. The system is configured with 4 2133MHz DDR4 channels and has a total of 16GiB. We run a Linux 3.13.0 kernel at runlevel S, which provides an environment with little OS interference and good facilities for implementing both the Dirigent predictor and controller, with an efficient sleep implementation and the built-in CPUFreq Governer, respectively. We pin all tasks to individual cores and Dirigent is pinned to a core that is shared with a BE task. We set the BE processes to have higher process niceness than the Dirigent runtime and LC processes to have the lowest niceness. We use the configuration above with no explicit resource management as the *baseline configuration*.

Workloads: Table 2.1 lists the benchmarks we use in the evaluation. We select the subset of PARSEC applications that represent latency-sensitive applications as LC tasks [17]. We chose PARSEC as it is designed to represent

emerging and user-facing workloads of the type that are being offloaded to cloud systems. We use a single run of each benchmark with sim-medium inputs as a single LC task. As shown in Figure 2.4, these tasks span a range of completion times (0.5 - 1.6s) and LLC miss rates. The figure shows the behavior of the LC benchmarks both when running alone and under contention. For this figure, we use 1 LC for all LC tasks and 5 BE cores all running *bwaves*, which falls in the middle of contention range. The LC workloads are all fairly compute-intensive, making them good offload candidates. While they are compute-intensive, they still offer a range of sensitivity to interference from BE tasks both because of LLC and memory access contention. This can be seen by the different correlation levels between LLC miss rate increase and execution time degradation between the different benchmarks. To ensure accurate measurements of these tasks, execution time is measured inside the LC processes using PARSEC's Region of Interests (ROI) interface.

We use two kinds of BE workloads to represent different interference types: BE phase changes and context switches. We use three standalone BE workloads that exhibit strong phase change behavior: the scientific simulation bwaves from SPEC 2006 [73] and the machine learning applications Principal Component Analysis (*PCA*) and Range Search (*RS*) from MLPack [39]. All other benchmarks we examined did not provide strong phase behavior, at least with respect to impact on interference, and we omit them from the evaluation—such workloads do not pose significant challenges to the Dirigent predictor.

Figure 2.4: Overview of LC Workloads.

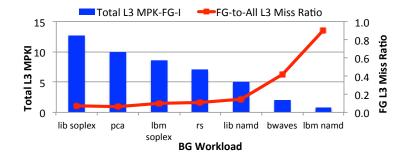

To mimic varying interference caused by context switches, we select four applications from SPEC 2006 that exhibit a range of memory intensiveness [73], though we arbitrarily chose between all benchmarks that exhibit similar intensity. We then form two-benchmark workloads and randomly switch between the two paired benchmarks each time a LC task completes. The pairs we use are (lbm+namd), (lib+namd), (lbm+soplex), and (lib+soplex). We refer these BE workloads as Rotate BE workloads. Figure 2.5 summarizes the different behaviors of the BE workloads while using a single core running *ferret* as a representative LC workload. The blue bars show the total number of L3 load misses per thousand LC instructions generated by all 6 cores. The red curve shows the fraction of misses generated by LC tasks, which can be interpreted as the ratio between LC task and total memory bandwidth consumption. As can be seen, the BE workloads cover a wide spectrum of behaviors and contention pressure. Similar trends are observed when mixing these BE tasks with other LC workloads.

Figure 2.5: Overview of BE Workloads.

Figure 2.6: Prediction Trace for *Raytrace* with *RS*.

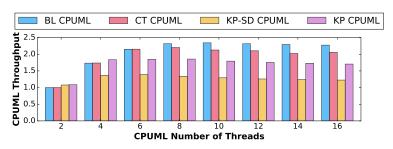

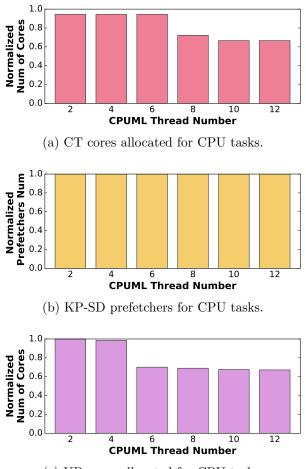

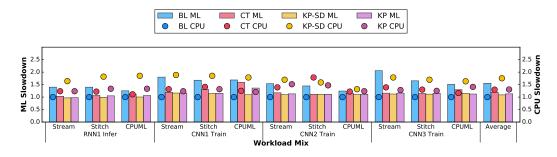

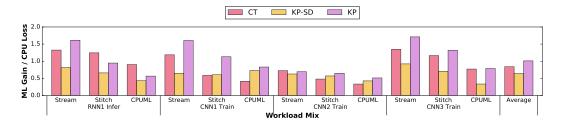

### 2.4.2 Predictor Accuracy