© 2020 Sweta Yamini Pothukuchi

# CODE GENERATION OF ARRAY CONSTRUCTS FOR DISTRIBUTED MEMORY SYSTEMS

BY

# SWETA YAMINI POTHUKUCHI

# DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2020

Urbana, Illinois

Doctoral Committee:

Professor David Padua, Chair Professor Laxmikant (Sanjay) V. Kale Professor Andreas Klöckner Professor Franz Franchetti, Carnegie Mellon University

# ABSTRACT

Programming for high performance systems to fully utilize the potential of the compute system is a complex problem. This is particularly evident when programming distributed memory clusters containing multiple NUMA chips and GPUs on each node since it would require a complex combination of MPI, OpenMP, CUDA, OpenCL, etc to achieve high performance even for sequentially simplistic codes. Programs requiring high performance are usually painstakingly written by hand in C/C++ or Fortran using MPI+X to target these machines.

This work presents a multi-layer code generation framework *Vaani* that takes a very high-level representation of computations, and generates C+MPI code by transforming the input through a series of intermediate representations. The very high level nature of the language greatly facilitates programming parallel systems. Additionally, the use of multiple representations provide a flexible and transparent venue for the user to interact and customize the transformation process to generate code suitable to the user and the target machine.

Experimental evaluation shows that the current implementation of *Vaani* generates code that is competitive with handwritten codes and hand-optimized libraries.

To my family, for their love and support.

### ACKNOWLEDGMENTS

First and foremost, I would like to thank my adviser Professor David Padua, for his support, guidance and patience. He has given me the freedom to pursue my interests, and provided invaluable insights while he guided my research. Also, I could not have completed this thesis without his infinite tolerance. Having two children while pursuing a Ph.D. is difficult and almost impossible without a supportive adviser. He has given me leeway and has been very understanding of my responsibilities and choices as a mother, as I tried not to alienate my work or my children.

I would like to express gratitude to Professor Laxmikant Kale, Professor Andreas Klöckner and Professor Franz Franchetti for being on my dissertation committee and for their critical feedback that helped shape my research.

I would like to thank all my friends here at University of Illinois at Urbana-Champaign (UIUC) for being with me, supporting me and having fun together while we cruise through graduate school. I would also like to thank my old friends Manisha, Vijetha, Rasha, Aghamarshan and Bharadwaj for being with me through all these years.

I would like to thank Anine Singh for rekindling my passion for dance, and Miss Sharon, Miss Kayla and Miss Monic for taking care of my son Srirama, while I was at work.

I cannot express in words the gratitude I have for my family for their love, care and support throughout my Ph.D. I cannot fathom the sacrifices my mother made to reach out and support me in times of need, and I wonder if I could have done the same in her place. I can never forget the trouble my father had to go through to take care of the children during a pandemic that wrecked havoc across the globe. I feel very lucky to have parents-in-law who are supportive of my work, who took time out of their busy schedules, and came to the United States to help me and my husband work on our research, even while they had to battle their own health issues. My husband Raghavendra has been a pillar of support through thick and thin, and I can't thank him enough for the troubles he put himself through to give me time to finish my dissertation. I would like to thank my brother Raghu Teja, his wife Harsha Sree, my brother-in-law Viswanatha Srinivas and his wife Aishwarya, for their love, support and the fun times we spent together. I would like to thank my grandmother for her help in taking care of my children. At her age, it was no mean task.

I owe this dissertation to my two children, Srirama Prahlada and Ameya Dakshayani, who were born during my Ph.D. My son has been very patient, caring and understanding, always waiting for me to find time to spend with him. It astonishes me how maturely he has handled the situation as a four year old, and I am extremely proud of him. I can't forget the cries of my daughter, as I shut the door to get some time to work.

I would like to thank my teachers at school, college, Indian Institute of Technology (IIT) Kharagpur, and UIUC, who have taught me invaluable lessons and shaped me into who I am today.

Lastly, I would like to thank the wheel of time to weave my life the way it willed, for making me come to this point in time through a million little nudges.

# TABLE OF CONTENTS

| СНАРТ        | TER 1    INTRODUCTION    INTRODUCTION               | 1        |

|--------------|-----------------------------------------------------|----------|

| 1.1          | Array Representation of Computations                | 1        |

| 1.2          | Code for Distributed Memory Systems                 | 2        |

| 1.3          | Overview of the Ideas in this Dissertation          | 4        |

| 1.4          | Contributions                                       | 4        |

| 1.5          | Thesis Organization                                 | 5        |

| СНАРТ        | TER 2    HIGH LEVEL LANGUAGE DESIGN                 | 6        |

| 2.1          | Grammar                                             | 8        |

| $2.1 \\ 2.2$ |                                                     | 12       |

| 2.2<br>2.3   |                                                     | 13       |

| 2.3<br>2.4   | 1 1 1                                               | 13       |

| 2.4<br>2.5   | J I                                                 | 16       |

| $2.5 \\ 2.6$ | •                                                   | 17       |

| $2.0 \\ 2.7$ | 0                                                   | 18       |

| $2.1 \\ 2.8$ |                                                     | 20       |

|              |                                                     | 20<br>21 |

| 2.9          | 0                                                   |          |

| 2.10         | User Functions                                      | 23       |

| СНАРТ        | TER 3    INTERMEDIATE REPRESENTATIONS    1          | 24       |

| 3.1          | Rationale for Multiple Intermediate Representations | 24       |

| 3.2          | High Level Intermediate Representation (HLIR)       | 25       |

| 3.3          |                                                     | 32       |

| 3.4          |                                                     | 35       |

| 3.5          | -                                                   | 41       |

| 0.0          | -                                                   |          |

| СНАРТ        | YER 4    COMPILATION PROCESS                        | 46       |

| 4.1          | Lexer and Parser                                    | 46       |

| 4.2          | Type Analysis                                       | 46       |

| 4.3          | HLIR to MLIR Translation                            | 48       |

| 4.4          | MLIR Node Merging                                   | 48       |

| 4.5          | Grid Creation                                       | 57       |

| 4.6          | Partitioning and Mapping                            | 58       |

| 4.7          | MLIR Algorithm Selection                            | 61       |

| 4.8          |                                                     | 61       |

| 4.9          |                                                     | 66       |

| 4.10         |                                                     | 77       |

|              |                                                     | 78       |

|              |                                                     | 78       |

|              |                                                     | 80       |

| CHAPTER 5 USING VAANI                                                                                       | . 87           |

|-------------------------------------------------------------------------------------------------------------|----------------|

| 5.1 Specification $\ldots$ | . 87           |

| 5.2 Compilation Script                                                                                      | . 87           |

| 5.3 Execution $\ldots$     | . 88           |

| 5.4 Alternate Versions                                                                                      | . 88           |

| CHAPTER 6 EXPERIMENTAL FRAMEWORK                                                                            | . 98           |

| CHAPTER 7 EVALUATION                                                                                        | . 99           |

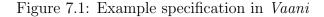

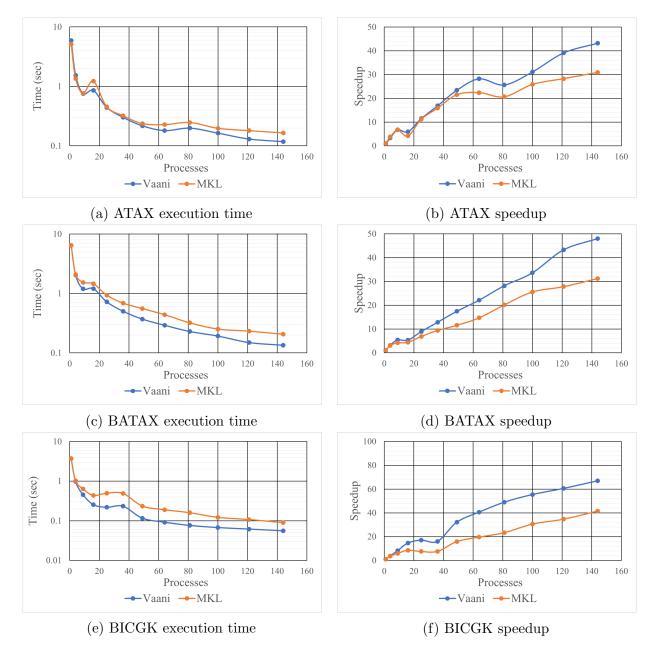

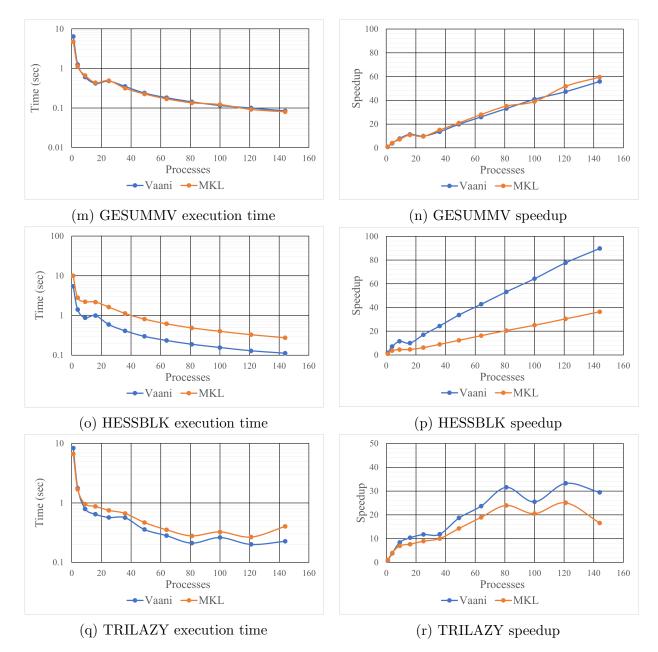

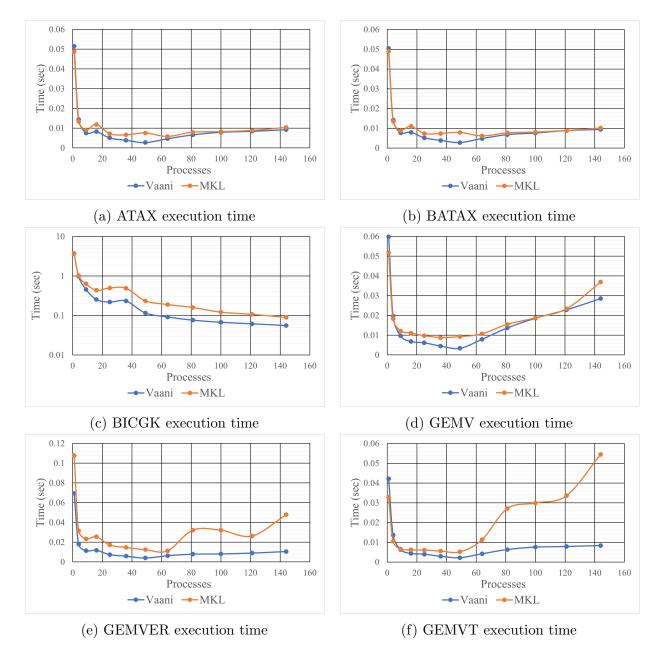

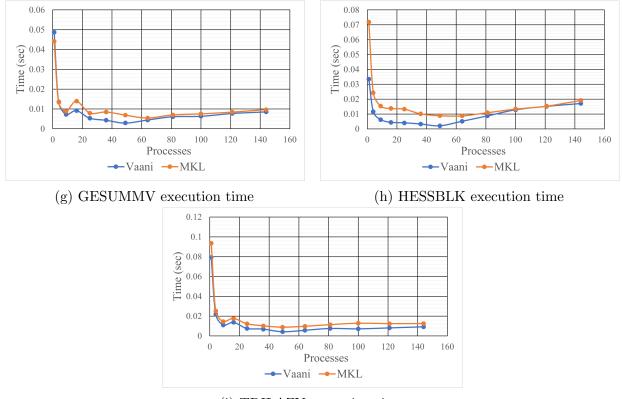

| 7.1 BLAS-Like Operations                                                                                    | . 99           |

| 7.2 Stencil Computations                                                                                    | . 100          |

| 7.3 Iterative Computations                                                                                  | . 100          |

| CHAPTER 8 RELATED WORK                                                                                      | . 114          |

| 8.1 Related Systems                                                                                         |                |

| 8.2 Related Components                                                                                      | . 119          |

| CHAPTER 9 FUTURE WORK                                                                                       | . 122          |

| 9.1 Operation Support                                                                                       |                |

|                                                                                                             | • 144          |

| 9.2 User Options and Optimizations                                                                          |                |

| <ul> <li>9.2 User Options and Optimizations</li></ul>                                                       | . 122          |

|                                                                                                             | . 122<br>. 122 |

# **CHAPTER 1: INTRODUCTION**

Array computations form the crux of many science and engineering applications, and can be succinctly represented in a very high-level notation. However, these codes are written today in C/C++ or Fortran for distributed memory systems using MPI. Supercomputers have different types of nodes and interconnects, and program optimization needs to be tailored to suit each set of target machines. The selection of algorithms, data layout, mapping and optimizations are interdependent and modifying one of them may typically require a complete rewrite of the application.

The following sections describe the representation of computations in high level notation and in C using MPI.

# 1.1 ARRAY REPRESENTATION OF COMPUTATIONS

C = A \* B

A significant portion of scientific and high performance computing use multi-dimensional arrays as primary data structures, and perform operations on the arrays that can be represented with an array view of the structure, as opposed to the scalar, element-by-element view provided in C/C++ or Fortran. These array representations are succinct, clear and easy to maintain and modify. The programmer intent and the core computation specification is available in this representation. Figure 1.1 shows a simple matrix multiplication written in MATLAB (left side) and C (right side). Straightforward C code is already much longer than the corresponding MATLAB code, but for high performance, it needs to be even longer since matrix multiplication benefits from two levels of blocking (possibly multiple levels of blocking), loop unrolling, vectorization and other optimizations, which tend to obfuscate the code. On the other hand, in C, we know exactly how the data is stored and accessed, possible

| <pre>for(int i = 0; i &lt; m; i++) {     for(int j = 0; j &lt; n; j++) {</pre> |

|--------------------------------------------------------------------------------|

| C[i][j] = 0;                                                                   |

| for(int $k = 0; k < r; k++$ ) {                                                |

| C[i][j] += A[i][k]*B[k][j];                                                    |

| }                                                                              |

| }                                                                              |

| }                                                                              |

Figure 1.1: Matrix multiplication in MATLAB and C

optimizations to perform, and their impact on performance. MATLAB does everything under the hood, and the user typically does not have much control over the performance.

# 1.2 CODE FOR DISTRIBUTED MEMORY SYSTEMS

Single Program Multiple Data (SPMD) programming style using MPI with C/C++ or Fortran is the most commonly adopted style to program for distributed memory systems. This requires the data to be manually partitioned across the processes, and communication needs to be explicitly specified using sends and receives for inter-process communication. The already long C code from Figure 1.1 becomes significantly more complex with explicit partitioning and data transfers as shown in Figure 1.2. It must also be noted that this example is already a simplified version, that make use of a simple algorithm (Cannon's algorithm) and assumes square matrices on a square grid. The choice of algorithms affect performance, and in this case, we can have 1D, 2D or 3D partitioning, with different algorithm choices in each of these partitioning schemes, where different matrices need to be communicated. For example, in 2D partitioning, we can keep either A, B or C in place, and move the other two matrices around to perform the computation. Again, the moving matrices can be broadcast step-by-step or moved around cyclically, as in Cannon's algorithm.

In this setting, the programmer must spend time in low level details, like index computations, buffer management, etc. in addition to the time consumed by the high level design decisions like the choice of partitioning, the choice of optimizations, etc. Further, modifying the code from one set of partitioning and optimization choices to another requires a complete rewrite of the program. The problem is exacerbated if we add the conventional optimizations mentioned above, like tiling, unrolling and vectorization to the MPI version.

Hybrid programming, combining distributed memory MPI models with shared memory paradigms like OpenMP are frequently used to find the optimum performance. MPI needs explicit communication, and can be expensive to use within the same node, while OpenMP threads are light weight. Computations which require data replication on each process benefit from this model, for example, stencil computations with ghost layers. Again, this adds another layer of optimizations, and thus complicates the design and implementation of programs significantly.

```

// Initial shuffle

MPI_Irecv(Ain[0], myrc*myrc, MPI_DOUBLE,

(col+row)%pp, pp, commRow, &req[0]);

MPI_Isend(Aout[0], myrc*myrc, MPI_DOUBLE,

(col+pp-row)%pp, pp, commRow, &req[1]);

MPI_Irecv(Bin[0], myrc*myrc, MPI_DOUBLE,

(row+col)%pp, pp, commCol, &req[2]);

MPI_Isend(Bout[0], myrc*myrc, MPI_DOUBLE,

(row+pp-col)%pp, pp, commCol, &req[3]);

MPI_Waitall(4, req, sts);

for(int l = 0; l < pp; l++) {</pre>

swapMatrix(&Ain, &Aout);

swapMatrix(&Bin, &Bout);

for (int i = 0; i < myrc; i++) {</pre>

for (int j = 0; j < myrc; j++) {</pre>

for (int k = 0; k < myrc; k++) {

Cl[i][j] += Aout[i][k] * Bout[k][j];

}

}

}

MPI_Irecv(Ain[0], myrc*myrc, MPI_DOUBLE,

(col+1)%pp, l, commRow, &req[0]);

MPI_Isend(Aout[0], myrc*myrc, MPI_DOUBLE,

(col+pp-1)%pp, l, commRow, &req[1]);

MPI_Irecv(Bin[0], myrc*myrc, MPI_DOUBLE,

(row+1)%pp, l, commCol, &req[2]);

MPI_Isend(Bout[0], myrc*myrc, MPI_DOUBLE,

(row+pp-1)%pp, l, commCol, &req[3]);

MPI_Waitall(4, req, sts);

}

```

Figure 1.2: Matrix multiplication in C+MPI using Canon's algorithm

# 1.3 OVERVIEW OF THE IDEAS IN THIS DISSERTATION

The very high-level notation used in this thesis provides a clear and succinct representation of a computation that is easy to maintain and modify. However, this lacks the flexibility to decide the placement of data and its corresponding optimizations. The main idea of this dissertation is to define a high level array notation language that can be used to create high performance code by following through a series of intermediate representations that lower the high level input to optimized C code with MPI. The layered approach provides an intuitive and clear transformation path, providing the users with an interface to transform the code based on high-level decisions on how the computation must be partitioned and mapped, the set of optimizations or strategies to adopt, without having to deal with the low-level details such as the generation of actual send and receive calls, index manipulations, etc.

To this effect, we define four intermediate representations (IR). High Level IR (HLIR) represents computations on arrays using a set of predefined operators. At this level, our system performs optimizations using symbolic computation and simplification. Mid level IR (MLIR) represents computations based on the data access patterns. During the translation from HLIR to MLIR, operations are categorized as Map, Stencil, Reduce/Scan, Multiply, etc. Low level IR (LLIR) represents local computations and communication, after data and computations are partitioned onto a virtual process grid. This level still retains a high level notation of the computation and communication. C level IR (CLIR) takes this one step further and represents the computation and communication in near C notation, using loops with index sets and instruction blocks; and lower level communication nodes.

We provide an interactive interface to the intermediate representations to lower a computation specified in the high level notation to MPI+C code. We also provide a user-guided tuning approach to tune the generated code to a target machine, by allowing the user to select parameterized optimizations and partitioning, and using autotuning to select the best values for a given input and machine size.

# 1.4 CONTRIBUTIONS

This dissertation introduces a framework called *Vaani* to generate efficient distributed memory code from high level specifications, while providing flexibility and transparency to the internal transformations in the process of generating the final code. This work proposes a layered approach to code transformation tailored for distributed memory systems that provides an interactive interface to generate efficient code. The main contributions of this dissertation are:

- 1. Design of a high-level array notation language to represent computations, particularly recurrences and stencil computations

- 2. Design of a series of intermediate representations to provide an interface to code generation

- 3. Development of a scripting language strategy to generate code from a high-level specification

# 1.5 THESIS ORGANIZATION

The rest of the thesis is organized as follows. Chapter 2 details the high level input language to the framework *Vaani*. Chapter 3 provides detailed description of the intermediate representations used in *Vaani*, and the rationale for choosing them. Chapter 4 discusses the compilation process and code generation. Chapter 5 describes the process of generating a program using *Vaani*. Chapters 6 and 7 describe the experimental setup and the evaluation of *Vaani* respectively. Chapter 8 explains the related work. And finally, chapters 9 and 10 explore future possibilities and conclude the thesis.

# CHAPTER 2: HIGH LEVEL LANGUAGE DESIGN

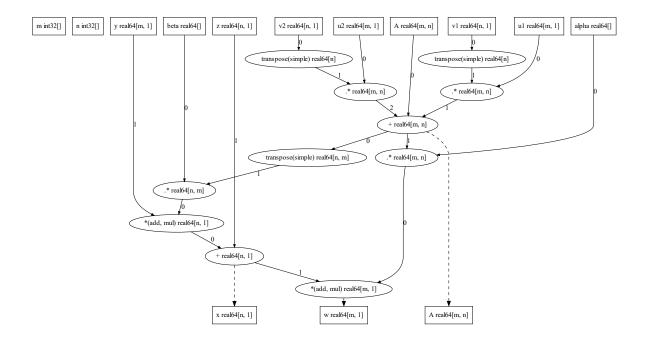

Vaani uses a very high-level array notation with a strong typing system to specify computations as input to the system. The language design takes ideas from existing languages that support array operations, like MATLAB [1] and NumPy [2], but does not adopt either of them as is, to provide a coherent notation that is succinct, clear and expressive. Figure 2.1 has a few examples to demonstrate the syntax and structure of the language.

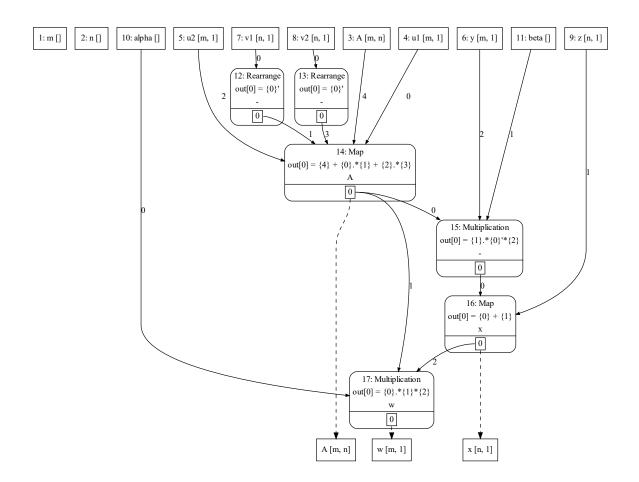

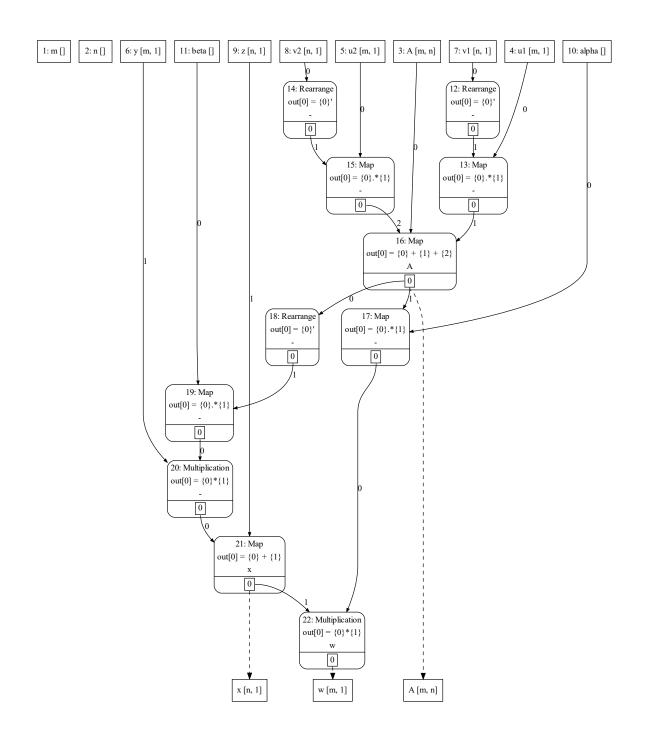

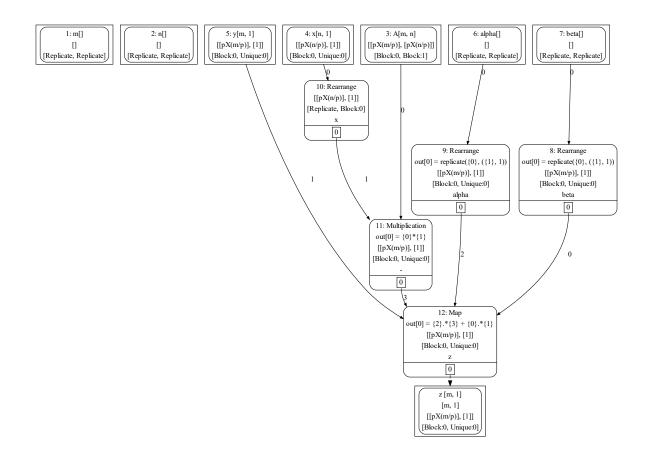

GEMVER (Figure 2.1a) is a program that takes a matrix A of size  $m \times n$ , three column vectors u1, u2, and y of size m (interpreted as  $m \times 1$ ), three column vectors v1, v2 and zof size n (interpreted as  $n \times 1$ ), and two scalars *alpha* and *beta* as inputs and gives three outputs A, x and w. Here, A is specified as inout, indicating it is both an input and an output to the system. A is updated with two outer products specified by the expressions u1 \* v1' and u2 \* v2', where the "" indicates a transpose. Then x is computed by performing a scaled matrix-vector multiplication with the matrix A transposed and the input vector y, and added to the input vector z. w is again computed by a scaled matrix-vector product.

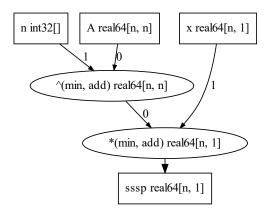

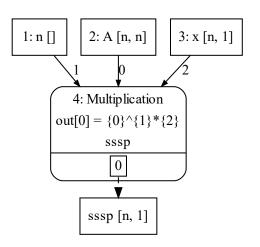

SSSP (Figure 2.1b) is a combination of matrix-power and matrix-vector multiplication with custom additive and multiplicative operators. Here, a square matrix A of size  $n \times n$ , a column vector x of size  $n \times 1$  are taken as inputs, and sssp is declared as an output. ssspis computed using a custom power operator '^' where the additive operator is min and the multiplicative operator is +. Here the matrix A is raised to the power of n with these custom operators, and again multiplied to x with the same custom operators as specified by the \*(min, +). This application, when provided with an adjacency matrix A where each element A[i, j] indicates the cost between nodes i and j if a path exists, and a very large number (that can be treated as infinity in this context) otherwise, and the vector x has the same very large number all over, except one node k that has a 0, then the vector  $A^n x$  gives the shortest path costs from the node k [3].

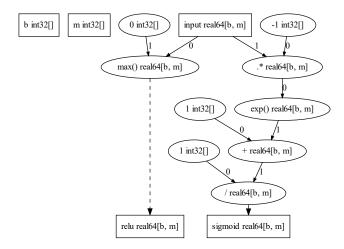

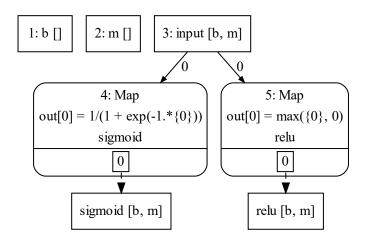

Activation (Figure 2.1c) represents two commonly used activation functions relu and sigmoid in deep neural networks. Here, the functions max and exp are maximum and exponential respectively. These functions and the other operators are applied to each element of the argument/operand matrices.

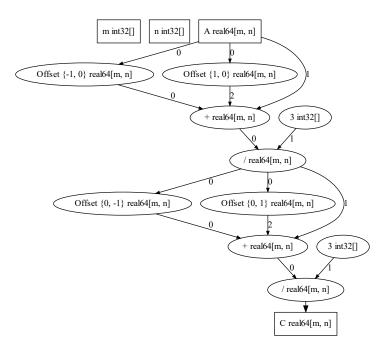

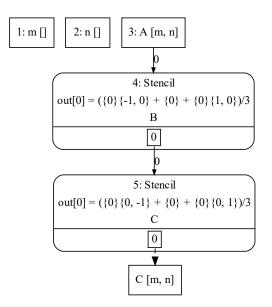

Blur (Figure 2.1d) is a  $3 \times 3$  box filter represented as two  $3 \times 1$  and  $1 \times 3$  filters in the x and y dimensions. Here, it takes a matrix A as input and gives a matrix C as the output, where the intermediate matrix B is a 3-point stencil computation in the first dimension, and the final result is a 3-point stencil computation in the y direction. Here, the curly brackets are used to indicate the relative offsets of the stencil.

```

program GEMVER

inout A matrix(m, n, real64)

in u1, u2, y cvector(m, real64)

in v1, v2, z cvector(n, real64)

in alpha, beta scalar(real64)

out x, w

A = A + u1*v1' + u2*v2'

x = beta*A'*y + z

w = alpha*A*x

```

(a) GEMVER: BLAS Level 2

```

function Activation

in input matrix(b, m, real64)

out relu, sigmoid

relu = max(input, 0)

sigmoid = 1/(1 + exp(-input))

```

(c) Activation: Some activation functions

```

program Jacobi2D

in A matrix(m, n, real64)

in iter scalar(int32)

out B

B = rec B [iter] {

B = (B{-1} + B{-1;0,1}

+ B{-1;0,-1} + B{-1;1,0}

+ B{-1;-1,0})/5

with boundary=periodic

} with B[0] = A

```

(e) Jacobi2D: Jacobi stencil computation

```

program SSSP

in A matrix(n, real64)

in x cvector(n, real64)

out sssp

sssp = A^(min, +)n *(min, +) x

```

(b) SSSP: Matrix power with custom operators

function Blur in A matrix(m, n, real64) out C B = (A{-1,0} + A + A{1,0})/3 C = (B{0,-1} + B + B{0,1})/3

(d) Blur:  $3 \times 3$  blur as  $3 \times 1$  and  $1 \times 3$  passes

```

program Gauss2D

in A matrix(m, n, real64)

in iter scalar(int32)

out B

B = rec B [iter] {

B = (B{-1} + B{-1;0,1}

+ B{0;0,-1} + B{-1;1,0}

+ B{0;-1,0})/5

with boundary=none

} with B[0] = A

```

(f) Gauss2D: Gauss-Siedel stencil computation

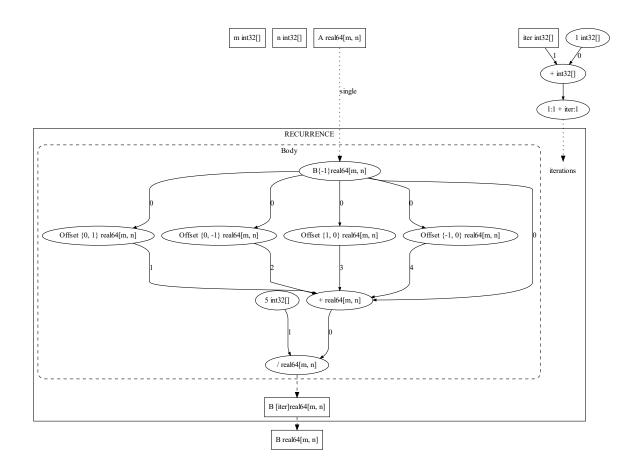

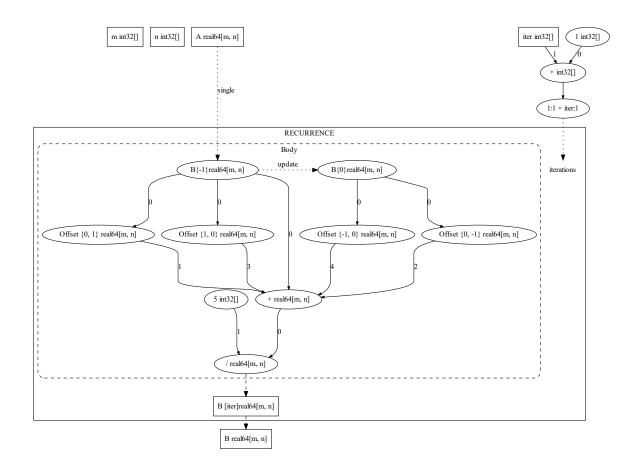

Jacobi2D (Figure 2.1e) is a two dimensional Jacobi 5-point stencil computation for a fixed number of iterations, while Gauss2D (Figure 2.1f) is a similar computation using Gauss-Siedel iterations. Here, both programs take a matrix A of size  $m \times n$  and a scalar integer *iter* as inputs. Matrix B is declared to be the output of the system. These programs use a novel recurrence construct to specify recurrences to compute new values of B. The recurrence of B is initialized with the matrix A in the with clause B[0] = A, and the value of B in the  $i^{th}$ iteration is computed from the B in  $(i-1)^{th}$  iteration by using the assignment statement in the body of the recurrence. Here, the numbers in the curly braces are divided by a semicolon, and the first number indicates a temporal offset (offset in the iteration space of the recurrence), while the ones following the ';' indicate spatial offsets (offsets in the iteration space of the array). It can be observed that to create a Gauss-Siedel iteration, one needs to change the temporal offset for some of the terms from -1 to 0 to indicate current iteration. Here, the 0 in  $B\{0; 0, -1\}$  and  $B\{0; -1, 0\}$  together create a Gauss-Siedel expression from the top-left to the bottom-right corner of the matrix. Also, the boundary clause in Jacobi2D (Figure 2.1e) indicates that a periodic boundary condition is applied to the computation, while that in Gauss2D (Figure 2.1f) indicates that the boundary is ignored.

Vaani generates code in the form of either a stand alone complete program, reading inputs from and writing outputs to files, or as functions which assume an MPI environment already running and the inputs and outputs spread across the process grid as specified in the code generation phase. For the functions, Vaani generates setup and teardown functions, and a function to perform the computation. These C functions can be called from another C program, such that the setup function must be called first, and then its output is an input to the computation function, which can be called multiple times, and then the teardown function is called. In Figure 2.1, GEMVER, SSSP, Jacobi2D and Gauss2D are programs, whereas Blur and Activation are functions, as identified by the first keyword **program** or **function**.

Vaani supports element-by-element operations, stencil operations, matrix products and powers, transpose, reductions, rearrangements and recurrences. It also supports user declared and user defined functions. The following sections describe their syntax and semantic behavior in detail.

# 2.1 GRAMMAR

Figure 2.2 presents *Vaani*'s grammar. The terms in angular brackets (like  $\langle program \rangle$ ) are non-terminal symbols, characters in quotes (like 'program' and ':') are keywords and accepted symbols, and capital character strings (like ID and CONSTANT) are terminal symbols.

```

\langle program \rangle ::= \langle header \rangle \langle declaration \rangle + \langle statement \rangle +

\langle header \rangle ::= \text{'program'} [ID]

'function' ID

\langle declaration \rangle ::=  'in' ID (', 'ID)* \langle objtype \rangle

'inout' ID (', 'ID)* (objtype)

'out' ID (', 'ID)* [\langle objtype \rangle]

\langle objtype \rangle ::= 'scalar' '('[\langle datatype \rangle]')'

['vector' | 'cvector' | 'rvector'] '(' \langle expr \rangle [', ' \langle datatype \rangle] ')'

'matrix' (' (expr) [', ' (expr)] [', ' (datatype)] ')'

'tensor' (' [\langle datatype \rangle] ')'

'tensor' (' \langle expr \rangle (', ' \langle expr \rangle)* [', ' \langle datatype \rangle] ')'

\langle datatype \rangle ::= 'bool' | 'int8' | 'uint8' | 'int16' | 'uint16'

'int32' | 'uint32' | 'int64' | 'uint64'

'real32' | 'real64' | 'complex64' | 'complex128'

\langle statement \rangle ::= \langle assignment \rangle \mid \langle recurrence \rangle \mid \langle function \rangle

\langle assignment \rangle ::= \langle lhs \rangle (`, `\langle lhs \rangle)^* `=` \langle expr \rangle (`, `\langle expr \rangle)^* [`with` \langle stmtblock \rangle]

\langle recurrence \rangle ::= \langle lhs \rangle (`, '\langle lhs \rangle)^* `=` `rec' \langle recheader \rangle [`[' \langle expr \rangle `]'] \langle stmtblock \rangle `with'

\langle stmtblock \rangle

\langle recheader \rangle ::= (ID (', 'ID) * '[' \langle selector \rangle ']') +

\langle stmtblock \rangle ::= \langle statement \rangle | `{' \langle statement \rangle + '}'

\langle function \rangle ::= \langle funcdecl \rangle \mid \langle funcdef \rangle

\langle funcdecl \rangle ::= 'extern' 'func' ID '(' \langle datatype \rangle (', ' \langle datatype \rangle)* ')' '=>' \langle datatype \rangle

\langle funcdef \rangle ::= \text{`func' ID `(' } \langle finputs \rangle \text{')' [`=>' } \langle datatype \rangle ] \text{`=' } \langle funcbody \rangle

\langle finputs \rangle ::= [\langle datatype \rangle] ID (', '[\langle datatype \rangle] ID)^*

\langle funcbody \rangle ::= \langle expr \rangle | `{' \langle statement \rangle^* \langle expr \rangle '}'

```

Figure 2.2: Grammar for the input specification of Vaani.

```

\langle lhs \rangle ::= ID [`[' \langle selector \rangle (`, ' \langle selector \rangle)* `]']

\langle expr \rangle ::= \langle expr \rangle \langle binop \rangle \langle expr \rangle

\langle unop \rangle \langle expr \rangle

\langle expr \rangle "," // transpose

\langle expr \rangle '?' \langle expr \rangle ':' \langle expr \rangle // conditional

\langle id \rangle '(' [\langle arg \rangle (', ' \langle arg \rangle)*] ')' // function call

(expr) '[' (selector) (', '(selector))* ']' // exact indexing

(expr) '{'[INT ';'] INT (', 'INT)* '}' // offset indexing

CONSTANT (INT | FLOAT | BOOL)

ID

\langle arq \rangle ::= \langle expr \rangle | \langle op \rangle

\langle selector \rangle ::= \langle expr \rangle | [expr] ': ' [expr] [': ' [expr]]

\langle op \rangle ::= `+` | `*` | `&&` | `| ]`

\langle binop \rangle ::= `+` | `.+` | `-` | `.-`

(*) [\langle genop \rangle] | (.*) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./) | (./

(\hat{}, \hat{}, [\langle genop \rangle] | (...)

`==' | `!=' | `<=' | `<' | `>=' | `>'

`<<' | `>>'

`&&' | ` | | '

\langle unop \rangle ::= `+' | `-' | `!'

\langle qenop \rangle ::= (' \langle arq \rangle ', ' \langle arq \rangle ')'

DIGIT ::= '0'..'9'

LETTER ::= 'a'..'z''A'..'Z'

INT ::= DIGIT+

DECIMAL ::= DIGIT* '.' DIGIT+

EXP::= ('e' | 'E') ['+' | '-'] INT

FLOAT ::= INT EXP | DECIMAL [EXP]

ID ::= (`_' | LETTER) (`_' | LETTER | DIGIT)^*

```

Figure 2.2: Grammar for the input specification of Vaani (cont.)

| Datatype                                      | Multidimensional array size |

|-----------------------------------------------|-----------------------------|

| scalar()                                      | []                          |

| vector(m)                                     | [m]                         |

| rvector(m)                                    | [m]                         |

| $\operatorname{cvector}(\mathbf{m})$          | [m, 1]                      |

| matrix(m)                                     | [m, m]                      |

| matrix(m, n)                                  | [m, n]                      |

| tensor()                                      | []                          |

| tensor(m,n)                                   | [m, n]                      |

| tensor(m, m, m)                               | $[\mathrm{m,m,m}]$          |

| tensor(m, n, k)                               | $[\mathrm{m,\ n,\ k}]$      |

| $\operatorname{tensor}(n_1, n_2, \dots, n_k)$ | $[n_1, n_2, \dots, n_k]$    |

Table 2.1: Type description and corresponding multidimensional array

\* indicates that the expression preceding it can repeat 0 or more times, and square brackets '[]' represent optional expressions. The | symbol separates options for the same non-terminal.

ID refers to any identifier. *Vaani* identifiers contain upper or lower case letters, underscore, and digits, but cannot start with a digit, similar to the identifiers used by almost all programming languages. The constants supported in *Vaani* are integer, floating point and boolean (true or false). Integers in *Vaani* are currently a sequence of digits. Floating point numbers accept decimal or exponential notation.

A Vaani program starts with the keyword **program** or **function** followed by an identifier to name the program or function. It is followed by a set of declarations of inputs and outputs, discussed in detail in Section 2.3. After the input output specification, a sequence of statements specify the actual computations. There are three types of statements recognized in Vaani: an assignment, a recurrence or a function. An assignment statements takes a list of expressions on the left hand side, a list of expressions on the right hand side, and an optional annotation of statements using the 'with' clause. The statements following the 'with' clause are first executed, then the right hand side expressions are evaluated, and then assigned to the left hand side expressions. Vaani supports assignments to either identifiers or a subset of an identifier (a tensor represented by an identifier) using square bracket indexing (described in Section 2.6.1). Recurrences are described in Section 2.7 and functions are described in Section 2.10.

| Vaani's datatype | C datatype              |

|------------------|-------------------------|

| bool             | bool (stored as a byte) |

| int8             | $int8_t$                |

| int16            | $int16_t$               |

| int32            | $int32\_t$              |

| int64            | $int64_t$               |

| uint8            | $uint8_t$               |

| uint16           | $uint16_t$              |

| unit32           | $uint332_t$             |

| uint64           | $uint64_t$              |

| real32           | float                   |

| real64           | double                  |

| complex64        | float complex           |

| complex 128      | double complex          |

Table 2.2: Primitive datatypes supported in Vaani and their corresponding C datatypes

# 2.2 TYPE SYSTEM

All data in *Vaani* is represented as a multidimensional array, with a fixed primitive datatype and number of dimensions, but the actual size of each dimension can be determined at runtime. For example, matrix 'A' in Figure 2.1a is a two dimensional array with size  $m \times n$ , where m and n can be determined at runtime. These multidimensional arrays are represented in *Vaani* as *tensors* with 0 or more dimensions (0 dimensions implying a scalar element). During declaration, the types can be defined using the keywords scalar, cvector (column vector), rvector (row vector), vector (default vector is a row vector), matrix and tensor (multidimensional). These keywords are provided for ease of declaring the types, but all of them are represented as *tensors* within the context of *Vaani*. Some example usages and their corresponding array sizes are presented in table 2.1.

The currently supported primitive datatypes are boolean (bool), signed (int8, int16, int32, int64) and unsigned (uint8, uint16, uint32, uint64) integers, real (real32 (float), real64 (double)) and complex (complex64 (float), complex128 (double)) numbers. The numbers in the names indicate the number of bits used by the datatype. *Vaani*'s primitive datatypes and their corresponding C datatypes are shown in table 2.2. The array sizes are represented as a list of symbolic expressions providing the size in each of the dimensions. Default scalar types are int32 (as the most commonly added scalars are indices) and all other types are real64 (double).

The input types are explicitly provided by the user and the output and intermediate data types are inferred by *Vaani* during the compilation process. Type analysis using casting rules and symbolic computations is described in Section 4.2. Distribution of these arrays onto a multidimensional grid is described in Section 4.6.

# 2.3 INPUT OUTPUT SPECIFICATION

Input and output to the program/function is required to be explicitly specified in *Vaani* using the keywords in for inputs, out for outputs and inout for variables that are both inputs and outputs. The inputs must be type annotated, and the output types can be deduced from the input types using type analysis (Section 4.2). The type declared in the output must be compatible (as defined in Section 2.4) with the type deduced by the type analysis algorithm, else *Vaani* flags an error.

$\langle declaration \rangle$  of the grammar in Figure 2.2 describes the input output specification for *Vaani*. each declaration begins with a keyword 'in', 'out' or inout; a list of identifiers, and an  $\langle objtype \rangle$  to define the type. *Vaani* allows for the use of undeclared identifiers in the size descriptions and implicitly adds them to the list of inputs with a default type of int32.

For a program, scalar inputs are read from command line arguments, while arrays are read from files. For a function, inputs and outputs are passed as arguments. inout variables are modified in place for functions.

## 2.4 ELEMENT-BY-ELEMENT OPERATIONS

Vaani supports element-by-element operations on compatible arrays using MATLAB like dot '.' representation for certain operations. For example, '.^' represents element-by-element power operation. Most other operations are provided as functions. Table 2.3 lists all the element-by-element operations supported by Vaani, currently. Element-by-element operations can also be performed using user defined or declared scalar functions on compatible arrays as described in Section 2.10. Table 2.4 gives the operator precedence in Vaani, from high to low.

Vaani supports combining arrays of different sizes to perform element-by-element operations. This is supported by replicating the values in an array to match the other input arrays. To check for compatibility of two arrays, the array sizes are extended by appending 1s if needed, to make the two array sizes of equal dimensions. Two arrays are compatible for binary operation if, at each dimension, either the two sizes are statically determined to be equal using symbolic equivalence checking, or atleast one of the two sizes is statically equal to 1. In this case, the array with size 1 is implicitly replicated along this dimension m times to match the size m of the other array. This replication is performed in as many dimensions

| Function            | Description              |  |  |  |

|---------------------|--------------------------|--|--|--|

|                     | Basic Arithmetic         |  |  |  |

| + or .+ Addition    |                          |  |  |  |

| - or                | Subtraction              |  |  |  |

| .*                  | Multiplication           |  |  |  |

| / or ./             | Division                 |  |  |  |

| .^ .                | Power                    |  |  |  |

| min                 | Minimum                  |  |  |  |

| max                 | Maximum                  |  |  |  |

| $\%~{\rm or}~.\%$   | Modulo                   |  |  |  |

| remainder           | Remainder                |  |  |  |

| ceil                | Round up                 |  |  |  |

| floor               | Round down               |  |  |  |

| R                   | elational operations     |  |  |  |

| ==                  | Equal to                 |  |  |  |

| !=                  | Not equal to             |  |  |  |

| <                   | Less Than                |  |  |  |

| <=                  | Less than or equal to    |  |  |  |

| >                   | Greater Than             |  |  |  |

| >=                  | Greater than or equal to |  |  |  |

| ]                   | Boolean Arithmetic       |  |  |  |

| &&                  | Logical and              |  |  |  |

|                     | Logical or               |  |  |  |

| xor                 | Logical xor              |  |  |  |

| !                   | Logical not              |  |  |  |

| Bitwise Operations  |                          |  |  |  |

| bitand              | Bitwise and              |  |  |  |

| bitor               | Bitwise or               |  |  |  |

| bitxor              | Bitwise xor              |  |  |  |

| bitflip Bitwise not |                          |  |  |  |

| <<                  | Left shift               |  |  |  |

| >>                  | >> Right shift           |  |  |  |

| Function                         | Description               |  |

|----------------------------------|---------------------------|--|

| Trigonometric functions          |                           |  |

| sin                              | Sine                      |  |

| cos                              | Cosine                    |  |

| tan                              | Tangent                   |  |

| asin                             | Inverse sine              |  |

| acos                             | Inverse cosine            |  |

| atan                             | Inverse tangent           |  |

| atan2                            | Four quadrant inverse tan |  |

| H                                | Iyperbolic functions      |  |

| sinh                             | Hyperbolic sine           |  |

| $\cosh$                          | Hyperbolic cosine         |  |

| tanh                             | Hyperbolic tangent        |  |

| asinh                            | Inverse hyperbolic sine   |  |

| acosh                            | Inverse hyperbolic cosine |  |

| atanh Inverse hyperbolic tangent |                           |  |

|                                  | Complex functions         |  |

| abs                              | Absolute value            |  |

| phase                            | Phase computation         |  |

| real                             | Real component            |  |

| imag                             | Imaginary component       |  |

| conjugate                        | Conjugate                 |  |

| Exponents and Logarithms         |                           |  |

| exp                              | Exponent                  |  |

| log                              | Logarithm base e          |  |

| log2                             | Logarithm base 2          |  |

| log10                            | Logarithm base 10         |  |

| sqrt                             | Square root               |  |

| cbrt Cube root                   |                           |  |

| Miscellaneous                    |                           |  |

| ?:                               | conditional               |  |

| < id > User functions            |                           |  |

Table 2.3: Element-by-element operations defined in Vaani

| Level                                                   | Operator   | Description                       |  |

|---------------------------------------------------------|------------|-----------------------------------|--|

| 1                                                       | ()         | function call                     |  |

| 2                                                       | []         | exact index                       |  |

|                                                         | {}         | offset index                      |  |

|                                                         | ,          | matrix conjugate transpose        |  |

| 3                                                       | .'         | matrix simple transpose           |  |

| 0                                                       | ^          | matrix power                      |  |

|                                                         | .^         | element-by-element power          |  |

|                                                         | +          | unary plus                        |  |

| 4                                                       | -          | unary minus                       |  |

|                                                         | !          | not                               |  |

|                                                         | *          | general matrix multiplication     |  |

| 5                                                       | .*         | element-by-element multiplication |  |

| 0                                                       | ./ or /    | division                          |  |

|                                                         | .% or $\%$ | mod                               |  |

| 6 .+ or +                                               |            | addition                          |  |

| 0                                                       | or -       | subtraction                       |  |

| 7                                                       | <<         | left shift                        |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |            | right shift                       |  |

|                                                         | <          | less than                         |  |

| 8                                                       | >          | greater than                      |  |

|                                                         | <=         | less than or equal to             |  |

|                                                         | >=         | greater than or equal to          |  |

| 9                                                       |            | equal to                          |  |

|                                                         |            | not equal to                      |  |

| 10                                                      | &&         | logical and                       |  |

| 11                                                      |            | logical or                        |  |

| 12                                                      | ?:         | Conditional                       |  |

Table 2.4: Operator precedence

| Input array sizes Extended array sizes              |                                          | Combined array size |  |

|-----------------------------------------------------|------------------------------------------|---------------------|--|

| Compatible array sizes                              |                                          |                     |  |

| [m, n]<br>[n]                                       | [m, n]<br>[1, n]                         | [m, n]              |  |

| $[m, n, k] \\ [n, 1]$                               | $[{\rm m,  n,  k}] \\ [1,  {\rm n,  1}]$ | [m, n, k]           |  |

| [m, 1]<br>[n]                                       | [m, 1]<br>[1, n]                         | [m, n]              |  |

| $[m, k] \\ [n, 1, k]$                               | [1, m, k]<br>[n, 1, k]                   | [n, m, k]           |  |

| $[m, n] \\ [k, 1, 1]$                               | $[1, m, n] \\ [k, 1, 1]$                 | [k, m, n]           |  |

| Incompatible array sizes                            |                                          |                     |  |

| [m, n]<br>[m]                                       | [m, n]<br>[1, m]                         | Х                   |  |

| $\begin{bmatrix} [m, n, k] \\ [m, k] \end{bmatrix}$ | [m, n, k]<br>[1, m, k]                   | Х                   |  |

Table 2.5: Example compatible and incompatible arrays

as necessary for each of the two arrays to match the two array sizes. This replication has been conventionally termed as a broadcast in NumPy and MATLAB.

The rules stated above are identical to the rules followed by NumPy. This differs from the broadcasting rules of MATLAB, where the 1s are appended to the end (instead of at the beginning) to extend the arrays to equal dimensions, mainly due to the default internal representation of the arrays. MATLAB, being column-major, has the first dimension the quickest changing, where as NumPy, our target language C and hence *Vaani*, being row-major, has the last dimension changing fast.

Table 2.5 provides a few examples of compatible and incompatible array combinations, and the final combined size of the operation.

These rules are extended by applying them pairwise for operations with more operands, like addition and element-by-element multiplication, which support multiple operands.

## 2.5 MATRIX OPERATIONS

Matrix operations (multiplication '\*', power '^', and transpose '', or '.'') are defined for matrices of upto two dimensions. General matrix multiplication and matrix power using user specified additive and multiplicative operations are supported using the operator followed by a pair of operations or user defined scalar binary functions. This is described in the grammar (Figure 2.2) using  $\langle genop \rangle$ . For example, A\*(min,+)B performs a matrix multiplication with minimum as the additive operation and addition as the multiplicative operation, which could be used to perform shortest path computations by using adjacency matrices as the operands [3]. Also, A^(min,+)n performs a similar matrix product n times with A. These operations are used in the example SSSP of Figure 2.1b.

## 2.6 INDEXING

Vaani uses two types of indexing into the arrays, exact and offset indexing.

## 2.6.1 Exact Indexing

Square brackets  $({}^{(i)}, {}^{(j)})$  are used to denote exact indexing into the array, to access individual elements or sub-arrays. *Vaani* supports a triplet notation with [start] : [[stop][: step]] to refer to sub-arrays (here, the square brackets in definition imply optional parameters). The notation implies a list of numbers starting from *start*, ending at *stop* but not including *stop*, and in increments of *step*. The default *step* size is 1, default *start* is 0, and default *stop* is context-dependent, and is the end of an array in the context of indexing. Statically determined constant indices can be negative to refer to the end of the array, but dynamic indices must be positive. For example, consider a matrix **A** of size  $m \times n$ . **A**[0, 0] refers to the first element and **A**[-1,-1] refers to the last element **A**[**m**-1, **n**-1]. **A**[:,0] refers to the first column of **A**, **A**[:, -1] to the last column (**A**[:, **n**-1]), and **A**[i1:j1, i2:j2] to a sub-matrix of **A** where all the values i1, i2, j1, j2 are assumed to be positive integers within the range. **A**[0, ::2] would imply alternate elements in the first row of **A**. This is similar to the notation in NumPy, however, the main difference is that only statically constant negative integers can be negative, while NumPy, being an interpreted language, allows any index to be negative.

## 2.6.2 Offset Indexing

Curly brackets ('{' '}') are used to denote offset indexing, which specifies the offset of the index from an abstract current index, for each element in the array. We use these offsets to represent spatial offsets for stencil computations and temporal offsets for recurrences. For example,  $A{0,1}$  represents the element A[i, j+1] for an abstract current index of [i,j]. Offsets are couple with boundary specifications to determine the range of the operations. Currently supported boundary conditions for *Vaani* are none and periodic. none denotes

that the boundary values are not computed, while periodic indicates the offsets are wrapped around circularly. The same offset index of  $A{0,1}$  for an  $m \times n$  matrix A would have indices of range [0:m, 0:n-1] if boundary is none while the full index range [0:m, 0:n] if boundary is periodic. In the case of periodic boundary condition,  $A{0,1}$  for an actual index of [i, n-1] would imply A[i, 0] by wrapping around to the beginning of the array.

If both spatial and temporal offsets are required, then the offsets are separated by a ';' to differentiate the first temporal offset, and the latter spatial offsets. An example of this indexing is used in Jacobi2D (Figure 2.1e) and Gauss2D (Figure 2.1f).

# 2.7 RECURRENCES

*Vaani* does not support traditional loops, but instead, supports recurrences. *<recurrence>* of the grammar in Figure 2.2 describes the syntax of recurrences. Components of a recurrence are described below.

#### 2.7.1 Output Variables

Output variables are a list of identifiers that are defined within the recurrence whose values will be carried over outside the recurrence. The B after the keyword **rec** in Figures 2.1e and 2.1f are the output variables.

#### 2.7.2 Selectors

Selectors specify both the number of iterations to run, and the values to be saved. An expression selector specifies the number of iterations to be run, and saves the last computed value of the variable. A selector with a ':' operator specifies both the number of iterations to be run, and that values of all iterations are to be saved. This increases the dimension of the variable by 1 from the internal recurrence size. The [iter] after the output variable B in Figures 2.1e and 2.1f are the selectors. Here, starting with the initial values of B, the iterations of the recurrence are run to obtain B[iter]. For example, if the selector had been B[0:iter], then the values of B would be stored for each iteration of B, and the resulting B would have a size of  $iter \times m \times n$ , increasing the dimensions of B. It should be noted here that in order to obtain B[iter], the computation must run for *iter* iterations starting from 1, while to compute B[0:iter], the computation runs for (iter - 1) iterations, as the expression 0:iter excludes *iter*.

Alternatively, a '\*' can be used as a selector, specifying that the recurrence runs to convergence. Since *Vaani* uses fixed array sizes, '\*' cannot be combined with the ':' specification and only the last (converged) value can be saved.

Selectors are combined with the initialization values to obtain the recurrence iterations, and the process is described in Section 2.7.6.

## 2.7.3 Condition

A condition can also be specified such that the iteration is run as long as this condition is true. When combined with '\*' selector, the recurrence is run till this condition is false. Combined with an iteration count, it terminates when either the condition is false or iteration count is reached. Conditional execution is not allowed with ':' selector for the same reason as '\*'.

#### 2.7.4 Body

The body of a recurrence is a list of statements, defining all the output variables in each iteration using variables from previous iterations. The values from previous iterations can be accessed using temporal offsets in the recurrence domain. For example,  $A\{-1\}$  denotes the value of the previous iteration, and  $A\{-2\}$  denotes the value 2 iterations before. For example, fibonacci numbers can be represented using the statement  $F = F\{-1\} + F\{-2\}$ . Temporal offsets can be combined with spatial offsets using the ';' operator. Jacobi2D and Gauss 2D from Figures 2.1e and 2.1f demonstrate the usage of both temporal and spatial offsets to perform iterative stencil computations. The temporal offsets here can only be non-positive integers, while spatial offsets can be any integer constant. The use of 0 as a temporal offset for some of the terms of Gauss2D suggests that the values computed in the current iteration must be used, which implies that a Gauss-Siedel iteration must be performed. The values an error.

#### 2.7.5 Initial Values

The statement block after the 'with' keyword provides the initial values to the recurrence. The initial values can be specified using two ways.

#### Single Iteration Point

The value of a variable at a single constant integer iteration point is specified using square brackets (B[0] in Figures 2.1e and 2.1f). The number of values specified must equal the maximum temporal offset of that variable that is used in the body of the recurrence. For example, if a variable A has temporal offsets of {-1} and {-3}, then three consecutive integer points must be specified.

#### All Iteration Points

The value of a variable for all iteration points can be specified using a ':' operator in square brackets, giving an array of values, where each element is mapped to one iteration (for example, a[:] = A, where A is a 2 dimensional array, would give vector values to a). The number of iterations must match the leading dimension of the array. This specification is only valid for fixed iteration space.

#### 2.7.6 Determination of the Iteration Space

Iteration space is determined by using the indices of the initial values and the selector. The initial values determine the lower bound of the iteration, and the selector specifies the upper bound. For example, in Figures 2.1e and 2.1f, the initial value of 0 specifies the iteration starts from 1, and the selector specifies that the final iteration is iter.

### 2.8 REDUCE/SCAN

Reduction and scan operations are supported in *Vaani* using functions. The function signatures are reduce(Array, [operation, axes]) and scan(Array, [operation, axes]). The operation can be a built-in function  $(+, *, \min, \max, \&\&, ||, xor, bitand, bitor, bitxor)$  or a user-defined function, and the default is addition (+). The axes for reduce can be one or more integers specifying the dimension to reduce along, default is 0. Scan can only be performed in one dimension.

Reduce removes the dimensions along which it is reduced, reducing the dimension of the result array. It is planned to take a user specified boolean to retain the dimensions or not, but is currently not implemented. For example, v = reduce(A, +, 1) on a matrix A of size  $m \times n$  results in a vector v of size m where each element v[i] is the sum of all the elements in the row i of matrix A.

Scan result has the same dimensions as the input array, with the elements in the specified dimension a cumulative of the values. Scan currently performs inclusive scan, and a future boolean to select inclusive or exclusive scan is planned.

### 2.9 REARRANGE

Rearrange functions currently supported in *Vaani* are described below.

#### 2.9.1 Reshape

reshape(array, sz1, sz2, ...) function takes an array A and recasts it as an array of size (sz1, sz2, ..). If the original size of the matrix is  $m_1 \times m_2 \times ... \times m_k$ , this operation flattens the original array to one dimension of size  $m_1 * m_2 * ... * m_k$ , and then recasts it to its new sizes  $sz_1 \times sz_2 \times ... \times sz_j$ . The total size of the array A and the size obtained by the new sizes must statically be equal on symbolic equivalence check, i.e.,  $m_1 * m_2 * ... * m_k = sz1 * sz2 * ... * sz_j$ . For example, an array of size (m, n, k) can be cast as (m\*n, k), (n, 1, k, m) or (m, 1, n, k), but not as (m, m, k) or (p, q) even if m\*n\*k = p\*q at runtime, as *Vaani* cannot determine it statically. Reshape operations are of two types.

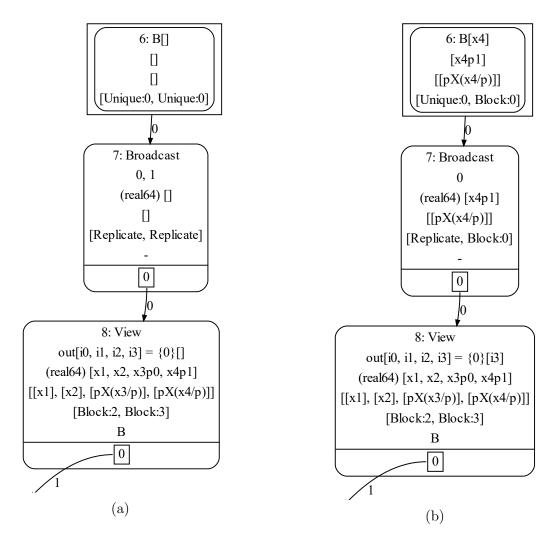

#### Implicit Reshape

This is possible if the original and final array shapes and distributions over the process grid remains the same before and after reshape. This is possible if the reshape adds or removes 1 length dimensions to the array, or combines adjacent sizes where at least one of them is not partitioned over the grid. This reshape does not generate any communication, and is only performed implicitly in the way underlying data is viewed.

### Explicit Reshape

The reshape must be explicit if the final array shape over the process grid differs from the initial array. This reshape involves communication across the process grid.

### 2.9.2 Reorder

reorder(array, order) changes the dimensions of an array to be viewed in the order specified. Matrix transpose is a special case of reorder, where reorder(A, 1, 0) is a simple

|          | expression                                         | original size | result size    |

|----------|----------------------------------------------------|---------------|----------------|

|          | replicate(A, m, n)                                 | [m, n]        | $[m^*m, n^*n]$ |

| Explicit | $\operatorname{replicate}(\mathbf{A}, \mathbf{n})$ | [m, n]        | [m, n*n]       |

|          | replicate(A, k, m, 1)                              | [m, n]        | $[k, m^*m, n]$ |

|          | replicate(A, k, 1, 1)                              | [m, n]        | [k, m, n]      |

| Implicit | replicate(A, n)                                    | [m, 1]        | [m, n]         |

|          | replicate(A, m, 1)                                 | [n]           | [m, n]         |

Table 2.6: Example replicate expressions

matrix transpose. Reorder retains the row or column distribution of the original matrix, but arranges them differently, often leading to a need to explicitly recreate the array. This often involves communication, unless the reorder only changes the order of dimensions not partitioned across the grid.

# 2.9.3 Flip

flip(array, [axis]) reverses the elements in axis dimension, defaulting to 0 if axis is not specified. Flip involves communication to place the data in the correct place.

#### 2.9.4 Replicate

replicate(array, rep1, rep2, ...) replicates the array by the sizes  $rep_i$  specified. This takes the sizes list of the array and the sizes represented by rep, aligns them at the end and appends 1s to make them the same size, and multiplies the terms pairwise to create a new array. Replicate again is of two types, similar to reshape. Table 2.6 shows some examples of replicate, and their final shapes.

## Implicit Replicate

Implicit replicate replicates the array along a dimension that is originally 1. This only has communication to make the array values available on the processes requiring it.

### Explicit Replicate

Explicit replicate is when an array is replicated along a dimension that is not originally 1. This increases the length of a dimension, and hence requires a redistribution of the array.

## 2.10 USER FUNCTIONS

Vaani supports two types of user functions, user declared and user defined functions. These functions can be used as element-by-element operations, as operators for general matrix multiplication and power, and as functions for reduction and scan. Currently, Vaani only supports scalar functions.

# 2.10.1 User Declared Functions

Externally defined scalar C functions can be declared in *Vaani* using the extern keyword. As an example,

```

extern func modadd(int32, int32) => int32

```

introduces a function modadd that takes two integers and returns an integer. *Vaani* declares these functions in the final generated C code as extern functions, and must be coupled with their implementations at compile time.

# 2.10.2 User Defined Functions

Users can also define functions in *Vaani* using statements and expressions supported in *Vaani*. As an example,

# func modadd(int32 a, int32 b) => int32 = { (a + b)%n }

introduces a function modadd that performs modulo addition. Here, the value n, that is not an input to the function, takes the value of n when the function is defined. User defined functions do not need type annotations, the types can be deduced on instantiation. For example, a function

# func square(a) = { a\*a }

introduces a function square that squares a given number where the return type is determined by the type of the argument at each instance.

# **CHAPTER 3: INTERMEDIATE REPRESENTATIONS**

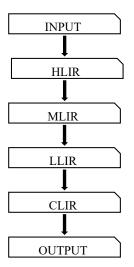

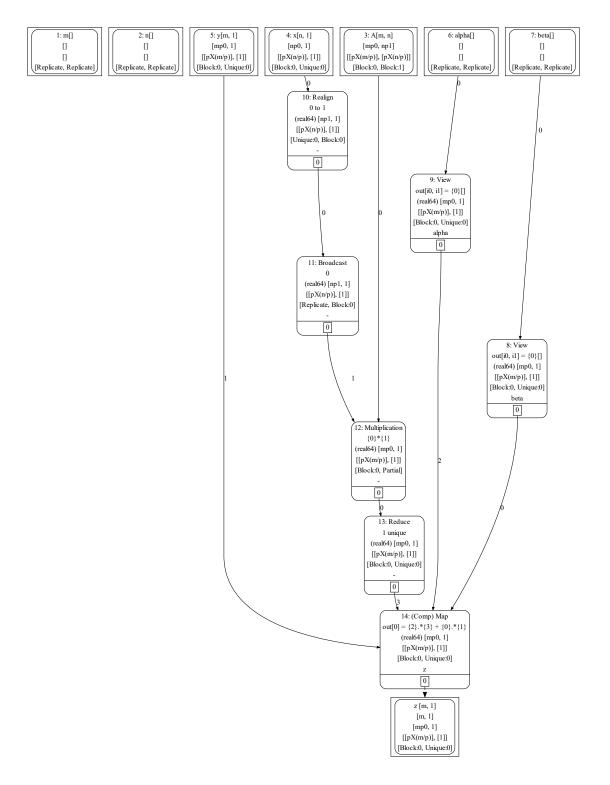

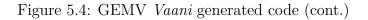

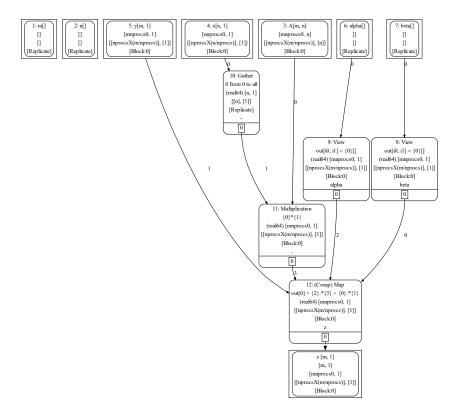

The intermediate representations(IR) of *Vaani* represent the specified computations at varying levels of detail. The representations are designed to enable different types of optimizations at different stages of the compilation. The high-level IR (HLIR) represents the operations on the arrays as specified by the user, the mid-level IR (MLIR) represents computations categorized by the data access patterns, the low-level IR (LLIR) represents the communication and local computation, and the C-level IR (CLIR) is the final step before generating the code, and is in the form of iterations spaces and instruction blocks. The input program is parsed and transformed through these representations as shown in Figure 3.1 before generating the final code. In this chapter, we explore the rationale for this design in Section 3.1 and look at the different IRs in sections 3.2 to 3.5. We provide details of the actual translation in chapter 4.

# 3.1 RATIONALE FOR MULTIPLE INTERMEDIATE REPRESENTATIONS

The design and implementation of a distributed memory program intuitively follows a general pattern. First, a high level computation specification is developed, which is independent of underlying implementation details. Then, the data and computation is distributed onto a process grid. Next, the communication necessary to carry out the computation assuming this distribution is determined. Finally, optimizations for local computations are selected and implemented. This represents a flow in which each step is dependent on the previous step, as a specification is necessary to perform distribution, a distribution is necessary to determine communication, and local computations must be extracted before performing local optimizations. These steps are typically performed in this order, even if a user wishes to backtrack or maintain multiple versions of the final code. Vaani's intermediate representations follow this intuitive pattern, and thus enable the user to intuitively define and refine the computations from a high level representation, breaking them down into simpler and smaller chunks of computation, that lends itself to a varying set of operations and optimizations. In Vaani, the language described in chapter 2 and HLIR provide the implementation independent specification of computations. MLIR is used to partition and distribute data and computation onto a virtual process grid. Communication is introduced on translation from MLIR to LLIR, and local optimizations are performed on LLIR and CLIR.

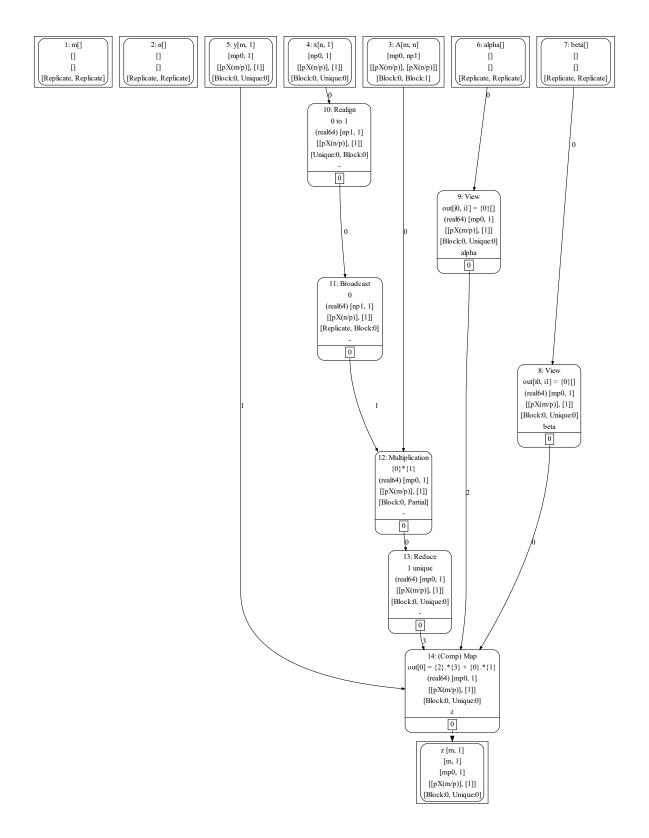

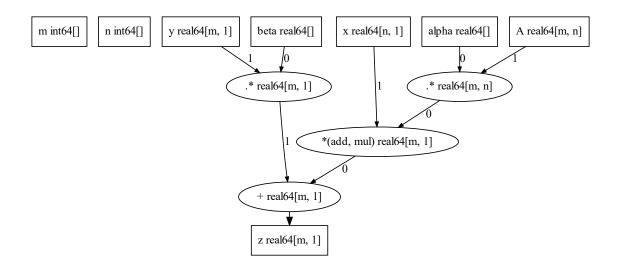

Figure 3.1: Translation through IRs

# 3.2 HIGH LEVEL INTERMEDIATE REPRESENTATION (HLIR)

The high level IR is used to denote the program using arrays as objects with the operations supported in the input language as-is as nodes. This representation has a list of inputs, a list of outputs, and a directed acyclic graph (DAG) connecting the inputs to the outputs, where each node is an operation. These nodes represent all possible computations defined in *Vaani* like element-by-element operations, matrix operations, indexing operations, etc.

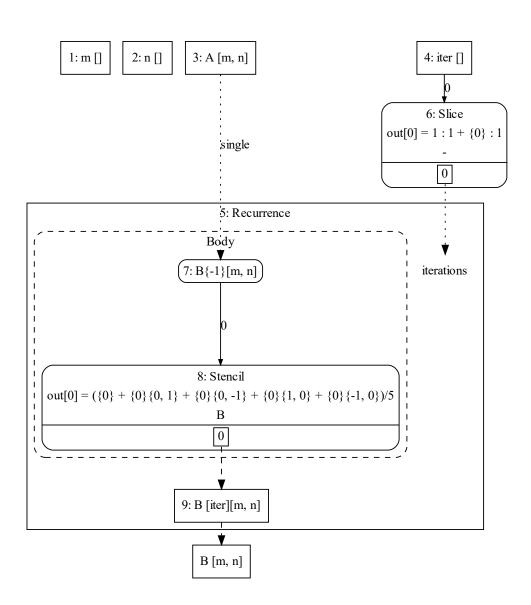

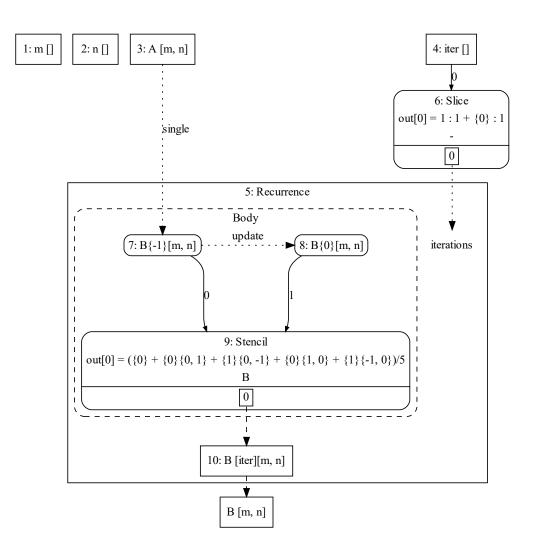

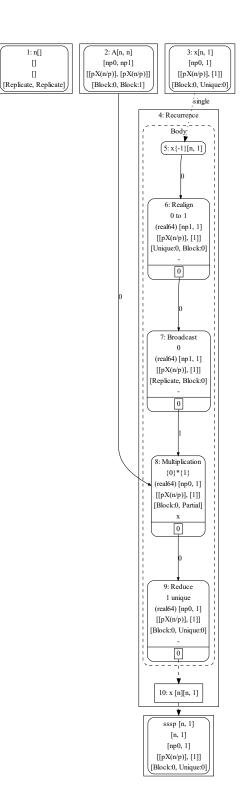

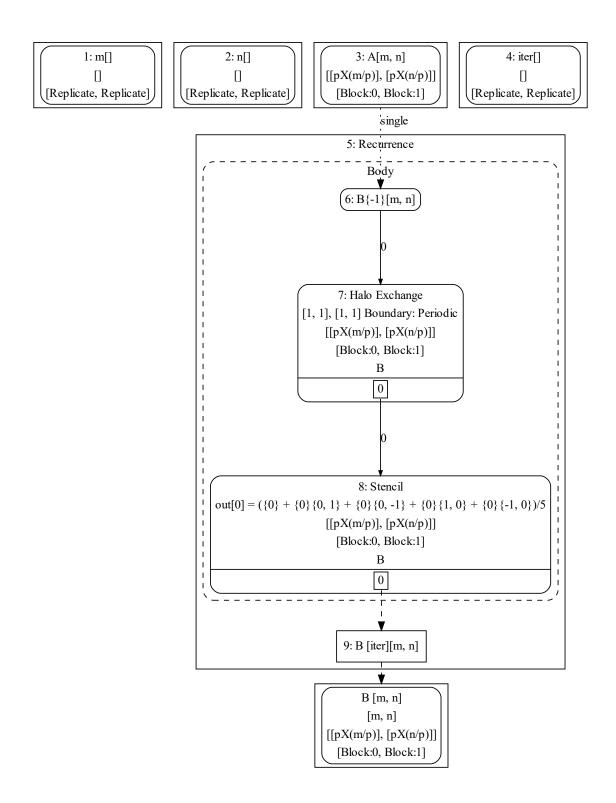

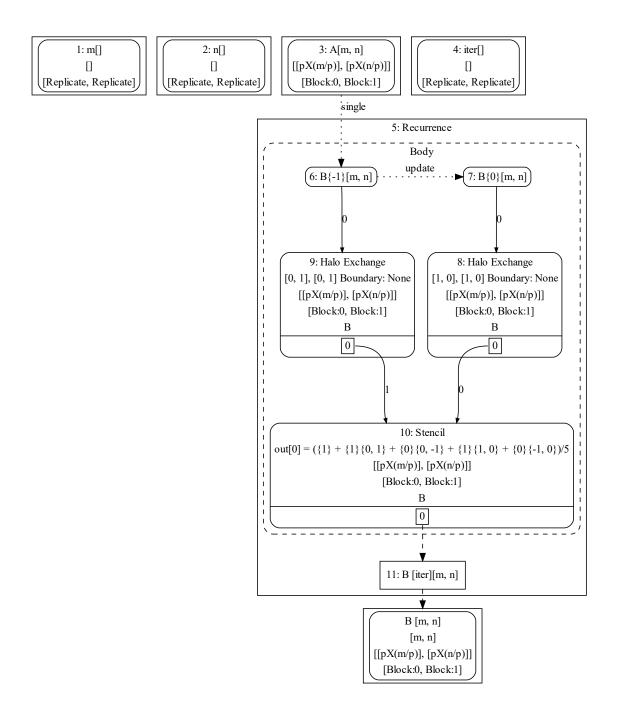

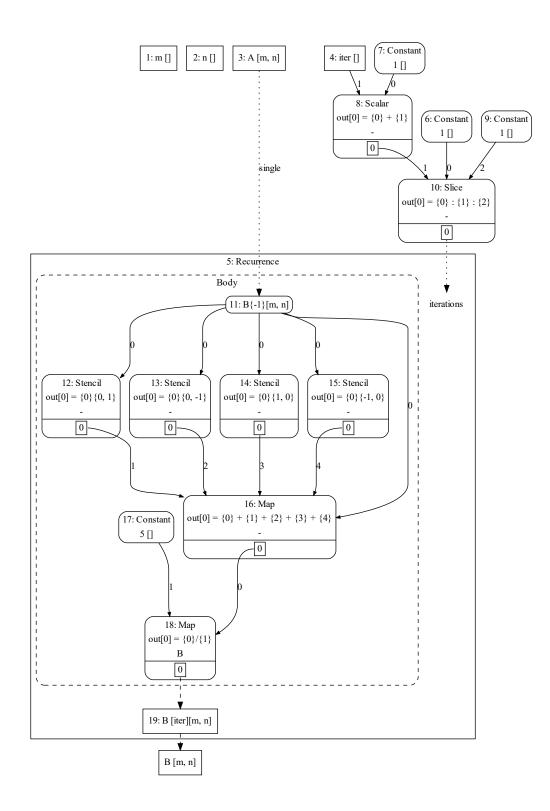

Recurrences are treated as a single node in HLIR, thus avoiding cycles but creating a hierarchical nesting, as shown in Figures 3.6 and 3.7 for Jacobi2D and Gauss2D, respectively. Recurrences have a set of recurrence variables and a set of recurrence outputs. Recurrence variables are the variables that are considered inputs to each iteration of the recurrence and have an initialization edge from outside the recurrence. Recurrence outputs are the outputs defined in each iteration of the recurrence, and they have an edge out of the recurrence. There is a loop in the recurrence, where the outputs of the current iteration are the inputs of the next iteration. This is ignored, and the body of the recurrence is treated as a DAG for the translation. Eventually, buffer allocation and code generation make sure that the output to input match is correctly performed in the final code. This input to output match can be performed unambiguously, as the temporal offsets of recurrences are constant integers. Nested recurrences create a hierarchy of recurrence nodes, where an inner recurrence is considered a statement in the outer recurrence.

HLIR is generated by parsing the input specification into an abstract syntax tree (AST) and performing type and shape analysis to annotate the intermediate nodes with a datatype and symbolic array size. Symbolic expression simplification, strength reduction and common

Figure 3.2: GEMVER HLIR

Figure 3.3: SSSP HLIR

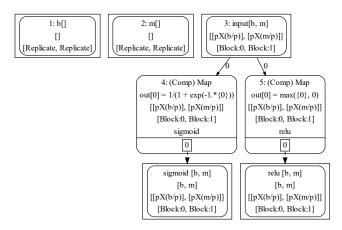

Figure 3.4: Activation HLIR

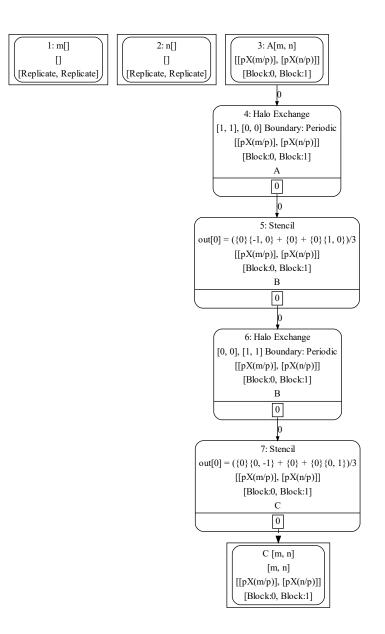

Figure 3.5: Blur HLIR

Figure 3.6: Jacobi2D HLIR

Figure 3.7: Gauss2D HLIR

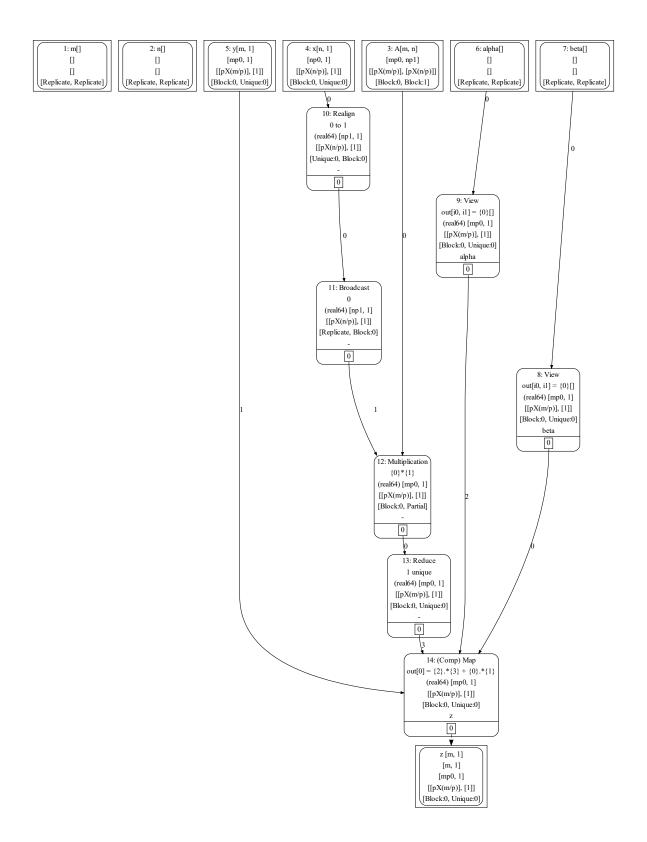

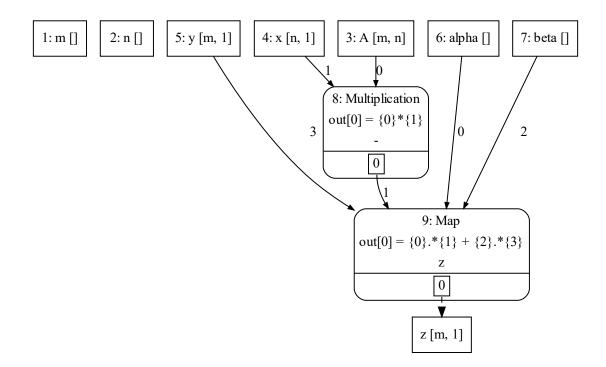

Figure 3.8: GEMVER MLIR

sub-expression elimination are possible optimizations at this level.

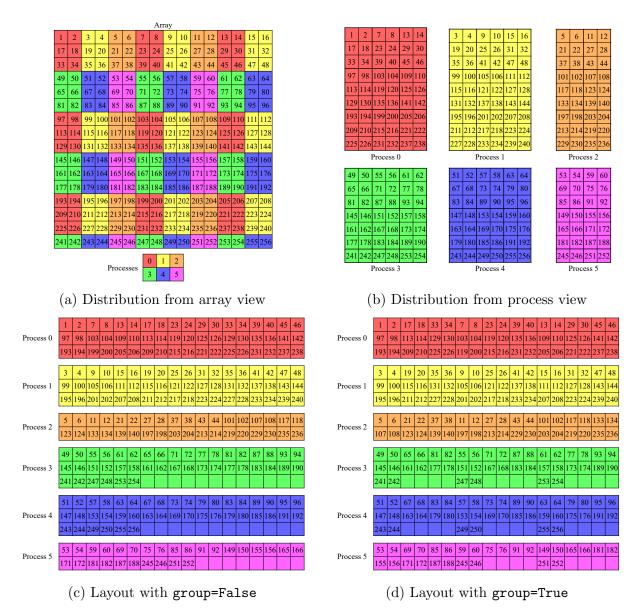

Figures 3.2 through 3.7 present the HLIR versions of the sample examples from Figure 2.1. In each of these examples, the topmost rectangular nodes represent the inputs, the bottom rectangular nodes represent the outputs, and the intermediate ovals represent computation nodes. A solid arrow brings all the required inputs to a computation node. These arrows are numbered to specify the order of the inputs to a node.

Inout parameters and assignment operations are technically expected to introduce cycles. However, *Vaani* treats them to be unique nodes in HLIR and thus do not produce cycles. This information is used in a much later stage (buffer allocation), to possibly reduce the total memory consumption by reusing buffers.

Figure 3.9: SSSP MLIR

Figure 3.10: Activation MLIR

Figure 3.11: Blur MLIR

#### 3.3 MID LEVEL INTERMEDIATE REPRESENTATION (MLIR)

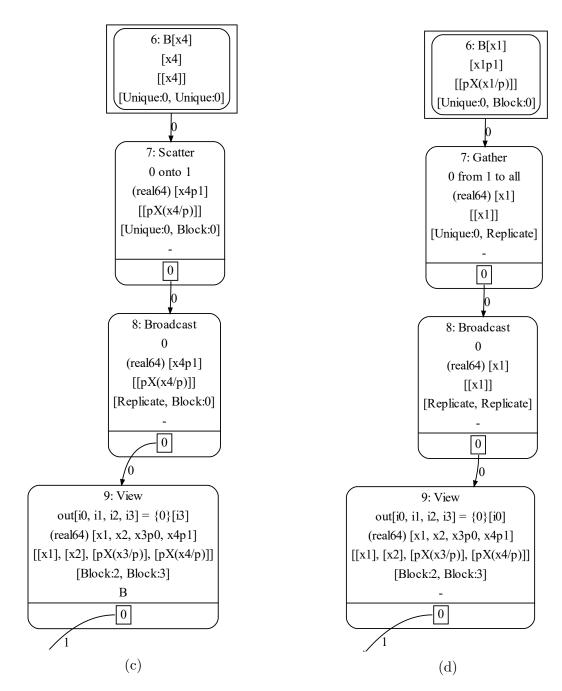

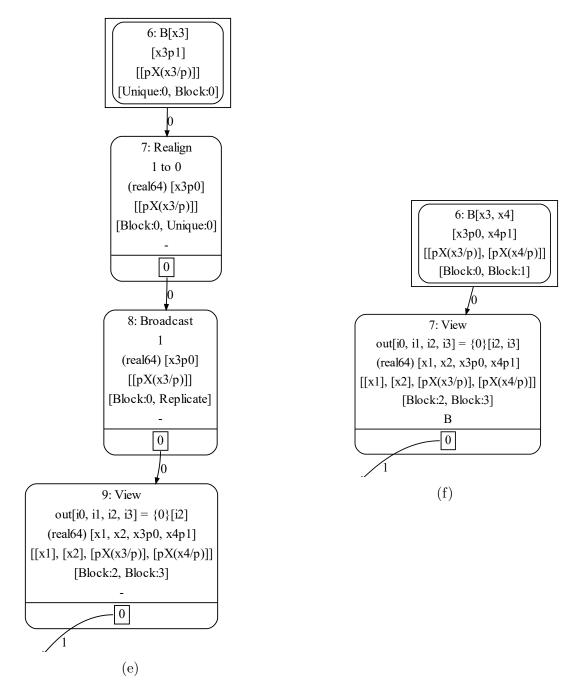

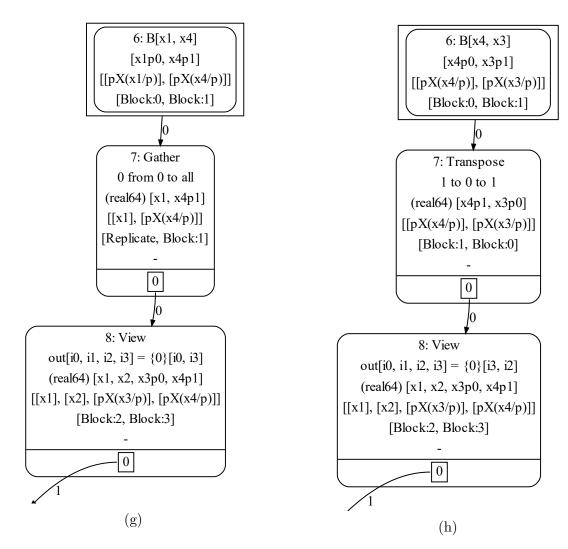

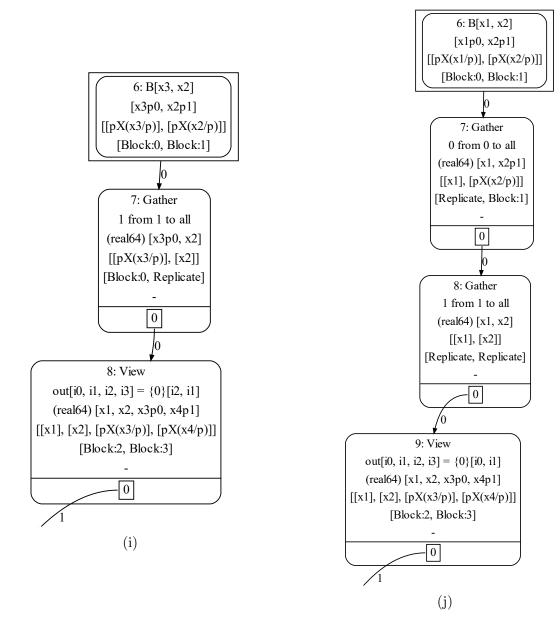

The mid-level IR represents computations grouped by the data access patterns. The main nodes are map nodes that represent element-by-element operations, stencil nodes that represent stencil computations, multiplication nodes that represent matrix-matrix and matrix-vector products, and matrix power operations, rearrange nodes that represent transpose, flip, replicate, reorder and reshape, combine nodes which have reduce and scan operations, and recurrence. Each node has a list of inputs, a list of outputs, and a function operating on the inputs to generate the outputs, which are again, represented as DAGS (a linear text version is presented in the figures).

map node takes a set of array inputs and performs element-by-element operations to generate a set of outputs. The actual operations are encoded as a function that map the inputs to the outputs through a set of operations, again stored as a DAG. These nodes need communication to align the arrays across the processes, and no communication for the actual computation. These nodes are obtained by translating element-by-element operations in HLIR and fusing the operations together.

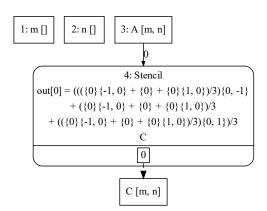

stencil node performs the same operations as a map node but also includes at least one offset-indexed array. This is different from the map node as offset-indexed arrays require ghost regions and data exchange with neighbor nodes.

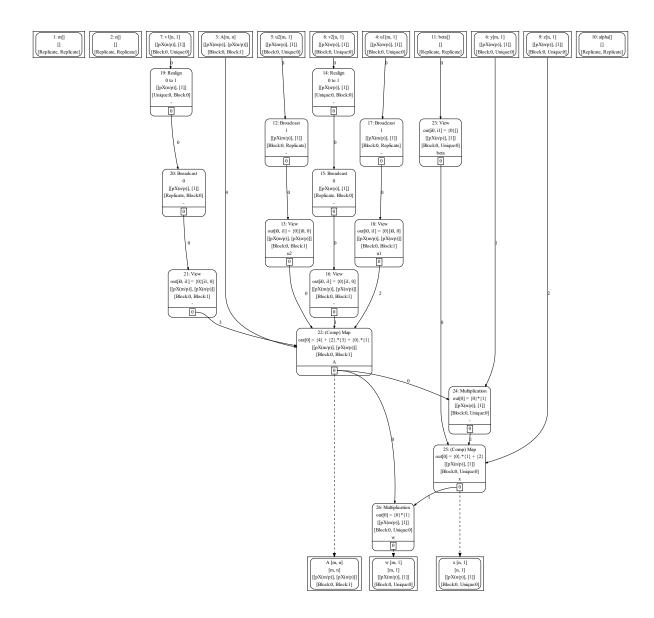

Figure 3.12: Jacobi2D MLIR  $\,$

Figure 3.13: Gauss2D MLIR

multiplication node performs matrix-matrix and matrix-vector multiplications, and matrix power operations. This node generates different communication patterns based on the algorithm selected.

rearrange nodes perform data alignment and rearrangement. These include transpose, flip, replicate, reorder and reshape operations. These nodes generate communication nodes depending on the pattern of rearrangement. These nodes also represent a change in data distribution on a virtual process grid.

combine nodes perform reduction and scan operations. These again generate reduce or scan communication patterns.

recurrence nodes are hierarchical, like in HLIR and have the same mechanics as in HLIR. Only difference is that the nodes in the DAG of the iteration are MLIR nodes instead of HLIR nodes.

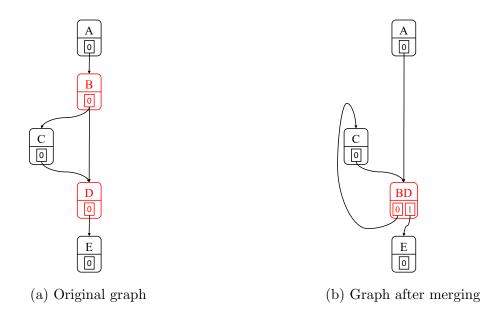

Since MLIR categorizes nodes based on the data access and communication patterns, it lends itself amenable to grouping computations together by merging nodes, defining the communication patterns in lower layers. Grid declaration, data partitioning and mapping (Section 4.6) are performed on the MLIR, and communication and computation strategies are selected for each node in MLIR.

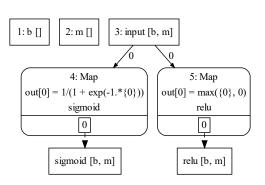

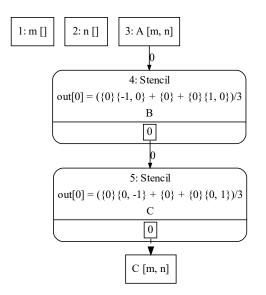

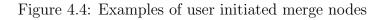

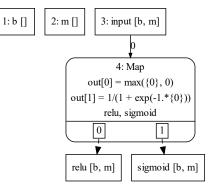

MLIR undergoes a series of transformations during the translation process. The initial MLIR is generated with a one-to-one correspondence to HLIR. Then nodes are merged to group the computations. MLIR also provides an interface to allow users to manually select nodes to merge. MLIR supports each node to have multiple outputs to allow for a greater freedom to the user in merging the nodes. Then, data partitioning and mapping is specified on the merged MLIR. Consistency and propagation of mapping type is performed on MLIR and each node (input, output and intermediate computation nodes) is annotated with a data partition and map.

Figures 3.8 through 3.13 present the MLIR version of the examples from Figure 2.1.

## 3.4 LOW LEVEL INTERMEDIATE REPRESENTATION (LLIR)

Low-level IR (LLIR) nodes represent computation and communication operations on each process on the virtual process grid. Local data arrays are computed using the partitioning and mapping on the MLIR, to determine the local inputs and outputs. Computation nodes in LLIR specify local computations on local inputs to generate local outputs based on the MLIR. Communication nodes define communication patterns. All LLIR nodes have a mask parameter to select or filter the nodes on which the computation/communication is performed.

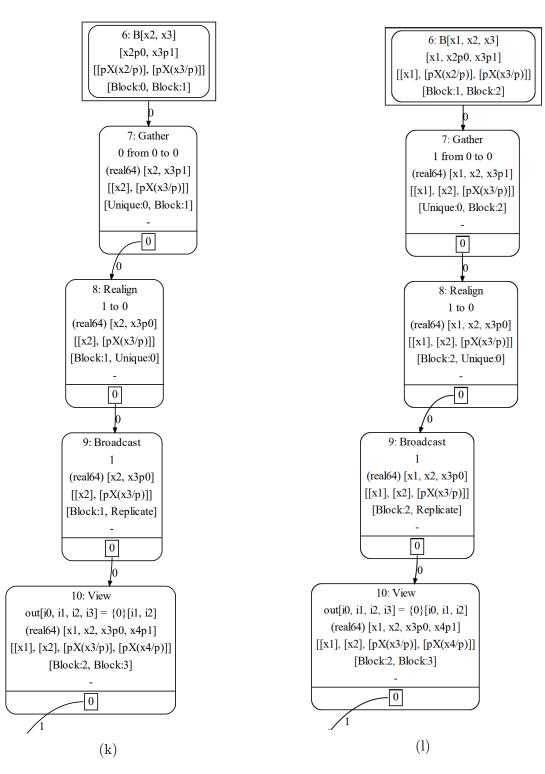

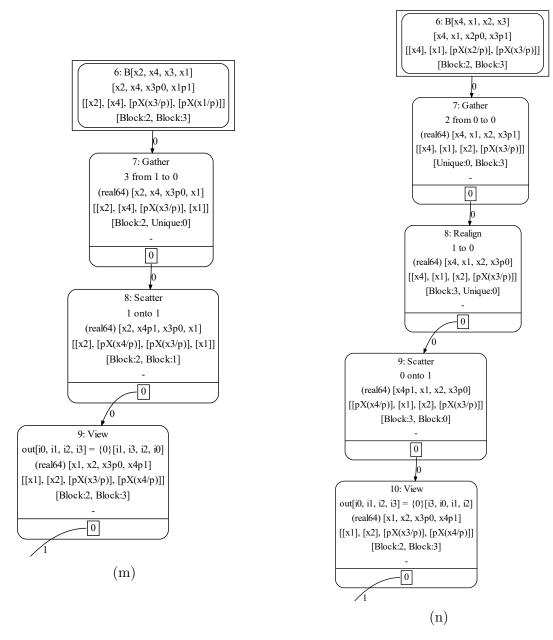

Figure 3.14: LLIR for matrix-vector multiplication

#### 3.4.1 Computation Nodes

Computation nodes have a set of inputs, a set of outputs and a function that maps outputs to inputs using a DAG. The main difference between the computation nodes of MLIR and LLIR is that LLIR nodes represent local computation. The main types of LLIR computation nodes are Map nodes, Stencil nodes, Multiplication nodes and Combine nodes. These perform the operations as their corresponding MLIR nodes, but on local arrays only. The communication requirements and data placements are taken care of in other nodes.

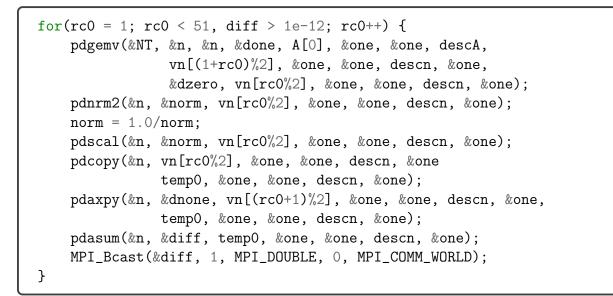

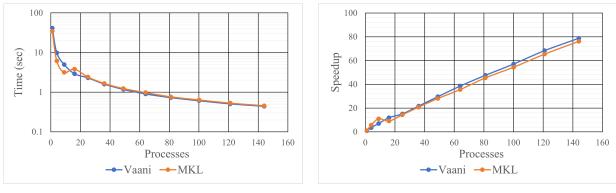

## 3.4.2 Communication Nodes