$\bigodot$ 2020 Liyi Li

# A VERIFICATION FRAMEWORK SUITABLE FOR PROVING LARGE LANGUAGE TRANSLATIONS

BY

## LIYI LI

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2020

Urbana, Illinois

Doctoral Committee:

Research Professor Elsa L. Gunter, Chair and Director of Research Professor Grigore Rosu Professor David A. Padua Professor Vikram S. Adve Professor Steve A. Zdancewic

#### ABSTRACT

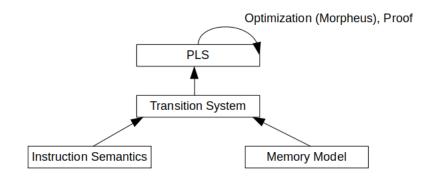

Previously, researchers established some frameworks, such as Morpheus [1], to specify a compiler translation in a small language and prove the semantic preservation property of the translation in the language under the assumption of sequential consistency. Based on the Morpheus specification language, we extend the verification framework to prove the compiler translation semantic preservation property in a large real-world programming language with a real-world weak concurrency model. The framework combines four different pieces. First, we specify a complete semantics of the  $\mathbb{K}$  framework and a translation from  $\mathbb{K}$  to Isabelle as our basis for defining language specifications and proving properties about the specifications. Second, we define a complete operational semantics of LLVM in  $\mathbb{K}$ , named **K-LLVM**, including the specifications of all instructions and intrinsic functions in LLVM, as well as the concurrency model of LLVM. Third, to verify the correctness of the **K-LLVM** operational model, we create an axiomatic model, named hybrid axiomatic timed relaxed concurrency model (HATRMM). The creation of HATRMM is to bridge the traditional C++ candidate execution models [2, 3, 4] and the **K-LLVM** operational concurrency model. Finally, to enhance our framework to prove the semantic preservation property in a relaxed memory model, we define a new simulation framework, named Per Location Simulation (PLS). PLS is suitable for proving semantic preservation property in a relaxed memory model.

To my parents, Jinfa Li and Wu Cheng, and my spouse, Jiaing Huang, with love and gratitude

#### ACKNOWLEDGMENTS

I would like to express my greatest appreciation to Professor Elsa Gunter. I was advised by Elsa since my undergraduate study in the University of Illinois at Urbana-Champaign. At that time, I was a Chinese student who could not speak proper English and lived in anxiety and loneliness. Now, I am a Ph.D. student who is going to graduate with a family. Elsa affected every aspect of my life. For the rest of my life, I will always remember Elsa as if she is my mother. I would like to thank my colleague, Professor William Mansky, coming up with such great platform, Morpheus, which my work is based on. I would like to thank my committee: Professor Grigore Rosu, who taught me the  $\mathbb{K}$  framework and guided me to finish the semantics of Lower Level Virtual Machine in K (K-LLVM); Professor Vikram Adve, who provided me knowledge on real-world languages and compilers; Professor David Padua, who advised me on different compiler optimizations; Professor Steve Zdancewic, who suggested me pick a particular Ph.D. thesis direction instead of a very large goal that might cost many years. I would like to thank my parents, who have supported me for many years. Finally, I would like to thank my wife, Jiaming Huang, who have followed me through every twist and turn. She listened to my complaints and gave me suggestions. I couldn't have made it this far without all these great people around me.

# TABLE OF CONTENTS

| Chapter 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2       RELATED WORK                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 3 BACKGROUND       10         3.1 Previous Approaches and Their Problems       10         3.2 Morpheus Syntax       11         3.3 Isabelle/HOL       12         3.4 The K Framework       14                                                                                                                                                                            |

| Chapter 4THE SEMANTICS OF K AND ITS TRANSLATION TO ISABELLE14.1A Breif Overview of IsaK144.2The Static Semantics of IsaK244.3The Dynamic Semantics of IsaK344.4K Design Issues and The Evaluation of IsaK344.5TransK: Translation from K to Isabelle444.6Soundness and Completeness between IsaK and TransK54                                                                    |

| Chapter 5       KLLVM: THE SEMANTICS OF LLVM IR       55         5.1       K-LLVM Background and Challenges       55         5.2       The Static Semantics of IsaK       64         5.3       The K-LLVM Dynamic Semantics       77         5.4       K-LLVM Evaluation and Applications       94                                                                               |

| Chapter 6 HYBRID AXIOMATIC TIMED RELAXED CONCURRENCY         MODEL (HATRMM)       9         6.1 HATRMM Beyond Other Previous Models       9         6.2 Preliminary: Memory Actions, Events, Executions, Relations, and Example Programming Language       10         6.3 HATRMM and Three Methodologies       10         6.4 Example Program Semantics Adapting HATRMM       13 |

| Chapter 7       THE LLVM OPERATIONAL MODEL       13         7.1       The Execution Model       13         7.2       The Memory Model       14         7.3       Relation Between the LLVM Operational Model and HATRMM       15                                                                                                                                                 |

| Chapter 8 A FRAMEWORK TO VERIFY COMPILER OPTIMIZATION SE-               |   |

|-------------------------------------------------------------------------|---|

| MANTIC PRESERVATION                                                     | 1 |

| 8.1 The Per-Location Simulation Definition                              | 3 |

| 8.2 Program Meaning Preservation                                        | 0 |

| 8.3 Isabelle Formalization of the Framework and the Proof               | 3 |

| Chapter 9CONCLUSION AND FUTURE WORK1649.1Conclusion1649.2Future Work164 | 5 |

| BIBLIOGRAPHY                                                            | 8 |

#### Chapter 1: INTRODUCTION

Compiler correctness is one of the most fundamental problems in programming, but the term can actually be understood on two different levels. When someone talks about a compiler, e.g. GCC [5], being "buggy", they are usually referring to a fault or unverified compiler with the potential to transform correct high-level code into low-level code containing errors. The problems appear in the low-level code, which is actually executed in a single-threaded environment. They are easy to observe but not easy to fix. However, there is a second level of compiler bugs, where multi-threaded programs are translated to low-level multi-core architecture and executed. Users might run their multi-threaded programs many times before observing some strange behaviors that the programs are not supposed to produce under the assumptions of the high-level language. These extra behaviors result from differences in the semantics of these two languages, e.g. because they have different concurrency models. For example, some behaviors that are not allowed in an instruction sequence in the high-level language, according to its concurrency model, occur in the compiled program because the low-level language has a more flexible concurrency model. Gaining behaviors is generally not desirable, and they can be classified as bugs. These behaviors can also invalidate the analyses of codes, causing correctly written programs to execute incorrectly; these problems may require considerable effort to detect and resolve.

Previously, Gunter and Rosu designed a formal framework in the VeriF-OPT project that addresses part of the compiler correctness problem on the first level [6]. The framework focused primarily on specifying compiler optimizations in a particular source language and proving them correct. Gunter and Mansky also developed a specification language, Morpheus [1], to specify and prove the correctness of compiler optimizations in Isabelle [7]. There are three points to note about VeriF-OPT. First, it focuses on a domain specific language (Morpheus). Even though the language is good for specifying properties related to control flow graphs, it might not be adequate for specifying all compilation steps in a compiler. Specially, it might not be able to specify all interesting compiler optimizations. For example, the Morpheus language is not able to specify the thread-inlining optimization, i.e. executing two threads' programs in one sequentialized thread. Second, the previous compiler correctness proof [1, 8] is based on a simple well-founded memory model. The proof strategy might not work for a language based on a real-world relaxed memory model such as the C++ memory model [2, 3]. Furthermore, the compiler correctness proof framework in the previous work [1, 8] is based on a simple bi-simulation framework. It neither considers program executions that lead to failure, nor does it include the extra program execution behaviors caused by a relaxed memory model.

In this thesis, we propose a framework, **Morpheus**+, that combines the Morpheus specification language with a system (**IsaK**) for defining concurrent language semantics and a system for proving the per-simulation relation between two language specifications for a particular transformation, in order to verify the compiler correctness for languages under a real-world multi-threaded concurrency model, such as the relaxed concurrency model. The primary goal of the project is to provide a memory-model-aware generalized framework for proving the correctness of transformations, especially compiler optimizations, and will include: the **IsaK** [9, 10] and **TransK** [11] tools for connecting language specifications in  $\mathbb{K}$ to theories in Isabelle, a generic memory model that is able to define relaxed concurrency models, such as the LLVM IR concurrency model; and a compiler correctness proof system based on the Per-Location Simulation framework (PLS). We rely on  $\mathbb{K}$  to easily define large and real-world language specifications and on Isabelle to prove correctness properties about the compilations between two languages. As an example of **Morpheus**+, we define compiler optimizations based on the complete semantics of LLVM IR with its operational concurrency model. Using PLS, we are able to prove the correctness of these compiler optimizations.

#### Chapter 2: RELATED WORK

We provide here some related work of the Morpheus+ project.

#### 2.1 COMPILER CORRECTNESS RELATED WORK

Compiler verification efforts date back at least to a 1973 paper by Morris [12]. Early efforts include the construction of an interpreter for the Piton language in the Boyer-Moore theorem prover [13, 14] and the verification of a compiler for a subset of the Gypsy language [15]. Also notable is Elsa Gunter's work in formalizing the syntax and semantics of SML, as well as its module system, in HOL-90 (the predecessor to Isabelle) [16, 17]. The proof assistants Coq [18] and Isabelle [19] have been the platform used for various significant formal verification efforts, including several in the area of verified compilation. Early Isabelle projects included an interpreter for a small functional language verified against its denotational semantics [20] and a verified lexer [21]. More recent developments have included verification of a code generation algorithm from SSA form [22], a bytecode verifier for the Java Virtual Machine (JVM) [23], and compilers for substantial subsets of C [24, 25] and Java [26]. Gesellensetter et al. [27] have also used a translation-validation approach in Isabelle to find bugs in GCC. The Jinja project has formalized a significant subset of Java, including its concurrency model, in Isabelle [28, 29]. Coq projects have included verification of the JavaCard smartcard platform [30], development of a formally specified and executable JVM [31], verification of an algorithm for sequentializing parallel assignments [32], verification of CPS transformations for functional languages [33], and creation of a verified compiler for simply-typed lambda calculus [34].

Perhaps the most impressive achievement in compiler verification to date is the CompCert project, culminating in an end-to-end proved-correct compiler from a subset of C to PowerPC machine code written entirely in Coq [35, 36, 37]. Though complete formal compiler verification was previously considered near-impossible by the formal analysis community (see [38]), the CompCert project has provided a powerful counterexample to this argument. While it does not cover the entire C specification, the compiler does include a range of real-world optimizations, and introduces a general method for proving correctness of optimizations involving dataflow analysis. Further work on the project includes a framework for adding new optimizations [39] and an extension for garbage collection [40], as well as a C-like memory model for verifying pointer-based programs [41]. Ŝevčik *et al.* [42] are in the process of developing an analogous compiler for a language including shared-memory con-

currency, and have lifted the proofs of correctness for several of CompCert's optimizations, including constant propagation and common subexpression elimination, to the parallel case. Blazy and Leroy [43] in the CompCert project have verified an optimizing compiler based on CLight, including compilation steps and C-like modular systems. They used Coq to generate a compiled code behaving exactly as described by the specification of the language. Other projects based on CompCert include Appel's, which combined program verification with a verified compilation software tool chain [44].

Building on CompCert, the Verified Software Toolchain (VST) project [45] seeks to link via formal methods the results of static analysis tools on high-level programs to the behavior of compiled code. VST has a particular focus on concurrent programs, and has so far produced several levels of operational semantics for a C-like source language with threads and locks, as well as a versatile program logic called Concurrent Separation Logic [46]. Integration of Morpheus with VST could potentially provide considerable benefits to both frameworks; Morpheus would offer improved generality and modularity and easier links to other source and target languages, while VST would offer an extensive set of tools and analysis approaches for verification of properties on compiler specifications.

The PVS theorem prover has also been used in some compiler verification efforts, such as a verification of peephole optimizations [47] and a framework for translation validation of optimizations [48]. PVS has not generally been a popular target for formal verification of compilers, perhaps due to the relatively large size of its trusted code base, but is potentially a versatile framework for formal analysis of transformations.

The TRANS language that forms the core of our approach to compiler specification is based on work by Lacey *et al.* [49, 50], and the original statement of TRANS is due to Kalvala *et al.* [51]. More recently, Kalvala and Warburton have used the TRANS approach to automatically find and fix bugs in Java programs [52]. Rather than using the formal semantics of TRANS to verify program correctness, this approach intentionally uses TRANS to change the semantics of programs, from potentially buggy programs (according to some user-provided pattern for bugs) to more correct ones. Since this could potentially lead to the introduction of bugs as well as their elimination, potential rewrites are not carried out automatically, but are rather suggested to the user of the system as possible fixes. Thus, in parallel with our work, TRANS is also being used as a software engineering tool for offering bug fixes to Java programmers. The Morpheus language, based on the TRANS language, allows users to specify program transformations and optimizations in a program that may involve parallelism and using proof theories in the previous VeriF-OPT project to prove the program optimizations correct under a semantics involving parallelism [1].

Cobalt [53] and Rhodium [54] are systems for specifying compiler optimizations developed

in parallel with TRANS, and also inspired by Lacey's work on optimizations and temporal logic [49]. As in TRANS, optimizations are written as rewrites conditioned on temporal properties of the control-flow graph. Cobalt and Rhodium extend Lacey's simple intermediate language to handle more complex features such as pointers, dynamically allocated memory, and recursive function calls. They also restrict the range of temporal formulae from general CTL to a tightly constrained subset, which in practice has allowed them to prove soundness of optimizations completely automatically. Optimix [55, 56] is another graph-rewriting-based system for expressing compiler optimizations, developed prior to TRANS and with a less compact method of establishing the conditions under which the rewrite should be performed.

In terms of functional programming languages (ML languages) and theorem provers, Milner, Tofte, Harper, and MacQueen [57] formalizes one of the most prominent and mathematical programming language specifications, whose formal and executable specifications were given by Lee, Crary, and Harper [58], also by VanInwegen and Gunter [16], and by Maharaj and Gunter [59]. In contrast to ML, formalizing other real world language specifications is a challenge because they are designed without formalism in mind. There have been a number of formal language specifications given in the HOL [60] and Coq [18]. For example, A small step semantics of C in HOL was specified by Norrish [61], who proved substantial metaproperties, but the specification has not been tested for conformance with implementations. Many other projects were done on Coq, such as the VeLLVM project [62].

#### 2.2 K RELATED WORK.

In this section, we discuss other work describing  $\mathbb{K}$  semantics, and language specifications defined in  $\mathbb{K}$ , as well as order-sorted algebras.

Order-sorted algebras were first introduced systematically by Goguen *et al.* [63]. Many people defined rewriting strategies, unifications and equational rules on top of order-sorted algebras and further extended the operational semantics of order-sorted algebras [64, 65, 66, 67, 68]. Based on order-sorted algebras, Meseguer *et al.* [69, 70] developed rewriting logic. A major contribution of rewriting logic is to contain the operational semantics of order-sorted algebras. The core idea of rewriting logic is that it distinguishes equations from rewriting rules – equations partition terms into equivalence classes while rewriting rules act like traditional transition rules in structural operational semantics. Maude [71] implemented the syntax and semantics of rewriting logic and provided several useful tools and applications [72, 73, 74]. Another implementation of an order-sorted algebra is PROTOS(L) [75], which has an operational semantics based on a polymorphic, order-sorted resolution.

$\mathbbm{K}$  has a brief English description of its semantics and provides some examples in the  $\mathbbm{K}$

overview document [76]. In addition, there is a compiler implementation in Java to allow users to define their language specifications and show traces of execution programs. The compiler has almost fifty compilation steps, and eventually executes a program in a very small core language that has no English description to describe its grammar or semantics. In this sense, these  $\mathbb{K}$  specifications are far from being formal. Matching Logic [77] is a logic system that is built on top of  $\mathbb{K}$  for reasoning about structures. The current invention of Matching Logic is Reachability Logic [78, 79]. It is a seven rule proof system and is language independent. It generalizes transitions of operational language specifications defined by users and the Hoare triples of axiomatic semantics [80] to prove properties about programs in the specifications, so that users do not need to define the axiomatic semantics of a specification. There is an ongoing project by Moore [81] that transfers the  $\mathbb{K}$  specifications to Coq [82] and plans to prove properties of the programs of the specifications in Coq. The current state is that Moore has managed to define a useful co-induction tool in Coq and prove some properties by defining small language specifications in Coq. Big language specifications have been defined in K including C [83], PHP [84], JavaScript [85], and Java [86]. They are executable, have been validated by test banks, and, through the addition of some formal analysis tools produced by  $\mathbb{K}$ , have shown usefulness.

Goguen *et al.* [63] introduced a way of translating solely initial free (having no equations or rules) order-sorted algebras to many-sorted ones. One recent attempt at translating order-sorted algebras into many-sorted ones was made by Meseguer and Skeirik [87]. Their algorithm provided a theoretical framework to translate order-sorted equations and rules to many-sorted ones by generating (potentially exponentially many) new copies of transition rules for each of the sorts subsorting to the ones in the original transition rules. In addition, Li and Gunter [11] provided a new translation method to translate order-sorted algebras into many-sorted ones, which is the theoretical foundation of our project.

The study of many sorted algebras has a long history. Their logic system was explored by Wang [88]. Many well-known programming languages such as C, Java, LLVM, and Python are based on them.

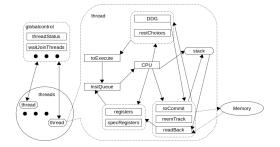

#### 2.3 RUNTIME EXECUTION MODELS AND MEMORY MODELS

The idea to have an execution model that connects the runtime, instruction semantics and memory model was inspired by real-world execution models. Mainly, we were enlightened by the Tomasulo algorithm [89], and to a lesser extent by some current execution models such as the MPC model by Perache *et al.* [90], the fractal model by Subramanian *et al.* [91], and the copy or discard (CorD) execution model by Tian *et al.* [92]. Tomasulo's algorithm is simple enough to act as a guideline for the execution model for our LLVM IR semantics (**K-LLVM**). The other models are too complicated for our purposes, containing too many details about hardware.

We are also helped by various memory models. Lamport probably was the first to define a memory model weaker than sequential consistency for multi-threaded programs [93]. Adve and Hill [94] started defining weak memory orders for memory operations. Focusing just on hardware models: Ahamad *et al.* [95] axiomatized causal memory and proved some important theorems. Higham *et al.* [96] formalized SPARC and a number of simpler memory models in both axiomatic and operational styles. Sevcik *et al.* created a formal verification framework for a small C-like language [42]. The same group [97] later developed the CompCertTSO to verify a compiler from CLight to X86 based on a relaxed memory model. Mansky *et al.* [98] developed an axiomatization of the CompCert sequential consistency memory model and combined the model with a subset of the LLVM language to verify the correctness compiler optimizations.

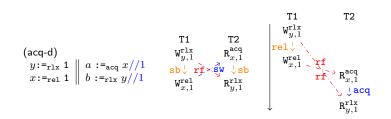

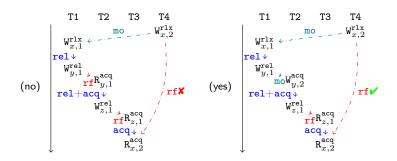

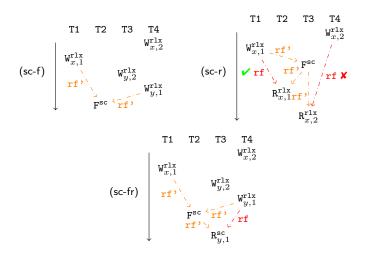

In the SPARC documentation [99], an axiomatic style similar to the candidate execution model was used. Alglave *et al.* [100] specified in great detail how to use a candidate execution model to define relaxed memory models and provided several verification tools. The C11 memory model was designed by the C++ standards committee based on a paper by Boehm and Adve [101]. Batty et al. formalized the C11 model with some improvements and proved the soundness of its compilation to X86-TSO [2]. A number of papers [102, 103, 104, 105] found that Batty et al.'s model enabled thin-air behaviors. Vafeiadis et al. [106] found many other limitations in Batty et al.'s model and proposed ways to handle them. In 2016, Batty et al. proposed a more concise model for sc atomics [107], but the model is stronger than C11, and their sc fences are too weak. Much previous work [103, 108, 109, 110] focused on a fragment of C++ concurrency. From this corpus, we select Lahav et al.'s SRA model [110] to show the soundness of our acg/rel atomics. In 2017, Lahav et al. [3] defined a comprehensive  $C^{++}$  model (RC11) based on all previous models, with extra extensions on Batty et al.'s model. In Chapter 6, we discussed this model as a part of several topics. The main limitations from our perspective with the model is that its OUT-OF-THIN-AIR condition is too strong and rules out too many good executions. Many previous papers [111, 112, 113] also proposed solutions for defining what are "good" out-of-thin-air behaviors. These models were not in the axiomatic candidate execution fashion, and one of them (the promising memory model [113]), which we have compared in Chapter 6, has been proved to be represented by the IMM model [4]. Chakraborty and Vafeiadis [114] provided a concurrent abstracted memory model for LLVM IR. It provided the semantics for a fragment of LLVM IR memory operations while keeping the model stronger than Lahav et al.'s. The IMM

model by Podkopaev *et al.* [4], based on RC11 and the promising memory model, defined its OUT-OF-THIN-AIR property with a weaker one than the one in RC11. We have shown in Chapter 6 that it is not suitable in handling many thin-air behaviors, and some of its control dependency is too weak so it enables some thin-air behaviors. The essential difference is that IMM is designed to provide a spiritual sample for people to understand how to compile C++ to hardware code, while HATRMM is designed to be used by a PLS to prove properties about a compiler.

#### 2.4 LANGUAGE SPECIFICATIONS RELATED TO LLVM IR

Besides **K-LLVM**, other formal executable sematics for LLVM-IR include VeLLVM [115] and the previous LLVM semantics in  $\mathbb{K}$  [116]. VeLLVM was the first project to define a relatively complete specification for the core of LLVM IR. It was defined in the theorem prover Coq [18] and covered a core set of LLVM IR instructions. VeLLVM formalizes a mechanized semantics for LLVM IR, its type system, and the properties of its SSA form. It also has an interpreter extracted from Coq that ran 145 test programs and passed 134 of them. The memory model of VeLLVM is based on CompCert with newly developed features that are specifically designed by the VeLLVM team for capturing the memory data layout features in LLVM IR. Their model associates metadata to memory byte data fields, so that an execution of a LLVM IR program can utilize the metadata. This feature is similar to the memory data layout in K-LLVM (see Sec. 5.3.3). With VeLLVM, users can prove properties about translations defined in LLVM IR. Many papers, such as [115, 117], have been published about compiler correctness, memory models, and verification of compiler schemes using VeLLVM. The LLVM semantics in  $\mathbb{K}$  by Ellison and Lazar [116] is a prior work of **K-LLVM**, and it provides many definitions for LLVM IR instructions for single-threaded programs. The definition influences **K-LLVM**, particularly the definition of LLVM's syntax, static semantics, and single-threaded dynamic semantics.

There are other pieces of work that are not meant to directly define the LLVM IR semantics but influence **K-LLVM**. First, Lee *et al.* [115] investigated the LLVM IR undefined behaviors with no concrete semantics for all undefined behaviors. Kang *et al.* [117] provided a model in C to support the inttoptr/ptrtoint casting operations and enabled the correctness proofs of many LLVM optimizations that rely on certain memory provenance model features that the previous CompCert model is not able to provide. The difference between Kang *et al.*'s work and the handling of inttoptr/ptrtoint casting operations in **K-LLVM** is that they focus more on the relations between the executions of such operations with respect to the memory and define the relations in terms of logical properties, whereas **K-LLVM** focuses more on the formalization of an abstract machine, and emphasizes different conceptual components finishing different tasks without communicating with each other through "unofficial" channels. Ellison and Rosu [83] defined the full C semantics with a simplified version of the CompCert model. Chakraborty and Vafeiadis [114] provided a concurrent abstracted memory model for LLVM IR that focused on an abstraction of the concurrent LLVM IR memory behaviors. Lee *et al.* [118] proposed a novel LLVM memory model including a data layout and memory pointer provenance model based on a small set of LLVM IR memory related instructions. Specially, they provide an algorithm for preventing address guessing when the total number of possible allocations in a system is bounded. A current challenge is the extension of that memory model to the full set of LLVM-IR memory related instructions. Memarian *et al.* [119] provided two pointer provenance models for C/C++ languages and reconciled the ISO C standard. Similar to Lee *et al.*'s work, Memarian *et al.* focused on creating better pointer provenance models for C/C++.

Other interesting work includes a JavaScript specification by Bodin *et al.* [120], and formalized semantics of OCaml Light by Owens *et al.*, which is built in Ott [121], which provides an easy way to write specifications, and automatically translates them into HOL, Isabelle, and Coq. Isabelle, HOL and Coq, being proof assistants, have a relatively steep learning curve.

A lot of work has been done on formalized specifications in Java and C#: Eisenbach's formal Java semantics [122] and Syme's HOL semantics [123] for Drossopoulou, the C# standard by Börger *et al.* [124], which is formally executable and uses abstract state machines, and the executable Java specification by Farzan *et al.* [125].

#### Chapter 3: BACKGROUND

Below we discuss the necessary background information for this paper, including the  $\mathbb{K}$  style rules that we use in this thesis.

#### 3.1 PREVIOUS APPROACHES AND THEIR PROBLEMS

We first investigate what the available verification approaches for compiler correctness. There are basically two kinds: proofs and validations. In terms of proofs, the TRANS approach is the trend. The basic idea is to define a domain-specific language as the core, and then build a proof infrastructure around it. The TRANS language developed by Kalvala et al. [51] is one of the significant pieces of this approach. Mansky and Gunter constructed a framework for the formal verification of compiler optimizations [126], which is an extension of the TRANS work. They also developed a domain specific language, Morpheus [1], based on temporal logic. It is used to express and verify properties over paths in transition systems. It has been used for a long time to verify properties of programs. In contrast to traditional first-order and higher-order logic systems, temporal logic systems have a built-in notion of progress through time, and have "next" and "until" as first-class concepts. The two most commonly used temporal logics are LTL [127], which is used to express properties on single paths, and CTL [128], which is used to express properties on sets of paths and can be thought as trees that branch over time. In the standard interpretations of both LTL and CTL, programs are modeled as finite-state automata (FSA), and formulae are evaluated over paths through the automata. In their Morpheus paper, Mansky and Gunter specified a set of compiler optimizations on LLVM that included redundant store elimination and loop peeling, and utilized the Isabelle semantics to verify the correctness of these optimizations on a subset of LLVM – MiniLLVM. The generalized control flow graphs along with the Morpheus paper allow users to describe transformations that may involve parallelism. In the VeriF-OPT project [6], Mansky and Gunter specified a simulation framework for proving compiler transformation correctness for language semantics involving parallelism [126], and provided the supporting theories. In the paper, they described how to use a Morpheus-like language (PTRANS was being developed into Morpheus) and its associated theories to verify a reordering optimization on parallel programs. Their method relies on an analysis of the use of locks in the target program.

The main trend in validation approaches is translation validation, in which each source program is compared with the corresponding low-level output of the compiler, and checked to ensure that the translation preserved the property  $\varphi$  [38]. This approach treats the compiler as a black box, producing unreliable output that must be verified every time. Individual proofs are considerably more lightweight than any complete compiler verification, and may often be performed automatically. Since its inception, this technique has been successfully applied to optimizing compilers in various instances [38, 129, 130, 131, 132].

The **Morpheus**+ project uses the two approaches for different tasks. The problem with the TRANS approach is that a domain specific language is often restricted. For example, the Morpheus language is only good for specifying compiler optimizations within a program that has a specific control flow graph. Some optimizations might not be able to be specified by using Morpheus only, such as thread inlining optimization. Another problem with the VeriF-OPT project is its simulation framework. The simulation framework is a traditional one similar to the CompCert simulation framework. In **Morpheus**+, we specify the perlocation simulation framework to verify compiler optimizations based on real-world relaxed memory model (Chapter 6). The **Morpheus**+ project also takes the validation trend into account. It is typically hard to prove if a language specification achieves the spirit of the original design. We use extensive program validation to test if the language specifications, especially the source language specifications, meet the design spirit of the language designer in  $\mathbb{K}$ , as we have done to test **K-LLVM**.

#### 3.2 MORPHEUS SYNTAX

Here we introduce the syntax of Morpheus. More details can be found at the work of Mansky *et al.* [1]. The basic approach of the Morpheus specification language is modeled after the TRANS language of Kalvala *et al.* [133]. Optimizations are specified as conditional compositions of rewrites on a generalized control flow graph (GCFG) containing the program's code. The language is partitioned into three largely independent components: core graph transformations (*H* below), conditions given in a variant of Computation Tree Logic (CTL) ( $\varphi$  below), and a strategy language (*T* below) for building complex transformations out of component transformations and conditions.

Intuitively, the rewrite portion of an optimization expresses the local transformation to be made, the condition characterizes the situations in which the optimization should be applied, and the strategy language allows us to build whole-system transformations out of collections of local ones. Morpheus is a special-purpose language for the transformation of GCFGs, and as such is parametrized by aspects of GCFGs, namely node names, node labels (program instructions), and edge labels (marking control flow). Transformation specifications may mention aspects of GCFGs concretely, but more generally, they use pattern variables that will be instantiated with control flow graph components in each specific application. We will use the term "expressions" to refer to patterns built from both concrete entities and metavariables (which will be instantiated with concrete entities when the transformation is applied). We use the term metavariable (a) to refer to the variables in the patterns and expressions in Morpheus transformations, as opposed to the concrete programming variables that will be found in instructions.

$$\begin{split} H &\triangleq \mathsf{add\_node}(\pi, B, (l_1, \pi_1), \dots, (l_n, \pi_n)) \mid \mathsf{add\_node}(\pi) \\ &\mid \mathsf{relabel\_node}(\pi, B) \mid \mathsf{move\_edge}((\pi, l, \pi_1), \pi_2) \\ \varphi &\triangleq \mathsf{true} \mid p(\overrightarrow{x}) \mid \varphi \land \varphi \mid \neg \varphi \mid \exists a. \varphi \mid \mathscr{AX} \varphi \mid \mathscr{AY} \varphi \mid \mathscr{EX} \varphi \mid \mathscr{EY} \varphi \\ &\mid \mathscr{A} \varphi \, \mathscr{U} \varphi \mid \mathscr{E} \varphi \, \mathscr{U} \varphi \mid \mathscr{A} \varphi \, \mathscr{S} \varphi \mid \mathscr{E} \varphi \, \mathscr{S} \varphi \\ T &\triangleq H \mid \mathsf{SATISFIED\_AT} \pi \varphi \mid \mathsf{NOT} \ T \mid T \backslash T \mid \mathsf{EXISTS} \ a. \ T \mid T + T \mid T \ ; \ T \mid T \ast \end{split}$$

Figure 3.1: The Morpheus Language

The syntax of Morpheus consists of actions (H), conditions ( $\varphi$ ), and transformations (T) (Fig. 3.1). The atomic actions H begin with add\_node and remove\_node, which add and remove nodes that have no incoming edges. In the case of add\_node, the addition only takes place if the node description is well-formed as a CFG node (i.e., it has the right number and kind of outgoing edges for its instruction label). The relabel\_node action relabels an existing node with a new instruction, as long as that new instruction is compatible with the existing edge structure. The only action that operates directly on edges (rather than nodes) is move\_edge, which moves the destination of an edge from one node in the graph to another. The conditions  $\varphi$  of Morpheus are based on First-Order CTL (FOCTL). Starting from a set of atomic predicates p, they include all of the usual propositional and temporal operators. The  $\mathcal{S}$  ("since") and  $\mathcal{Y}$  ("yesterday") operators are the past-time counterparts to the  $\mathcal{U}$  ("until") and  $\mathfrak{X}$  ("next") operators respectively; for instance,  $\mathfrak{C} \varphi_1 \mathfrak{S} \varphi_2$  holds when there exists some path backwards through the graph such that  $\varphi_1$  holds until a previous point at which  $\varphi_2$  holds. The existential quantifier  $\exists$  is used to quantify over metavariables in a formula: these metavariables may then appear in the atomic predicates of a formula, enhancing the expressive power of the conditions. At the top level, a transformation T combines conditions and rewrites using strategies. Strategies are inherently non-deterministic, as is reflected by their returning a set of possible transformed graphs. The simplest strategy is just to perform an action H. The strategy SATISFIED\_AT  $\pi \varphi$  acts as the identity transformation if  $\varphi$  holds of the GCFG at the node  $\pi$ , and returns the empty set if  $\varphi$  fails to hold on  $\pi$ . Thus SATISFIED\_AT  $\pi \varphi$  acts as filter, allowing through only those GCFGs and nodes  $\pi$ that satisfy  $\varphi$ . On the other hand, NOT T and  $T_1 \setminus T_2$  allow us to deselect graphs by the ability to perform a transformation. The transformation NOT T selects those graphs that T cannot transform, i.e., those not in the domain of T, and deselects those that it can

transform. The transformation  $T_1 \setminus T_2$  restricts the output of  $T_1$  to those graphs that could not be produced by  $T_2$ , i.e., those not in the image of  $T_2$ . Note the difference between these two filters: NOT T filters based on the complement of the domain of a transformation, while  $T_1 \setminus T_2$  filters based on the complement of the range of a transformation. The strategy EXISTS a. T binds a in T, limiting its scope to the free occurrences of a in the conditions and actions of T. Finally, the constructs + and ; allow for choice between and sequencing of two transformations respectively, and the iteration operator \* allows for the repeated application of a transformation any number of times.

For a simple example of a Morpheus transformation, assume we have a language of instructions that supports assign- ments and binary arithmetic expressions. In this setting, if we have a variable assigned the result of applying an arithmetic operation to two constants, we might want to replace the operation with its result. This can be done by the transformation in Fig. 3.2.

simple\_constant\_folding( $\pi$ )  $\triangleq$  EXISTS  $x \ a \ b \ c \ oper$ . SATISFIED\_AT  $\pi$  stmt(x = oper(a, b))  $\land$  is\_const(a)  $\land$  is\_const(b)  $\land$  is\_const(c)  $\land$  eval(oper(a, b), c); relabel\_node( $\pi, x = c$ )

#### Figure 3.2: A Morpheus Example

This is an existentially quantified sequence of a condition and an action. (Note that *oper* is a metavariable that will be bound to an arithmetic operator appearing in the program syntax, and eval(e,c) is a predicate asserting that the expression e evaluates to the constant c.) We may apply simple\_constant\_folding to a program with a node labeled diff = 10 - 2, and the transformation will match  $\pi$  to (the name of) this node, x to diff, a to 10, b to 2, *oper* to (op - ), and c to 8 (because of the clause is (c, oper(a, b))), and relabel the node to diff = 8.

#### 3.3 ISABELLE/HOL

Isabelle/HOL [19] is an interactive proof engine that allows users to prove properties about language specifications. The basis of Isabelle is high-order typed  $\lambda$ -calculus (System F). To prove that a theory in **IsaK** is equivalent to another one that was translated from the theory in **IsaK** by **TransK**, we define a simple Isabelle (based on simple typed  $\lambda$ -calculus) in Isabelle/HOL. A fragment of it is shown in Figure 3.3.

In Isabelle, we use a construct datatype to define a datatype. Variables beginning with the symbol "'" are type variables such as the 'tyVar in the datatype isaType. Constructor parameters begin with a capital letter, while type or function names begin with a lower case one.

```

datatype ('tyVar, 'tyConst) isaType =

TyVar 'tyVar

| TyConst "'tyConst" "('tyVar, 'tyConst) isaType list"

datatype ('tyVar, 'iVar, 'cVar) isaTerm =

VarTm 'tyVar 'iVar | Const 'tyVar 'cVar

| App "('tyVar, 'iVar, 'cVar) isaTerm" "('tyVar, 'iVar, 'cVar) isaTerm"

| Lambda 'iVar 'tyVar "('tyVar, 'iVar, 'cVar) isaTerm"

...

locale ITheory =

fixes TypeConsts :: "'tyConst set"

and Types :: "('tyVar, 'tyConst) isaType set"

and FunType :: "'tyConst"

...

assumes funTypeRule : "∀ a b . a ∈ Types ∧ a = TyConst FunType b ⇒ (length b = 2)"

...

```

Figure 3.3: A Simple Isabelle Theory

As in Standard ML, users are able to use the keywords primrec, fun and function to define a function. The difference is that a primrec function has a fixed structure so that it does not require termination proof; a fun function needs an automatic termination proof from Isabelle; and a function labeled function requires a programmer termination proof. Users are also able to use the keyword inductive to define transition rules for a transition system. The keywords lemma and theorem allow users to define theorems about datatypes, functions and inductive relations in Isabelle. The typical way to write theorems is with a combination of first-order logic and high-order Isabelle variables. In Figure 3.3, the assumption after funTypeRule provides a way to define a theorem in Isabelle. A locale (Fig. 3.3) is a special way to define a parameterized theory in Isabelle. The body of a locale is just a set of functions, inductive relations, or theorems. In the header of a locale, users are able to use keyword fixes to provide the locale with a list of different global data, while the keyword **assumes** can allow users to provide a list of assumptions that a system needs to satisfy in order to use the locale. In Figure 3.3, there is only one assumption, which means that any term with the constructor TyConst in the locale named ITheory must have two children.

#### 3.4 THE K FRAMEWORK

We will briefly introduce  $\mathbb{K}$  in this subsection.  $\mathbb{K}$  [76] is a rewrite-based executable semantic framework in which programming languages, type systems and formal analysis tools can be defined using configurations, computations and rules. For a given syntax and semantics of a language in  $\mathbb{K}$ ,  $\mathbb{K}$  can generate an interpreter, as well as some formal analysis tools. Most of the information about  $\mathbb{K}$  here is from the work of Li and Gunter [9].

(a) SYNTAX

$$Exp ::= Exp / Exp [strict(1)]$$

(b)  $\left\langle \langle \$ PGM : KItem \rangle_k \langle .Map \rangle_{env} \langle .Map \rangle_{heap} \right\rangle_{\langle \langle \langle K \rangle_{name} \langle .K \rangle_{body} \rangle_{classes}} \right\rangle_{\mathsf{T}}$

(c)

$$\left\langle \frac{X}{E} \right\rangle_{k} \langle \cdots X \mapsto N \cdots \rangle_{env} \langle \cdots N \mapsto E \cdots \rangle_{heap}$$

(d)  $\frac{X : Int / Y : Int}{X : Int / Int Y : Int}$

requires  $Y \neq 0$

$\begin{array}{l} \text{(e)} & \langle B:Bag \ \langle X \frown \kappa \rangle_{\mathsf{k}} \ \langle \rho_1, X \mapsto N, \rho_2 \rangle_{\mathsf{env}} \ \langle \rho_3, N \mapsto E, \rho_4 \rangle_{\mathsf{heap}} \rangle_{\mathsf{T}} \\ & \Rightarrow \langle B:Bag \ \langle E \frown \kappa \rangle_{\mathsf{k}} \ \langle \rho_1, X \mapsto N, \rho_2 \rangle_{\mathsf{env}} \ \langle \rho_3, N \mapsto E, \rho_4 \rangle_{\mathsf{heap}} \rangle_{\mathsf{T}} \end{array}$

(f) exp( X )  $\equiv$  aExp( X )

#### Figure 3.4: A Simple $\mathbb{K}$ Program

Figure 3.4 (a) shows how a syntactic definition is defined in  $\mathbb{K}$ . It uses the assignment operator (::=) to connect a target sort with a list of terminals or non-terminals. After that, K automatically generates a kLabel name (having the sort KLabel) representing the constructor and a sort *KList* term representing the argument list of the construct. Inside the bracket, K allows users to define attributes, some of which have semantic meanings. For example, the strict(1) attribute generates a pair of heat/cool rules for the first non-terminal position of the construct. Two features that  $\mathbb{K}$  uses to keep object language specifications succinct are localization and concision. Localization means to allow users to define language syntax by using conventional BNF annotated with semantic attributes, while the semantics based on the language syntax is given as a set of reduction equations and rules interpreted over a configuration, mentioning only those components accessed or altered by the rule. Figure 3.4 (b) is a very simplified version of the K-LLVM and Kaskell configuration. The configuration of a language is an algebraic structure of the program states, organized as nested labeled cells, in XML formats, holding semantic information, including the program itself. While the order of cells is irrelevant in a configuration (having a Bag sort in  $\mathbb{K}$ ), the contextual relations between cells are relevant and must be preserved by the rules defined by the users and subsequently "completed" by the compilation step in  $\mathbb{K}$  according to the configuration. Leaf cells represent pieces of the program state, like a computation stack or continuation (e.g., k), environments (e.g., env), heaps (e.g., heap), etc. A typical rule for reading a variable would be as in Figure 3.4 (c). There are three cells in the rule: k, env and heap. The content of the k cell symbolizes a computation sequence waiting to be performed, while the head element in the cell represents the next item to be computed. The env cell contains a map of variables to location numbers, while the cell heap

is a map of location numbers to expression values. The meaning of the above rule is that if the next computation to be executed is a variable lookup expression X, then we locate X in the environment to get its location number N in the location memory, and locate N in the heap to find its expression value E. Then we transform the computation into that value, E; the horizontal line represents a transition. A cell with no horizontal line means that it is read but not changed during the transition.

Concision in rule Figure 3.4 (c) in K refers to the "..." operator, which represents portions of cells that are irrelevant, and it could have different types depending on the context. This unconventional notation including its two features is useful in terms of allowing users to write less. The rule in Figure 3.4 (c) would be written out as the traditional rewrite rule (also allowed in  $\mathbb{K}$ ) shown in Figure 3.4 (e), which still relies on the  $\mathbb{K}$  configuration, but without localization and concision. We need to add the top cell T and a variable B with its sort Bag in the rule to indicate irrelevant program state pieces. Computations in the k cell are separated by " $\curvearrowright$ " (a built-in sort *KItem* list concatenation operator in  $\mathbb{K}$ ), which is now observable.  $\kappa$ ,  $\rho_1$ ,  $\rho_2$ ,  $\rho_3$ , and  $\rho_4$  take the place of "…". The most important thing to notice is that many parts of the rule are duplicated on the right-hand side. Duplication in a definition can lead to subtle semantic errors if users are not careful to synchronize changes in their specifications in multiple places. In a big language like C, Java or LLVM IR, the configuration structure is very complicated, and requires including more cells than a typical rule needs to mention. These intervening cells are automatically inferred in  $\mathbb{K}$ , which keeps the rules more succinct. Figure 3.4 (d) shows another way of defining rules in  $\mathbb{K}$ . A rule that does not mention any cell structure means that it matches the content of the head of the k cell. X: Int in the rule means that a variable X has sort Int. The keyword requires is a way of introducing a condition expression in a rule. Figure 3.4 (f) shows an equation in K. An equation forms an equivalence relation for two groups of ground terms represented by the parameterized terms on the two sides of the equation. In the example, we equate the ground terms represented by exp(X) with those represented by aExp(X).

Modularity is another important feature of K. Its module system can be classified as a set of separate files whose contents might not be related. In fact, the rules in Figure 3.4 could be put in a single module by adding a module name. In defining specifications, users usually do not need to modify the existing rules to add a new feature to the language. K maintains this feature by structuring its configuration as nested cells and by allowing users to design their specification rules by only mentioning the cells that are needed in those rules, indeed only the portions of those cells. For example, the above rule only refers to the k, env, and heap cells, while the entire configuration contains other cells (Figure 3.4 (b)). The modularity of K not only allows users to create a compact and humanly readable specification, but also speeds up the semantics development process. For example, the above lookup rule does not change, even though a new cell is added to the configuration to support a new feature. The modular system of  $\mathbb{K}$  also allows users to develop syntax and rules incrementally by defining a syntactic construct in one  $\mathbb{K}$  module with rules containing the construct in different  $\mathbb{K}$  modules.

Another important feature of K is the inherent support of non-determinism. K is based on rewriting logic [134], so users can easily define, execute, and reason about non-deterministic specifications in K. One example is the execution of multi-threaded programs in K-LLVM [135]. The execution of multi-threaded programs in K-LLVM results in two different thread cells, which represent two thread processes with their environment information. Typically, when we have two threads, we need to talk about the multi-threaded behaviors that occur when interleaving threads. By using the *ksearch* command in K, one can see the final results of executing the Thread-1 and Thread-2 programs with interleaving. By setting a proper step number and flag for the *ksearch*, one can also get the results of all traces of interleaved threads. In addition, by using the *krun* command, K fixes an order (the lexicographical order of the rule text) and produces a single trace for executing a K-LLVM program. In K-LLVM, We can use *ksearch* to collect the set of all final results, compare it with the set of expected results defined by the Pthread library, and see if the second one contains the first one.

### Chapter 4: THE SEMANTICS OF K AND ITS TRANSLATION TO ISABELLE

We introduce the semantics of  $\mathbb{K}$  (IsaK) and a translation procedure (TransK) from language specifications defined in IsaK to transformed specifications in Isabelle.  $\mathbb{K}$  is a domain specific language that takes a language specification as an input and generates an interpreter for the specification, including an execution engine to show trace behaviors of a program in the specification. There is a rich body of published work on  $\mathbb{K}$  itself [136], and specifications given in  $\mathbb{K}$ , such as the Java semantics [86], the Javascript semantics [85], the PHP semantics [84] and the C semantics [83, 137]. Despite the success of  $\mathbb{K}$ , there are issues. While there have been a number of papers published concerning theorems related to K, there is no source sufficiently complete to define the complete syntax and semantics of K, or allow for rigorous proofs of properties of the languages defined in  $\mathbb{K}$ . In addition, while  $\mathbb{K}$  supports specific tools for analyzing programs in a language defined in  $\mathbb{K}$ , it provides very little support for formal reasoning about the languages it defines. Finally, the fact that early versions of  $\mathbb{K}$  had features that were dropped in intermediate versions, only to be reintroduced in the latest versions, and different versions have displayed different behaviors unveils the fact that researchers in the  $\mathbb{K}$  community do not have a consensus on what  $\mathbb{K}$ is. As an answer for these problems, we have created a complete formal semantics of  $\mathbb{K}$ clarifying different aspects and features of  $\mathbb{K}$ .

Our contribution, a full, formal language specification of  $\mathbb{K}$ , called **IsaK**, addresses these concerns and forms the foundation of tools for the maintenance, revision, and expansion of  $\mathbb{K}$ . We also define a shallow embedding of  $\mathbb{K}$  into Isabelle (Sec. 4.5), named **TransK**, and prove that the embedded  $\mathbb{K}$  specification in Isabelle bi-simulates it original  $\mathbb{K}$  specification in **IsaK** (Sec. 4.6) for any specification defined in  $\mathbb{K}$ , so we now can define a language specification in  $\mathbb{K}$  and prove theorems about the specification in Isabelle. See Sec. 4.2 and 4.3.2 for more details.

Several benefits accure from our work. To the best of our knowledge, **IsaK** is the *first* complete semantics of  $\mathbb{K}$ . Other than the two simple descriptions of  $\mathbb{K}$  [76] and [138], there are no resources talking about its syntax or semantics. Indeed, all  $\mathbb{K}$  implementations contain some undesirable behaviors, so it is hard for us to learn the exact meanings of  $\mathbb{K}$  operators. In the process of defining  $\mathbb{K}$ , we needed to constantly interview the  $\mathbb{K}$  team to understand the meanings of the  $\mathbb{K}$  operators and look at the Java source code of the  $\mathbb{K}$  implementation to understand how  $\mathbb{K}$  was being defined, which was a time-consuming task.

To the best of our knowledge, **TransK** is the *first translation process* from an ordersorted algebraic system ( $\mathbb{K}$ ) to a many-sorted one (Isabelle). Previously, we have defined the general concepts for translating order-sorted terms into many-sorted ones [11]. **TransK** is the first complete formation of these general concepts on real-world systems (K and Isabelle). The result of translating specifications defined in K into Isabelle theories is the sudden marriage of the programming language field and the theory proving field. Now, we are able to define a formal language specification and learn about the formal meaning of the language in **IsaK**, then translate it into an Isabelle theory through **TransK** and prove inductive theories about the whole language in Isabelle. Before **TransK**, no K tools were able to handle this job. We want to define language specifications in K because of how much faster it is than defining them in Isabelle directly, and the several complete real-world specifications [83, 84, 85, 86, 137] in K are the proof. We want to prove theorems about such specifications in the theory translated by **TransK** because it is a lot simpler and clearer than the representations of these specifications in **IsaK**. See Sec. 4.5.2 for one example. All **IsaK** and **TransK** programs and theorems have been formalized and proved in Isabelle in the following link: https://github.com/liyili2/KtoIsabelle, and the implantation of **TransK** is defined as a Java and Ocaml combined program.

#### 4.1 A BREIF OVERVIEW OF **ISAK**

We briefly discuss  $\mathbb{K}$ 's current semantic layout. The formal semantics as it is presented in **IsaK** is divided into two parts: static and dynamic semantics. The static semantics takes as input the frontend-AST (FAST) representation of a user-defined language specification ( $\mathbb{K}$ /**IsaK** theory) or programs that are allowed by the specification. Through the translation process in the static semantics, which performs computations that can be done statically (referred to as compile-time operations), the  $\mathbb{K}$ /**IsaK** theory in FAST is processed and translated into a representation in backend-AST format (BAST). Then the type checking step in the static semantics outputs a type-checked BAST, which is passed to the dynamic semantics for execution. We first discuss some features of  $\mathbb{K}$  through an example below.

#### 4.1.1 An Example K Specification (Theory)

Here, we introduce  $\mathbb{K}$  as a language specification platform with the ability to automatically generate an interpreter for a specification. The operational behavior of the  $\mathbb{K}$  specification language contains four major steps: parsing, language compilation, sort checking, and semantic rewriting. Parsing itself comes in two phases: one to learn the grammar of the object language (the programming language being defined), and the second to incorporate that grammar into the grammar of  $\mathbb{K}$  for parsing the definitions of the rules and semantic objects defining the executable behavior of programs in the object language. These parsers translate the concrete syntax for both  $\mathbb{K}$  and the object languages defined therein into concrete syntax, eliminating mixfix syntax and other syntactic sugar in the process. The language compilation, sort checking and semantic rewriting are the major steps in **IsaK**. Here, we briefly introduce what a  $\mathbb{K}$  specification (theory) looks like.

```

Syntax

SYNTAX Exp ::= Var | Int | Exp / Exp [strict] | ... SYNTAX KResult ::= Int | Bool

SYNTAX BExp ::= Bool | Exp < Exp [strict] | BExp && BExp [strict] | ...

SYNTAX Stmt ::= Bloc | Var := Exp [strict(2)] | if (BExp) Bloc Bloc [strict(1)] | while (BExp) Bloc

Stmt ; Stmt | Var := thread(Stmt)

SYNTAX Bloc ::= {} | {Stmt} SYNTAX Prog ::= int Vars ; Stmt SYNTAX Vars ::= list{Var, ","}

Configuration

\left< \left< \left< \left< 0 \text{ ::Int} \right>_{key} \left< \$ pgm:: \operatorname{Prog} \right>_k \left< . \operatorname{Map} \right>_{env} \right>_{thread*} \right>_{threads} \right>_{threads} \right>_{0 > count} \left< . \operatorname{Map} \right>_{heap} \left< \operatorname{SetItem}(0) \right>_{keys} \right>_{\mathsf{T}} \right>_{threads} \right>_{\mathsf{T}}

Rules

\langle (x:: \mathsf{Var} \Rightarrow e) \cdots \rangle_{\mathsf{k}} \ \langle \because x \mapsto n \cdots \rangle_{\mathsf{env}} \ \langle \because n \mapsto e \cdots \rangle_{\mathsf{heap}}  (b) x:: \mathsf{Int} / y:: \mathsf{Int} \Rightarrow x / \mathsf{Int} y \text{ when } y \neq 0

(a)

\langle \cdots \langle (x := \texttt{thread}(t) \Rightarrow .K) \cdots \rangle_k \langle M \Rightarrow M[n/x] \rangle_{env} \cdots \rangle_{thread}

\begin{array}{l} \langle (\operatorname{int}(x, xs \Rightarrow xs); \_) \neg \rangle_{\mathsf{k}} \langle \cdots x \mapsto n \cdots \rangle_{\mathsf{env}} \\ \langle M \Rightarrow M [ \mathsf{0} / n ] \rangle_{\mathsf{heap}} \langle n \Rightarrow n + \mathsf{Int} 1 \rangle_{\mathsf{count}} \end{array} \tag{d} \begin{array}{l} ( .\mathsf{Bag} \Rightarrow \langle \cdots \langle t \rangle_{\mathsf{k}} \langle M \rangle_{\mathsf{env}} \langle \mathsf{fresh}(S, \mathsf{0}) \rangle_{\mathsf{key}} \cdots \rangle_{\mathsf{thread}} \\ \langle \cdots n \mapsto (\_ \Rightarrow \mathsf{fresh}(S, \mathsf{0})) \cdots \rangle_{\mathsf{heap}} \langle S \rangle_{\mathsf{keys}} \end{array}

(c)

(e)(\langle \cdots \langle key \rangle_{key} \langle .K \rangle_k \cdots \rangle_{thread} \Rightarrow .Bag) \langle S \Rightarrow S \setminus \{key\} \rangle_{keys}

Function and Function Rules

SYNTAX Int ::= fresh(Set, Int) [function]

(f) fresh(.Set, n) \Rightarrow n +Int 1 (g) fresh(SetItem(n::Int) S, m) \Rightarrow fresh(S, n) when m < \text{Int } n (i) fresh(SetItem(n::Int) S, m) \Rightarrow fresh(S, m) when m >= \text{Int } n

Heating/Cooling Rule Example

Expanded Configuration Rule

\left\langle \begin{array}{c} C_1::\mathsf{Bag}\left\langle \left\langle \left\langle x \curvearrowright \kappa \right\rangle_{\mathsf{k}} \right. \left\langle \rho_1, x \mapsto n, \rho_2 \right\rangle_{\mathsf{env}} \left. C_2::\mathsf{Bag} \right\rangle_{\mathsf{thread}} \right\rangle_{\mathsf{threads}} \\ \left\langle \rho_3, n \mapsto e, \rho_4 \right\rangle_{\mathsf{heap}} \end{array} \right\rangle \mathsf{T}

(i)

\Rightarrow \left\langle \begin{array}{c} C_1::\mathsf{Bag} \left\langle \left\langle \left\langle e \frown \kappa \right\rangle_{\mathsf{k}} \left\langle \rho_1, x \mapsto n, \rho_2 \right\rangle_{\mathsf{env}} C_2::\mathsf{Bag} \right\rangle_{\mathsf{thread}} \right\rangle_{\mathsf{threads}} \\ \left\langle \rho_3, n \mapsto e, \rho_4 \right\rangle_{\mathsf{heap}} \end{array} \right\rangle_{\mathsf{T}}

An Example Execution In IMP

Program: int x; x := 1

\begin{array}{l} & \begin{array}{l} & \text{Configuration After One Step (Rule (c)):} \\ & \left< \left< \left< \left< 0 \right>_{key} \left< \text{int .Ids ; } x := 1 \right>_k \left< x \mapsto 0 \right>_{env} \right>_{thread} \right>_{threads} \right>_{threads} \\ & \left< 1 \right>_{count} \left< 0 \mapsto 0 \right>_{heap} \left< \text{SetItem(0)} \right>_{keys} \right>_{T} \end{array} \right.

Initial Configuration:

\begin{array}{c} & \left\langle \left\langle \left\langle \left\langle 0 \right\rangle_{key} \left\langle \texttt{int } x \texttt{ ; } x \texttt{:= 1} \right\rangle_k \left\langle .\texttt{Map} \right\rangle_{env} \right\rangle_{thread} \right\rangle_{threads} \\ & \left\langle 0 \right\rangle_{count} \left\langle .\texttt{Map} \right\rangle_{heap} \left\langle \texttt{SetItem(0)} \right\rangle_{keys} \end{array} \right\rangle \mathsf{T}

```

Figure 4.1: A Summary of  $\mathbb{K}$  By IMP

Fig. 4.1 contains a small language specification, named IMP, with most of its syntax and some semantic definitions. In IMP, all program variables are heap ones that can be shared through different threads. In K, the keyword SYNTAX introduces a finite set of syntactic definitions, separated by "|", such as the definition of the sort Exp. Each syntactic definition is a list of names. The names in Sans serif font are non-terminals (sorts), while the names in tt font are terminals. A syntactic definition (e.g. Exp ::= Var) introducing only a singleton sort defines a subsort relation subsorting the singleton sort (Var) to the target sort (Exp). The subsort definition that subsorts sorts to KResult defines the evaluation result sorts in a specification. Other kinds of syntactic definitions introduce syntactic definitions as user defined terms used to express rules and programs. Every real syntactic definition (not subsorting) creates a prefix AST format like KLabel (KList), where the KLabel term acts as the constructor automatically generated from the terminals and the structure of the definition, and the *KList* term is the argument list generated from the non-terminals of the definition. K allows users to define attributes (written in brackets e.g. [strict] in Fig. 4.1), some of which have semantic meanings. For example, the strict(2) attribute (in the definition: Var := Exp [strict(2)]) means to generate a pair of heating/cooling rules for the second non-terminal position of the term created by the definition. We show an example pair of heating/cooling rules for the first non-terminal position of the "/" operator in Fig. 4.1. The [strict] attribute without any numbers indicates there is a pair of heating/cooling rules generated for each non-terminal position in the definition. " $\cap$ " is a list concatenation operator for connecting the computation sequence in a k cell, while " $\Box$ " is a special builtin operation in K representing the removal of a redex subterm from a term and the creation of a "hole" waiting to be filled. The syntax definitions in a K theory are compiled by the IsaK static semantics (Sec. 4.2) into a sort set, a symbol table, a subsort relation and several heating/cooling rules as inputs for the IsaK dynamic semantics in Sec. 4.3.

The initial configuration of a specification is an algebraic structure of the program states, organized as nested, labeled cells, in XML formats that hold semantic information, including the program itself (prefixing by the \$ operator in Fig. 4.1). While the order of cells in a configuration is irrelevant, the contextual relations between cells are relevant and must be preserved by rules defined by users and subsequently "completed" in the compilation step in K according to the configuration. In a trace evaluation, each step of computation should produce a result state that "matches" the structure of the initial configuration, meaning that the cell names, sorts of cells, and structural relations of the cells are the preserved in the result states and the initial configuration. Leaf cells represent pieces of the program state, like computation stacks or continuations (e.g., k), environments (e.g., env), heaps (e.g., heap), etc. The content in each cell in an initial configuration has dual roles. It is the initial value defined for the computation and also defines the sort of the cell content. For example, the key cell in the IMP configuration in Fig. 4.1 is defined as 0 and sort Int; during an evaluation, the cell's initial value is 0, and in every state of the evaluation, its content has sort Int. The last part of Fig. 4.1 provides an example program in IMP combined with its initial configuration. After evaluating the initial configuration by rule (c) in IMP, the contents of several cells are updated, but the structure relations and sorts of the cells do not change during the evaluation.

Fig. 4.1 also contains a set of IMP rules. The simplest form of rules, such as rule (b), describe behaviors that can happen in the first element position in a k cell, without mentioning any cells and without mentioning the tail of the computation list of the k cell. A little more complicated form of rules, such as rules (heat) and (cool), mention the tail

of the computation list (connecting by " $\curvearrowright$ "). They describe behaviors that can happen in a k cell, especially the relationship among different positions in the computation list. In BAST format, these two kinds of rules are compiled to the same form (K rules). The most complicated form of rules, such as rule (a), are typical configuration rules in K and they describe interactions among different device components in a system. For example, rule (a) is reading from a value in the main memory (the heap cell) for a variable in the k cell through an local stack (env). The "…" operator in these rules represents portions of cells that are irrelevant. This unconventional notation allows users to write less.

In this thesis, we focus on the dynamic semantics of K. All these unconventional configuration rules are assumed to be compiled to a standard form (BAST form) by the **IsaK** static semantics (Sec. 4.2), and the dynamic semantics is defined based on the compiled format. For example, the rule (a) is compiled to rule (j). In translating (a) to (j), we would need to add the cells T, thread, threads in rule (j) and the variables  $C_1$  and  $C_2$  with its sort **Bag**, to indicate the irrelevant program state pieces. Computations in the k cell are separated by " $\curvearrowright$ ", which is now observable in (j). The  $\kappa$  and  $\rho_1$ ,  $\rho_2$ ,  $\rho_3$ , and  $\rho_4$  fill in the place corresponding to the "…" in rule (a).

In  $\mathbb{K}$ , configuration rules are also powerful enough to manipulate language device resources. For example, rules (d) and (e) create or finish a thread by adding or deleting a thread cell. These are handled by rewriting an empty Bag place (.Bag) to a new cell thread (rule (d)), or rewriting a thread cell to an empty place (rule (e)). In  $\mathbb{K}$ , this is allowed only if the specific cell in the initial configuration (e.g. the configuration in Fig. 4.1) is marked as "\*".

K also allows users to write equational rules, named function rules. The format is like the fresh definition in Fig. 4.1. Its syntactic definition (e.g. fresh) is labeled by an attribute function, and then the rules whose left-hand top-most constructor is the same as the  $\mathcal{K}_{Label}$  term syntactic definition are recognized by K to be the function rules under the function definition. The left-hand-side of a valid function rule has argument sorts subsorting to the argument sorts defined in the function definition, and the target sort of the right-hand-side subsorts to the target sort of the definition. All these rules are compiled to standard BAST forms (described in Sec. 4.3.1) and stored in a rule set as the input for IsaK dynamic semantics.

#### 4.1.2 Challenges of Defining K Specification

Several formidable challenges are faced by the **IsaK** project. First, other than the two simple descriptions of  $\mathbb{K}$  [76] and [138], there are no resources talking about its syntax and semantics, as we have mentioned in the beginning of the Chapter.

Second, the  $\mathbb{K}$  implementations usually contain a front-end language and a back-end language that perform different tasks. The allowed syntactic definitions for users in the  $\mathbb{K}$ front-end is strictly larger than the allowed syntactic definitions in the  $\mathbb{K}$  back-end. More precisely, there are some constructs and semantic rules in  $\mathbb{K}$  that users think they can define but are in fact not supported by K. K implementations sometimes produce no error messages or warnings about these limits, so users have no way to figure out if there is something wrong in their specifications or there are some problems in  $\mathbb{K}$ . For example, in the configuration [86], we can see that the class cell is associated with the key word \*, and in the class cell, the methodDec cell is also labeled with the key word \*. This means that it can have multiple class cells and methodDec cells when we define a Java rule or evaluate a Java program by using this rule in  $\mathbb{K}$ . When we interpret Java programs in  $\mathbb{K}$ , we find that a rule mentioning two nested cells both having the key word \* is actually not valid in K, even if someone can define two such cells nested together in a rule. If users define this kind of rule in their specifications and use *krun* to run the testing programs, once the program triggers the rule, krun crashes immediately without giving any valid error messages. More surprisingly, if users write a Java rule to add a method definition to a specific class (a cell with \*), and run their testing programs, when *krun* triggers the rule the first time, it works, but it fails the second time in the current  $\mathbb{K}$  implementation. Users will have no clue what is going on here. The problem is a poor design decision made by the  $\mathbb{K}$  team. In their early  $\mathbb{K}$  implementation in Maude, the nested cell feature was supported. When they implemented  $\mathbb{K}$  in Java, they decided not to support this feature because it would slow down the generated interpreter for a language specification in K. However, since some big languages such as Java have used this feature, they decided to partially support it in their Java implementation, but gave no information on the boundaries of what is and is not allowed for it.

Third, the path compiling from the front-end language in  $\mathbb{K}$  to the back-end one is not so clear. In the implementation of  $\mathbb{K}$  4.0 (in Java), there are 48 compilation steps to compile the front-end language to the back-end one. These 48 steps have different tasks. To understand the different tasks, and combine all of them in **IsaK** is a tough job to do.

Fourth, one of the best features of  $\mathbb{K}$  is the modularity system, but it is also one of the hardest to understand in  $\mathbb{K}$ . Resolving the modularity in each rule is a compilation step in the  $\mathbb{K}$  implementation. The basic idea of the compilation step is to take the configuration in a language specification, compare it with a given rule, and fill the missing pieces in the rule to make the rule "complete". The problem is that adding the missing pieces is not so trivial. For example, there are two ways to define a rule for removing the existence of all holding locks in a thread based on the Java configuration [86] in Fig. 4.2.

At first glance, people might think that the left-hand side rule (Rule 1) and the right-hand

$$\left\langle \cdots \ \left\langle \begin{matrix} M \\ \hline \end{matrix} \right\rangle_{\mathsf{holds}} \ \left\langle X \right\rangle_{\mathsf{tid}} \ \cdots \right\rangle_{\mathsf{thread}} \qquad \frac{\left\langle \cdots \ \left\langle M \right\rangle_{\mathsf{holds}} \ \left\langle X \right\rangle_{\mathsf{tid}} \ \cdots \right\rangle_{\mathsf{thread}}}{\left\langle \cdots \ \left\langle \cdot \right\rangle_{\mathsf{holds}} \ \left\langle X \right\rangle_{\mathsf{tid}} \ \cdots \right\rangle_{\mathsf{thread}}}$$

Figure 4.2: An Example Configuration From The Java Semantics [86]

side rule (Rule 2) are the same in Fig. 4.2, but they are not. Rule 1 means that in a given thread with id X, we remove all its holds. Rule 2 means that for a given thread with id X, except the tid cell, we discard all the program states in the thread and initialize them with the ones in the initial configuration, such as the one in Figure 4.1. Specifically, we remove all locks in the holds cell. The main problem here is that the "…" is not a simple syntactic sugar when it is associated with  $\mathbb{K}$  cells. The compilation of the "…" in the  $\mathbb{K}$  cells level desires a well-defined algorithm to accomplish this problem properly.

Nevertheless, even if these challenges are many and hard, **IsaK** is defined without compromise and includes every feature of  $\mathbb{K}$ .

#### 4.2 THE STATIC SEMANTICS OF ISAK

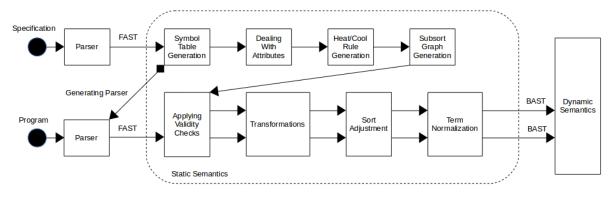

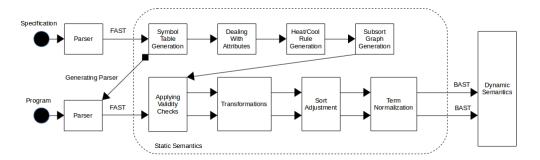

We briefly introduce the static semantics of  $\mathbb{K}$  in this section and will discuss some design issues of  $\mathbb{K}$ , especially  $\mathbb{K}$  modularity, localization and concision features in the next section. The static semantics of  $\mathbb{K}$  describes how we compile away the localization, concision and modularity features of  $\mathbb{K}$  to a uniformed backend AST. It contains several phases, as listed in Figure 4.3. Each phase digs deeper into the syntactic structure of  $\mathbb{K}$  and either performs a set of transformations over the user-defined  $\mathbb{K}$  specifications or applies some checks on the input FAST of the specifications.

We assume that there is an external parser that parses user-input  $\mathbb{K}$  object language specifications and object level programs to a FAST format. The parser is divided into two phases. In the first phase, it uses ocamllex and ocamlyacc (variants of lex and yacc for Ocaml) to read all syntactic definitions in a given specification, and then generates a symbol table based on the syntactic definitions. In the second phase, it uses the symbol table to generate lexers and parsers in the formats of ocamllex and Dypgen (a general LR parser) to parse rewrite rules and programs for the specification. The two-phase parser is a direct copy of the K parser (SDF-to-K adapter [139]) and is intended to be suitable for the OCaml-based K implementation extracted directly from **IsaK** in Isabelle.

After the parsing, the static semantics takes as input the FAST representation of a user-

defined language specification or programs that are allowed in the specification. Through the translation process in the static semantics, which performs computations that can be done statically (referred to as compile-time operations), the specification in FAST is processed and translated into a representation in BAST. Then the sort adjustment step in the static semantics outputs a sort-adjusted BAST, which is passed to the dynamic semantics for execution.