# A SELF-CALIBRATED POWER DETECTOR AND CURRENT SENSOR FOR USE IN A

## POWER AMPLIFIER CONTROL CIRCUIT

A Thesis

by

## JAMES KEITH LUNSFORD

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

| Chair of Committee,    | Aydin Karsilayan    |

|------------------------|---------------------|

| Co-Chair of Committee, | Jose Silva-Martinez |

| Committee Members,     | Robert Nevels       |

|                        | Jay Porter          |

| Head of Department,    | Miroslav Begovic    |

December 2018

Major Subject: Electrical Engineering

Copyright 2018 James Lunsford

### ABSTRACT

The power amplifier in a transmitter, especially high-power transmitters, generally uses more power than any other component in the signal chain. As a result, large power savings can be achieved if the efficiency of the power amplifier is optimized. Additionally, power amplifiers in high-power transmitters generally experience substantial amounts of reliability-reducing stress such as high temperature operation. Given these considerations, a power amplifier control loop is proposed which will calculate various parameters of the amplifier, such as the power-added efficiency. This control loop will then adjust the input power and DC bias current of the power amplifier to maximize the efficiency while also ensuing the amplifier is not placed in a situation where its reliability is compromised. This thesis will discuss the design of two major blocks that are required in this control loop: a DC bias current sensor and a power detector.

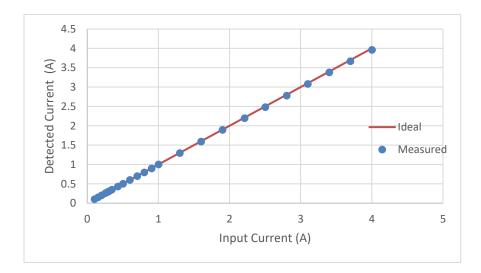

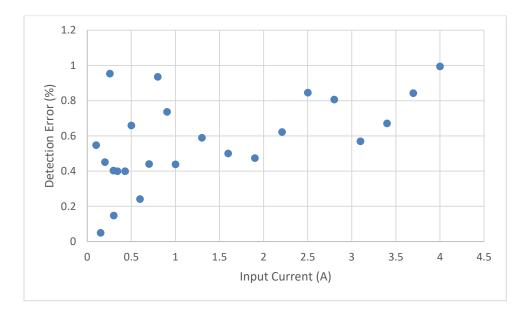

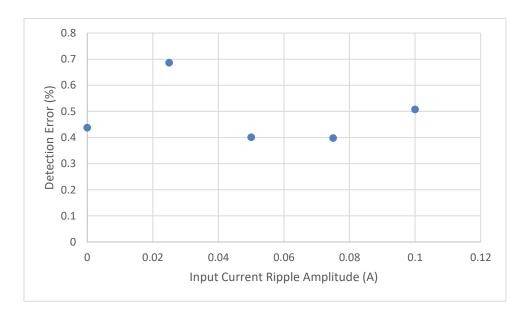

The DC bias current sensor must accurately measure the DC bias of the power amplifier since this current is used to calculate the DC power dissipation for the power-added efficiency. In order to ensure the DC current sensor's output is accurate over a wide temperature range, a reference current calibration scheme is introduced. The fabricated current sensor is able to achieve a measurement accuracy of +/-1% over a current range from 100mA to 4A.

The power detector must measure the input and output power of the power amplifier since the power added efficiency takes into account the gain of the amplifier. The proposed power detector utilizes an on-chip reference generator in order to calibrate the peak detector used and provide an accurate and absolute power level. The simulated power detector is able to provide an accuracy of +/-0.5dB over a dynamic range of 40dB. These two designs will be incorporated in the overall power amplifier control system in future work.

#### ACKNOWLEDGEMENTS

I would firstly like to thank my parents for all of the love and support they have shown me through the years. I am so blessed to be able to call you guys mom and dad, and I am so thankful that you raised me in a home where I was pushed to work hard, try my best, and trust the rest into God's hands. The completion of this journey would not have been possible without your encouragement and support, and I will forever be grateful for the countless ways you have blessed Elaine and me.

To my siblings and their wonderful spouses: thank you for all of the laughs and the good times we have had over my years at Texas A&M. I am incredibly blessed to have a family that supports me so well and that models hard work so clearly. Thank you for encouraging me to do what I love, even if that means a couple extra years at school. I am so thankful for the memories we have made, and I look forward to the memories we will make in the future.

I'd also like to thank all of my friends that have been with me throughout my time here. All of the laughs and good times that we have had will be with me forever, and I thank God every day for the people he has placed in my life. I look forward to growing in our friendship throughout the rest of our lives, and I hope that we can continue to encourage each other and laugh with each other for years to come.

Last, but certainly not least, I would like to thank my wonderful wife, Elaine. You have shown me so much patience and love throughout my time here at Texas A&M, and I am so thankful to have such an amazing wife to go through life's ups and downs with.

You have been a constant source of encouragement, and I know I would not be where I am today without you by my side. God blessed me immensely when he brought you into my life, and I am a better person as a result of it. We have made so many amazing memories so far in our relationship, and I am so excited to get to be by your side as we see where God takes us in the future.

### CONTRIBUTORS AND FUNDING SOURCES

This work was supported by a dissertation committee consisting of the thesis advisor Professor Karsilayan and the thesis co-advisor Professor Silva-Martinez of the Department of Electrical Engineering. It was also supported by Professor Nevels of the Department of Electrical Engineering as well as Professor Porter of the Department of Engineering Technology and Industrial Distribution.

The previous power detector architecture discussed in Section 4.1 and whose measurements are discussed in Section 4.3 was designed by Clayton Bridge with help from the author of this thesis. All laboratory measurements discussed in Section 4.3 were obtained by the author of this thesis.

Graduate study was supported by a fellowship from the Texas A&M University Department of Electrical and Computer Engineering as well as funding from Sandia National Laboratory.

# TABLE OF CONTENTS

| ABSTRACTii                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiv                                                                                                                                                                                                                                                                                                         |

| CONTRIBUTORS AND FUNDING SOURCES                                                                                                                                                                                                                                                                                           |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                          |

| LIST OF FIGURESix                                                                                                                                                                                                                                                                                                          |

| LIST OF TABLES xii                                                                                                                                                                                                                                                                                                         |

| 1. INTRODUCTION1                                                                                                                                                                                                                                                                                                           |

| 1.1. Motivation       1         1.2. Organization of the thesis       5                                                                                                                                                                                                                                                    |

| 2. INTRODUCTION TO POWER DETECTORS AND CURRENT SENSORS                                                                                                                                                                                                                                                                     |

| 2.1. Power Detectors62.1.1 RMS Power Detectors92.1.2 Peak Power Detectors152.2 Current Sensors19                                                                                                                                                                                                                           |

| 3. PROPOSED CURRENT SENSOR                                                                                                                                                                                                                                                                                                 |

| 3.1 Current Sensor Architecture273.2.1 Problem Description273.2.2 Architecture Overview293.2 Implementation of Current Sensor403.1.1 Input Buffer403.1.2 ADC483.1.3 Reference Current Source583.1.4 Level-Shifting Capacitors673.1.5 Digital Control Block703.1.7 Top-Level Simulations743.3 Current Sensor Measurements76 |

| 4. PROPOSED POWER DETECTOR                                                                                                                                                                                                                                                                                                 |

| 4.1 Power Detector Architecture      | 85  |

|--------------------------------------|-----|

| 4.1.1 Problem Description            |     |

| 4.1.2 Architecture Overview          |     |

| 4.2 Implementation of Power Detector |     |

| 4.2.1 Peak Detectors                 |     |

| 4.2.2 Sine-Wave Generator            |     |

| 4.2.3 Amplifier                      |     |

| 4.2.4 ADC                            |     |

| 4.2.6 Digital Controller             |     |

| 4.2.5 Top-Level Simulations          |     |

| 4.3 Power Detector Measurements      | 119 |

| 5. SUMARY AND CONCLUSIONS            |     |

| REFERENCES                           |     |

# LIST OF FIGURES

Page

| Figure 1: Power Amplifier Control System Overview                    |

|----------------------------------------------------------------------|

| Figure 2. Standard Transmitter Chain with Power Detector4            |

| Figure 3. Typical PA Current Measurement Setup5                      |

| Figure 4. Comparison Between Various Power Definitions9              |

| Figure 5. Basic Translinear Loop12                                   |

| Figure 6. Peak Detector Schematic13                                  |

| Figure 7. Diode-based Peak Detector16                                |

| Figure 8. Typical Series-Resistor Sensing Scheme21                   |

| Figure 9. Basic Sense-FET Scheme                                     |

| Figure 10. Capacitor-Based Current Sensor Operation26                |

| Figure 11. Copper Resistivity over Temperature29                     |

| Figure 12. Current Sensor Architecture                               |

| Figure 13. Level Shifting Capacitors                                 |

| Figure 14. ADC and Supporting Circuitry                              |

| Figure 15. Effect of Chopping on the DC Input Signal                 |

| Figure 16. Input Square Wave with Moving-Average Filter Responses    |

| Figure 17. Input Noise and Output Noise after Moving-Average Filters |

| Figure 18. Reference Current Calibration Circuit                     |

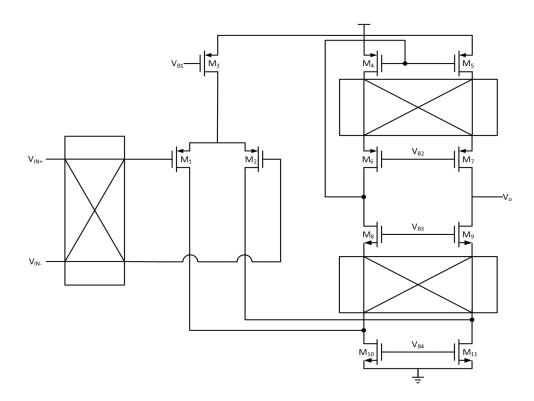

| Figure 19. Fully-Differential Differential Difference Amplifier42    |

| Figure 20. FDDA Schematic43                                          |

| Figure 21. CMFB Circuit for FDDA44                                   |

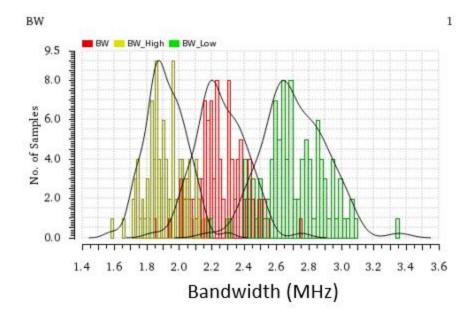

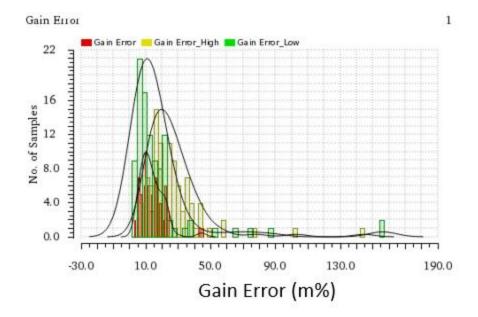

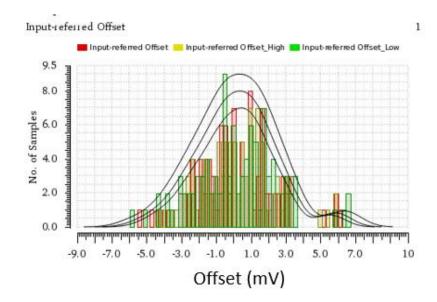

| Figure 22. FDDA Buffer Bandwidth Results                             |

| Figure 23. FDDA Buffer Gain Error Results                                   | 46 |

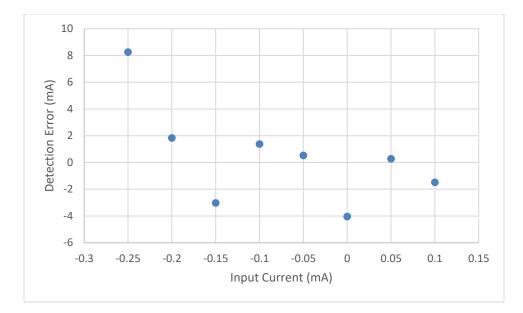

|-----------------------------------------------------------------------------|----|

| Figure 24. Buffer Offset Simulations                                        | 47 |

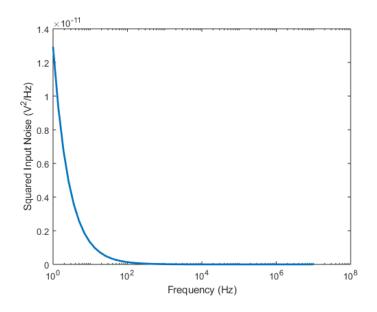

| Figure 25. Buffer Squared Input Noise                                       | 47 |

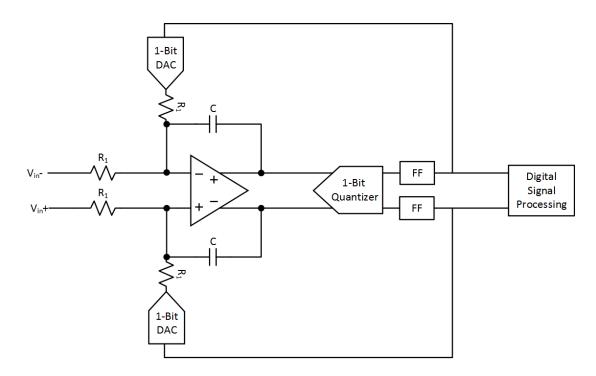

| Figure 26. ADC Topology                                                     | 48 |

| Figure 27. Loop Filter Op-amp                                               | 51 |

| Figure 28. CMFB Amplifier for Loop Filter Op-amp                            | 52 |

| Figure 29. Loop Filter Op-amp Bandwidth                                     | 52 |

| Figure 30. Loop Filter Op-amp Phase Margin                                  | 53 |

| Figure 31. Loop Filter Op-amp Gain                                          | 54 |

| Figure 32. Strong-ARM Comparator                                            | 55 |

| Figure 33. Falling Delay of Quantizer                                       | 56 |

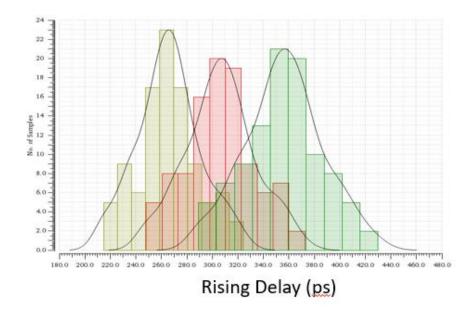

| Figure 34. Rising Delay of Quantizer                                        | 57 |

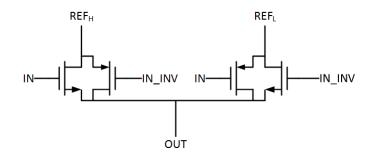

| Figure 35. 1-bit DAC                                                        | 57 |

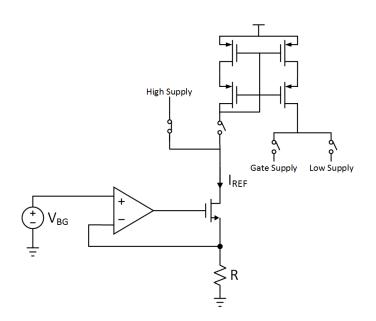

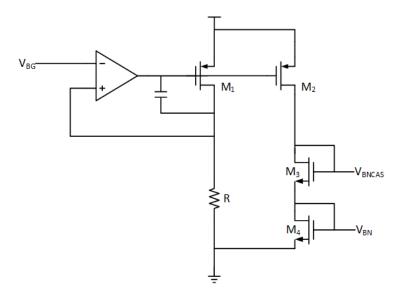

| Figure 36. Reference Current Source Schematic                               | 58 |

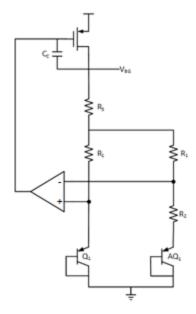

| Figure 37. Bandgap Voltage Reference Schematic                              | 60 |

| Figure 38. Chopper-Modulated Op-Amp                                         | 61 |

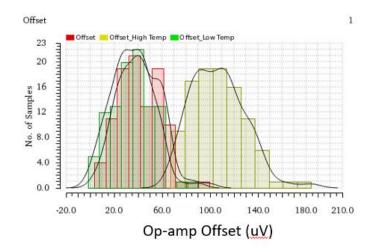

| Figure 39. Bandgap Op-amp Offset                                            | 62 |

| Figure 40. Bandgap Output Voltage                                           | 63 |

| Figure 41. Reference Current Source Current Mirror                          | 64 |

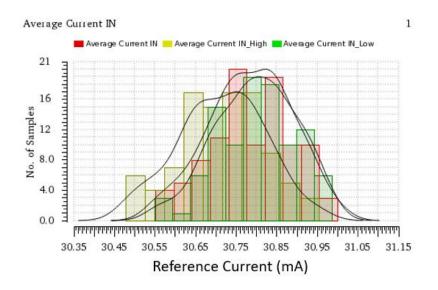

| Figure 42. Reference Current Output                                         | 65 |

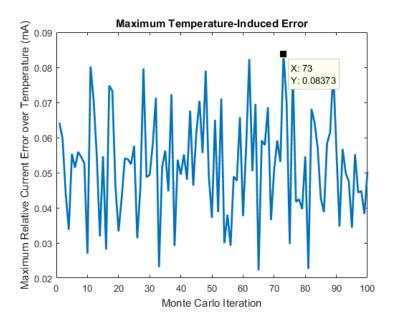

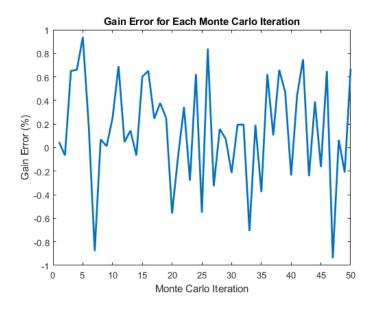

| Figure 43. Maximum Temperature-Induced Error for each Monte-Carlo Iteration | 66 |

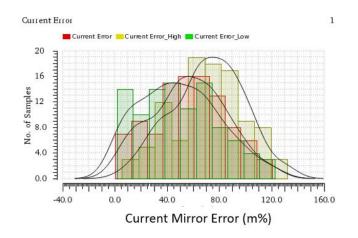

| Figure 44. Current Mirror Mismatch Error                                    | 66 |

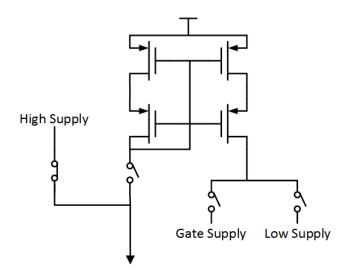

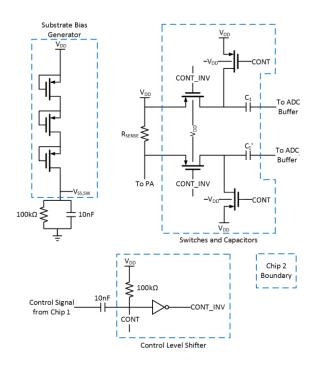

| Figure 45. V <sub>DD</sub> Interface Chip                                   | 67 |

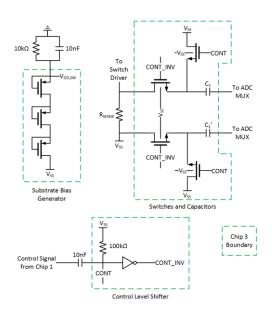

| Figure 46. Interface Chip Schematic for Negative and Gate Supplies          | 69 |

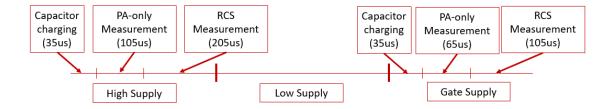

| Figure 47. Sensor Measurement Timing                                   | 70 |

|------------------------------------------------------------------------|----|

| Figure 48. Reference Current Source Protection                         | 71 |

| Figure 49. Buffer Interface Protection                                 | 73 |

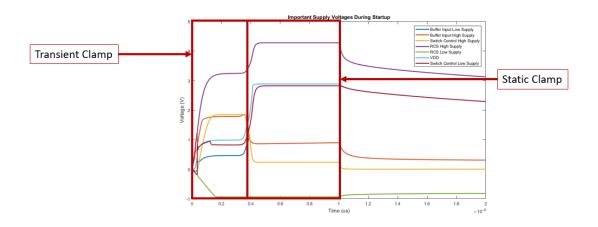

| Figure 50. VDD Static and Transient Clamps                             | 73 |

| Figure 51. Interface Voltages During Startup                           | 74 |

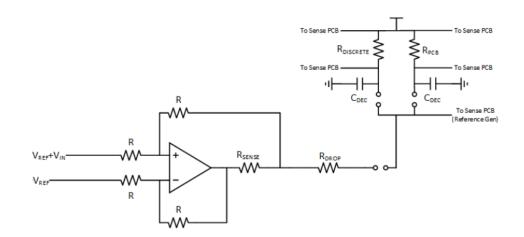

| Figure 52. Current Source PCB Schematic                                | 76 |

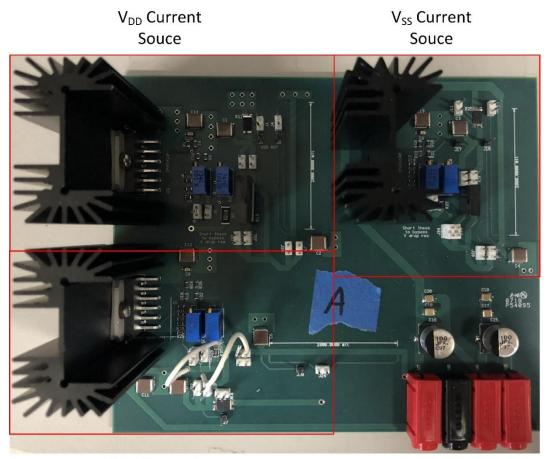

| Figure 53. Current Source PCB                                          | 77 |

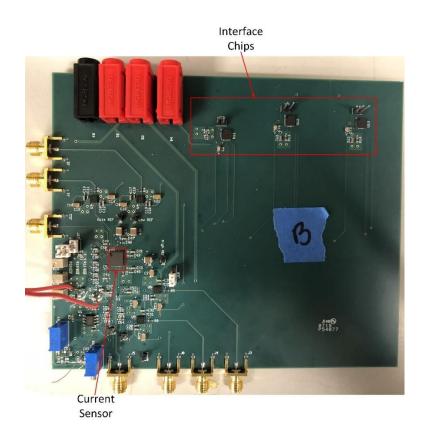

| Figure 54. Current Sensor PCB                                          |    |

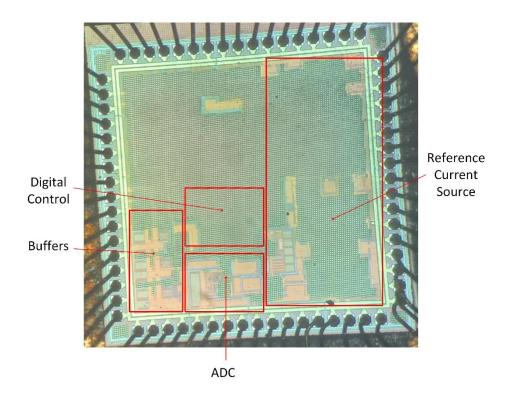

| Figure 55. Current Sensor Chip Micrograph                              | 79 |

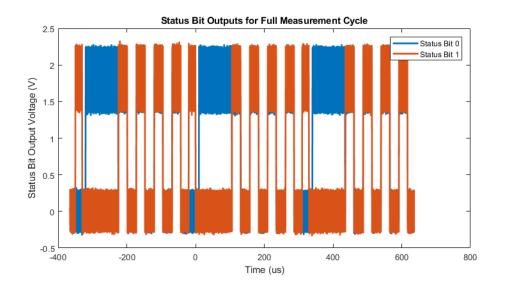

| Figure 56. Current Sensor Status Bits                                  | 80 |

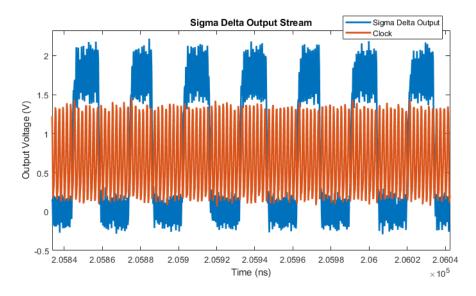

| Figure 57. Sigma-Delta Output Bit stream                               | 81 |

| Figure 58. Detected Current from Current Sensor                        | 81 |

| Figure 59. Detection Error for DC Input                                |    |

| Figure 60. Detection Error for Various Input Current Ripple Amplitudes | 83 |

| Figure 61. Detection Error for V <sub>SS</sub> Supply                  | 84 |

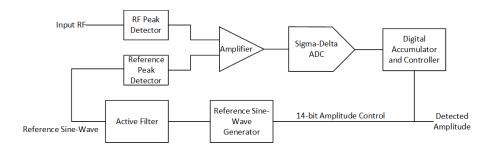

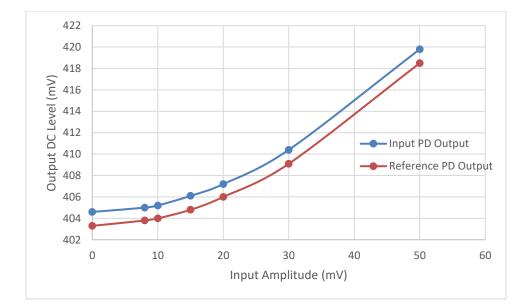

| Figure 62. Previous Power Detector Architecture                        |    |

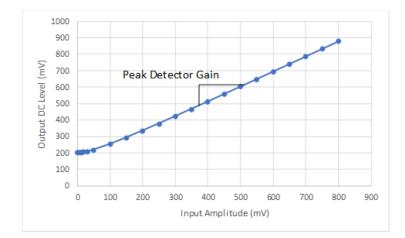

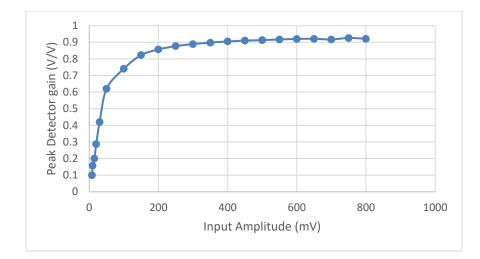

| Figure 63. Peak Detector DC Output vs. Input Amplitude                 |    |

| Figure 64. Peak Detector Gain                                          | 90 |

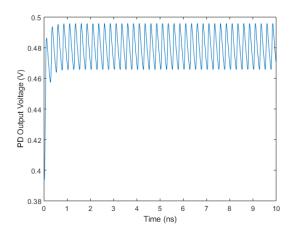

| Figure 65. PD Output Showing Significant Ripple                        | 91 |

| Figure 66. Proposed Peak Detector Architecture                         | 92 |

| Figure 67. Peak Detector                                               | 93 |

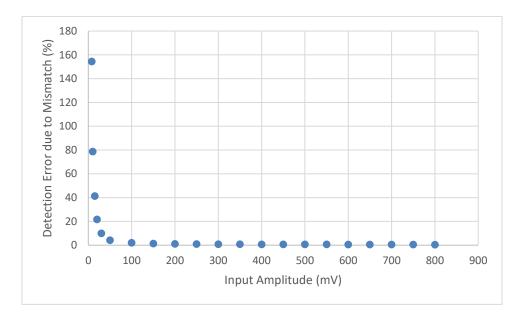

| Figure 68. Peak Detector Outputs with Mismatch                         | 97 |

| Figure 69. Amplitude Detection Error due to Mismatch                   | 98 |

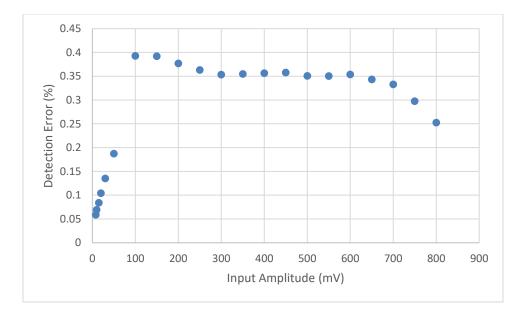

| Figure 70. Amplitude Detection Error with Offset Correction            | 99 |

|                                                                        |    |

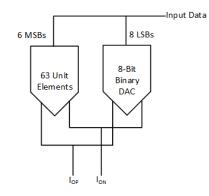

| Figure 71. DAC Topology                                    | 100 |

|------------------------------------------------------------|-----|

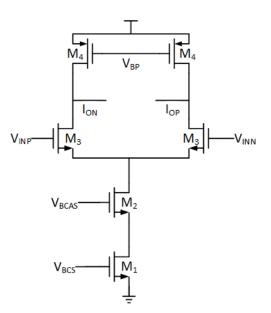

| Figure 72. DAC Element                                     | 102 |

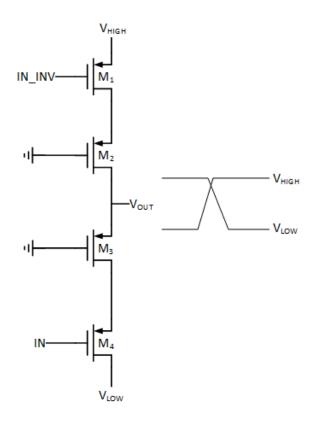

| Figure 73. High-Crossing Switch Driver                     | 103 |

| Figure 74. DAC Bias Generator                              | 104 |

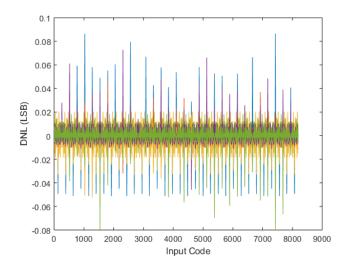

| Figure 75. DAC DNL                                         | 105 |

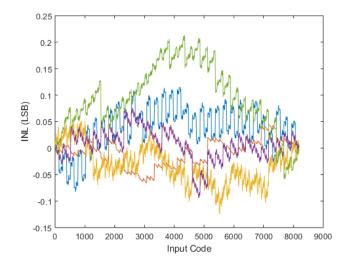

| Figure 76. DAC INL                                         | 105 |

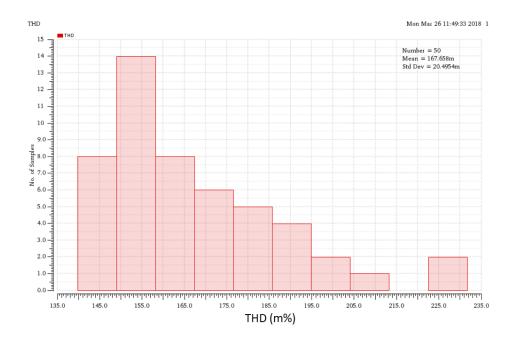

| Figure 77. DAC Filter Output THD                           | 106 |

| Figure 78. DAC Output Amplitude Variation                  | 107 |

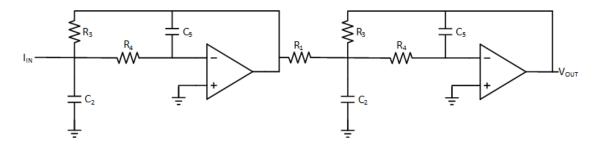

| Figure 79. Filter Schematic                                | 107 |

| Figure 80. Filter Op-amp                                   | 109 |

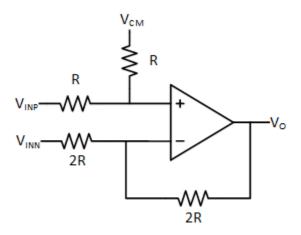

| Figure 81. Differential to Single-Ended Converter          | 110 |

| Figure 82. Rail-to-Rail Operational Amplifier              | 111 |

| Figure 83. Filter Tuning Results                           | 112 |

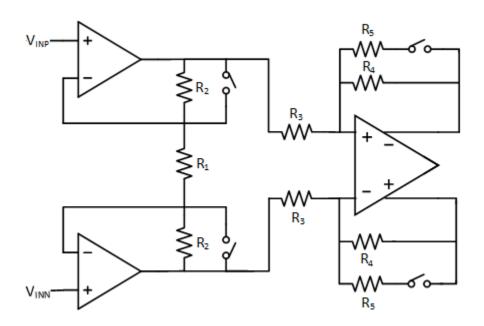

| Figure 84. Amplifier with Gain Control Switches            | 114 |

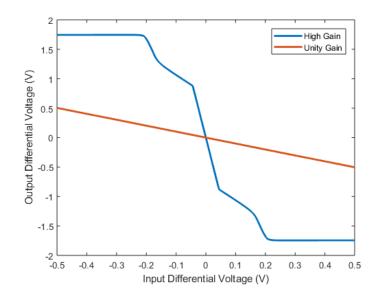

| Figure 85. Output Voltage for Instrumentation Amplifier    | 115 |

| Figure 86. Gain for Instrumentation Amplifier              | 116 |

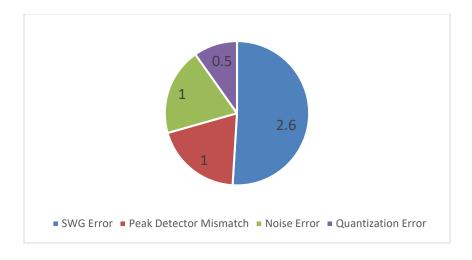

| Figure 87. Error Distribution in Percent of Power Detector | 118 |

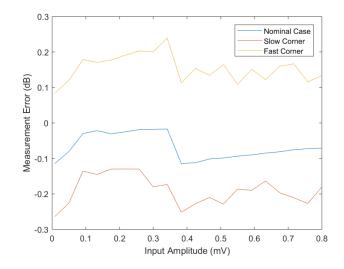

| Figure 88. Top-Level Simulation Error Results              | 119 |

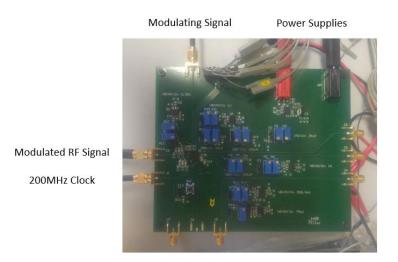

| Figure 89. Power Detector Test PCB                         | 120 |

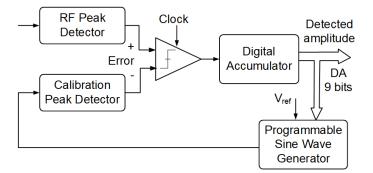

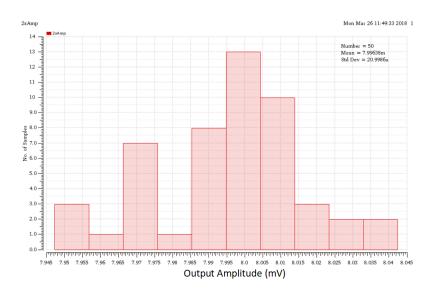

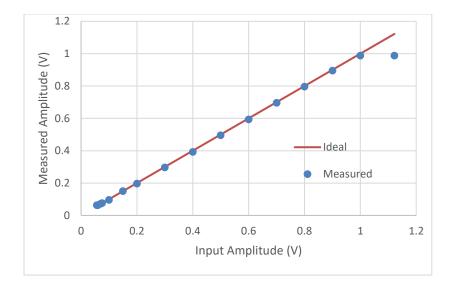

| Figure 90. Measured Amplitude from Power Detector          | 121 |

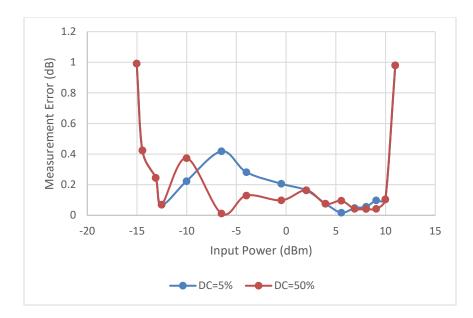

| Figure 91. Measurement Error for F=4GHz, PRF=10MHz         | 122 |

| Figure 92. Measurement Error for PRF=1MHz, DC=50%          | 122 |

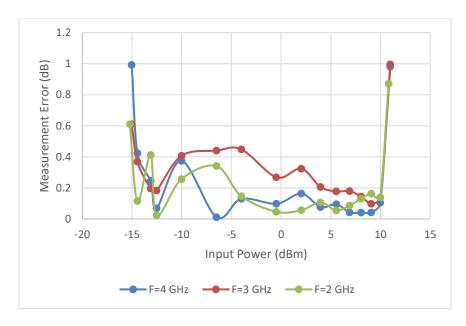

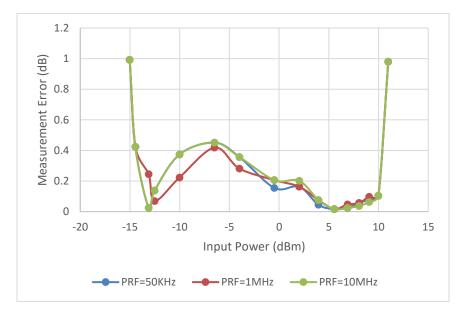

| Figure 93. Measurement Error for F=4GHz, DC=5%             | 123 |

# LIST OF TABLES

| Table 1. Comparison of RMS Power Detectors             | 14 |

|--------------------------------------------------------|----|

| Table 2. Current Sensor Topology Comparison            | 26 |

| Table 3. Current Range and Accuracy Requirements       | 27 |

| Table 4. Requirements for Input Buffer                 | 41 |

| Table 5. Current Sensor Post-Layout Simulation Results | 75 |

| Table 6. Power Detector Requirements                   | 86 |

#### **1. INTRODUCTION**

### **1.1. Motivation**

The current demand for transmitters in mobile communications exceeds 6 billion units per year, and it is expected that this demand will increase in the near future. Improving the power efficiency and yield of high-performance transmitters will have significant impact on the efficiency, reliability, and production cost of these transmitters and will ensure sustainable growth of the consumer electronics industry. The military sectors will also benefit from monitoring systems that are able to accurately measure power amplifier gain and bias current to optimize it for power efficiency in demanding applications with very high power levels. A major goal of this research is the design of robust yet efficient power and current monitoring systems with digital output that allow the use of digital methodologies to adjust various power amplifier (PA) parameters during operation.

Radio-frequency (RF) PAs are a vital component of wireless communication systems to-day, significantly impacting the daily lives of people around the world. However, significant challenges arise in PAs due to the large amount of power that they must output. Indeed, PAs have been described by many as an incredibly inefficient piece of hardware [1]. In mobile hand-sets, for instance, RF PAs can consume up to 65% of the total power when transmitting, playing a major role in the limitation of battery life [2]. Inefficiencies in RF PAs also directly correlate with the generation of waste heat, threatening the reliability of the system due to extreme temperature exposure. Whether embedded in a cellphone or a military defense radar, transmitters are integral to modern infrastructure, and their efficiency has long been a major bottleneck of system performance. This work deals with the design of two BiCMOS sensors to accurately measure the DC bias current and input and output power levels of high power gain PAs delivering up to 28-54dBm power while operating in the range of 2-6GHz to cover multiple standards.

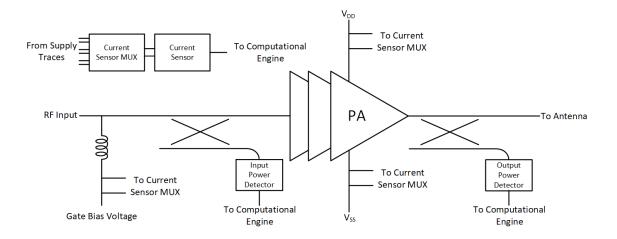

A PA control circuit which will measure in real-time the performance of the PA and dynamically adjust its operating conditions to optimize the efficiency of the system is proposed. The controller will treat the PA as a "black box", with no direct access to any PA nodes except its input and output paths. This PA control circuit will be integrated onto a single chip in order to maximize reliability and minimize the footprint as well as the manufacturing and assembly costs for the system. The proposed controller will measure the RF PA's input power, output power, drain current, gate current, and temperature. The system will pass the digital information from these sensors to a computational engine (CE), which will use the information to calculate the power-added efficiency (PAE) and estimate the peak channel temperature of the PA. The CE will use the same information to simultaneously maximize output power and PAE while maintaining gate current and channel temperature within acceptable limits. Again, the entirety of the controller will be implemented in a single integrated circuit (IC), separate the RF PA itself. See Figure 1 for a block diagram of the proposed system controlling a power amplifier. This research specifically will deal with the gate and drain current sensors as well as the input and output power sensors.

Figure 1: Power Amplifier Control System Overview

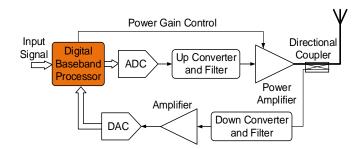

Figure 2 below shows the standard transmitter signal chain with the power amplifier driving the transmitter's antenna. A directional coupler is typically used to obtain a small portion of the PA's output power or input power which is then converted into a low frequency voltage using a power detector which, in turn, is digitized using a digital-to-analog converter. This digitized measure of the PA's output power is then processed by the digital baseband processor and the gain of the power amplifier is adjusted to provide the desired output power. This output power may be set based on the maximum output power possible to maintain the desired reliability of the power amplifier or it may be set based on the minimum power required to achieve a given accuracy or range for a radar or communication system.

Figure 2. Standard Transmitter Chain with Power Detector

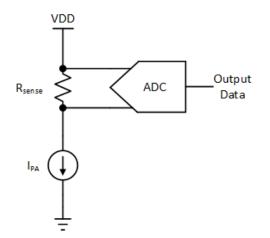

Not shown in Figure 2 above is the current sensor for the power amplifier. This is shown in more detail in Figure 3 below. Power amplifiers, especially those utilizing III-IV HEMT transistors with on-chip drain modulators, will generally have three different currents to be measured. The first is the supply current that feeds the main gain transistor of the PA, or the  $V_{DD}$  supply. The bias current through this supply can provide information on the power-added efficiency (PAE) of the PA. Indeed, knowing the PAE of the PA can allow the gate bias to be adjusted to achieve optimal (maximum) PAE. The second is the supply current associated with the on-chip drain modulator, or the (negative) V<sub>SS</sub> supply [3]. The third current is associated with the gate bias supply which, during normal operation, should be low since the Schottky diodes associated with the gate input are typically reverse biased. However, certain conditions, such as those caused by amplifier gain variation over temperature, may cause a large forward bias current to flow through the gate [4]. It is therefore useful to monitor the current through the gate bias supply since large forward bias current through the gate of the PA's transistor can cause permanent damage or greatly reduce reliability.

Figure 3. Typical PA Current Measurement Setup

## **1.2.** Organization of the thesis

Section 2 of this thesis will present the fundamental principles of power detection and current sensing. Previous topologies as well as important performance characteristics for both will be presented.

Sections 3 and 4 of this thesis will discuss the architecture of the proposed current sensor and power detector, respectively. Motivation behind the various architectural decisions made will be presented as well as block-level simulations of the components required in the design. Top level simulations along with the various error sources in each design will be presented. Lastly, measurement results for each sensor will be presented.

Section 5 of this thesis will provide a summary and some conclusions.

### 2. INTRODUCTION TO POWER DETECTORS AND CURRENT SENSORS

This section will provide an overview of the processes of power detection and current sensing as well as the performance metrics used to characterize these systems. Various topologies previously reported for both systems will be discussed, and each topology will be compared in terms of its advantages and disadvantages in the application targeted by this research.

### **2.1.** Power Detectors

The purpose of the power detector in a transmitter is to provide an estimate of the input and/or output power of the PA. If both the input and the output power are measured, the power gain of the PA can be calculated and can be adjusted to the desired or optimum value. Additionally, the power-added efficiency (PAE) of the PA can also be calculated. This will be discussed in section 2.2 below. Alternatively, the output power alone can be adjusted to the level required for the desired accuracy/range of the system, to the maximum reliable output power level, or to a level required by the communication standard the system is utilizing. Based on these varying requirements, there are two main types of measurements that various power detectors provide. The first measurement type is the RMS power which provides a measure of the average power at the output of the PA. The second type is the peak envelope power detector which provides an output that tracks with the power of the input signal's modulating envelope.

RMS power detectors are generally useful in communication systems utilizing modulation schemes with high modulation bandwidths. These communication systems are generally governed by standards that specify minimum or maximum output powers

based on the average power [5]. Additionally, the high modulation bandwidth of these systems generally means that peak envelope power detectors are unable to accurately track the modulation envelope of the input signal. Therefore, the average power, which inherently requires low-pass filtering, provides a more accurate measure.

On the other hand, peak envelope power detectors are generally useful in communication systems with lower modulation bandwidths or in other systems such as radar [9]. Indeed, peak power measurements can provide a much better estimation of the power radiated during a radar's "on" period which determines important radar characteristics such as the achievable range. Additionally, the peak power measurement also provides a good measure of the stress placed on the power amplifier. Therefore, if the purpose of the PA feedback loop found in Figure 2 is to improve the reliability of a high output-power PA, the peak power should be measured. Since the ultimate target application of this research is radar systems, the peak power will be measured. Nonetheless, since RMS power detectors are much more prevalent in the literature, the power detector presented in this research will be compared against RMS detectors and RMS detectors will be discussed in the following section.

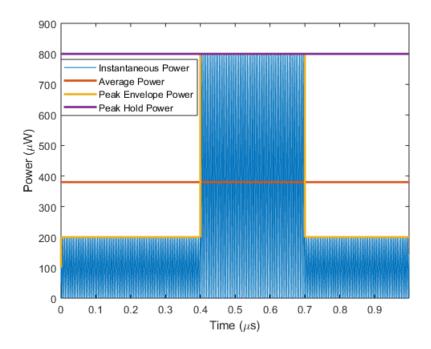

Figure 4 below shows a comparison between the various power detector definitions. The signal being examined has a frequency of 100MHz and an amplitude of 100mV from time 0 to 0.4 $\mu$ s, an amplitude of 200mV from 0.4 $\mu$ s to 0.7 $\mu$ s, and an amplitude of 100mV from 0.7 $\mu$ s to 1 $\mu$ s. The instantaneous power is calculated using the input voltage and assuming this is referred to a 50 $\Omega$  source. Therefore:

$$P_{inst} = \frac{V(t)^2}{50\Omega} \tag{1}$$

Since the incoming signal in real transmitter designs may be upwards of several GHz, it is impractical to attempt to measure the instantaneous power. Therefore, it is more reasonable to measure the average power, as described above. This power is measured by measuring the RMS voltage of the input signal and is also plotted in Figure 3 below. Since the RMS voltage is computed as an average over a period of time, the average power remains theoretically constant over this time. In practical systems, this is accomplished by lowpass filtering with a low bandwidth. The next power measure shown is the peak envelope power. Typically, the peak envelope power is obtained by measuring the peak power and ensuring the bandwidth of the filter following the peak power detector is high enough that it can track the modulation envelope of the signal. Therefore, the bandwidth of a peak envelope power detector must be higher than the modulation envelope but lower than the carrier signal's bandwidth [9]. This research will implement a peak hold power detector which measures the power at a particular point of the input signal and provides an output with the power at that point. In this case, the peak hold power at the end of the radar's "on" period will be provided.

Figure 4. Comparison Between Various Power Definitions

## 2.1.1 RMS Power Detectors

The RMS power of a signal is obtained by first finding the RMS voltage of the signal [6]:

$$V_{rms} = \sqrt{avg[V^2(t)]} = \sqrt{\frac{1}{t_2 - t_1} \cdot \int_{t_1}^{t_2} |V(t)|^2 dt}$$

(2)

Where V(t) is the input voltage and  $t_1$  and  $t_2$  are the times during which the rms voltage is to be measured. The rms voltage can then be used to find the average power of the signal referenced to  $50\Omega$ :

$$P_{ave} = \frac{V_{rms}^2}{50\Omega} \tag{3}$$

We can see from (2) that there are two basic operations that must be performed to find the RMS value of the input voltage. First, the signal must be squared and then that

squared voltage must be averaged. Various RMS power detectors differ in the ways they perform these two operations.

There are also several performance metrics used to distinguish among the performance of various power detectors. One metric is the dynamic range achievable by the detector. This dynamic range defines the input range over which the output power estimate is valid. Therefore, it is important that an acceptable error be specified along with the dynamic range. For example, a dynamic range of 20dB with an error of 1dB indicates that the valid input range is 20dB wide (or over a factor of 100 in power), and within that 20dB range, the maximum error between the detector's output and its "ideal" output is 1dB. Another important measure of the power detector's performance is the operating frequency range over which the dynamic range is valid. While the requirement for the operating frequency may vary from application to application, RF power detectors for communication systems and radar must generally cover up to several GHz of range. A final measure of power detector performance is its power consumption. Since these power detectors may be used in battery-powered transmitters, the power consumption of the power detector should be as low as possible to ensure it does not have an adverse effect on the battery life of the device.

It is also important to note that the "ideal" output used in the dynamic range performance specification changes from detector to detector. For most power detectors [6-8], the output is simply a voltage. Therefore, the ideal output is obtained by measuring the output voltage over a wide range of input voltages and finding the linear range. A linear best-fit curve is then applied to this linear range and each measured point is compared to this best-fit curve. Therefore, most detectors will require calibration when placed in the final system so that the baseband processor knows which output voltage corresponds to which input signal power level [9].

The RMS detector reported in [6] utilizes the square law characteristics of MOS transistors in strong inversion to perform the squaring operation and a low pass filter to perform the averaging. The input voltage is converted into a current that has terms proportional to the square of the input voltage:

$$i_{DS} = \frac{\mu_n C_{ox}}{2} \cdot \frac{W}{L} (V_{in} - V_t)^2 = \frac{\mu_n C_{ox}}{2} \cdot \frac{W}{L} (V_{in}^2 - 2V_{in}V_t + V_t^2)$$

(4)

This design also utilizes the exponential behavior of MOS transistors in weak inversion to convert the output of the lowpass filter to a linear-in-decibel output:

$$i_{ds} = \frac{W}{L} I_{D0} exp\left(\frac{qV_{in}}{nkT}\right) \tag{5}$$

This linear-in-decibel output can then be used by the baseband processor to set the output power. This detector provides a linear output characteristic over a range of 20dB at 5.5GHz with a maximum error of 0.5dB.

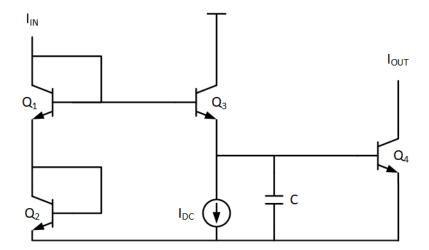

Another RMS detector topology is reported in [7] and utilizes a translinear loop, which is described in detail in [10] and is shown in its basic form in Figure 5 below, to perform the squaring and averaging operations using one single loop. The output current of this circuit can be shown to be:

$$I_{out} = \frac{\frac{I_{in}^2}{I_{DC}}}{1 + \frac{SCV_T}{I_{DC}}}$$

(6)

From (6), we see that the input current is squared and is also low-pass filtered by the capacitor at the emitter of  $Q_3$ . Therefore, we see that the squaring and averaging operations are accomplished by this single translinear loop. This design achieves an impressive dynamic range of 40dB, but this dynamic range is only achieved at 1.3GHz. Indeed, translinear-based power detectors can generally only operate at lower frequencies.

**Figure 5. Basic Translinear Loop**

Another RMS power detection design previously reported in [8] also utilizes the square-law behavior of MOS transistors in strong inversion to generate an output current proportional to the square of the input voltage. This current is then directed to a TIA which converts it into a voltage. The main contribution of this design is the implementation of segmenting gain amplifiers which boost low input signals into the dynamic range of the detector where the output characteristic is linear. This allows the dynamic range of the overall detector to be extended beyond the range of the detector by itself. As a result, a dynamic range of >40dB is achieved by this design at frequencies

ranging from 0.7 to 4GHz. This design also utilizes a temperature compensation bias circuit, so this dynamic range is valid over a wide temperature range.

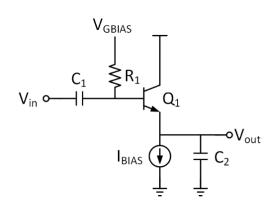

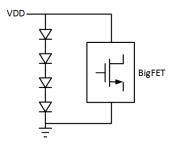

A final RMS power detector is presented in [11]. This power detector, like the power detector in [8], segments the dynamic range to obtain a dynamic range much higher than the detector can achieve alone. In this case, however, the dynamic range is segmented using attenuators since accurate attenuators are more easily designed than accurate amplifiers. The core detector for this design is based on a bipolar power detector which can be found in Figure 6 below. While at high amplitudes, the output of this circuit is approximately equal to the peak input voltage shifted by a  $V_{BE}$  drop, at low input amplitudes, the output voltage of this peak detector is approximately equal to the square of the input voltage. Therefore, the peak detector can, over a small range, be used as an RMS detector. The peak detector will be discussed again later in this thesis since it is used in the power detector presented in this research.

**Figure 6. Peak Detector Schematic**

The table below shows a comparison of the four previously discussed RMS power detectors with the performance metrics discussed above. There are several things to note in this comparison table. The first is that the translinear detector provides a very high dynamic range with very low error in a single segment. It is important to note, however, that this performance is only achieved up to 1.3GHz. It is also interesting to note that the peak-detector based RMS detector provides only 8dB of dynamic range within a single segment. This is because the peak detector provides a much better estimate of the amplitude of the input signal than it does the RMS value of the input signal. Based on the table below, the square-law detector provides a good tradeoff between the operating frequency and the dynamic range, but it requires segmentation to achieve a dynamic range above 20dB. Another important note is that none of these detectors provide an absolute power reading; each detector only outputs a voltage.

| Detector      | [6]           | [7]           | [8]               | [11]              |

|---------------|---------------|---------------|-------------------|-------------------|

| Topology      | Square-Law    | Translinear   | Square-Law        | Peak-Detector     |

| Dynamic Range | 20dB          | 40dB          | 40dB (4 Segments) | 40dB (5 Segments) |

|               | (0.5dB Error) | (0.1dB Error) | (1dB Error)       | (0.5dB Error)     |

| Operating     | 0.1-8.5GHz    | 0-1.3GHz      | 0.7-4GHz          | 5.2GHz            |

| Frequency     |               |               |                   |                   |

| Power         | 0.18mW        | N.R.          | 11.8mW            | N.R.              |

| Consumption   |               |               |                   |                   |

**Table 1. Comparison of RMS Power Detectors**

### 2.1.2 Peak Power Detectors

As mentioned in the discussion above, peak envelope power detectors provide an output that tracks with the input signal's modulating envelope:

$$P_{env} = \frac{(V_{env}(t)^2)}{50\Omega}, t_1 < t < t_2$$

(7)

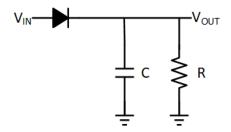

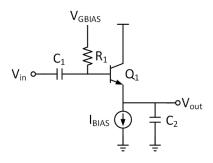

As seen in (7) above, peak power detectors must track the envelope power of the input signal. Therefore, the detector must be fast enough to track the modulating envelope of the input signal but must also limit the bandwidth of the output so that the high-frequency carrier at the input is sufficiently attenuated. As a result, most peak power detectors utilize either BJT or diode-based peak detectors [12-14]. A schematic of a BJT-based peak detector can be found in Figure 6 in the discussion above while a simplified schematic of a diode-based peak detector can be found in Figure 7 below. The operation of these two circuits is fairly similar. In the diode-based detector, if  $V_{in}$  rises more than the required diode turn-on voltage above  $V_{out}$ ,  $V_{out}$  will begin to track  $V_{in}$  minus a diode voltage drop. If  $V_{in}$  then falls again, the diode will turn off, but  $V_{out}$  will begin to decrease as the capacitor discharges through the resistor. The output voltage will decrease with a slope equal to:

$$\frac{dV_{out}}{dt} = \frac{V_{out}}{RC}$$

(8)

Therefore, the output will exponentially decay to 0 with a time-constant of RC. If this RC time constant is very large compared to the period of the incoming signal, the voltage drop during the lower portion of the signal will be insignificant compared to the amplitude, and the output voltage will approximately equal the input amplitude minus a diode voltage

drop. The resistor is included in this circuit to set the DC voltage at the output since this DC voltage is ill-defined with only the capacitor and diode connected to this node. Since the input signal to the diode-based peak detector will be high frequency, the diode will need to be able to operate at sufficiently high frequency so that the output voltage can track the input voltage. Therefore, designs utilizing diode-based peak detectors typically use high-speed Schottky diodes.

Figure 7. Diode-based Peak Detector

The operation of the BJT-based peak detector shown in Figure 6 is similar to the diode-based peak detector discussed above. In this circuit, the capacitor  $C_1$  and the resistor  $R_1$  form an ac-coupling network at the input of the peak detector so that the bias voltage of the base of  $Q_1$  can be set independently from the DC bias of  $V_{in}$ . If the voltage at the base of  $Q_1$  is sufficiently above the voltage at the emitter of  $Q_1$ , the BJT will turn on and the voltage at the output will track the voltage at the input minus a  $V_{BE}$  diode-voltage drop. Once the voltage at the base of  $Q_1$  falls back below the required turn-on voltage, the transistor  $Q_1$  will turn off and the output voltage will begin to decrease as  $I_{BIAS}$  discharges  $C_2$  at a rate of:

$$\frac{dV_{out}}{dt} = \frac{I_{BIAS}}{C_2} \tag{9}$$

Once again, if  $C_2$  is large and  $I_{BIAS}$  is small, the output voltage will not change much during the low period of the input signal, and the DC voltage at the output will be close to the peak voltage at the base of the BJT minus a  $V_{BE}$  voltage drop.

It is interesting to note that the diode-based and BJT-based peak detectors can be used as peak detectors or as RMS detectors [11]. The main difference between the two applications is that RMS detectors require high time constants in the detectors so that the output does not track with the envelope and provides a measure of the average power. In the case of peak envelope power detectors, the time constants are generally much smaller so that the output can track the modulating envelope of the input signal.

Peak power detectors generally utilize the same performance metrics as RMS power detectors. These include the dynamic range, or the input range over which the output of the peak power detector is valid, the frequency of operation, or the input frequency range over which the output of the peak power detector is valid, and the power consumption, which is important since many power detectors utilized are run off a battery supply and therefore should not dissipate excessive power.

One design based on a BJT peak detector is reported in [13]. This design utilizes one peak detector with the RF input and subtracts the output voltage of a matched peak detector with no input in order to compensate for temperature and process variations. The output voltage still has some dependence on temperature, however, and the output voltage decreases as the temperature increases. In order to solve this issue, this design utilizes a PTAT current source to generate a compensation current that is added to the output of the peak detector circuit in order to boost the output voltage at higher temperatures to match the output voltage at lower temperatures. This compensation scheme, however, assumes that the temperature dependence of the peak detector output is linear, so the detector still shows some temperature-related errors at low input amplitudes. Additionally, the compensation factor is determined experimentally which requires post-fabrication calibration. While not explicitly reported, this design appears to achieve a dynamic range of approximately 20dB.

One issue with the BJT peak detector is its non-linearity for small input amplitudes. As the input amplitude decreases, the magnitude of the ripple at the output during the low portion of the input begins to approach the amplitude of the input signal. Therefore, the output does not linearly track with the input amplitude which introduces some errors if a linear relationship between the input amplitude and the output voltage is assumed. The design in [15] alleviates this issue by utilizing a replica peak detector and generating a compensation current to correct for this non-linearity. This extends the linear range of the peak detector to approximately 26dB.

The design specified in [16] represents a typical peak power detector available on the market. This detector achieves an accuracy of 0.5dB at full input power and an accuracy of 1.5dB at low input power. The detection range is from -16dBm to 5dBm which represents a 21dB dynamic range. As mentioned before, an important characteristic of most power detectors is their error over a wide temperature range since the devices they are used in can be subject to many different environmental conditions. This detector achieves a 0.3dB detection error over a temperature range from  $-40^{\circ}$  to  $85^{\circ}$ . One common issue with all of the power detectors mentioned thus far is that they do not output an absolute power detection reading. All of these designs output a voltage that must be digitized by the baseband processor in the loop in Figure 2 which must then convert that output voltage into an appropriate power reading. For varying input frequencies, temperatures, process variations, and non-linearities, this conversion of the output voltage into an appropriate power reading often requires extensive post-fabrication calibration and storage of data into read-only-memories in either the detector or the baseband processor [9]. This research seeks to greatly reduce the amount of calibration and data storage required by moving much of that calibration on-chip. The architecture required to accomplish this task will be discussed in detail in Section 3.

### **2.2 Current Sensors**

The purpose of the current sensor in the transmitter is to measure the bias current of the PA, the bias current of the PA's modulator, and the gate current of the PA. One purpose in measuring the bias current of the PA is to calculate the PA's power-added efficiency (PAE). This is defined as:

$$PAE = 100 \times \frac{P_{OUT} - P_{IN}}{P_{DC}} \tag{10}$$

From (10), we see that the output power, input power, and DC power consumption of the PA must be known to compute the PAE. In the final system, the PAE will be used as one of the parameters to be optimized by the computational engine. The DC bias current can be adjusted through the gate bias voltage while the input power can be adjusted through an input attenuator to attempt the combination of these two parameters that provides the maximum PAE while also taking into account the reliability of the PA [17]. This DC

power includes the bias current for the PA's gain transistor as well as the bias current for the PA's modulator. Therefore, both currents will be measured by the current sensor. Also important is the PA gate current. If there is excessive PA gate current, the reliability of the PA will be greatly reduced [4]. Therefore, the computational engine will also attempt to minimize the gate current of the PA in order to maximize its reliability.

There are several metrics used to measure the performance of current sensors. Since these current sensors often interface to very high supply voltages, the sensor should be able to handle a large common-mode range at its input. Also important is the gain error which is a measure of how accurately the sensor measures the input current over its full input current range. This gain error may be due to temperature or process variations in the series resistance or errors in the amplification and readout circuitry. The next metric is the offset of the current sensor which is generally due to errors in the readout circuitry. Many current sensors will include offset-cancellation circuits to reduce this as much as possible. The resolution of the detector, which determines the minimum current step that can be accurately measured, is also generally determined by the accuracy of the readout circuitry. Finally, the power consumption of the sensor is important as many of these current sensors operate in battery-powered environments. Therefore, the power consumption should be reduced as much as possible to ensure the battery life is as long as possible.

There are several current-sensing topologies that can be utilized to measure the various currents in the PA. One is the series sense-resistor topology whose basic schematic is shown in Figure 8 below. This topology requires a sense resistance to be

placed in series with the current that is to be measured. If the resistance of the sense resistor is well-known, the voltage across it provides information on the desired current:

$$I = \frac{V_{sense}}{R_{sense}} \tag{11}$$

Therefore, the sense voltage can be digitized and used by the computational engine in its efficiency calculations and adjustments. There are some issues with this topology, however. One issue is that the addition of the sense resistor in series with the current to be measured leads to additional power loss in the system, especially if the current or the sense resistance is large. Therefore, for systems where large currents must be measured, the sense resistance must be very small. As a result, the signal-to-noise ratio (SNR) of the voltage across the resistor may be very low which will affect the accuracy of the current sensing operation. In some systems, any additional sense resistance is unacceptable, and the sense voltage will either need to be obtained without any additional resistor added, or the current estimate will need to be obtained another way.

Figure 8. Typical Series-Resistor Sensing Scheme

The design reported in [18] utilizes a delta-sigma modulator to digitize the voltage across a  $10m\Omega$  shunt resistor that is implemented on-chip. The on-chip shunt resistor occupies an extremely large area and is subject to electromigration which changes its resistance over time [19]. In order to compensate for variations in temperature causing variations in the sense resistance, a PTAT voltage reference is used to generate a compensation voltage which is added to the input voltage. This allows the sensor to achieve a gain error of just 0.9% over a wide temperature range with a single-temperature trim with a 40µA offset. The use of a sigma-delta along with averaging also allows the SNR of the input signal to be improved since random noise caused by the sense resistance is averaged and its effective RMS value is decreased. Therefore, the sensor achieves an effective resolution of 13-bits with a conversion time of 2ms. As discussed before, most current sensors must interface to high-voltage supplies. In this design, this is accomplished by utilizing a high-voltage CMOS process with high-voltage transistors utilized at the input interface of the ADC. This allows the standard-voltage ADC to interface to voltages from 0V up to 25V.

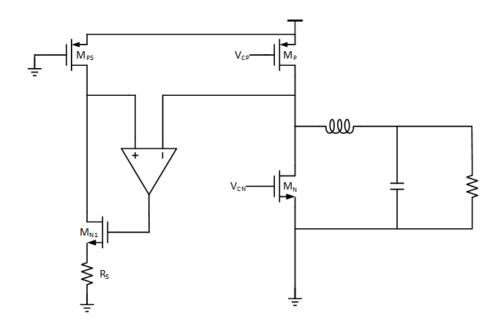

Other current sensors, such as the one reported in [20], are intended for use in switching power converters and utilize sense-FETs placed in parallel with the transistor current to be measured. The basic sense-FET scheme utilized in a buck-converter is shown in Figure 9 below. The current through M<sub>P</sub> is to be measured, so another PFET transistor, M<sub>PS</sub>, with a lower number of fingers is placed in parallel to this transistor. Therefore, the current through M<sub>PS</sub> should be some ratio of the current through M<sub>P</sub>. However, the current

through the transistors, taking into account channel-length modulation, can be approximated as:

$$I_{DS} = \frac{\mu_n C_{OX}}{2} \cdot \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(12)

Therefore, in order to ensure the ratio of the currents through  $M_P$  and  $M_{PS}$  are well-known, the drain voltages of M<sub>P</sub> and M<sub>PS</sub> should be equal. This is accomplished using the transistor M<sub>N1</sub> and the operation amplifier (op-amp) shown in Figure 9 below. Therefore, the voltage across  $R_S$  can be measured to find the current through  $M_{PS}$  which can then be multiplied by the ratio of current through M<sub>P</sub> and M<sub>PS</sub> to find the current through M<sub>P</sub>. The design reported in [20] extends the basic sense-FET scheme mentioned above to allow the sensor to measure the current through both M<sub>P</sub> and M<sub>N</sub>. This design achieves a gain accuracy of 3.2% at a maximum load current of 2A and a settling of 6ns. No ADC is included to digitize the voltage across R<sub>s</sub>, so it is difficult to compare the power consumption of this sensor with others. Since the sense-FET is integrated with the current to be measured, the CM input range is not important for this design. One major drawback of this topology, and the reason it was not used in this research, is the sense-FET must be matched to the transistor through which the current must be measured. Since the idea of this PA control system is to treat the PA as a black box, it is not possible to properly match a transistor to the PA's internal transistors.

**Figure 9. Basic Sense-FET Scheme**

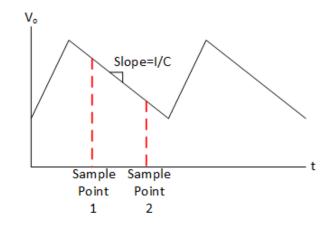

A final current sensing topology is described in [21]. This current sensor is targeted for use in buck and boost converters, such as the one shown in Figure 9 above. During the time when the switch formed by  $M_P$  in Figure 9 is on, the filter capacitor at the output is charging. When the switch formed by  $M_P$  turns off and the switch formed by  $M_N$  turns on, the capacitor at the output is discharging. During this time, the discharge rate can be approximated as:

$$\frac{dV_o}{dt} = \frac{i_L}{c_L} \tag{13}$$

Where  $i_L$  is the current required by the load of the converter and  $C_L$  is the output capacitor. Therefore, if the slope of the output voltage is measured during this period, the current can be calculated by multiplying this slope by the filter capacitance. The design in [21] utilizes a concept similar to the single-slope ADC. Two points on the output voltage curve are sampled with a known time in between them and held on capacitors. One capacitor is then discharged by a known current until the voltage on that capacitor equals the voltage on the other capacitor. A counter is used during this time to digitize the difference between the two voltages. Since the difference between the two voltages as well as the time between the two samples is known, the slope can be calculated. This is shown in Figure 10 below. This slope is then multiplied by the capacitance to calculate the load current for the converter. This design achieves an impressive maximum error of 0.4% but consumes a total power of approximately 18mW. This design utilizes level-shifting capacitors at the input of the detector and can, with proper protection circuitry, handle high common-mode input voltages and interface with very large supply voltages. The conversion time of the sensor is 500ns which allows for very fast sensor measurements to be taken. The resolution of the detector is 8-bits. While the conversion time and resolution are good for this topology, the sensor relies on accurately knowing the value of the filter capacitor in the buck converter. In [21], the value of the discharging current source is trimmed to provide the proper absolute output current at room temperature. Many capacitors, however, have strong temperature dependence and can vary by up to +/-15% across a range from -40°C to 85°C. Therefore, this circuit would need some sort of temperature compensation circuit to provide satisfactory performance across a wide range of temperatures. The issue with this solution, however, is that the capacitance does not necessarily vary linearly with temperature. As a result, the compensation circuit may need to account for non-linear changes in the capacitance with respect to temperature.

Figure 10. Capacitor-Based Current Sensor Operation

Table 2 below shows a summary of the current sensors discussed above. The series-R topology provides the lowest power consumption but has higher gain error than the capacitor-based sensor. The capacitor-based sensor, however, is not measured over a wide temperature range and will require a complex compensation circuit to achieve adequate performance. The sense-FET sensor integrates very well with monolithic buck converters but exhibits high gain error. The power consumption is not reported for this design

| Table 2. Current Bensor Topology Comparison |          |           |           |  |

|---------------------------------------------|----------|-----------|-----------|--|

| Sensor                                      | [18]     | [20]      | [21]      |  |

| Topology                                    | Series-R | Sense-FET | Capacitor |  |

| Gain Error                                  | 0.9%     | 3.2%      | 0.4%      |  |

| Common-Mode Range                           | 0-25V    | N.A.      | 0-50V     |  |

| Power Consumption                           | 16.35µW  | N.R.      | 18mW      |  |

Table 2. Current Sensor Topology Comparison

#### 3. PROPOSED CURRENT SENSOR

#### **3.1 Current Sensor Architecture**

This research presents a current sensor that is based on the series-R currents sensor topology introduced in the previous section. First, the various requirements of the current sensor will be defined. Next, an overview of the current architecture will be presented.

# 3.2.1 Problem Description

The current sensor has several requirements that are set in order to ensure the computational engine can accurately calculate the PAE and control the gate input current. First, the sensor must measure three supply currents: the positive ( $V_{DD}$ ) at a voltage of around 40V. This is the supply that provides the bias current to the PA. The bias current flowing through the PA flows to ground (not the negative supply). Next is the negative supply (modulator supply) at a voltage of around -6V. This supply provides a negative voltage required for the drain-modulator on the PA chip and the current for the drain-modulator flows from the positive supply to the negative ( $V_{SS}$  supply). Finally, there is the gate supply which ranges from 0V to -5V and sets the bias voltage for the gate of the PA's main transistor. The current ranges and required accuracies are shown in the table below. The measurements for all three supplies must be obtained within 1ms.

| Supply               | $V_{DD}$ | V <sub>SS</sub> | $V_{GG}$        |

|----------------------|----------|-----------------|-----------------|

| Current Range        | 1A-4A    | -250mA to 100mA | -250mA to 100mA |

| Accuracy Requirement | 1%       | 10mA            | 10mA            |

Table 3. Current Range and Accuracy Requirements

In addition to the currents listed above, the detector will also need to take into account the fact that the PA is modulated using pulse modulation. Therefore, during periods where the pulse is off, the PA will have no current flowing through it. This pulse modulation is characterized by a pulse repetition frequency (PRF) and a duty cycle (DC). The PRF can range from 50kHz to 10MHz while the duty cycle can range from 5% to 50%. The supply node of the PA, however, is well-bypassed, and the current flowing to the PA will have a DC component with some ripple around this DC level. Therefore, the detector will need to adequately filter this ripple component at the PRF out in order to provide an accurate DC current estimate. If the peak current is desired, the average current can simply be divided by the duty cycle to find the peak current.

There are several other constraints placed on the current sensor so that it can be useful in the PA control circuit. The first is that the sensor must interface to the 40V supply used for the PA. Since the ground of the PA is connected directly to a ground plane on the PCB through several vias, there is nowhere to insert a sense resistance to accurately measure the current. As a result, the current sensor must perform "high-side sensing" on the positive supply of the PA. Additionally, to reduce power supply noise and improve efficiency, a large current-sense resistor cannot be used in series with the PA's power supply. Indeed, a  $10m\Omega$  is targeted in this design. Therefore, the current sensor will lead to large detection errors. As a result, the SNR of the sensing measurement will need to be improved in some manner. Lastly, it is not even desirable in this system to introduce a discrete current sense resistance in series with the PA's power supply. As a result, the PCB trace connecting the PA to its power supply will be utilized for current sensing. This PCB trace will be approximately  $10m\Omega$  at room temperature, but this sense resistance can vary greatly with temperature. This is seen in Figure 11 below which shows the resistivity of a copper trace over a wide temperature range. The resistivity of the copper changes as much as 28% from room temperature to either temperature extreme. Therefore, the current sensor will require some form of temperature compensation in order to provide an accurate estimate of the supply current.

Figure 11. Copper Resistivity over Temperature

## 3.2.2 Architecture Overview

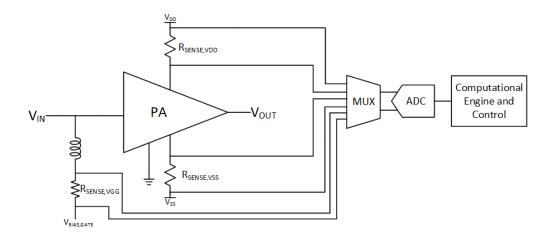

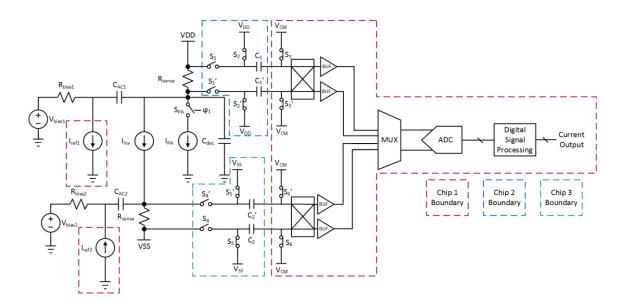

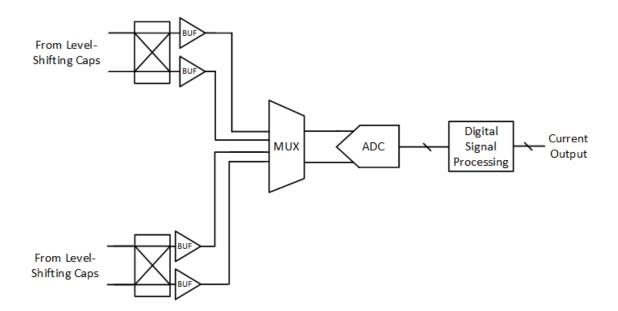

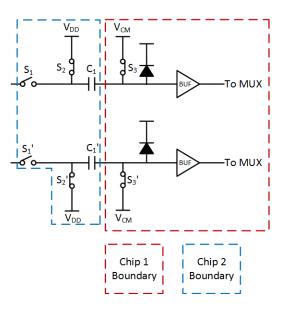

The current sensor architecture is shown in Figure 12 below. Only the positive and negative supplies are shown for simplicity, but the gate supply sensor section is identical to the negative supply sensor section since these supplies have identical accuracy requirements. The overall design consists of a level-shifting capacitor chip which will shift the high supply voltage to a level suitable for use in a standard CMOS process, an oversampling ADC which will measure the voltage across the sense resistance for each supply, and a reference current source that will pass a well-known current through the sense trace to estimate its resistance.

Figure 12. Current Sensor Architecture

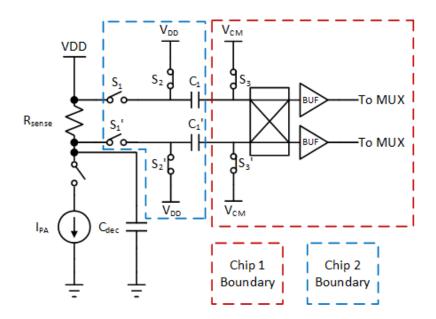

Figure 13 below shows the level-shifting capacitors in more detail. During the charging phase, switches  $S_2$  and  $S_3$  are closed while switch  $S_1$  is opened. This charges the capacitors such that the voltage on the right side of  $C_1$  is a common-mode voltage suitable for the standard CMOS process used while the voltage on the left side is the high-supply voltage. Since the switches  $S_{1,2}$  and  $S_3$  operate at such different voltages, these switches must reside on separate chips. Chip 1 is powered by a standard 1.8V

supply. As a result, the common-mode voltage chosen for chip 1 is 0.9V. Chip 2, on the other hand, is powered by a 40V supply. Therefore, the capacitors are charge to a voltage of approximately 39.1V.

Since a standard CMOS process is still used for this chip, a negative supply that is approximately 1.8V below 40V must be generated. This is accomplished by using diode-connected transistors, and more details can be found in the next section. During the time when  $S_2$  and  $S_3$  are closed, the differential input to the buffer is 0V.

**Figure 13. Level Shifting Capacitors**

After sufficient time for the capacitor to charge has elapsed, switch  $S_3$  is opened followed by  $S_2$ . This is done to ensure that charge injection from the switches to the levelshifting capacitors is minimized. Once these switches are opened, switch  $S_1$  is closed and the voltage appearing at the input of the buffers is the differential voltage across the sense resistance but shifted down by the voltage stored on the level-shifting capacitors. The buffer leading to the MUX must have a high impedance input to ensure the charge on the capacitors remains constant during the measurement period. Additionally, while the switches may allow some leakage current through, the capacitors are recharged at the beginning of each measurement cycle.

Figure 14 below shows an overview of the circuits contained on Chip 1. The input of this section comes from the level shifting capacitors and goes to the buffer. The buffer provides some gain to ensure that the ADC can properly digitize the small input signals coming from the small sense resistance. The buffer outputs for each supply are multiplexed so that one ADC can be used to digitize each input. The output of the ADC is then processed to determine the current estimate.

Figure 14. ADC and Supporting Circuitry

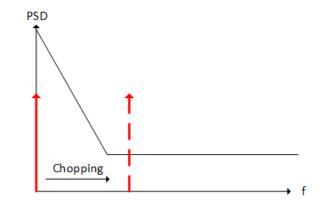

One issue in DC current measurement is that low frequency noise and offsets can greatly impact the accuracy of the current estimate. Especially in CMOS current sensors, flicker noise will play a significant role in determining the accuracy of the detector. In order to decrease the effect of offsets and flicker noise, a chopping modulator is added at the input of the buffers. This modulator switches the polarity of the input signal at a rate of 25kHz. This moves the desired DC information up to 25kHz where it is less impacted by offsets and flicker noise in the buffer, MUX, or ADC. This is demonstrated in Figure 15 below. In analog chopping systems, an identical chopping modulator is added to the output of the amplifier in order to move the low-frequency information back down to its original frequency position. In this case, however, the chopping de-modulation is performed in the digital signal processing.

Figure 15. Effect of Chopping on the DC Input Signal

One can also examine the advantage of chopping by considering the output of the ADC during each chopping period. When the input polarity is not reversed, the output

voltage is the sense voltage plus the offset voltage of the buffer and ADC as well as an error due to flicker noise.

$$V_{+} = V_{sense} + V_{OS} + \epsilon_{flicker}(t_{o}) \tag{14}$$

When the input polarity is reversed, T<sub>chop</sub> seconds later, the output voltage will be:

$$V_{-} = V_{sense} + V_{OS} + \epsilon_{flicker}(t_o + T_{chop})$$

(15)

The digital signal processor will take the difference between (14) and (15) to obtain an estimate of the sense voltage:

$$V_{out} = V_{+} - V_{-} = 2V_{sense} + \left(\epsilon_{flicker}(t_o) - \epsilon_{flicker}(t_o + T_{chop})\right)$$

(16)

We note first and foremost that the offset of the buffer and ADC is eliminated by the chopping. This is important since the input voltage is so small, and the offset would greatly limit the accuracy of the current estimate if it was allowed to corrupt the signal. We also note that slow-varying flicker noise will also be eliminated. This is because, for slow-varying flicker noise:

$$\epsilon_{flicker}(t_o) = \epsilon_{flicker}(t_o + T_{chop}) \tag{17}$$

Therefore, flicker noise well below the chopping frequency (<5kHz) will not have a significant impact on the accuracy of the current sense estimate.

Another design challenge in the ADC is how components at the PRF will be eliminated in the final output measurement. Since the current through the sense resistor will have a DC component as well as (possibly large) components at the PRF and multiples of the PRF, the digital signal processing will need to eliminate these components in order to obtain an accurate measure of the DC component. This can be easily achieved by using a moving average filter with the following impulse response:

$$h[n] = \begin{cases} \frac{1}{M}, 0 \le n \le M - 1\\ 0, & otherwise \end{cases}$$

(18)

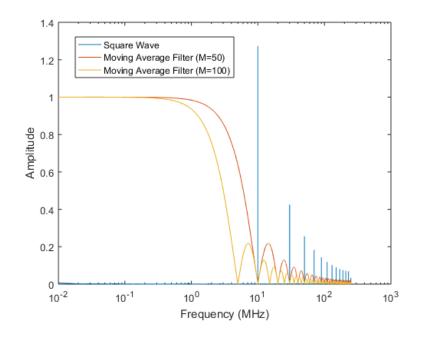

Therefore, the output of an M-tap moving average filter at any given time is simply the average of the M previous samples, including the current sample. In order to visualize how this eliminates the tones at the PRF and multiples of the PRF, the filter response is plotted below for M=50 and a sampling rate of 500MHz. Also plotted is a 10MHz square wave which has components at 10MHz, 30MHz, 50MHz, and so on. We note that the period of the 10MHz square wave is the same as the averaging period for the 50-tap moving-average filter since  $\frac{500MHz}{50} = 10MHz$ . We see that the first notch of the moving-average filter falls at 10MHz and eliminates the 10MHz component. Other notches in the filter fall at multiples of the 10MHz component and will therefore eliminate them as well. Also shown in the frequency response for a moving average filter for M=100. This filter also eliminates the desired components. Therefore, in order to eliminate the frequency components caused by the pulse modulation, the digital signal process just needs to average a number of samples that is an integer multiple of the number of samples in one period of the pulse modulation.

Figure 16. Input Square Wave with Moving-Average Filter Responses

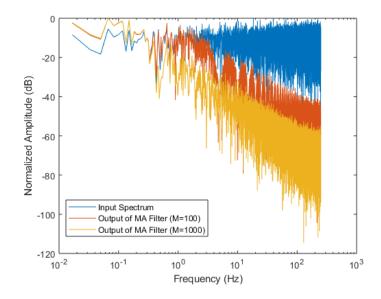

Another important property of the moving-average filter is its ability to decrease the effective noise at the output of the digital signal processor. Assuming that the input noise is white, the application of an M-tap moving-average filter improves the SNR by a factor of M while preserving the DC value since the magnitude response of the filter at DC is unity. Therefore, the poor SNR of the signal after it has passed through the ADC and the buffer can be improved greatly by averaging a large number of samples from the output of the ADC. This is illustrated in Figure 17 below. The input spectrum is white across the full frequency range. The noise power clearly decreases at higher frequencies when the moving average filter is applied and is decreased more drastically when a larger moving-average filter is applied.

Figure 17. Input Noise and Output Noise after Moving-Average Filters

This noise reduction property is verified by calculating the relative noise powers of the three signals shown in Figure 17 above. The noise power at the input is  $3.249nV^2$ while the noise power at the output of the 100-tap moving-average filter is  $39.42pV^2$  and the noise power at the output of the 1000-tap moving-average filter is  $3.5pV^2$ . Therefore, we see that the 100-tap moving average filter improves the SNR by a factor of 82 and the 1000-tap moving-average filter improves the SNR by a factor of 928. These values are close to the values predicted above. Therefore, an oversampling sigma-delta ADC is utilized in this design to digitize the voltage across the sense resistor.

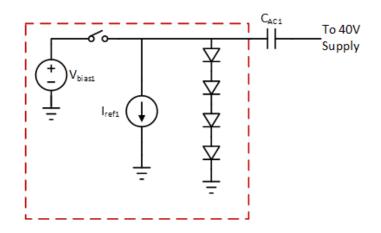

Another concern in the design of the current sensor is estimating the resistance of the PCB trace. As discussed previously, the current sensor requires some form of compensation circuit to ensure that changes in the sense resistance over temperature are taken into account. This is accomplished using the reference current calibration circuit shown in Figure 18 below.

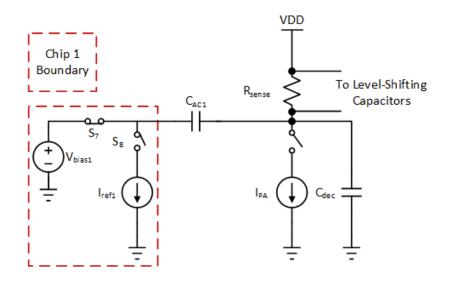

Figure 18. Reference Current Calibration Circuit

The purpose of this circuit is to apply a known current to the sense resistance so that the ADC can measure the voltage drop and use the known current value and the voltage drop value to compute an estimate of the sense resistance. Since this reference current source must also interface to the high-voltage supply, another level-shifting capacitor  $C_{AC1}$  is used. During the charging period, switch  $S_7$  is closed while switch  $S_8$  is open. This charges the capacitor such that the voltage at the current source is set to 1.8V. Once this charging cycle is complete, switch  $S_7$  is opened and switch  $S_8$  is closed. This allows the current  $I_{ref1}$  to flow through the coupling capacitor and through the sense resistance. During this period, the capacitor begins to charge to an even greater voltage. Therefore, the voltage across the current source begins to decrease once it is activated at a rate of:

$$\frac{\Delta V}{\Delta t} = \frac{I_{ref1}}{C_{AC1}} \tag{19}$$

Therefore, the current source cannot remain activated indefinitely and will need to be periodically recharged during the measurement cycle. A large  $1\mu$ F capacitor is used at this interface to ensure a sufficiently long reference current pulse can be used.

The voltage drop measured during the reference calibration period must be used by the sensor when calculating the final current. First, we measure the voltage drop caused by the reference current:

$$\Delta V = I_{REF} R_{SENSE} \tag{20}$$

It is assumed that there is no period during which the PA current is not flowing through the sense resistor. Therefore, this voltage drop must be measured by taking the voltage drop across the sense resistor with only the PA active ( $V_{PA}$ ) and subtracting it from the voltage drop across the sense resistor with the PA and the reference current source active ( $V_{PA+REF}$ ):

$$\Delta V = V_{PA+REF} - V_{PA} = I_{REF} R_{SENSE} \rightarrow R_{SENSE} = \frac{V_{PA+REF} - V_{PA}}{I_{REF}}$$

(21)

We can therefore calculate the PA current using the Pa measurement and the sense resistance:

$$I_{PA} = \frac{V_{PA}}{R_{SENSE}} = \frac{V_{PA}}{V_{PA+REF} - V_{PA}} \cdot I_{REF}$$

(22)

Therefore, the digital signal processor only needs to combine the PA measurement and the PA plus reference current source measurement along with the known reference current value to calculate the current flowing through  $R_{SENSE}$ .

Besides measuring the sense resistance, the reference current source measurement provides another very useful property. Suppose that the ADC or buffer has a gain error of  $\varepsilon$ . Therefore, the ideal PA and reference measurements will both be multiplied by (1+ $\varepsilon$ ) at the output of the ADC. Therefore, the PA current will be measured as:

$$I_{PA} = \frac{V_{PA}(1+\epsilon)}{V_{PA+REF}(1+\epsilon) - V_{PA}(1+\epsilon)} \cdot I_{REF} = \frac{V_{PA}}{V_{PA+REF} - V_{PA}} \cdot I_{REF}$$

(23)

As a result of the reference current source measurement, the gain error in the ADC or the buffer is eliminated in the final current calculation and therefore does not affect the accuracy of the current sensor. Additionally, since the chopping scheme eliminates the effects of buffer and ADC offsets and this technique eliminates gain errors, the main accuracy requirements are moved to the quantization performance of the ADC and the accuracy of  $I_{REF}$ . Therefore, most design effort is focused in these two places. One thing to note, however, is that any non-linearity in the system will cause current measurement errors as the reference current calibration only cancels linear gain errors.

## **3.2 Implementation of Current Sensor**

#### 3.1.1 Input Buffer

The purpose of the input buffer is to boost the DC voltage at the input to a level suitable for the ADC to digitize. Therefore, the input buffer provides a gain of approximately 10V/V for the incoming signal. As mentioned before, the exact gain of the buffer is not critical as any gain variations are compensated by the reference current

calibration. There are several other important parameters for the input buffer. Firstly, the input buffer must be very linear since non-linear errors in the buffer are not cancelled by the calibration scheme. Additionally, the buffer must present a large (ideally infinite) input impedance as it is not desirable to bleed any charge off of the level-shifting capacitors at the input of the detector. The buffer should also have relatively low noise as high input-referred noise in the buffer will corrupt the input signal. As mentioned before, however, the effective noise of the buffer will be greatly decreased by the averaging at the output of the ADC. Lastly, the buffer should have a reasonable bandwidth to ensure that when the reference current source is activated, the buffer output does not take excessive time to rise to the new output value. Table 1 below shows the requirements for the buffer.

| Parameter  | Required Value     |

|------------|--------------------|

| Gain       | ~10V/V             |

| Bandwidth  | >1.5MHz            |

| Noise      | $< 50 \mu V_{rms}$ |

| Gain Error | <0.1%              |

**Table 4. Requirements for Input Buffer**

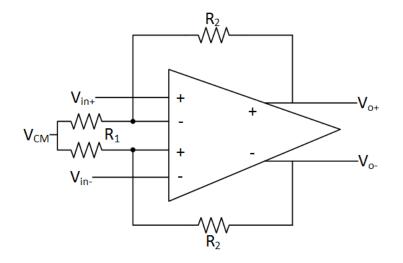

Based on the buffer requirements discussed above, the fully-differential difference amplifier (FDDA) shown in Figure 19 is used [22]. This amplifier provides fully differential gain with a high input impedance and is therefore very suitable for this application. This amplifier is similar to the single-ended non-inverting operational amplifier configuration and provides a gain equal to:

$$A_V = 1 + \frac{R_2}{R_1} \tag{24}$$

Therefore, we choose  $R_2$  to be 90k $\Omega$  while  $R_1$  is 10k $\Omega$ . This provides the desired nominal gain of 10V/V.

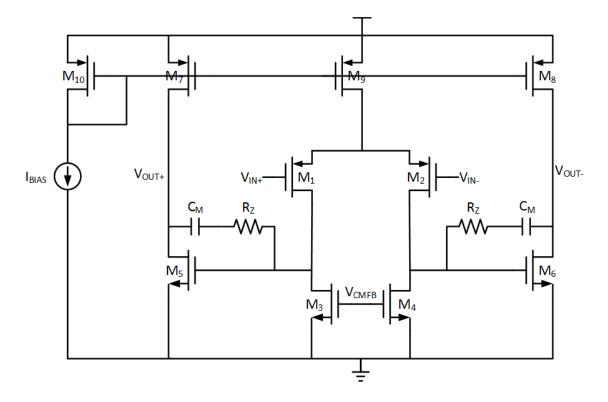

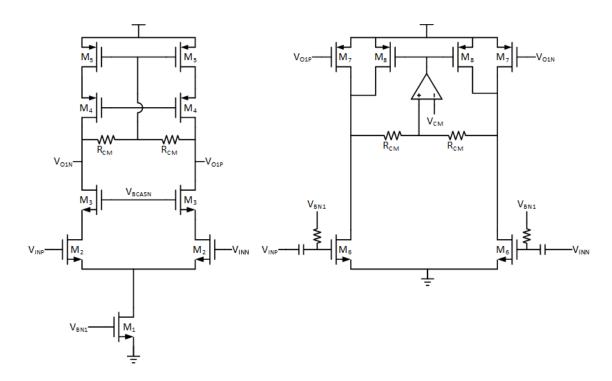

Figure 19. Fully-Differential Difference Amplifier

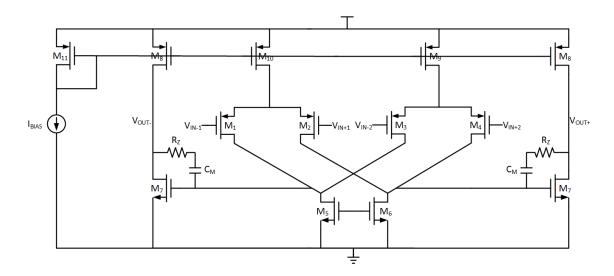

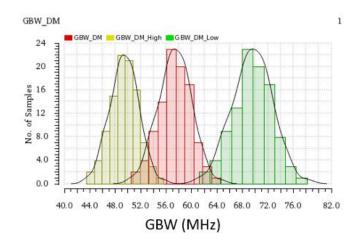

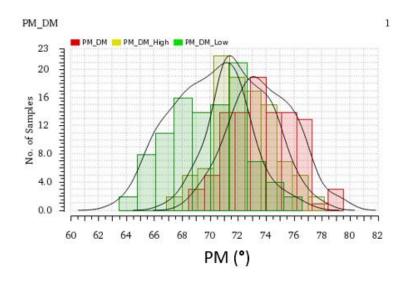

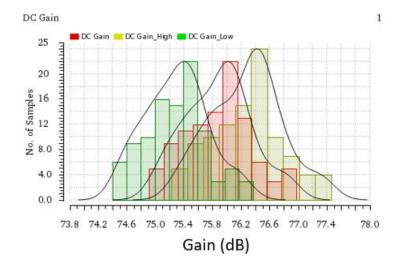

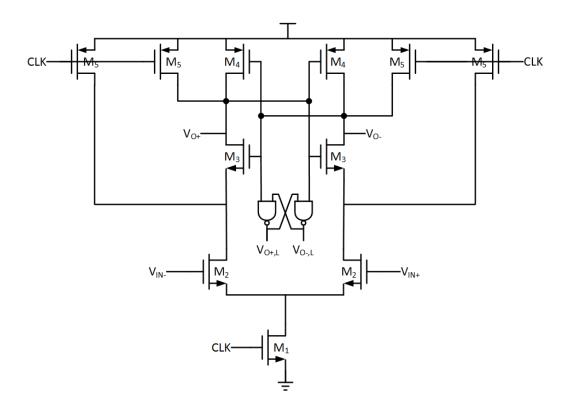

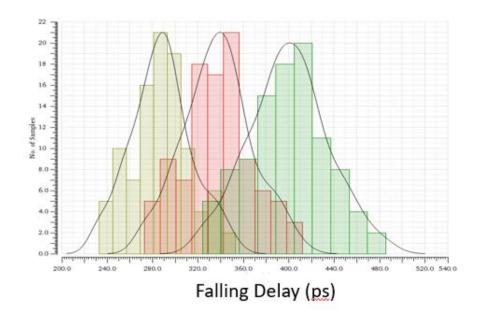

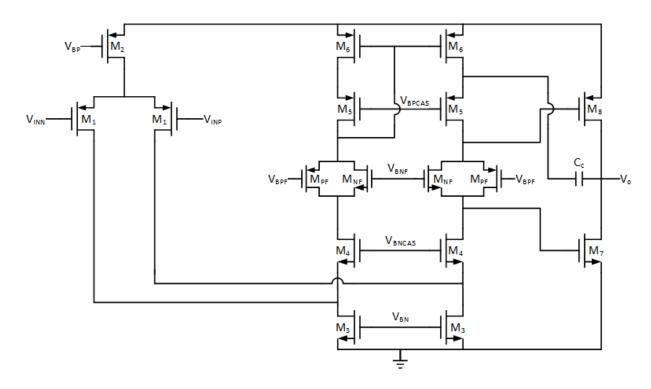

The FDDA is implemented using the schematic in Figure 20 below. The implementation is a fully differential, Miller-compensated op-amp with a zero nulling resistor and two differential pairs at the input to implement the differential-difference operation. We select the transconductance of the input transistors,  $g_{m1-4}$ , and the miller capacitor  $C_M$  to provide a gain-bandwidth (GBW) of approximately 20MHz. Therefore, with process and temperature variations, the bandwidth of the buffer should remain above 1.5MHz. Next, we select the size and bias of transistor  $M_7$  to ensure the second pole of the amplifier is at least twice the GBW of the amplifier. This, in combination with selecting the value of  $R_z$  to move the RHP zero formed by  $C_M$  to infinity, ensures that the

phase margin remains above  $60^{\circ}$ . Lastly, the sizes of  $M_5$  and  $M_6$  are sized with long lengths and relatively short widths to decrease their transconductance and ensure they do not contribute excessive noise.

**Figure 20. FDDA Schematic**

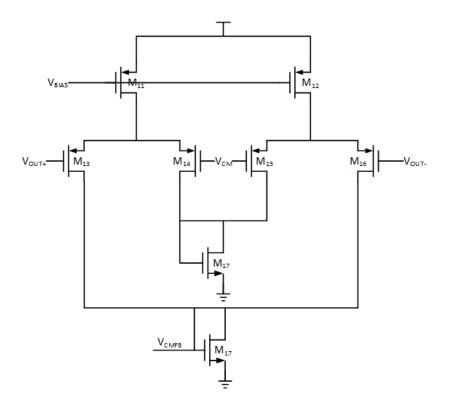

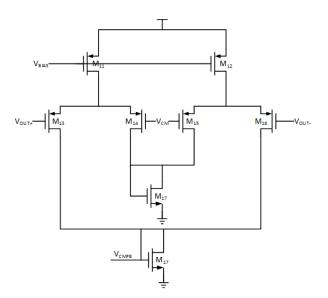

Since the output common-mode level of the FDDA is not well-defined, a commonmode feedback (CMFB) circuit is required. The CMFB amplifier used is shown below in Figure 21. This circuit does not resistively load the output of the amplifier and compares the common-mode output of the FDDA to the desired voltage,  $V_{CM}$ . This amplifier then adjusts the voltage  $V_{CMFB}$ , which is connected to  $M_5$  and  $M_6$  in Figure 20 to adjust the common-mode output.  $M_{17}$  is sized such that the current density ( $I_D/(W/L)$ ) is equal to the current density of  $M_3$  and  $M_4$ . This ensures that there is no offset in the output common-mode voltage.

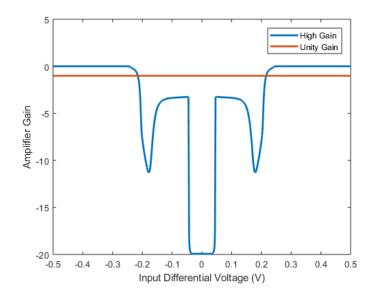

Figure 21. CMFB Circuit for FDDA