## POWER AND PERFORMANCE OPTIMIZATION IN GPGPU

## A Dissertation

## by

# AHMAD MAHMOUD MESLEH RADAIDEH

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Paul Gratz         |

|---------------------|--------------------|

| Committee Members,  | Jiang Hu           |

|                     | Ulisses Braga Neto |

|                     | Eun Kim            |

| Head of Department, | Miroslav Begovic   |

May 2020

Major Subject: Computer Engineering

Copyright 2020 Ahmad Mahmoud Mesleh Radaideh

### ABSTRACT

Thread parallel hardware, as the Graphics Processing Units (GPUs), greatly outperform CPUs in providing high compute throughput and memory bandwidth which make them ideal for accelerating various data-parallel applications. These hardware designs provide high performance computing by supporting a massive thread level parallelism (TLP) processing model. Our work focuses on making the thread parallel hardware more power and energy efficient and higher performance. It also focuses on making the simulation of this type of hardware more accurate. Our work is divided into three main parts: (1) We introduce a coalescing-aware register file organization that takes advantage of frequent narrow-width data present in general-purpose applications in order to increase performance and reduce energy consumption in GPU. We present a new design that is capable of combining read and write accesses originated from same or different warps into fewer accesses. Our design reduces the number of register file accesses by 30.5%, achieves IPC speedup of 16.5%, and reduces overall GPU energy by 32.2% on average. (2) We present a low-cost power saving scheme in GPU that dynamically exploits frequent zero data within and across registers in order to gate off register file reads and writes and execution units to reduce dynamic power without impacting performance. Our scheme reduces register file reads and writes on average by 50% and 54%, respectively. The register file and execution unit dynamic power are reduced on average by 27% and 19%, respectively. The reduction in total GPU dynamic power achieved is about 8% on average. (3) For multi-threaded applications, the results taken from full system architecture simulation can often be inconsistent, primarily because of a combination of small input sets and the behavior of the Linux thread scheduler. We propose a simple solution wherein the scheduler is modified to enforce mapping of software threads into available distinct processors that provides consistent runtimes for short-run, multi-thread benchmarks, leading to expected, consistent experimental results.

# DEDICATION

To all my family with love.

## ACKNOWLEDGMENTS

I would like to thank my advisor Dr. Paul Gratz for his invaluable guidance and feedback that made this work successful. I would also like to thank my committee members, Dr. Eun Kim, Dr. Jiang Hu, and Dr. Ulisses Braga Neto, for their time and effort reviewing this work. Finally, I would like to thank all my family, my father, brothers, sisters, and my wife and daughter, for their endless love, encouragement, and support.

## CONTRIBUTORS AND FUNDING SOURCES

## Contributors

This work was supported by a dissertation committee consisting of my advisor Dr. Paul Gratz, Dr. Jiang Hu, and Dr. Ulisses Braga Neto of the Department of Electrical and Computer Engineering and Dr. Eun Kim of the Department of Computer Science and Engineering.

All work conducted for the dissertation was completed by the student, Ahmad Radaideh, independently.

## **Funding Sources**

Graduate study was supported in part by a tuition assistance program from Qualcomm Technologies, Inc.

# TABLE OF CONTENTS

| AF | BSTR                              | ACT                                         |                                                                                                                                                                                         | ii                                         |

|----|-----------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Dł | EDIC.                             | ATION                                       |                                                                                                                                                                                         | iii                                        |

| AC | CKNC                              | WLED                                        | GMENTS                                                                                                                                                                                  | iv                                         |

| CO | ONTF                              | RIBUTC                                      | ORS AND FUNDING SOURCES                                                                                                                                                                 | v                                          |

| TA | BLE                               | OF CC                                       | NTENTS                                                                                                                                                                                  | vi                                         |

| LI | ST O                              | F FIGU                                      | RES                                                                                                                                                                                     | ix                                         |

| LI | ST O                              | F TABI                                      | LES                                                                                                                                                                                     | xv                                         |

| 1. | INT                               | RODUC                                       | CTION                                                                                                                                                                                   | 1                                          |

|    | $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5$ | Exploit<br>Archite<br>Dissert               | er File Access Coalescing in GPU<br>ting Zero Data to Reduce Power Consumption in GPU<br>ecture Simulation and the Impact of Linux Thread Scheduler<br>ation Statement<br>ation Outline | 2<br>4<br>5<br>8<br>9                      |

| 2. | BAC                               | KGRO                                        | UND                                                                                                                                                                                     | 10                                         |

|    | <ul><li>2.1</li><li>2.2</li></ul> | $2.1.1 \\ 2.1.2 \\ 2.1.3 \\ 2.1.4 \\ 2.1.5$ | n GPU Architecture Model<br>CUDA Overview<br>GPU Chip Layout<br>Warp Scheduler<br>Register File<br>Execution Units<br>stem Simulation                                                   | $\begin{array}{c} 14\\ 15\\ 17\end{array}$ |

| 3. | REC                               | ISTER                                       | FILE ACCESS COALESCING IN GPU                                                                                                                                                           | 22                                         |

|    | $3.1 \\ 3.2 \\ 3.3$               | Perform                                     | action<br>nance Impact of Limited Access Ports<br>tion<br>Register Operands Width<br>Register File Bandwidth<br>Warp Instruction Operands                                               | 22<br>22<br>25<br>25<br>27<br>28           |

|    | 3.4 | Prome  | oting Coalescing Opportunities                      | 29 |

|----|-----|--------|-----------------------------------------------------|----|

|    | 3.5 | Relate | d Work                                              | 32 |

|    |     | 3.5.1  | Non-coalescing Techniques                           |    |

|    |     | 3.5.2  | Register Coalescing Techniques                      |    |

|    | 3.6 | Regist | er File Access Coalescing Design                    | 39 |

|    |     | 3.6.1  | Design Overview                                     | 40 |

|    |     | 3.6.2  | Coalescing-aware Register File Organization         | 43 |

|    |     |        | 3.6.2.1 Registers Layout (Register to Bank Mapping) |    |

|    |     |        | 3.6.2.2 Register File Bank                          | 44 |

|    |     |        | 3.6.2.3 Register Alignment                          |    |

|    |     |        | 3.6.2.4 Dual-access Banks                           | 49 |

|    |     |        | 3.6.2.5 Register File Bank Arbiter                  |    |

|    |     |        | 3.6.2.6 Register File Interconnect                  |    |

|    |     |        | 3.6.2.7 Operand Collector Write                     |    |

|    |     |        | 3.6.2.8 Register Width Detection                    |    |

|    |     |        | 3.6.2.9 Design Overhead                             | 61 |

|    | 3.7 | Evalua | ation                                               |    |

|    | 0   | 3.7.1  | Methodology                                         | 62 |

|    |     | 3.7.2  | Register File Access Reduction                      | 65 |

|    |     | 3.7.3  | Register File Bandwidth Increase                    | 67 |

|    |     | 3.7.4  | Register File Coalesced Access                      | 70 |

|    |     | 3.7.5  | IPC Performance Speedup                             |    |

|    |     | 3.7.6  | Dynamic Energy Reduction                            |    |

|    |     | 3.7.7  | Result Summary                                      |    |

|    | 3.8 |        | usion                                               | 75 |

|    | 0.0 | 0      |                                                     |    |

| 4. | EXP | LOITI  | NG ZERO DATA TO REDUCE REGISTER FILE AND EXECUTION  |    |

|    | UNI | T DYN  | AMIC POWER CONSUMPTION IN GPU                       | 77 |

|    |     |        |                                                     |    |

|    | 4.1 |        | uction                                              |    |

|    | 4.2 |        | ation                                               |    |

|    | 4.3 |        | ing Register File Dynamic Power                     | 80 |

|    |     | 4.3.1  | Using the Thread Active Mask                        |    |

|    |     | 4.3.2  | Using the In-lane Zero Mask                         |    |

|    |     | 4.3.3  | Using the Cross-lane Zero Mask                      | 84 |

|    |     | 4.3.4  | Dynamic Zero Mask Selection                         | 85 |

|    | 4.4 |        | ing Execution Unit Dynamic Power                    |    |

|    |     | 4.4.1  | Using the Active Thread Mask                        |    |

|    |     | 4.4.2  | Using the Operand Zero Masks                        | 88 |

|    | 4.5 |        | ation                                               | 89 |

|    |     | 4.5.1  | Register File Power                                 | 90 |

|    |     | 4.5.2  | Execution Units Power                               | 92 |

|    |     | 4.5.3  | GPGPU total Power                                   | 94 |

|    | 4.6 |        | ed Work                                             | 95 |

|    | 4.7 | Conclu | usion                                               | 97 |

| 5. |     | TI-PROCESSOR FULL SYSTEM SIMULATION AND THE IMPACT OF UX THREAD SCHEDULER                                                                                              | 98              |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|    | -   | IntroductionBehavior of Thread Scheduler in Full System Simulation5.2.1Thread Scheduling and Load Imbalance5.2.2Periodic Load balancing15.2.3Immediate Load balancing1 | 98<br>98<br>.00 |

|    | 5.3 | Proposed Solution                                                                                                                                                      |                 |

|    | 5.4 | Evaluation1                                                                                                                                                            | 04              |

|    | 5.5 | Conclusion1                                                                                                                                                            | .09             |

| 6. | CON | ICLUSION1                                                                                                                                                              | 10              |

| RE | FER | ENCES 1                                                                                                                                                                | 12              |

# LIST OF FIGURES

| FIGUR | LE F                                                                                                                                                                                                                                                                                 | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

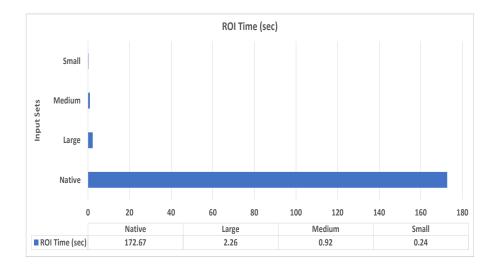

| 1.1   | Actual run-time of 12-thread Canneal benchmark with different input sets on 12-core hardware machine                                                                                                                                                                                 | 6    |

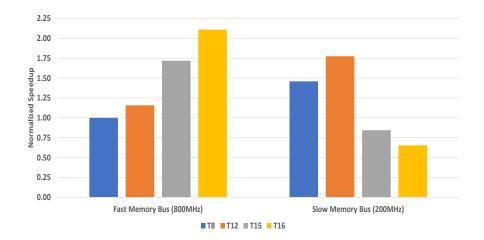

| 1.2   | Performance speedup for Canneal benchmark using small input set, with 8, 12, 15, and 16 threads under memory speeds of 200MHz and 800MHz in full system simulation with original Linux scheduler. Results are normalized against an 8-thread 800MHz case.                            | . 7  |

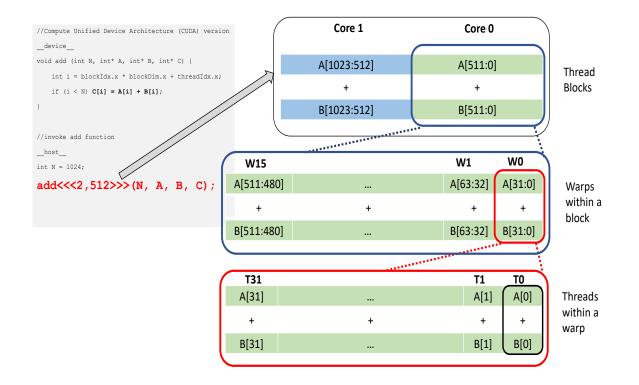

| 2.1   | C++ code example for vector addition (a) Serial code that typically runs on CPU. (b) CUDA thread-parallel version of the code that runs on GPU                                                                                                                                       | 11   |

| 2.2   | CUDA hierarchy of threads that maps to a hierarchy of processing elements on the GPU.                                                                                                                                                                                                | . 12 |

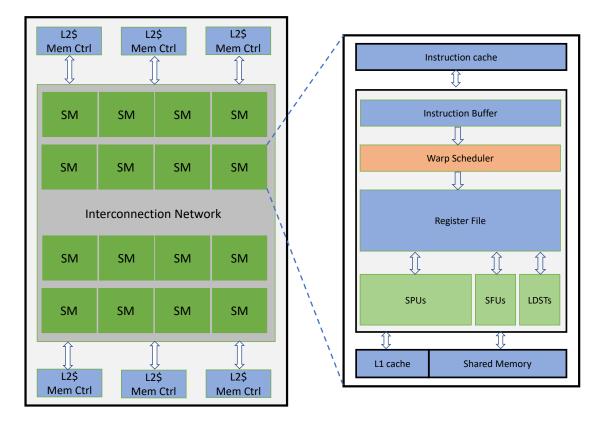

| 2.3   | Modern GPU chip layout with 16 Streaming Multiprocessors (SMs), each of which has its own register file, instruction and data caches, and execution units. Reprinted from [1].                                                                                                       | . 13 |

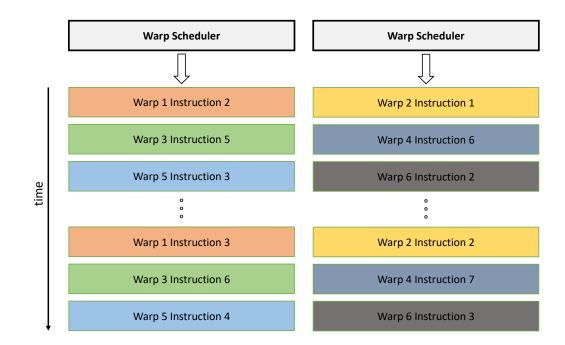

| 2.4   | Dual-warp scheduler used in Fermi GPU. Reprinted from [1].                                                                                                                                                                                                                           | 14   |

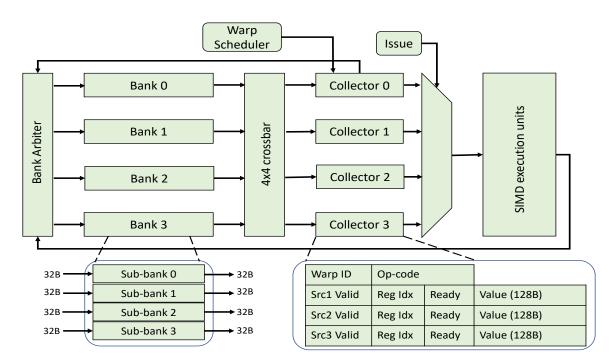

| 2.5   | GPU main register file and execution pipeline                                                                                                                                                                                                                                        | 15   |

| 2.6   | A 128B warp register entry in one register file bank occupying four 32B sub-<br>bank entries that have the same index. Each 32B sub-bank entry holds data<br>for 8 threads within the warp.                                                                                          | 16   |

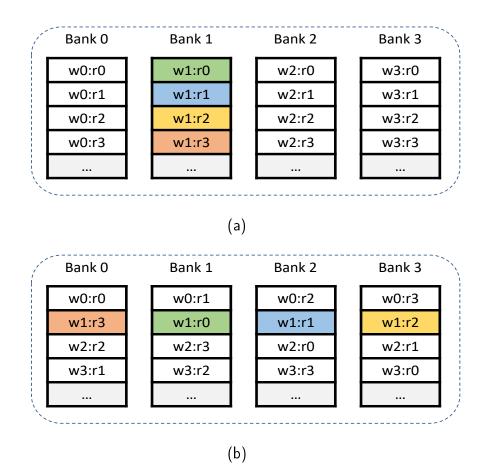

| 2.7   | Register-to-bank mapping (layout) with warp registers interleaved across reg-<br>ister file banks                                                                                                                                                                                    | . 16 |

| 2.8   | Execution units in a GPU Streaming Multiprocessor (SM) core with 32 Stream-<br>ing Processing Units (SPUs), 4 Special Functional Units (SFUs), and 16 mem-<br>ory Load/Store Units (LDSTs). Reprinted from [1]                                                                       | . 18 |

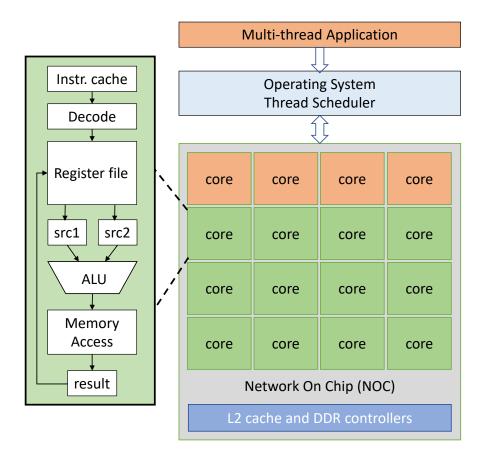

| 2.9   | Full system simulation environment for a Core Multi-Processor (CMP) chip<br>with 16 cores managed by a real Operating System (OS) running a thread<br>scheduler. The full simulation system runs multi-threaded user applications<br>similar to a real multi-core system with an OS. | . 19 |

| 3.1   | A limit study on the potential IPC performance speedup of reducing register file banks port conflicts.                                                                                                                                                                               | 23   |

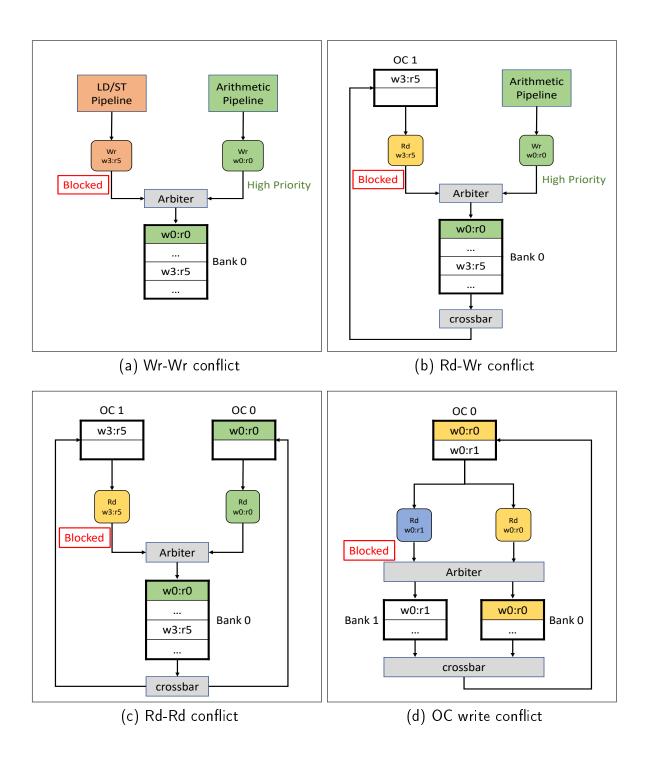

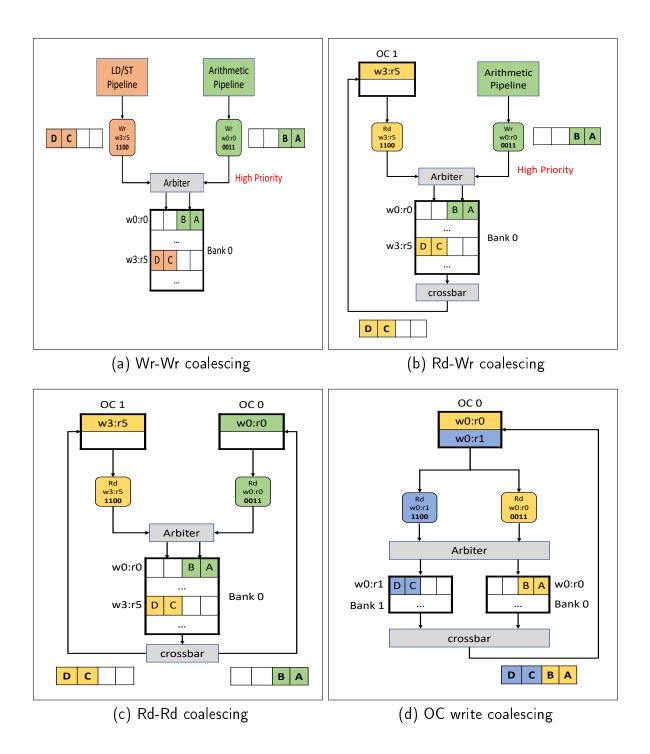

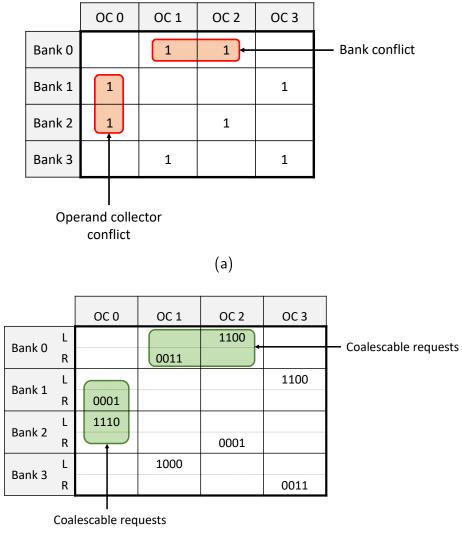

| 3.2  | Examples of port conflict on register file bank and operand collector accesses<br>(a) Bank conflict between two write requests. (b) Bank conflict between a<br>read and a write request. (c) Bank conflict between two read requests. (d)<br>Port conflict on two writes to an operand collector unit                      | 24 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

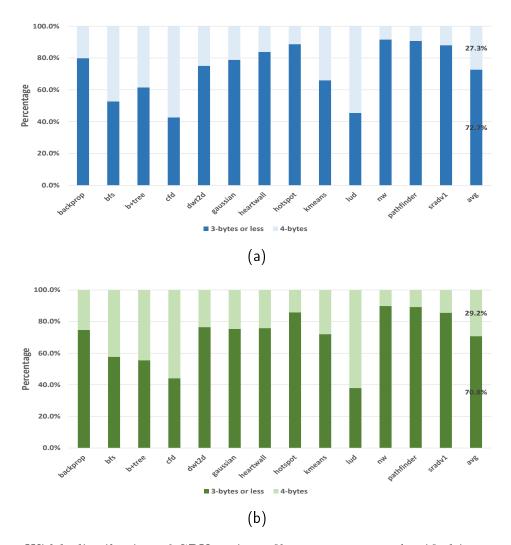

| 3.3  | Width distribution of GPU register file warp accesses classified into two groups:<br>accesses that require 4-byte per thread (full width) and accesses that require<br>less than 4-byte per thread (narrow width) (a) source operands width distri-<br>bution (b) destination operands width distribution                  | 26 |

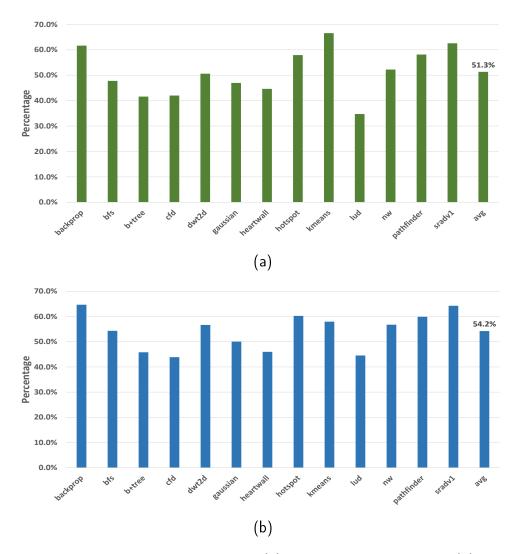

| 3.4  | Unused register file bandwidth on (a) register file banks access (b) collector<br>units write access.                                                                                                                                                                                                                      | 27 |

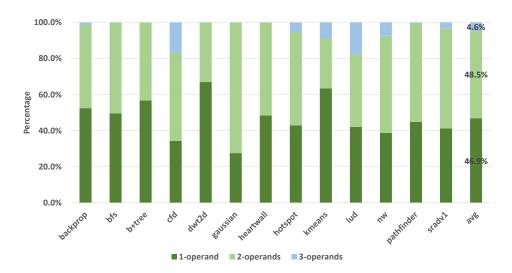

| 3.5  | Percentage of the number of source register operands in warp instructions. A given warp instruction can have one, two, or three source register operands                                                                                                                                                                   | 28 |

| 3.6  | Examples of register coalescing on register file bank and operand collector<br>accesses (a) Access coalescing of two write requests. (b) Access coalescing of<br>a read and a write request. (c) Access coalescing of two read requests. (d)<br>Access coalescing of two writes to an operand collector unit               | 30 |

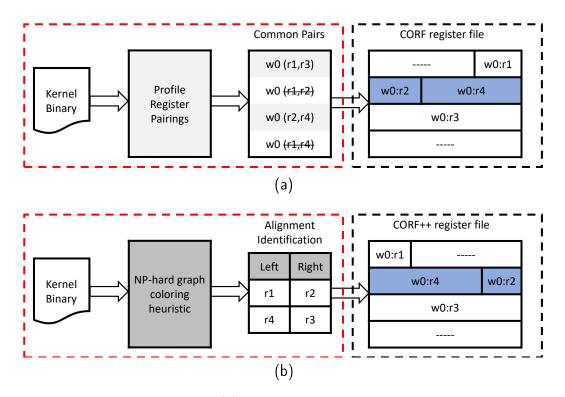

| 3.7  | CORF design overview (a) limited CORF with read coalescing support within<br>the same physical register entry (b) enhanced CORF++ with read coalescing<br>support across two register entries within a bank. Reprinted from [2]                                                                                            | 35 |

| 3.8  | GPU register file design used in CORF. Reprinted from [2]                                                                                                                                                                                                                                                                  | 36 |

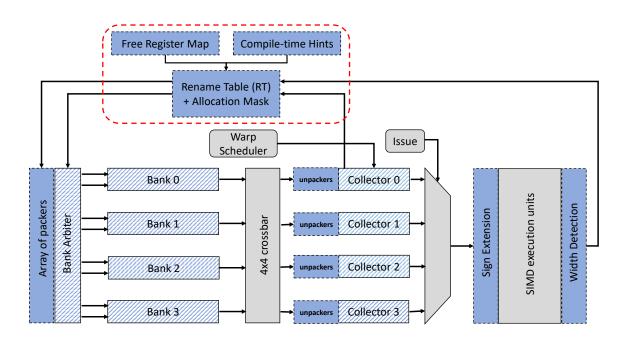

| 3.9  | Our coalescing-aware GPU register file design                                                                                                                                                                                                                                                                              | 40 |

| 3.10 | Registers to banks mapping (register layouts): (a) all registers belonging to<br>the same warp are mapped into one register file bank and (b) warp registers<br>are interleaved across register file banks                                                                                                                 | 43 |

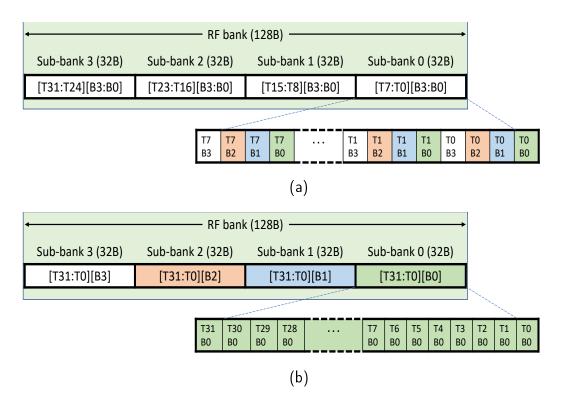

| 3.11 | Data format of a 128B warp register within an RF bank entry: (a) Byte-<br>interleaved format: each 32B sub-bank entry holds data for 8 threads in the<br>warp and (b) Thread-interleaved format (supports register coalescing): each<br>32B sub-bank entry holds 1-byte (same byte number) for every thread in the<br>warp | 45 |

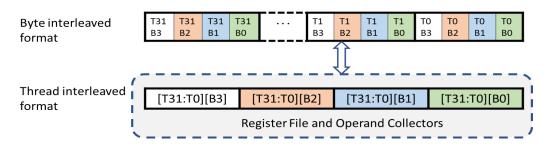

| 3.12 | Register data representation within the register file and operand collectors<br>and outside. Switching data from one format to the other is done through<br>wiring bytes into different byte-position (no logic cost)                                                                                                      | 45 |

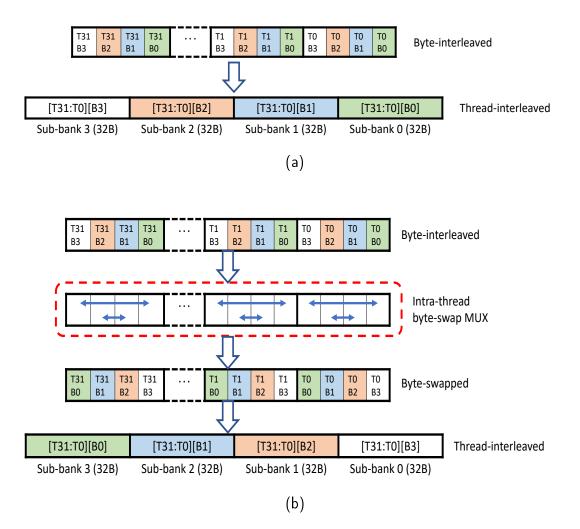

| 3.13 | Warp register data alignment: (a) Default right-alignment with byte 0 for all 32 threads map to sub-bank 0 and (b) Left alignment using intra-thread byte-swap MUX with byte 0 for all 32 threads map to sub-bank 3                                                                                                        | 47 |

| 3.14 | Data alignment of warp registers within a register file bank based on even/odd register entry number. Even registers are right aligned with byte 0 of all threads map to sub-bank 0. Odd registers are left aligned (byte swapped) with byte 0 of all threads map to sub-bank 3                                                                                                                                  | 48 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

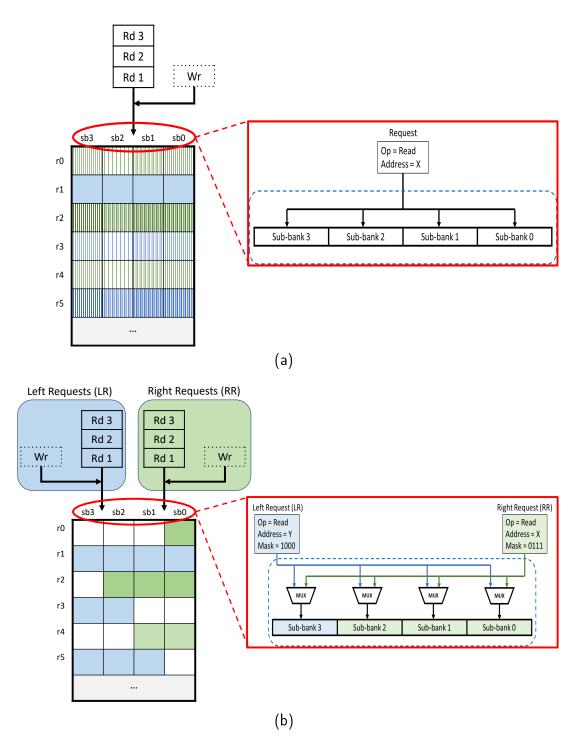

| 3.15 | Comparison between basline register file bank and our coalescing-aware bank:<br>(a) Baseline bank with single-access support (b) Our dual-access bank with<br>left and right requests that can access two register entries with different data<br>alignments in non-overlapping sub-banks.                                                                                                                       | 50 |

| 3.16 | Register file request matrix: (a) Request matrix for baseline arbiter. Up to four requests can be granted access at the same time (b) Request matrix for our coalescing-aware arbiter. Each bank can have left or right requests with each request having a 4-bit mask to indicate the sub-banks it needs to access. Up to eight requests (four coalesced requests) can be granted access at the same time.      | 53 |

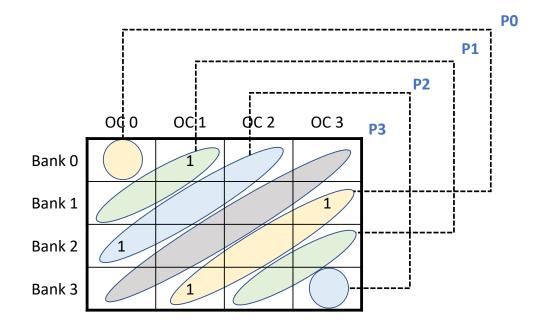

| 3.17 | A wrapped wavefront arbitration scheme (WWFA) used in GPU register file matrix arbiter. Four priority diagonals are used $P0-P3$ with a priority wave initially starting at $P0$ and propagating from one diagonal to the next every cycle.                                                                                                                                                                      | 54 |

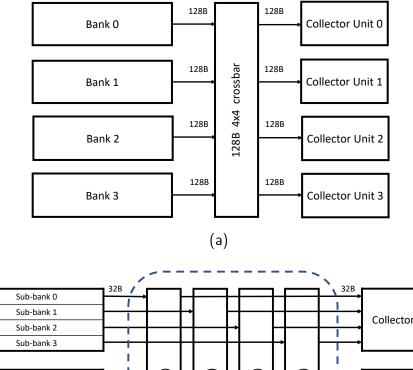

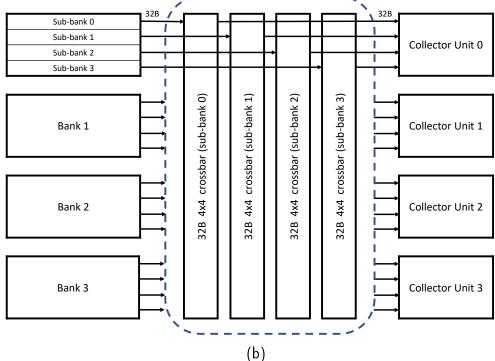

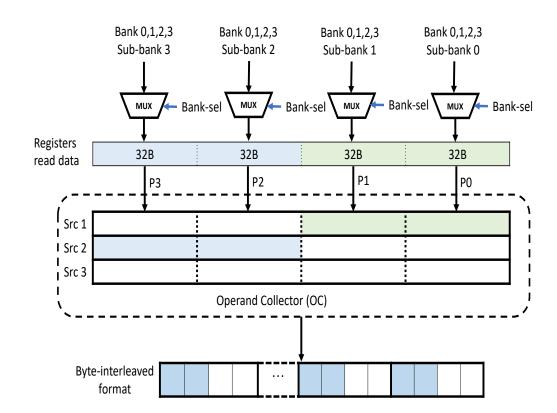

| 3.18 | Register file interconnect: (a) Baseline $4 \times 4$ crossbar with 128B ports that connects register file banks to the operand collector units. (b) New crossbar structure used in our design, which supports register coalescing at no extra cost, with four $4 \times 4$ crossbars each of which has narrow 32B ports and connects a particular sub-bank (from all four banks) to the operand collector units | 56 |

| 3.19 | Coalescing-aware operand collector unit with 32B write ports. Coalesced read data is naturally unpacked into the destined source operands buffering space                                                                                                                                                                                                                                                        | 58 |

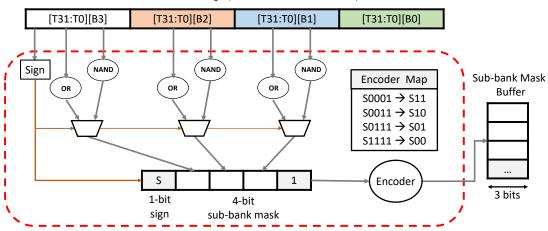

| 3.20 | Width detection and sub-mask generation logic for a warp result in WB stage.<br>The 4-bit sub-bank mask is saved in a buffer in a 2-bit encoded form along with the sign-bit.                                                                                                                                                                                                                                    | 60 |

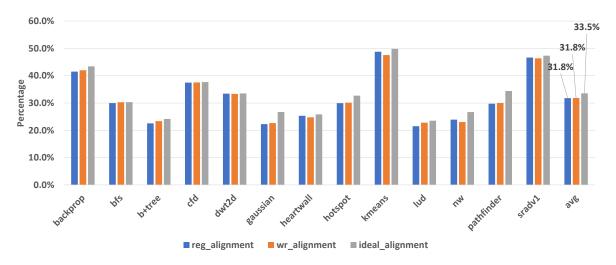

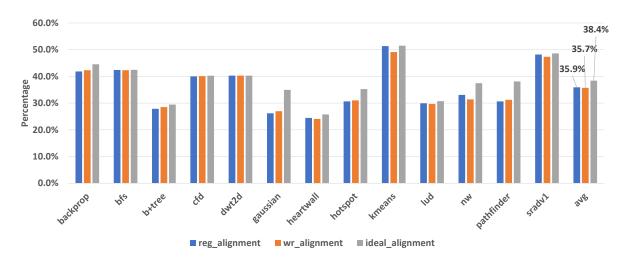

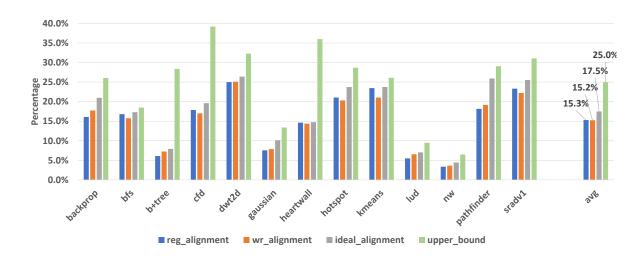

| 3.21 | Percentage of register file access reduction with a <i>wid_layout</i> register file and using different register alignment schemes: fixed alignment based on register number ( <i>reg_alignment</i> ), write interleaved alignment ( <i>wr_alignement</i> ), and an ideal alignment ( <i>ideal_alignment</i> ).                                                                                                  | 66 |

| 3.22 | Percentage of operand collectors write reduction with a <i>wid_layout</i> register<br>file and using different register alignment schemes: fixed alignment based<br>on register entry number ( <i>reg_alignment</i> ), register interleaved alignment on<br>writes ( <i>wr_alignement</i> ), and an ideal alignment ( <i>ideal_alignment</i> )                                                                   | 66 |

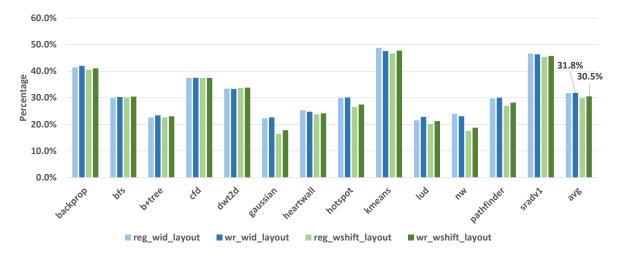

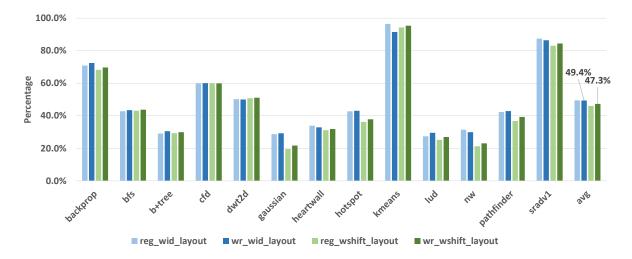

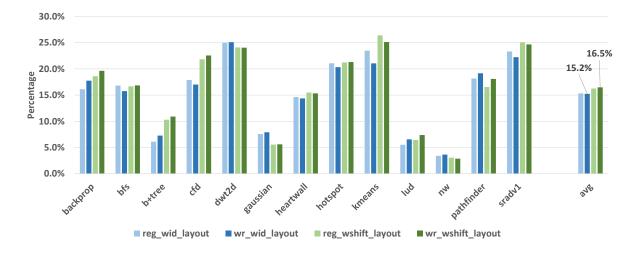

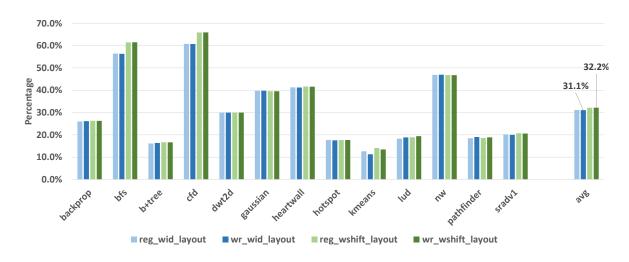

| 3.23 | Percentage of register file access reduction comparison between two different register file layouts: $wid\_layout$ and $wshift\_layout$ using two register alignment schemes: fixed alignment based on register number $(reg\_*)$ and write interleaved alignment $(wr\_*)$                                                                                                     | 67 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

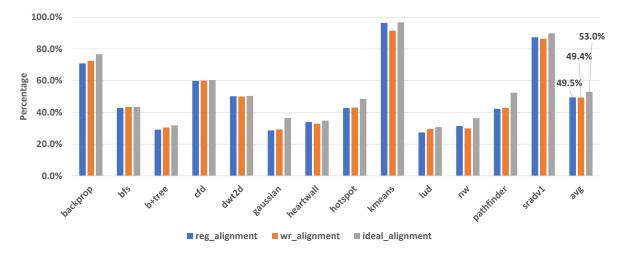

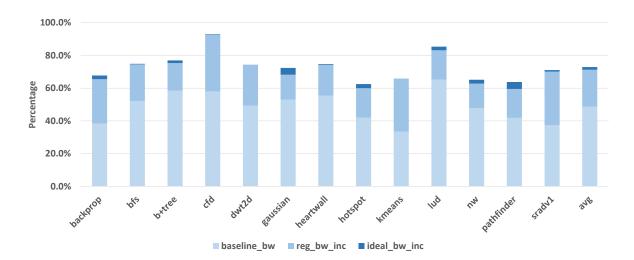

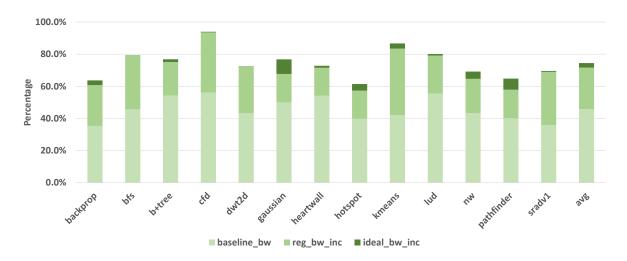

| 3.24 | Percentage of register file bandwidth increase with a <i>wid_layout</i> register file<br>and using different register alignment schemes: fixed alignment based on reg-<br>ister number ( <i>reg_alignment</i> ), write interleaved alignment ( <i>wr_alignement</i> ),<br>and an ideal alignment ( <i>ideal_alignment</i> )                                                     | 68 |

| 3.25 | Percentage of operand collectors bandwidth increase with a <i>wid_layout</i> register file and using different register alignment schemes: fixed alignment based on register entry number ( <i>reg_alignment</i> ), register interleaved alignment on writes ( <i>wr_alignement</i> ), and an ideal alignment ( <i>ideal_alignment</i> )                                        | 68 |

| 3.26 | Percentage of used register file bandwidth showing the bandwidth increase from register coalescing using a fixed register alignment $(reg\_bw\_inc)$ and an ideal register alignment $(ideal\_bw\_inc)$ over the baseline bandwidth $(base-line\_bw)$                                                                                                                           | 69 |

| 3.27 | Percentage of used operand collector bandwidth showing the bandwidth increase from register coalescing using a fixed register alignment $(reg\_bw\_inc)$ and an ideal register alignment $(ideal\_bw\_inc)$ over the baseline bandwidth $(baseline\_bw)$ .                                                                                                                      | 69 |

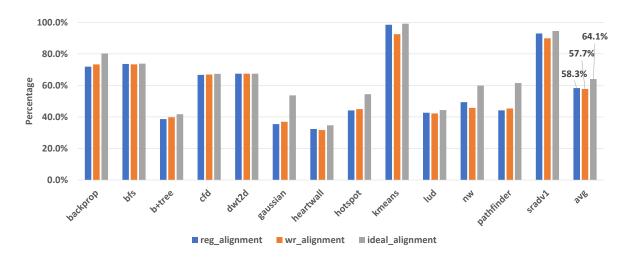

| 3.28 | Percentage of register file bandwidth increase comparison between two dif-<br>ferent register file layouts: $wid\_layout$ and $wshift\_layout$ using two register<br>alignment schemes: fixed alignment based on register number $(reg\_*)$ and<br>write interleaved alignment $(wr\_*)$                                                                                        | 70 |

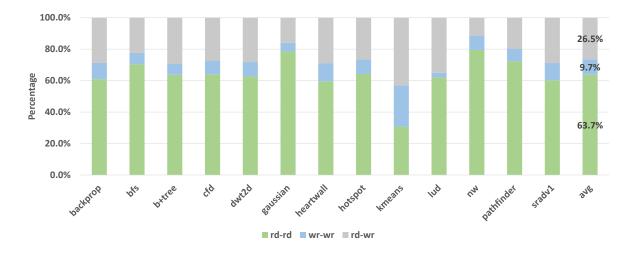

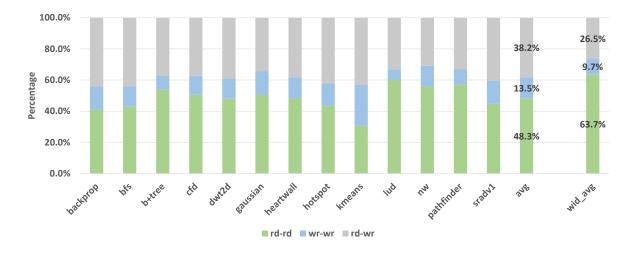

| 3.29 | Breakdown of register file coalesced accesses with a $wid\_layout$ register file:<br>Read-Read coalesced accesses $(rd-rd)$ , Write-Write coalesced accesses $(wr-wr)$ ,<br>and Read-Write coalesced accesses $(rd-wr)$                                                                                                                                                         | 71 |

| 3.30 | Breakdown of register file coalesced accesses with a $wshift\_layout$ register file:<br>Read-Read coalesced accesses $(rd-rd)$ , Write-Write coalesced accesses $(wr-wr)$ ,<br>and Read-Write coalesced accesses $(rd-wr)$                                                                                                                                                      | 71 |

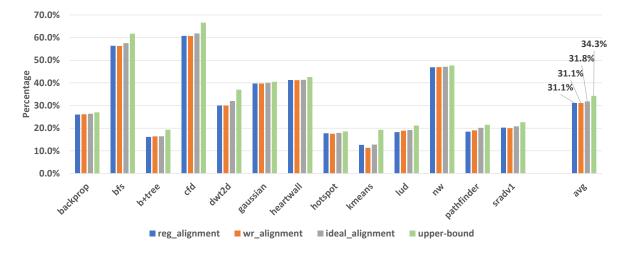

| 3.31 | Percentage of overall IPC speedup in GPU with a <i>wid_layout</i> register file<br>and using different register alignment schemes: fixed alignment based on reg-<br>ister number ( <i>reg_alignment</i> ), write interleaved alignment ( <i>wr_alignement</i> ),<br>and an ideal alignment ( <i>ideal_alignment</i> ) compared to the upper bound ( <i>up-<br/>per_bound</i> ). | 72 |

|      |                                                                                                                                                                                                                                                                                                                                                                                 | 14 |

| 3.32 | Percentage of overall IPC speedup comparison between two different register file layouts: $wid\_layout$ and $wshift\_layout$ using two register alignment schemes: fixed alignment based on register number $(reg\_*)$ and write interleaved alignment $(wr\_*)$                                                                                                                              | 73 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

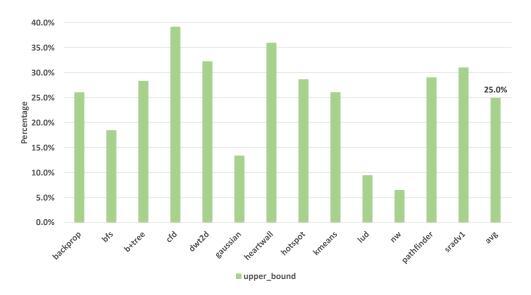

| 3.33 | Percentage of overall dynamic energy reduction in GPU with a <i>wid_layout</i> register file and using different register alignment schemes: fixed alignment based on register entry number ( <i>reg_alignment</i> ), register interleaved alignment on writes ( <i>wr_alignement</i> ), and an ideal alignment ( <i>ideal_alignment</i> ) compared to the upper bound ( <i>upper_bound</i> ) | 74 |

| 3.34 | Percentage of overall dynamic energy reduction comparison between two dif-<br>ferent register file layouts: $wid\_layout$ and $wshift\_layout$ using two register<br>alignment schemes: fixed alignment based on register number $(reg\_*)$ and<br>write interleaved alignment $(wr\_*)$                                                                                                      | 74 |

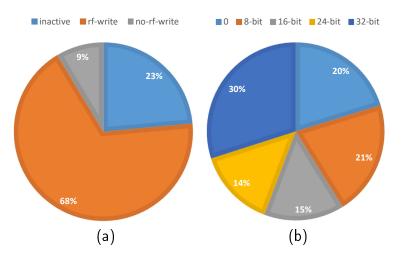

| 4.1  | GPGPU application warp thread statistics: (a) Percentage of warp threads in<br>an inactive state, active and writing to register file, and active but not writing<br>to register file. (b) Percentage of warp thread results with zero and non-zero<br>values that can be represented with 8, 16, 24, and 32 bits                                                                             | 78 |

| 4.2  | GPGPU main register file and execution pipeline with added components for power reduction highlighted.                                                                                                                                                                                                                                                                                        | 80 |

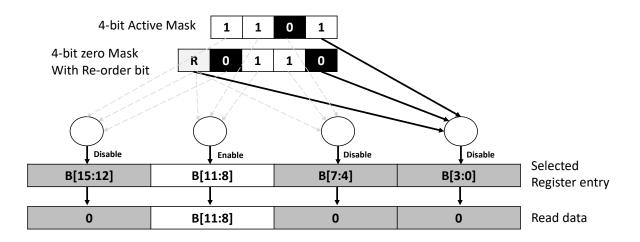

| 4.3  | Usign the thread active mask and operand zero mask to gate off register file read access to the first four threads in a warp register                                                                                                                                                                                                                                                         | 81 |

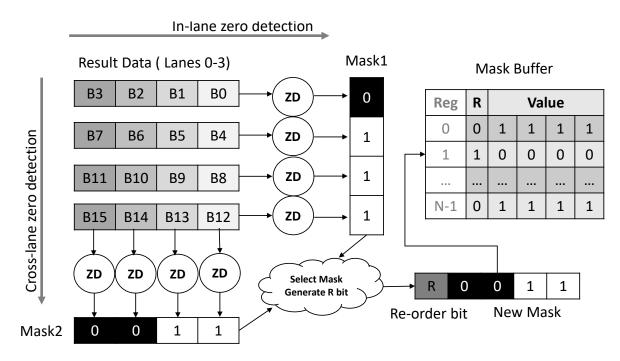

| 4.4  | Generating the zero mask from data result produced by four execution lanes                                                                                                                                                                                                                                                                                                                    | 83 |

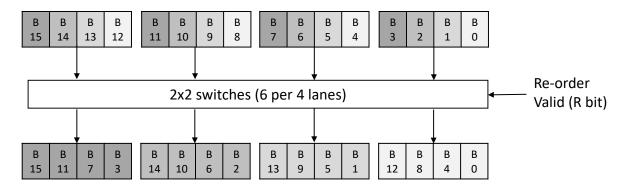

| 4.5  | Data re-ordered in byte-position form to take advantage of low dynamic range values for power reduction                                                                                                                                                                                                                                                                                       | 85 |

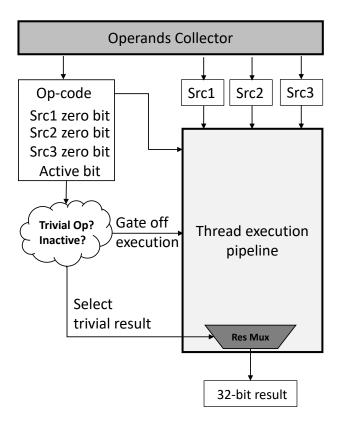

| 4.6  | Power reduction for one execution lane using thread active mask bit and operands zero mask bits                                                                                                                                                                                                                                                                                               | 87 |

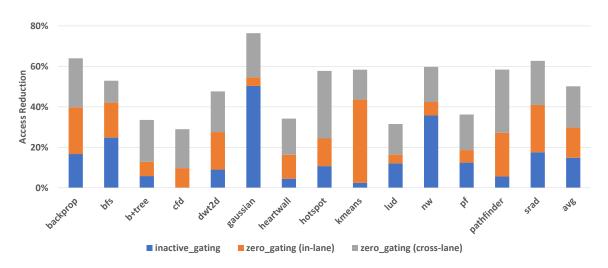

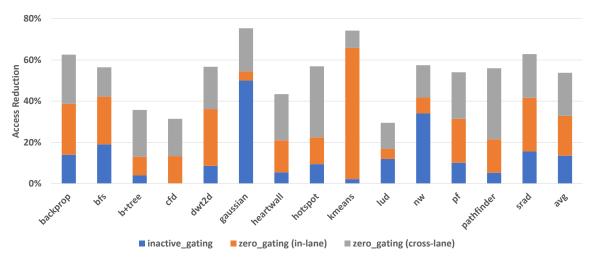

| 4.7  | Register file access reduction for read requests using power savings tech-<br>niques: access reduction using threads active mask (inactive_gating), in-lane<br>operands zero masks (zero_gating(in-lane)), and operands zero masks with<br>data re-ordering(zero_gating (cross-lane))                                                                                                         | 90 |

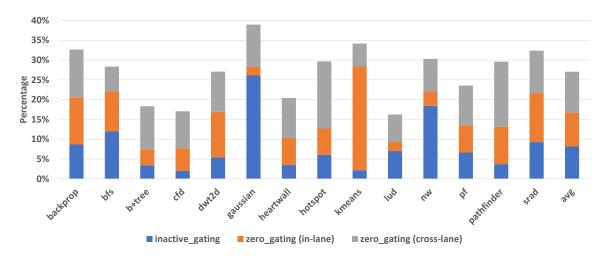

| 4.8  | Register file access reduction for write requests using power savings tech-<br>niques: access reduction using threads active mask (inactive_gating), in-lane<br>operands zero masks (zero_gating(in-lane)), and operands zero masks with<br>data re-ordering(zero_gating (cross-lane))                                                                                                        | 91 |

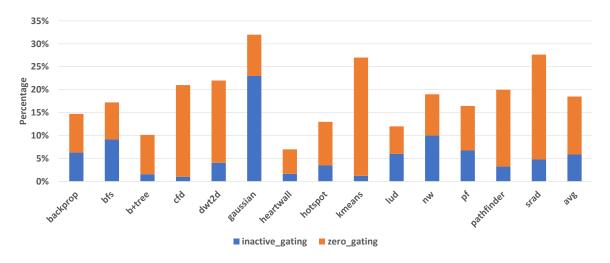

| 4.9  | Dynamic power reduction in GPGPU register file contributed by power reduc-<br>tion techniques using threads active mask (inactive_gating), in-lane operands<br>zero masks (zero_gating (in-lane)), and operands zero masks with data re-<br>ordering (zero_gating (cross-lane)) |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.10 | Dynamic power reduction in GPGPU execution units contributed by power<br>reduction techniques using threads active mask (inactive_gating) and trivial<br>operations handling using operands zero masks (zero_gating)                                                            |

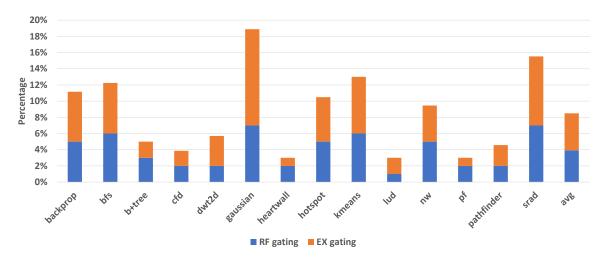

| 4.11 | Dynamic power reduction in total GPGPU chip power contributed by power<br>reduction techniques applied to the register file (RF gating) and the techniques<br>applied to the execution units (EX gating)                                                                        |

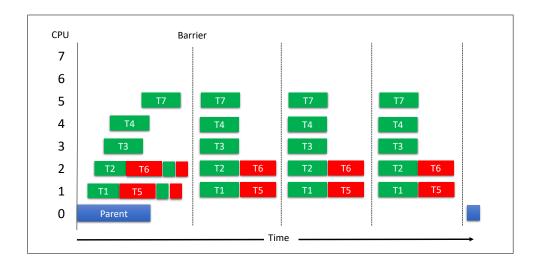

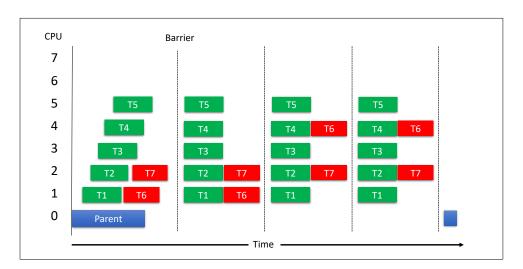

| 5.1  | Behavior of Linux scheduler for a multi-thread benchmark running on archi-<br>tecture simulator                                                                                                                                                                                 |

| 5.2  | Periodic load balancing done by Linux scheduler for a multi-thread benchmark<br>running on architecture simulator                                                                                                                                                               |

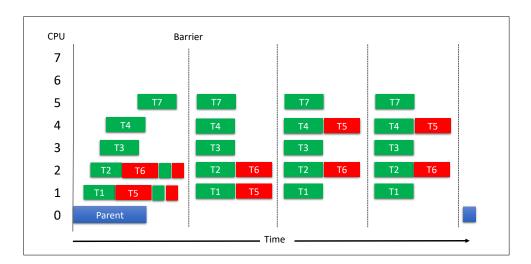

| 5.3  | Behavior of Linux scheduler with immediate load balancing for a multi-thread<br>benchmark running on architecture simulator                                                                                                                                                     |

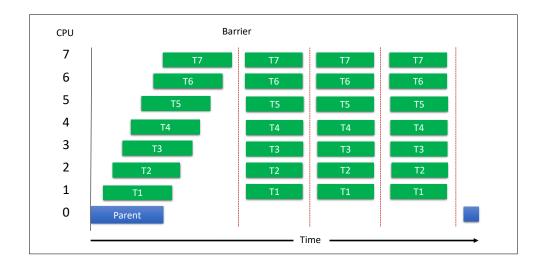

| 5.4  | Mapping of new thread and core status update with the patched scheduler. $\dots 104$                                                                                                                                                                                            |

| 5.5  | Behavior of patched Linux scheduler for a multi-thread benchmark running<br>on architecture simulator                                                                                                                                                                           |

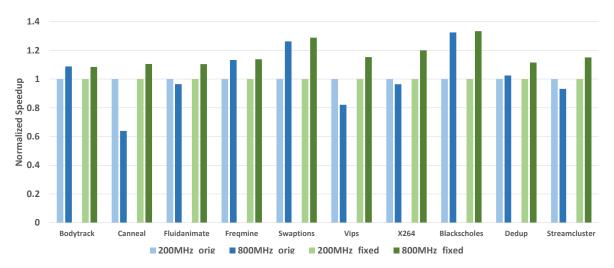

| 5.6  | Percentage of workload per core for 12-thread Canneal benchmark with dif-<br>ferent input sets run on 12-core hardware machine                                                                                                                                                  |

| 5.7  | Performance speedup for Canneal benchmark using small input set, with 8, 12, 15, and 16 threads under memory speeds of 200MHz and 800MHz in full system simulation with the patched Linux scheduler. Results are normalized against an 8-thread 800MHz case                     |

| 5.8  | Normalized performance speedup for PARSEC benchmarks runs with two<br>memory speed settings using current and patched Linux schedulers in full<br>system simulation                                                                                                             |

# LIST OF TABLES

| TABLE |                                                                                 | Page  |

|-------|---------------------------------------------------------------------------------|-------|

| 3.1   | Design overhead of CORF compared with our low-cost design                       | . 37  |

| 3.2   | Register coalescing support in CORF compared with our design                    | . 39  |

| 3.3   | Comparison between CORF dual-address banks and our new dual-access banks.       | . 51  |

| 3.4   | Design overhead cost for our coalescing-aware design compared with CORF design. | . 62  |

| 3.5   | Configuration parameters for our GPU design with register coalescing support    | . 63  |

| 3.6   | GPGPU application benchmarks from Rodinia general-purpose suite                 | . 63  |

| 3.7   | Summary of results achieved by our design compared with CORF design. $\dots$    | . 75  |

| 4.1   | GPU configuration parameters.                                                   | . 89  |

| 5.1   | Configurations of the hardware machine used                                     | . 105 |

| 5.2   | Configurations of the multi-core simulator used.                                | . 106 |

### 1. INTRODUCTION

In the single-core era, increasing performance primarily was obtained through transistor and clock frequency scaling while a constant power envelop was maintained due to Dennard scaling [3]. Dennard *scaling law* states that voltage and current of a digital integrated circuit scale with transistor dimensions, and therefore, power consumption is proportional to the circuit area. With the recent breakdown of Dennard scaling, the subsequent power consumption and heat dissipation constraints [4, 5], and the consequent inability to increase clock frequency significantly have forced the computer industry to rely upon core-count (and particularly thread level parallelism) scaling as the way forward to improve performance with increasing transistor density.

Thread parallel hardware significantly outperform single-core CPUs in both computational and memory bandwidth capabilities and became an ideal accelerator for multithreaded and data-parallel applications. Graphics processing units (GPUs) are thread parallel processors that concurrently run thousands of hardware threads for graphics applications. General-purpose GPUs (GPGPUs) achieve high compute throughput and remarkable performance speedups leveraging GPUs to run more general compute applications. The increasing computational complexity of general purpose applications demands for higher compute capabilities which have been primarily accomplished by integrating more compute resources and promoting higher number of parallel threads in the GPU.

To support massive thread level parallelism (TLP) and fast context switching between active threads, GPUs provide a large register file to hold execution state (context) of each thread and a large number of execution units to execute threads in parallel. The size of the register file in the GPU has been almost doubling for every new generation of the Nvidia GPUs, recently reaching 20MB in Tesla VG100 [6]. The number of execution units have been also increasing as the number of units in Tesla VG100 is eleven times the number found in Fermi GTX480 [1]. Prior power analysis showed that the register file and the execution units are the largest dynamic power consumers in the GPU and both contribute to about 40% of the total chip dynamic power consumption [7].

To avoid the high cost of multi-ported register file design, GPUs deploy a multi-banked structure with physical banks built using 6T SRAM arrays having a single read/write access port. The 6T arrays have a significant area benefit over 8T arrays at the cost of reducing the number of access ports from two to one. In addition, GPUs use single-ported operand collector units to capture the read data out of the register file banks. The register file banks operate in parallel to support high access demand and provide high bandwidth. However, due to access port limitation on the banks as well as the collector units, multiple access requests that target the same shared resource at the same time experience *port conflicts* and their access is serialized. As a result, register file access latency increases and negatively impacts overall GPU performance and energy efficiency.

### 1.1 Register File Access Coalescing in GPU

As mentioned earlier, port serialization on the GPU register file banks and operand collector units increase the register file access latency and negatively impact overall all performance and energy efficiency. In this work, we present a new register file design that supports read and write access coalescing in order to improve performance and reduce overall energy in GPGPU. Access coalescing has been used in memory system to combine multiple access requests to contiguous memory space into a single request in order to reduce memory traffic and improve bandwidth utilization. We applied the concept of access coalescing on GPU register file to combine multiple bank accesses that target different registers within the bank into fewer accesses. In addition, we also supported coalescing registers reads from different register file banks that target the same operand collector unit. Coalescing opportunities arise from the frequent narrow-width data found in general purpose compute applications that are read from and written into the register file. Read and write requests of narrow-width data that target register file banks can be combined to reduce the number of bank accesses, yield higher bandwidth utilization for register file banks and operand collectors, reduce register file and operand collectors ports contention, and as a result, improve overall performance and energy efficiency in GPU.

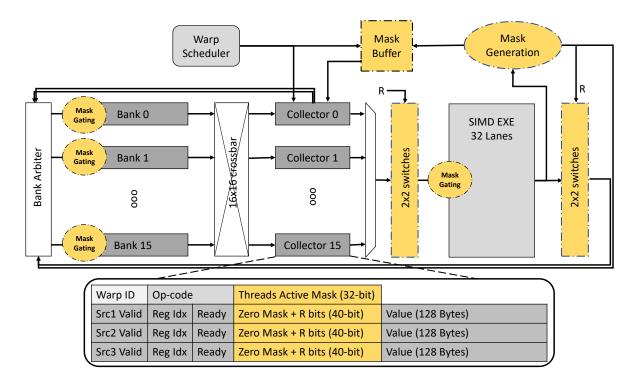

Our design seeks to support all possible coalescing opportunities between access requests that contend on the limited access ports available on the register file banks and the operand collectors. The register file bank is physically built with multiple sub-banks each of which holds a slice of every physical register entry. In our design, a narrow-width read or write request into a register file bank is arranged in a way that only a subset of the sub-banks within the bank is accessed. This allows for read or write requests to different register entries that access non-overlapping sub-banks in a given bank to be coalesced into a single access. To help reduce contention on the collector unit write port, our design also supports coalescing read requests from the same warp instruction across different banks given that the read requests access non-overlapping sub-banks (across the banks) to allow their read data to be packed into a single operand collector write. With these access coalescing capabilities, our design supports coalescing the following register file requests into a single physical access: two read requests from same or different warps accessing the same bank, two write requests into the same bank, a read and write requests accessing the same bank, two read requests from the same warp accessing different banks.

In this work, we made the following main contributions:

- We present a new register file organization that supports coalescing across different register entries within register file banks for read and write requests and combine them into a single bank access. It also supports coalescing read accesses across different banks that target the same operand collector by combining their read data into a single operand collector write.

- We provide a hardware-only solution to support register file access coalescing with low overhead and complexity. Our design requires minimal addition of micro-architectural states and small combinational logic that do not require extra pipelining.

• We support a coalescing-aware register file that place no restrictions on how physical registers are arranged among the register file banks. And we also do not require accessed registers to be packed in the same physical register entry for their access to be coalesced as we freely support coalescing across physical register entries within a bank.

#### 1.2 Exploiting Zero Data to Reduce Power Consumption in GPU

As mentioned earlier, the main register file and execution units are the largest dynamic power consumers in the GPU. In this work, we focus on reducing dynamic power for these two power-hungry components without impacting performance for GPGPU applications by proposing gating techniques that support the following power savings opportunities:

- Inactive threads: A warp represents the unit of execution in GPGPU and it consists of 32 threads executing in a lock-step in a single instruction multiple data (SIMD) execution pipeline. Divergent flow presented in general-purpose compute applications are causing warps to be under-utilized. In other words, some of the threads in a warp are inactive due to control divergence and need not be executed. We take advantage of this program attribute to reduce dynamic power of the main register file and execution units by gating off inactive threads during warp execution.

- In-lane zero data: Each thread in a warp executes in one 32-bit execution lane. Data operands or results that are specific to a given thread, which we refer to as an in-lane data, can have a zero value sometimes. The presence of zero value gives an opportunity to reduce threads dynamic power consumption by having the zero information for every architectural register saved in a separate state. This allows for unnecessary access to the power-hungry register file to read or write zero values to be avoided. It also allows for avoiding unnecessary execution of certain instructions that perform trivial operations when one or more of their source operands having a zero value.

- Small dynamic range data (cross-lane zero data): As the execution lane in

GPGPU is 32-bits wide, a thread in a given lane reads or writes 32-bit data values from the register file. The register file is typically comprised of  $32 \times 32$ -bit vector registers that supply operands to 32 threads within a warp. Per-thread data values used in compute applications varies in size and some values can be represented by only 8, 16, or 24 bits with the upper most-significant bits being zeros but these values are still being treated as 32-bit values when read and written into the register file. To take advantage of such small dynamic range of program values, in-lane data produced by adjacent execution lanes can be ordered (cross lanes) in a way to group the upper zero bytes together and potentially forming 32-bit zero values that can be captured in a separate zero state. This way the register file access for these 32-bit zero values can be gated to further reduce the register file dynamic power.

In this work, we propose a power reduction scheme that has low area and power overheads and has no performance impact. The proposed scheme takes advantage of the high percentage of zero data that exist in general purpose GPU applications to reduce dynamic power for the following power-hungry GPU components:

- **Register file:** avoid reading and writing zero data (in-lane or cross-lane) from the register file by capturing the zero information in a separate low area state.

- Execution unit: use the captured zero information to detect trivial operations which have one or more zero operands and avoid their execution by generating their trivial results directly.

### 1.3 Architecture Simulation and the Impact of Linux Thread Scheduler

As we have mentioned, the computer industry as well as architecture research have moved to multi-core systems with the end of Dennard scaling. Exploring new microarchitectures often requires simulation to do quantitative analyses of the performance and other metrics of these new designs, since implementing them in hardware is often prohibitively expensive.

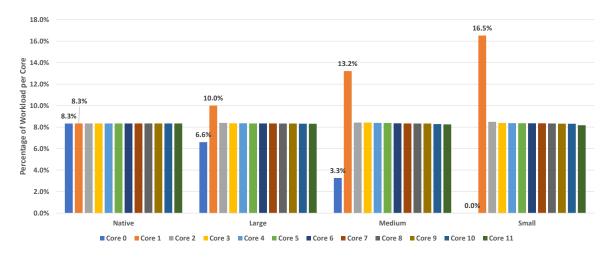

Figure 1.1: Actual run-time of 12-thread Canneal benchmark with different input sets on 12-core hardware machine.

Unfortunately, simulating an architecture incurs huge overheads in terms of simulated cycles per second versus the machine being simulated [8, 9, 10]. Typically, the slowdown of simulation versus real hardware is on the order of 10,000-100,000:1. As a result, architecture simulation experiments usually run scaled down versions of real applications where input data set and run iterations are chosen such that the runtime is reasonably short, while the performance characteristics of the full/native run of the benchmark are maintained. Fig. 1.1, which illustrates this point, shows the execution time of a 12-thread Canneal benchmark (from PARSEC suite [11]) with different input data sets when run on a real machine. In the figure, the *Small, Medium*, and *Large* represent the runtimes of input sets designed for architecture research, as compared to the *Native* input set which would be a typical production input for the application. As we see, the architecture research input sets are between 70-700x smaller than the native set. We note, that this same small input set for this benchmark takes approximately 6 hours from start to end, in full system simulation on the gem5 simulation toolkit [12].

Unlike the single threaded benchmarks of the previous era, wherein simulators could

simply emulate the operating system, architecture research on multi-threaded applications requires "full system" simulation. In full system simulation, the simulated system boots a real operating system then launches the multi-threaded application under test. Achieving scaling performance with core count in multi-threaded applications, according to Amdahl's Law [13], critically requires that the OS balance the workload across cores effectively. Architecture researchers rely on the fact that the OS is providing maximum utilization of the core resources and system software has no impact on their experimental results relative to a real system running the same program. Unfortunately, we have found that, for the short input sets typically used in architectural research, the behavior of the OS thread scheduler is often not as expected.

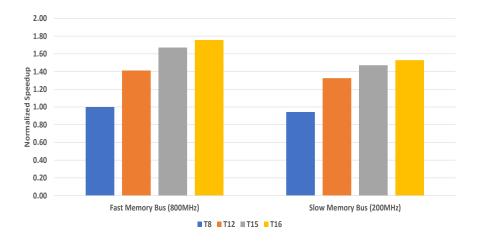

Figure 1.2: Performance speedup for Canneal benchmark using small input set, with 8, 12, 15, and 16 threads under memory speeds of 200MHz and 800MHz in full system simulation with original Linux scheduler. Results are normalized against an 8-thread 800MHz case.

Fig. 1.2 illustrates how the short runtimes used in architecture research, together with the thread-scheduling/balancing of typical OSes interact to produce inconsistent and incorrect results from simulation. The Figure shows normalized speedups of Canneal benchmark with the small input set and with different number of software threads under two memory-bus

speed settings. The benchmark was run under full system simulation of a (gem5 [12]) 16core system with Linux OS. Looking at the results we see several inconsistencies. First, we see that increasing thread-count with the 200MHz memory bus has a seemingly random effect on runtime, sometimes lowering it, sometimes raising it. Second, we see that the 8-thread, 200MHz bus counter-intuitively produces better performance than the 8-thread and 12-thread version with an 800MHz bus. As we will show the main source of these inconsistencies is due to the behavior of the current OS thread scheduler when it is used for short-lived simulation experiments.

This work focuses on the impact of system software on the behavior and correctness of simulation experiments performed in full system simulation with real OSes. We show that, for the short runtimes used in architecture research, the scheduler does not behave as expected to provide global load balance and fully utilize the simulated multi-core system. We characterize why and how this effect occurs. Finally, we propose a simple patch for the OS scheduler, for use in architecture research, to improve the consistency and correctness of multi-threaded applications when used for architecture research.

#### **1.4** Dissertation Statement

As thread parallel computing became essential for accelerating a variety of general purpose applications in use today, our goal is to make the thread parallel hardware more power and energy efficient, higher performance, and its simulation to be more accurate. To this end, our work covers the following topics: (1) We significantly improved overall performance and dynamic energy efficiency on the GPU by introducing a new register file organization that supports access coalescing of narrow-width registers frequently found in general purpose applications. (2) We improved dynamic power consumption of the main register file and execution units in the GPU by introducing power saving techniques that take advantage of programs attributes, inactive threads and zero data, frequently found in general purpose applications. (3) We also addressed inaccuracies in full system simulation environment with a real operating system (Linux kernel) that is primarily used in architecture research on multi-threaded applications.

#### **1.5** Dissertation Outline

Chapter 2 provides a background on modern GPU architectures and full system simulation environment. In Chapter 3, we present our new coalescing-aware register file organization to improve performance and energy efficiency in GPGPU. We start the chapter with a brief introduction in Section 3.1 followed by performance limitations in GPU register file that we aim to overcome in Section 3.2. Our motivations for register file coalescing is presented in Section 3.3. Section 3.4 presents illustrative examples of register access coalescing supported by our design. In Section 3.5, we present related work on GPU power optimization as well as prior work done on register file coalescing. The new coalescing-aware register file design is presented in Section 3.6 and is evaluated in Section 3.7. Then, we conclude this chapter in Section 3.8.

In Chapter 4, we propose power optimization techniques in GPU by exploiting zero data that exist in general-purpose applications. Section 4.1 gives a brief introduction followed by statistical measurements that show our motivations in Section 4.2. The design of the proposed techniques are presented in Section 4.3 and in Section 4.4 for register file and execution units, respectively. The power saving techniques are evaluated in Section 4.5. Section 4.6 covers related work on GPU power optimization and we then conclude this chapter in Section 4.7.

In Chapter 5, we present the negative impact of system software behavior on multithreaded applications running on full system architecture simulation when small input sets are used with a brief introduction given in Section 5.1. Section 5.2 demonstrates the behavior of Linux thread scheduler when running multi-threaded application with small input set and show the negative impact on the correctness of simulation results. We propose a solution to the unexpected behavior of the Linux scheduler in full system simulation in Section 5.3 and evaluate our solution in Section 5.4. We conclude this chapter in Section 5.5. Finally, an overall summary of our research work is given in Chapter 6.

#### 2. BACKGROUND

#### 2.1 Modern GPU Architecture Model

### 2.1.1 CUDA Overview

Compute Unified Device Architecture (CUDA) is the software platform that enables Nvidia GPUs to execute programs written in C, C++, or other languages [14]. A serial C++ program that performs a vector addition as in Fig. 2.1a can be accelerated to run on the GPU by creating a CUDA equivalent version of the program as in Fig. 2.1b. Each function defined on the device, as the *add* function, is called a program kernel. A CUDA program can have one or more kernels which are called and executed in parallel. The *add* kernel executes in parallel across a set of parallel threads. The program specifies the number of threads needed to execute the kernel and organizes the threads into thread blocks and grids of thread blocks. Each thread within a thread block executes an instance of the kernel and has its own thread identifier. CUDA thread hierarchy maps to a hardware hierarchy of multi-processors in the GPU.

The CUDA program for the vector add example requires 1024 threads where each thread performs the addition operation on a single instance (element) of the input vectors. Threads are organized into a grid of two thread blocks with each block has 512 of the threads as shown in Fig. 2.2. A grid is an array of thread blocks that perform the same kernel and execute in parallel on different GPU Streaming Multiprocessors (SMs) or cores. A thread block, of 512 threads in this example, is assigned into an SM core and has concurrently executing threads that execute in groups of 32 threads called warps (also known as wavefronts). A warp of 32 threads is the the amount of work an SM core can initiate in a cycle. The warp scheduler within each SM picks an active warp every cycle and threads within the warp

```

//C++ serial version

void add (int N, int* A, int* B, int* C) {

for (int i = 0; i < N; i++) {

C[i] = A[i] + B[i];

}

}

//invoke add function

int N = 1024;

add(N, A, B, C);

```

(a)

(b)

Figure 2.1: C++ code example for vector addition (a) Serial code that typically runs on CPU. (b) CUDA thread-parallel version of the code that runs on GPU.

Single Instruction Multiple Data (SIMD) execution pipeline.

## 2.1.2 GPU Chip Layout

Fig. 2.3 shows a modern GPU chip of the Nvidia Fermi family [1]. The GPU consists of 16 Streaming Multiprocessor units (SMs) with an on-chip shared level-two (L2) cache.

Figure 2.2: CUDA hierarchy of threads that maps to a hierarchy of processing elements on the GPU.

The SMs access the L2 cache and the external Dynamic Random Access Memory (DRAM) using an interconnection network which is usually referred to as Network On Chip (NOC). Each SM has a single execution core that consists of level-one (L1) instruction and data caches, warp schedulers, main register file, multiple execution units, and a shared memory. Threads within the thread block executing on the SM core communicate through the local shared memory and each thread in the thread block has its own private register file entries to save its architectural state (context). The register file in each SM has a total size of 128KB and is organized into multiple banks. The SM execution units are of three types: (1) Streaming Processing Units (SPUs) to execute integer and floating-point arithmetic and logical instructions. (2) Special Functional Units (SFUs) for executing special functions like sin and cosine. (3) Load and Store units (LDSTs) to perform memory accesses. The SM has

Figure 2.3: Modern GPU chip layout with 16 Streaming Multiprocessors (SMs), each of which has its own register file, instruction and data caches, and execution units. Reprinted from [1].

a configurable partitioning of L1 data cache and shared memory space with a total size of 64KB which can be configured as 48KB shared memory and 16KB cache or as 16KB shared memory and 48KB cache.

A program kernel, as the vector add example mentioned earlier and shown in Fig. 2.1, is divided up into thread blocks (also known as Concurrent Thread Arrays (CTAs)) and each block gets allocated into one of the SMs to be worked on. Threads within the thread block are divide up into groups of 32-thread warps (or wavefronts) that get issued by the warp scheduler once every cycle. Each issued warp requires an Operand Collector Unit (OCU) to read all needed source operands from the register file before it gets dispatched into the execution pipeline. Threads in a warp execute in a SIMD fashion in a lock-step where each thread executes the same instruction on a 32-bit slice of the operands data. The 32-bit wide execution pipeline for a single thread is referred to as an execution unit or (lane).

#### 2.1.3 Warp Scheduler

Figure 2.4: Dual-warp scheduler used in Fermi GPU. Reprinted from [1].

The GPU relies on the warp scheduler to maintain high utilization of the compute resources available. Warps within a thread block, as shown in Fig. 2.2, are organized by the warp scheduler, as in the two-level scheduler [15], into two groups: (1) pending warps that are waiting on long-latency memory access and (2) warps that are active. The active warps are also organized into two groups:(1) warps that have dependency on older executing warps that is either a Read-After-Write (RAW) or a Write-After-Write (WAW) dependency and (2) warps that have no data dependencies and are *ready* to be issued. The warp scheduler selects one of the *ready* warps to issue every cycle using an arbitration policy, such as Round-robin (RR) or Least Recently Used (LRU), to provide fair arbitration among available warps. Fig. 2.4 shows the dual-warp scheduler used in the Fermi GPU. An issued warp is assigned an available operand collector unit to read its needed source register operands from the register file before it gets dispatched into the execution units pipeline.

### 2.1.4 Register File

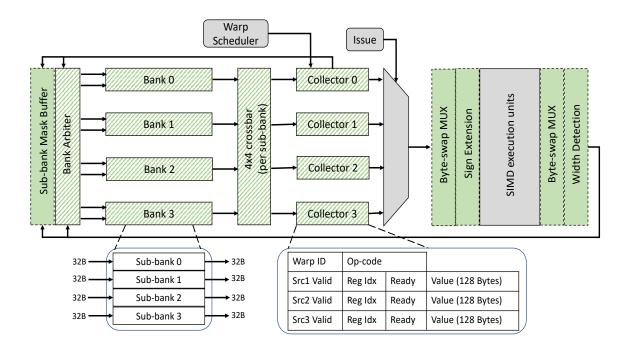

Figure 2.5: GPU main register file and execution pipeline.

Fig. 2.5 shows the register file organization similar to the Fermi family of Nvidia GPUs [1]. To avoid the area cost of multi-ported design, GPUs adopt for a multi-banked register file organization built with single read-write port SRAM banks to provide large access bandwidth. Register file banks operate in parallel to serve read and write requests where each of these requests can target only one bank. Multiple requests that target the same bank experience a *bank conflict* and their access is serialized due to access port limitation.

| ← RF bank (128B)                                                 |               |                           |          |          |  |          |                  |          |          | •        |          |          |          |

|------------------------------------------------------------------|---------------|---------------------------|----------|----------|--|----------|------------------|----------|----------|----------|----------|----------|----------|

| Sub-bank 3 (32B)                                                 | Sub-bank 2 (3 | (2 (32B) Sub-bank 1 (32B) |          |          |  |          | Sub-bank 0 (32B) |          |          |          |          |          |          |

| [T31:T24][B3:B0] [T23:T16][B3:B0] [T15:T8][B3:B0] [T7:T0][B3:B0] |               |                           |          |          |  |          |                  |          |          |          |          |          |          |

|                                                                  |               |                           |          |          |  |          |                  |          |          |          |          |          |          |

|                                                                  | Т7<br>ВЗ      | T7<br>B2                  | T7<br>B1 | Т7<br>В0 |  | T1<br>B3 | T1<br>B2         | T1<br>B1 | T1<br>B0 | T0<br>B3 | Т0<br>В2 | T0<br>B1 | Т0<br>В0 |

Figure 2.6: A 128B warp register entry in one register file bank occupying four 32B sub-bank entries that have the same index. Each 32B sub-bank entry holds data for 8 threads within the warp.

| 1 | Bank 0 | <br>Bank 1 | <br>Bank 2 | <br>Bank 3 |   |

|---|--------|------------|------------|------------|---|

|   | w0:r0  | w0:r1      | w0:r2      | w0:r3      |   |

|   | w1:r3  | w1:r0      | w1:r1      | w1:r2      |   |

|   | w2:r2  | w2:r3      | w2:r0      | w2:r1      |   |

|   | w3:r1  | w3:r2      | w3:r3      | w3:r0      |   |

|   |        |            |            |            |   |

| 1 | ~      | <br>       | <br>       | <br>       | 1 |

Figure 2.7: Register-to-bank mapping (layout) with warp registers interleaved across register file banks.

A register file bank is built using multiple narrower sub-banks each of which holds a 32B slice of all register entries in the bank. A read or write request to a given bank accesses all its sub-banks with the same index at the same time. Every warp in the GPU has a dedicated set of 128B registers that are indexed using the warp number. As shown in Fig. 2.6, the 32 thread-registers within a warp form a single bank entry which is split across the sub-banks and are accessed with the same warp register index. Data in the warp register entry is represented in a byte-interleaved format where the four bytes (byte 0, 1, 2, and 3) of thread 0 is presented in the least significant position, followed by the four bytes of thread 1, and so

There is a one-to-one mapping between logical registers and physical registers. Warp registers are mapped to the register file banks based on the layout chosen with one possible layout is to map all registers for a given warp into the same bank. Another layout, used to reduce bank conflicts between warps, has registers belonging to the same warp interleaved across the banks as shown in Fig. 2.7.

Operand collector units are used to buffer warps operands data as they are read from the register file, over multiple cycles, with one collector unit used per warp instruction. The number of register operands to read for a given warp varies by instruction type with a maximum of three operands needed for a fused-multiply-add (FMA) instruction. The number of write ports on an operand collector is limited to only one 128B wide port that can accept read data from one of the register file banks at a time. Multiple bank reads that target the same operand collector experience a *port conflict* and are serialized due to the single-port limitation on the collector unit. Routing read data from the banks into the operand collector units is done using a crossbar interconnection network.

#### 2.1.5 Execution Units

Each SM has three different types of SIMD execution pipelines as shown in Fig. 2.8. An arithmetic/logic Streaming Processing Unit pipeline (SPU) is used to execute integers and floating-point instructions, a Special Functions Unit (SFU) pipeline is used to execute special functions such as sin/cosine and square root operations, and a Load/Store Unit (LDST) pipeline used to perform memory loads and stores.

A 32-thread warp instruction is issued into an execution pipeline when all its operands are marked ready in the operand collector and is also found the oldest among other ready warps. Each thread within a warp requires a single 32-bit lane (pipeline unit) to execute the warp instruction. 32-thread warp instructions are dispatched every cycle into the SPUs, every 8 cycles into the SFUs, and every 2 cycles into the LDST units. With a dual-warp scheduler, two warp instructions can be dispatched into the the SPUs at the same time were

on.

|           | SPU | SPU | SPU | SPU | CELL | LDST | LDST |

|-----------|-----|-----|-----|-----|------|------|------|

|           | SPU | SPU | SPU | SPU | SFU  | LDST | LDST |

| src1 src2 | SPU | SPU | SPU | SPU | SFU  | LDST | LDST |

| ALU       | SPU | SPU | SPU | SPU | 550  | LDST | LDST |

| rsit      | SPU | SPU | SPU | SPU | SFU  | LDST | LDST |

|           | SPU | SPU | SPU | SPU | 550  | LDST | LDST |

|           | SPU | SPU | SPU | SPU | SFU  | LDST | LDST |

|           | SPU | SPU | SPU | SPU |      | LDST | LDST |

Figure 2.8: Execution units in a GPU Streaming Multiprocessor (SM) core with 32 Streaming Processing Units (SPUs), 4 Special Functional Units (SFUs), and 16 memory Load/Store Units (LDSTs). Reprinted from [1].

each warp uses half the number of the SPUs and dispatched over two cycles. Once a warp is dispatched, the operand collector assigned to the warp is freed and can be immediately used by one of the younger warps. The three pipelines can operate on different warp instructions in parallel and each may write up to one result back into the register file.

## 2.2 Full System Simulation

As previously discussed, architecture simulators are used by the research community to validate their new ideas and proposed solutions. Some simulators, such as gem5 [12], can run the full Linux kernel<sup>1</sup> within the simulation environment in *full system* simulation experiments. Fig. 2.9 shows a full system simulation environment with 16 single-threaded cores managed by an operating system kernel running a thread scheduler. Just as in a real

$<sup>^1\</sup>mathrm{We}$  focus on Linux here, as it is the OS typically used in architecture research.

Figure 2.9: Full system simulation environment for a Core Multi-Processor (CMP) chip with 16 cores managed by a real Operating System (OS) running a thread scheduler. The full simulation system runs multi-threaded user applications similar to a real multi-core system with an OS.

system, the kernel is booted on one of the cores in the simulated system before user-level code can be executed. Once the kernel is up and running on the simulator, multi-threaded application benchmarks (e.g. the PARSEC benchmarks [11]) can be run on the system. These benchmarks use the pthread run-time libraries to fork software threads and manage communication/synchronization between those threads. Ultimately the pthreads library is a wrapper around OS calls to complete these tasks. Similarly, the OS handles the scheduling of threads; it is expected to be performed in a way that provides high performance and fair execution among running threads. Further, thread-to-core mapping is another important

job of the kernel and is expected to be performed in a way to fully utilize the multi-core system and achieve good global load balance.

Linux scheduler has evolved over time to support different platforms such as desktops and servers. Early versions of the Linux scheduler only supported simple, uniprocessor systems with no multi-threading or multi-processing. Starting with version 1.2, the scheduler used a circular buffer, enforcing a round-robin policy to provide fairness among software threads regardless of their type or class. Later in version 2.2, scheduling classes were added to provide different polices for real-time and none-real-time tasks. This version also had the first support for symmetric multi-processing (SMP). With the introduction of SMP, the scheduler's job became more complicated as it needs to provide fair scheduling among running tasks and also provides global load balancing over the available cores in the multi-core system. The scheduler has been an active research topic and been evolving to improve fairness and reduce run-time complexity. The current scheduler in use today is the "completely fair scheduler" (CFS) [16] which followed O(1) scheduler [17] in version 2.6.23. This scheduler's goal is provide better fairness among running threads and enhance applications performance compared to previous schedulers.

While it is important to achieve fairness among threads running on a given core, achieving global fairness is highly important for multi-thread applications running on a multi-core system. CFS made some improvements for global load balancing in version 2.6.24 among them the introduction of scheduling domains [18, 19]. Each scheduling domain spans a number of cores in the system and domains are built in a hierarchical fashion. Cores within a scheduling domain are organized into groups where the union of the groups is the span of the domain and the intersection between any two groups is an empty set. Load balancing within a scheduling domain happens between groups. Each group is considered an entity with a load equal to the sum of loads of all cores in the group. Tasks are moved from one group to another when imbalance condition is detected. In SMP mode, all cores in the multi-core system belong to one parent scheduling domain where each group within the domain

has only one core.

A multi-thread application running on a multi-core system relies on the global load balance provided by the scheduler in order to achieve scaling performance with core count. When a new software thread is forked, the scheduler performs a minimum search among the available cores in the system to find a candidate core to run the thread. The scheduler relies on current core status information to select the first idle or otherwise least busy core found during the search to run the thread. Critically, this search starts from the same core ID each time, taking into no account whether that core has already had a given application's thread mapped to it in the recent past, only whether or not that core is currently idle.

Lacking an application-level view can lead the scheduler to map more threads to some cores over others in the event that those threads are currently idling, causing load imbalance in the multi-core system. To address the adapting load per core, the OS periodically (approximately once every 30 milliseconds) performs a load balancing operation on all cores to incrementally reduce the degree of load imbalance and enhance applications performance. In this operation, a single core searches for the busiest other core in the system, and performs a thread migration when a high load imbalance is detected between the two cores. The heavy-weight system-wide search is initiated by one core at a time in a sequential order to reduce contention and avoid ordering complexity among cores performing the rebalance. Thus, one full iteration of the core balancing requires  $30 \times N$  milliseconds, where N is the number of cores in the system. Over the long haul this system will generally find an optimal thread-core mapping balance, however it can often take many iterations of this search to do so. For example ten full iterations of core rebalancing on a 16-core system could take as long as 5 seconds to find an optimal balance of threads, much longer than the runtime of the benchmarks used in architecture research (see Fig. 1.1).

## 3. REGISTER FILE ACCESS COALESCING IN GPU

## 3.1 Introduction

As we mentioned in Chapter 1, a multi-banked register file structure with limited access ports has been used in GPUs to mainly reduce its area cost. With limited number of ports, register file accesses are serialized when accessing individual banks which impacts access latency and overall IPC performance for the GPUs. In this chapter, we focus on improving IPC performance and energy utilization for the GPU by proposing a new register file organization that support register file access coalescing. Access coalescing provides combining different narrow-width read and write requests that contend on available bank ports to form a single physical request which in turn reduce the overall number of bank accesses and register file pressure, improve bandwidth utilization, reduce access latency which improves overall IPC performance and energy efficiency in GPU.

#### 3.2 Performance Impact of Limited Access Ports

As we mentioned in Section 2.1, the warp scheduler in each SM core maintains a pool of ready warp instructions and selects one of these warp instructions to issue in a cycle. The issued warp instruction is assigned an available operand collector unit (OCU) to read its source operands before it starts executing. Each operand collector may fetch up to three source register operands from the register file by sending read requests to the banks where the registers are located. Write requests targeting the banks can be generated from an arithmetic instruction or a memory load instruction when their results are ready. As illustrated in Fig. 3.2, with limited number of access ports, read or write requests can experience one of the following types of *port conflicts* and their access is serialized: