| Title       | Vectorizing and Parallelizing Compiler Techniques for Block-Structured Languages( Dissertation_全文) |

|-------------|----------------------------------------------------------------------------------------------------|

| Author(s)   | Uehara, Tetsutaro                                                                                  |

| Citation    | Kyoto University (京都大学)                                                                            |

| Issue Date  | 1996-03-23                                                                                         |

| URL         | http://dx.doi.org/10.11501/3110540                                                                 |

| Right       |                                                                                                    |

| Туре        | Thesis or Dissertation                                                                             |

| Textversion | author                                                                                             |

## Vectorizing and Parallelizing Compiler Techniques for Block-Structured Languages

**UEHARA** Tetsutaro

November 1995

### Abstract

With the recent progress in technology of semi-conductor devices and architectures, the performance of vector and parallel supercomputers have been remarkably advanced. Today they have become a fundamental tool of science which is widely used in various fields of science and engineering. Supercomputers manufacturers are providing automatic vectorizing and parallelizing compilers (or *supercompilers*) which generate suitable object codes from programs written in sequential languages. Since most of these compilers are for FORTRAN77 which has been commonly used for numerical applications, supercompilers for languages other than FORTRAN are indispensable to utilize supercomputers for non-numerical applications. Moreover, various features which have been considered to be specific to block-structured languages, such as pointers and recursive calls, are introduced in the new standard specification of FORTRAN called Fortran 90. This thesis discusses various vectorizing and parallelizing compiler techniques which are effective not only for block-structured languages but also for Fortran90.

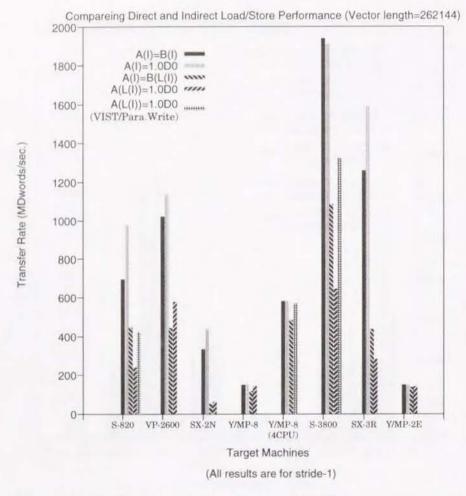

In Chapter 2, the performance of load/store instructions on each VP/PVP supercomputer is evaluated. In particular, the performance of vector indirect load/store instructions is precisely discussed since the performance of these operations are important not only for numerical applications but for non-numerical applications which treat pointers. We have developed a benchmarking program to evaluate this performance and show the obtained results.

In Chapter 3, a new method to vectorize and parallelize recursive procedures is proposed. Since recursive procedures are often seen in programs written in block-structured languages, this control should be also regarded as the targets for automatic vectorization and parallelization. We propose the breadth-first method and show that some recursive procedures will be greatly accelerated by this method. In particular, this method is effective for the recursive procedures which are the implementations of divide-and-conquer algorithms because this method utilizes the parallelism between recursive invocations of the procedures. We also discuss about the analysis to determine whether the target procedure can be vectorized/parallelized by this method or not. Since there is a difficulty for the determination when the procedure

refers global array variables in general, we propose a method which has a restriction but still effective in practical programs.

In Chapter 4, the overview of our automatic vectorizing and parallelizing compiler V-Pascal version 3 is presented. On the compiler, various analyzing, vectorizing and parallelizing techniques have been developed even for Algol-like features, such as alias analysis of pointers, vectorization/parallelization of while/repeat-until loops and recursive procedures. These techniques may also be useful for the full-fledged vectorizing/parallelizing compilers for the languages Fortran 90 and C.

## Contents

| 1 | Intr | oduction                                             | 13 |

|---|------|------------------------------------------------------|----|

|   | 1.1  | Backgrounds                                          | 13 |

|   |      | 1.1.1 Supercomputers                                 |    |

|   |      |                                                      | 14 |

|   |      |                                                      | 16 |

|   |      | 1.1.4 Outline of this thesis                         | 17 |

| 2 | Ben  | chmarking Vector Indirect Access                     | 19 |

|   | 2.1  |                                                      | 19 |

|   | 2.2  |                                                      | 20 |

|   |      |                                                      | 20 |

|   |      |                                                      | 22 |

|   |      | 2.2.3 Performance Factors and their Compound Effects | 23 |

|   | 2.3  | The Benchmarking Program                             | 24 |

|   |      |                                                      | 24 |

|   |      | 2.3.2 Benchmarking Program                           | 25 |

|   | 2.4  |                                                      | 28 |

|   |      |                                                      | 28 |

|   |      | 2.4.2 Target Machines and the Results                | 31 |

|   | 2.5  | Conclusions                                          | 38 |

| 3 | The  | Breadth-first method                                 | 15 |

|   | 3.1  | Introduction                                         | 45 |

|   | 3.2  | Preliminaries                                        | 46 |

|   |      |                                                      | 46 |

|   |      | 3.2.2 Facilities of Vector Supercomputers            | 48 |

|   | 3.3  |                                                      | 51 |

4

|      | 3.3.1   | The Depth-first Vectorization 51                      |

|------|---------|-------------------------------------------------------|

|      | 3.3.2   | Problems                                              |

| 3.4  | Basic   | Idea                                                  |

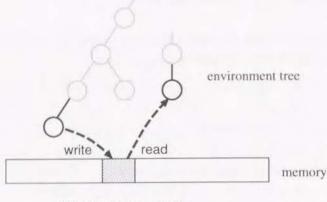

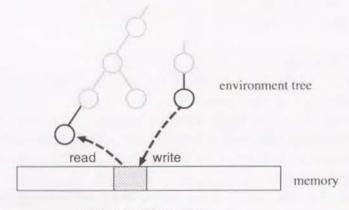

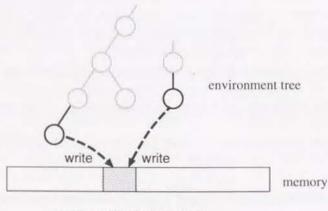

| 3.5  | Depen   | dence between Environments 61                         |

| 3.6  |         | h-first vectorization                                 |

| 3.7  | Impler  | nentation Details                                     |

|      |         | Code generation                                       |

|      | 3.7.2   | Storage Overflow 80                                   |

| 3.8  | Enviro  | onment Dependence Analysis 80                         |

|      | 3.8.1   | Without writing external variables 80                 |

|      | 3.8.2   | External simple variables and pointer variables 83    |

|      | 3.8.3   | External array variables                              |

|      | 3.8.4   | Additional Remarks 89                                 |

| 3.9  | The B   | readth-first Parallelization                          |

|      |         | mance Evaluation                                      |

|      |         | Opportunities of vectorization and parallelization 92 |

|      |         | Execution speed                                       |

| 3.11 |         | d Works                                               |

| 3.12 |         | mental Results                                        |

|      |         | ısion                                                 |

|      |         |                                                       |

| V-P  | 'ascal  |                                                       |

| 4.1  |         | uction                                                |

| 4.2  | Overv   | ew                                                    |

| 4.3  | Organ   | ization of the Compiler                               |

| 4.4  | Facilit | ies of Analysis                                       |

|      | 4.4.1   | Alias Analysis                                        |

|      | 4.4.2   | Control/Data-flow Analysis                            |

|      | 4.4.3   | Value-Range Estimation of Integer Variables 109       |

|      | 4.4.4   | Dependence Analysis of Array Subscripts 109           |

| 4.5  | Facilit | ies of Vectorization/Parallelization 111              |

|      | 4.5.1   | Vectorization/Parallelization of Multiply-nested      |

|      |         | Loops                                                 |

|      | 4.5.2   | Vectorization of While Loops                          |

|      | 4.5.3   | Vectorization and Parallelization of Recursive Pro-   |

|      |         | cedures                                               |

| 4.6  | Conclu  | ision                                                 |

|      |         |                                                       |

CONTENTS

| CONTENTS                           | Э   |

|------------------------------------|-----|

| 5 Conclusion                       | 115 |

| Bibliography                       | 116 |

| Acknowledgements                   | 123 |

| List of Publications by the Author | 125 |

6 CONTENTS

# List of Figures

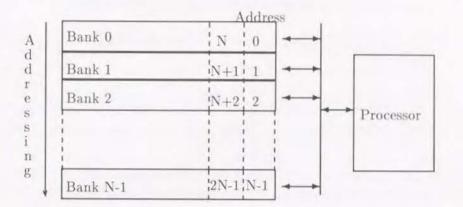

| 2.1  | Bank Interleaving                                             | 23      |

|------|---------------------------------------------------------------|---------|

| 2.2  | A sample of $S_{half}$ and $S_{worst}$                        | 30      |

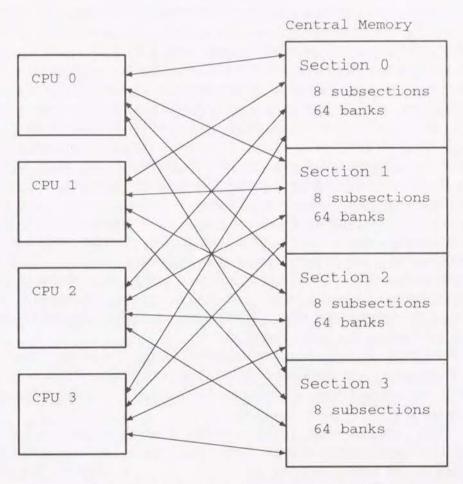

| 2.3  | Y-MP Memory Organization[7]                                   | 35      |

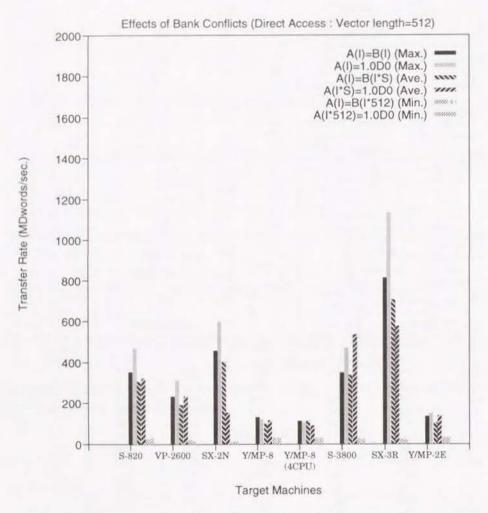

| 2.4  | Effects of bank conflicts using direct access instructions.   | 42      |

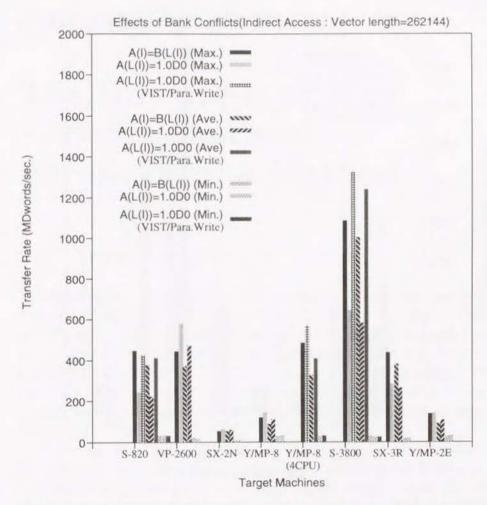

| 2.5  | Effects of bank conflicts using indirect access instructions. | 43      |

| 2.6  | Maximum throughput using direct/indirect access in-           |         |

|      | structions                                                    | 44      |

| 3.1  | Conversion from an indirectly recursive procedure to di-      |         |

|      | rectly recursive procedure                                    | 47      |

| 3.2  | An indirectly recursive procedure which is impossible to      |         |

|      | convert into directly recursive procedure by inline expan-    | * 4 450 |

|      | sion                                                          | 47      |

| 3.3  | Examples of recursive procedures                              | 49      |

| 3.4  | A procedure to get N-th factorial                             | 52      |

| 3.5  | Converted form of the procedure fact                          | 52      |

| 3.6  | Non-recursive form of the procedure fact                      | 53      |

| 3.7  | Vectorized form of the procedure fact                         | 54      |

| 3.8  | Normalized type-1 procedure                                   | 56      |

| 3.9  | Normalization of type-1 procedures                            | 56      |

| 3.10 | After conversion from a type-1 recursive procedure to a       |         |

|      | non-recursive procedure                                       | 57      |

| 3.11 | The algorithm to convert a type-1 procedure to a non-         |         |

|      | recursive procedure (cont.)                                   | 58      |

| 3.12 | The algorithm to convert a type-1 procedure to a non-         |         |

|      | recursive procedure (cont'd)                                  | 59      |

| 3.13 | A normalized type-2 procedure without loops                   | 60      |

| 3.14 | A target procedure for the breadth-first vectorization        | 60      |

8

### LIST OF FIGURES

| 3.15  | A sample of the environment tree                             | 62  |

|-------|--------------------------------------------------------------|-----|

|       | Dependence between environments                              | 64  |

| 3.17  | Direct and indirect dependence between environments          |     |

|       | environments                                                 | 65  |

| 3.18  | The behavior of a type-2 procedure vectorized by the         |     |

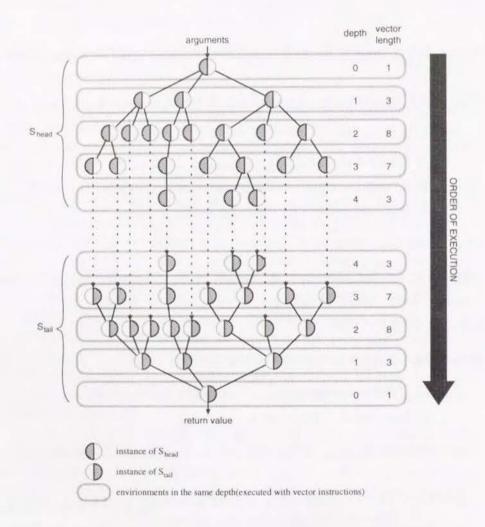

|       | breadth-first vectorization method                           | 67  |

| 3.19  | Breadth-first vector execution                               | 68  |

| 3.20  | After the breadth-first vectorization                        | 69  |

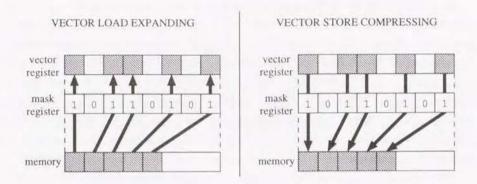

| 3.21  | Vector expand/compress instructions                          | 71  |

| 3.22  | A procedure to get the sum of a binary-tree data             | 71  |

| 3.23  | Vectorized sample procedure of type-2 procedure. (cont.)     | 73  |

| 3.24  | Vectorized sample procedure of type-2 procedure. (cont'd)    | 74  |

| 3.25  | The algorithm to convert a type-2 procedure to apply         |     |

|       | the breadth-first vectorization. (cont.)                     | 75  |

| 3.26  | The algorithm to convert a type-2 procedure to apply         |     |

|       | the breadth-first vectorization. (cont'd)                    | 76  |

| 3.27  | Example of the breadth-first vectorization of a normal-      |     |

|       | ized type-3 procedure. (cont.)                               | 77  |

| 3.28  | Example of the breadth-first vectorization of a normal-      |     |

|       | ized type-3 procedure. (cont'd)                              | 78  |

| 3.29  | A normalized type-3 procedure for the breadth-first vec-     |     |

|       | torization                                                   | 79  |

| 3.30  | A measure for storage overflow                               | 81  |

| 3.31  | Shape of an environment tree when executed with a mea-       |     |

|       | sure for storage overflow                                    | 82  |

| 3.32  | Recursive procedures without writing external variables.     | 84  |

| 3.33  | Example for divide-and-conquer detection. (cont.)            | 87  |

| 3.34  | Example for divide-and-conquer detection. (cont'd)           | 88  |

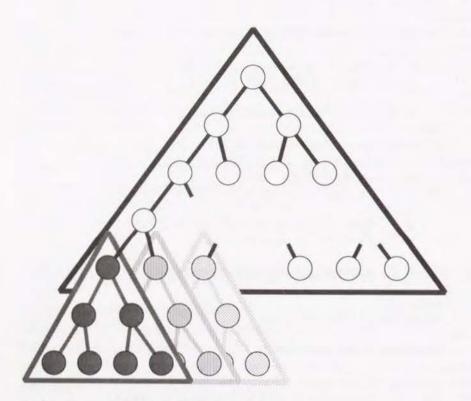

| 3.35  | A technique to execute vector load expanding and vector      |     |

|       | store compression in parallel                                | 91  |

| 3.36  | N-queen for the breadth-first vectorization $\dots$ .        | 91  |

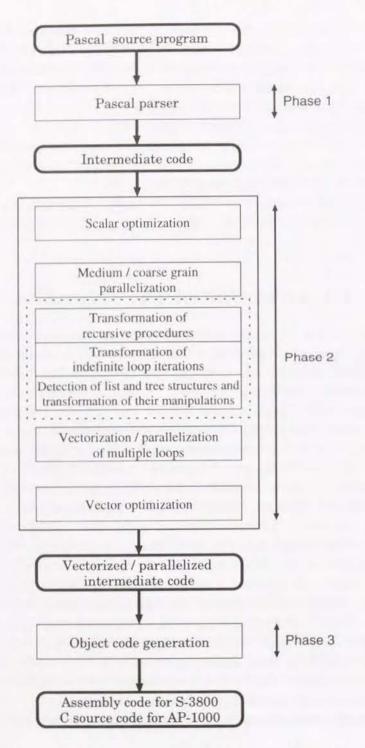

| 4.1   | The organization of V-Pascal Version 3                       | 104 |

| 4.2   | An example of alias pairs caused by call-by-reference pa-    |     |

| 41.64 | rameters                                                     | 107 |

| 4.3   | An example of alias pairs caused by pointer references       |     |

| 4.4   | An example of the detection of aliases of pointer variables  |     |

| T. I  | and cample of the detection of allases of pointer variables. | LUO |

| LIST C            | OF FIGURES 9           |

|-------------------|------------------------|

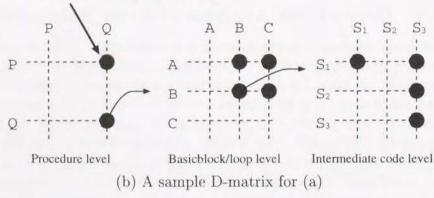

| 4.5<br>4.6<br>4.7 | An example of D-Matrix |

|                   |                        |

|                   |                        |

|                   |                        |

LIST OF FIGURES

## List of Tables

| 1.1<br>1.2 | Today's VP/PVP supercomputers                                                                |    |

|------------|----------------------------------------------------------------------------------------------|----|

| 2.1<br>2.2 | The performance and hardware facilities of each machine Experimental results on each machine | 40 |

| 3.1        | Examples of the vector-macro instructions                                                    | 50 |

| 3.2        | Benchmarking results of VITRD instruction on S-820/80                                        | 95 |

| 3.3        | Execution time of the procedure SUM                                                          | 95 |

| 3.4        | Execution time of the procedure in Figure 3.23 (Fortran simulation)                          | 97 |

| 3.5        |                                                                                              |    |

|            | version 2)                                                                                   | 99 |

## Chapter 1

### Introduction

### 1.1 Backgrounds

### 1.1.1 Supercomputers

With the recent progress in technology of semi-conductor devices and architectures, the peak performance of *supercomputers* have reached to tens or several hundreds GFLOPS (Giga Floating-point Operations Per Second). Their high performance enabled us to perform many billions of operations which are needed to solve various problems in fields of science and engineering, such as biology, energy research, high energy physics, astrophysics, aerospace engineering, seismology, petroleum exploration, image processing, pattern matching, VLSI design, tomography, scientific visualization and so on. Now supercomputers have become a fundamental tool of science.[54]

Architectures of today's supercomputers can be divided into three categories: vector processor (VP), parallel vector processors (PVP) and massively parallel processors (MPP).

The main feature of VP machines is that they each have *vector-processing units* aside of the ordinal scalar processor. These units can perform vector operations which perform the same operations for each element of vectors (i.e. 1-dimensional arrays). Since these operations are performed by pipelined arithmetic units with quite high speed, the peak performance of a VP machine reaches up to several GFLOPS. A typical PVP machine is configured as a symmetric multi-processor

system of several VPs which share the same main memory.<sup>1</sup> Today's high-end PVPs, such as Cray T90 and NEC SX-4, can be configured with up to 32 processors and their total peak performance is more than 50 GFLOPS. These machines have been widely used for computational science and engineering. In other words, these are conventional supercomputers. Table 1.1 shows a list of today's conventional supercomputers.

But these VP/PVP machines are generally quite expensive. The main reasons are that they needs advanced technologies to achieve quite short clock-cycle of their devices, and that they need contrived memory units to obtain high load-store bandwidth to supply enough data to the high-speed arithmetic units. To achieve the comparable peak performance with reduced costs, MPP is proposed as a loosely-coupled multi-processor of RISC microprocessors. Recently these processors have remarkably progressed and achieved the performance of tens or hundreds MFLOPS (Mega Floating-point Operations Per Second). In a typical MPP machine, hundreds processors are coupled with a high-speed inter-connection network, therefore they can achieve the peak performance of several GFLOPS. These machines are still hard to utilize for general purpose, but considered to be effective for some specific problems which can be highly parallelized and need less data-transfer between the parallelized program sections.

### 1.1.2 Supercompilers for Supercomputers

The high performance of VP/PVP machines derives from their multiple vector pipelines with a very short pipeline period. These pipelines manage the vector operations which are 10 or 100 times faster than that by scalar processors. Since vector operations belong to parallel operations which are not familiar for ordinal users, it is very important to provide peculiar compilers which generate vector instructions automatically from programs written in conventional sequential programming languages. Now most of the manufacturers provide automatic vectorizing compilers for FORTRAN, which is commonly used in scientific

Table 1.1: Today's VP/PVP supercomputers

| Vendor           | Model    | Maximum number<br>of processors | Total peak<br>performance<br>(GFLOPS) |

|------------------|----------|---------------------------------|---------------------------------------|

| Cray Research[8] | T90      | 32                              | >60                                   |

| Cray Research[8] | C90      | 16                              | 16                                    |

| Convex [5]       | C4/XA    | 4                               | 6.4                                   |

| Hitachi [25]     | S-3800   | 4                               | 32                                    |

| Fujitsu          | VP-2600E | 1                               | 5.5                                   |

| NEC [27]         | SX-4     | 32 <sup>‡</sup>                 | 64                                    |

† With single precision.

‡ For single-node (i.e. shared-memory) system.

Table 1.2: Today's MPP supercomputers

| Vendor                | Model       | Processor<br>element | Max, num.<br>of nodes | Total peak<br>performance<br>(GFLOPS) |

|-----------------------|-------------|----------------------|-----------------------|---------------------------------------|

| Cray Research [8]     | T3D         | DEC 21064(150MHz)    | 2048                  | 300                                   |

| Thinking Machine [41] | CM-5E       | SuperSparc(40MHz)    | 1024                  | 80                                    |

| Convex [5]            | SPP-1200/XA | HP PA-7200           | 128                   | 30.7                                  |

| Intel [17]            | Paragon     | i860XP(50MHz)        | n/a <sup>†</sup>      | 0.075×nodes                           |

| IBM [16]              | SP-2        | POWER2 <sup>‡</sup>  | n/a*                  | 0.267×nodes                           |

| NEC                   | Cenju-3     | R4400SC              | 256                   | 12.8                                  |

| Ncube [35]            | Ncube3      | Original             | 10240                 | >1000                                 |

| Hitachi               | SR2001      | Original             | 128                   | 23                                    |

<sup>†</sup> The largest one installed at Sandia National Lab.(US) has 1840 nodes

<sup>&</sup>lt;sup>1</sup>Some newly announced vector-parallel machines (such as Fujitsu VPP series and NEC SX-4 multi-node models) are configured with distributed main memory, but we don't include them in our definition of PVP.

<sup>‡</sup> PowerPC based nodes are also available.

<sup>\*</sup> Announced as up to 128, but 512-nodes systems are also available

and technological fields. Today's vectorizing compilers have high ability to find out vectorizable loops within programs and we can obtain quite high ratio of speedup. The techniques for automatic vectorization can be easily extended and applied to parallelization of loops and PVP machines can execute these loops effectively, therefore automatic vectorizing and parallelizing FORTRAN compiles for PVP machines are also provided. These compilers are called *supercompilers* and they have much contributed to utilize VP/PVP supercomputers in various fields of science. Thus VP/PVP supercomputers have been successful for scientific numerical computations.

On the other hand, fully-automatic parallelizing compilers for MPP machines are still hard to realize. While the techniques to recognize parallelizable parts of the target program for VP/PVP machines are also applicable for compilers for MPP, it is hard the compilers to decide the optimal distribution of data among processing nodes to reduce the amount of data-transfer. Therefore the current compilers provided by manufacturers are for parallel languages or conventional sequential languages with extension to be directed the data-distribution by users.

#### 1.1.3 The Goal of This Research

For any type of supercomputer architectures, it is fairly important to provide supercompilers which assist users to enjoy the high performance of supercomputers. Most of current supercompilers provided by manufactures are for FORTRAN77 which is popular for numerical computation. However, FORTRAN77 is not effective for general purposes because it has rather poor control structures and data types. Therefore, it is indispensable to develop automatic vectorizing compilers for other programming languages to utilize supercomputers more efficiently. This is the motivation of this research. To extend the horizon of vector supercomputer usage, we were interested in developing automatic vectorizing/parallelizing compilers for block-structured languages, i.e. descendants of Algol60, which is equipped with more versatile control/data structures than FORTRAN77.

Toward the goal, we choose Pascal as the target language of our compiler. Pascal is a typical block-structured language which is widely spread for general purpose. Pascal has been used not only for educational purposes in classrooms but also for real-world problems, for example, the early TeXprocessor by D.E. Knuth, the vectorizing Fortran compiler construction by an American supercomputer manufacturer, and the implementation of an operating system for some Japanese minicomputers. Therefore the vectorization and parallelization techniques obtained through this research must be effective to execute various programs effectively in vector processors and parallel processors. The techniques will be also applicable to the other languages including Fortran90 which is the newest version of FORTRAN and is equipped with various control/data structures which have been considered to be specific to block-structured languages.

#### 1.1.4 Outline of this thesis

This thesis discusses a way to construct an automatic vectorizing and parallelizing compiler for a block-structured language. The following three topics are included in this thesis.

In Chapter 2, the performance of vector load/store of vector supercomputers is evaluated with our newly developed benchmarking program. In particular, vector indirect load/store performance is precisely examined. One of the reason why we focused on the indirect addressing is that these instructions must be often used in non-numerical applications which contain data-structures constructed with pointers. Therefore these results are indispensable to construct a compiler for a blockstructured language and to obtain optimal performance on VP/PVP machines in executing non-numerical applications. The other reason is that the vector-indirect addressing is also important for some numerical applications. The details will be described in the chapter.

In Chapter 3, we propose a new method to execute recursive procedures (and functions) on supercomputers. Generally, the targets for automatic vectorization and parallelization compilers are limited to D0 loops of FORTRAN77. But block-structured languages have more versatile control structures to express iterations, such as while loops and repeat/until of Pascal. Moreover, recursive procedures can be used in these languages. Needless to say, these iterative control structures should be also vectorized/parallelized if possible. But there are not many researches to discuss this issue. In particular, there are few re-

searches to treat recursive procedures. We propose a method to cope with the difficulty of automatic vectorization and parallelization of recursive procedures. The methods named "breadth-first" method is to utilize parallelism among two or more recursive calls and to execute them in parallel. Some procedures are accelerated more than 50 times by this method.

Chapter 4 describes the organization and the features of our automatic vectorizing/parallelizing Pascal compiler named **V-Pascal** Version 3. V-Pascal Ver.3 is designed as an automatic vectorizing and parallelizing compiler for PVP machines. The target language is a sequential block-structured language Pascal. Many techniques and methods we have implemented will be described later.

The last chapter, Chapter 5 is the conclusion of this thesis with some open questions and future works.

## Chapter 2

## Benchmarking Vector Indirect Load/Store Instructions

### 2.1 Introduction

In some fields of large-scaled numerical computations, the data should be expressed as huge random sparse matrices. We can enumerate some important examples such as Finite Element Method(FEM), Linear Programming(LP), Electric Circuit Simulation, Neural Network Simulation and so on. In processing these computations on VP/PVP machines, vector indirect load/store instructions are useful for both memory-space efficiency and the execution speed. In other words, the performance of the indirect vector accesses affects the overall performance of these computations.

We also believe that indirect vector accesses are effective for advanced automatic vectorization. For example, in some cases nested loops can be converted into non-nested loops by using list vectors, and allow longer vector lengths. Supercomputers with high performance tend to have large  $N_{half}[15]$  values, so this conversion is useful for those machines that have good performance on vector indirect accesses. We have already implemented it in the early version of "V-Pascal" and have shown its usefulness[43].

Furthermore, to extend the applications of supercomputers beyond numerical computations, compilers or languages must support the data represented by pointers e.g., linked lists, trees etc. To vectorize applications, indirect vector load/store instructions are essential. These types of automatic vectorization must be supported on V-Pascal version 3 and then indirect vector load/store instructions will become more important in the field of vectorization.

Therefore, we have been investigating the performance of vector indirect access on vector supercomputers but enough data has not been accumulated to date. Some existing benchmarks showed the performance of applications where indirect vector load/store instructions were used but we wanted to know the "pure" performance of these instructions, because the precise information about these instructions are very important in code-generation of compilers. This chapter describes a newly developed benchmarking program for this purpose and obtained some interesting results.

# 2.2 Factors Dominating the Performance of Indirect Vector Access

This section describes the factors dominating the performance of indirect vector load/store instructions. Generally an indirect vector access is slower than a direct vector access for the same amount of data. There are two main reasons for this.

- Complications in the behavior of load/store pipelines as a result of indirect accesses.

- 2. Effect of bank conflicts.

The following sections describes these two factors.

### 2.2.1 Behavior of Indirect Vector Operations

This section discusses the behavior of indirect vector access and compare it with that of direct vector access.

### 2.2. FACTORS DOMINATING THE PERFORMANCE

Let us start with the direct operations. A sample of a vector direct load instruction is written in assembly code as follows.

vload BASE, STRIDE, vr1

In this statement  $\mathtt{vr1}$  means a vector register and BASE means an address. STRIDE expresses the distance between each data elements on the memory. When expressing the i-th element of  $\mathtt{vr1}$  as  $\mathtt{vr1}(i)$ , the semantics of the instruction are presented as follows.

for each  $i \in \{1,2,..., < vector \ length > \}$ , let vr1(i) to the content of the address BASE+STRIDE×(i-1)× $< size \ of \ each \ element >$

Note that the 3rd line shows the effective address for each element. Turning to indirect vector access a sample of an indirect vector load instruction is as follows.

viload BASE, vr1, vr2

The semantics of this instruction are as follows.

for each  $i \in \{1,2,..., \langle vector \ length \rangle \}$ , let vr2(i) to the content of the address BASE+ $vr1(i) \times \langle size \ of \ each \ element \rangle$

As shown above, the semantics are similar. The difference is seen only in the calculation of effective addresses. In fact, complications in the behavior of indirect vector access comes from this difference. We considered the detailed complications as follows.

- An indirect vector operation must treat two vector registers and the set-up sequences may be more complicated.

- Another data path for list vectors is needed between vector registers and each load/store pipeline, but an implementation without this path is also possible, at the cost of throughput.

3. In a direct vector operation, effective addresses of the array elements are estimated when the vector unit is set up. But in indirect vector operations, they are known only at run-time. This means that it is impossible to foresee the occurrences of bank conflicts or memory-protection exceptions. Moreover, when some elements in the list vector are of the same value, the stores must be serialized to guarantee the sequential order of writes<sup>1</sup>. Therefore complicated pipeline controls are needed lowering the throughput of the pipeline.

Note that the complications are separated into two types. Some of them affect the instruction set-up time and others affect the throughput. In the above list, 1 belongs to the former, 2 belong to the latter and 3 may belong to the both.

#### 2.2.2 Bank Conflicts

Bank interleaving is one of commonly used techniques to utilize slow memory chips in high-performance computer systems. As supercomputer systems are of quite high-performance, even faster S-RAM chips are sometimes regarded as slow. Therefore most VP/PVP supercomputers have memory units interleaved with many banks. Another common technique is caching but it will not work well in supercomputers which tend to have large working sets in memory. Accordingly caching is rarely used in VP/PVP machines.

A simple model of bank interleaving is shown in Figure 2.1. On a memory chip, there is a delay between giving an address and accessing the location. It is called **Access Time**(and represented as  $T_a$ ). Also it takes a time (called **Recovery Time** represented as  $T_r$ ) from the finish of one access and before the next one is possible. We call  $T_a + T_r$  the **Continuous Access Time**<sup>2</sup> and represent it as  $T_c$ . Interleaving with N-banks seemingly decreases  $T_c/N$  if an access is for stride-1. But if two accesses to the same memory occur with an interval shorter than  $T_c$ , the latter access will be delayed until  $T_c$  passes. This is called a

Figure 2.1: Bank Interleaving

Bank Conflict. Obviously, in indirect vector accesses, bank conflicts occur more frequently than in direct vector accesses and their frequency dominates the performance of indirect vector accesses.

In the simple model (shown in Figure 2.1), expressing the pipeline period of the load/store pipeline as  $T_p$ , the following equation characterizes the frequency of the occurrence of bank conflicts.

$$s = T_p \times N/T_c$$

s means that this memory unit allows accesses for stride-s without any bank conflicts. The greater s becomes, the less is the frequency of conflict.

Actually as most memory architectures are not simple as this. As described in Section 2.4.2, some machines have much more complicated memory units, in particular, in multi-processor systems. But s is still useful as a criterion of performance. N and  $T_c$  still remain as the dominating factors of the performance of indirect vector accesses.

### 2.2.3 Performance Factors and their Compound Effects

As mentioned in the former sections, the performance of indirect accesses is affected by the following factors.

<sup>&</sup>lt;sup>1</sup>The S-820 and S-3800 have another indirect store instruction which does not guarantee the order. See Section 2.4.2.

<sup>&</sup>lt;sup>2</sup>Actually this value differs between read and write accesses.

- 1. Set-up times for indirect vector load/store instructions.

- Throughput of each load/store pipeline in indirect vector operation.

- 3. The number of load/store pipelines and of processors.

- 4. The frequency of bank conflicts and their penalties.

These factors should be examined in benchmarking. We also have to note the compound effects of these factors. In some systems, the penalties of bank conflicts in indirect accesses seem to be worse than that in direct accesses. It is considered to be caused from the difficulty of pipeline control under irregular occurrences of bank conflicts.

### 2.3 The Benchmarking Program

This section describes our new benchmarking program for indirect vector load/store instructions.

### 2.3.1 Our Main Goal

Our main goal is to evaluate the performance of vector indirect addressing on each machine. The most specific feature of our benchmark is to evaluate both the throughput of indirect addressing and the effect of bank conflicts. We insist that it is quite important to evaluate them separately while existing older benchmarks try to evaluate them at once.

Assume that a machine show enough performance of the throughput but it is seriously decelerated by bank conflicts. Such machine may show poor performance in older benchmarks, but this machine is still available when an application with vector indirect accesses is carefully programmed to avoid bank conflicts. It is also possible for a compiler to generate efficient objects for advanced vectorization with indirect accesses described in Section 2.1 if the compiler has an accurate information of the penalties of bank conflicts on the machine.

# 2.3. THE BENCHMARKING PROGRAM 2.3.2 Benchmarking Program

To take an accurate measurement assembly coding is ideal, but it is hard to program each benchmark in assembler, because the architectures of some machines are proprietary. Therefore our benchmarking program is written in FORTRAN77 and it causes some problems. The main problem of our program is that it cannot evaluate performance of vector direct/indirect load instructions exactly. The reason is as follows.

- 1. We cannot generate vector load instructions without generating vector store instructions. For example, a FORTRAN statement A(I)=B(I) includes both of vector load and store instructions and we cannot get rid of the store. On the other hand, we can easily generate a vector store instruction alone by a Fortran statement A(I)=1.0D0.

- "<Execution time of A(I) = B(I)> <execution time of A(I) = 1.0DO>", does not always mean the execution time of the vector load instruction because of the chained behaviour of vector pipeline units in the target machine.

The details of these reasons are described in [48].

Our program is carefully designed to avoid unexpected effects caused by optimization of compilers. The main technique to avoid them is to use some variables of which value cannot be assumed by compilers. Our program is also designed to take execution times of each benchmarking item twice and reports the latter value because instruction/data cache of scalar units may affect the execution time. The details of our benchmarking techniques are also described in [48].

The items examined in our benchmarking are as follows. (In the following, A and B are arrays of REAL\*83. L is an array of INTEGER\*4.)

· The execution times of

$$A(I) = B(I)$$

with vector lengths  $2^4$ ,  $2^6$ ,  $2^8$ , ...,  $2^{18}$  are used to estimate the throughput of load/store pipelines on vector direct load/store operations,

<sup>&</sup>lt;sup>3</sup>8bytes/element

and are also used for comparison with the results of indirect load/store operations.

· The execution time of

$$A(I) = B(I)$$

$$A(I) = 1.000$$

at vector lengths  $2^{18}$  are used to estimate the throughput on direct accesses.

· The execution time of

$$A(I) = B(I*STRIDE)$$

$A(I*STRIDE) = 1.000$

for strides 1, 2, 3, ..., 512 and vector lengths  $2^4, 2^6, 2^8$  are used to estimate the time  $T_c$  of the memory unit.

· The execution time of

$$A(I) = B(L(I))$$

$A(L(I)) = 1.000$

for each L as

$$L(I) = ((I*STRIDE).MOD.(2**18))+1$$

for strides 1, 2, 3, ..., 512 and vector lengths 2<sup>4</sup>, 2<sup>6</sup>, 2<sup>8</sup>, ..., 2<sup>18</sup> are used to estimate the throughput on vector indirect accesses when bank conflicts occur periodically.

· The execution time of

$$A(I) = B(L(I))$$

$$A(L(I)) = 1.0D0$$

with L initialized as shown below. (In these expressions, N means the vector length.)

#### 2.3. THE BENCHMARKING PROGRAM

```

- L1(I) = I.

- L2(I) = N-I+1.

- {L3(I)} = {random permutation of 1, 2, ..., N }.

- L4(I) = <random number from [1, N]>.

- L5(I) = 1.

- LS(I) = I.MOD.X, X∈ {2, 3, 4, ..., 10}

```

for vector lengths  $2^4, 2^6, 2^8, ..., 2^{18}$ . This includes the influence of bank conflicts that occur when addressing is either regular or random.

If a VP has 2 load pipes and 1 store pipe, it becomes easy to evaluate the throughputs of indirect load and store instructions. The statement A(I)=B(I) needs only 1 load pipe and 1 store pipe for direct load and store instructions while the statement A(I)=B(L(I)) needs 2 load pipes and 1 store pipe, and for both of these statements all of the pipelines are organized into a chain and can be work simultaneously. Therefore, if the throughput of the load pipe for both of indirect and direct accesses are the same and no bank conflict occurs, the execution times of these statements can be assumed to be almost the same. Similarly, if the throughputs of indirect and direct store are the same, the execution time of the statements A(I)=1.0D0 and A(L(I))=1.0D0 can be almost the same. If the throughput of load or store pipes for indirect accesses is much lower than that for direct access, the pipe for the indirect access becomes the bottleneck of the whole operation and the execution time shows the throughput for indirect accesses.

Note that A, B and L are allocated continuously in the memory. It means that A(I), B(I), L(2\*I-1) and L(2\*I) of a specific value of I are all on the same bank. This allocation may be also taken into consideration when we evaluate the result in detail.

### 2.4 Experimental Results

### 2.4.1 Performance parameters

We show the following performance parameters as a summary from the results of our benchmarking program.

Firstly, as the parameter of throughput of load/store pipelines, we show the following values.

- Data transfer rate with the following statements

- -A(I)=B(I)

- A(I)=1.0D0

at each vector length of 28, 218.

- Data transfer rate with the following statements

- -A(I)=B(L(I))

- -A(L(I))=1.0D0

for L(I)=I at vector length of 218.

Secondly, we show the following values to estimate the averaged throughput of load/store pipelines under the consideration to the effects of bank conflicts.

Averaged data transfer rate with the following statements

$$A(I) = B(I*S)$$

$A(I*S) = 1.000$

at S = 1, 2, 3, ..., 512 and vector length  $2^8$ .

• Averaged data transfer rate with the following statements

$$A(I) = B(L(I))$$

$$A(L(I)) = 1.0D0$$

for strides 1, 2, 3, ..., 512 and vector length  $2^{18}$ .

## Thirdly, to evaluate the worst case of the data transfer rate caused

by bank conflicts, we show the following values. These values imply the case where all of the memory accesses are to the same bank.

Data transfer rates with the following statements

$$A(I) = B(I*S)$$

$A(I*S) = 1.000$

2.4. EXPERIMENTAL RESULTS

at S = 512 and vector length  $2^8$ .

Data transfer rates with the following statements

$$A(I) = B(L(I))$$

$$A(L(I)) = 1.000$$

with L(I)=512\*(I-1) and vector length 2<sup>18</sup>.

Lastly, we show the following strides to evaluate the performance of memory systems. The smaller these values are, The more serious are the influence of bank conflicts.

The minimum number of stride which causes the performance which is less than the half performance of the maximum with the following statements.

```

A(I) = B(I*S)

A(I*S) = 1.000

```

(We call this number  $S_{half}$  in this thesis.)

The minimum number of stride which causes as the same performance as that of the worst case with the following statements.

```

A(I) = B(I*S)

A(I*S) = 1.000

(We call it S_{worst} in this thesis.)

```

Figure 2.2: A sample of  $S_{half}$  and  $S_{worst}$ .

Stride

See Figure 2.2 as an example of  $S_{half}$  and  $S_{worst}$ .

The results are shown in Table 2.2 at the end of this report. To express the performance, we use a unit MDwords/sec<sup>4</sup>. This unit is useful for comparison to MegaFLOPS<sup>5</sup> but note that it is not always equal to the transfer rate between memory and the processor.

We also show some additional values which can be got from the above values labeled (U),(V),(W) and (X) in the Table 2.2. These values are calculated by the expressions written in the first column of the table.

The value of (U),(V) implies the relative throughput of load/store

pipelines in indirect accesses compared to that in direct accesses.

(W) and (X) are helpful to evaluate the robustness to bank conflicts on each machine, but we should note that (W) is measured by the vector length of 2<sup>8</sup> which is too short for some machines to evaluate the throughput. We should also note that (X) is measured by indirect accesses and it may cause some compounded effects of bank conflicts and indirect accesses.

The results in Table 2.2 are also shown in Figure 2.4, Figure 2.4 and Figure 2.6.

### 2.4.2 Target Machines and the Results

Table 2.1 shows the performance and hardware facilities of each target machine.

The features and some notices for each machine are described below with the results.

### Hitachi S-820/80

The S-820/80<sup>6</sup> is an old type machine announced in 1987. Now this series of machines are obsolete and replaced by the S-3000 series.

One of the specific features of this machine is a support of a special instruction of indirect vector store, called VIST[13]. As this instruction does not preserve the sequential order of the store, the elements of the list vector must be differ from each other, but its throughput is higher than that of the normal indirect store instruction called VSTX[13]. We have added the results using VIST in Table 2.2 in parentheses. According to the results labeled (F) and (J) in Table 2.2, VIST instruction shows about 80% better performance than VSTX instruction shows. VIST is not only used through user directives but also used by our V-Pascal compiler to utilize the instruction.

We also have to note that (B) does not show the maximum data transfer rate in direct accesses. The transfer rate for stride-2 access shows 563 MDwords/sec and is about 20% better than that for stride-1. The performance for any other odd number of stride is no better

<sup>&</sup>lt;sup>4</sup>Mega Doublewords per second. Doubleword means the size of REAL\*8

<sup>&</sup>lt;sup>5</sup>Mega FLoating-OPerations per Second

<sup>&</sup>lt;sup>6</sup>The S-820/80 was settled at Computer Centre, The University of Tokyo. This machine has been replaced by the S-3800/480 in Feb. 1993.

than 350 MDwords/sec. It is not obvious why this machine shows better performance of the direct store only for stride-1 and stride-2. It may have to do with the complicated bank interleaving in the memory unit of the S-820.

Since the S-820 was equipped with only two pipes for memory access, the statement A(I)=B(L(I)) cannot be processed in a chain of pipelines. Taking the pipeline organization of the S-820 in consideration, it is assumed that A(I)=B(L(I)) will be executed as follows.

- 1. The processor loads L and B with chaining.

- 2. Then it stores A while it loads next L.

- 3. Lastly it loads B and stores A with chaining.

Note that 2\* <vector length of strip mining> elements of data are processed by these 3 stages which takes the same time with A(I)=B(I) to transfer 3\* <vector length of strip mining>. Therefore the throughput of A(I)=B(L(I)) is at most 66% of that of A(I)=B(I) even if the throughput of the indirect load is the same as that of the direct load. According to the value of (U), the performance parameter for indirect load accesses (E) is 64% of that for direct load access (C). Thus it is assumed that the throughput of indirect loads on the S-820 is as the same as that of direct loads. The throughput of indirect stores is not so good as that of direct loads even if VIST instructions are used, but the absolute performance is still kept to high.

As the values of direct load (A) and direct store (B) is almost the half of indirect load (C) and indirect store (D), 2<sup>8</sup> is not considered to be enough for the vector length to evaluate the effects of bank conflicts and the value of (W) is not reliable as the parameter of robustness to the bank conflicts. Taking (X) as the parameter, the S-820 is consider to be robust to the bank conflicts in indirect addressing and will show good performance even for randomized list vectors. The values of (X) for the SX series seem to be better than that of the S-820, but as described later, these values are not reliable because the absolute performances of indirect accesses on the SX-2N and the SX-3R are worse.

### Fujitsu VP-2600/10

One of the specific features of the VP-2600<sup>7</sup> is that it is equipped with 2 load/store pipes[46]. It means that the VP-2600 can execute A(I)=1.0D0 twice faster than A(I)=B(I) if both of the pipes work in parallel. But it is inappropriate to evaluate the throughput of indirect store instruction because these pipes are used separately for load and store to execute A(L(I))=1.0D0. The compiler did not unroll the loops in our program because we had hided the vector lengths of the loops to avoid unexpected optimizations. Therefore the values labeled (B),(D) in Table 2.2 reflect the throughput of one pipeline.

As the value of (U) is a lower one compared with the other machines, the VP-2600 is considered to be of a rather poor performance of the indirect load. But contrarily, the indirect store (V) shows remarkable performance. Note that VP-2600 has no special instructions to keep the order. The values of the Y-MPs with 1 CPU are better than that of VP-2600, but the Y-MPs are too slow to compare with. The value of (V) of the Y-MP with 4 CPUs also seems better, but like VIST of the S-820 and the S-3800, the sequential order of the stores in elements of the list vector for an indirect store on Y-MP cannot be preserved. On the VP-2600, both of the absolute and relative performance of indirect stores, which preserves the order of stores, are remarkably high.

It is conspicuous that the values of direct accesses (A), (B) are much lower than those of indirect accesses (C),(D). Therefore (W) is not considered to be suitable for the parameter of the performance for the indirect accesses for the same reason with the S-820. The alternative value (X) is neither so high nor so low when compared with the other target machines.

Note that the minimum data transfer rates of the store instructions are lower than those of the load instructions. It may be caused from the difference of the continuous access times between read and write to the memory. It should be also noticed that the absolute performance of the minimum data transfer rates are lower than those of the most of the other machines.

<sup>&</sup>lt;sup>7</sup>Data Processing Center, Kyoto University.

### NEC SX-2N

The SX-2N<sup>8</sup> is a dated machine but we show the results from the SX-2N for comparison with the SX-3R series. Since the vector unit of the SX-2 series is equipped with only one load/store pipe, it does not match the model to evaluate the benchmarking results as described in Section 2.3.

As shown in Table 2.2, the SX-2N showed quite poor performance for vector indirect accesses. As our main interest is the improvement of the performance of the SX-3R, we only summarize the result in short. The SX-2N shows only quite poor performance for both of the indirect loads and stores. It is interesting that even in a direct store, the performance is rapidly degraded by bank conflicts (see (V) in Table 2.2).

### Cray Y-MP 8/4128 and Y-MP 2E/264

The memory organization of Cray Y-MP series has complicated structure (except Cray Y-MP EL) and does not match with our simple model in Figure 2.1. However, in the case of Y-MPs, the memory organization and detailed behaviors of the memory unit are fully described in manuals [7]. Figure 2.3 shows the block diagram of the memory unit of our target machines, Y-MP 8/41289 and Y-MP 2E/264<sup>10</sup>. The memory systems of these two machines are organized as the same except the capacity. The memory is divided into 4 sections, each section consists of 8 sections and each section contains 8 banks. The basis for memory performance for a CPU is the number of section because each CPU can access continuously to a section only in every 5 clock periods. Different CPUs can access to the same section simultaneously but each bank can be accessed only in every 5 clock periods. Therefore, the worst performance of memory access is the same as 1/5 of the peak performance.

On the benchmark with 4 processors, we allowed the program to do indirect vector store in parallel. This access may break the sequential

#### 2.4. EXPERIMENTAL RESULTS

Figure 2.3: Y-MP Memory Organization[7]

<sup>&</sup>lt;sup>8</sup>This machine was settled at Computation Center, Osaka University. This machine has been replaced by the SX-3R/14 in Feb. 1993.

<sup>&</sup>lt;sup>9</sup>Institute of Fluid Science, Tohoku University.

<sup>&</sup>lt;sup>10</sup>Supercomputer Laboratory, Institute for Chemical Research, Kyoto University.

order of writes, therefore the result should be treated as the same as that of VIST on the S-820 and the S-3800. When the order of stores must be preserved, the performance of the indirect store will be degraded as the same as that of 1 CPU.

Since the Y-MPs are equipped with 2 load pipes and 1 store pipe on each CPU, it is easy to evaluate our benchmarking results as described in Section 2.3. One of the most remarkable results is that the values of (C),(D),(E) and (F), on Y-MPs with both 1 CPU and 4 CPUs, indicate that the throughput of the load and store pipelines seem to be always constant on both of the direct and indirect accesses. The values of (U) also substantiate it. The values of (E) are a little worse than those of the others, but the performance of A(I)=B(L(I)) relative to A(I)=B(I) on the Y-MPs are still quite good compared with the other machines. However, in the case of the results from Y-MP with 1 CPU, as the absolute performance is much lower than the other machines, the results are not so surprising. Another remarkable result is that the obtained results with 4 CPUs show that the performance of the Y-MP is quite good unless bank conflict occurs. The absolute performance of (C),(D),(E) and (F) are comparable to that of the S-820. As the peak performance of the Y-MP 8/4128 is 2 GFlops, the balance of the performance of memory access and that of the computation is much better than that of the S-820. This balance of the Y-MPs seems to be the best among the target machines.

Although the maximum performances of indirect accesses of the Y-MP are quite good, the value of (W) indicates that the performances of indirect loads and stores are degraded by bank conflicts rather seriously compared with the other machines.

Note that the Y-MP 2E/264 and the Y-MP 8/4128 are equipped with the same memory system except their capacity and their architectures are the same. Therefore the results are almost the same. But the results show that the newer model 2E has been a little improved in the performance of direct stores.

### S-3800/480

The S-3800 is a successor of the S-820 and has similar features with the S-820. Each vector processor of the S-3800 is also equipped with 1

load/store and 1 load pipe. VIST instruction is also supported. Therefore the tendency of the results is similar to that of the S-820. The main difference is that the S-3800 is a multi-processor system while the S-820 is a single-processor system. The S-3800 on which we executed our benchmarking program is a system with 4 CPUs, but we had no chance to obtain the results with multi-processors.

We should comment that there was no unusual result of the performance as seen in the S-820. The performance for stride-1 is always the same as the peak performance.

As shown in Table 2.2, the peak transfer rates of memory accesses of the S-3800 are the most high among the target machines. In comparison with that of the S-820, they are improved about 2.5 times. VIST of the S-3800 is 3 times faster than that of the S-820 and the relative throughput of indirect access (U) is also improved. From the point of view of the balance between the performance of memory access and computation, S-3800 with 1 CPU is 2.7 times faster than the S-820, therefore the balance can be considered to be almost the same as that of the predecessor. This improvement is significant because the clock period of the S-3800 is only the half of that of S-820 and there is no change in the organizations of the load and store pipelines.

Another improvement of the performance is seen in the robustness to bank conflicts. The value (W) is the best among the target machines<sup>11</sup>. The large number 64 of  $S_{half}$  also proves the robustness.

However, the relative throughput of the indirect load is a little decelerated for load operations. The reason is that the performance of direct load (C) is improved remarkably. Another deceleration is seen in the results of direct access for vector length  $2^8$ . The value of (A),(B) is almost as the same as that of the S-820 while the performances for vector length  $2^{18}$  is 2 or 3 times faster than that. It means that the S-3800 has much bigger  $N_{half}$  value which also affects to the unusual value of the robustness to bank conflicts (W).

Also the minimum data transfer rates of the store instructions are lower than that of the load instructions like VP-2600. It is curious that the absolute performance of the minimum data transfer rates of store

<sup>&</sup>lt;sup>11</sup>The value of (W) for SX-2N is neglectable because of its poor indirect load and store performance.

### SX-3R/14

A fully configured SX-3R system is a multi-processor system with 4 CPUs, but the machine we could use is a SX-3R/14<sup>12</sup> which is the fastest machine among the single processor models.

Unlike the S-3800, the SX-3R series is equipped with fully reorganized memory system compared with the predecessors. A CPU of the SX-3R has 2 load and 1 store pipes while the SX-2N has only 1 pipe. This means that it is easy to evaluate the results as described in Section 2.3.

From the results, it is noticed that this machine shows quite good performance for direct loads and stores even for the short vector length. On the contrary, throughput for indirect access is still poor. The absolute performance of the indirect access is almost the same as that of S-820/80, but compared with the performance of the direct access, the performance of indirect read is 2.9 times lower than that of direct read and indirect write is 7.8 times lower than direct write. It is obvious that the throughput of the load and store pipelines of the SX-3R is seriously degraded in indirect access.

Since this machine shows good performance even for a short length of vector, the value of (W) is available to evaluate the robustness to bank conflicts. The value of (W) means that SX-3R can be decelerated easily by bank conflicts. Comparing the performance parameters of direct store (B) with (H), we can see that the effects of bank conflicts on this machine is quite serious when writing. It also indicates that the minimum data transfer rate of the SX-3R is not only lower than that of the other machines but also decelerated by indirect accesses as shown in the values (I),(J).

### 2.5 Conclusions

We have obtained fundamental data on the performance of indirect vector accesses. As mentioned in the first section, vector indirect ac2.5. CONCLUSIONS 39

cesses are valuable in the fields of numerical computations, and are also needed for advanced automatic vectorization. Therefore this data enables us to make good use of supercomputers and make it possible to extend their applications.

We had no chance to run the benchmarking program on neither SX-3R with 4 CPUs, Y-MP 8 with 8 CPUs, C90 nor T90. To make our research more concrete, it is indispensable to get their data and we are eager for the chance.

<sup>&</sup>lt;sup>12</sup>Computation Center, Osaka University.

Table 2.1: The performance and hardware facilities of each machine

| Machine                              | S-820/80                                                               | VP-2600/10                            |          | SX-2N                                                                     | CRAY<br>Y-MP 8-4128                            |

|--------------------------------------|------------------------------------------------------------------------|---------------------------------------|----------|---------------------------------------------------------------------------|------------------------------------------------|

| Number of<br>Processors              | 1                                                                      |                                       | 1        | 1                                                                         | 4                                              |

| Theoretical<br>Max.speed<br>(MFlops) | 3000†                                                                  | .5                                    | 000      | 1142                                                                      | 500†<br>× 4 processors                         |

| Load/store<br>pipes                  | (4data para.)<br>× 1 load pipe<br>(4data para.)<br>× 1 load/store pipe | (4data para.)<br>× 2 load/store pipes |          | (8data para.)  × 1 load pipe also serves as (4data para.)  × 1 store pipe | 2 load pipes<br>1 store pipe<br>× 4 processors |

| lock period(ns)                      | 4                                                                      |                                       | 3.2      | 7                                                                         | 6                                              |

| Number of<br>Memory Banks            | 128                                                                    |                                       | 512      | 512                                                                       | 256                                            |

| Vector length<br>per<br>strip mining | 512                                                                    | 2                                     | 048      | 256                                                                       | 64                                             |

| Compiler<br>Version                  | FORT77/HAP<br>V24-0F                                                   | FORTRA<br>V11L10                      | N77EX/VP | FORT77/SX<br>Rev.041                                                      | CFT77<br>4.0.3.6                               |

| Machine                              | S-3800/480                                                             |                                       | SX-3R/14 | CRAY<br>Y-MP 2E-264                                                       |                                                |

| Number of<br>Processors              | 4                                                                      |                                       | 1        | 2                                                                         |                                                |

| CDA                                  |                                                                        |                                       |          |                                                                           |                                                |

| Machine                              | S-3800/480                                                                      | SX-3R/14                                                           | Y-MP 2E-264                                    |

|--------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|

| Number of<br>Processors              | 4                                                                               | 1                                                                  | 2                                              |

| Theoretical<br>Max.speed<br>(MFlops) | 8000<br>× 4 processors                                                          | 6400                                                               | 500†<br>× 2 processors                         |

| Load/store<br>pipes                  | (4data para.)  × 1 load pipe (4data para.)  × 1 load/store pipe  × 4 processors | (4data para.)<br>× 2 load pipes<br>(4data para.)<br>× 1 store pipe | 2 load pipes<br>1 store pipe<br>× 2 processors |

| clock period(ns)                     | 2                                                                               | 2.5                                                                | 6                                              |

| Number of<br>Memory Banks            | 512                                                                             | 512                                                                | 256                                            |

| Vector length<br>per<br>strip mining | 512                                                                             | 256                                                                | 64                                             |

| Compiler<br>Version                  | FORT77/HAP<br>V26-00                                                            | f77sx<br>Rev.040                                                   | CFT77<br>5.0.3.0                               |

<sup>†</sup> This value differs from the official performance in U.S. and Europe, but can be achieved and officially announced in Japan.

#### 2.5. CONCLUSIONS

| Table 2 2- | Experimental | results on | each machine |

|------------|--------------|------------|--------------|

|            |              |            |              |

|             | Benchmarki     | ing                         | Vector                                 | (Label         | ) S-82       | 0/80    | VP-2600/10 | SX-2 |

|-------------|----------------|-----------------------------|----------------------------------------|----------------|--------------|---------|------------|------|

|             | items          |                             | length                                 |                |              |         |            |      |

| Maximu      | m data         | A(I)=B(I)                   | 28                                     | (A)            | 3            | 52      | 234        | 457  |

| transfe     | r rate         | A(I)=1,0D0                  | 28                                     | (B)            | 4            | 69      | 312        | 599  |

| (Dword      |                | A(I)=B(I)                   | 218                                    | (C)            | 6            | 97      | 1024       | 334  |

|             |                | A(I)=1.0D0                  | 218                                    | (D)            | 9            | 78      | 1139       | 438  |

|             | A              | (I)=B(L(I))                 | 218                                    | (E)            | 4            | 46      | 443        | 53.  |

|             | A              | (L(I))=1.0D0                | 218                                    | (F)            | 244(         | 426†)   | 578        | 61.  |

| Average     | ed data I      | A(I)=B(I*S)                 | 28                                     | (G)            | 3            | 04      | .191       | 403  |

| transfe     | r rate A       | (I*S)=1.0D0                 | 28                                     | (H)            | 3            | 20      | 233        | 15   |

| (Dword      | s/sec.) A      | (I)=B(L(I))                 | 218                                    | (1)            | 3            | 79      | 371        | 52.  |

|             | A              | (L(I))=1.0D0                | 218                                    | (J)            | 224(         | 413†)   | 472        | 61.  |

| Minimu      | m data A       | (I)=B(I*512)                | 28                                     | (K)            | 25           | 9.6     | 20.6       | 10.  |

| transfe     | rrate A(       | I*512)=1.0D0                | 28                                     | (L)            | - 31         | 3.3     | 16.6       | 11.  |

| (Dword      | s/sec.) A      | (I)=B(L(I))                 | 218                                    | (M)            | 30           | 0.0     | 21.6       | 9.7  |

| 78-23-77-77 | A              | (L(I))=1.0D0                | 218                                    | (N)            | 31.1(        | 31.1†)  | 17.1       | 10.  |

| $S_{ho}$    |                | A(I)=B(I*S)                 | 28                                     | (0)            |              | 6       | 16         | 8    |

| (stri       | 11/2           | (I*S)=1.0D0                 | 28                                     | (P)            |              | 6       | 16         | 8    |

| (Str)       |                | (I)=B(L(I))                 | 218                                    | (Q)            |              | 16      | 4          | 12   |

|             |                | (L(I))=1.0D0                | 218                                    | (R)            |              | 32†)    | 4          | 12   |

| 21          |                | (L(1))=1.000<br>A(I)=B(I*S) | 28                                     |                |              | 28      | 256        | 25   |

| $S_{wo}$    |                |                             | 28                                     | (S)            |              | 28      | 256        | 25   |

| (stri       |                | (I*S)=1.0D0                 | 2                                      | (T)            | 1            | 40      | 200        | 40   |

| Rela        |                | (E)                         | 218                                    | (U)            | 0.0          | 640     | 0.433      | 0.1  |

| through     |                | (C)                         |                                        | 1.7            |              |         |            |      |

| indi        |                | (F)                         | 218                                    | (V)            | 0.249(       | 0.436†) | 0.507      | 0.1  |

| load/       | store          | (D)                         |                                        | 4.4            |              |         |            | -    |

| Robust      | ness to        | (G)+(H)                     | 28                                     | (W)            | 0.           | 760     | 0.777      | 0.5  |

|             |                | (A)+(B)                     |                                        |                | 70.700.77.70 |         | 70.70      |      |

| bank co     | onflicts       | $\frac{(I)+(J)}{(E)+(F)}$   | 218                                    | (X)            | 0.874(       | 0.908†) | 0.826      | 0.9  |

| /T = 1 = 10 | N. APPROVED    |                             | EV SUBSE                               | 100            | SX-3R/14     | Y-MP 2  | Pines 1    | 1    |

| (Label)     | Y-MP8/4128     | Y-MP8/4128                  | 5-3800/                                | 480            | 5A-3H/14     | (1CF    |            |      |

|             | (4CPUs)        | (1CPU)                      |                                        |                |              |         |            |      |

| (A)         | 133            | 114                         | 351                                    |                | 813          | 13      | 9-1        |      |

| (B)         | 123            | 107                         | 470                                    |                | 1133         | 14      |            |      |

| (C)         | 152            | 583                         | 194                                    |                | 1259         | 150     | ST.        |      |

| (D)         | 152            | 582                         | 1913                                   | 3              | 1592         | 15      | 2          |      |

| (E)         | 121            | 485                         | 1087                                   |                | 437          | 139     | 9          |      |

| (F)         | 144            | 571                         | 646(133                                | 24†)           | 285          | 143     |            |      |

| (G)         | 102            | 114                         | 338                                    |                | 706          | 10-     | 4          |      |

| (H)         | 116            | 90.1                        | 536                                    |                | 577          | 13      | 9          |      |

| (1)         | 88.7           | 326                         | 100-                                   | 1              | 382          | 92.     | 2          |      |

| (L)         | 109            | 411                         | 583(12                                 |                | 265          | 10      | 8          |      |

| (K)         | 32.0           | 30.1                        | 29.0                                   |                | 23.8         | 31.     | 5          |      |

| (L)         | 32.0           | 30.7                        | 23.9                                   |                | 21.7         | 32.     |            |      |

| (M)         | 29.4           | 29.6                        | 30.2                                   |                | 17.7         | 29.     |            |      |

| (N)         | 31.2           | 32.9                        | 24.4(24                                |                | 17.5         | 31.     |            |      |

|             |                | A                           |                                        | -              |              | 16      |            |      |

| (0)         | 16             | 16                          | 64                                     |                | 8            | 16      |            |      |

| (P)         | 16             | 32                          | 16                                     |                | 8            | 1300    |            |      |

| (Q)         | 128            | 16                          | 32                                     |                | 16           | 16      |            |      |

| (R)         | 16             | 16                          | 32(16                                  |                | 16           | 16      |            |      |

| (S)         | 16             | 32                          | 512                                    |                | 256          | 32      |            |      |

|             | 32             | 32                          | 512                                    |                | 256          | 32      |            |      |

| (T)         | 0.796          | 0.832                       | 0.56                                   | 0              | 0.347        | 0.93    | 16         |      |

|             |                |                             | The second second second second second | 1-14-74-1 TO 1 |              | 0.0     | 63         |      |

| (U)         |                | 0.981                       | 0.338(0.0                              | 692†)          | 0.179        | 0.94    | * 1        |      |

|             | 0.947<br>0.852 | 0.981                       | 0.338(0.0                              |                | 0.179        | 0.94    |            |      |

<sup>†</sup> Values in parentheses are measured using VIST instructions.

Figure 2.4: Effects of bank conflicts using direct access instructions.

Figure 2.5: Effects of bank conflicts using indirect access instructions.

Figure 2.6: Maximum throughput using direct/indirect access instructions.

## Chapter 3

## The Breadth-first Vectorization and Parallelization Method

### 3.1 Introduction

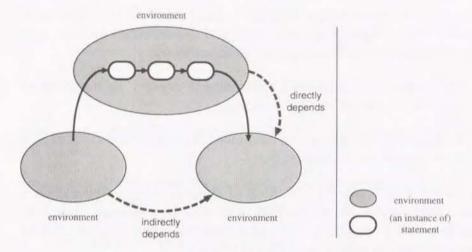

In this chapter, we propose a new method for automatic vectorization and parallelization of recursive procedures and functions<sup>1</sup>. There are a number of recursive algorithms for searching, sorting, manipulation of structured data such as trees. Writing programs with recursive procedure is a natural and neat way to implement such algorithms. Accordingly automatic vectorization and parallelization of recursive procedures enable us to apply these recursive algorithms easily on supercomputers.