### **Characterization of the gate-voltage dependency of input capacitance in a SiC MOSFET**

# Nathabhat Phankong $^{\rm 1a)},$ Tsuyoshi Funaki $^2,$ and Takashi Hikihara $^1$

<sup>1</sup> Kyoto University, Dept. of Electrical Eng., Graduate School of Engineering, Katsura, Kyoto, 615–8510 Japan

<sup>2</sup> Osaka University, Div. Electrical, Electronic, and Information Eng., Graduate School of Engineering, Suita, Osaka, 565–0871 Japan

a) phankong@dove.kuee.kyoto-u.ac.jp

**Abstract:** The charge/discharge phenomenon of capacitance between terminals in a power MOSFET affects on its switching behavior of the device. The input capacitance is composed of the gate-source capacitance  $C_{\rm GS}$  and the gate-drain capacitance  $C_{\rm GD}$ , which vary with gate voltage  $V_{\rm GS}$ . This paper characterizes the relationship between the input capacitance of a SiC MOSFET and the gate voltage with considering the internal device structure. The results give us a clue to understand the switching dynamics of the power MOSFET.

**Keywords:** C-V characteristics, voltage dependency, SiC, MOSFET **Classification:** Electron devices, circuits, and systems

#### References

- D. A. Grant, Power MOSFETs: theory and applications, John Wiley & Sons, New York, 1989.

- [2] B. J. Baliga, Fundamentals of power semiconductor devices, Springer, New York, 2008.

- [3] S. E. Saddow and A. Agarwal, *Advances in silicon carbide processing and applications*, Artech House, Boston, 2004.

- [4] S. M. Sze and K. K. Ng, Physics of semiconductor devices: 3rd edition, John Wiley & Sons, New Jersey, 2007.

- [5] Y. Tsividis, Operation and modeling of the MOS transistor: 2nd edition, McGraw-Hill, New York, 1999.

- [6] A. S. Spinelli, A. Pacelli, and A. L. Lacaita, "Simulation of polysilicon quantization and its effect on n- and p-MOSFET performance," *Solid-State Electron.*, vol. 46, pp. 423–428, 2002.

- [7] T. Funaki, N. Phankong, T. Kimoto, and T. Hikihara, "Measuring terminal capacitance and its voltage dependency for high-voltage power devices," *IEEE Trans. Power Electron.*, vol. 24, no. 6, pp. 1486–1493, June 2009.

- [8] M. Noborio, Y. Kanzaki, J. Suda, and T. Kimoto, "Experimental and theoretical investigations on short-channel effects in 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 9, pp. 1954–1962, Sept. 2005.

[9] R. S. Scott, A. Franz, and J. L. Johnson, "An accurate model for power DMOSFET's including interelectrode capacitance," *IEEE Trans. Power Electron.*, vol. 6, no. 2, pp. 192–198, April 1991.

#### **1** Introduction

Power MOSFETs are practically used in high frequency switching power converter circuits due to fast turn-off capability [1, 2]. Recently, power converters have been requested to operate at high voltage, high-temperature, and fast switching to realize their high performances. However, the limitation to the above requirements is low for the silicon (Si) power devices. To overcome the difficulty, silicon carbide (SiC) power devices have been researched and developed because of its several superior physical characteristics than Si [2, 3].

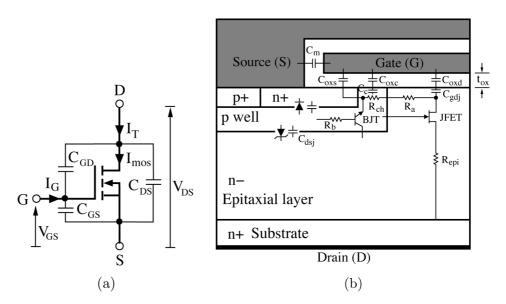

The equivalent capacitance between terminals of a power device affects on its switching behavior, because it must be charged and discharged at the turn-off and turn-on operations. The capacitance in a power device changes nonlinearly with the applied voltage between terminals, because it comprises the depletion capacitance in the device [4]. Then, it is important to characterize the *C-V* characteristics of the SiC MOSFET to estimate its switching performance. Figures 1 (a) and (b) show the equivalent capacitance between terminals and the cross section of the SiC DiMOSFET cell, respectively [2, 3]. The equivalent capacitances are composed of the capacitances  $C_{\rm GS}$ ,  $C_{\rm GD}$ , and  $C_{\rm DS}$ . Here, the  $C_{\rm GS}$  and  $C_{\rm GD}$ , which combine the gate oxide and depletion capacitance, constitute the input capacitance  $C_{\rm ISS}(=C_{\rm GS}+C_{\rm GD})$  [4, 5]. The  $C_{\rm GS}$  mainly depends on the applied gate-source voltage  $V_{\rm GS}$  and drain-source voltage  $V_{\rm DS}$ .

This paper focuses on the gate-source capacitance  $C_{\text{GS}}$ , gate-drain capacitance  $C_{\text{GD}}$ , and input capacitance  $C_{\text{ISS}}$  of power MOSFETs. Then it compares the difference in  $V_{\text{GS}}$  dependency between the SiC MOSFET and the Si MOSFET to estimate the difference in their switching behavior. The constitution of internal parasitic components in the devices are also addressed.

## **2** Interelectrode input capacitance of SiC MOSFET and setup for characterization

This section describes the origin of the interelectrode capacitive components in a SiC MOSFET and discusses their gate-voltage dependency.

#### 2.1 Input capacitance $C_{\rm ISS}$ of SiC MOSFET

Figure 1 (b) illustrates the simplified cross section of one cell structure in a SiC DiMOSFET studied in this paper [2, 3]. SiC DiMOSFET is fabricated to have the structure similar to that of a Si DMOSFET [1]. The main differences between these two devices are the fabrication process and dimensions of p well and  $n^+$  source regions. They are formed by ion implantation for SiC

Fig. 1. Example of a gate-controlled transistor to illustrate parasitic components. (a) Equivalent capacitance between terminals of SiC DiMOSFET. (b) Cross section of a SiC DiMOSFET cell.

DiMOSFET and shallower than a Si DMOSFET formed by diffusion. The various internal parasitic components of the device are superimposed on its cross section in Fig. 1 (b). The physical capacitances residing in the SiC DiMOSFET are composed of the gate oxides and the depletion layer formed in the semiconductor. They are integrated into the equivalent capacitances between terminals of MOSFET  $C_{\text{GS}}$ ,  $C_{\text{GD}}$ , and  $C_{\text{DS}}$ . The  $C_{\text{DS}}$  corresponds to the junction capacitance stemmed by depletion at the junction between the p well and the n<sup>-</sup>-epitaxial layer  $C_{dsj}$ . It largely depends on  $V_{DS}$ . The two other  $C_{\rm GS}$  and  $C_{\rm GD}$  have MOS structures provided with inversion charge injectors. The  $C_{\rm GS}$  is comprised of the gate oxide capacitance between the gate-source electrode  $C_{\rm m}$ , the capacitance between the gate electrode and source n<sup>+</sup> region  $C_{\text{oxs}}$ , the capacitance between the gate electrode and the top surface of the p well region  $C_{\text{oxc}}$ , and the capacitance between the depletion region of the p well region under the gate  $C_{\rm c}$ . The  $C_{\rm c}$  varies depending on  $V_{\rm GS}$ . Though the polysilicon is utilized as gate electrode, it also depletes the applied gate voltage. It is heavily doped, so that its effect on the synthesized capacitance can be neglected [6]. As for  $C_{GD}$ , it is the series connection of the gate-drain oxide capacitance  $C_{\text{oxd}}$  and the drain depletion layer beneath the gate oxide capacitance  $C_{\rm gdj}$ . It varies with gate-drain voltage  $V_{\rm GD} (= V_{\rm GS} - V_{\rm DS})$ . Thus,  $C_{\rm GS}$  and  $C_{\rm GD}$  can be expressed by the capacitive components as

$$\begin{cases} C_{\rm GS} = C_{\rm m} + C_{\rm oxs} + \frac{1}{1/C_{\rm oxc} + 1/C_{\rm c}}, \\ C_{\rm GD} = \frac{1}{1/C_{\rm oxd} + 1/C_{\rm gdj}}. \end{cases}$$

(1)

In this paper, we focus on the characterization of  $C_{\rm ISS}$ , which is sum of the  $C_{\rm GS}$  and  $C_{\rm GD}$ , and the dependency on  $V_{\rm GS}$ .  $C_{\rm m}$ ,  $C_{\rm oxs}$ ,  $C_{\rm oxc}$ , and  $C_{\rm oxd}$ , related to the gate oxide, do not change with the applied voltage.  $C_{\rm c}$  and  $C_{\rm gdj}$ , originated from the depletion layer in the top of p well and n<sup>-</sup>-epitaxial

layer semiconductor respectively, are associated with the depletion region formed in the semiconductor beneath the gate oxide. They can be derived from the depleted space charge  $Q_s$ , which varies as a function of the surface potential of semiconductor  $\psi_s$ . The surface potential  $\psi_s$  is governed by gate voltage [4, 5]. Then, the depleted charge sensitivity to the voltage expresses a differential capacitance  $dQ_s/d\psi_s$ .

#### 2.2 Characterization setup

The interelectrode input capacitance  $C_{\rm ISS}(=C_{\rm GS}+C_{\rm GD})$  of the SiC DiMOS-FET has already been discussed in the section 2.1. Voltage dependence of the capacitance is evaluated by the clarification of the device structure and fabrication. The *C-V* characteristics are precisely measured by a LCR meter with applying the dc bias voltage  $V_{\rm GS}$  and  $V_{\rm DS}$  to the device, through *C-V* measurement fixture in Ref. [7]. In this paper, we measure  $C_{\rm GS}$ ,  $C_{\rm GD}$ , and  $C_{\rm ISS}$  individually.

#### 3 Results and discussion of C-V characteristics

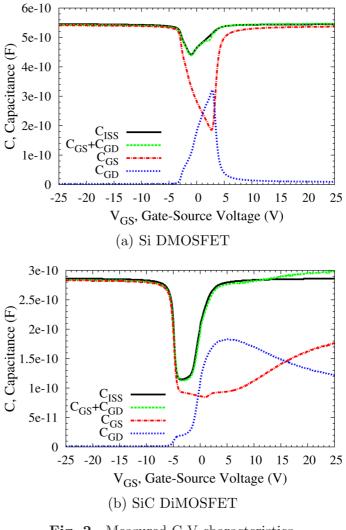

Figures 2 (a) and (b) show the measured C-V characteristics, which illustrate the relationships between the measured  $C_{\rm GS}$ ,  $C_{\rm GD}$ ,  $C_{\rm ISS}$ , and the  $V_{\rm GS}$ , for a 600-V, 2-A Si DMOSFET and a 900-V, 1-A SiC DiMOSFET, respectively. The measurements are performed with setting  $V_{\rm DS} = 0$  V to minimize the depletion region at the top of the n<sup>-</sup>-epitaxial layer ( $C_{\rm gdj}$ ) and to neglect its influence in the equivalent capacitance. When  $V_{\rm GS}$  is swept from -25 V to +25 V, the relationship between the capacitance characteristics and the device structure can be characterized.

When the applied voltage  $V_{\rm GS}$  is lower than  $-5\,{\rm V}$  (Si DMOSFET) and  $-7\,{\rm V}$  (SiC DiMOSFET), the capacitance holds a constant value. This is because the carrier accumulation occurs at the device channel in the top of the p well region. The  $C_{\rm c}$  results in very large capacitance or disappears with conducting condition. Then, the  $C_{\rm GS}$  achieves their highest values. On the other hand, the inversion occurs at the top of the n<sup>-</sup>-epitaxial layer under the gate oxide as the negative  $V_{\rm GS}$  attracts holes to the interface and constitutes depletion layer underneath, then the  $C_{\rm gdj}$  is very small. Thus, the  $C_{\rm GD}$  achieves their lowest values.

When the applied voltage  $V_{\rm GS}$  becomes higher than  $-5 \,\rm V$  (Si DMOSFET) and  $-7 \,\rm V$  (SiC DiMOSFET), the  $C_{\rm GS}$  begins to decrease and reaches to a minimum around  $V_{\rm GS} = 3 \,\rm V$  (Si DMOSFET) and  $= 1 \,\rm V$  (SiC DiMOSFET), because the holes in the p well are repelled from the surface. Thus, the depletion layer appears at the surface of the channel. The inversion at the channel begins to occur with increasing  $V_{\rm GS}$  when  $V_{\rm GS}$  exceeds  $3 \,\rm V$  (Si DMOSFET) and  $1 \,\rm V$  (SiC DiMOSFET). The  $C_{\rm GS}$  increases up to the threshold gate voltage  $V_{\rm T}$  where the  $C_{\rm c}$  disappears by channel conduction. At the same region of  $V_{\rm GS}$ , the electrons are attracted to the top of the JFET region or the  $n^-$ -epitaxial layer under the gate oxide. Thus, it induces the accumulation layer there, and increase of  $C_{\rm gdj}$ . Then, the  $C_{\rm GD}$  becomes large within the

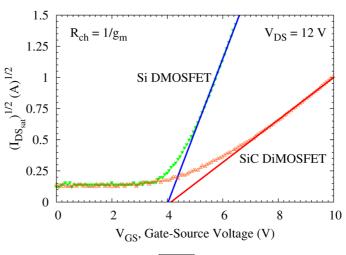

Fig. 3. Measured  $\sqrt{I_{\text{DS}_{\text{sat}}}}$ - $V_{\text{GS}}$  characteristics.

$-3 \text{ V} < V_{\text{GS}} < 3 \text{ V}$  region for the Si DMOSFET and  $-5 \text{ V} < V_{\text{GS}} < 5 \text{ V}$  for the SiC DiMOSFET. The  $V_{\text{T}}$  of the Si DMOSFET is 4.0 V and of the SiC DiMOSFET is 4.1 V, as shown in Fig. 3. The  $V_{\text{T}}$  from measured C-V characteristics corresponds to the  $V_{\text{T}}$  from the measured  $\sqrt{I_{\text{DSsat}}}-V_{\text{GS}}$  char-

acteristics. In Fig. 3, when  $V_{\rm GS} < V_{\rm T}$ , the measured  $\sqrt{I_{\rm DS_{sat}}}$  is kept around  $0.1\,{\rm A}^{1/2}$ . This does not mean leakage current, but is the residual error due to quantization of A/D converter in curve tracer.

The channel conducts when the applied voltage  $V_{\rm GS}$  becomes higher than the  $V_{\rm T}$ . Then, the strong inversion of electrons occurs at the top of the p well region. The  $C_{\rm GS}$  of the Si DMOSFET becomes abruptly large and saturates with increasing  $V_{\rm GS}$ , but the  $C_{\rm GS}$  of the SiC DiMOSFET becomes gradually large and hardly saturates with increasing  $V_{\rm GS}$ . This nonsaturable characteristics stem from the short channel effects [8]. The channel length of the SiC DiMOSFET is approximately equal to  $0.75 \,\mu\text{m}$ . Thus, the channel resistance  $R_{\rm ch}$  [see Fig. 1 (a)] of the Si DMOSFET is much lower than that of the SiC DiMOSFET. At the same region of  $V_{\rm GS}$ , the electrons are attracted to the surface of the JFET region and forms the accumulation layer when  $V_{\rm DS}$  is lower than  $V_{\rm GS}$ . The  $C_{\rm GD}$  of the Si DMOSFET becomes abruptly small and saturates with increasing  $V_{\rm GS}$ , but the  $C_{\rm GD}$  of the SiC DiMOSFET becomes gradually small and hardly saturates with increasing  $V_{\rm GS}$ . The variation of the  $C_{\rm GD}$  associates with the total of the parasitic resistance  $R_{\rm JFET}$ and epitaxial resistance  $R_{epi}$ , which depend on the impurity concentration in  $n^{-}$ -epitaxial layer [1, 9]. These resistances of the Si DMOSFET are higher than that of the SiC DiMOSFET, because the doped impurity concentration of Si DMOSFET is lower than that of SiC DiMOSFET [2, 9]. The  $C_{\rm GD}$ characteristics in Fig. 2 validates this facts.

As the results in Figs. 2 (a) and (b), the  $C_{\rm ISS}$  are obtained as the sum of  $C_{\rm GS}$  and  $C_{\rm GD}$ . In Fig. 2 (b), the measured  $C_{\rm ISS}$  is smaller than the sum of  $C_{\rm GS}$  and  $C_{\rm GD}$ . This can be attributed to the overlap area, between p well and n<sup>-</sup>-epitaxial layer, which appears through the strong inversion and the accumulation of electrons at the top of them individually. The difference of the *C-V* characteristics between the Si DMOSFET and the SiC DiMOSFET is explained by the short channel effects in SiC DiMOSFET and the doping density difference in the n<sup>-</sup>-epitaxial layer.

#### 4 Conclusions

This paper has experimentally shown the relationship between input capacitance  $C_{\rm ISS}$  and gate-voltage of the SiC DiMOSFET with comparison to the Si DMOSFET, precisely. Input capacitance  $C_{\rm ISS}$  results from the sum of the gate-source capacitance  $C_{\rm GS}$  and gate-drain capacitance  $C_{\rm GD}$ . The measured capacitances can be explained along the device structure and the physical phenomenon in the device, which is distinguished as the accumulation, the depletion, and the inversion condition. The dynamics in the switching operation of the devices can be investigated based on these results.

#### Acknowledgments

This research was supported in part by GCOE Program and Environmental Nano-cluster project of the Ministry of Education, Culture, Sports, Sciences and Technology in Japan. Samples of SiC DiMOSFET were produced and

offered by ROHM Company, Ltd. The authors appreciate for their research collaboration.