'Kyoto Ur

| Kyoto University Research Info |                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title                          | Measuring Terminal Capacitance and Its Voltage Dependency for High-Voltage Power Devices                                                                                                                                                                                                                                                                        |

| Author(s)                      | Funaki, Tsuyoshi; Phankong, Nathabhat; Kimoto, Tsunenobu;<br>Hikihara, Takashi                                                                                                                                                                                                                                                                                  |

| Citation                       | IEEE TRANSACTIONS ON POWER ELECTRONICS (2009), 24(5-6): 1486-1493                                                                                                                                                                                                                                                                                               |

| Issue Date                     | 2009-05                                                                                                                                                                                                                                                                                                                                                         |

| URL                            | http://hdl.handle.net/2433/109805                                                                                                                                                                                                                                                                                                                               |

| Right                          | © 2009 IEEE. Personal use of this material is permitted.<br>However, permission to reprint/republish this material for<br>advertising or promotional purposes or for creating new<br>collective works for resale or redistribution to servers or lists,<br>or to reuse any copyrighted component of this work in other<br>works must be obtained from the IEEE. |

| Туре                           | Journal Article                                                                                                                                                                                                                                                                                                                                                 |

| Textversion                    | publisher                                                                                                                                                                                                                                                                                                                                                       |

# Measuring Terminal Capacitance and Its Voltage Dependency for High-Voltage Power Devices

Tsuyoshi Funaki, Member, IEEE, Nathabhat Phankong, Tsunenobu Kimoto, Senior Member, IEEE, and Takashi Hikihara, Member, IEEE

Abstract—The switching behavior of semiconductor devices responds to charge/discharge phenomenon of terminal capacitance in the device. The differential capacitance in a semiconductor device varies with the applied voltage in accordance with the depleted region thickness. This study develops a C-V characterization system for high-voltage power transistors (e.g., MOSFET, insulated gate bipolar transistor, and JFET), which realizes the selective measurement of a specified capacitance from among several capacitances integrated in one device. Three capacitances between terminals are evaluated to specify device characteristics-the capacitance for gate-source, gate-drain, and drain-source. The input, output, and reverse transfer capacitance are also evaluated to assess the switching behavior of the power transistor in the circuit. Thus, this paper discusses the five specifications of a C-V characterization system and its measurement results. Moreover, the developed C-V characterization system enables measurement of the transistor capacitances from its blocking condition to the conducting condition with a varying gate bias voltage. The measured C-Vcharacteristics show intricate changes in the low-bias-voltage region, which reflect the device structure. The monotonic capacitance change in the high-voltage region is attributable to the expansion of the depletion region in the drift region. These results help to understand the dynamic behavior of high-power devices during switching operation.

Index Terms—C-V characteristics, high-voltage power device, terminal capacitance, voltage dependency.

## I. INTRODUCTION

**P**OWER electronics requires high efficiency and versatile power conversion. High-voltage capability is preferable, especially in high-power circuits, to reduce the conduction loss

Manuscript received October 1, 2008; revised February 21, 2009. Current version published May 29, 2009. This work was supported in part by the Ministry of Education, Culture, Sports, Sciences and Technology in Japan, under Grant-in-Aid for Scientific Research 17686024, Grant 18360137, and the 21st Century Centers of Excellence (COE) Program 14213201. Recommended for publication by Associate Editor J. Shen.

T. Funaki is with the Division of Electrical, Electronic and Information Engineering, Graduate School of Engineering, Osaka University, Suita 565-0871, Japan (e-mail: funaki@eei.eng.osaka-u.ac.jp).

N. Phankong is with the Department of Electrical Engineering, Graduate School of Engineering, Kyoto University, Kyoto 615-8510, Japan, and also with the Department of Electrical Engineering, Rajamangala University of Technology Thanyaburi, Thanyaburi 12110, Thailand (e-mail: phankong@dove.kuee.kyoto-u.ac.jp).

T. Kimoto is with the Department of Electronic Science and Engineering, Graduate School of Engineering, Kyoto University, Kyoto 615-8510, Japan (e-mail: kimoto@kuee.kyoto-u.ac.jp).

T. Hikihara is with the Department of Electrical Engineering, Graduate School of Engineering, Kyoto University, Kyoto 615-8510, Japan (e-mail: hikihara@kuee.kyoto-u.ac.jp).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2009.2016566

of large currents. High-frequency switching enables minimization of bulky passive components and provides control functionality. The power switching device is the key component in realizing this; therefore, development efforts focus on a power device with a high breakdown voltage, low forward voltage drop, and fast switching capability [1]–[3].

As a result, an Si-insulated gate bipolar transistor (IGBT) has been developed and improved to meet these requirements [4], [5]. Recently, a superjunction structure of Si power MOS-FET was proposed to realize a high breakdown voltage using a p-n junction and fast switching capability by majority carriers [6]–[8]. In addition to the Si-based power device, wide-bandgap semiconductor power devices have been researched and developed to realize lower loss, higher voltage breakdown, and faster switching with a thin voltage blocking layer. SiC and GaN devices are good examples [3], [7], [9]–[21].

The capacitance between the terminals of a power device affects its switching behavior, because it must be charged and discharged during turn-off and turn-on operations [22], [23]. The capacitance of a power device increases as the thickness of the voltage blocking layer is decreased to minimize conduction resistance. The capacitance varies widely with the applied bias voltage because of depletion in the voltage blocking layer. Therefore, it is necessary to quantify the capacitance between the terminals of the power device as well as the capacitance's voltage dependency. One method is to estimate the capacitance value with finite-element (FE) device simulation and validate it with circuit simulation or experiments [24]-[26]. However, this approach requires a detailed device structure, dimensions, and process parameters. Another method is to characterize the capacitances experimentally. However, there is no commercial product that is able to measure the terminal capacitance of a high-voltage power device by applying the bias voltage up to its rated value. JEDEC [27] and IEC [28] standardized the capacitance measurement between the terminals of a power device with a capacitance bridge, but no actual configuration or circuit topology for the measurements are provided. Elferich et al. [26] measured the C-V characteristics of a power MOSFET and validated the FE device simulation; however, the measurement setup is not clearly described and the applied voltage was low  $(0 \le V_{\rm ds} \le 20, -10 \le V_{\rm gs} \le 0)$ . Therefore, the authors developed a C-V measurement system for high-voltage power devices. Funaki et al. [29] and [30] presented the C-V measurement system for high-voltage power diodes with evolving [31] and clarified the punch-through structure of SiC Schottky barrier diodes (SBDs) from the measured results. This study develops a C-V measurement system for gate-controlled, high-voltage

power devices, e.g., power MOSFET, JFET, and IGBT. There are three terminals in a single device, and five specifications of the measurement circuit are presented to measure the capacitance between gate–source  $(C_{\rm gs})$ , gate–drain  $(C_{\rm gd})$ , and drain–source  $(C_{\rm ds})$ , and to measure input  $(C_{\rm iss})$ , output  $(C_{\rm oss})$ , and reverse transfer  $(C_{\rm rss} = C_{\rm gd})$  capacitances. The capacitances  $C_{\rm gs}$ ,  $C_{\rm ds}$ , and  $C_{\rm ds}$  are measured to clarify the device structure and physical behavior, and  $C_{\rm iss}$ ,  $C_{\rm oss}$ , and  $C_{\rm rss}$  are used to estimate their influence on circuit operation.

The developed measurement circuit can apply a bias voltage between drain and source, and simultaneously to the gate with reference to the source potential. Thus, the circuit can measure the C-V characteristics for both normally OFF and normally ON devices [32]. Also, it enables measurement of the capacitances from the blocking condition to the conducting condition with varying gate bias voltage. For instance, an IGBT is a high-voltage power device, and its measurements illustrate the physical phenomenon occurring in the device, which depends on the applied drain (collector) and gate bias voltage.

# II. CAPACITANCE OF A POWER DEVICE AND MEASUREMENT CIRCUIT

This section examines the makeup of the capacitive component in a power transistor when assuming a planar gate device structure and a vertical drift region-type double-diffusion MOS-FET (VDMOSFET) [3]. Further, the paper discusses a circuit for measuring the capacitance between the power device terminals; the circuit can apply a bias voltage between the drain and the source, and the gate and the source, up to the rated voltage of the device.

#### A. Terminal Capacitance of VDMOSFET

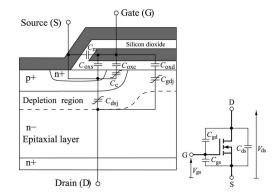

Fig. 1(a) shows the cross section of one cell in a VDMOS-FET chip. The main dielectrics for inducing capacitance in the cell are the depletion layer formed in the semiconductor and the gate oxides. The capacitances arising from the gate oxide have a constant value, irrespective of the voltage applied across it. However, the capacitance arising from the depletion layer, which is formed in the semiconductor, changes with the applied voltage across it, where the capacitance is treated as a differential capacitance dQ/dV. Here, dQ denotes the charge depleted to the incremental bias voltage dV. The capacitance components that reside in the VDMOSFET are integrated into the terminal capacitances  $C_{\rm gs}$ ,  $C_{\rm gd}$ , and  $C_{\rm ds}$ , when seen from the terminal of the electrode in a discrete device, as shown in Fig. 1(b). These terminal capacitances are configured by the capacitive components shown in Fig. 1(a) as

$$\begin{cases} C_{\rm gs} = C_{\rm m} + C_{\rm oxs} + \frac{1}{1/C_{\rm oxc} + 1/C_{\rm c}} \\ C_{\rm gd} = \frac{1}{1/C_{\rm oxd} + 1/C_{\rm gdj}} \\ C_{\rm ds} = C_{\rm dsj}. \end{cases}$$

(1)

Here,  $C_m$  is the capacitance between the gate electrode and the source electrode across the gate oxide,  $C_{\text{oxs}}$  is the capacitance of the gate electrode and source n<sup>+</sup> region,  $C_{\text{oxc}}$  is the capacitance of the gate electrode and the top surface of the p<sup>+</sup> region,  $C_c$  is the capacitance of the depletion region for the p<sup>+</sup>

Fig. 1. Example of a gate-controlled transistor to illustrate device capacitance. (a) Cross section of a VDMOSFET cell. (b) Equivalent capacitances between terminals of VDMOSFET.

region under the gate,  $C_{\text{oxd}}$  is the capacitance of the gate electrode and top surface of the drain region across the gate oxide,  $C_{\text{gdj}}$  is the capacitance of the depletion region for the drain under the gate, and  $C_{\text{dsj}}$  is the capacitance of the depletion region for the drain region for the drain under the source.

The combination of terminal capacitances in the power device determines circuit operation. The input capacitance is the equivalent capacitance when the transistor is seen from the gate terminal to drive the gate; it can be expressed as  $C_{\rm iss} = C_{\rm gs} + C_{\rm gd}$ . The reverse transfer capacitance  $(C_{\rm rss})$  is the same as  $C_{\rm gd}$ . It induces the well-known Miller effect and deteriorates the gate driving response because of the effectively increased capacitance by the multiplier factor of device transconductance [22]. The output capacitance corresponds to the capacitance seen from the drain terminal, and its charge/discharge operation by the drain current affects the main circuit response. It can be expressed as  $C_{\rm oss} = C_{\rm ds} + C_{\rm gd}$ . Thus, five capacitance specifications are needed to characterize the device.

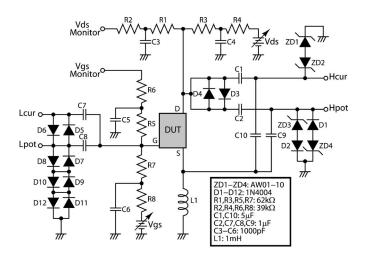

#### B. C<sub>gs</sub> Measurement Circuit

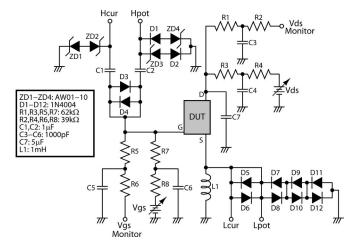

Fig. 2 shows the circuit for measuring  $C_{\rm gs}$ . This circuit can perform four-terminal (Kelvin sense) measurements— $H_{\rm pot}$  and  $L_{\rm pot}$  (for detecting the small ac voltage of the measurement signal) and  $H_{\rm cur}$  and  $L_{\rm cur}$  (for detecting the current of the measurement signal). The four measurement terminals are connected to an *LCR* meter or impedance analyzer.

C1 and C2 block the bias gate voltage, transferring only the ac measurement signal from terminals  $H_{\rm pot}$  and  $H_{\rm cur}$ . These blocking capacitors enable application of the gate–source bias voltage ( $V_{\rm gs}$ ), and the circuit measures the capacitance characteristics related to channel condition, such as accumulation, depletion, and inversion. Moreover, the blocking capacitance enables the measurement of  $C_{\rm gs}$  for a normally ON device by applying a gate voltage and making the device channel operate in the blocking condition. The voltage source  $V_{\rm gs}$  and  $V_{\rm ds}$  impose the dc bias voltage, and the C-V characteristics are measured by sweeping one of them. The ac measurement signal at the source terminal is blocked by L1 (because of its high impedance at the operating frequency); therefore, it is transferred to terminals  $L_{\rm cur}$  and  $L_{\rm pot}$ . L1 shorts the source terminal to dc ground

Fig. 2.  $C_{gs}$  measurement circuit.

Fig. 3.  $C_{\rm gd}$  ( $C_{\rm rss}$ ) measurement circuit.

and establishes the dc bias voltages  $V_{\rm gs}$  and  $V_{\rm ds}$  at the device terminals with reference to ground potential. Diodes D1–D12 and ZD1–ZD4 provide protection. The *RC* circuit at the voltage source input and the monitor output constitute a low-pass filter to block the measurement signal, and apply and measure the dc bias voltage. *C*7 shorts the drain terminal when measuring an ac frequency and blocks dc from the measurement.

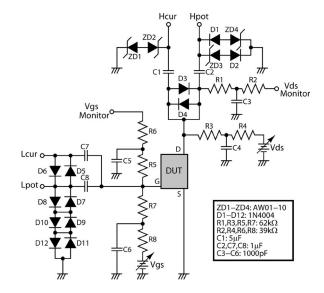

# C. $C_{\rm gd}$ ( $C_{\rm rss}$ ) Measurement Circuit

Fig. 3 shows the circuit diagram for measuring  $C_{\rm gd}$  ( $C_{\rm rss}$ ). This circuit has two groups of blocking capacitors for the drain and source terminals to ensure ground potential at the source terminal. C1 and C2 block the dc bias voltage of  $V_{\rm ds}$ , and C7 and C8 block the dc bias voltage of  $V_{\rm gs}$ . The capacitances transfer the ac measurement signal from  $H_{\rm cur}$  and  $H_{\rm pot}$  to  $L_{\rm cur}$  and  $L_{\rm pot}$ , respectively. The source terminal is directly grounded, and the capacitance component in the device related

Fig. 4.  $C_{ds}$  measurement circuit.

to the source terminal is excluded from the measurement. The dc bias voltages  $V_{\rm ds}$  and  $V_{\rm gs}$  are applied and monitored through the *RC* filter.

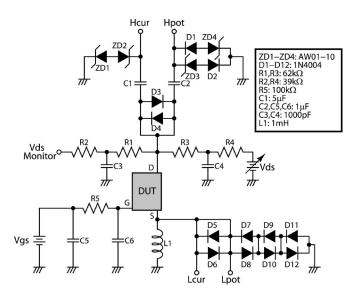

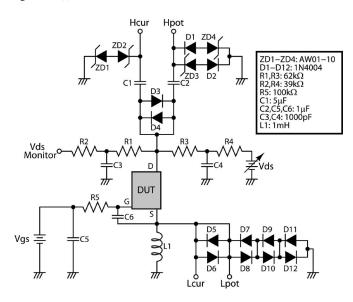

# D. C<sub>ds</sub> Measurement Circuit

Fig. 4 shows the circuit diagram for measuring  $C_{ds}$ . C1 and C2 block the dc bias voltage  $V_{ds}$  and transfer the ac measurement signal from  $H_{cur}$  and  $H_{pot}$  terminals. The dc bias voltages  $V_{ds}$  and  $V_{gs}$  are applied and monitored through the RC filter circuit. Inductor L1, connected to the source terminal, blocks the measurement ac signal and transfers it to  $L_{cur}$  and  $L_{pot}$ . However, it shorts the source terminal to dc ground and helps establish the dc bias voltage with reference to the source terminal. C6, connected to the gate terminal, blocks the dc voltage and establishes the dc potential of the gate terminal, but shorts ac signals to ground. Therefore, the capacitive component connected to the ground.

#### E. C<sub>iss</sub> Measurement Circuit

Fig. 5 shows the circuit diagram for measuring the input capacitance  $C_{iss}$ . This circuit differs from the former measurement circuits in that it measures the combined capacitance of  $C_{gs}$  and  $C_{gd}$ , which have different dc potentials for the drain and source. C1, C2, C7, and C8 block the dc bias voltages of  $V_{ds}$  and  $V_{gs}$ , and transfer the ac measurement signal from  $H_{cur}$  and  $H_{pot}$  to  $L_{cur}$  and  $L_{pot}$ , respectively. The dc bias voltages  $V_{ds}$  and  $V_{gs}$ are applied and monitored through the *RC* filter. Inductor *L*1 shorts dc signals at the source terminal to ground, establishes the reference potential for the dc bias voltage, and blocks the ac measurement signal from shorting to ground. The blocked ac measurement signal is transferred to  $H_{cur}$  and  $H_{pot}$  terminals through the bypass capacitors C9 and C10. Consequentially, the capacitance between the drain and source terminals are eliminated by bypass capacitors C1, C2, C9, and C10.

Fig. 5.  $C_{iss}$  measurement circuit.

Fig. 6.  $C_{\rm oss}$  measurement circuit.

## F. Coss Measurement Circuit

Fig. 6 shows the circuit diagram for measuring the output capacitance  $C_{\rm oss}$ , which is the combined capacitance of  $C_{\rm ds}$  and  $C_{\rm gd}$ —the capacitances have different dc potentials at the gate and source terminals. Capacitors C1 and C2 block the dc bias voltage of  $V_{\rm ds}$  and transfer the ac measurement signal from terminals  $H_{\rm cur}$  and  $H_{\rm pot}$ . The dc bias voltages  $V_{\rm ds}$  and  $V_{\rm gs}$  are applied and monitored through the RC filter. L1 shorts dc signals to ground at the source terminal and establishes the reference potential for the dc bias voltage. It also blocks the ac measurement signal from shorting to ground and helps transfer it to terminals  $L_{\rm cur}$  and  $L_{\rm pot}$ . C6 blocks the dc bias voltage of  $V_{\rm gs}$  from the source and passes the ac measurement signal, which is then transferred to  $L_{\rm cur}$  and  $L_{\rm pot}$  terminals; L1 provides a high ac resistance to ground. C6 bypasses and eliminates the capacitance between the gate and source ( $C_{\rm gs}$ ).

The values of the blocking and bypass capacitances are selected to have sufficiently small impedance relative to the capacitance measurement or elimination ability in the device.

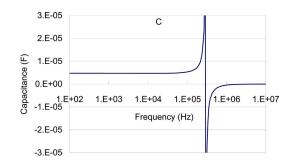

Fig. 7. Frequency characteristics of the blocking capacitor. (4.7  $\mu$ F, 630 V, film-type capacitor,  $C_{\rm s} + R_{\rm s}$  measurement.)

TABLE I TEST RESULTS FOR REFERENCE CAPACITANCE (nF)

| GS   | GD                                                | DS | C <sub>gs</sub> | $C_{gd}$ | C <sub>iss</sub> | $C_{gs}+C_{gd}$ | $C_{ds}$ | $C_{oss}$ | $C_{ds}+C_{gd}$ |  |  |

|------|---------------------------------------------------|----|-----------------|----------|------------------|-----------------|----------|-----------|-----------------|--|--|

|      |                                                   |    | (err%)          | (err%)   | (err%)           | (err%)          | (err%)   | (err%)    | (err%)          |  |  |

| Ca   | Cb                                                | Cc | 11.465          | 21.439   | 32.642           | 32.904          | 33.346   | 54.494    | 54.785          |  |  |

|      |                                                   |    | (4.104)         | (0.603)  | (0.184)          | (0.988)         | (0.036)  | (0.788)   | (0.259)         |  |  |

| Ca   | Cc                                                | Cb | 11.332          | 33.254   | 44.462           | 44.586          | 22.112   | 53.888    | 55.366          |  |  |

|      |                                                   |    | (2.897)         | (0.312)  | (0.205)          | (0.485)         | (2.518)  | (1.892)   | (0.799)         |  |  |

| Cb   | Ca                                                | Cc | 22.022          | 11.018   | 32.715           | 33.040          | 34.053   | 44.304    | 45.071          |  |  |

|      |                                                   |    | (2.100)         | (0.045)  | (0.408)          | (1.406)         | (2.083)  | (0.151)   | (1.578)         |  |  |

| Cb   | Cc                                                | Ca | 21.742          | 33.415   | 55.176           | 55.157          | 11.456   | 43.354    | 44.871          |  |  |

|      |                                                   |    | (0.802)         | (0.171)  | (0.453)          | (0.419)         | (4.023)  | (2.292)   | (1.127)         |  |  |

| Cc   | Ca                                                | Cb | 33.826          | 11.049   | 44.645           | 44.875          | 22.399   | 32.466    | 33.448          |  |  |

|      |                                                   |    | (1.403)         | (0.327)  | (0.618)          | (1.136)         | (3.848)  | (0.356)   | (2.658)         |  |  |

| Cc   | Cb                                                | Ca | 33.592          | 21.376   | 55.248           | 54.968          | 11.505   | 32.155    | 32.881          |  |  |

|      |                                                   |    | (0.701)         | (0.895)  | (0.584)          | (0.075)         | (4.467)  | (1.311)   | (0.918)         |  |  |

| Ca = | Ca = 11.013  nF, Cb = 21.569  nF, Cc = 33.358  nF |    |                 |          |                  |                 |          |           |                 |  |  |

Film-type capacitors are adopted because of their superior highfrequency performance, but high-voltage-blocking large capacitors tend to be bulky and have relatively large effective series inductance (ESL). Fig. 7 shows the frequency characteristics of the capacitance used for blocking high voltages as measured by an impedance analyzer (Agilent 4294A). The largest capacitance used in the measurement circuit has a self-resonant frequency around 300 kHz because of the capacitance and ESL, as shown in Fig. 7. JEDEC [32] suggests that the measurement frequency be low enough to prevent the introduction of the error stemming from parasitic components, and frequencies below 2 MHz are preferred. Therefore, 100 kHz was selected as the measurement frequency.

## III. MEASUREMENT OF C-V CHARACTERISTICS

This section certifies the measured capacitance using the developed capacitance measurement circuit, based on a reference capacitance set whose values are known *a priori*. The measured C-V characteristics of an example device are presented and their features discussed as associated with the device structure and composition.

## A. Certification of the Measurement Circuit

The developed capacitance measurement circuit is connected to a HIOKI 3522 *LCR* meter to quantify the capacitance through measurement terminals  $H_{cur}$ ,  $H_{pot}$ ,  $L_{cur}$ , and  $L_{pot}$ . At the beginning of setting up the experiment, open- and short-circuit

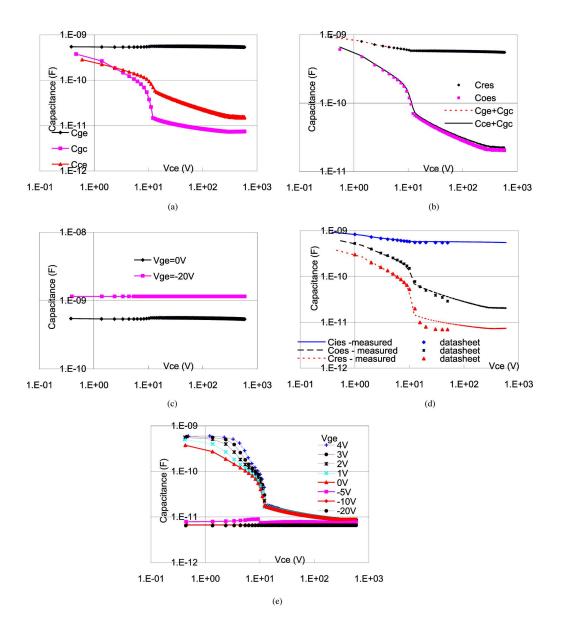

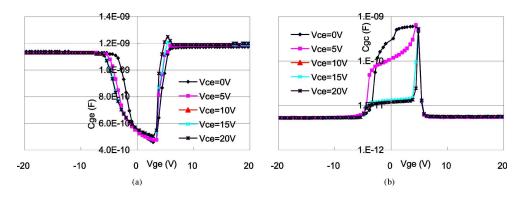

Fig. 8. Measured C-V characteristics for  $V_{ce}$ . (a)  $C_{ge}$ ,  $C_{gc}$ , and  $C_{ce}$  ( $V_{ge} = 0$  V). (b)  $C_{ies}$  and  $C_{oes}$  ( $V_{ge} = 0$  V). (c)  $C_{ge}$  for different  $V_{ge}$ . (d) Comparison between measured value and datasheet. ( $V_{ge} = 0$  V). (e)  $C_{gc}$  ( $C_{res}$ ) for different  $V_{ge}$ .

calibration of the measurement circuit is performed for *LCR* meter operation. Although the developed circuit applies a bias voltage between terminals, a dc short-circuit current flows through the bias voltage source. Therefore, a 0-V dc bias voltage is applied during circuit calibration.

Three capacitances *Ca*, *Cb*, and *Cc*, whose values are given in the margin of Table I and are similar to those of an actual semiconductor device, are used to validate the measurement circuit. The test capacitors are connected in delta to imitate the terminal capacitance of a power device, and six possible combinations of the terminal connection are tested for the five capacitance measurements. The measured values for the respective combinations of reference capacitance connections are given in Table I. The relative percentage error of the actual value is also given in parentheses. The compound capacitances  $C_{\rm gs} + C_{\rm gd}$ and  $C_{\rm ds} + C_{\rm gd}$ , which are, respectively, equivalent to  $C_{\rm iss}$  and  $C_{\rm oss}$ , are also shown in the table for comparison.

The measurement errors for  $C_{\rm gd}$  and  $C_{\rm iss}$  were confirmed as less than 1%—a low error. The error in measuring  $C_{\rm gs}$  tends to become large when  $C_{ds}$  is larger than  $C_{gs}$ . This can be attributed to measurement signal leakage in the blocking inductor L1 and bypass capacitor C7 (see Fig. 2). The opposite effects are found in the measurement of  $C_{\rm ds}$ . The error in  $C_{\rm ds}$  becomes large when  $C_{\rm gs}$  is larger than  $C_{\rm ds}$ . This is attributed to measurement signal leakage in blocking inductor L1 and bypass capacitor C6(see Fig. 4). Thus, the errors of compound capacitance  $C_{\rm gs}$  +  $C_{\rm gd}$  tend to become larger than directly measured  $C_{\rm iss}$ , except when  $C_{\rm ds}$  is small. The error in the measured  $C_{\rm oss}$  becomes large when  $C_{\rm gd}$  is larger than  $C_{\rm ds}$ . Leakage of the measurement signal through L1 in Fig. 6 cannot explain this phenomenon. Hence, this can be attributed to the residue of the measurement signal for the bypass capacitor C6 (see Fig. 6), i.e., the detection terminal for  $C_{ds}$  is directly connected to the *LCR* meter through  $L_{\rm cur}$  and  $L_{\rm pot}$  terminals, but the detection terminal for  $C_{\rm gd}$  is

Fig. 9. Measured C-V characteristics for  $V_{ge}$ . (a)  $C_{ge}$ . (b)  $C_{gc}$  ( $C_{res}$ ).

indirectly connected to the *LCR* meter through *C*6. Therefore, the  $C_{\rm oss}$  measurement circuit is amenable to  $C_{\rm gd}$  value, and the errors of directly measured  $C_{\rm oss}$  tend to become larger than the compound capacitance  $C_{\rm ds} + C_{\rm gd}$  when  $C_{\rm gd}$  is small.

The extracted error falls within 5% using the measurement circuit parameters, as shown in Figs. 2–7. This error can be reduced by increasing the value of the blocking and bypassing elements, but the accuracy given in Table I is sufficient to characterize the device because of the dispersion of the characteristics among devices.

## B. Measured Results

The measured C-V characteristics are exemplified here by considering a planar gate IGBT with a 600-V-rated voltage (IRG4BC20S) as an example, and the relationship of the capacitance characteristics to the device structure is discussed.

Fig. 8(a) illustrates the relationship of the measured  $C_{ge}(=$  $C_{\rm gs}$ ),  $C_{\rm gc} (= C_{\rm gd})$ , and  $C_{\rm ce} (= C_{\rm ds})$  to the collector voltage with  $V_{

m ge} = 0$  V.  $C_{

m ge}$  is larger than  $C_{

m ce}$  and  $C_{

m gc}$  because of the closely spaced gate and emitter electrodes at the surface of the device. It barely changes with the applied  $V_{\rm ce}$ , because  $V_{\rm ce}$ does not affect the expansion of the depletion region across the gate and emitter. Also, depletion in the drift layer depends on  $V_{\rm ce}$ . Therefore,  $C_{\rm ce}$  and  $C_{\rm gc}$  decrease with increase in  $V_{\rm ce}$  in accordance with the expansion of the depletion region. There are irregular capacitance changes around  $V_{\rm ce} = 10$  V, which can be attributed to the transition of the expanding depletion region from the JFET region of the planar gate IGBT to the entire drift region. The decrease of the capacitance in  $C_{ce}$  and  $C_{\rm gc}$  stops around  $V_{\rm ce} = 300$  V, which indicates the termination of the depletion region expansion in the drift layer because of the punch-through structure of the device.

Fig. 8(b) illustrates the directly measured  $C_{\rm ies}(=C_{\rm iss})$ and  $C_{\rm oes}(=C_{\rm oss})$  and the calculated  $C_{\rm ies}(=C_{\rm ge}+C_{\rm gc})$  and  $C_{\rm oes}(=C_{\rm ce}+C_{\rm ge})$  from the measured  $C_{\rm ce}, C_{\rm ge}$ , and  $C_{\rm gc}$ . The respective results coincide, validating the adequacy of the measured results. Fig. 8(d) compares the measured ( $C_{\rm ies}, C_{\rm oes}, C_{\rm res}$ ) and datasheet values. The datasheet provides capacitances up to  $V_{\rm ge} = 50$  V and validates the measured capacitances.

Fig. 8(c) shows  $C_{\rm ge}$  to  $V_{\rm ce}$  for different  $V_{\rm ge}$ . The accumulation of charge (holes) occurs at the device channel and results in a decrease in  $C_{\rm c}$ , as shown in Fig. 1(a), when a gate voltage of  $V_{\rm ge} = -20$  V is applied. Capacitance  $C_{\rm ge}$  becomes larger

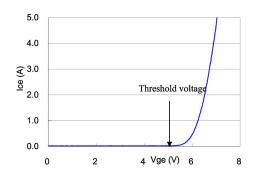

Fig. 10. Measured  $V_{ge}$ - $I_{ce}$  characteristics.

than the depleted condition of the channel by the time  $V_{\rm ge} =$ 0 V. This phenomenon is shown clearly in Fig. 9(a), where  $C_{

m ge}$  is measured to  $V_{

m ge}$  and  $V_{

m ce}$  is changed as the parameter. Capacitance  $C_{ge}$  begins to decrease when  $V_{ge}$  becomes higher than -6 V and it reaches a minimum around  $V_{ge} = 3$  V. This indicates the depletion of the accumulated charge (holes) at the channel with increase in gate voltage  $V_{ge}$ . The inversion at the channel begins to occur with increasing gate voltages when  $V_{\rm ge}$  exceeds 3 V, and  $C_{\rm ge}$  increases to the threshold gate voltage. The threshold gate voltage of this device is 5 V, as shown in Fig. 10, and the channel conducts for a higher gate voltage. Fig. 8(e) shows  $C_{\text{ge}}$  ( $C_{\text{res}}$ ) to  $V_{\text{ce}}$  for different  $V_{\text{ge}}$ . The accumulation phenomenon is also seen at the top of the JFET region in a planar device [around  $C_{\rm gdj}$  in Fig. 1(a)], and  $C_{\rm gc}$ varies with  $V_{\rm ge}$  especially in the low  $V_{\rm ce}$  region ( $V_{\rm ce} < 10$  V). It also shows that negative  $V_{\rm ge}$  reduces  $C_{\rm gc}$ . This phenomenon is clearly confirmed in Fig. 9(b), where  $C_{\rm gc}$  is measured at  $V_{\rm ge}$ and  $V_{\rm ce}$  is the parameter being changed. The accumulation at the top of the JFET region tends to occur when voltages with different polarities are applied across that part, resulting in an increase in  $C_{\rm gdj}$  [see Fig. 1(c)]. Then,  $C_{\rm gc}$  becomes large for low  $V_{ce}$  within the  $-6 \text{ V} < V_{ge} < 3 \text{ V}$  region.

The capacitance measurement is by no means restricted to merely determining the capacitance between terminals, but it can also clarify a wide variety of physical phenomenon occurring in the device.

#### **IV. CONCLUSION**

The capacitances between the terminals of a power device are important in understanding the dynamic behavior of the device, such as its switching operation. The device capacitances are not constant and change with the voltage applied between the terminals. Therefore, a C-V characterization system for gate-controlled power devices was developed in this study. Five measurement circuits were proposed to measure the three combinations of capacitances between the device terminals, and three combinations of device capacitance for circuit operation. The adequacy of the proposed measurement system was verified using a reference capacitance and the factor of error was discussed. The developed capacitance characterization system can measure capacitance from the blocking condition to the conducting condition while changing the gate bias voltage. The variation of the depletion and accumulation condition in the device was reflected in the device capacitance. The measured capacitance explained the device structure and the physical phenomenon occurring in the device.

#### ACKNOWLEDGMENT

The authors thank to Prof. J. C. Balda from the University of Arkansas for discussions regarding C-V measurements.

#### REFERENCES

- [1] B. J. Baliga, Modern Power Devices. New York: Wiley, 1987.

- [2] B. J. Baliga, *Power Semiconductor Devices*. Boston, MA: PWS-Kent, 1995.

- [3] B. J. Baliga, Silicon Carbide Power Devices. Singapore: World Scientific, 2006, pp. 15–33.

- [4] B. J. Baliga, M. S. Adler, R. P. Love, P. V. Gray, and N. D. Zommer, "The insulated gate transistor: A new three-terminal MOS-controlled bipolar power device," *IEEE Trans. Electron Devices*, vol. ED-31, no. 6, pp. 821– 828, Jun. 1984.

- [5] K. Fujii, P. Koellensperger, and R. W. De Doncker, "Characterization and comparison of high blocking voltage IGBTs and IEGTs under hard- and soft-switching conditions," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 172–179, Jan. 2008.

- [6] X.-B. Chen and J. K. O. Sin, "Optimization of the specific on-resistance of the COOLMOS," *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 344– 348, Feb. 2001.

- [7] Z. Liang, B. Lu, J. D. van Wyk, and F. C. Lee, "Integrated CoolMOS FET/SiC-diode module for high performance power switching," *IEEE Trans. Power Electron.*, vol. 20, no. 3, pp. 679–686, May 2005.

- [8] Y. Chen, Y. C. Liang, and G. S. Samudra, "Design of gradient oxide bypassed superjunction power MOSFET devices," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1303–1310, Jul. 2007.

- [9] J. L. Hudgins, G. S. Simin, E. Santi, and M. A. Khan, "An assessment of wide bandgap semiconductors for power devices," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 907–914, May 2003.

- [10] A. R. Hefner, R. Singh, J. Lai, D. Berning, S. Bouche, and C. Chapuy, "SiC power diodes provide breakthrough performance for a wide range of applications," *IEEE Trans. Power Electron.*, vol. 16, no. 2, pp. 273–280, Mar. 2001.

- [11] B. Ozpineci and L. M. Tolbert, "Characterization of SiC Schottky diodes at different temperatures," *IEEE Power Electron. Lett.*, vol. 1, no. 2, pp. 54–57, Jun. 2003.

- [12] Y. Jian, L. Zhenxian, and J. D. van Wyk, "High temperature embedded SiC chip module (ECM) for power electronics applications," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 392–398, Mar. 2007.

- [13] T. Funaki, J. Balda, J. Junghans, A. Kashyap, A. Mantooth, F. Barlow, T. Kimoto, and T. Hikihara, "Power conversion with SiC devices at extremely high ambient temperatures," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1321–1329, Jul. 2007.

- [14] T. Funaki, J. C. Balda, J. Junghans, A. S. Kashyap, F. D. Barlow, H. A. Mantooth, T. Kimoto, and T. Hikihara, "SiC JFET dc characteristics under extremely high ambient temperatures," *IEICE Electron. Exp.*, vol. 1, no. 17, pp. 523–527, 2004.

- [15] T. Funaki, J. C. Balda, J. Junghans, A. Jangwanitlert, S. Mounce, F. D. Barlow, H. A. Mantooth, T. Kimoto, and T. Hikihara, "Switching characteristics of SiC JFET and Schottky diode in high-temperature dc–dc power converters," *IEICE Electron. Exp.*, vol. 2, no. 3, pp. 97–102, 2005.

- [16] P. Shah, B. Geil, M. Ervin, T. Griffin, S. Bayne, K. Jones, and T. Oldham, "Advanced operational techniques and pn-pn-pn structures for highpower silicon carbide gate turn-off thyristors," *IEEE Trans. Power Electron.*, vol. 17, no. 6, pp. 1073–1079, Nov. 2002.

- [17] G. Spiazzi, S. Buso, M. Citron, M. Corradin, and R. Pierobeon, "Performance evaluation of a Schottky SiC power diode in a boost PFC application," *IEEE Trans. Power Electron.*, vol. 18, no. 6, pp. 1249–1253, Nov. 2003.

- [18] T. R. McNutt, A. R. Hefner, H. A. Mantooth, J. Duliere, D. W. Berning, and R. Singh, "Silicon carbide PiN and merged PiN Schottky power diode models implemented in the saber circuit simulator," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 573–581, May 2004.

- [19] T. McNutt, A. Hefner, A. Mantooth, D. Berning, and R. Sei-Hyung, "Silicon carbide power MOSFET model and parameter extraction sequence," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 353–363, Mar. 2007.

- [20] A. M. Abou-Alfotouh, A. V. Radun, H. R. Chang, and C. Winterhalter, "A 1-MHz hard-switched silicon carbide DC–DC converter," *IEEE Trans. Power Electron.*, vol. 21, no. 4, pp. 880–889, Jul. 2006.

- [21] T. Nomura, M. Masuda, N. Ikeda, and S. Yoshida, "Switching characteristics of GaN HFETs in a half bridge package for high temperature applications," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 692–697, Mar. 2008.

- [22] J. M. Miller, "The dependence of the amplification constant and internal plate circuit resistance of a three-electrode vacuum tube upon the structural dimensions," *Proc. IRE*, vol. 8, pp. 64–72, 1920.

- [23] S. Pittet and A. Rufer, "The equivalent electron density concept for static and dynamic modeling of the IGBT base in soft- and hard-switching applications," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2223– 2233, Nov. 2007.

- [24] T. Biondi, G. Greco, M. C. Allia, S. F. Liotta, G. Bazzano, and S. Rinaudo, "Distributed modeling of layout parasitics in large-area high-speed silicon power devices," *IEEE Trans. Power Electron.*, vol. 22, no. 5, pp. 1847– 1856, Sep. 2007.

- [25] S. Rael and B. Davat, "A physics-based modeling of interelectrode MOS capacitances of power MOSFET and IGBT," *IEEE Trans. Power Electron.*, vol. 23, no. 5, pp. 2585–2594, Sep. 2008.

- [26] R. Elferich, T. Lopez, and N. Koper, "Accurate behavioural modeling of power MOSFETs based on device measurements and FE-simulations," presented at the 2005 Eur. Conf. Power Electron. Appl., Dresden, Germany, Sep. 11–14, Paper 0708.

- [27] JESD6 Measurement of Small Values of Transistor Capacitance, JEDEC Standard, 1967.

- [28] Semiconductor Devices, IEC Standard 60747, 2006.

- [29] T. Funaki, S. Matsuzaki, T. Kimoto, and T. Hikihara, "Characterization of punch-through phenomenon in SiC-SBD by capacitance-voltage measurement at high reverse bias voltage," *IEICE Electron. Exp.*, vol. 3, no. 16, pp. 379–384, 2006.

- [30] T. Funaki, T. Kimoto, and T. Hikihara, "Evaluation of high frequency switching capability of SiC Schottky barrier diode, based on junction capacitance model," *IEEE Trans. Power Electron.*, vol. 23, no. 5, pp. 2602– 2611, Sep. 2008.

- [31] Impedance Measurement Handbook. Agilent Technol., Santa Clara, CA, AN-5950-3000, Jul. 2006, pp. 27–28.

- [32] T. Funaki, T. Kimoto, and T. Hikihara, "Evaluation of capacitance-voltage characteristics for high voltage SiC-JFET," *IEICE Electron. Exp.*, vol. 4, no. 16, pp. 517–523, 2007.

**Tsuyoshi Funaki** (S'92–M'00) received the B.E. and M.E. degrees in electrical engineering and the Ph.D. degree from Osaka University, Suita, Japan.

He joined Osaka University as a Research Associate in 1994 and became an Assistant Professor in 2001 and a Professor in 2008. In 2002, he joined Kyoto University, Kyoto, Japan, as an Associate Professor. From 2004 to 2005, he was a Visiting Scholar in the Department of Electrical Engineering, University of Arkansas, Fayetteville, where he was engaged in collaborative research on SiC devices and their application.

Prof. Funaki is a member of the Institute of Electrical Engineers of Japan, the Institute of Electronics, Information and Communication Engineers of Japan, the Institute of Systems, Control and Information Engineers, the Society of Atmospheric Electricity of Japan, and the Institution of Engineering and Technology, London, U.K. **Nathabhat Phankong** was born in Yala, Thailand, on May 18, 1975. He received the B.Eng. and M.Eng. degrees in electrical engineering from King Mongkut's University of Technology Thonburi, Bangkok, Thailand, in 1999 and 2003, respectively. He is currently working toward the Ph.D. degree at the Power Device Modeling Group, Kyoto University, Kyoto, Japan.

He is also an Instructor in the Department of Electrical Engineering, Rajamangala University of Technology Thanyaburi, Thanyaburi, Thailand. His current research interests include semiconductor device modeling, power electronic system design, and characteristics of power devices.

Mr. Phankong is a member of the Institute of Electrical Engineers of Japan and the Institute of Electronics, Information and Communication Engineers of Japan.

**Tsunenobu Kimoto** (M'03–SM'06) received the B.E. and M.E. degrees in electrical engineering and the Ph.D. degree from Kyoto University, Kyoto, Japan, in 1986, 1988, and 1996, respectively.

In April 1988, he was with Sumitomo Electric Industries, Ltd., where he was engaged in research on amorphous Si solar cells and semiconducting diamond material. In 1990, he was a Research Associate at Kyoto University. From September 1996 to August 1997, he was a Visiting Scientist at Linköping University, Sweden, where he was involved in fast epitaxy of SiC and highvoltage Schottky diodes. He is currently a Professor in the Department of Electronic Science and Engineering, Kyoto University. His current research interests include SiC epitaxial growth, optical and electrical characterization, ion implantation, MOS physics, and high-voltage devices. He has also been involved in nanoscale Si devices and novel materials for nonvolatile memory. He has authored or coauthored more than 250 papers in scientific journals and international conference proceedings.

Prof. Kimoto is a member of the Japan Society of Applied Physics, the Institute of Electronics, Information and Communication Engineers of Japan, and the Institute of Electrical Engineers of Japan. **Takashi Hikihara** (S'84–M'88) was born in Kyoto, Japan, in 1958. He received the B.E. degree from the Kyoto Institute of Technology, Kyoto, Japan, in 1982, and the M.E. and Ph.D. degrees from Kyoto University, Kyoto, in 1984, and 1990, respectively.

From 1987 to 1997, he was with the faculty of the Department of Electrical Engineering, Kansai University, Suita, Japan. From 1993 to 1994, he was a Visiting Researcher at Cornell University. In 1997, he joined the Department of Electrical Engineering, Kyoto University, where he is currently a Professor. He is an Associate Editor of *European Journal of Control* and the Vice Editor of the journal *Systems Control and Information*. His current research interests include nonlinear science and its application. He is also involved in system control and nanotechnology.

Prof. Hikihara is a member of the Institution of Engineering and Technology, London, U.K., the Institute of Electronics, Information and Communication Engineers of Japan, the Institute of Electrical Engineers of Japan, the American Physics Society, the Society for Industrial and Applied Mathematics, etc.