W&M ScholarWorks

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2020

# Hardware-Assisted Security Mechanisms On Arm-Based Multi-Core Processors

Shengye Wan William & Mary - Arts & Sciences, simonsywan@gmail.com

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Wan, Shengye, "Hardware-Assisted Security Mechanisms On Arm-Based Multi-Core Processors" (2020). *Dissertations, Theses, and Masters Projects.* Paper 1616444331. http://dx.doi.org/10.21220/s2-8x2h-rm46

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

Hardware-Assisted Security Mechanisms on ARM-Based Multi-Core Processors

Shengye Wan

Nanchang, China

Master of Science, College of William & Mary, 2016 Bachelor of Engineering, Huazhong University of Science and Technology, 2014

> A Dissertation presented to the Graduate Faculty of College of William & Mary in Candidacy for the Degree of Doctor of Philosophy

> > Department of Computer Science

College of William & Mary August 2020

$\bigodot$  Copyright by Shengye Wan 2020

#### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Shengye Wan

Approved by the Committee, August 2020

Committee Chair Kun Sun, Adjunct Associate Professor, Computer Science College of William & Mary

Gang Zhou, Professor, Computer Science College of William & Mary

Qun Li, Professor, Computer Science College of William & Mary

Xu Liu, Assistant Professor, Computer Science College of William & Mary

Ning Zhang, Assistant Professor, Computer Science and Engineering Washington University in St. Louis

#### ABSTRACT

During the last decade, Trusted Execution Environment (TEE) provided by ARM TrustZone had become one of the most popular techniques to build security on mobile devices. On a TrustZone-enabled system, the software can execute in either Secure World (trusted) and Normal World (untrusted). Meanwhile, along with the expeditious development of TrustZone technology, the security of TEE is also challenged by dealing with more and more on-board hardware and in-TEE applications. In this dissertation, we explicitly study the security of ARM TrustZone technology with the latest ARM architecture in three aspects.

First, we study the security of the TrustZone-assisted asynchronous introspection. Previously, asynchronous introspection mechanisms have been developed in the secure world to detect security policy violations in the normal world. However, we identify a new normal-world evasion attack that can defeat the asynchronous introspection by removing the attacking traces in parallel from one core when the secure-world checking is performing on another core. As the countermeasure, we propose a trustworthy asynchronous introspection mechanism called SATIN, which can effectively prevent evasion attacks with a minor system overhead by increasing the attackers' evasion time cost and decreasing the defender's inspecting time.

Second, we design an ARM TrustZone-assisted connectivity mechanism, called TZNIC, to enable the secure world's access to network even at the presence of a malicious OS. TZNIC deploys two NIC drivers, one secure-world driver, and one normal-world driver, that multiplex one physical NIC. We utilize the ARM TrustZone high-privilege to protect the secure-world driver, and further resolve several challenges about sharing one set of hardware peripheral between two isolated software environments. The evaluation shows that TZNIC can provide a reliable network channel for the secure world.

Third, we investigate the memory-safety of secure-world trusted applications. Though the existing TrustZone hardware focuses on protecting the application's confidentiality and integrity from malicious accesses of the normal world, there is little the secure world can do when the inside applications contain vulnerabilities and are further exploited by the normal world. To enhance the security of the secure-world application, we propose RusTEE, a TrustZone-based SDK that enables the development of trusted applications in the memory-safe programming language Rust. RusTEE can utilize the built-in security checks of Rust to mitigate all memorycorruption vulnerabilities for trusted applications. Besides, we enhance the trusted application's security by enforcing the memory-safety on its invocations of systemservice APIs and cross-world communication channels.

## TABLE OF CONTENTS

| Acknowledgments                                                 |            |                                                     | vi   |  |

|-----------------------------------------------------------------|------------|-----------------------------------------------------|------|--|

| De                                                              | Dedication |                                                     |      |  |

| Li                                                              | st of      | Tables                                              | viii |  |

| Li                                                              | st of      | Figures                                             | ix   |  |

| 1                                                               | Intr       | oduction                                            | 2    |  |

|                                                                 | 1.1        | Problem Statement                                   | 4    |  |

|                                                                 | 1.2        | Contributions                                       | 5    |  |

|                                                                 | 1.3        | Dissertation Organization                           | 7    |  |

| 2                                                               | ARI        | M TrustZone Background                              | 9    |  |

|                                                                 | 2.1        | Security Model                                      | 9    |  |

|                                                                 | 2.2        | Memory Model                                        | 10   |  |

|                                                                 | 2.3        | Interrupt Model                                     | 11   |  |

|                                                                 | 2.4        | ARM Multi-Core Processor                            | 12   |  |

| 3 SATIN: A Secure and Trustworthy Asynchronous Introspection of |            |                                                     |      |  |

|                                                                 | Core       | e ARM Processors                                    | 13   |  |

|                                                                 | 3.1        | Introduction                                        | 13   |  |

|                                                                 | 3.2        | TZ-Evader: Evasion Attacks on Multi-core Processors | 17   |  |

|                                                                 |            | 3.2.1 Assumptions and Threat Model                  | 17   |  |

|     | 3.2.2 | New Attack Surface                                        | <br>17 |

|-----|-------|-----------------------------------------------------------|--------|

|     |       | 3.2.2.1 Probing CPU Core's Running State                  | <br>17 |

|     |       | 3.2.2.2 Race Condition on Multi-core Processors           | <br>20 |

|     | 3.2.3 | ΓZ-Evader Design                                          | <br>21 |

|     |       | 3.2.3.1 KProber-I                                         | <br>22 |

|     |       | 3.2.3.2 KProber-II                                        | <br>22 |

| 3.3 | TZ-E  | der Evaluation                                            | <br>23 |

|     | 3.3.1 | ΓZ-Evader Implementation                                  | <br>23 |

|     |       | 3.3.1.1 Kernel-Level Prober Implementation                | <br>23 |

|     |       | 3.3.1.2 Sample Kernel-Level Attack                        | <br>24 |

|     | 3.3.2 | ΓZ-Evader Evaluation                                      | <br>25 |

|     |       | 3.3.2.1 Introspection Time Delay                          | <br>25 |

|     |       | 3.3.2.2 Attack Time Delay                                 | <br>26 |

|     | 3.3.3 | Race Condition Analysis                                   | <br>28 |

| 3.4 | SATI  | Secure Asynchronous Introspection                         | <br>29 |

|     | 3.4.1 | Asynchronous Introspection Challenges                     | <br>29 |

|     |       | 3.4.1.1 Challenge 1: Performance vs. Detection Accuracy . | <br>29 |

|     |       | 3.4.1.2 Challenge 2: Evasion Attack                       | <br>30 |

|     | 3.4.2 | Integrity Checking Module                                 | <br>31 |

|     | 3.4.3 | Self Activation Module                                    | <br>32 |

|     | 3.4.4 | Multi-Core Collaboration                                  | <br>33 |

| 3.5 | SATI  | Evaluation                                                | <br>35 |

|     | 3.5.1 | SATIN Implementation                                      | <br>35 |

|     |       | 3.5.1.1 Self Activation Module                            | <br>35 |

|     |       | 3.5.1.2 Integrity Checking Module                         | <br>35 |

|     | 3.5.2 | SATIN Evaluation                                          | <br>36 |

|     |       | 3.5.2.1 Defeating TZ-Evader                               | <br>36 |

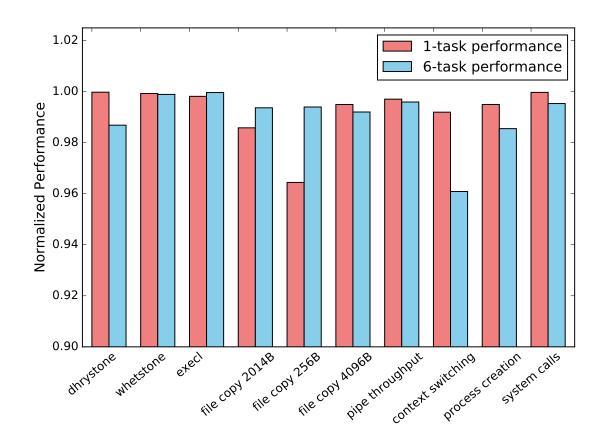

|   |     |          | 3.5.2.2 SATIN Overhead                                    | 37 |

|---|-----|----------|-----------------------------------------------------------|----|

|   |     | 3.5.3    | SATIN Security Analysis                                   | 38 |

|   |     |          | 3.5.3.1 SATIN's Security                                  | 38 |

|   |     |          | 3.5.3.2 SATIN Capability                                  | 38 |

|   | 3.6 | Work     | Conclusion                                                | 39 |

| 4 | TZN | JIC· To  | owards Providing Reliable Network for ARM TrustZone-Based |    |

| т |     | lication |                                                           | 40 |

|   | 4.1 |          |                                                           | 40 |

|   |     |          |                                                           |    |

|   | 4.2 |          | 0                                                         | 44 |

|   | 4.3 |          |                                                           | 45 |

|   |     | 4.3.1    | Threat Model and Assumptions                              | 45 |

|   |     | 4.3.2    | Key Idea and Challenges                                   | 45 |

|   |     | 4.3.3    | Our Solution                                              | 47 |

|   | 4.4 | TZNI     | C Design                                                  | 49 |

|   |     | 4.4.1    | Secure Receiving Module                                   | 49 |

|   |     | 4.4.2    | Secure Transmitting Module                                | 51 |

|   |     | 4.4.3    | Secure Switching                                          | 52 |

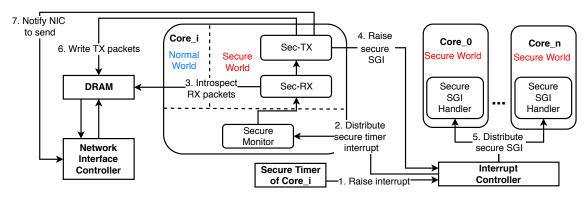

|   |     | 4.4.4    | TZNIC Workflow                                            | 53 |

|   | 4.5 | TZNI     | C Evaluation                                              | 54 |

|   |     | 4.5.1    | System Implementation                                     | 54 |

|   |     |          | 4.5.1.1 Secure World Initialization                       | 54 |

|   |     |          | 4.5.1.2 Sec-RX Implementation                             | 55 |

|   |     |          | 4.5.1.3 Sec-TX Implementation                             | 56 |

|   |     | 4.5.2    | System Evaluation                                         | 57 |

|   |     |          | 4.5.2.1 Size of TCB                                       | 57 |

|   |     |          | 4.5.2.2 Communication Connectivity                        | 58 |

|   |     |          | ·                                                         |    |

|   |     |        | 4.5.2.3 Sec-RX Overhead                           | 59 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 4.5.3  | Sec-TX Overhead                                   | 62 |

|   |     | 4.5.4  | Portability of TZNIC                              | 63 |

|   | 4.6 | Work   | Conclusion                                        | 65 |

| 5 | Rus | TEE: I | Developing Memory-Safe ARM TrustZone Applications | 66 |

|   | 5.1 | Introd | luction                                           | 66 |

|   | 5.2 | Work   | Background                                        | 68 |

|   |     | 5.2.1  | GlobalPlatform TEE Specification                  | 68 |

|   |     | 5.2.2  | Rust                                              | 70 |

|   | 5.3 | Motiv  | ation and Challenges                              | 71 |

|   |     | 5.3.1  | Motivation                                        | 71 |

|   |     | 5.3.2  | Challenges                                        | 73 |

|   | 5.4 | RusT   | EE Design                                         | 74 |

|   |     | 5.4.1  | Assumptions and Threat Model                      | 74 |

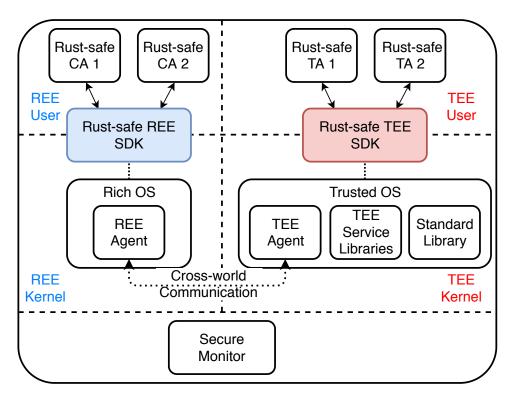

|   |     | 5.4.2  | Overview                                          | 74 |

|   |     | 5.4.3  | Secure System-service APIs                        | 76 |

|   |     | 5.4.4  | Secure Cross-world Communication                  | 80 |

|   | 5.5 | RusT   | EE Evaluation                                     | 82 |

|   |     | 5.5.1  | System Implementation                             | 82 |

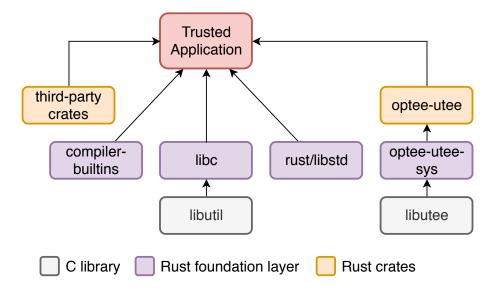

|   |     |        | 5.5.1.1 Porting Rust into OP-TEE                  | 83 |

|   |     |        | 5.5.1.2 Binding OP-TEE'S TEE Internal APIs        | 84 |

|   |     |        | 5.5.1.3 REE and Examples                          | 85 |

|   |     | 5.5.2  | System Evaluation                                 | 86 |

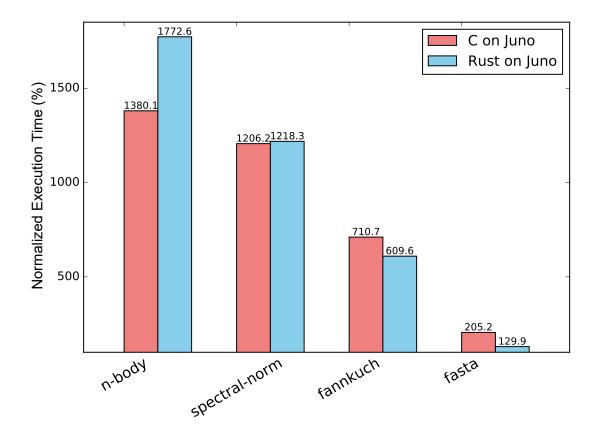

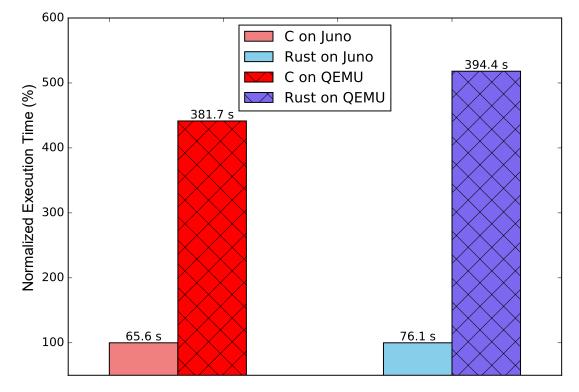

|   |     |        | 5.5.2.1 Language-wise Overhead                    | 87 |

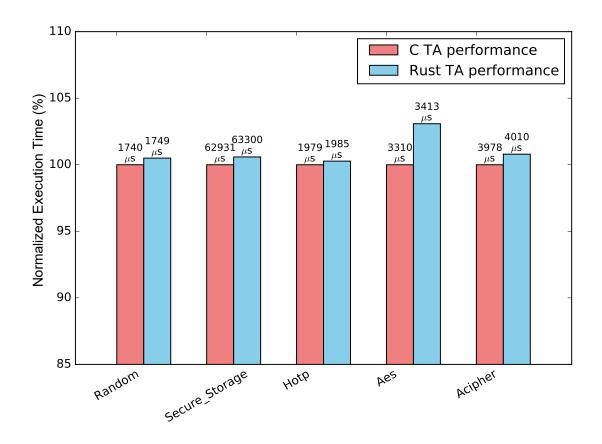

|   |     |        | 5.5.2.2 Enhanced APIs' Overhead                   | 90 |

|   | 5.6 | Work   | Conclusion                                        | 91 |

| 6  | 6 Related Work                         |         |                                |     |  |

|----|----------------------------------------|---------|--------------------------------|-----|--|

|    | 6.1 High-Privileged Operating Modes    |         |                                |     |  |

|    | 6.2 Introspection Mechanisms           |         |                                |     |  |

|    |                                        | 6.2.1   | Asynchronous Introspection     | 93  |  |

|    |                                        | 6.2.2   | Synchronous Introspection      | 94  |  |

|    | 6.3 TrustZone-Based Network Connection |         |                                |     |  |

|    |                                        | 6.3.1   | Rust-assisted Systems          | 95  |  |

| 7  | Con                                    | clusion | and Future Research Directions | 97  |  |

| Vi | ta                                     |         |                                | 116 |  |

#### ACKNOWLEDGMENTS

This dissertation is written with the help of many influential people to me. I express my gratitude to all of them.

First and foremost, I would like to thank my advisor Dr. Kun Sun. Without his kindly encouragement, I would not be able to start pursuing my research career. He always supports me in working on my research interests and advises me with plenty of patience.

Next, I would like to thank Dr. Ning Zhang and Dr. Yue Li. They both share much valuable research experience with me and guide me to walk through the tough time in my early days.

I would also like to thank my committee members Dr. Qun Li, Dr. Xu Liu, and Dr. Gang Zhou, for their insightful suggestions on my research projects.

I thank my dear friends, Jing Tian, Jianhua Sun, Qijue Wang, and Xiao Liu, for their help and companionship in my Ph.D. career.

Finally, I would like to thank my family members, my father, my grandmother, and my sister, who support and love me unconditionally.

I dedicate this dissertation to my dear father, Limin Wan.

## LIST OF TABLES

| 3.1 | Secure World Introspection Time   | 26 |

|-----|-----------------------------------|----|

| 3.2 | Probing Threshold on Multi-Core   | 26 |

| 4.1 | Power Consumption of Sec-RX       | 62 |

| 4.2 | Sec-TX Execution Time             | 62 |

| 4.3 | Porting TZNIC to Other NIC Models | 63 |

| 5.1 | RusTEE Component's LOC            | 85 |

## LIST OF FIGURES

| 2.1 | ARMv8-A Architecture                                   | 10 |

|-----|--------------------------------------------------------|----|

| 3.1 | User-level Multi-thread Prober                         | 18 |

| 3.2 | Race Condition Between Two Worlds on Multi-Core System | 19 |

| 3.3 | KProber Probing Threshold Stability                    | 27 |

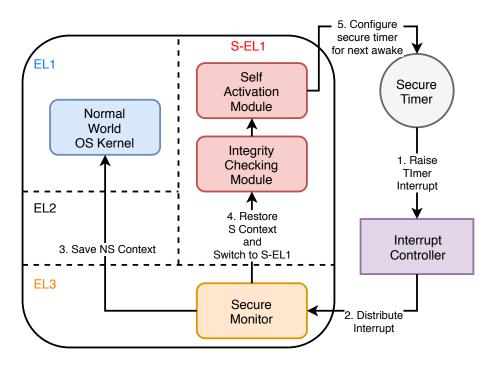

| 3.4 | SATIN Architecture                                     | 30 |

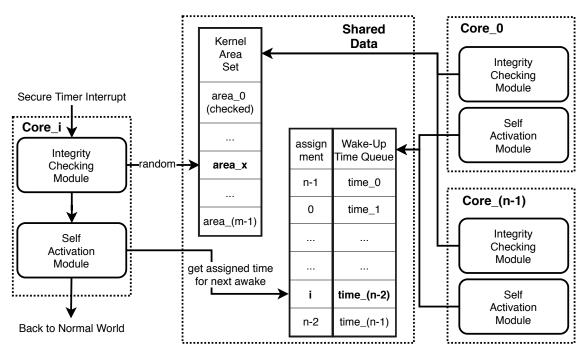

| 3.5 | Multi-Core Collaboration of SATIN                      | 33 |

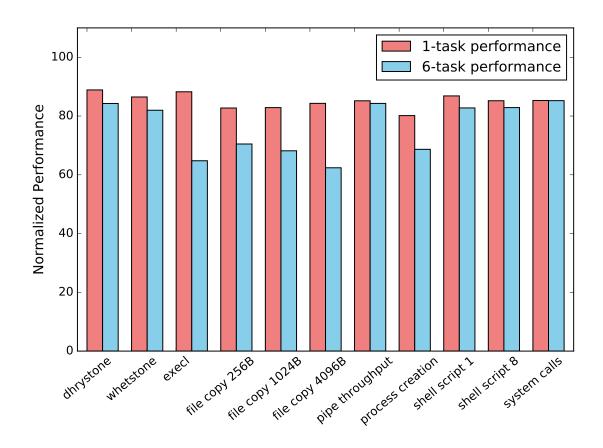

| 3.6 | SATIN Overhead                                         | 38 |

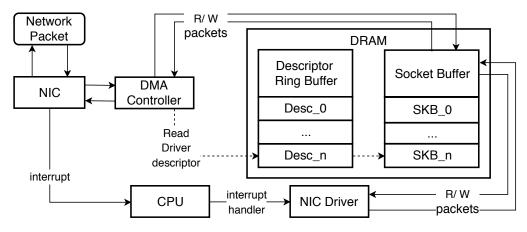

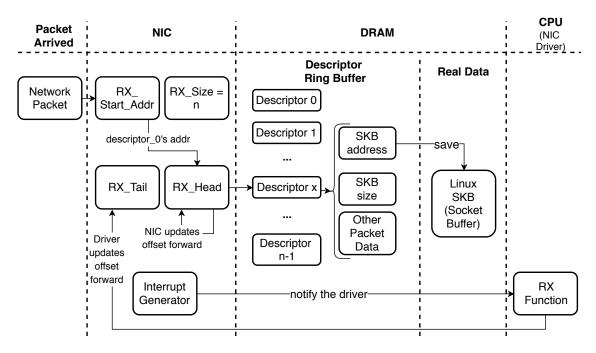

| 4.1 | DMA-Based NIC Workflow                                 | 44 |

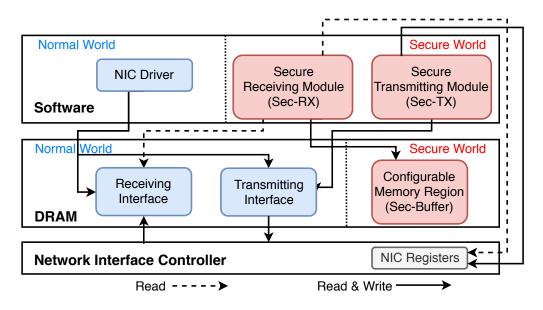

| 4.2 | TZNIC Architecture                                     | 48 |

| 4.3 | TZNIC Workflow                                         | 52 |

| 4.4 | DMA-Based NIC RX Workflow                              | 56 |

| 4.5 | Performance Overhead on Normal World                   | 61 |

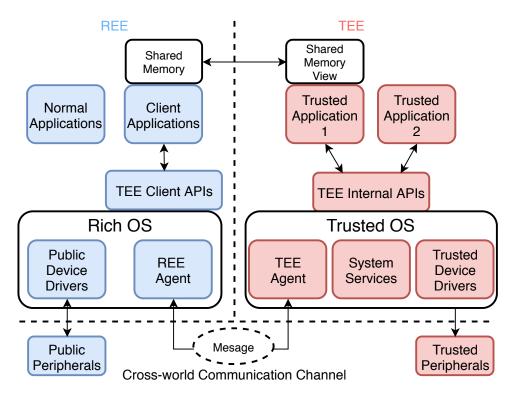

| 5.1 | GlobalPlatform TEE Architecture                        | 69 |

| 5.2 | RusTEE Architecture                                    | 75 |

| 5.3 | Porting Rust into OP-TEE                               | 83 |

| 5.4 | C vs. Rust Performance on Juno                         | 88 |

| 5.5 | QEMU vs. Juno Performance                              | 89 |

| 5.6 | Performances of C-based TAs vs. Rust-based TAs         | 91 |

Hardware-Assisted Security Mechanisms on ARM-Based Multi-Core Processors

# Chapter 1

# Introduction

Over the last ten years, ARM TrustZone has been leveraged extensively to provide security protection on the ARM platforms [16, 103, 24, 54, 123]. With the assistance of TrustZone technology, ARM enables system-wide isolation by creating a Trusted Execution Environment (TEE) for security-sensitive code and data, and this isolation is realized via the hardware features that are built-in with the processor as well as the bus interconnect. A typical TrustZone-based system divides all resources across the System-on-Chip, including the hardware components and running software, into two different worlds with different privilege-settings and protections. Among the two worlds, *Normal World* is responsible for running *rich OS* and all the regular applications, named as *Client Applications (CA)*. In contrast, another isolated *Secure World* only executes a small and trusted *secure OS* along with some high-level security management tasks that are developed as *Trusted Applications (TA)*.

Previously, most TrustZone-related researches [16, 24, 109, 117] place trust on the secure-world side and focus on exploiting the secure world to conduct different secure-sensitive tasks. Meanwhile, in the pace of the advancement of TrustZone technology, the security of the secure world now faces several newly rising challenges from the latest hardware features and inside applications. First, as most advanced ARM architecture are multi-core supported, the architecture allows each core to enter its secure world inde-

pendently, which means the rich OS and the secure OS can run in parallel [18, 69, 58]. Even such simultaneously execution capability certainly increases the performance on the normal-world side, it raises the new race conditions for the security components inside the secure world. For example, when the secure world conducts an introspection on the rich OS in one core, the inspected rich OS is still running in other cores, so it may infer the introspection's execution on other cores or even deceive the introspection by feeding the false result.

Moreover, because the latest ARM TrustZone supports the secure world to obtain a dynamic and ample memory space, the secure OS is no longer limited by the size of its Trusted Computing Base (TCB). Therefore, the secure OS can be developed with more and more functionalities, such as integrating the drivers of the necessary peripherals. However, as most peripherals, such as the Network Interface Card (NIC), is also required by the rich OS, both OSes have the same privilege to operate the same piece of hardware. Moreover, a general-purpose peripheral cannot differentiate the security attributes of an I/O operation, so it treats a secure-world operation as same as the normal-world one. In this case, it is challenging to achieve a balance between two worlds for the peripheral's availabilities while also promising the security of secure-world operations.

Finally, every TA inside the secure world can be risky and even harm the TEE's security. As the recent TA is developed with a variety of functionalities, it is hard to validate each TA's semantic correctness. These TAs could be compiled with the memory-unsafe vulnerabilities, and then get imported into the secure world. Moreover, as the TA collaborates with the corresponding CA that resides in the normal world, the communication channels between the two worlds can be exploited to attack the TA and conquer the entire secure world. Understanding how to assure the memory-safety of every TA and prevent the cross-world attack on TA is a critical and challenging question.

#### **1.1** Problem Statement

In this dissertation, we thoroughly study the latest ARM TrustZone technology and three particular security concerns regarding the ARM multi-core system.

(1) Conducting Secure Asynchronous Introspection on Multi-Core ARM Processors. It is a well-known technology to utilize TEE to inspect the rich OS's kernel's integrity. However, previous solutions are impractical on the ARM single-core platform as the secure world execution freezes the rich OS entirely and lead to unaffordable performance overhead. As the modern ARM architecture introduces the multi-core features, a more acceptable introspection mechanism is utilizing one core for the secureworld introspection while preserving other cores for the normal world tasks. Though such a mechanism maintains both worlds' performances, it also introduces the severe security concern on the secure-world introspection because the malicious rich OS may conduct the evasion attack during the introspection to hide its attacking trace. Such a new rising risk requires a detailed investigation of its practicality, and the secure world may require an enhanced introspection mechanism if such risk is a real threat to the latest ARM platform.

(2) Providing Reliable Network for TrustZone Secure World. Traditionally, the mobile device's network is maintained by the network driver, which is integrated as part of the mobile rich OS (such as Android). However, in recent years, numerous attacking methods have been reported to obtain the root privilege of the rich OS and therefore gain the capability to manipulate the network. For example, 315 new CVEs have been reported on Android in 2019 [36] as the privilege-escalation related vulnerabilities. Allowing attackers to take over the network availability can cause severe consequences, especially for the remote security management applications that are deployed in the secure world, such as remote attestation [74, 66], remote deletion [118, 83], and remote patching [78, 28]. A compromised network channel can lead to loss of access to these services, while the remote attacker can still connect to the phone for stealing user data or even hijacking users' banking transaction [87]. As TrustZone-based applications cannot trust the unre-

liable normal-world network driver for communicating with the remote server, we should provide a reliable mechanism for the secure world to interact with the network peripherals and therefore maintain the secure-world network availability.

(3) Enhancing the memory-safety of Trusted Applications. Due to the protection of hardware-assisted isolation, it becomes common for TrustZone-based systems [16, 24, 109] to assume the trust of entire TEE, including the trusted applications (TAs) running in the TEE. Also, the functionalities of TEE systems are extended dramatically by installing various TAs in the trusted isolated environment. Though TrustZone technology can assure isolation between TEE and REE, dozens of software-based vulnerabilities in TAs have been reported to compromise the entire TEE system [31, 122, 48]. The term "Trusted Application" only refers to an application that should be trusted to run in TEE, but it does not mean the application is bug-free. The risk of TEE systems being compromised will increase along with the number of TAs installed.

#### **1.2** Contributions

This dissertation proposes three projects that contribute to enhancing the TrustZone secure world's security across the application to OS level. The detailed contributions are listed.

Conducting Secure Asynchronous Introspection on Multi-Core ARM Processors. While performing a systematic study on the security of TrustZone-based asynchronous introspection [109], we propose the idea that traditional introspection strategy can be vulnerable to an evasion attack and then demonstrate our improved asynchronous introspection mechanism. In summary, we make the following contributions.

• we discover a new evasion attack called TZ-Evader against asynchronous inspection on multi-core ARM processors. The attack utilizes the side channel information to infer if any core is running in the secure world and then begins to clean the attacking traces simultaneously on other cores that run in the normal world.

- We develop a high-accurate probing technique called KProber for the normal world to fast probe the running state of all cores. Based on KProber, we implement a proofof-concept TZ-Evader, which can defeat existing TrustZone-Based asynchronous introspection mechanisms.

- We propose a secure and trustworthy asynchronous introspection mechanism called SATIN to protect mobile devices against TZ-Evader. It wins the race condition over the attacker by minimizing the running time of each introspection round and maximizing the probing delay of TZ-Evader.

**Providing Reliable Network for TrustZone Secure World.** We design the mechanism for the secure world to reliably conduct I/O tasks on the general-purpose peripherals, which resolves the limitation on the peripheral that cannot tell the privilege differences between the secure world and the normal world. Specifically, we make the following contributions.

- We propose an ARM TrustZone network mechanism TZNIC for reliably sharing one physical network peripheral between two network drivers, inside and outside of the isolated execution environments. The secure-world driver can achieve secure network I/O operations by reliably enforcing the sharing of the normal-world driver's software interfaces.

- By utilizing ARM TrustZone protection on multi-core processors, we design a secure receiving module and a secure transmitting module to reliably receive packets and send responses, respectively, even when the rich OS cannot be trusted. Our mechanism does not require any modification to the rich OS, does not put any trust on the OS component, and is robust on the concurrent read/write challenges.

- We implement a prototype of TZNIC on a development board. The experimental

results show that TZNIC can maintain the secure-world network channel with a small system overhead on rich OS. Our system can be deployed on ARM-based processor platforms with the support of a wide range of wired and wireless network devices.

**Enhancing the memory-safety of Trusted Applications.** We propose a TA-development mechanism, which assists developers to compile TAs in the memory-safe language Rust. By taking advantage of Rust's built-in security, we remove all the memory-unsafe implementation bugs of TA and further enhance its security of sensitive APIs and cross-world behaviors. Particularly, we make contributions in three aspects:

- We propose RusTEE, the first memory-safe trusted application development environment with comprehensive functionalities for TrustZone-assisted systems. By utilizing the built-in security properties and benefits of the Rust programming language, our trusted application environment removes most known memory-unsafe implementation bugs in trusted applications and thus enhance the security of TEE.

- We address two security concerns of the TrustZone-assisted TEE systems, namely, the widely exposed system-service APIs and cross-world communication channels, to enhance the security of Rust-based trusted applications.

- We implement a prototype of RusTEE and evaluate its performance in both a simulation environment and a real development board. Our experimental results show that our system can comply with strictly safe Rust, and it only incurs a minimal overhead. We will open source the system prototype.

#### 1.3 Dissertation Organization

The rest of this dissertation is organized as follows. In Chapter 2, we introduce the background knowledge of ARM TrustZone architecture. In Chapter 3, we present the details of the new evasion attack on the TrustZone-based introspection, and the corresponding countermeasure. In Chapter 4, we propose the TrustZone-based network peripheral mechanism, which enables both the normal world and secure world to apply isolated network drivers on the shared device simultaneously. In Chapter 5, we study the integration of the Rust language and the existing development environment of trusted applications. In Chapter 6, we summarize the related works of TEE-based architecture, introspection technology, TEE-based network management, and Rust-languages, respectively. Finally, we conclude the dissertation's highlight contributions and propose future research directions in Chapter 7.

# Chapter 2

# **ARM TrustZone Background**

This chapter presents the general background of ARM TrustZone technology. ARM designs and applies the TrustZone technology for its most-advanced Cortex-A chipset family (e.g., ARMv7-A, ARMv8-A) as an efficient and system-wide approach to creating the hardware-level Trusted Execution Environment (TEE). In this chapter, we will focus on the ARMv8-A architecture, which is the latest 64/32-bit ARM architecture and supports execution instructions with 64-bit registers and remains backward compatible with the 32-bit ARMv7 architecture. In the following sections, we will present the TrustZone key features about its security model, memory model, interrupt model, and features related to the multi-core processors.

#### 2.1 Security Model

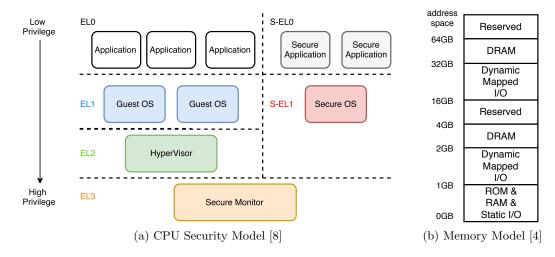

With ARM architecture, the TrustZone security feature is defined for the system to operate under two environments: the Normal World (non-secure) and the Secure World (secure), as shown in Figure 2.1a. The normal world is accessible to the secure world, but not vice versa. The security setting of each core is achieved via hardware logic in the ARM AMBA bus, and it is independent from the settings of other cores. Each processor core can execute instructions in one of six privileges, where *EL0*, *EL1*, *EL2* are used in the normal world, and *S-EL0*, *S-EL1*, *EL3* are the secure world privileges. Among these privileges,

Figure 2.1: ARMv8-A Architecture

EL3 is the highest privilege level that only contains a Secure Monitor for controlling the context switch between the secure world and the normal world. In the normal world, the user applications run at EL0, the guest OSes run at EL1, and the hypervisor runs at EL2. In the secure world, the secure applications run in the S-EL0 level, and the secure OS runs in the S-EL1 level. There is no S-EL2 level, so the secure world does not support a hypervisor layer.

#### 2.2 Memory Model

ARMv8-A uses a uniform memory address map to provide a consistent physical address to all shared resources, as shown in Figure 2.1b. The memory can be classified into two main types: *normal memory* and *device memory* [9]. ROM, SRAM, and DRAM belong to the normal memory, which can be configured as either secure memory or non-secure memory [6]. The device memory supports I/O devices, including Static I/O for on-chip peripherals and Dynamic Mapped I/O for general-purpose peripherals (e.g., NIC, mouse, and keyboard). Currently, most general-purpose peripherals treat all read/write access with uniform non-secure privilege, so the normal world and the secure world have the same view and operation privileges on the peripherals' registers [113].

#### 2.3 Interrupt Model

Besides the running application and memory, ARMv8-A also provide the interrupt mechanism with two privileges, namely *normal interrupt* and *secure interrupt*. The secure interrupts are always routed to the secure world no matter which world the CPU core is in [5], while the normal interrupts can be routed to either the normal world or the secure world, depending on specific configuration registers [5]. Since in most cases the device is running normal world tasks and the secure world is asleep, the secure interrupt is a key technique to guarantee the execution of the secure-world components, especially when the normal world is compromised and may decline to invoke the secure world.

The ARM interrupt management framework is responsible for configuring the interrupt routing behavior [11]. Normally, Interrupt Request (IRQ) is configured as a normal world interrupt and Fast Interrupt Request (FIQ) is configured as a secure world interrupt. There are two generic requirements. First, it should be guaranteed to route secure interrupts to be handled by the secure world, even when the current execution is in the normal world. Thus, it protects secure interrupts against potential intervention from nonsecure software. Second, it should be able to route the non-secure interrupts to the normal world when current execution is in the secure world. When the non-secure interrupt is configured to be routed to EL3, the secure monitor in EL3 can save the state of software in secure world before handing the interrupt to non-secure software. In this case, the secure world is *preemptive*. When the non-secure interrupt is configured to be routed to the S-EL1 or S-EL0, the secure software can either hand the interrupt to the non-secure software in a preemptive mode, or ignore the interrupt until its running task completes in a *non-preemptive* secure mode. OP-TEE OS [69] is an open-source secure operating system that supports preemptive secure world.

#### 2.4 ARM Multi-Core Processor

All latest ARMv8-A processors (e.g., Cortex-A53, 57, and 72) can be configured with one to four cores within one processor. Furthermore, ARM presents the big.LITTLE heterogeneous design to satisfy different application requirements on system performance and power consumption. Since each core maintains an independent security status, a multi-core platform may run the secure and non-secure software at the same time.

# Chapter 3

# SATIN: A Secure and Trustworthy Asynchronous Introspection on Multi-Core ARM Processors

#### **3.1** Introduction

Introspection mechanisms have been developed and deployed in a high privileged execution environment to prevent or detect security policy violations in a low privileged execution environment on the host machine [53]. In general, introspection mechanisms can be classified into two categories: *synchronous introspection* for attack prevention [38, 42, 91, 93, 16, 29, 25] and *asynchronous introspection* for attack detection [17, 120, 85, 37, 93, 102]. ARM TrustZone technology is a system-wide security mechanism to provide hardwarelevel isolation between two execution worlds that share the CPU in a time-sliced fashion, where the secure world has a higher privilege to access the system resources of the normal world such as memory, CPU registers, and peripherals, but not vice versa. To enhance the security of mobile devices, a number of TrustZone-assisted introspection mechanisms have been developed and deployed on millions of mobile devices [93, 16, 29, 25, 102].

Synchronous introspection mechanisms focus on intercepting and mediating security

sensitive operations inline by the high privileged execution environment to prevent security policy violations in the low privileged execution environment. For instance, synchronous mechanisms have been developed in the virtual machine manager to ensure memory page protection in virtual machines [38, 42, 91]. Similarly, Samsung's KNOX Real-time Kernel Protection (RKP) mechanism [93, 16] relies on ARM TrustZone technique to intercept certain privileged system functions in the normal world and screen them through the secure world for inspection and approval before being executed.

However, synchronous introspection mechanisms face two main challenges. First, it has to hook up to all security sensitive locations that are potentially exploitable to attackers. Though it is possible to build up a near-complete list based on recently discovered policy violations, it is hard to ensure the completeness of such list. Second, certain implementation bugs, such as write-what-where, allows an attacker to launch *data attacks* bypassing the function checkpoints setup for the synchronous introspection [62, 88]. Once an attacker discovers any vulnerability of synchronous introspection, she can deploy a persistent rootkit to maintain the root access to the normal world OS (rich OS), steal data or mislead user behaviors without being detected by synchronous introspection.

Asynchronous introspection mechanisms can effectively detect those persistent rootkits via analyzing attacking traces of security policy violations from a snapshot of memory along with CPU state information that is periodically or randomly acquired from the low privileged execution environment (e.g. the normal world). Besides simply checking the integrity of the invariant kernel code, a number of proof of concept approaches have been developed to provide a more fine-grained security checking on dynamic kernel data structures after filling the semantic gaps [17, 120, 85, 37]. Unlike the synchronous introspection that requires to intercept all read/write transactions on the target, asynchronous introspection conduct the introspect the target completely and therefore detect a persistent attack. Meanwhile, as stated in Section 1.1, the TrustZone-based introspection is majorly challenged by securely taking the rich OS's snapshot, especially under the condition that rich OS is not frozen on the multi-core scenario.

One major limitation on applying asynchronous introspection mechanism in practice is that the introspection process may introduce a large system overhead. Particularly, on single core ARM processors, whenever the secure world is performing the security checking, the entire rich OS will be suspended during the memory acquisition and online memory analysis process. Due to this poor usage experience on mobile devices, TrustZone-based asynchronous introspection has not been widely deployed or enabled.

Modern multi-core ARM processors creates new opportunities to deploy a practical asynchronous introspection based on TrustZone without pausing the rich OS. Specifically, the ARM multi-core architecture allows each core to enter its secure world independently, so the rich OS and the secure OS can run in parallel [18, 69, 58]. It is now feasible to make one core or all cores taking turns to perform the asynchronous introspection tasks while leaving other cores to continue the normal world's operations. For example, Samsung KNOX includes a Periodic Kernel Measurement (PKM) mechanism in the secure world to perform periodic asynchronous introspection on a specific core [93].

In this chapter, we reveal a new type of evasion attack that can defeat the asynchronous introspection on multi-core systems by removing the attacking traces concurrently from one core while the security checking is executing on another. Evasion attacks target at defeating asynchronous introspection by predicting precisely the time of next security check and thus removing all attacking evidence to avoid detection [120, 93]. However, on multi-core mobile devices that can run both normal world and secure world concurrently, besides removing the attacking traces before security check, an attacker can also hide its attacking trace right after the start of introspection but before it has the opportunity to examine any malicious bytes. We name this type of evasion attacks as TZ-Evader.

There are two main challenges to be solved when designing a TZ-Evader attack. First, the malicious code running in the normal world needs to know if the asynchronous introspection is running on any core's secure world; however, the ARM TrustZone architecture protects the secure world running information from being accessed by the normal world. To solve this challenge, we propose to utilize the CPU core's availability as the side channel information to decide if the introspection is running on any core. We develop a user-level prober to stealthily probe the current state of each core. Second, when one core enters the secure world and begins to run the inspection, the malicious normal world needs to detect the core's state changes at an earliest time in order to maximize its evasion capability. To solve this challenge, we propose a kernel-level prober that can accurately monitor the running state changes of all cores. There are two implementation options for deploying the kernel-level prober, either by intercepting the timer interrupt to inject the prober in the rich OS or by manipulating the real-time scheduler of the Linux kernel to add the prober as a high priority process.

We implement a proof-of-concept TZ-Evader attack by integrating the kernel-level prober with traditional persistent rootkit on the ARM Juno r1 development board [14]. We evaluate its effectiveness against the state-of-the-art asynchronous introspection mechanisms, and the experimental results show the new TZ-Evader attack can accurately detect the running of asynchronous introspection and thus conduct a successful evasion attack.

With a deep understanding of the TZ-Evader attack, we propose a secure and trustworthy asynchronous introspection solution called SATIN in the secure world to defeat the TZ-Evader attack. The basic idea is to minimize the running time of each introspection and maximize the probing delay of TZ-Evader at the same time. We propose a number of techniques including *random wake-up time*, *random introspection area*, and *random CPU affinity* to ensure that the asynchronous introspection is always completed before TZ-Evader can hide any attacking traces. We implement a prototype of SATIN on the ARM Juno r1 development board and the experimental results show that it can effectively detect the TZ-Evader attacks with a minor system overhead.

#### 3.2 TZ-Evader: Evasion Attacks on Multi-core Processors

#### 3.2.1 Assumptions and Threat Model

We assume the secure world can be trusted and all the introspection components in the secure world are secure from attacks in the normal world. The asynchronous introspection can run randomly on any core at any time, and it cannot be intercepted by the normal world. We assume the asynchronous introspection does not suspend the rich OS on all cores; otherwise, it will face the same poor user experience problem as that on single-core processors. We assume the rich OS can be compromised and the attacker can bypass the existing synchronous introspection mechanisms to gain root privilege [88, 62]. We assume the attack is an Advanced Persistent Threat (APT), which aims to maintain its presence on the target and makes various effort to remain undetected. For example, a key-logger may collect all user inputs on the keyboard by intercepting a system interrupt, while the hijacking is detectable to the introspection. In this case, whenever the introspection is running, the key-logger should stop the attack and clean its attack trace to camouflage its existence; Meanwhile, for all the other time, it remains in the attacking phase.

#### 3.2.2 New Attack Surface

On multi-core ARM processors, attackers may defeat the existing asynchronous introspection by satisfying two requirements. First, the malicious code in the normal world can detect if one core is entering the secure world. Second, before the core in the secure world can access the attacking traces, the malicious code running on other cores can remove the attacking traces.

#### 3.2.2.1 Probing CPU Core's Running State

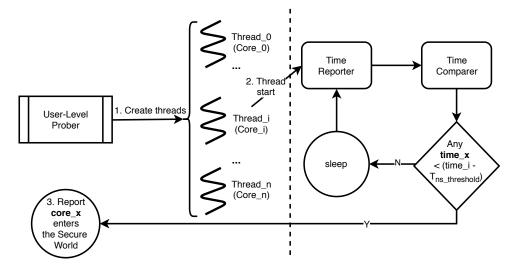

Since the normal world cannot directly access any secure world information, we propose to utilize the availability of the shared CPU cores as a side channel information to infer the running state of each core. The main idea is that after the secure world holds one core to perform the introspection, the normal world cannot use that core to run any process. A user-level prober process can be used to conduct this probing task. To trace when the normal world loses the control on a CPU core, the prober process assigns each core with a child-thread, which keeps reporting back the corresponding core's availability. Since the rich OS kernel may migrate one thread task to other cores, especially when one core is paused, we fix the CPU affinity of each thread. Thus, when one core enters the secure world, the attached thread will be paused and cannot be migrated to other cores by the OS scheduler. When one thread is paused, the prober process can detect that the corresponding core enters the secure world.

Figure 3.1: User-level Multi-thread Prober

Figure 3.1 shows the multi-thread design of the user-level prober. For a device with n cores, we start a process with n threads, and each thread's CPU affinity is fixed to its corresponding core. Each thread has two components: *Time Reporter* and *Time Comparer*. On core i, the Time Reporter obtains the latest time *time\_i* from a shared timer among all CPU cores and then reports the time into a buffer that is readable to all threads. After that, the Time Comparer compares core i's *time\_i* with all other cores' latest reported times.

Since each thread reports its latest time independently, even if we can start the Time

Figure 3.2: Race Condition Between Two Worlds on Multi-Core System

Reporters on all cores simultaneously, there exists a time difference when reading those reported time buffers and comparing their values. Meanwhile, since the kernel scheduler manages to provide the "fairness" to all threads, even though we cannot control all threads in a completely synchronized manner, each thread can be executed within a threshold, and the time differences between any two threads have an upper limit. We define this upper limit as  $T_{ns\_threshold}$ .

If thread *i* finds any core *x*'s latest  $time_x$  is earlier than its reporting time and the latency is larger than the threshold, namely,  $time_i > (time_x + T_{ns\_threshold})$ , then this thread reports that *core\_x* switches to the secure world. To remain stealthy, we can afford to have the threads sleep for a time interval. We assume the threads can be scheduled with the average frequency  $f_{ns\_sched}$ , so between any two consecutive rounds of Time Comparer, there is a delay  $T_{ns\_sched} = 1/f_{ns\_sched}$ . Finally, the prober needs time  $T_{ns\_delay} = T_{ns\_sched} + T_{ns\_threshold}$  to detect that one core enters the secure world.

We implement and evaluate this user-level prober on the ARM Juno development board (see Section 3.3.1). When running one round of probing every 8 seconds, we found the  $T_{ns\_delay}$  is smaller than  $5.97 \times 10^{-3}$  s while the average time for one core to conduct a kernel integrity check is  $8.04 \times 10^{-2}$  s. We can see the prober is capable of detecting the running of a typical TrustZone-based kernel integrity checking. Since each step of the prober requires no modification with OS kernel privilege, it is stealthy and useful to check if the secure world is ever entered.

#### 3.2.2.2 Race Condition on Multi-core Processors

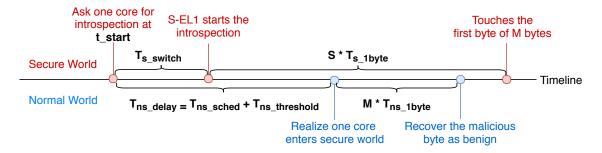

One state-of-the-art defense mechanism against evasion attacks is to trigger the security checking randomly. However, on multi-core systems, we observe that as long as the normal world is not frozen on all cores, there exist a race condition between the normal world to remove the attacking traces and the secure world to detect the attacking traces. We assume the introspection will check N bytes of critical memory and the normal world needs to clean M bytes of attacking traces.

We formalize the race condition between the evasion attacks and the asynchronous introspection. We suppose the secure world requests to start the asynchronous introspection at the time moment  $t\_start$ . To switch one core to the secure world for conducting introspection, the ARM processor needs to save the normal world context of this core and then switch to the secure world. We define this context switching period as  $T_{s\_switch}$ . Thus, the moment that the secure world starts the integrity checking can be as early as  $t\_start + T_{s\_switch}$ . We define the time for the secure world to inspect one byte as  $T_{s\_lbyte}$ . Since the secure world assumes all N bytes may be vulnerable while it does not know exactly what bytes are modified by the attacker, it may check S bytes before it touches any malicious byte where  $0 \le S \le N - M$ . Therefore, the introspection cannot find any malicious bytes before the time moment  $t\_start + T_{s\_switch} + S * T_{s\_lbyte}$ .

From the attacker's point of view, since she wants to attack the system with the longest duration (e.g., to collect inputted password), she would only stop the attack and hide the attacking trace if she believes there is an introspection. If it can predict the  $t\_start$ , it can easily hide before the introspection starts. When the  $t\_start$  is unknown or unpredictable, the attacker need to detect it by probing the secure world's state. We define the probing delay for the attacker to notice one core entering the secure world as  $T_{ns\_delay}$ . Assume the time for the attacker to recover one malicious byte is  $T_{ns\_lbyte}$ . The total recovering time for the attacker is  $T_{ns\_recover} = M * T_{ns\_lbyte}$ . Then after the moment  $t\_start + T_{ns\_delay} + T_{ns\_recover}$ , the secure world cannot detect the malicious modification.

The timing relationship between the two worlds is shown in Figure 3.2. Finally, for the attacker that is able to escape from the introspection, the condition 3.1 should be satisfied :

$$(T_{s\_switch} + S * T_{s\_1byte}) > (T_{ns\_delay} + T_{ns\_recover})$$

$$(3.1)$$

We can see that the key element for evasion attacks to win the race condition is to minimize the probing delay  $T_{ns\_delay}$ . Though the user-level prober shows the capability of understanding the secure world state stealthily, its probing stability and accuracy cannot be guaranteed. Particularly, when one core is scheduled with several threads that have the same or higher schedule priority than the probing thread, the prober's  $T_{ns\_sched}$  is increased. To improve the probing accuracy, we should minimize the detection delay. In the next subsection, we present a new evasion attack called TZ-Evader based on a more accurate kernel-level prober.

#### 3.2.3 TZ-Evader Design

TZ-Evader includes two components: a kernel-level attack module that conducts the persistent attack on the OS and removes the attacking trace accordingly; a fine-grained kernel-level prober module that can accurately and reliably monitor the running state of each core. The kernel-level prober also contains two components Time Reporter and Time Comparer, the same as the user-level prober. After obtaining the root privilege in rich OS, the prober module is loaded. If the prober can receive the time reported from all CPU cores, TZ-Evader believes there is no introspection in the secure world and keeps the attack active on the rich OS. Once the prober module reports that one core may be switched to the secure world, TZ-Evader begins to remove its attacking trace. We provide two implementation options for the kernel-level prober. The first option KProber-I is based on intercepting the timer interrupt to inject the prober in the rich OS, and the second option KProber-II works by manipulating the real-time scheduler of the Linux kernel to add the prober as a high priority process to be scheduled.

#### 3.2.3.1 KProber-I

On ARM processors, each core has its own timers to generate time interrupts. The Time Reporter and Time Comparer are injected into the normal world timer interrupt handler, so as to ensure the prober being executed with the same frequency as the timer interrupts. After this hijacking, for any incoming timer interrupt to core i, the interrupt handler updates the time\_i into its corresponding  $buffer_i$  and compares it with other n-1cores' time reports before resuming the normal timer interrupt handler. Linux kernel is typically configured as the CONFIG\_NO\_HZ\_IDLE mode, which means when the core is not in the IDLE state, the per-core timer raises the timer interrupt for schedulingclock ticks periodically with the frequency of HZ. For most versions of the Linux kernel,  $100 \leq HZ \leq 1000$  [34]. To avoid any core entering the idle mode, KProber-I keeps running a user-level multi-threads program on each core. KProber-I can guarantee to work with a frequency no less than HZ on any core, no matter how many tasks are running on that CPU core. Though this implementation option can achieve the highest time accuracy from the rich OS perspective, it requires to modify the timer interrupt handler, which may introduce extra attacking trace for the defender to detect. In Section 3.2.3.2, we present another implementation without modifying any kernel static area. Moreover, since there are many potentially unknown mechanisms to manipulate the handler, the defender has to scan the entire kernel for detecting all potential preparation traces, which gives KProber-I a larger chance to be recovered as we evaluated in Section 3.3.3.

#### 3.2.3.2 KProber-II

This prober utilizes the Linux's real-time (RT) scheduler to ensure a reliable execution of Time Reporter and Time Comparer. According to the Linux kernel design, RT scheduler has higher scheduling priority than the default Linux CFS scheduler, which is responsible for scheduling most of Linux application threads. Meanwhile, RT scheduler can be used to schedule tasks with higher priority. Therefore, by setting the prober with the highest priority of RT scheduler, KProber-II can protect the reliable execution of Time Reporter and Time Comparer from being affected by either CFS-scheduled threads or low priority RT-scheduled threads.

Theoretically speaking, the timer-interrupt based prober is more stable than the RT scheduler based prober, since the frequency of the RT scheduler relies on the timer interrupt. However, injecting a prober into the interrupt handler demands more engineering efforts than simply increasing the priority of the attacking threads using the real-time scheduler. We present more implementation details in Section 3.3.1.1.

## 3.3 TZ-Evader Evaluation

#### 3.3.1 TZ-Evader Implementation

We develop a prototype of TZ-Evader on ARM Juno r1 development board [12], which is featured with the ARM big.LITTLE technology that consists of a 4-core Cortex-A53 "LIT-TLE" processor for maximum power efficiency and a 2-core Cortex-A57 "big" processor to achieve maximum computation performance. The secure monitor running in EL3 is provided by ARM trusted firmware (ARM-TF), and the secure world OS running in S-EL1 is modified based on the Test Secure Payload (TSP) of ARM-TF [11]. We modify the secure timer interrupt handler in the TSP to perform the integrity check over the normal world. The normal world runs OpenEmbedded LAMP OS with kernel version lsk-4.4-armlt in EL1, which is downloaded using the script from Juno Wiki of ARM Community [14].

## 3.3.1.1 Kernel-Level Prober Implementation

We deploy two types of KProber to probe a specific core or a randomly chosen core. To probe a specific core's running state, we fix one thread of Time Reporter on the targeted core and fix another thread containing Time Reporter and Time Comparer on another core. To probe a random CPU core, we assign each core with one thread that contains Time Reporter and Time Comparer. To implement the timer interrupt based KProber-I, one key technical issue is to hijack the time interrupt handler. In ARMv8-A architecture, the address of the original timer interrupt address is saved in the *IRQ Exception Vector*, which can be located in the AArch64 Exception Vector Table [10]. The table's starting address is saved in the Vector Based Address Registers  $VBAR\_ELi(1 \le i \le 3)$ . After locating the timer interrupt, we modify its corresponding table entry to redirect it to our hijacking code.

For the real-time scheduler based KProber-II, we use the function  $pthread\_setschedparam()$ to schedule the targeted threads with the real-time scheduler. We use the rt-scheduler  $SCHED\_FIFO$  with the priority parameter  $sched\_get\_priority\_max(SCHED\_FIFO)$ for all KProber-II's threads. After investigating the relationship between thread sleeping and CPU utilization, we set the sleep time  $T_{sleep} = 2 \times 10^{-4}$  s and we assume the  $T_{ns\_sched} = T_{sleep}$ . In the following experiments, we implement Time Reporter with KProber-I and Time Comparer with KProber-II to demonstrate that both techniques can achieve reliable probing results.

#### 3.3.1.2 Sample Kernel-Level Attack

To facilitate the evaluation of TZ-Evader, we implement a kernel-level attack that can hijack the GETTID system call. Successful system hijacking requires modifying an entry of the system call table, and this attack modifies one 8-bytes address of the system call table. Since the system call table is defined as text kernel data, TrustZone-based introspection can detect the GETTID system call is hijacked if the introspection scans and detects any of these 8 bytes is modified. Note there are many other kernel level attacking vectors, we just use GETTID hijacking attack as an example to study the evasion attacks.

## 3.3.2 TZ-Evader Evaluation

#### 3.3.2.1 Introspection Time Delay

We first evaluate the time delay of the introspection. As we mentioned in the Equation 3.1, TrustZone-based asynchronous introspection suffers two major delays:  $T_{s\_switch}$  and  $s * T_{s\_1byte}$ . To evaluate  $T_{s\_switch}$ , we execute the context switching function of Test Secure Payload Dispatcher 50 times on one A53 core and one A57 core. The result shows for a secure timer interrupt raised at  $t\_start$ , the time for the dispatcher to pause the normal world and jump to the related timer interrupt on the A53 core or A57 core are similar, ranging from  $2.38 \times 10^{-6}$  s to  $3.60 \times 10^{-6}$  s.

Then we evaluate  $T_{s.1byte}$  regarding two different introspection techniques. Traditional hardware-assisted asynchronous kernel introspection takes a snapshot of the kernel [120, 119] and then analyzes the memory copy. Since this copy remains inaccessible by the attacker, the analysis steps after taking the snapshot are not vulnerable to the TOCTTOU attack. Meanwhile, since the secure world and the normal world share the system hardware, TrustZone-based introspection can directly read the normal world OS' kernel from the secure world. After reading the kernel data, it can hash the data and compare the hash value to a pre-calculated authorized value. In our experiment, we measure the time for the secure world to take the snapshot and hash the kernel data. We use djb2 [82] as the hash function. Each measurement is repeated 50 times. Table 3.1 shows that directly hashing the kernel's memory is more efficient than capturing and hashing the snapshot. In addition, it consumes less memory than the snapshot approach. Therefore, directly hashing the memory is better than taking snapshot when the asynchronous introspection targets at the static kernel area. We also find that it takes less time to conduct the introspection on the A57 core than the A53 core, since A57 core is more powerful than the A53 core.

| Core-Time   | Hash 1-Byte                  | Snapshot 1-byte              |  |

|-------------|------------------------------|------------------------------|--|

| A53-Average | $1.07	imes10^{-8}\mathrm{s}$ | $1.08	imes10^{-8}\mathrm{s}$ |  |

| A53-Max     | $1.14	imes10^{-8}\mathrm{s}$ | $1.57	imes10^{-8}\mathrm{s}$ |  |

| A53-Min     | $9.23	imes10^{-9}\mathrm{s}$ | $9.24	imes10^{-9}\mathrm{s}$ |  |

| A57-Average | $6.71	imes10^{-9}\mathrm{s}$ | $6.75	imes10^{-9}\mathrm{s}$ |  |

| A57-Max     | $7.50	imes10^{-9}\mathrm{s}$ | $7.83	imes10^{-9}\mathrm{s}$ |  |

| A57-Min     | $6.67	imes10^{-9}\mathrm{s}$ | $6.67	imes10^{-9}\mathrm{s}$ |  |

Table 3.1: Secure World Introspection Time

#### 3.3.2.2 Attack Time Delay

We evaluate normal world attack time delay in two aspects, where  $T_{ns\_recover}$  is introduced by the the kernel-level attack module, and  $T_{ns\_threshold}$  is introduced by the prober module. We repeat the measurement of the recovery time  $T_{ns\_recover}$  50 times on one A53 core and one A57 core. For the A53 core, the average recovering time is  $5.80 \times 10^{-3}$  s. For the A57 core, the average recovering time is  $4.96 \times 10^{-3}$  s.

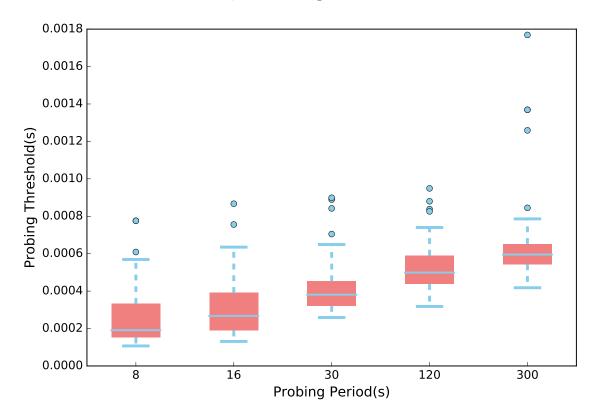

Then we present the prober's time delay  $T_{ns\_threshold}$  when KProber is probing all cores simultaneously. As the prober execution involves all available cores, we present the prober's time delay  $T_{ns\_threshold}$  regardless of core types. To observe the variation of the threshold, we execute the KProber with different probing periods. For each probing period, we choose the largest difference calculated by the Time Comparer as the threshold, and we repeat the measurement 50 times. We present the average threshold, maximum threshold, and minimum threshold of the 50 rounds for each time period in Table 3.2.

Table 3.2: Probing Threshold on Multi-Core

| Probing Period | Average                      | Max                          | Min                          |

|----------------|------------------------------|------------------------------|------------------------------|

| 8 s            | $2.61	imes10^{-4}\mathrm{s}$ | $7.76	imes10^{-4}\mathrm{s}$ | $1.07	imes10^{-4}\mathrm{s}$ |

| 16 s           | $3.54	imes10^{-4}\mathrm{s}$ | $1.38	imes10^{-3}\mathrm{s}$ | $1.31	imes10^{-4}\mathrm{s}$ |

| 30 s           | $4.21	imes10^{-4}\mathrm{s}$ | $8.99	imes10^{-4}\mathrm{s}$ | $2.59	imes10^{-4}\mathrm{s}$ |

| 120 s          | $5.26	imes10^{-4}\mathrm{s}$ |                              |                              |

| 300 s          | $6.61	imes10^{-4}\mathrm{s}$ | $1.77	imes10^{-3}\mathrm{s}$ | $4.18	imes10^{-4}\mathrm{s}$ |

Based on the experiment results, we find that the average threshold becomes larger along with a longer probing period and the maximum threshold is around  $1.8 \times 10^{-3}$  s. To

further understand the variation of the threshold, we investigate the reported time of each thread and identify that, in some rare cases, Time Comparer on *core\_i* may get the *time\_x* of the *core\_x* with an abnormal large delay, which is up to  $1.3 \times 10^{-3}$  s. This cross-core reading delay leads to the large threshold. Meanwhile, a longer probing period increases the occurrence of those rare cases, so the average threshold increases too.

Figure 3.3: KProber Probing Threshold Stability

To present the stability of KProber, we show the variation of the thresholds with different probing periods in Figure 3.3. We can see that even though the KProber's average probing threshold increases with the probing period, the upper whiskers of the thresholds only go up slightly, and only few extreme large outliers are introduced for probing period 300 s, which go over  $1 \times 10^{-3}$  s.

Finally, we also observe that setting introspection with a fixed CPU affinity is easier to be probed than using all cores randomly. As we mentioned in Section 3.3.1.1, we also evaluate the case to use KProber for figuring out one single core's availability. We conduct the experiment with the same setting as presented above. According to our experiment result, the average thresholds to probe the single core only equal to  $\sim 1/4$  of the presented threshold for probing all cores, for all five probing periods we evaluated. This means the more cores KProber needs to probe, the larger probing threshold it suffers.

## 3.3.3 Race Condition Analysis

Based on the experiment results, we have following observations on the race condition between the normal world and the secure world:

- 1. The switch delays  $T_{s\_switch}$  for the A53 core and A57 core are similar.

- 2. The secure world can use more powerful CPU core (i.e., A57 core) for introspection to achieve a shorter  $T_{s\_1byte}$ .

- 3. The secure world is easier to be probed if it's CPU affinity is predictable to the normal world.

- 4. The timing bottleneck of TZ-Evader is the time period for recovering its attacking trace  $T_{ns\_recover}$ .

According to Equation 3.1, we know the attack can finish its cleaning task after the secure world inspects S memory bytes, where:

$$S > \frac{T_{ns\_sched} + T_{ns\_threshold} + T_{ns\_recover} - T_{s\_switch}}{T_{s\_1byte}}$$

(3.2)

Now we consider the worst case for the TZ-Evader: the introspection starts on one A57 core while the TZ-Evader uses on one A53 core to remove its attacking trace. In Section 3.3.2.1, we have  $T_{s\_switch} \leq 3.60 \times 10^{-6}$  s. Also, the secure world can inspect the kernel data with the maximum speed  $T_{s\_1byte} = 6.67 \times 10^{-9}$  s. The attacker recovers its attacking trace as the lowest efficiency  $T_{ns\_recover} = 6.13 \times 10^{-3}$  s, and  $T_{ns\_sched} = 2 \times 10^{-4}$  s. In Section 3.3.2.2, we have for the worst case of TZ-Evader,  $T_{ns\_threshold} \leq 1.80 \times 10^{-3}$  s. By applying the experimental data into the above Equation 3.2, we have  $S \leq 1218351$  bytes. Supposing the attack bytes appears randomly in the kernel and the introspection checks the entire OS kernel whose size is 11916240 bytes, nearly  $1 - \frac{1218351}{11916240} \approx 90\%$  of the kernel space is not protected by existing TrustZone-based asynchronous introspection. Therefore, as long as both kernel attack module and prober module do not locate in the 10% scanned area, the system suffers TZ-Evader attack.

## 3.4 SATIN: Secure Asynchronous Introspection

We propose a secure and trustworthy TrustZone-based asynchronous introspection mechanism named SATIN that can practically inspect rich OS and effectively defeat TZ-Evader attacks. We first discuss two major challenges on developing the secure asynchronous introspection and then present the detailed design of the proposed mechanism. Figure 3.4 shows the architecture of SATIN, which is implemented in the secure world. It consists of two major components, where the integrity checking module performs the integrity checking on rich OS using a divide-and-conquer method to control the checking time of each round and the self activation module is responsible for waking up the secure world with the help of a secure timer and ensuring that the entrance cannot be either predicted or quickly probed by the normal world.

## 3.4.1 Asynchronous Introspection Challenges

We identify two main challenges on developing secure asynchronous introspection mechanisms against TZ-Evader.

## 3.4.1.1 Challenge 1: Performance vs. Detection Accuracy

On single core processors, the TrustZone-based introspection introduces unacceptable overhead as the introspection has to suspend the rich OS during the security checking process. The pausing issue leads to poor user experience. For example, a music song

Figure 3.4: SATIN Architecture

played in the normal world becomes incoherent when the CPU enters the secure world. Similarly, on the multi-core processors, we cannot frequently freeze all cores even for a small period of time. For instance, Azab et al. [17] propose an introspection mechanism that requires to freeze all CPU cores on the server every 8 or 16 seconds. It becomes one of the biggest obstacles for asynchronous introspection mechanisms to be widely adopted and deployed, though a better detection accuracy can be achieved by freezing all cores. Meanwhile, even a multi-core platform can execute the introspection and other tasks simultaneously, the execution of the secure world still possesses some shared resources such as the CPU core. It is not well studied how much overhead is introduced by running the introspection in parallel to the rich OS.

## 3.4.1.2 Challenge 2: Evasion Attack

It is a challenge to defend against evasion attack when designing asynchronous introspection mechanisms [53]. If the attacker can escape ahead of the introspection by predicting or probing the execution of the asynchronous introspection, then the introspection result cannot be trusted [111, 102]. On single core processors, random checking is an effective scheme to defeat evasion attacks. However, on multi-core ARM processors, TZ-Evader can even escape from the random checking on any random core. It is critical to develop a secure asynchronous introspection mechanism to defeat the new evasion attacks.

## 3.4.2 Integrity Checking Module

To improve the detection rate, we propose to reduce the introspection time for each round by dividing the entire OS kernel into smaller areas and taking turns to check one area in each round. Therefore, it can guarantee to finish one round of security checking right before the malicious normal world can probe it but have not chance to remove any attacking traces. The integrity checking module prepares the hash value of each small area's benign status during booting stage. Then for each round of wake-up, it scans one small area and compares the hash value with the pre-calculated benign one. If the integrity checking module finds any abnormal small area, it can raise an alarm to the server side or the device user. To ensure that the malware cannot remove its traces before we finish checking on one small area, the size of each small area should be smaller than  $(T_{ns\_delay} + T_{ns\_recover} T_{s\_switch})/T_{s\_lbyte}$  by tes. We develop a pseudo-random method to select the next small area for introspection. Suppose the set  $set_{area} = \bigcup_{i=0}^{m-1} area_i$  contains all the areas of the OS kernel, and each  $area_i$  satisfies the above size condition. When the secure world starts one round of the introspection, the module randomly picks one area  $area_x$  from  $set_{area}$  and then applies  $set_{area} = set_{area} - area_x$ . If  $set_{area} = NULL$ , then SATIN resets  $set_{area} = \{area\_0, ..., area\_(m-1)\}.$

Also, the integrity checking module needs to guarantee its execution is not interrupted by other non-secure parties. According to the latest ARM interrupt routing model [11], the normal world interrupt signal is possible to interrupt the execution of secure world. To prevent the normal world from using interrupts to interfere in the introspection process, SATIN needs to block all interrupts during each round of the introspection. We propose to deploy the integrity checking module into the secure timer interrupt handler, and then set EL3 to not trap the normal world interrupt by configuring  $SCR\_EL3.IRQ = 0$ . With this setting, even if the normal world interrupt signal can arrives the secure world, their priorities are lower than the integrity checking module.

## 3.4.3 Self Activation Module

The self activation module is designed to make sure the secure world can invoke the integrity checking module anytime without the help of the normal world. It relies on a secure timer that the normal world cannot access. Each TrustZone-enabled core has an individual secure timer that can only be read or written with the secure world privilege. During the booting time, the self activation module is invoked once on each core to write the next awake time into the secure timer register.

After the trusted booting process, when the timer condition meets, the timer raises an interrupt for the secure world and the secure monitor switches the core from the normal world to the secure world to handle this interrupt. By configuring the secure timer, we can activate the secure world without involving the normal world. Thus, we can prevent the normal world from disturbing the invocation of introspection. When one core enters the secure world via the secure timer interrupt, SATIN first performs the introspection on one small area and then sets the awake time for the next round of introspection. The self activation module decides the next awake time by *time\_x*, which is set to a base period time  $t_p$  (e.g., 8s, 16s, etc.) plus a random deviation  $t_d$  (e.g., a random time from  $-t_p$  to  $t_p$ ). By applying the random deviation with the next awake time, the interval between two consecutive rounds of introspection is among  $[0, 2 * t_p]$ , which means at any moment the introspection could start to scan and the attacker has to keep probing all cores. In addition, the random deviation can effectively minimize the exposure of any recognized patterns on the invocation of the asynchronous introspection to the normal OS. We set  $t_p = T_{goal}/m$ , where  $T_{goal}$  is the time period to guarantee that all the target areas can be scanned at least once.

## 3.4.4 Multi-Core Collaboration

To increase the checking accuracy, we propose to choose a random core for conducting the introspection task. This design choice is based on the observation that if only one core is used for asynchronous introspection, the malicious normal world can achieve a better probing accuracy than that when all cores are randomly chosen to conduct introspection, as mentioned in Section 3.3.2.2.

Figure 3.5: Multi-Core Collaboration of SATIN

Figure 3.5 illustrates the collaborative introspection of SATIN on the multi-core architecture. When any core i wakes up for the introspection, it randomly takes one kernel area from the shared Kernel Area Set  $set_{area}$  and inspects this area. Later, other cores are not going to inspect this area repeatedly since core i removes the area it chooses from the set. If there is no more area available, the set is refilled with all areas again. Next, core iobtains the next wake-up time from a wake-up time queue and configures it's secure timer accordingly, where the wake-up time queue is responsible to coordinate all cores that wake up in a random sequence. Coordinating all cores to wake up in a random sequence is also a challenged task. ARMv8-A architecture does not provide a solution for one core to directly read or write the timer of another core. In this case, an intuitive design is to use the cross-core interrupt to notify all cores on serving the introspection in turn. ARMv8-A allows one core to generate a secure interrupt to forcibly switching another core into the secure world, so after core i finishes one round of introspection, it can switch another core j into secure world and then core j sets the secure timer for the next round introspection. However, the switch of core j can also be probed by the normal world so this method may leak the wake up sequence to the normal world, which can defeat the benefits from randomly waking up cores.

To protect the wake-up pattern from the normal world, SATIN does not apply the cross-core interrupt mechanism, and instead coordinates all cores via the secure memory. SATIN stores the wake-up time of each core in the wake-up time queue and requires each wake-up core to check the queue to get next wake up time. For the devices with n cores, the wake-up time queue contains n wake-up time slots. Each time value is determined by the rule discussed in 3.4.3. The initial wake-up sequence of all CPU cores is set during the trusted booting process. Then when any core enters the self activation module, it picks the next time based on a random assignment. Once all core extract their assigned slots from the queue, the self activation module refreshes the queue with n newly generated time values and newly generated random assignment. By flushing the wake-up time queue and re-assigning the time slots to each core, we can use all cores for kernel introspection while prevent the normal world from knowing the awake core or awake time for the next round of introspection. Finally, all cores can coordinate to make sure each core inspects a random memory area at a random wake-up time.

## 3.5 SATIN Evaluation

## 3.5.1 SATIN Implementation

To verify the effectiveness of SATIN on defeating TZ-Evader, we develop a prototype of SATIN on the ARM Juno r1 development board with the same configuration as mentioned in Section 3.3.1. We modify the Test Secure Payload in S-EL1 to implement the major modules of SATIN.

## 3.5.1.1 Self Activation Module