**Doctoral Dissertation**

# Low-Cost Deep Convolutional Neural Network Acceleration with Stochastic Computing and Quantization

Hyeonuk Sim

Department of Computer Science and Engineering

Ulsan National Institute of Science and Technology

2021

# Low-Cost Deep Convolutional Neural Network Acceleration with Stochastic Computing and Quantization

Hyeonuk Sim

Department of Computer Science and Engineering

Ulsan National Institute of Science and Technology

# Low-Cost Deep Convolutional Neural Network Acceleration with Stochastic Computing and Quantization

A dissertation submitted to Ulsan National Institute of Science and Technology in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Hyeonuk Sim

12/07/2020 of submission

Approved by

Advisor

Jongeun Lee

# Low-Cost Deep Convolutional Neural Network

# Acceleration with Stochastic Computing and Quantization

Hyeonuk Sim

This certifies that the dissertation of Hyeonuk Sim is approved.

12/07/2020 of submission

Signature

Advisor: Jongeun Lee

Signature

Kyuho Lee: Committee Member #1

Signature

Myeongjae Jeon: Committee Member #2

Signature

Sam H. Noh: Committee Member #3

Signature

Woongki Baek: Committee Member #4;

#### Abstract

For about a decade, image classification performance leaded by deep convolutional neural networks (DCNNs) has achieved dramatic advancement. However, its excessive computational complexity requires much hardware cost and energy. Accelerators which consist of a many-core neural processing unit are appearing to compute DCNNs energy efficiently than conventional processors (e.g., CPUs and GPUs). However, a huge amount of general-purpose precision computations is still tough for mobile and edge devices. Therefore, there have been many researches to simplify DCNN computations, especially multiply-accumulate (MAC) operations that account for most processing time.

Apart from conventional binary computing and as a promising alternative, stochastic computing (SC) was studied steadily for low-cost arithmetic operations. However, previous SC-DCNN approaches have critical limitations such as lack of scalability and accuracy loss. This dissertation first offers solutions to overcome those problems. Furthermore, SC has additional advantages over binary computing such as error tolerance. Those strengths are exploited and assessed in the dissertation.

Meanwhile, quantization which replaces high precision dataflow by low-bit representation and arithmetic operations becomes popular for reduction of DCNN model size and computation cost. Currently, low-bit fixed-point representation is popularly used. The dissertation argues that SC and quantization are mutually beneficial. In other words, efficiency of SC-DCNN can be improved by usual quantization as the conventional binary computing does and a flexible SC feature can exploit quantization more effectively than the binary computing. Besides, more advanced quantization methods are emerging. In accordance with those, novel SC-MAC structures are devised to attain the benefits.

For each contribution, RTL implemented SC accelerators are evaluated and compared with conventional binary implementations. Also, a small FPGA prototype demonstrates the viability of SC-DCNN. In a rapidly changing and developing deep learning world headed by conventional binary computing, multifariously enhanced SC, though not as popular as binary, is still competitive implementation with its own benefits.

## Contents

| I. Introduction                                            | 7  |

|------------------------------------------------------------|----|

| II. Background and Related Work                            | 10 |

| 2.1. Deep Convolutional Neural Network Accelerators        | 10 |

| 2.2. Stochastic Computing                                  | 11 |

| 2.3. Dynamic Precision and Logarithmic Quantization        | 12 |

| III. Scalable, Accurate, and Efficient SC-DCNNs            | 14 |

| 3.1. Binary-Interfaced Stochastic Computing                | 14 |

| 3.2. New Stochastic Computing Multiplication Algorithm     | 17 |

| 3.3. Evaluation                                            | 23 |

| IV. Stochastic Computing in Synergy with Quantization      | 36 |

| 4.1. Dynamic Precision Scaling                             | 36 |

| 4.2. Log-Quantized Stochastic Computing                    | 42 |

| 4.3. Successive Log-Quantization and Its Application to SC | 46 |

| 4.4. Evaluation                                            | 53 |

| V. Conclusion                                              | 71 |

| References                                                 | 72 |

## **List of Figures**

| 1.  | A generic accelerator for convolution layers                   | 10  |

|-----|----------------------------------------------------------------|-----|

| 2.  | SC multiplication example                                      | 11  |

| 3.  | Signed and bit-parallel SC multiplication example              | 11  |

| 4.  | Structure of a MAC unit                                        | 16  |

| 5.  | How new SC multiplication works                                | 17  |

| 6.  | Simple and accurate low-discrepancy code generation using FSM  | 19  |

| 7.  | Our SC-MVM and operation                                       | 21  |

| 8.  | Convolution layer tiled along three loop levels                | 22  |

| 9.  | Area breakdown of a MAC                                        | 24  |

| 10. | Recognition accuracy vs. stochastic bitstream length           | 26  |

| 11. | Area-delay product comparison (SBL: 128-bit)                   | 27  |

| 12. | Error statistics of various SC multipliers                     | 28  |

| 13. | MNIST, CIFAR-10 recognition accuracy                           | 29  |

| 14. | Comparison of MAC arrays                                       | 31  |

| 15. | Block diagram of MVM-based accelerator implementation on VC707 | 34  |

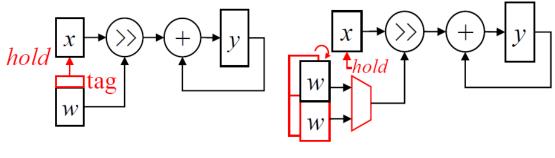

| 16. | DPS SC-MAC                                                     | 37  |

| 17. | Supporting HRS mode for <i>x</i> along with the normal mode    | 39  |

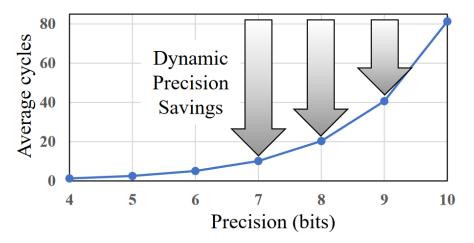

| 18. | Dynamic precision can give huge boost in efficiency for SC     | 41  |

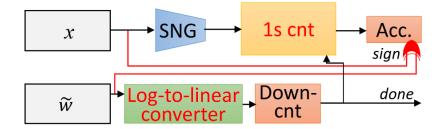

| 19. | Proposed log-quantized SC-MAC                                  | 42  |

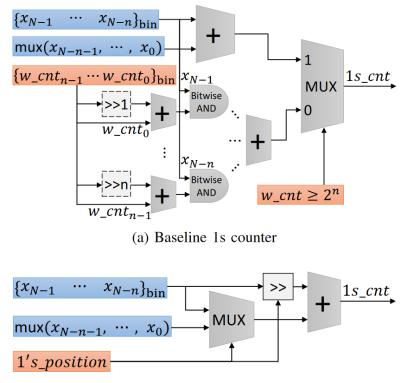

|     | Logic implementation comparison of 1s counter                  |     |

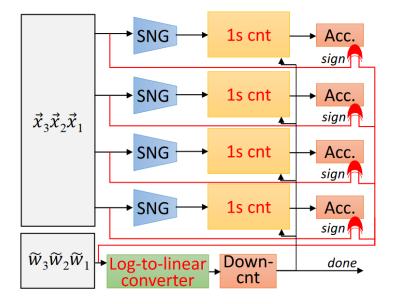

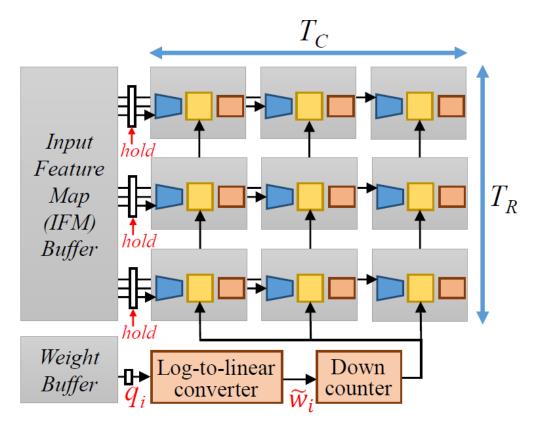

| 21. | Proposed log-quantized SC-MVM                                  | -44 |

| 22. | Multiplication error against floating-point weights            | -45 |

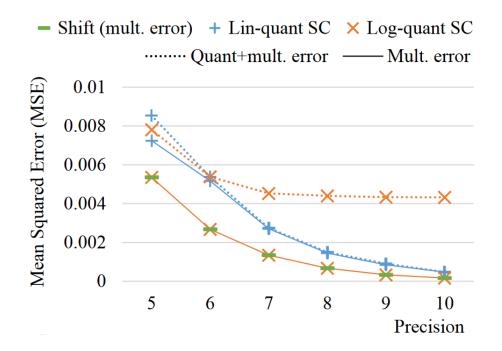

| 23. | Quantization error comparison                                  | 47  |

| 24. | New SC-MAC                                                     | 48  |

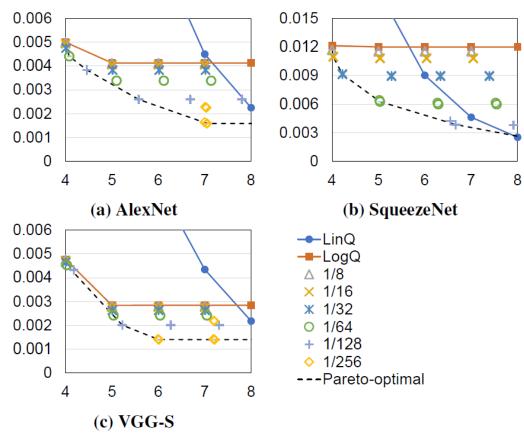

| 25. | RMS error vs. L                                                | 50  |

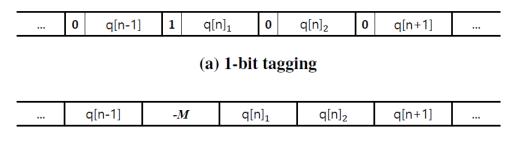

| 26. | Encoding schemes                                               | -50 |

| 27. | Conventional-binary MAC with SLQ                               | 51  |

| 28. | SC-MVM using SLQ for weight parameters                         | 52  |

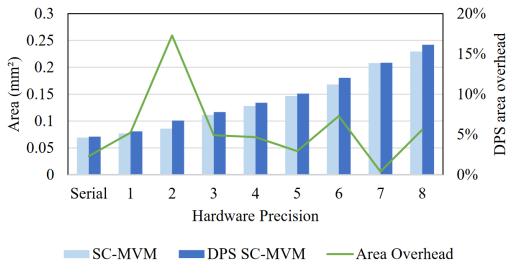

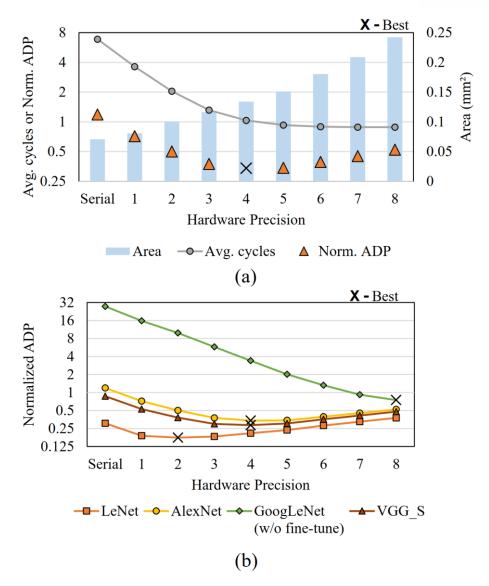

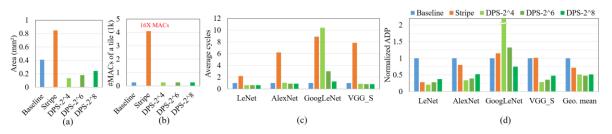

| 29. | Area overhead of DPS-MVM                                       | 54  |

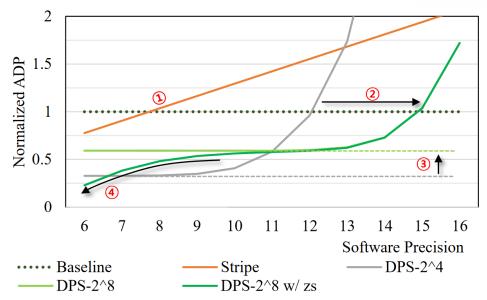

| 30. | ADP vs. software precision                                     | 55  |

| 31. | ADP vs. hardware precision                                     | 56  |

| 32. | Comparison with the digital baseline and Stripe [35]           | 57  |

# SCIENCE AND TECHNOLOGY

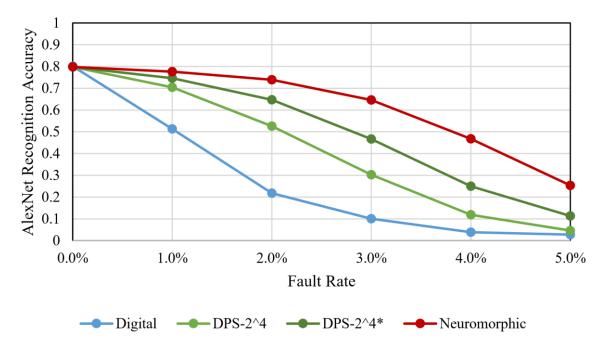

| 33. | Comparison with previous SC-DCNN on AlexNet58                      |

|-----|--------------------------------------------------------------------|

| 34. | Fault tolerance comparison among different schemes, for AlexNet59  |

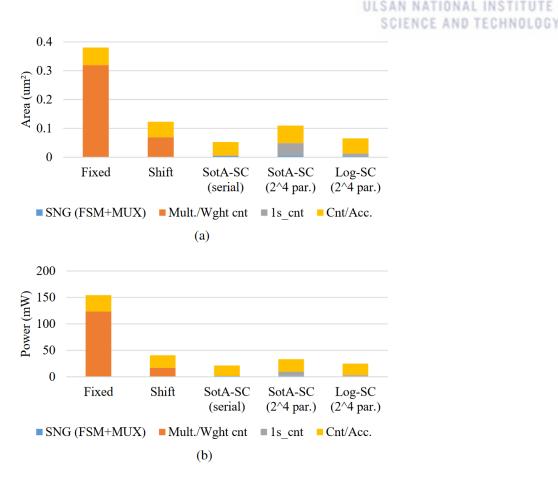

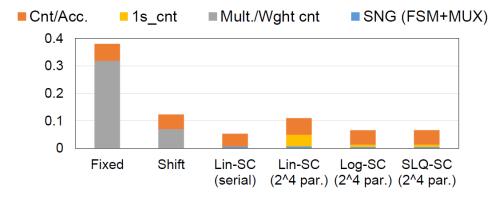

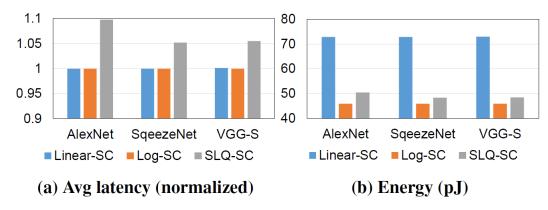

| 35. | Area and power breakdown of MVMs61                                 |

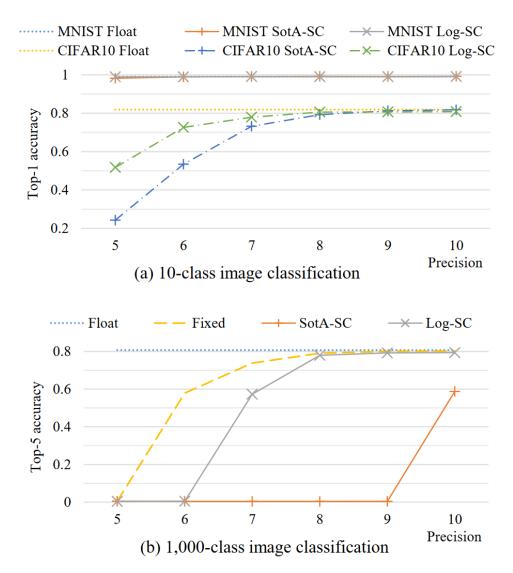

| 36. | Recognition test on target DCNNs fine-tuned for 5,000 iterations62 |

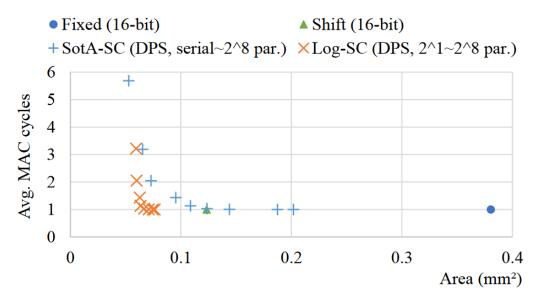

| 37. | Area and latency Pareto-optimal points of MVMs64                   |

| 38. | RMSE vs. effective resolution65                                    |

| 39. | Area breakdown (um <sup>2</sup> )68                                |

| 40. | Latency and energy comparison of SC-DCNNs68                        |

### **List of Tables**

| 1.  | Logarithmic data representation example                         | -13 |

|-----|-----------------------------------------------------------------|-----|

| 2.  | Signed multiplication example                                   | 20  |

| 3.  | Compute tile synthesis results                                  | 25  |

| 4.  | Area breakdown of a MAC (synthesis result)                      | 31  |

| 5.  | Comparison with previous neural network accelerators            | 33  |

| 6.  | Comparison of various MVM implementations on FPGA               | 35  |

| 7.  | Comparison of linear vs. logarithmic quantization               | 46  |

| 8.  | Quantization examples                                           | -49 |

| 9.  | Recognition accuracy (for 10K images) and DPS precision setting | -57 |

| 10. | Geo-mean latency and energy consumption comparison              | 63  |

| 11. | SC-DCNN classification accuracy (top-5, unit: %)                | -66 |

| 12. | Model size comparison (convolution layers only)                 | -67 |

| 13. | SLQ on SC vs. conventional binary DCNN                          | -69 |

#### I. Introduction

Deep convolutional neural networks (DCNNs) [1]-[4] are showing dominant image classification performance. However, those abilities are not free. In fact, computation costs are expensive. DCNNs contain dozens of layers which consist of millions of neurons and weights. The complexity of appearing networks is increasing fast even now. In energy constrained system, such as a mobile phone, the problem becomes more significant while the demand for the deep learning on edge devices rises. That is why the necessary of new computing paradigms, for instance, approximate computing, is being magnified.

Stochastic computing (SC) is also well known as a low-cost computing paradigm. Stochastic number is generated from stochastic number generator (SNG) and represented as a bitstream, whose positive signals (1s in digital implementation) occur with the frequency of its value. Unlike multi-bit binary numbers that is without time domain, the bitstream can be carried on a single wire over a period of time, which is reminiscent of analog computing, yet at the same time, SC circuits can be entirely made out of digital components. The bitstream is also called signal probability. The placement of 1s is assumed as random and there are no positional weights among bits, that is, all positions have the equal weight. This property gives SC circuits unique strengths in terms of (i) better error resilience. Because the number is represented as frequency of 1s, the longer bitstream can produce the more precise number. It enables (ii) free, dynamic trade-off between performance, accuracy, and energy. The bitstream itself may be arranged in series, in parallel, or in some combination of the two. The most popular advantage of SC is (iii) simple multiplication which consumes much costs in conventional binary computing, where the majority of computations are multiply-accumulate (MAC) operations in DCNNs. In SC, an AND gate simply outputs the bitstream which has the probability that equals to the multiplication of two input streams, in contrast to a complex binary multiplier. The outcome might not be exact but DCNNs tolerate some level of computation error. There are weaknesses too. SC inherently contains computation error coming from the probability. When high precision or accuracy is required, processing cycles can be increased without hardware modification, that is an advantage, but it ultimately leads to long latency. When it comes to precision, an *n*-bit fixed-point number requires  $2^n$  cycles to be represented as a stochastic number.

SC is seen as a promising approach to accelerating certain applications including deep neural networks [5]-[9] where exact computation is not required. Previous work on SC-based neural networks has shown the viability of SC in the context of neural networks, and proposed ideas on overcoming certain limitations of SC [7]-[9]. However previous work has some critical limitations, such as the fully-parallel architecture assumption and using fully-connected networks only. This prevents the previous solutions from being applicable to recent DCNNs. There are at least three problems in applying previous SC-based neural network solutions to DCNNs. First, DCNNs typically consist of many layers, with

GoogLeNet [4] having more than a hundred layers. It is virtually impossible to implement all the layers in parallel using dedicated hardware on a single chip even in SC. Second, DCNNs have many layer types whose SC versions are unknown. Examples include max-pooling layer (due to the difficulty of doing comparison in SC), ReLU (Rectified Linear Unit) layer, and local response normalization (LRN) layer. Third, even if one solves the first two problems, it remains uncertain whether the accuracy will be high enough. No one has shown that SC-DCNNs can achieve even similar recognition performance as conventional binary designs. This is a very critical issue, as low-performing neural network has very little value. As a first step towards evaluating the feasibility of SC for DCNNs, the dissertation considers a hybrid design where only part of the architecture is in SC. Clearly this marks an important departure from earlier work on SC-based neural networks to support DCNNs at scale. For large DCNNs or when the target DCNN is not known, one must use a more general architecture, which essentially executes an array of MAC operations repeatedly while simultaneously accessing on/off-chip memory for intermediate results. Still, there should be also a solution to produce stable and better accuracy by SC.

On the other hand, quantization becomes crucial and takes a significant role for reducing both model size and the complexity of DCNN calculations [10]-[11]. The idea is prompted by the fact that neural networks do not require single or double precision of floating-point all the time. As a matter of fact, the requirements depend on the application, layer, etc. As DCNNs grow more complex and diverse, there is a need for a more reconfigurable hardware architecture that can run various DCNNs with different precision requirements at high efficiency. This is particularly useful for SC, where 1-bit saving could reduce computation latency by 50%, suggesting a great potential for higher efficiency on DCNNs with layers of different precision requirements. This dissertation presents a SC-DCNN accelerator that is not only highly efficient for large DCNNs but also very flexible in terms of supporting various DCNNs with different precision requirements.

Besides, there are advanced quantization methods appearing. One particular representation of interest is logarithmic quantization [12]-[13], which is to place quantization points in logarithmic scale. This can be achieved by quantizing the exponent of a number (throwing away the mantissa part). The latest work on this shows [14] that logarithmic quantization can reduce the precision of weight parameters by a few bits as compared to linear (fixed-point) quantization with the comparable accuracy of large DCNNs. The dissertation proposes to use logarithmic quantization to SC-DCNNs. It goes one step further which combines the advantages of both schemes, simpler hardware of logarithmic quantization and high precision of linear quantization, by suggesting a new quantization method.

This dissertation makes following contributions which are based on a series of published papers authored by the writer of this dissertation [15]-[20].

- It is argued that for scalability, it is essential to have some elements designed in conventional binary representation. Based on this, a scalable SC-based accelerator architecture for DCNNs, called binary-interfaced SC (BISC), is proposed.

- A novel SC multiply algorithm for BISC is presented and turned into a vectorized form called BISC-MVM (Matrix-Vector Multiplier). It improves both the efficiency and accuracy of SC considerably.

- A dynamic precision scaling (DPS) SC-DCNN accelerator is designed, which extends BISC-MVM, such that the precision of input/output data can be arbitrarily changed at runtime. The extension has very little overhead, but allows SC-MAC to be efficiently parsimonious in terms of precision, with an exponential reward in latency due to SC.

- Logarithmic quantization is applied to SC-DCNN and design improvement of the accelerator correlated to the quantization is made demonstrating that also in SC, there is no handicap for logarithmic quantization compared to linear (fixed-point binary).

- A new quantization method, called successive log-quantization (SLQ), is presented which solves the problem that, increasing resolution, or the bitwidth of log-quantized words quickly saturates accuracy due to uneven precision distribution.

- Experimental results demonstrate the feasibility of proposed SC-based DCNNs basically in terms of area-delay-product (ADP) and network accuracy. There are additional experiments on error resiliency which is a benefit of SC. Finally, a small FPGA prototype, validates our new SC multiplication algorithm's correctness as well as its implementation efficiency on an FPGA.

Section II provides the backgrounds and related works on DCNN acceleration, SC, and quantization. In Section III, we presents methods for enhancing SC-DCNN with those evaluations. Section IV demonstrates how SC can take the advantage of quantization effectively and presents state-of-the-art efficiency over fixed-point binary implementation in terms of ADP. Lastly, the dissertation concludes in Section V.

#### **II. Background and Related Work**

#### 2.1. Deep Convolutional Neural Network Accelerators

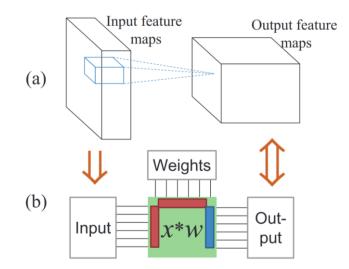

Let us consider one convolution layer as convolution layers in a typical DCNNs account for more than 90% of the MAC operations. The computation in a convolution layer can be seen as a transformation from one 3D array of data called input feature maps to another 3D array called output feature maps, as illustrated in Figure 1-(a). Each element of the output array is computed by the 3D convolution between the input array and the weight matrix, followed by a bias addition. Different output array elements are created by applying the same convolution operation for different input subarrays or different weight subarrays. With limited resources, not all neurons can be simultaneously active, causing resources to be shared among different neurons. Hence using a good architecture can make a difference in terms of performance and energy efficiency. Several architectures for neural network acceleration have been proposed in the domain of conventional binary computing [21]-[24]. One important point here is that the input/output feature maps can be very large, and is stored in the off-chip memory in the general case. The off-chip memory may have sufficiently large capacity, but accessing it requires memory bandwidth, which is often quite limited. Another factor is on-chip buffer size. In general, there can be three on-chip buffers, for input, output, and weight parameters (see Figure 1-(b)), and unless the entire data can fit in the buffer, buffers need to be double-buffered to hide the off-chip memory access latency. The computation itself is very simple. We need no operation but a number of MAC operations. Accelerators are often built around an array of hardware MAC units, which can be organized as simply as a 1D array or a 3D array. The exact shape (such as 1D vs. 2D) and the size of the MAC array, along with the hyper-parameters of each layer (number of neurons, size of filters, etc.), affect the performance of the accelerator.

Figure 1: A generic accelerator for convolution layers.

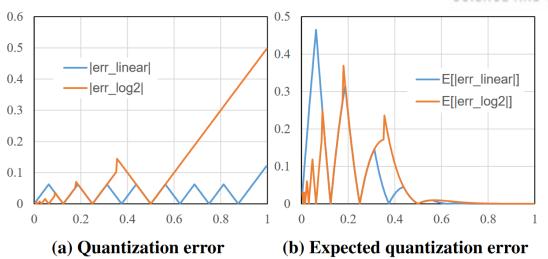

#### 2.2. Stochastic Computing

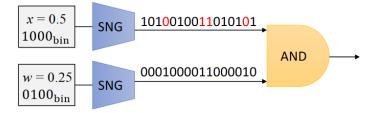

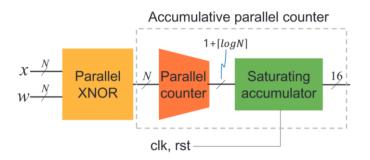

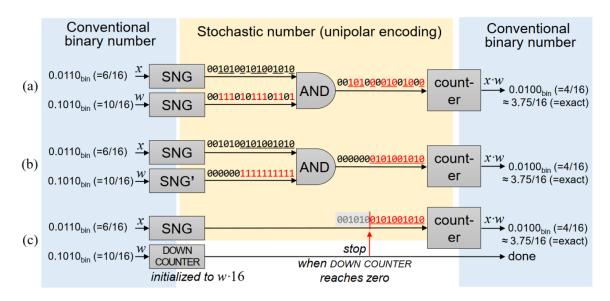

SC is not grown-up technology yet so that here we introduce SC backgrounds. Considering Figure 2, stochastic number is represented by bitstream which have the target probability. Stochastic number generator (SNG) converts conventional binary number into bitstream when the inputs are given as binary numbers. An AND (XNOR in case of signed multiplication) gate computes multiplication between 2 input streams. 1s in the output stream can be counted as converted into the conventional binary number of 1s' frequency. Computation with negative values can be done with bipolar format easily. To reduce the long latency of SC-MAC, bit-parallelism which computes several stochastic cycles at one time is applied as Figure 3. A parallel counter is used to count 1s of parallel streams.

Figure 2: SC multiplication example.

Figure 3: Signed and bit-parallel SC multiplication example.

As early as in 1994, SC was applied to implementing neural networks on a then resource-limited FPGA [25]. Circuit elements for SC are described in [26], with a companion paper [27] giving a neural network design as an example. Recently SC has been applied in designing Deep Belief Networks [8], [28] and other non-DCNN-type fully-connected neural networks [9], [29]. Previous work on SC-based acceleration of deep neural networks can be classified into the category: fully-parallel. In the fully parallel approach, all neurons are implemented spatially and they operate in parallel such that the neural network circuit will produce output as the wave of input data sweeps through the circuit. It can have very high energy efficiency owing to the fact that it does not involve external memory access to store intermediate result, but has limited applicability because it cannot support arbitrarily large networks.

We target DCNNs, which are more widely used today but much more complicated than the aforementioned fully-connected types of neural networks. The StoRM approach [30] is similar to ours in that both focuses on a MAC array. However, our proposed techniques are tied to DCNNs, and designed to improve scalability and accuracy of SC-DCNN accelerators whereas [30] is not.

#### 2.3. Dynamic Precision and Logarithmic Quantization

Many techniques have been proposed to address the high computational complexity of deep neural networks DCNNs. At the algorithm level, researchers have proposed model reduction such as low-rank approximation, which can reduce complexity with little impact on accuracy. It is also shown that storage requirement due to weight parameters can be reduced to its 5 to 10% level [31], which may alleviate memory bottleneck problem. However, these techniques are effective mainly for fully-connected layers, with much less success with convolution layers, which account for the majority of computational complexity. At the implementation level, reducing the precision of arithmetic operations can reduce hardware cost, without significantly affecting accuracy. Approximate computing has also been applied to some of the neurons [32], which may be exploited to improve energy efficiency of neural network accelerators. All these results strongly suggest that current DCNN models are highly redundant, and essentially the same recognition performance can be achieved through retraining with much less weight parameters and less precise computation. That is why we may expect higher energy efficiency through SC, which is known to be more efficient for low-precision computation.

Recent DCNN hardware implementations [23], [33]-[34] all have their precision fixed at design time. This has obvious disadvantages when the precision requirement is different, such as low accuracy (when the needed precision is higher) and lower efficiency than achievable (when lower). Also, since these DCNN accelerators have tile-based architectures, all layers must use the same precision. However, the precision requirement of layers can be quite different [35], which causes some inefficiency even when the accelerator is running the DCNN for which it is designed. One solution to these problems is to use bit-serial hardware such as bit-serial multiplier [35] which can calculate the inputs of dynamic precisions at different runtime. While this approach can solve the abovementioned problems, bit-serial multipliers are inherently inefficient compared with a bit-parallel version except in low precision, which limits the effectiveness of the approach. The dissertation proposes to exploit dynamic precision for SC. The effect could be higher in SC than in conventional digital, since 1-bit reduction in SC may reduce delay by up to 50%.

There is an emerging format of quantization, logarithmic quantization. There are many applied logarithmic quantization researches on deep neural networks [12]-[14], [36]-[39]. [12] introduces logarithmic quantization for activation and weight, showing their acceptable network accuracy. [13]-

[14], [38] include hardware implementation results. [37] proposes an automation methodology of quantization. [14] shifts logarithmically quantized network accuracy really close to the level of floating-point. [39] applies logarithmic quantization to the biomedical image segmentation. Their logarithmic base is 2 by default to calculate the multiplication of linear (fixed-point) input activation and logarithmic weight by a shifter which is usually much smaller than a fixed-point multiplier. When, extreme cases, recognition rate is not acceptable, choosing more fine-grained base (e.g.,  $\sqrt{2}$ ) can improve it [12]. We explain how weights are represented in detail. Suppose maximal data precision is 16-bit (including sign bit). *w* is a real number of weight and ranges (-1, 1) because weights are distributed near 0 and the magnitude is mostly less than 1. Logarithmic representation  $\tilde{w}$  is sign-magnitude formatted so that 1-bit is used for a sign. The magnitude is  $|\tilde{w}|=\text{round}(-\log(|w|))$ . Because  $\tilde{w}$  is saved as an integer, the real logarithmic value is rounded. How many bits would be required for the magnitude? Because |w|<1,  $|\tilde{w}|$  is larger than 0. The least unit that can be represented by 16-bit (including sign bit) is  $1/2^{15}$  resulting  $|\tilde{w}|=15$ .  $|\tilde{w}|$  ranges [1,15] except when *w*=0. Covering this range, 4-bit unsigned integer ranges [0,15]. 0, which is not assigned yet, can represent the case where *w*=0. The complete equation is

$$|\tilde{w}| = \begin{cases} \operatorname{round}(-\log(|w|)). & \text{if } w \neq 0 \\ 0 & \text{otherwise} \end{cases}$$

In conclusion,  $16 \rightarrow 5$  data size reduction happens. To help understanding, Table 1 gives representation examples.

| w          | ilde w   |               |                  |

|------------|----------|---------------|------------------|

| Real value | Sign bit | $ \tilde{w} $ | Binary format    |

| -0.5       | 1        | 1             | 1 0001           |

| 0          | 0 or 1   | 0             | 0 0000 or 1 0000 |

| 0.25       | 0        | 2             | 0 0010           |

Table 1: Logarithmic data representation example.

#### III. Scalable, Accurate, and Efficient SC-DCNNs

#### 3.1. Binary-Interfaced Stochastic Computing

#### 3.1.1. Tile-Parallel Architecture for Scalability

Previous work on SC-neural networks [8]-[9], [28] has assumed that every layer and neuron can have dedicated resources. At the same time, since the networks they use are all fully-connected, it means that the application throughput is one (e.g., 1 image per cycle), and there is no need to buffer any intermediate result for any extended length of time. This is an ideal situation in terms of energy efficiency, since no memory and no resource sharing mean almost no power dissipation for anything but computation. Such a fully-parallel architecture may be realizable for special applications where the area budget is large and the size of the neural network is small. It may also be how biological neural networks operate. However, for low-cost embedded applications and/or if targeting real-life DCNNs, the fully-parallel architecture quickly becomes very irrelevant. We need an architecture that can support large DCNNs as well. A typical solution is to partition computation into multiple equal-sized blocks (or tiles) in a manner analogous to loop tiling, and to design hardware for one computation tile. Such hardware requires on-chip buffers for fast processing, but on-chip memory is invariably too small to hold entire data even for one layer. Double buffering is commonly employed, where on-chip buffers hold only the portion of the data currently needed while the entire layer data are stored in the off-chip memory. The on-chip buffers should be large enough to hide the data transfer latency. In this paper we call such an architecture tile-parallel architecture.

#### 3.1.2. Rationale for Binary-Interfaced Stochastic Computing Design

Compared with conventional binary, SC uses much less resources for computation but requires far more cycles to achieve an equivalent resolution. The simplicity of SC circuits can help achieve higher clock speed. Let us assume that SC needs  $2^k$  bits to get a similar resolution of k-bit fixed-point implementation in the conventional binary. One can see that from the throughput point of view, SC can beat conventional binary when k is low. When it comes to handling data, such as storing them on-chip or sending them to off-chip, conventional binary is more efficient for any value of k, although a conventional binary representation may also be more susceptible to errors. Thus fully-stochastic design such as in [8], [9] is largely incompatible with the idea of tile-parallel architecture. Otherwise the overhead in on-chip memory capacity and off-chip bandwidth can be many-fold: as much as 32X for k=8, and 4X even when k=4. Further, given that a large portion of the die area is dedicated for on-chip memory rather than the MAC array itself [23], the many-times increase in overhead in the case of fullystochastic design seems simply too high. Thus, we conclude that for scalable architecture it is necessary

to have binary-interfaced design. We assume that the conversion from stochastic bitstreams to binary numbers happens before they are saved to on-chip memory.

#### 3.1.3. Our Proposed Architecture: Doubly Hybrid

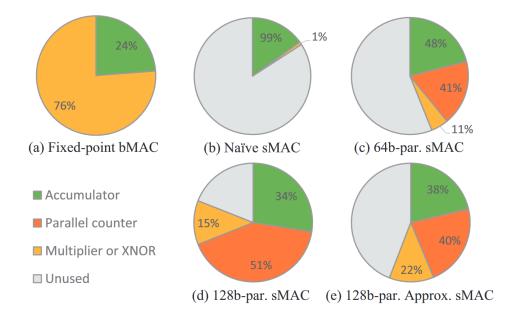

1) Binary-Interfaced SC for Scalability: Our DCNNs accelerator uses SC for the MAC array only, converting the input and weights from conventional binary to SC bitstreams, and converting back the output bitstreams to binary. Coincidentally this helps us avoid implementing other layers in SC, such as max-pooling layer, ReLU layer, and LRN layer, which can be tricky to implement in SC. We perform even the accumulation (of a MAC operation) using conventional binary arithmetic, utilizing SC for multiplication only. Multiplication is quite important, accounting for 76% of the area in our synthesis result for a conventional-binary MAC design (see Figure 9-(a)). Thus, even with this hybrid approach we can expect some efficiency improvement.

Perhaps one of the biggest downsides of this scheme is the conversion overhead between SC and conventional binary. It is not that there are unnecessarily many converters all around the accelerator; physically, there is only one array of binary-to-stochastic (B-to-S) converters and one array of stochastic-to-binary (S-to-B) converter, as shown in red/blue blocks in Figure 1-(b). But these converters are used for every layer of a DCNN, which may seem redundant and unnecessary from the viewpoint of a fully-parallel, fully-stochastic-computing accelerator. However, we see this as a fair price to pay, necessary to support large DCNNs on a small accelerator. Also, the B-to-S overhead can be amortized by sharing resources such as LFSRs (Linear Feedback Shift Registers) across the MAC array, or reduced significantly by using emerging devices such as magnetic tunnel junction (MTJ) transistors [40]. We address the S-to-B overhead by using approximation and bit-parallel SC design (see Section 3.1.4).

2) Hybrid Layer Composition for Accuracy: The other feature of our architecture is that SC is applied to convolution layers only whereas fully-connected layers use conventional binary, which is one form of what we term hybrid layer composition. This is the rationale. The number of MACs in the fully-connected layers of a DCNN is usually very small, but just because they are very close to the output, they can have a direct impact on the final outcome. Using conventional binary for the fully-connected layers can therefore ensure high accuracy, while using SC for convolutional layers can increase cost-effectiveness, thus striking a good balance between accuracy and efficiency. Though simple, it does not cost any more hardware and works surprisingly well.

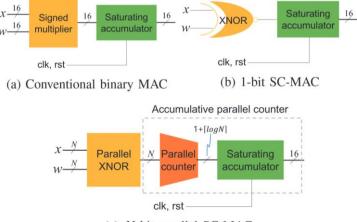

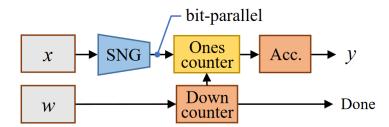

#### 3.1.4. SC-MAC Unit: Minimizing Overhead with Parallelism and Approximation

Figure 4 illustrates our SC-MAC design in comparison with a conventional binary one. In SC, multiplication and addition can be performed very cheaply by an XNOR gate and a MUX, respectively [26]. The problem is that they are too small, compared with the ensuing S-to-B converter, which is typically done by a counter. This counter can also serve as the accumulator, leading to a very simple 1bit SC-MAC design as shown in Figure 4-(b). But in this design the overhead of the accumulator (also serving as a counter) can be nearly 100 times (see Figure 9-(b)), in terms of area according to our evaluation. We address this problem by employing bit-parallel SC design and approximation. An N-bit parallel SC design allows us to share the accumulator among N 1-bit SC-MACs, essentially reducing the accumulator overhead by N times. However, in a bit-parallel version we need an explicit counter, such as an N-bit parallel counter, as illustrated in Figure 4-(c). Since the size of the accelerator is largely unchanged regardless of N, we can reduce the accumulator overhead very effectively with bitparallelism. The parallel counter overhead, however, is a different story, which we tackle using approximation. Nonetheless by putting together a parallel counter and an accumulator, which are together known as accumulative parallel counter, we can exploit known circuit optimization techniques such as [41] to achieve higher operating frequency and smaller area. The parallel counter overhead cannot be reduced by going parallel, because it increases in proportion to N. Instead we use an approximate S-to-B method [42]. The idea is to reduce N bits into N/2 bits with approximately half the number of "one"s. While this can nearly halve the parallel counter overhead, it has a side effect that lowering the recognition accuracy, as a result of which we may end up using a longer bitstream, defeating the purpose of using approximation. Thus, we need a careful evaluation to assess its effectiveness (see Section 3.3).

(c) N-bit parallel SC-MAC

Figure 4: Structure of a MAC unit. Our SC-MAC integrates a stochastic-to-binary (S-to-B) converter

(i.e., parallel counter).

#### 3.2. New Stochastic Computing Multiplication Algorithm

#### **3.2.1.** Conventional Stochastic Computing Multiplication

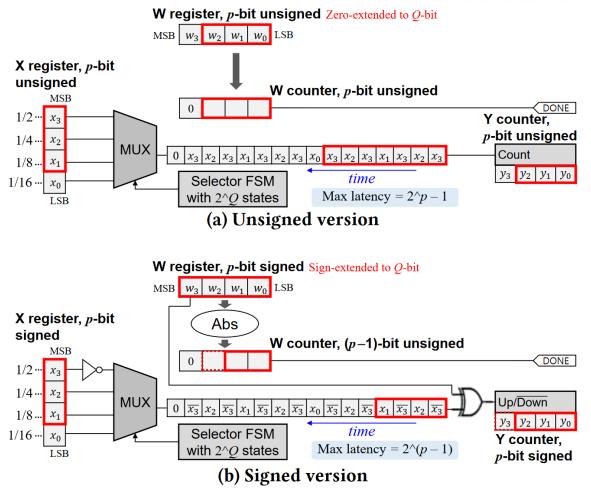

Figure 5-(a) illustrates conventional SC multiplication which is conducted in Section 3.1. In SC, a number is represented by a bitstream, whose signal probability, or the frequency of 1, determines its value depending on the range, which is known *a priori*. Popular choices for the range include [0,1] called unipolar and [-1,1] called bipolar. An SNG, which is synonymous to B-to-S converter, takes an *N*-bit binary number and generates a stochastic bitstream, and it typically consists of a random number generator such as an *N*-bit LFSR and an *N*-bit comparator, which generates 1 if the random number is less than the input binary number, and 0 otherwise [43]. An AND gate can perform multiplication for unipolar encoding if the input SN bitstreams are statistically uncorrelated with each other. An XNOR gate does the same for bipolar encoding. Finally, a bit-counter converts a unipolar stochastic number to a binary number. An up-down counter does the same for bipolar.

Figure 5: How new SC multiplication works.

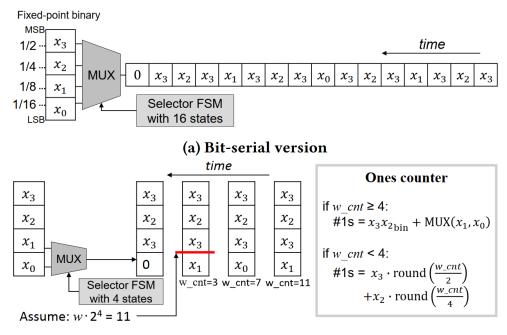

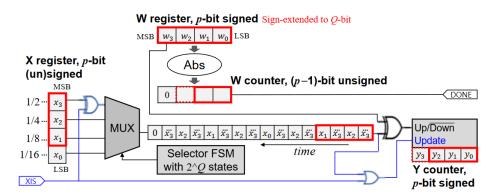

#### 3.2.2. Our Proposed SC-MAC

Suppose we reorder the bits for one input w such that all the 1s appear first as illustrated in Figure 5-(b). Certainly, it does not affect the value of stochastic number for w or that of the resulting stochastic number after the AND operation, if the two stochastic numbers are still statistically uncorrelated. Therefore, the binary number outcome in Figure 5-(b) is expected to be the same as that of Figure 5-(a). Note that the order of stochastic number bits for the other input x does not affect the outcome either as long as it is randomized.

Now since we know that all the zeros in the SN bitstream for w and the corresponding bits for x will have zero contribution to the final outcome, we can skip those bits altogether. This observation leads to the alternative method illustrated in Figure-(c), which connects an SNG directly to the bit-counter that is activated for  $w \cdot 2^N$  cycles only.

This new SC multiplication method works only for unipolar encoding and is relevant to BISC only, but it has the following important advantages. First, its design is simpler as it eliminates an SNG and an AND gate in exchange for a down-counter, which is much less than an SNG. Second, it enables sharing of some circuitry in an array version without losing accuracy at all, as given in Section 3.2.6. Third, it has a shorter average latency, again without losing any accuracy, as compared to the conventional method. Our SC multiplier illustrated in Figure 5-(c) can also be called SC-MAC, since the counter naturally accumulates results from consecutive multiplications. The counter only needs to have a wider width.

#### 3.2.3. Enhancing Accuracy via Low-Discrepancy Code

The accuracy of the binary number output in Figure 5-(c) depends on how uniformly the 1s are distributed in the stochastic number bitstream, suggesting a good use of low-discrepancy code such as Halton sequences [5]. Though low-discrepancy code has already been used in SC [5], [44], in previous work low-discrepancy code is limited to improving the accuracy of SNG only, with no guarantee on the accuracy of an SC operation's output. However, in our scheme the value of a stochastic number is the outcome of SC; therefore, the use of low-discrepancy code can directly improve the accuracy of our SC multiplier.

In addition to the strong guarantee on the accuracy of SC multiplier itself, which we quantify empirically, our SC multiplication result depends only on the distribution of bits, not on the order at all. This allows us to use a simple and deterministic bit shuffling scheme via an *N*-bit FSM (Finite-State Machine) and one MUX, which is in fact simpler than the conventional LFSR-comparator-based SNG and far simpler than a Halton sequence generator [5] (see Section 3.3.3).

Given an *N*-bit fractional number  $w \in [0,1)$ , let  $k = 2^N w$ . The accuracy objective for our SC multiplication in Figure 5-(c) dictates that the partial sum,  $P_k$ , of the stochastic number sequence  $\{X_i\}$  for x must satisfy  $P_k = \sum_{i=0}^{k-1} X_i \approx xk$  for  $\forall k$ . Since x is an N-bit binary number,  $x_{N-1} \cdots x_0$ , we have  $x = \sum_{i=1}^{N} 2^{-i} x_{N-i}$ , from which we can write the reference output, xk, as follows:  $xk = k \sum_{i=1}^{N} 2^{-i} x_{N-i} = \sum_{i=1}^{N} k/2^i \cdot x_{N-i}$ . A good approximation of this is  $\sum_{i=1}^{N} \text{round}(k/2^i) x_{N-i}$ .

We can design an FSM-MUX circuit such that the partial sum always equals this approximation, as illustrated in Figure 6-(a). The essence of the pattern generated by the FSM-MUX circuit is that  $x_{N-i}$  first appears at cycle  $2^{i-1}$ , and thereafter in every  $2^i$  cycles. It is proved that with this pattern, the number of

times  $x_{N-i}$  appears within the first k cycles equals round $(k/2^i)$ . The theoretical maximum error of our SC multiplication is  $\sum_{i=1}^{N} 1/2 = N/2$  for xk, or  $N/2^{N+1}$  for wx. But this error bound is not tight; instead, we show maximum error empirically in Section 3.3.3.

#### (b) Bit-parallel version: 4-bit parallel processing example (unsigned)

Figure 6: Simple and accurate low-discrepancy code generation using FSM.

#### **3.2.4. Extension to Support Signed Multiplication**

Our scheme can be extended to support signed multiplications, where both x and w as well as the output are represented in two's complement. The only major change is that the bitstream counter now becomes an up-down counter, counting up for input '1' and down for '0'. The other changes are minor. The sign bit of input x is flipped and XOR-ed with the sign bit of the other input w after being converted to sign-magnitude representation, and the magnitude part is fed to the down counter as before. The FSM-based bitstream generator can be used without modification.

To see how it works, let us consider the values of x and w listed in Table 2. In this example, N, the number of bits of each operand including the sign bit, which we call multiplier precision, is 4. Thus, the examples are for the max/min values of w. Our SC multiplier generates an N-bit two's complement number as output. Column 3 is the binary representation of x. After sign bit flipping, the MUX out is XOR-ed with the sign bit of w, which is fed to the up-down counter, whose value is read at cycle  $|2^{N-1}w|$  as the result of multiplication. When compared with the true multiplication result with sufficient precision in the last column, one can see that they are very close.

| $2^3 w$ | $2^3x$ | Binary | Sign-flipped | MUX out  | Counter | Ref. $(2^3 w x)$ |

|---------|--------|--------|--------------|----------|---------|------------------|

|         | 0      | 0000   | 1000         | 10101010 | 0       | 0                |

| -8      | 7      | 0111   | 1111         | 11111111 | -8      | -7               |

|         | -8     | 1000   | 0000         | 00000000 | 8       | 8                |

|         | 0      | 0000   | 1000         | 1010101  | 1       | 0                |

| 7       | 7      | 0111   | 1111         | 1111111  | 7       | 6.125            |

|         | -8     | 1000   | 0000         | 0000000  | -7      | -7               |

Table 2: Signed multiplication example.

#### 3.2.5. Bit-parallel Processing Optimization

To further reduce the latency of our SC multiplier, we propose bit-parallel processing. Let us consider the example in Figure 6-(b), where the degree of bit-parallelism, b, is 4, meaning that we process this bitstream in 4 cycles instead of 16. We first rearrange the  $2^N$ -bit sequence into a b-row,  $2^N/b$ -column matrix, and process each column in one cycle. Let w be the other operand (i.e., multiplier) of this multiplication. If  $w \ge b$ , we only need to know how many ones are included in the current column. Otherwise we need to count the number of ones in the top w bits. And we repeat this for the next column after decrementing w by b.

Counting the number of ones (i) in a column and (ii) in a sub-column, can be done by the formulas in the inset (called *ones counter*). To understand why, first notice that half the bits are  $x_3$ , and half the remaining ones are  $x_2$ . Thus for (i), the only variation is in the last row, which we can easily provide using a small FSM with  $2^N/b$  states. For (ii), we need to multiply *w* to the number of ones in the column, which we do using the approximation formula we derived in Section 3.2.3. Thus, our bit-parallel computation result is exactly the same as our bit-serial result.

Increasing bit-parallelism can reduce multiplier latency at the cost of hardware overhead. Therefore, the degree of bit-parallelism needs to be chosen carefully.

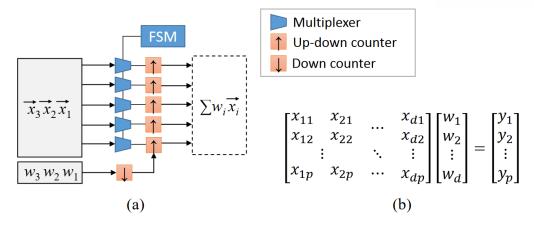

#### 3.2.6. Proposed BISC-MVM and SC-DCNN Accelerator

1) BISC-MVM, Vectorization of Our SC-MAC: Figure 7-(a) illustrates our BISC-MVM, which contains *p* parallel SC-MACs of *N*-bit multiplier precision. Each SC-MAC requires a MUX and an updown counter, whose width is *N*+*A* bits (*A* additional bits are for accumulation). All MUXes share the same control input, hence the same FSM. The down counter can be shared as well if the other operand, *w*, is common to all, as is the case with our BISC-MVM. This SC multiplier array can perform one scalar-vector multiplication,  $w\vec{x}$ , in  $|2^{N-1}w|$  cycles. Moreover, it can be used to calculate accumulation,  $\sum_{i=1}^{d} w_i \vec{x}_i$ , simply by feeding a sequence of  $\vec{x}$  and  $w_i$ ; no additional hardware is necessary. Then the accumulation result can be read from the array of up-down counters at cycle  $\sum_{i=1}^{d} |2^{N-1}w_i|$ .

Figure 7: (a) Our SC matrix-vector multiplier (simplified) and (b) the operation it performs, where  $y_j = \sum_i w_i x_{ij}$ .

Mathematically this is a matrix-vector multiplication in the form of Figure 7-(b). Our BISC-MVM has the following features. First, all SC multipliers share both the down counter and the FSM, but this causes no accuracy degradation, which is quite contrary to conventional SC. In addition, by sharing *w*, all SC multiplications finish simultaneously, which enables our BISC-MVM to retain the latency reduction feature of our single SC multiplier.

The high accuracy of our BISC-MVM can be attributed to the following. First our SC multiplier itself is highly accurate. Second, accumulation does not introduce any error, given that the up-down counter is wide enough. Third, sharing the FSM and the down counter does not introduce any error. At the same time, sharing certain resources makes our BISC-MVM more cost-efficient than a set of SC multipliers.

One potential downside of our BISC-MVM is that the particular matrix-vector multiplication in the form of Figure 7-(b) may not be how a neural network layer is typically described mathematically. We next discuss how this BISC-MVM can be applied to accelerate DCNNs.

2) Applicability to DCNN: The computation in convolution layers is typically represented as a 6deep nested loop of MAC operations. There are different ways to design an accelerator for the loop nest, but recent work [45] suggests that superior performance can be achieved by accelerating along three dimensions including the output feature map (M), the output width (C), and the output height (R). This is equivalent to tiling the loop as shown in Figure 8, where the 3 innermost loops are executed by a hardware accelerator as fully unrolled (i.e., simultaneously).

for

$$(m_1 = 0; m_1 < M; m_1 + = T_M)$$

for  $(r_1 = 0; r_1 < R; r_1 + = T_R)$

for  $(c_1 = 0; c_1 < C; c_1 + = T_C)$

for  $(z = 0; z < Z; z + +)$

for  $(i = 0; i < K; i + +)$

for  $(j = 0; j < K; j + +)$

for  $(m = m_1; m < \min(M, m_1 + T_M); m + +)$

for  $(r = r_1; r < \min(R, r_1 + T_R); r + +)$

for  $(c = c_1; c < \min(C, c_1 + T_C); c + +)$

$B[m][r][c] + W[m][z][i][j] × A[z][Sr + i][Sc + j]$

Figure 8: Convolution layer tiled along three loop levels. Arrays *A*, *B*, and *W* are input feature map, output feature map, and weight parameters, respectively, and *S* is stride.

This accelerator requires  $T_M T_R T_C$  number of MAC units, out of which every  $T_R T_C$  MACs use the same weight parameter W[m][z][i][j], which does not depend on either *r* or *c*. Thus, our BISC-MVM is wellsuited for this kind of architecture, and can be configured as  $p=T_R T_C$  and  $d=K^2 Z$ , generating *p* output feature map values in every *t* cycles, where

$$t = \sum_{z=0}^{Z-1} \sum_{i=0}^{K-1} \sum_{j=0}^{K-1} \left| 2^{N-1} W[m][z][i][j] \right|.$$

The actual latency reduction as compared to conventional SC (which requires  $2^N$  cycles for each multiplication) depends on the value of weight parameters. But it is a well-known fact that weight parameter values in a typical neural network layer including convolution layers are distributed in a bell-shaped form centered around zero, in which the average (of absolutes) is far less than the maximum. This leads to significant latency reduction as demonstrated in our experiments, which reinforces the suitability of our BISC-MVM for DCNN acceleration.

3) Our SC-DCNN Accelerator Architecture: Our SC-DCNN accelerator architecture is by design very similar to previous DCNN accelerators [45]-[46] based on conventional binary. In fact, there should be no difference in the top-level architecture from that of [45] in particular, since we use the same parallelization scheme for the nested loop. Even the on-chip memory sizes for input/output/weight buffers are exactly the same, which should make our comparison with binary implementation more credible. As in the previous work [15] we apply SC to convolution layers only, which account for 90~99% of computation of a DCNN, with no restriction on how the other layers are implemented.

#### 3.3. Evaluation

#### **3.3.1. Experimental Setup and Implementation Detail**

An evaluation of any SC design must consider both functional accuracy and the efficiency of hardware implementation. In the case of SC-DCNN, we also need to consider (re) training of weight parameters, which is really crucial as we will show. Fortunately for us, we were able to easily extend an existing DCNN model, Caffe [47], to generate a model of our SC-DCNN and use it for training and functional simulation, because our architecture retains the same interface as the conventional binary version.

To see the efficiency of hardware implementation we also designed and implemented our SC-MAC unit. We designed not just one SC-MAC unit, but an array of SC-MAC units, which we call compute tile or simply a tile, as needed in a DCNN accelerator. Again, because our SC-MAC compute tile has the same interface as its binary version, we can easily and accurately evaluate our proposal without necessarily building the entire system in hardware.

We use a DCNN designed for the MNIST digit recognition benchmark, which has been frequently used in previous work [8]-[9], [28]. Ours is based on a DCNN model distributed with Caffe, but modified by adding tanh-activation layers, in line with previous work using the same dataset.

1) MAC Design: We have implemented different MAC designs in Figure 4 using Verilog RTL. For bit-parallelism N, we use 64 and 128 (The approximate version is 128-bit only). In the binary MAC, we use fixed-point consisting of a 1-bit sign bit and a 15-bit fractional part. No integer part is necessary as values are between -1 and 1. The multiplier generates 16-bit signed number. The accumulator, which is shared with SC-MACs, uses 18 bits internally due to a 2-bit integer part, but the final output is given by the most significant 16 bits. The parallel counter is an up/down counter as our stochastic bitstream follows a bipolar representation.

For accurate area evaluation we have implemented the entire compute tile, including LFSR-based Bto-S, referred to as SNG (Stochastic Number Generator), and a MAC array, whose size is varied from 4x4x4 to 8x8x8. For synthesis we use Synopsys Design Compiler with TSMC 45nm technology. The target clock period is set to 0.65ns from the best achievable value by the binary MAC array. No pipelining is used inside a MAC unit.

2) Simulation and Training: We have extended Caffe with a new convolution layer definition and a new fully-connected layer definition based on our SC-MAC array. The binary input and weight parameters are first converted into stochastic bitstreams and go through the SC-MAC array, after which the binary-converted output is generated. The binary input values are within -1 and 1 due to tanh function, but weight values may not be. Thus, we scale them before convolution and re-scale back after

convolution. We use 4 and 2 for scale parameters for the first and second convolution layers, respectively.

Due to the way the convolution operation is defined mathematically, the input data are reused for computing different output feature maps. Our modeling, as well as our hardware architecture, assumes that these input data are reused at the binary level as opposed to the stochastic bitstream level, and new stochastic bitstreams are generated from the same binary input data whenever they are needed. Retraining of SC-DCNN is done by applying SC to the forward pass only. The B-to-S conversion is done by comparing a random number with the binary input. For random number generation we tested both LFSR and CUDA random function, but the latter, which is used in all our results, turned out to be orders-of-magnitude faster than LFSR without much difference in accuracy.

#### 3.3.2. Binary-Interfaced Stochastic Computing

1) Hardware Implementation Efficiency: Figure 9 shows the area breakdown of a MAC unit. The area of a MAC (without the gray portion in the figure) is the average value obtained by dividing the tile area by the number of MAC units. The figure shows that the accumulator area is almost the same for all the cases, and the parallel counter area is proportional to the bit-parallelism. The approximate version is very effective in reducing the parallel counter overhead.

Figure 9: Area breakdown of a MAC, where bMAC and sMAC stand for a conventional binary MAC and an SC-MAC, respectively. Each whole pie, including the *unused* portion shown in gray, represents the same area, which is the area of the bMAC; sMAC uses far less. A number in each pie represents the portion of a component in the *used area*.

Under the same area-delay product, naïve SC-MAC (1-bitserial version) can process 8 bits while the binary version processes 1 word. Our 128-bit approximate version can process nearly 256 bits, which is about 30X improvement. Increasing bit-parallelism increases parallel counter area and latency, but does not increase the overall MAC latency because the parallel counter and the accumulator can be optimized together as an accumulative parallel counter. The larger area of the accumulator in Figure 9-(d) is due to the increased critical paths, which increase the areas of both the parallel counter and accumulator due to timing optimization.

Table 3 summarizes tile synthesis result, where the data for tile size of 12x12x12 are extrapolated (could not be synthesized due to size). Extrapolation is possible because the area is linearly proportional to the size of the array and increasing tile size does not affect the critical path (affected most by bit-parallelism). The peak performance is the theoretical performance assuming that the MAC units are utilized 100%. In practice, utilization varies depending on the layer parameters and whether there are other bottlenecks in the system such as data transfer. For the SC versions we use sMAC/s, which is the number of 1-bit SC-MAC operations performed per second, since the application throughput depends on the stochastic bitstream length. The table shows that the SNG overhead, which includes that of both input and weight parameters, is quite high when the tile is small, but reduced quickly as the tile size increases.

| Tile size | Case            | Are   | ea $(mm^2)$ | Peak          |  |

|-----------|-----------------|-------|-------------|---------------|--|

|           | Case            | SNG   | MAC array   | Performance   |  |

|           | Binary —        |       | 0.094       | 98.5G MAC/s   |  |

| 4x4x4     | 64b-SC          | 0.074 | 0.042       | 6.3T sMAC/s   |  |

|           | 128b-SC approx. | 0.151 | 0.053       | 12.6T sMAC/s  |  |

|           | Binary          | —     | 0.765       | 787.7G MAC/s  |  |

| 8x8x8     | 64b-SC          | 0.220 | 0.336       | 50.4T sMAC/s  |  |

|           | 128b-SC approx. | 0.448 | 0.426       | 100.8T sMAC/s |  |

|           | Binary          | —     | 1.494       | 2.7T MAC/s    |  |

| 12x12x12  | 64b-SC          | 0.442 | 1.134       | 170.1T sMAC/s |  |

| (est.)    | 128b-SC approx. | 0.904 | 1.438       | 340.3T sMAC/s |  |

Table 3: Compute tile synthesis results.

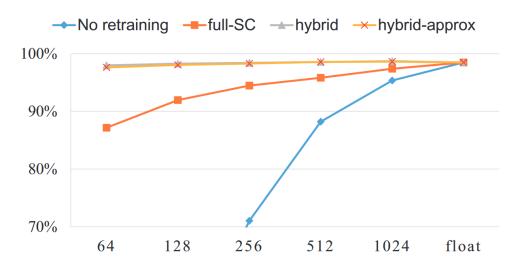

2) Overall Performance: Figure 10 shows the recognition accuracy of different schemes for different stochastic bitstream length (SBL) values. The original DCNN using floating-point arithmetic is first trained using the default training script provided in Caffe, which runs 10,000 iterations. It is followed by retraining of 5,000 iterations using different versions of SC-DCNN. We use the same parameters except that the base learning rate is decreased by 10 times, which is a common practice.

Figure 10: Recognition accuracy vs. stochastic bitstream length.

These graphs are obtained after retraining the network, except for the floating-point case. Without retraining the recognition accuracy is extremely poor, being around 88% even for SBL of 512 bits (the full-SC DCNN case), with steep decline for lower values of SBL.

The graph clearly shows that there is a significant gap in recognition performance between our hybrid DCNN and full-SC DCNN (i.e., fully-connect layers are in SC as well), suggesting the superiority of the hybrid design. Between the two versions of hybrid design, approximate vs. non-approximate versions, we see that the difference in recognition performance is negligible. However, the MNIST dataset is relatively easy, and we may find larger gap for more complex dataset, which is left for future work.

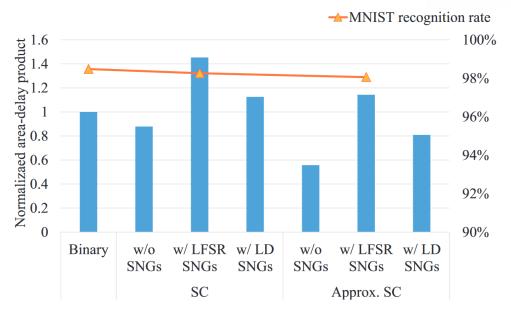

Figure 11 shows the overall performance as measured in area-delay product, which is the inverse of throughput per area, for different cases. For this comparison we use SBL of 128 bits, for both approximate and non-approximate SC-MAC cases, and the tile size is 8x8x8. Tile size being the same, utilization must also be the same for all the cases considered here, regardless of layer parameters.

Figure 11: Area-delay product comparison (SBL: 128-bit).

The graph shows that in terms of the recognition accuracy, there is only less than 1%-point difference among them. Yet in terms of throughput the approximate version can achieve about 35% higher performance over the non-approximate version, without considering SNGs. If SNGs are not considered, the best SC version can be nearly twice as area-efficient as the binary version. With recent MTJ devices the cost of SNG is getting much cheaper, but here due to the lack of accurate area information of MTJbased random number generators, we instead use the area of the recent low-discrepancy (LD) SNGs [44], which are designed for bit-parallel SC circuits and therefore well-suited for our application. This can reduce the area overhead of SNGs down to about 50% of the MAC array. Overall this graph suggests that SC-DCNN can be both accurate and area-efficient, even with SNG overhead, compared with a conventional binary version. Note that this comparison is without considering the inherent advantages of SC such as dynamic energy-quality trade-off and better error tolerance. For future technologies in which variability and noise are expected to grow, the advantages of SC will be greater.

#### 3.3.3. New Stochastic Computing Multiplication Algorithm

We compare our proposed SC multiplication method with conventional SC and fixed-point binary (short-handed as binary), in the context of a DCNN accelerator, where most computation occurs in the MAC array.

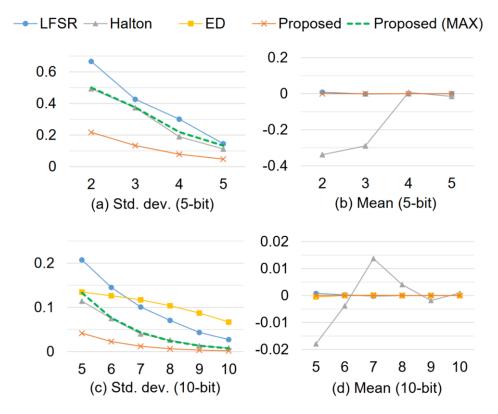

1) Accuracy Analysis of Our Proposed SC Multiplication Algorithm: The conventional SC has different flavors depending on the SNG: (1) LFSR and comparator, (2) Halton [5], and (3) evendistribution-based low-discrepancy code abbreviated as ED [44]. To evaluate accuracy, we simulate

various SC multiply algorithms in software, testing for all input combinations from 5- and 10-bit fixedpoint binary numbers. Figure 12 shows error statistics, where error is defined as the difference from the fixed-point multiplication result without rounding (thus having twice the precision). The graphs show the running statistics of error at cycle  $2^x$ , where *x* is the *x*-coordinate value. For our proposed method, at cycle  $|w|/2^{5-x}$  or  $|w|/2^{10-x}$ . Thus, it shows not only the statistics at the end of the bitstream, but also how fast the output converges. ED [44] is applied to the 10-bit case only, since it generates 32 bits per cycle. Note that our bit-parallel version and vector version (i.e., BISC-MVM) generate the same output as our SC multiplier, only faster.

Figure 12: Error statistics of various SC multipliers.

The graphs suggest that among the conventional SC methods the Halton method is the most accurate and converges fast. However, ours has much less error, about 1/3 of Halton, at all times. In addition, the figure shows the maximum absolute error of our proposed scheme, which can be calculated easily because our scheme does not rely on LFSR. Interestingly the max error of our scheme roughly coincides with the standard deviation of error of Halton, which unequivocally shows the high accuracy of our scheme. Finally, the mean graphs confirm that ours is zero-biased. Actually, the result for the Halton case depends on the prime number base. We use 2 and 3 for *x* and *w*, respectively.

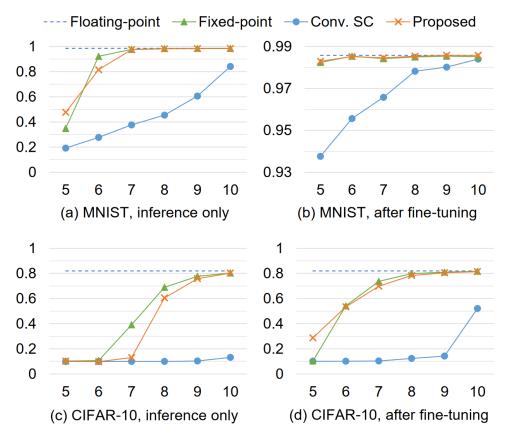

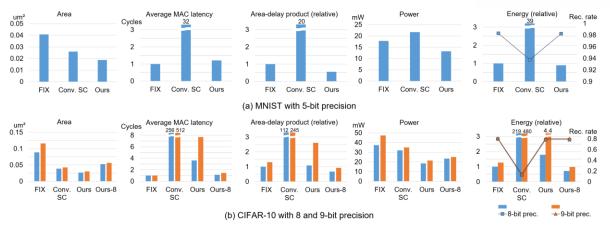

2) Recognition Accuracy of Our Proposed SC-DCNN: To evaluate the recognition performance of our SC-based DCNNs we use the Caffe framework [47], in which the convolution layer is extended for fixed-point and SC. We use two DCNNs designed for MNIST and CIFAR-10 datasets, comparing three cases: (1) fixed-point binary, (2) conventional SC based on LFSR, and (3) our proposed SC. We use the network definitions and training parameters included in the Caffe distribution. For the CIFAR-10 network we scale the input feature map before/after convolution by 128 so that the values mostly come in the [-1,1] range. We vary multiplier precision (N) from 5 to 10, with 2 additional bits for accumulation (A=2). We use a saturating accumulator/up-down counter. For the binary case the multiplication result is truncated before accumulation.

The upper graphs in Figure 13 show the test accuracy of the MNIST network. The left one is the accuracy when using the weight parameters obtained from the training of the original floating-point net. The right one is after fine-tuning for 5,000 iterations (with the same learning rate) atop the original training, which runs for 10,000 iterations. During fine-tuning, fixed-point or SC-based convolution is used in the forward pass.

Figure 13: MNIST, CIFAR-10 recognition accuracy (the first 5,000 test images), where *x*-axis is multiplier precision including the sign bit.

The graphs reveal many interesting points. First, fixed-point binary shows very good recognition performance, and 5- or 7-bit precision seems to be enough for MNIST depending on whether fine-tuning is done. Second, without fine-tuning conventional LFSR-based SC can have much lower accuracy, though fine-tuning can recover most of the accuracy loss. Third, under the same precision setting, our SC-DCNN achieves almost the same accuracy as the fixed-point binary. While this is significant, MNIST is relatively easy and a similar result is achieved in previous work as well [9].

We run a similar experiment with CIFAR-10, the result of which is summarized in Figure 13-(c), (d). Again, we use the same precision setting across different methods. For the fixed-point case, achieving the floating-point recognition rate requires 9- to 10-bit precision without fine-tuning or 8- to 9-bit with fine-tuning. On the other hand, conventional LFSR-based SC shows a very poor performance even with fine-tuning, whereas our proposed SC shows almost the same performance as binary, especially with fine-tuning. Specifically, the fact that our SC-DCNN can achieve near-fixed-point performance even without fine-tuning at 9~10 bits underscores the high accuracy of our BISC-MVM. Eventually, however, without retraining the small error of our SC multiplier creates a performance gap at 7~8 bits; nonetheless, it is successfully filled via retraining, making our SC-DCNN virtually indistinguishable from the fixed-point version in terms of accuracy.

3) Implementation Efficiency of Our Proposed SC-DCNN: To evaluate implementation efficiency we have designed MAC arrays in Verilog RTL based on our proposed (i) BISC-MVM, (ii) LFSR-based conventional SC, and (iii) fixed-point binary, and synthesized them with Synopsys Design Compiler using TSMC 45nm technology as did in Section 3.3.2. The three cases are designed to use the common setting as much as possible, including size (256 MACs), input/output data representation (two's complement), and multiplier/accumulator precisions. Specifically, multiplier precision, N, is set to 5 bits for MNIST, and varied to 8~9 bits for CIFAR-10. The accumulator is saturating and A is 2 bits as before. All three cases are synthesized for the same clock frequency of 1GHz.

SNG sharing is enabled for the SC cases. In particular in the conventional SC case, the SNG for the weight parameter is shared across all SC-MACs within the MAC array. Similarly, for our BISC-MVM, an FSM and a down counter are shared across all SC-MACs. Results are summarized in Figure 14, where we include the bit-parallel processing option for the CIFAR-10 experiment, with the parallelism of 8 bits.

ULSAN NATIONAL INSTITUTE OF SCIENCE AND TECHNOLOGY

Figure 14: Comparison of MAC arrays: fixed-point binary version ("FIX"), LFSR-based conventional SC version ("Conv. SC"), and our proposed BISC-MVM (Ours and Ours-8 are our bit-serial and 8-bit-parallel versions, respectively).

As expected, SC designs require smaller area than the binary, with our proposed scheme (in particular, the bit-serial version) being the smallest. Also, the area difference between SC and binary is larger when the precision is higher, which is due to the quadratic relationship between precision and binary multiplier complexity. What may be surprising is that the area difference is not nearly as high as the latency difference between SC and binary. This is because of the large conversion overhead from binary number to stochastic number and back, as confirmed by area breakdown in Table 4.

| MP Case |          | Design      | SNG     |        | Mult./            | Par. CNT/ | Accum./ | Tetal |

|---------|----------|-------------|---------|--------|-------------------|-----------|---------|-------|

| MP      | Case     | Design      | Reg/FSM | Combi. | XNOR <sup>a</sup> | 1s CNT    | UD CNT  | Total |

|         | Binary   | Fixed-point | _       | -      |                   | _         | 66.3    | 155.2 |

| 5       | Conv. SC | LFSR        | 51.5    | 19.1   | 1.8               | _         | 64.9    | 137.2 |

|         |          | Halton      | 87.7    | 18.3   | 1.8               | _         | 64.9    | 172.7 |

|         | Proposed | Bit-serial  | 31.2    | 6.0    | 38.8              | -         | 66.7    | 142.7 |

|         | Binary   | Fixed-point | _       |        | 305.0             | -         | 110.1   | 415.1 |

|         |          | LFSR        | 89.6    | 37.0   | 1.8               | -         | 104.4   | 232.8 |

|         | Conv. SC | Halton      | 203.7   | 33.9   | 1.8               | _         | 108.0   | 347.3 |

| 9       |          | ED          | 346.8   | 226.3  | 57.9              | 136.0     | 124.9   | 891.9 |

|         | Proposed | Bit-serial  | 60.9    | 11.8   | 80.6              | -         | 103.4   | 256.7 |

|         |          | 8b-par.     | 38.6    | _b     | 78.7              | 108.5     | 111.1   | 336.9 |

|         |          | 16b-par.    | 37.7    | _b     | 80.6              | 174.1     | 112.2   | 404.7 |

|         |          | 32b-par.    | 23.8    | _b     | 76.9              | 239.4     | 107.4   | 447.5 |

Table 4: Area breakdown of a MAC (synthesis result).

*Note:* a. This is the down counter for our proposed method.

b. This is not zero, but includes a small mux, whose area is included in the ones counter (1s CNT).

Table 4 shows detailed area breakdown of a single MAC for two multiplier precision (MP) settings: 5 bits and 9 bits. We add a number of other designs not included in the DCNN-level comparison, but it is important to note that these numbers are area only, and latency must be taken into account when comparing different designs. For instance, the ED case [44], which is evaluated for the 9-bit precision setting only, uses a bit-parallel SNG that generates 32 bits per cycle, requiring 32X as many XNOR gates and a parallel counter (Column 7) while simultaneously reducing latency by 32X. Similarly, our proposed SC-MAC, even for the bit-serial version, has a very low latency compared to the conventional SC (see Figure 14).

From the table we can make the following observations. First, ED is quite cost-efficient. In fact, it has the lowest area-delay-product (ADP) among the conventional SC methods. However, ED has also the lowest quality in terms of multiplication accuracy (see Figure 12-(c)). Second, Halton has a very good accuracy but also the highest area per throughput. Third, while in the previous work accuracy and ADP are only a trade-off, ours improves both of them simultaneously. The average delay of ours is data-dependent, but very small as shown in Figure 14. In particular the bit-serial version has a latency of up to 7.7 cycles for CIFAR-10, but it is effectively suppressed by the bit-parallel version. Fourth, in the 9-bit precision setting, increasing the bit-parallelism for our proposed SC-MAC increases the total area, only modestly. However, the 8-bit parallelism already achieves very low average latency and thus has the lowest ADP (not shown in the graph). Finally, unlike the binary case, our proposed scheme becomes more cost-efficient when vectorized due to the sharing of the FSM and down counter. This helps explain the larger gap between the binary and our proposed designs (and between Ours-8 and Ours) in Figure 14 than in Table 4.

In summary, our proposed BISC-MVM can achieve 29~44% lower ADP even when compared with the fixed-point binary design of the same accuracy, thanks to the very low average MAC latency of our scheme.

Since we use the same clock frequency for all designs, power dissipation as reported by the synthesis tool is largely proportional to the area result, with one exception. We found that LFSRs have unusually high-power dissipation per area, negatively impacting power efficiency of the conventional SC case. As a result, the conventional SC case turns out to be about as high power-dissipating as the binary case even before considering its high toll on latency. Of course, this weakness of conventional SC is mostly due to the conversion overhead between stochastic number and binary number, and ultimately because we are targeting BISC, and things could be very different if we exclude such overheads as would be more relevant for a fully-parallel architecture.

Our new proposed SC-DCNN has the lowest power consumption and extremely low latency, which make it about 40X (for MNIST) and 300X~490X (for CIFAR-10) more energy-efficient in the MAC

array than the conventional SC while at the same time being more accurate. Our proposed solution is also slightly more energy-efficient  $(23 \sim 29\%)$  for CIFAR-10 and 10% for MNIST) than the fixed-point binary while having nearly the same accuracy. Note that this comparison is without considering the inherent advantages of SC such as dynamic energy-quality trade-off and better error tolerance. For future technologies in which variability and noise are expected to grow, the advantages of SC may be greater.

Table 5 provides a brief comparison with previous neural network accelerators. Due to differences in many aspects including target neural networks, we compare performance in GOPS, with 1 MAC counted as 2 operations. SC's (long) latency is taken into account when computing GOPS. SNGs are included for area calculation except for ArXiv'15. Note also that the first two cases (MWSCAS'12 and ISSCC'15) are not directly comparable with the rest, since they include large on-chip buffers, which should dominate area.

|        |                         | Frequency | Area* | GOPS   | GOPS/mm <sup>2</sup> | Tech. | Scaled GOPS/mm <sup>2</sup> *** | Scope for area                 |

|--------|-------------------------|-----------|-------|--------|----------------------|-------|---------------------------------|--------------------------------|

| Binary | MWSCAS'12               | 400 MHz   | 12.50 | 160.00 | 12.80                | 45nm  | 65                              | Total chip                     |

|        | ISSCC'15                | 200 MHz   | 10.00 | 411.30 | 41.13                | 65nm  | 869                             | Total chip                     |

|        | ASPLOS'14               | 980 MHz   | 0.85  | 501.96 | 592.94               | 65nm  | 2,556                           | NFU <sup>**</sup> only         |

|        | GLSVLSI'15              | 700 MHz   | 0.98  | 274.00 | 278.85               | 65nm  | 1,683                           | SoP ( $\simeq$ MAC) units only |

| SC     | ArXiv'15                | 400 MHz   | 0.09  | 1.01   | 11.91                | 65nm  | 126                             | One neuron                     |

|        | DAC'16                  | 1000 MHz  | 0.06  | 75.74  | 1262.33              | 45nm  | 2,556                           | One neuron with 200 inputs     |

|        | Proposed (9b-precision) | 1000 MHz  | 0.06  | 351.55 | 6242.37              | 45nm  | 12,641                          | MAC array (size: 256)          |

Table 5: Comparison with previous neural network accelerators.

\*Note 1: See the rightmost column for the scope of area (in mm<sup>2</sup>)

\*\*Note 2: NFU can also perform pooling and activation functions.

\*\*\*Note 3: GOPS/mm<sup>2</sup> normalized by frequency and (1/technology)<sup>2</sup>

Compared to a recent SC design [9], ours has much higher area efficiency. Note that the previous work is a fully-parallel architecture, but ours has scalability, which cannot be provided by the previous work. Compared to the others, our architecture has the highest area-efficiency.

In addition to the differences in terms of the scope of area and the level of implementation, the performance-per-area (GOPS/mm<sup>2</sup>) metric in Table 5 uses different frequencies and technologies. Thus, we provide another comparison which normalizes frequency and technology effects, shown in the 8<sup>th</sup> column. The technology is normalized in square because area scales at the square of technology node ("Scaled GOPS/mm<sup>2</sup>" = GOPS/mm<sup>2</sup> \* Tech.<sup>2</sup> / frequency). In this comparison, DAC'16 and ALPLOS'14 tie for the second position while our proposed SC-MVM shows the best compute density.

There are other recent SC-based DCNNs [48]-[49], which however do not provide area/power numbers (focusing on accuracy or targeting FPGAs), as well as DCNNs based on concepts similar to SC [50]. In particular XNOR-Net [50] shows that through clever learning tricks, the same recognition accuracy as that of a floating-point network can be achieved using XNOR computation only even for

AlexNet [1]. Such training methods are orthogonal to our contributions, and can bolster the case for SC-DCNNs in general.

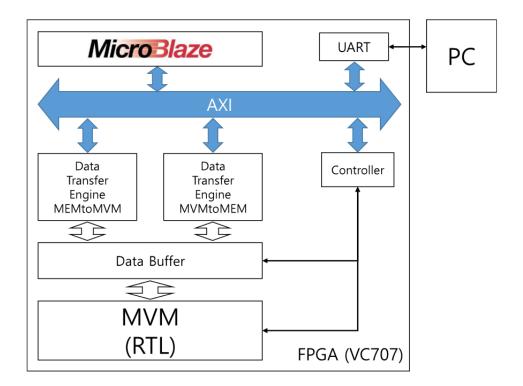

# 3.3.4. Small FPGA Prototype

We have also prototyped a DCNN accelerator on an FPGA board. The goal of this is two-fold: to validate our BISC MVM-based DCNN accelerator as well as to assess our new SC multiplication algorithm's suitability for FPGA implementations. We have used a Xilinx VC707 board, which includes a Virtex-7 FPGA and a DDR3 memory. Figure 15 illustrates the system architecture, where the MicroBlaze softcore is used to run the software part, and an AXI bus and an AXI memory controller are used to connect hardware modules to the DDR3 memory. The main MVM module (which contains 8x8 MAC units) is designed in Verilog HDL, for the conventional binary case as well as various proposed SC cases. For the prototyping we have used LeNet-5 and CIFAR-10 DCNN, with precisions as listed in Table 6. Only the convolution layers are implemented on the MVM while the other layers are implemented in software on the MicroBlaze. We have verified the correct operation, matching with the software simulation results produced by Caffe on a GPU.

Figure 15: Block diagram of MVM-based accelerator implementation on VC707.

| Target DNN                 | Case                   | Frequency | LUT                  | FF                | DSP  |

|----------------------------|------------------------|-----------|----------------------|-------------------|------|

| LeNet-5 (5-bit precision)  | FIX<br>LFSR-SC         |           | 2494<br>1161         | 448<br>469        |      |

| CIFAR-10 (9-bit precision) | Ours<br>FIX<br>LFSR-SC | 100 MHz   | 1035<br>6976<br>1742 | 457<br>704<br>729 | None |

|                            | Ours<br>Ours-8         |           | 1668<br>3585         | 722<br>727        |      |

-

Table 6: Comparison of various MVM implementations on FPGA (#MAC=8x8).

Table 6 shows our FPGA synthesis result, after technology mapping and place and route. For fair comparison, LUT-based MACs are used for the binary case, as DSP blocks are hardly used in SC-based designs. No manual optimization is attempted for any design; all optimization is that of the Xilinx RTL synthesis tool. Even then, we can see from the table that SC-based designs use much less resources compared with the binary designs, thanks to the simpler computational units. Thus SC-based designs can be useful for cost-sensitive applications. On the other hand, conventional SC designs take much longer latency as shown in Figure 14. Our proposed SC designs including the 8-bit parallel version for CIFAR-10, achieves near 1 cycle latency for MNIST and less than 1.5 cycles for CIFAR-10, and thus consistently achieve the highest efficiency in terms of area-delay product. Since our SC-MAC does not utilize DSP blocks, a hybrid approach that combines both binary MVMs and SC-MVMs on a single FPGA could provide the best solution in terms of FPGA resource utilization, which remains for future work.

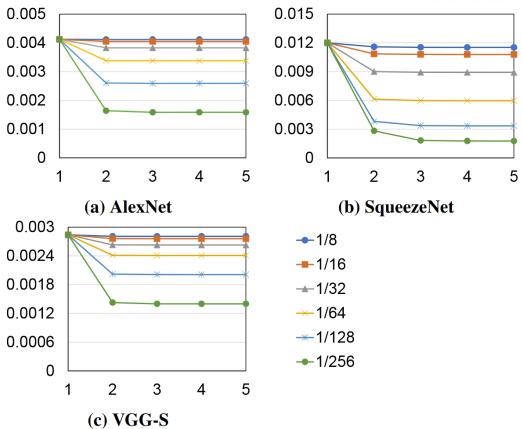

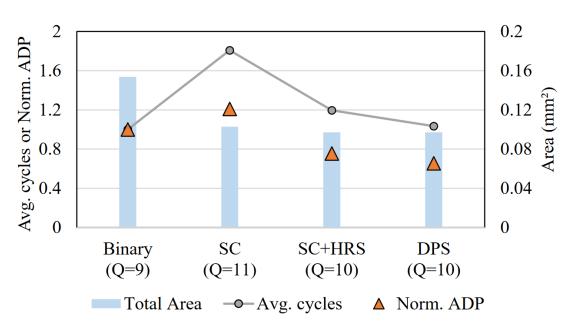

# **IV.** Stochastic Computing in Synergy with Quantization